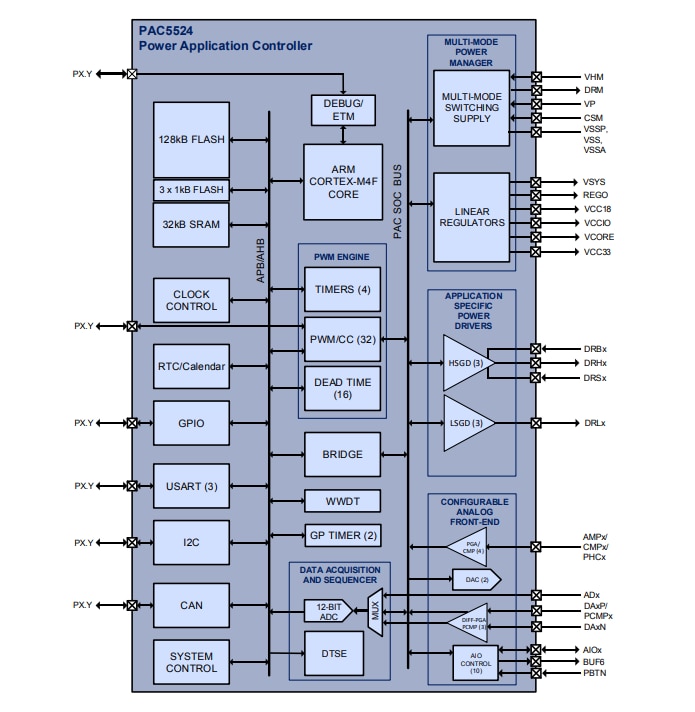

Qorvo PAC5524 High Pin-Count Motor Controller & Driver

Qorvo PAC5524 High Pin-Count 70V Motor Controller and Driver is a Power Application Controller© (PAC) optimized for a high-pin count and high-speed BLDC motor control. The PAC5524 integrates a 150MHz Arm® Cortex®-M4F 32-bit microcontroller core with Active-Semi’s proprietary and patent-pending Multi-Mode Power Manager™, Configurable Analog Front-End™, and Application Specific Power Drivers™. With these features, the PAC5524 forms an ideal compact microcontroller-based power and motor control solution.The PAC5524 microcontroller offers 128kB of embedded FLASH and 32kB of SRAM memory, a 2.5MSPS analog-to-digital converter (ADC) with programmable auto-sampling of up to 24 conversion sequences, 3.3V IO, flexible clock control system, PWM and general-purpose timers, and several serial communications interfaces.

The Multi-Mode Power Manager (MMPM) provides an “all-in-one” efficient power management solution for multiple types of power sources. The MMPM has a configurable multi-mode switching supply controller capable of operating a buck or SEPIC converter and up to four linear regulated voltage supplies. Additionally, the Application Specific Power Drivers (ASPD) are power drivers designed for a half-bridge, H-bridge, 3-phase, and general-purpose driving. Furthermore, the Configurable Analog Front End (CAFE) comprises differential programmable gain amplifiers, single-ended programmable gain amplifiers, comparators, digital-to-analog converters, and I/Os for programmable and interconnective signal sampling, feedback amplification, and sensor monitoring of multiple analog input signals.

The PAC5524 High Pin-Count Motor Controller and Driver is available in an 8mm x 8mm, 64-lead, QFN package and is designed for compact battery-powered BLDC motor applications.

Features

- Multi-Mode Power Manager™ (MMPM)

- Optional multi-mode switching supply controller configurable for DC/DC Buck or SEPIC topologies

- 20V max direct DC supply

- Integrated LDOs for MCU core, IO, analog with power and hibernate management

- Power and temperature monitor, warning and fault detection

- Low-power total hibernate mode, IQ = 18µA

- Configurable Analog Front-End™ (CAFE)

- Three differential programmable-gain amplifiers

- Four single-ended programmable-gain amplifiers

- 2.5V ADC reference

- Programmable over-current shutdown

- Hibernate push-button wake-up

- Power supply monitoring via ADC

- Application-Specific Power Drivers™ (ASPD)

- Integrated level shifters and pre-drivers

- Three low-side and three high-side gate drivers with 1.5A gate driving capacity

- Break-before-make (BBM) hardware dead-time enforcement to prevent shoot-through

- Configurable propagation delay and fault protection

- OC, UV protection

- MCU

- 150MHz Arm® Cortex®-M4F MCU

- Hardware multiplier and divider

- Single-precision Floating Point Unit (FPU)

- Nested Vectored Interrupt Controller (NVIC) with 32 interrupts and eight priority levels

- Clock-gating for low-power operation

- Embedded Trace Macrocell (ETM) for in-system debugging in real-time without breakpoints

- Memory

- 128kB FLASH, 32kB SRAM with ECC

- 2 x 1kB INFO FLASH for manufacturing information

- 1 x 1kB INFO FLASH for user parameter storage and application configuration code

- Four-level user-configurable code protection

- ADC

- 12-bit 2.5MSPS SAR ADC

- Dynamic Triggering and Sequence Engine (DTSE)

- Up to 16 configurable sequences

- Dedicated memory for conversion results

- IO

- 3.3V digital input/output or analog input for ADC

- Configurable weak pull-up or pull-down

- 6mA to 25mA minimum configurable drive strength

- Flexible peripheral MUX allowing each IO pin to select from up to eight peripheral functions

- Flexible interrupt controller

- Flexible Clock Control System (CCS)

- 300MHz PLL from internal 2% oscillator

- 20MHz ring oscillator

- Optional 20MHz external clock input

- Timing Generators

- Four 16-bit PWM timers with up to 8 CCR output units each

- 24-bit SysTick count-down timer

- Windowed Watchdog Timer (WWDT)

- 24-bit Real-Time Clock (RTC) with calendar and alarm

- 2 x 24-bit General-purpose count-down timers with interrupt

- Hibernate wake-up timer for sleep modes from 0.125s to 8s

- Communication Peripherals

- 3 x USART (UART or SPI)

- I2C master/slave

- SPI master/slave, up to 25MHz

- CAN 2.0B Controller

- SWD or JTAG serial debug interfaces

- Embedded Trace Macrocell (ETM)

- 8b/16b CRC Engine

- 96-bit Unique ID

- Physical

- -40°C to +125°C ambient temperature range

- QFN 8mm x 8mm 64-pin package

- Exposed pad for thermal management

Related Development Tools

Block Diagram