# ADRV9001 System Development User Guide UG-1828

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

Preliminary Technical Data

# System Development User Guide for the RF Agile Transceiver Family

#### ADRV9001 SYSTEM DEVELOPMENT USER GUIDE OVERVIEW

The ADRV9001 is family designator assigned to the System Development User Guide (UG-1828 for new ADRV9002, ADRV9003, ADRV9004, and upcoming additional family members).

The ADRV9001 System Development User Guide covers:

- ADRV9002 integrated dual RF transceiver

- ADRV9003 integrated single RF transceiver (excludes DPD)

- ADRV9004 integrated dual RF transceiver (excludes DPD)

This user guide provides details on functionality across the entire family. Some family members do not include all the features or functions. Refer to the individual product data sheet for each product available features and functions.

# UG-1828

# **TABLE OF CONTENTS**

| How To Use This Document5                                      | LVDS Synchronous Serial Interface (LVDS-SSI)  | 54  |

|----------------------------------------------------------------|-----------------------------------------------|-----|

| Block Diagram6                                                 | Power Saving for LSSI                         | 57  |

| Product Highlights7                                            | SSI Timing Parameters                         | 57  |

| ADRV90027                                                      | CSSI/LSSI Testability and Debug               | 58  |

| Bandwidth And Sample Rate Support7                             | API Programming                               | 59  |

| ADRV90039                                                      | Microprocessor and System Control             | 60  |

| ADRV90049                                                      | System Control                                | 61  |

| ADRV9001 Example Use Cases10                                   | Timing Parameters Control                     | 61  |

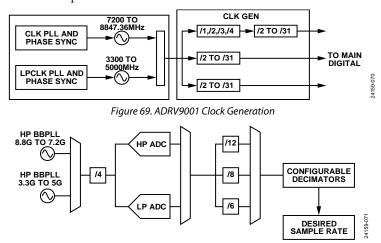

| ADRV9001 In a Single-Band 2RT2R FDD Type Small-Cell            | Clock Generation                              | 75  |

| Application10                                                  | Clock Generation                              | 75  |

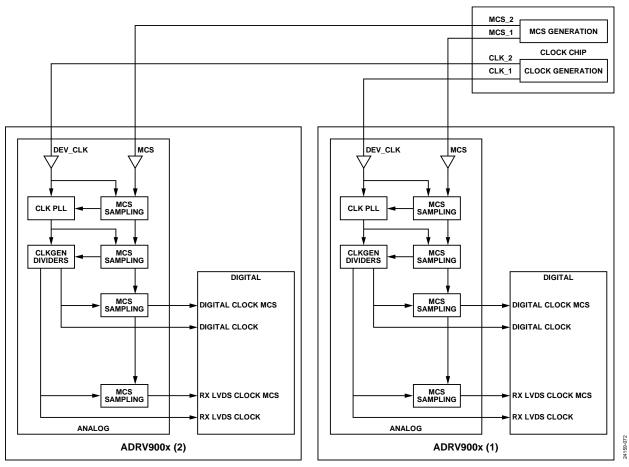

| ADRV9001 in Dual-Band 2RT2R FDD Type Small-Cell                | Multichip Synchronization                     | 77  |

| Application                                                    | Introduction                                  | 77  |

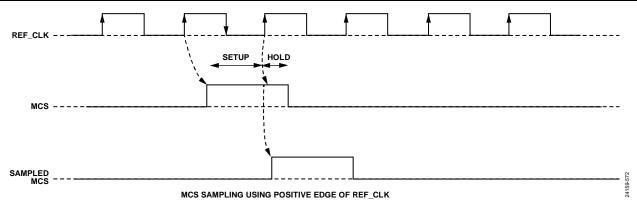

| ADRV9001 in Single-Band 2T2R TDD Type Small-Cell Application14 | Theory of Operation                           | 77  |

| ADRV9001 in 1T1R FDD with DPD Type Application 16              | MCS Substates (Internal MCS State Transition) | 80  |

| ADRV9001 in TETRA Type Portable Radio Application 18           | Procedure                                     | 80  |

| ADRV9001 in DMR Type Portable Radio Application 20             | Synthesizer Configuration and LO Operation    | 82  |

| ADRV9001 in FDD Type Repeater Application22                    | Clock Synthesizer                             | 82  |

| ADRV9001 in a FDD Type Repeater Application Using              | RF Synthesizer                                | 82  |

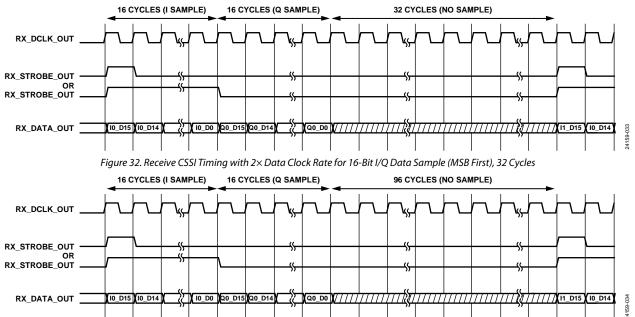

| Internal Loopbacks24                                           | Auxiliary Synthesizer                         | 83  |

| ADRV9001 in TDD Type Repeater Application26                    | External LO                                   | 83  |

| ADRV9001 in Radar Type Application28                           | API Operation                                 | 85  |

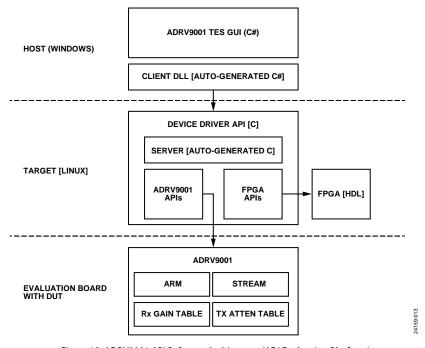

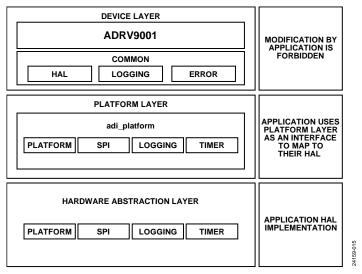

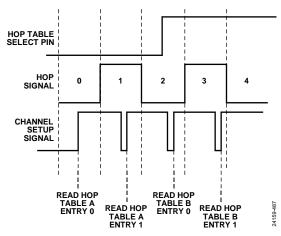

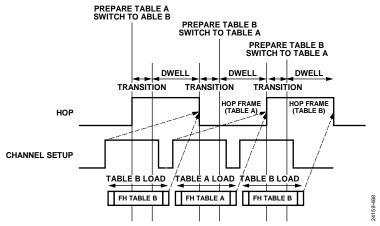

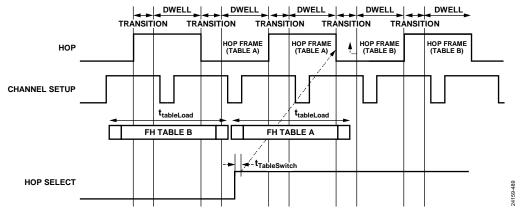

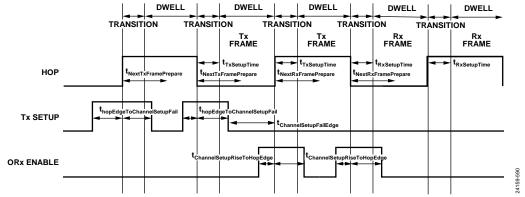

| Software System Architecture Description30                     | Frequency Hopping                             | 87  |

| Software Architecture30                                        | Key Signals                                   | 87  |

| Folder Structure31                                             | Modes of Operation                            | 88  |

| Software Integration                                           | Channel and Profile Selection                 | 89  |

| Hardware Abstraction Layer                                     | Frequency hopping operation ranges            | 89  |

| Developing the Application34                                   | Frequency hopping table                       | 89  |

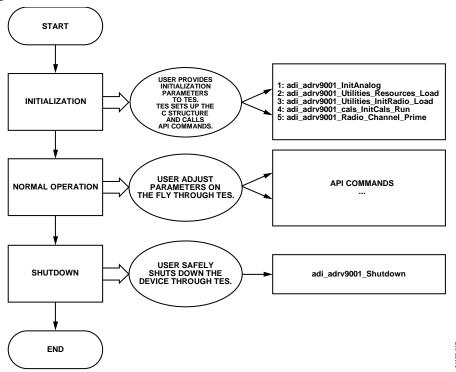

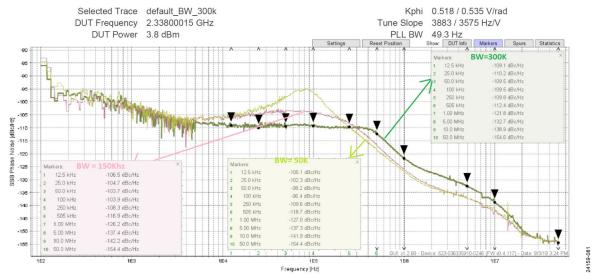

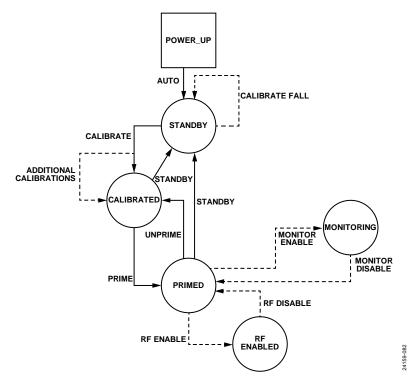

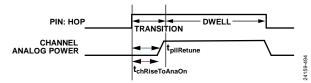

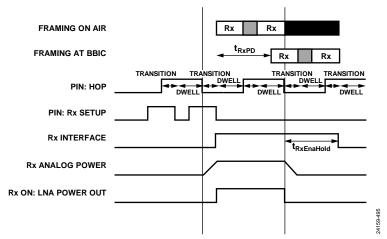

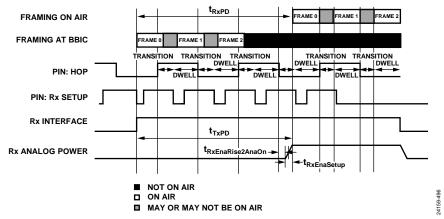

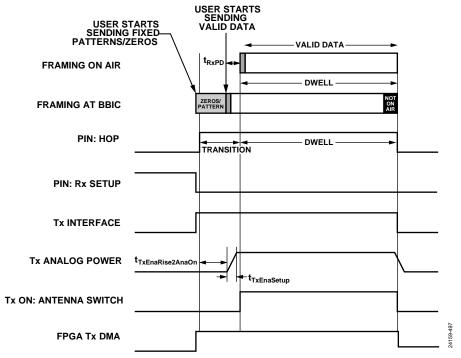

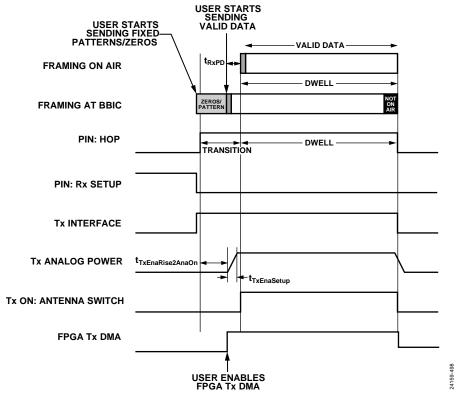

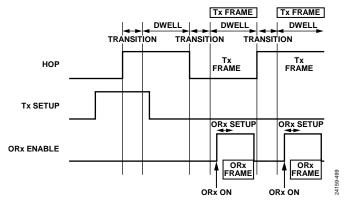

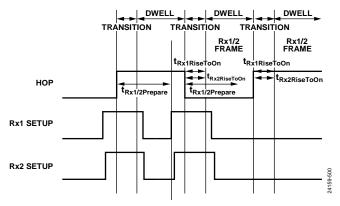

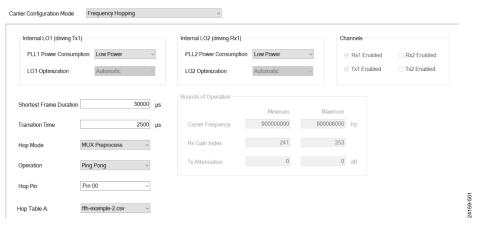

| System Initialization and Shutdown                             | Frequency Hopping Timing                      | 93  |

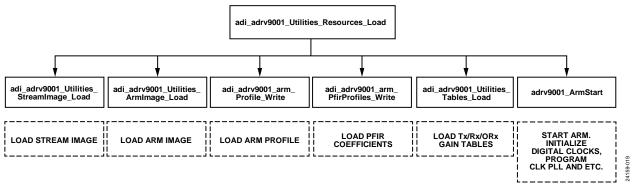

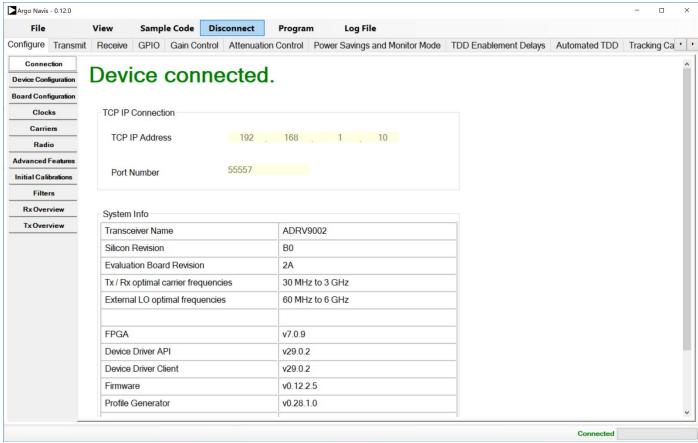

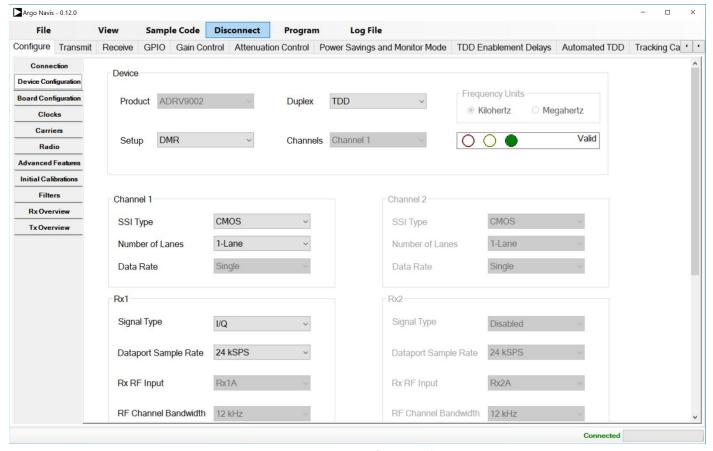

| TES Configuration and Initialization36                         | Additional Frequency Hopping Operations       | 97  |

| API Initialization Sequence                                    | Diversity Mode                                | 100 |

| Shutdown Sequence39                                            | Frequency Hopping with Rx/ORx Gain Control    | 101 |

| Serial Peripheral Interface (SPI)40                            | Frequency Hopping TES Examples                | 101 |

| SPI Configuration40                                            | Transmitter Signal Chain                      | 106 |

| SPI Bus Signals41                                              | Data Interface                                | 106 |

| SPI Data Transfer Protocol41                                   | Datapath                                      | 107 |

| Timing Diagrams                                                | Digital Front End (DFE)                       | 107 |

| Data Interface45                                               | Analog Front End (AFE)                        | 113 |

| General Description45                                          | Transmit Data Chain API Programming           | 113 |

| Electrical Specification45                                     | Receiver/Observation Receiver Signal Chain    | 114 |

| CMOS Synchronous Serial Interface (CMOS-SSI)47                 | Receive Data Chain                            | 116 |

# **Preliminary Technical Data**

| Analog Front-End Components117                          | Board Configuration186                                    |

|---------------------------------------------------------|-----------------------------------------------------------|

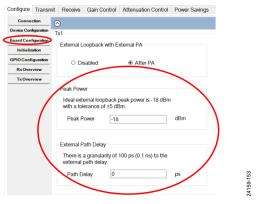

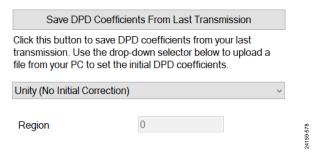

| LPF                                                     | Save and Load DPD Coefficients from Last Transmission.187 |

| ADC118                                                  | DPD API Programming187                                    |

| Digital Front End Components                            | DPD Tuning and Testing188                                 |

| DC Offset                                               | General-Purpose Input/Output and Interrupt Configuration  |

| QEC119                                                  |                                                           |

| DDC120                                                  | Digital GPIO Operation192                                 |

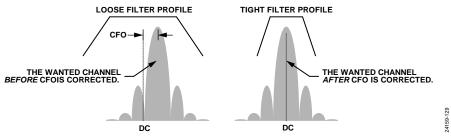

| Frequency Offset Correction                             | Analog GPIO Operation195                                  |

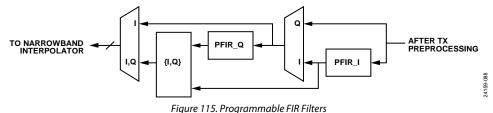

| PFIR                                                    | Interrupt196                                              |

| RSSI                                                    | Auxiliary Converters and Temperature Sensor198            |

| Receive Data Chain API Programming121                   | Auxiliary DAC (AuxDAC)198                                 |

| Transmitter/Receiver/Observation Receiver Signal Chain  | Auxiliary ADC (AuxADC)198                                 |

| Calibrations                                            | Temperature Sensor199                                     |

| Initial Calibrations                                    | RF Port Interface Information200                          |

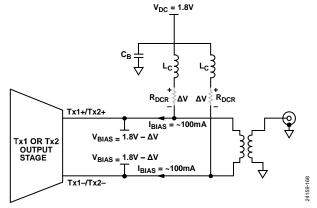

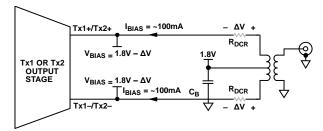

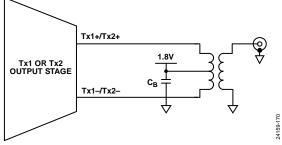

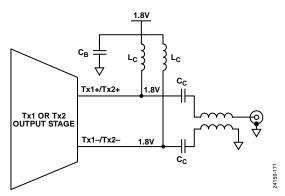

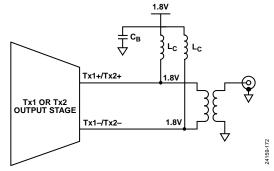

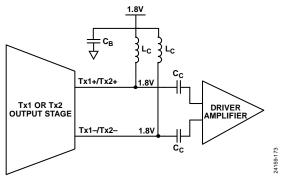

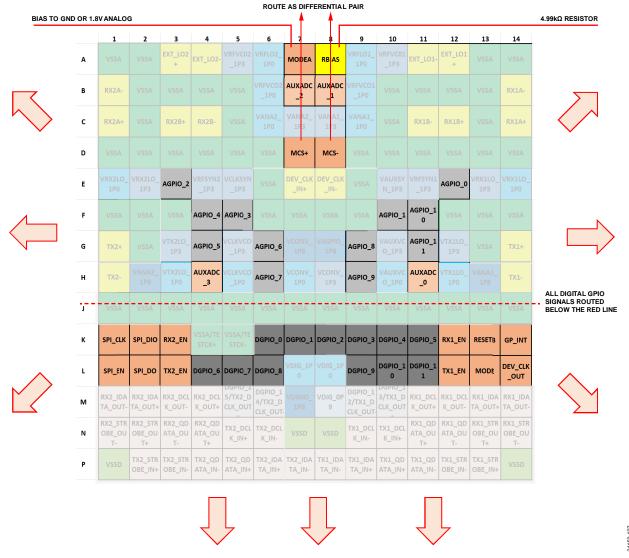

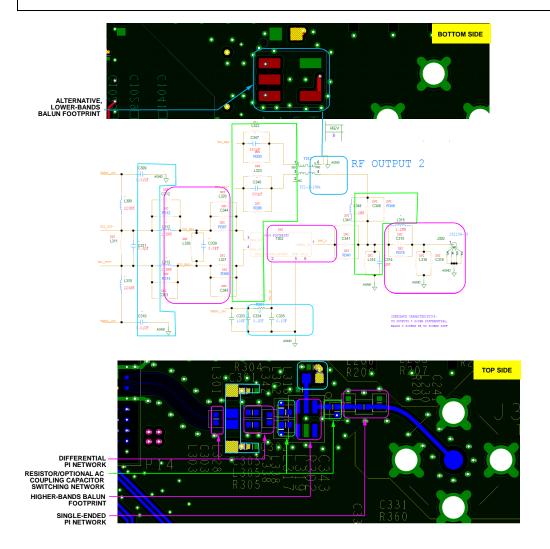

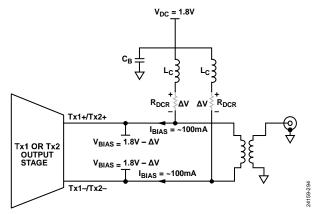

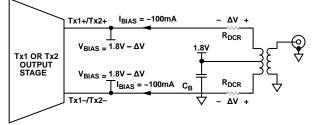

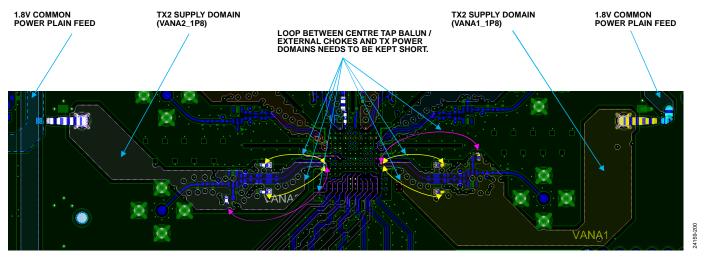

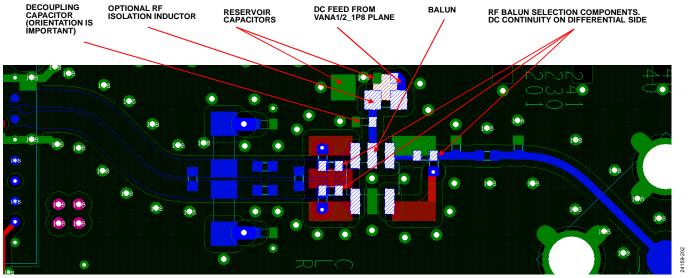

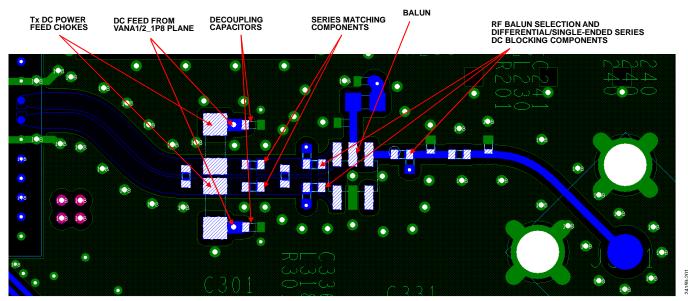

| Tracking Calibrations                                   | Transmit Ports: TX1± and TX2±200                          |

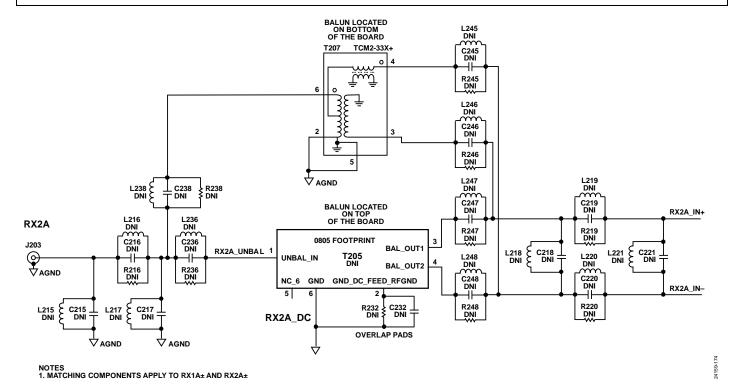

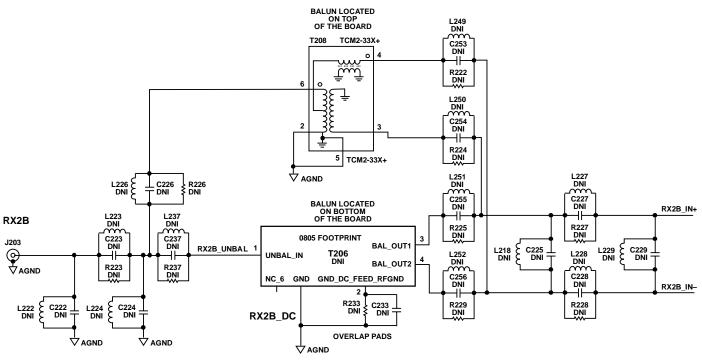

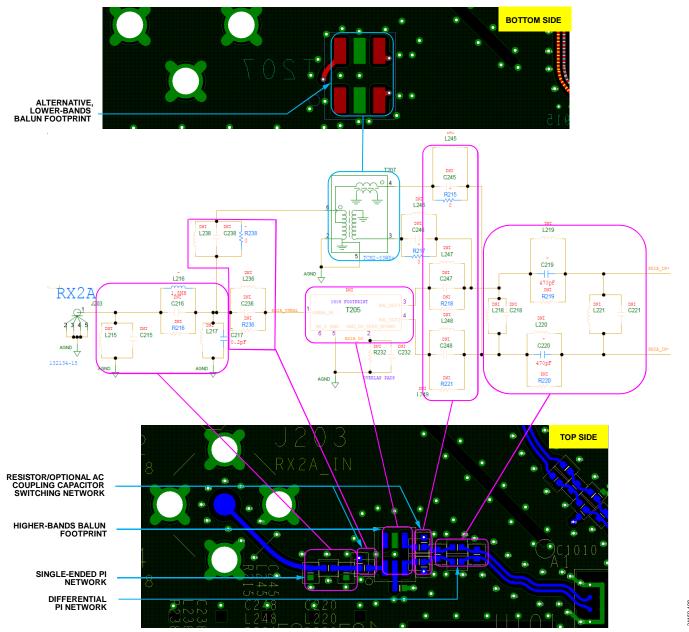

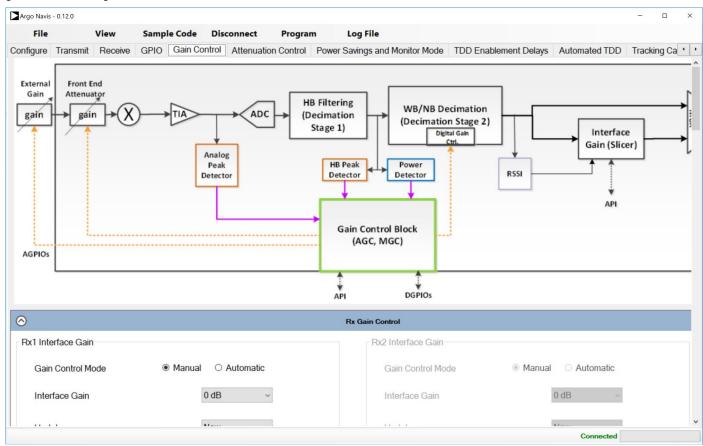

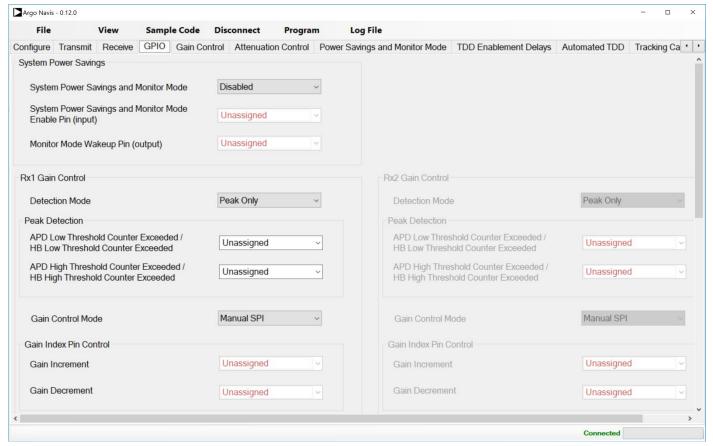

| Receiver Gain Control                                   | Receive Ports: RX1A±, RX1B±, RX2A±, and RX2B±200          |

| Receiver Datapath                                       | External LO Ports: LO1± and LO2±200                       |

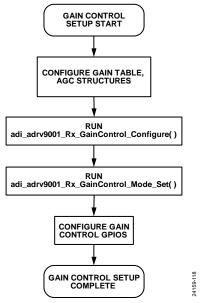

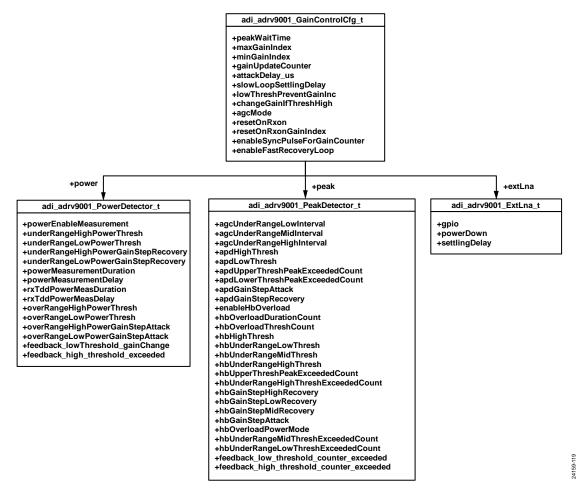

| Gain Control Modes                                      | Device Clock Port: DEV_CLK1±200                           |

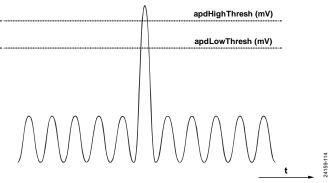

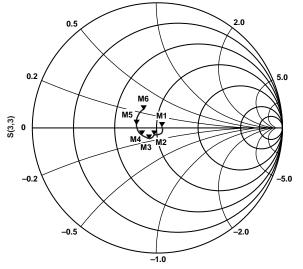

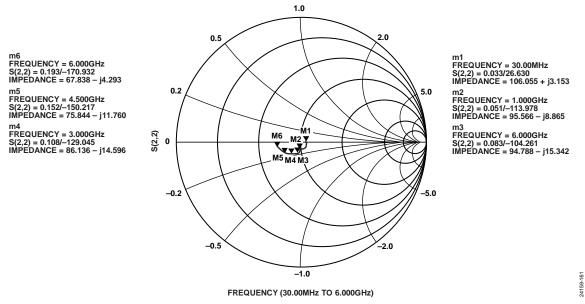

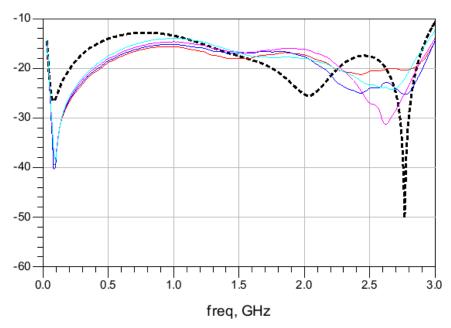

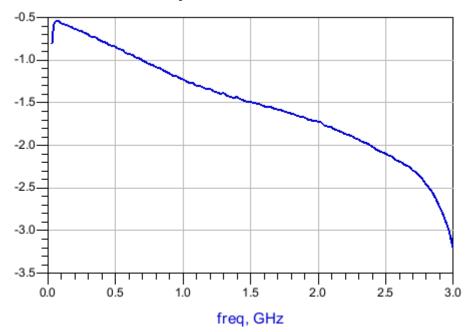

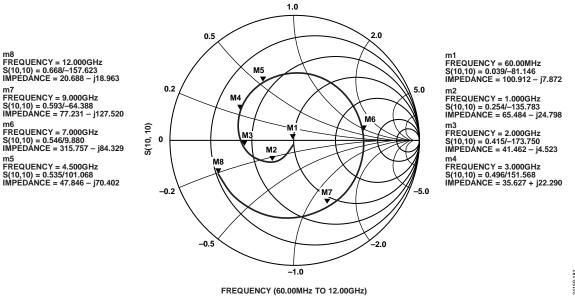

| Gain Control Detectors                                  | RF Rx/Tx Ports Impedance Data200                          |

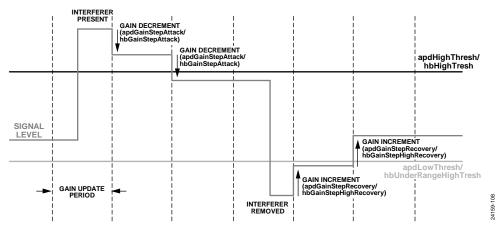

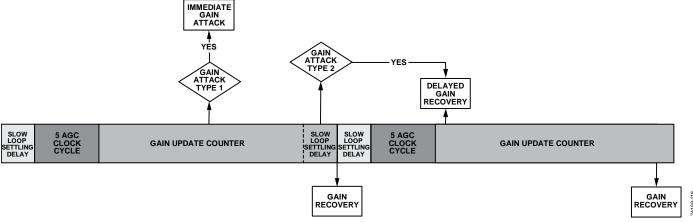

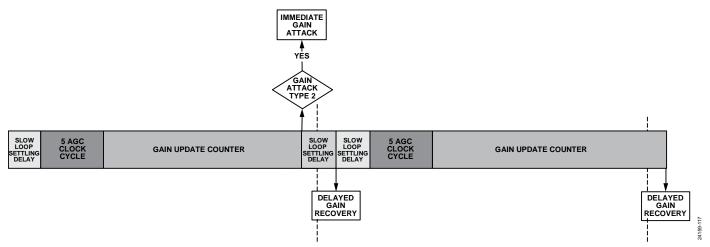

| AGC Clock and Gain Block Timing 149                     | General Receiver Port Interface203                        |

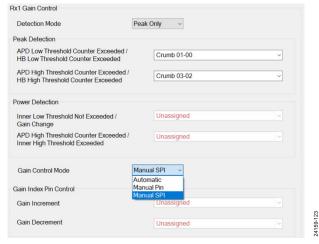

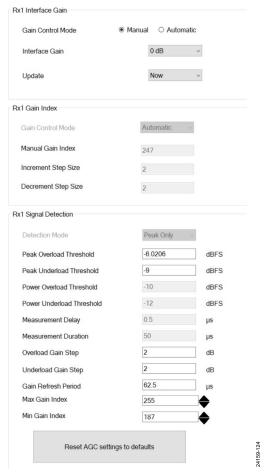

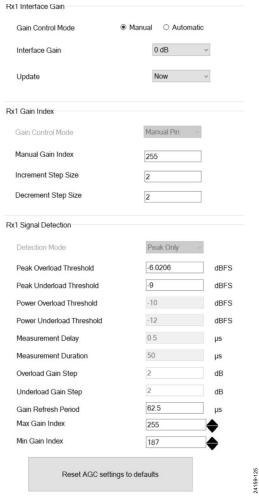

| Analog Gain Control API Programming 150                 | General Transmitter Bias and Port Interface204            |

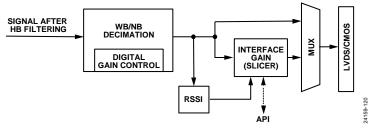

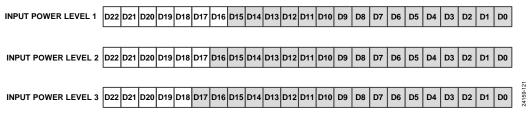

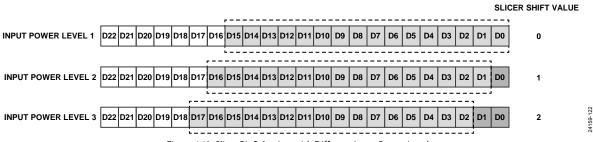

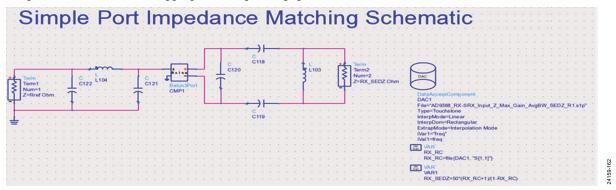

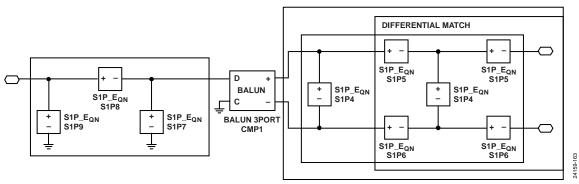

| Digital Gain Control and Interface Gain (Slicer) 157    | Impedance Matching Network Examples207                    |

| Digital Gain Control and Interface Gain API Programming | Receiver RF Port Impedance Matching Network207            |

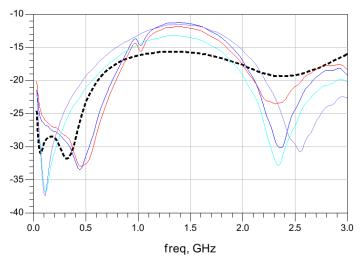

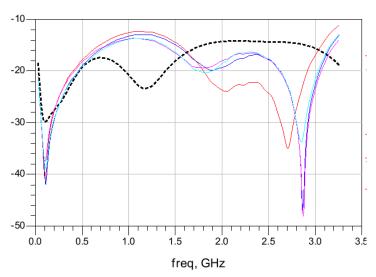

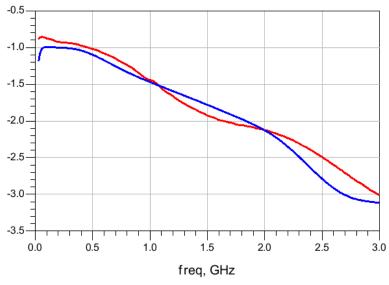

|                                                         | Receiver RF Port Impedance Match Measurement Data210      |

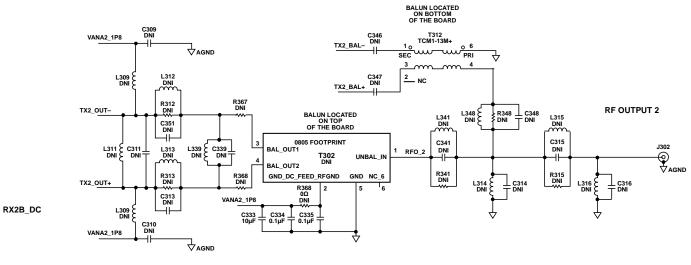

| Usage Recommendations                                   | Transmitter RF Port Impedance Matching Network212         |

| TES Configuration and Debug information                 | Transmitter RF Port Impedance Match Measurement Data      |

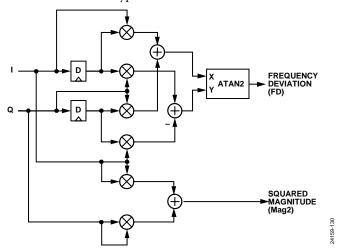

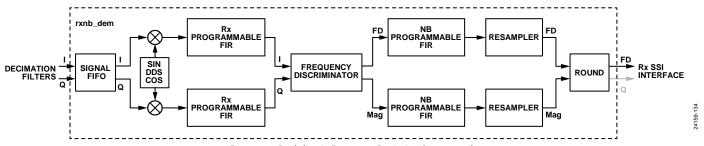

| Rx Demodulator                                          | 213                                                       |

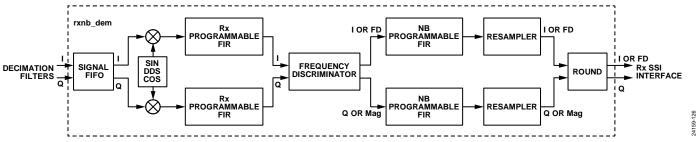

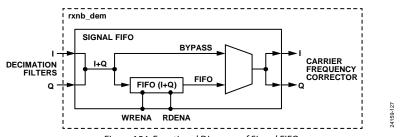

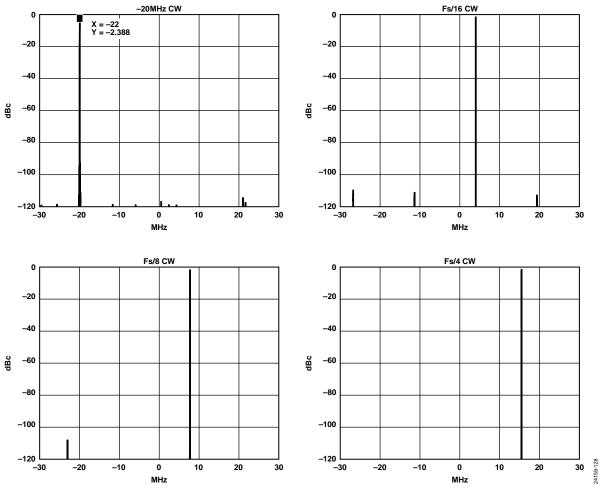

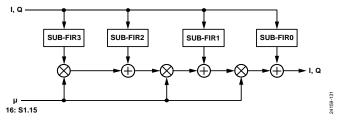

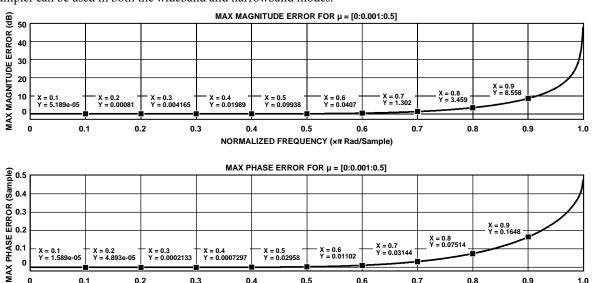

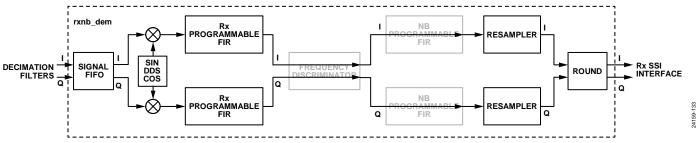

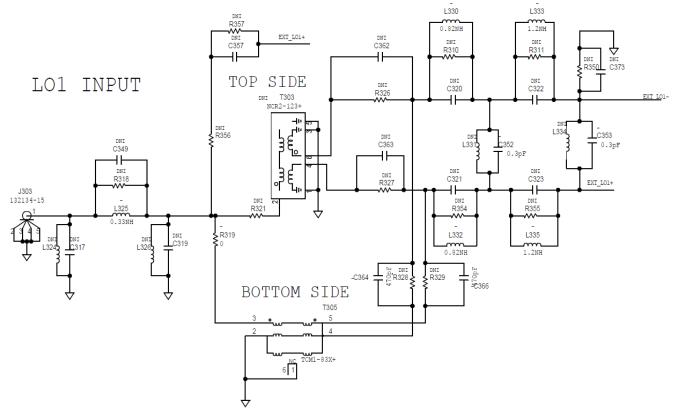

| Rx Narrow-band Demodulator Subsystem 164                | External LO Port Impedance Matching Network214            |

| Normal IQ Output Mode 168                               | External LO Impedance Match Measurement Data217           |

| Frequency Deviation Output Mode 168                     | Connection for External Device Clock (DEV_CLK_IN)218      |

| API Programming                                         | DEV_CLK_IN Phase Noise Requirements220                    |

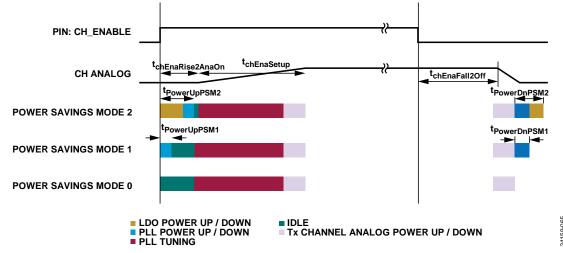

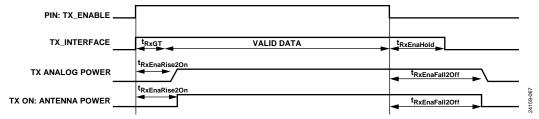

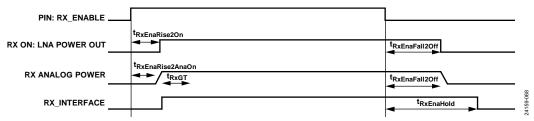

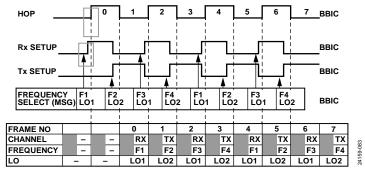

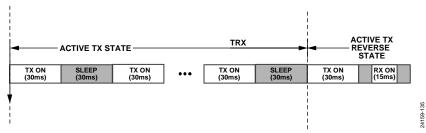

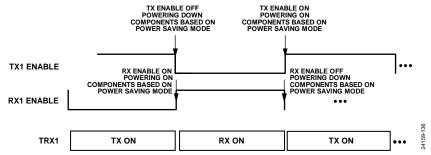

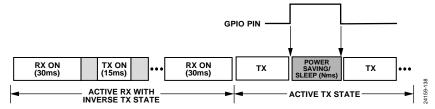

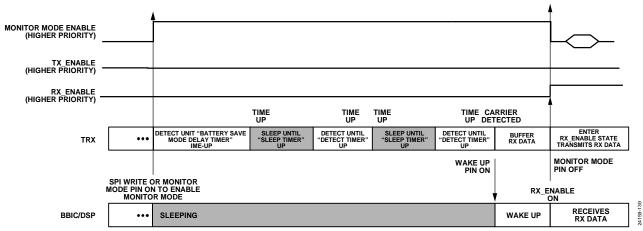

| Power Saving and Monitor Mode 171                       | Connection for MultiChip Synchronization (MCS) input.221  |

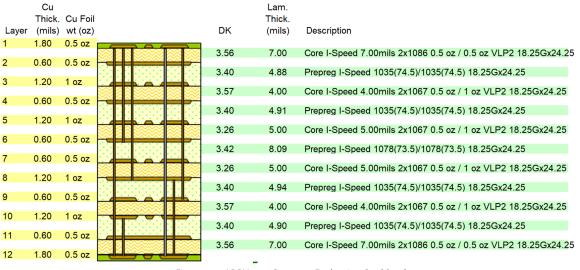

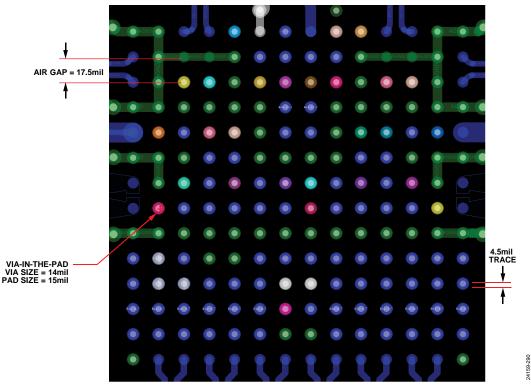

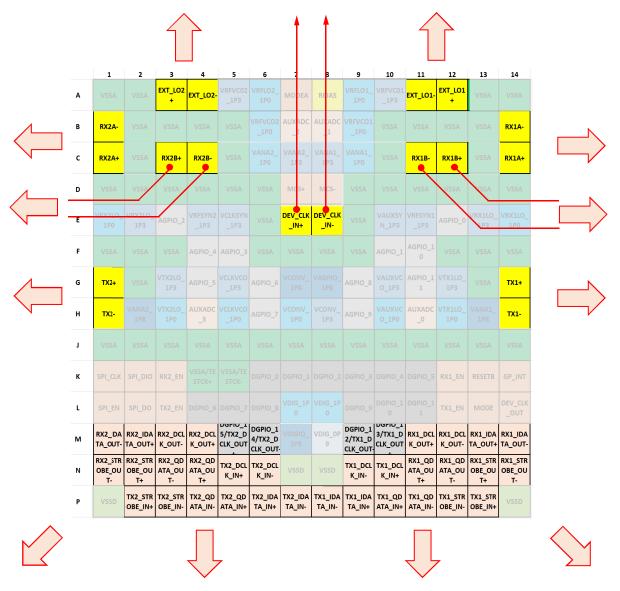

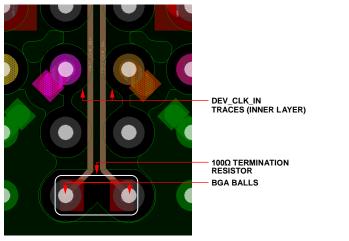

| Power-Down Modes                                        | Printed Circuit Board Layout Recommendations222           |

| Power-Down/Power-Up Channel in Calibrated State 172     | PCB Material And Stack Up Selection222                    |

| Dynamic Interframe Power Saving                         | Fan-out and Trace Space Guidelines223                     |

| Monitor Mode                                            | Component Placement and Routing Priorities224             |

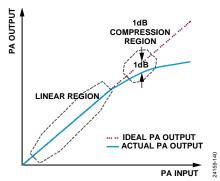

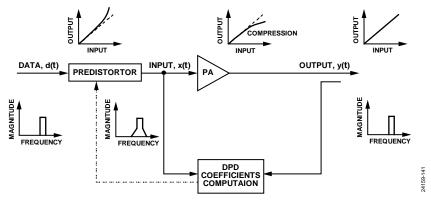

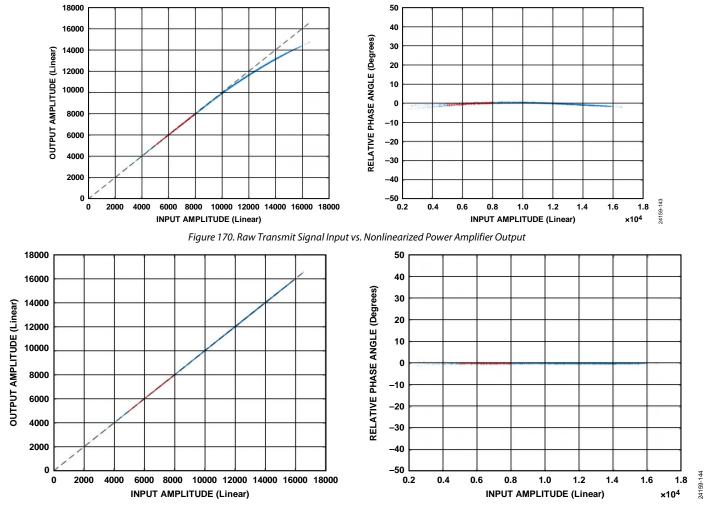

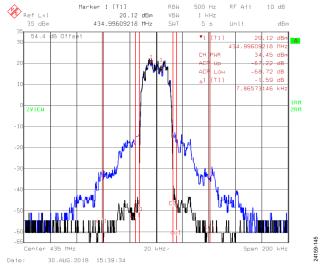

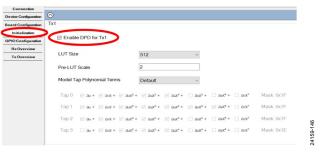

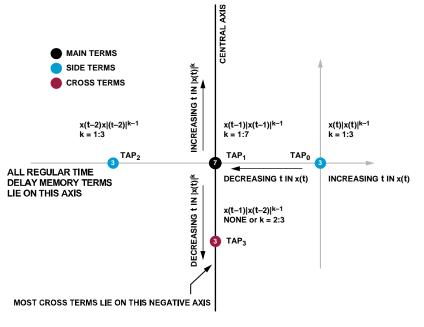

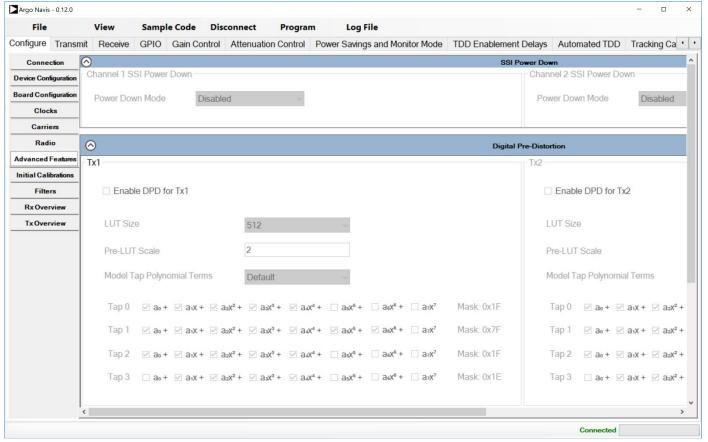

| Digital Predistortion176                                | RF and Data Port Transmission Line Layout230              |

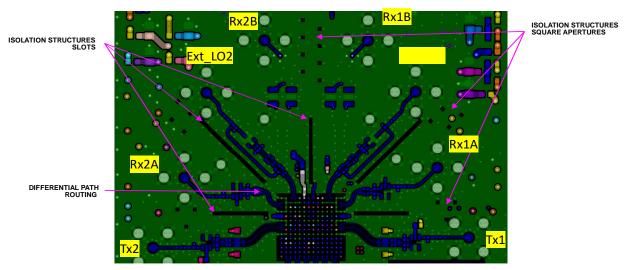

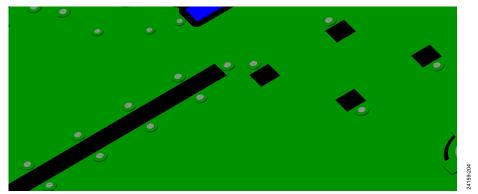

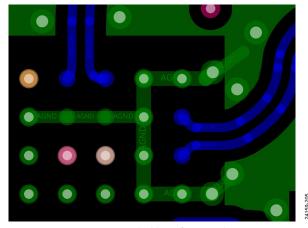

| Background                                              | Isolation Techniques Used on the ADRV9001 Evaluation      |

| ADRV9001 DPD Function                                   | Card                                                      |

| ADRV9001 DPD Supported Waveforms 178                    | Power Supply Recommendations240                           |

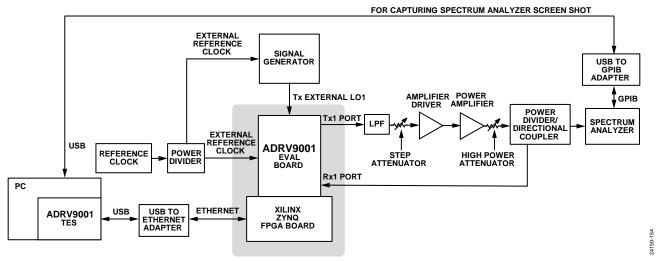

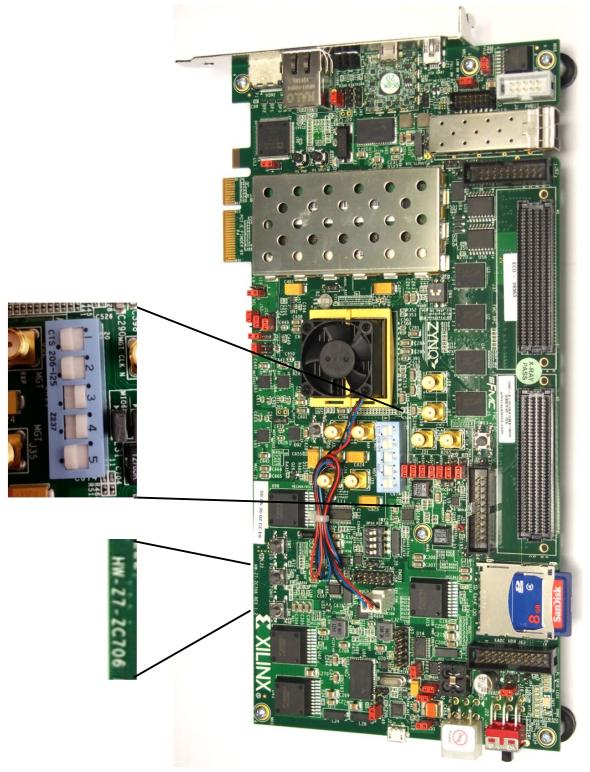

| ADRV9001 DPD Performance                                | ADRV9001 Evaluation System243                             |

| DDD Configuration 190                                   | Initial Setup243                                          |

# UG-1828

# **Preliminary Technical Data**

| Hardware Kit243                            | Auxiliary DAC/ADC                 |

|--------------------------------------------|-----------------------------------|

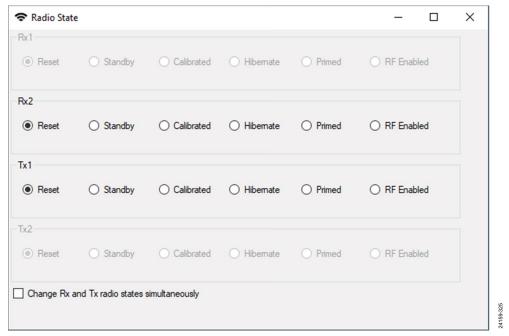

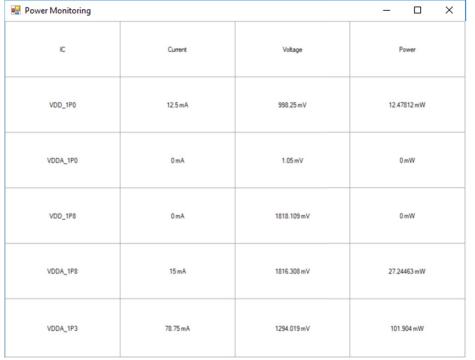

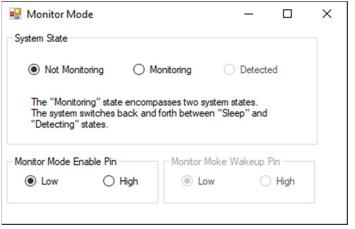

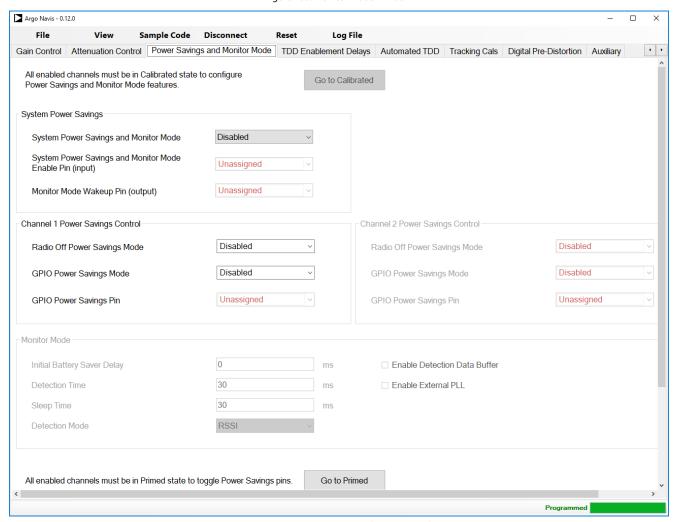

| Hardware Operation246                      | Radio State                       |

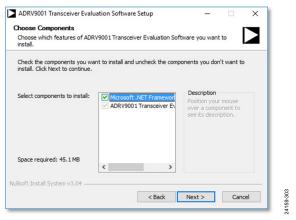

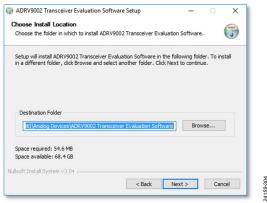

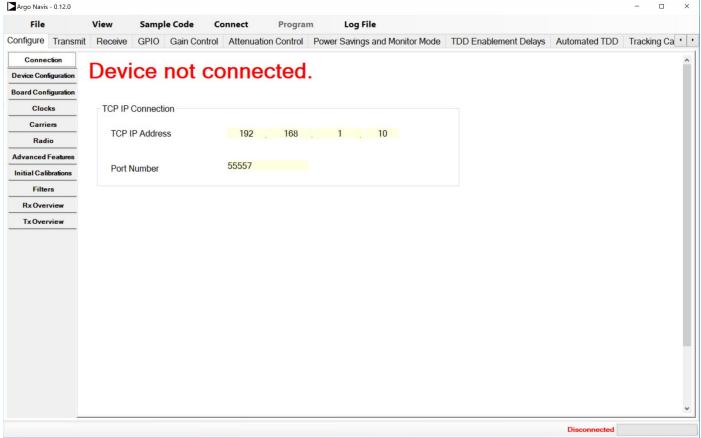

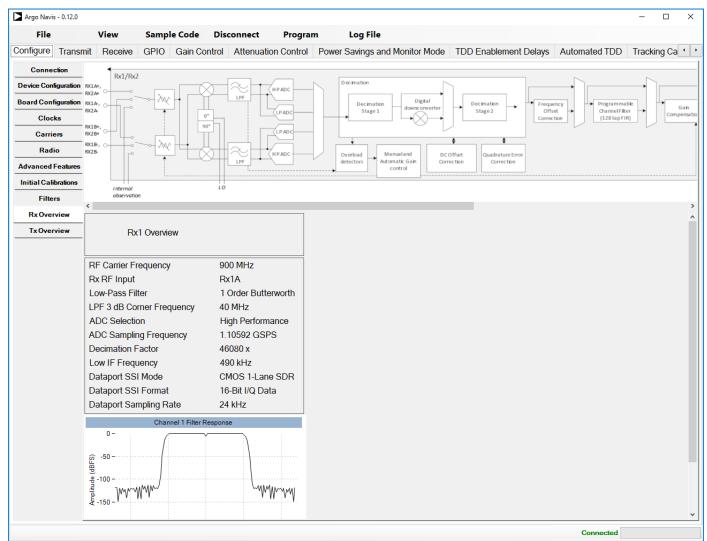

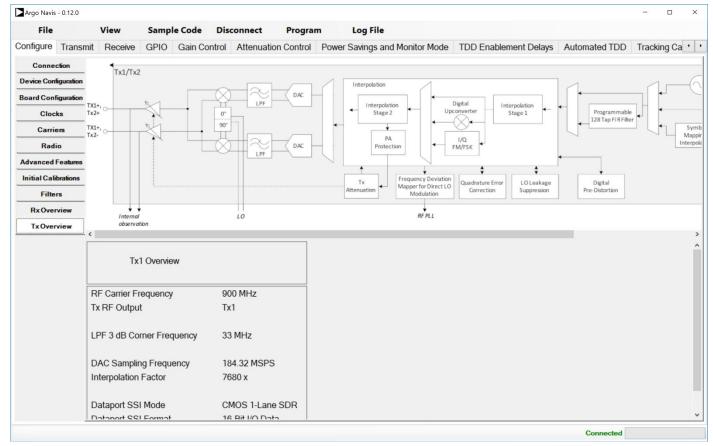

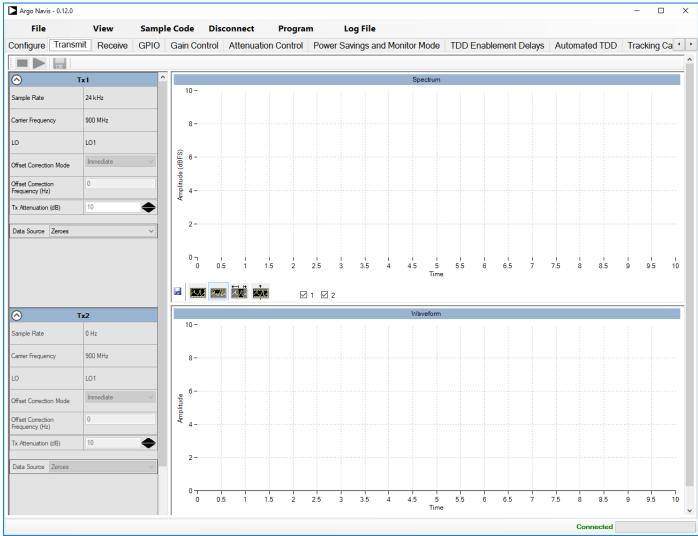

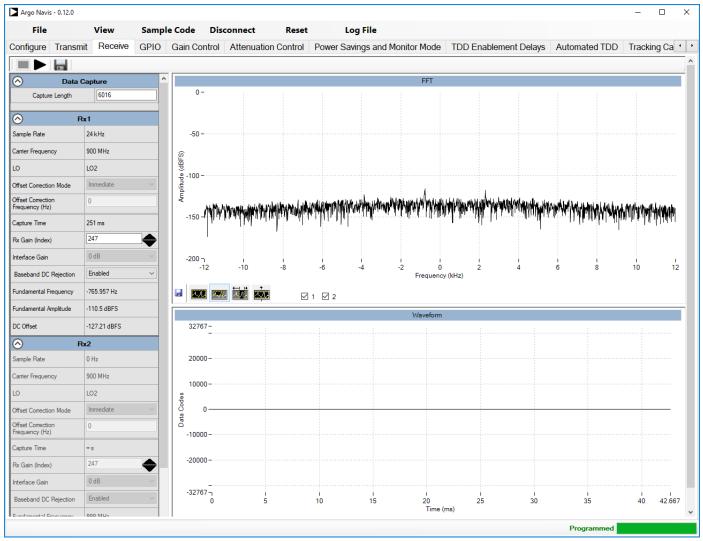

| Transceiver Evaluation Software (TES)247   | Power Monitoring                  |

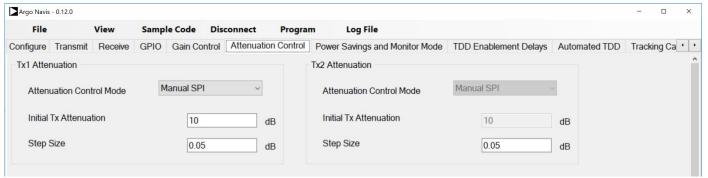

| Transmitter Operation260                   | Power Savings and Monitor Mode    |

| Receiver Operation263                      | Driver Debugger                   |

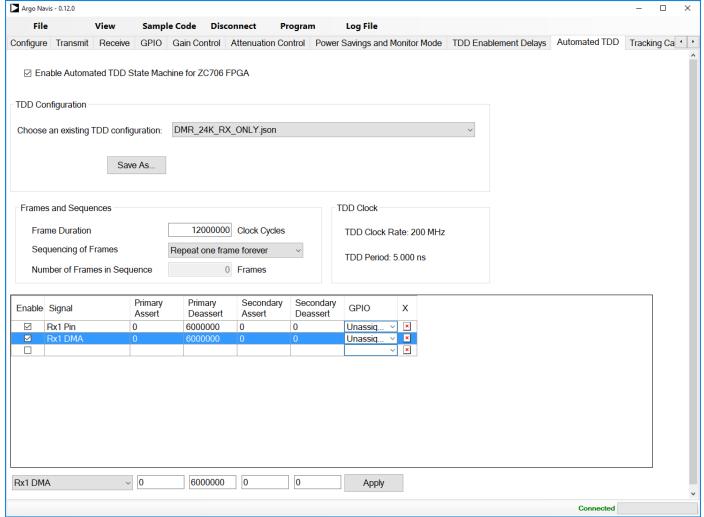

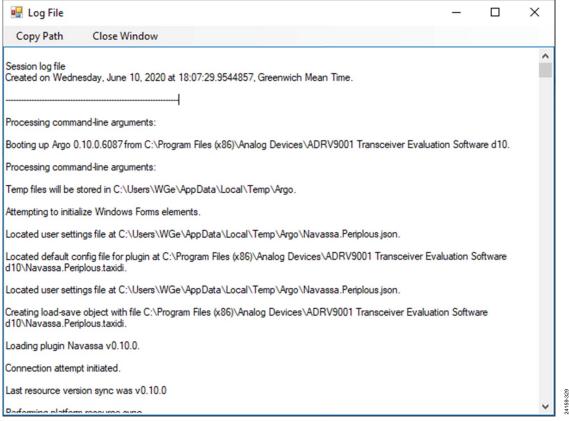

| Automated Time Division Duplexing (TDD)266 | Log File                          |

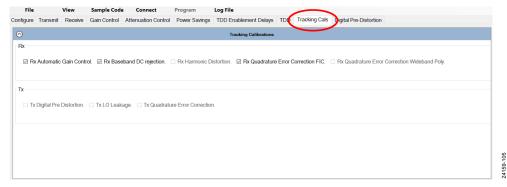

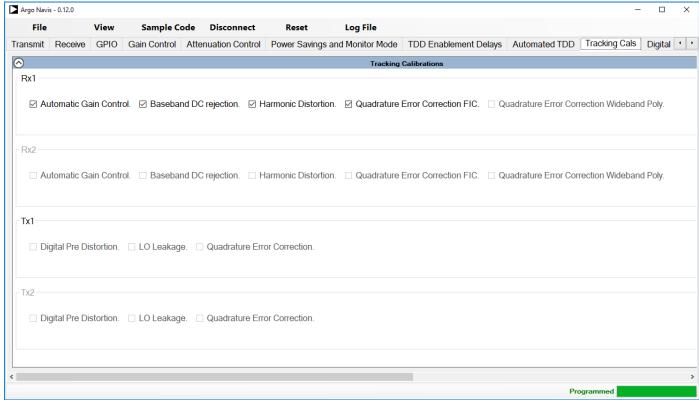

| Tracking Calibrations269                   | Using of Matlab and Python        |

| Digital Predistortion270                   | Evaluation System Troubleshooting |

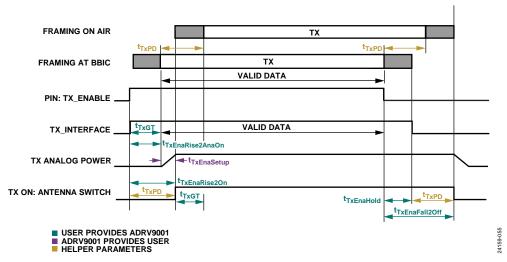

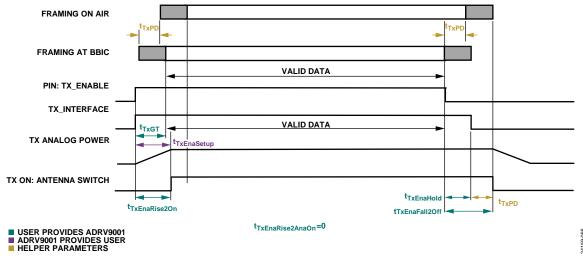

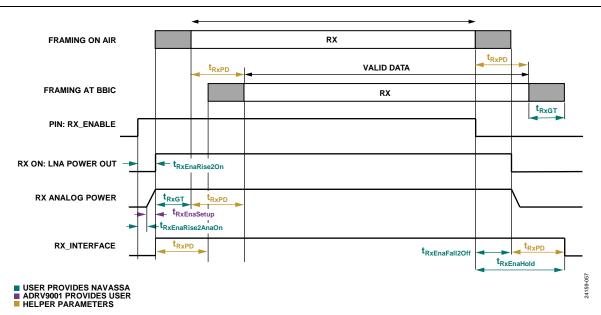

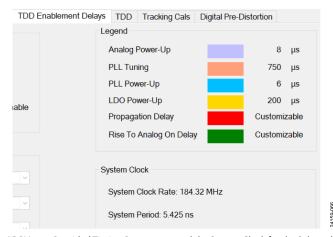

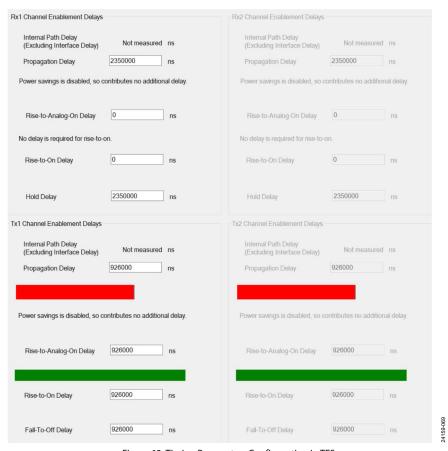

| TDD Enablement Delays 270                  |                                   |

# **HOW TO USE THIS DOCUMENT**

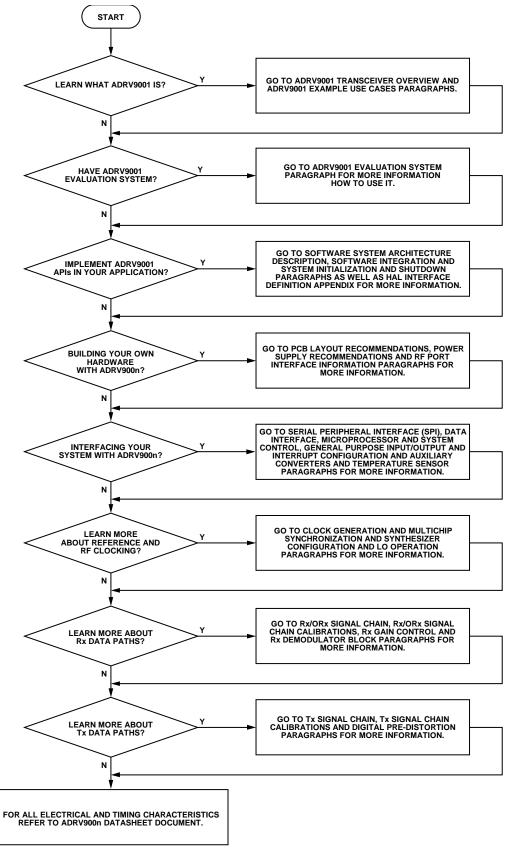

Figure 1. Document Flowchart for Document Navigation

Rev. PrB | Page 5 of 277

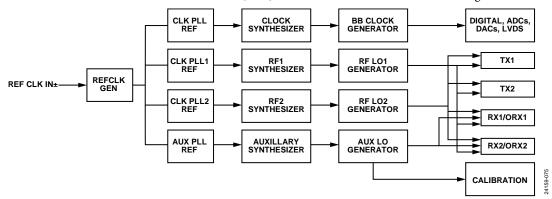

### **BLOCK DIAGRAM**

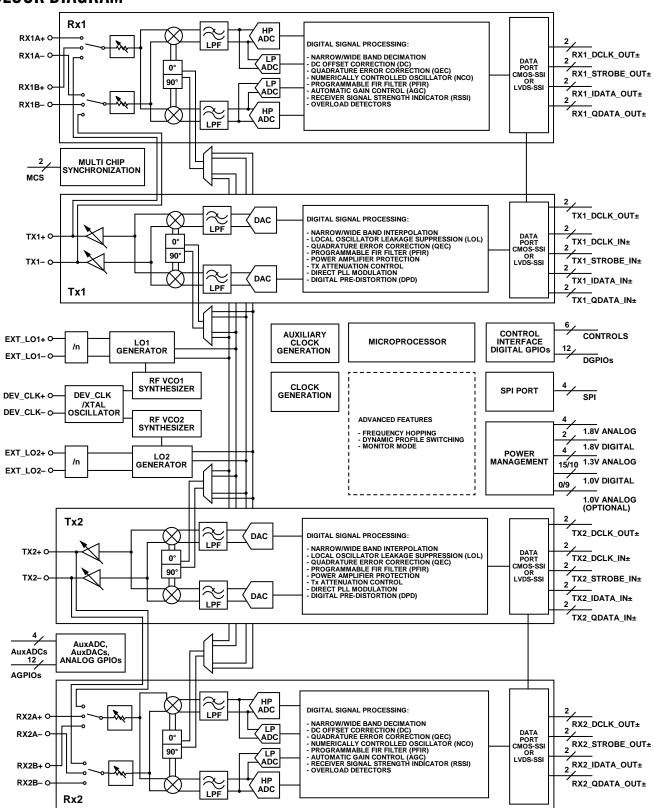

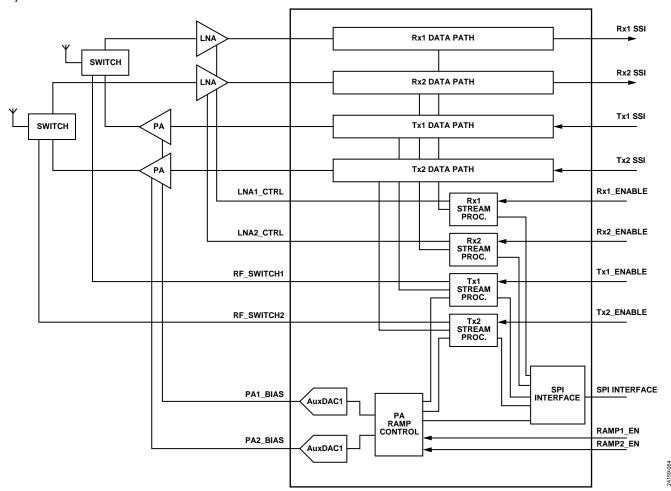

Figure 2. ADRV9002 Block Diagram

### PRODUCT HIGHLIGHTS

#### **ADRV9002**

The ADRV9002 delivers a versatile combination of high performance and low power consumption required by battery powered radio equipment and can operate in both frequency division duplex (FDD) and time division duplex (TDD) modes. The ADRV9002 operates from 30 MHz to 6000 MHz covering the VHF, licensed and unlicensed cellular bands, and ISM bands. The IC is capable of supporting both narrowband and wideband standards up to 40 MHz bandwidth on both receiver and transmitter.

The transceiver consists of direct conversion signal paths with state-of-the-art noise figure and linearity. Each complete receiver and transmitter sub-system includes DC offset correction, quadrature error correction, and programmable digital filters, eliminating the need for these functions in the digital baseband. In addition, several auxiliary functions such as an auxiliary ADC, auxiliary DACs, and GPIOs are integrated to provide additional monitoring and control capability.

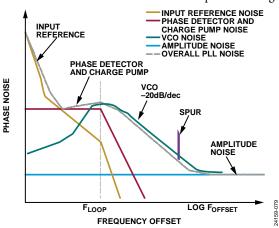

The fully integrated phase locked loops (PLLs) provide high performance, low power fractional-N frequency synthesis for the transmitter, receiver, and clock sections. Careful design and layout techniques have been implemented to provide the isolation demanded in high performance Mobile Radio applications.

All VCO and loop filter components are integrated to minimize the external component count. The LOs have flexible configuration options and include fast lock modes.

The transceiver includes low power sleep and monitor modes to save power, which extends battery life of portable devices while continuing to monitor communication.

The fully integrated low power digital predistortion (DPD) is supported by ADRV9002. It can linearize wideband signals as well as it has been optimized for narrowband type signals to enable linearization of high efficiency power amplifiers. In use cases where the integrated DPD is used, main receivers are used as a power amplifier observation path.

Power supply for ADRV9002 is distributed across four or five different voltage supplies: 2 or 3 analog and 2 digital. The analog supplies are 1.8 V, 1.3V, and 1.0V (in internal LDO bypass mode). 1.3V domain feeds directly some blocks and also internal LDO regulators for some functions to maximum performance. 1.8 V analog domain is used to optimize transmitter and auxiliary converter performance. The digital processing blocks are supplied by a 1.0V source. In addition, a 1.8 V supply is used to supply all GPIO and interface ports that connect with the baseband processor.

High data rate and low data rate interfaces are supported using configurable CMOS or LVDS Synchronous Serial Interface choice.

The core of the ADRV9002 is controlled via a standard 3 or 4-wire serial port. All software control is communicated via this interface. There is also a control interface that uses GPIO lines to provide hardware control to and from the device. These pins can be configured to provide dedicated sets of functions for different application scenarios.

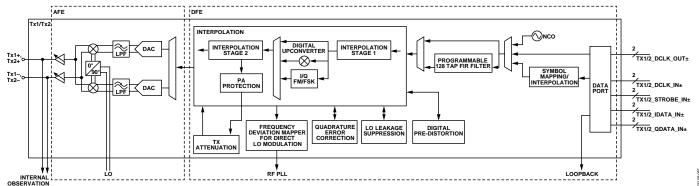

The block diagram in Figure 2 shows a high level view of the functions in the ADRV9002. Descriptions of each block with setup and control details are provided in subsequent sections of this document.

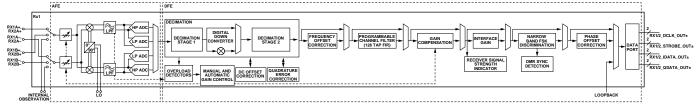

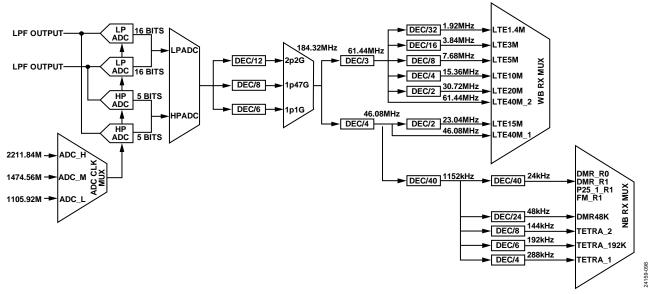

#### **BANDWIDTH AND SAMPLE RATE SUPPORT**

The ADRV9002 supports the reception and transmission of channels up to 40 MHz bandwidth. Standard sample rates of 24 kHz (typically for narrowband FM waveforms), 144 kHz and 288 kHz (typically for TETRA signals), and 1.92 MHz, 3.84 MHz, 7.68 MHz, 15.36 MHz, 23.04 MHz, 30.72 MHz, and 61.44 MHz (typically for LTE signals) are available.

In addition, the ADRV9002 supports an almost continuous range of sample rates between 24 kHz and 61.44 MHz. Some sample rates cannot be supported due to internal clocking constraints.

Sample rate scaling is accomplished by enabling or disabling decimation or interpolation filters in the digital signal chain.

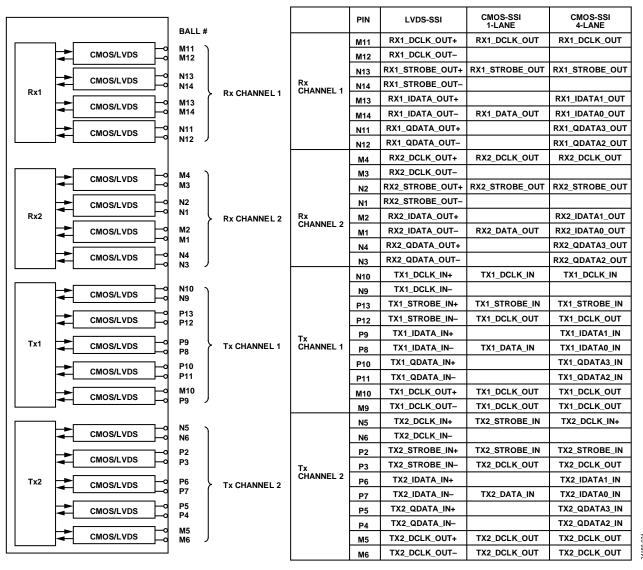

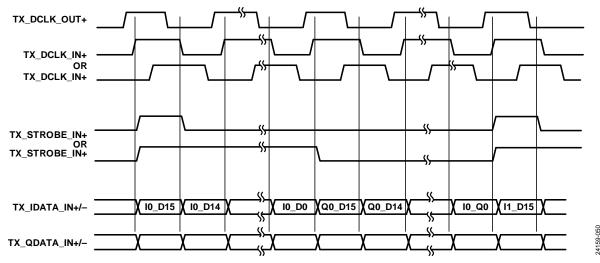

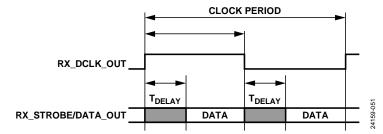

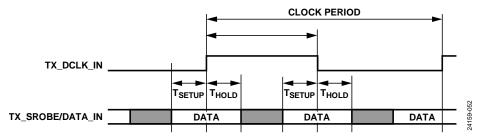

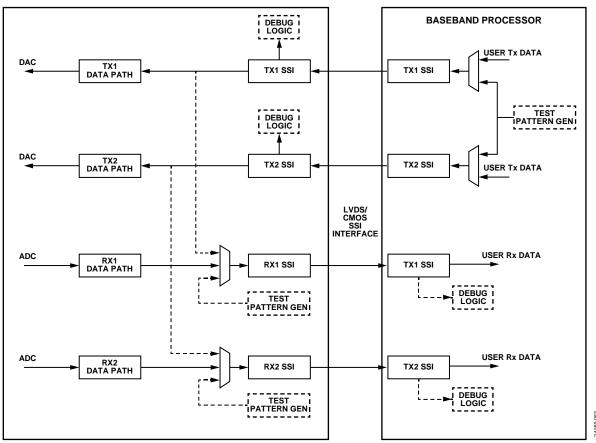

#### **Data Interfaces**

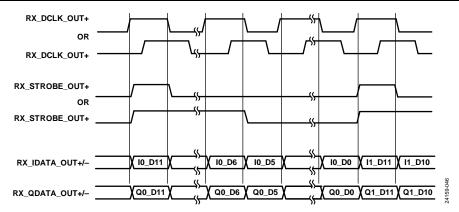

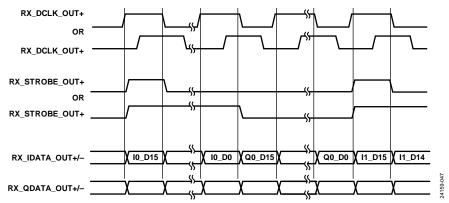

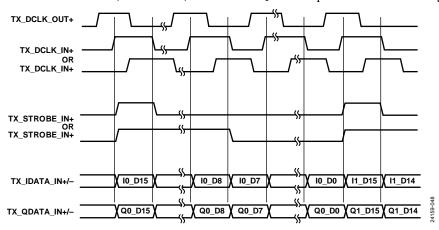

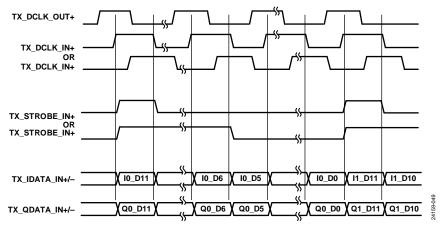

The ADRV9002 supports both CMOS and LVDS electrical interfaces for its data lanes. All data lanes support both electrical interfaces, but concurrent operation of both interfaces is not supported. Each receive and transmit channel has a dedicated set of lanes for transferring information.

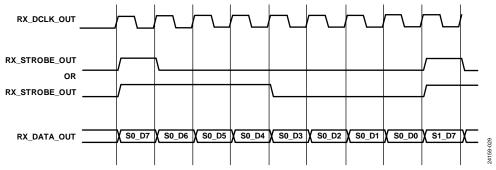

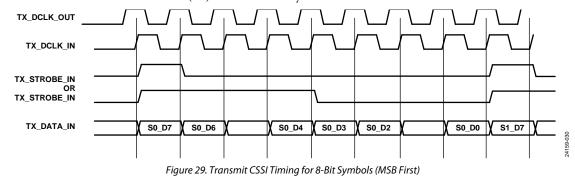

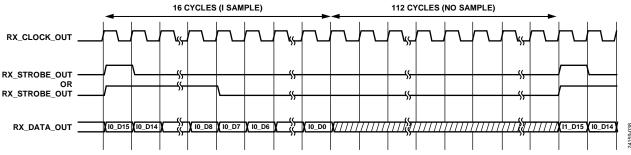

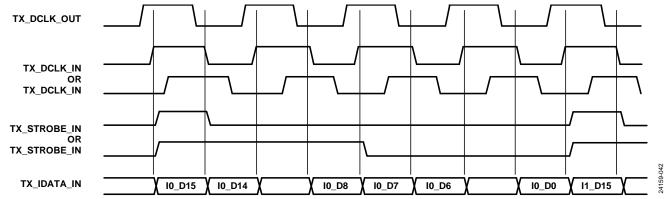

The CMOS bus speed is limited to 80 MHz. Two operating modes are available for the CMOS-SSI electrical interface. For low sample rates, a mode in which 32 bits (16 bits of I and Q data each) are serialized over a single lane, with two additional lanes total required for a clock (SDR or DDR) and a frame synchronization signal, supports a maximum sample rate of 2.5 MHz.

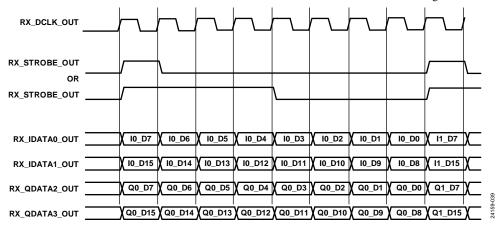

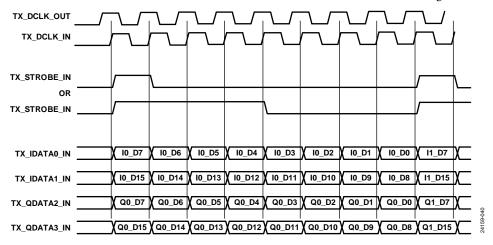

For sample rates above 2.5 MHz, single channel data is serialized over four lanes, with two additional lanes total required for a clock (SDR or DDR) and a frame synchronization signal, supporting a maximum sample rate of 20 MHz.

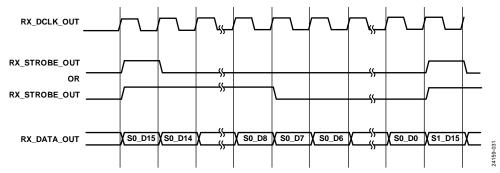

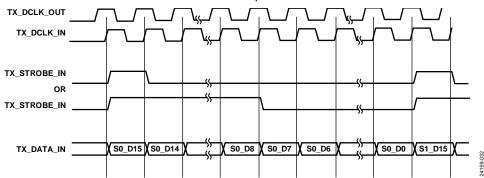

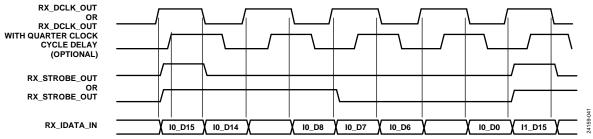

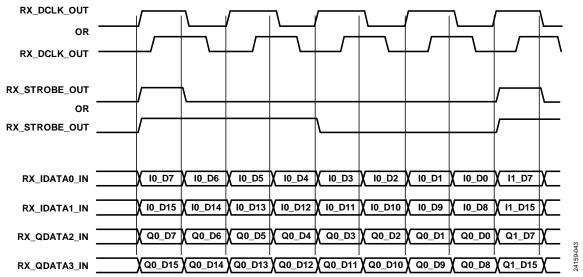

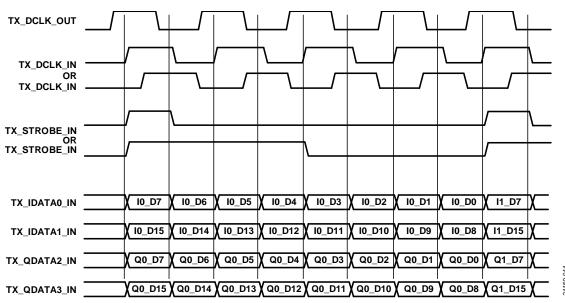

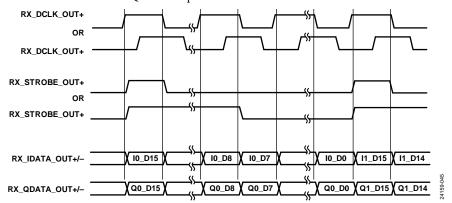

The LVDS electrical interface supports two modes of operation. The 32 total bits of I and Q data are serialized over one LVDS lane (32 bits composed of 16 bits of I and 16 bits of Q data) or two LVDS-SSI lanes (each dedicated to 16 bits of I or Q data), with two additional lanes total required for a DDR clock and a frame synchronization signal. Sample rates ranging from 24 kHz to 61.44 MHz are supported via the LVDS-SSI interface, resulting in a maximum lane rate of 983.04 MHz.

Note that in LVDS-SSI mode, 12-bit I and Q words are supported for most sample rates.

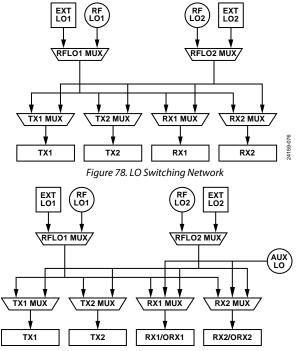

#### RF LO Frequency Range and Multiplexing

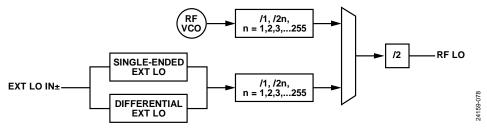

The ADRV9002 supports a RF LO range from 30 MHz to 6 GHz. RF LOs can be generated via two internal PLLs, or applied externally to the device. When LOs are provided from an external source, double or more of the desired frequency must be applied to the ADRV9002 to allow for the generation of quadrature signals internally.

An LO multiplexing scheme exists on the ADRV9002, that allows for the routing of either of the RFPLLs to any of the transmit or receive channels. The RF channels and RFPLLs can operate concurrently and independently, off a common reference clock, thus enabling: FDD operation, single or dual frequency repeater operation, multi-band TDD operation, and diversity operation amongst various other configurations.

#### **Frequency Hopping**

The ADRV9002 supports various forms of frequency hopping, with the main distinguishing factor between them being frequency transition time. RFPLL phase noise, and QEC and LOL algorithm performance may degrade as a function of decreasing frequency transition time.

A fast frequency hopping (FFH) mode exists that supports 64 hop frequencies or less, that are pre-loaded by the user onto the ADRV9002 at power-up. In this mode, the 64 frequencies are cycled through in a circular buffer fashion. Hopping between the frequencies in FFH mode is triggered via a GPIO pin toggle. An API command with SPI transaction can also trigger a frequency hop, albeit with a longer frequency transition time.

A random order FFH mode is also supported, whereby a finite set of frequencies already pre-loaded onto the ADRV9002 can be hopped between in a random manner dictated by the user. Selecting the next frequency to hop to is accomplished by asserting a frequency index word onto the GPIO bus. Alternatively, the API can be used to select the next frequency index, albeit with a longer frequency transition time.

In addition to FFH mode, the ADRV9002 supports other frequency hopping modes where the desired hop frequencies need not be preloaded into on-board memory. In these modes, desired hop frequencies can be streamed in via the API. Frequency transition times in these modes are greater than that available in FFH mode.

Note that all frequency hopping modes are available for use in conjunction with the monitor mode described in the Power Consumption Modes section.

#### **Profile Switching**

The ADRV9002 supports rapid switching between different RF channel profiles. A transmit or receive RF channel profile contains settings such as bandwidth, sample rate, filtering, input port selection, AGC settings, and algorithm configuration. The profile switching mode enables the support of waveforms that vary modulation schemes and bandwidths dynamically.

#### Low IF Reception

The receive digital datapath on the ADRV9002 contains an optional digital mixer that is driven by a programmable NCO. The RX LO is offset from the frequency of the desired channel, and then the digital mixer and NCO are used to down convert signal to base-band before being processed by their baseband processor.

There are several advantages to offset the RX LO from the frequency of the desired channel: Impairments that exist about the RX LO, such as LO-leakage, can be avoided. The effect of flicker noise from base-band circuits can be mitigated since the received signal is offset from DC in the analog signal path. Also, image rejection can be improved if the RX LO is offset enough from the desired channel, such that the image frequency lies in the attenuation region of the user's external RF filter.

The low IF reception mode is targeted predominately towards low bandwidth channels, which supports offsets range of  $\pm$  20 MHz about the receiver LO.

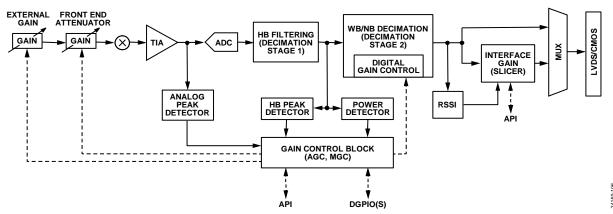

#### Receive Dynamic Range and Blocking

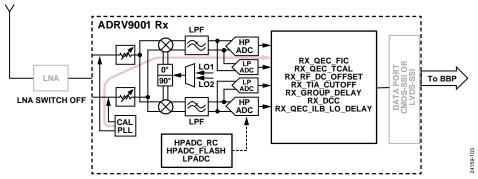

As depicted in Figure 2, the ADRV9002 receive path consists of an input mixer, followed by a base-band filter that drives an ADC. A highly programmable digital decimation and filtering datapath follows the ADC. RF analog gain control is provided in analog attenuator, and additional gain is provided in the digital datapath via AGC loops.

# **Preliminary Technical Data**

The ADC in the receive chain possesses a high dynamic range. Assuming a mixer gain of 0 dB, the ADC's noise and maximum input power referred to the RF input are -142 dBm/Hz and 8.6 dBm, respectively. These levels translate into a dynamic range in excess of 150 dB on a per Hertz basis. Taking into account the digital filtering and AGC loops, an even greater dynamic range can be achieved.

Given the high dynamic range of the receiver ADC, very little channelization or blocker filtering occurs in the analog signal chain since the ADC can simultaneously absorb weak signals and large blockers. Blocker suppression and channelization are then achieved in the digital signal path.

If reciprocal mixing of the RX LO phase noise by a large blocker close to the desired channel significantly degrades blocking performance, a lower phase noise external LO source can be used in place of the on-board RFPLLs.

The receive path also contains two types of ADCs connected to the chip's RF front end, that allow for the trade-off between power consumption and dynamic range: a high performance ADC, and low power ADC that possess degraded dynamic range. Users can trade-off receive channel dynamic range and power consumption by selecting between either set of ADCs.

#### **Power Consumption Modes**

The ADRV9002 provides users with various levels of power control. Power scaling on individual analog signal path blocks can be performed to trade-off power and performance. In addition, enabling and disabling various blocks in TDD RX and TX frames to reduce power can be customized, at the expense of RX/TX or TX/RX turnaround time.

A specialized "RX Monitor mode" exists that allows the ADRV9002 to autonomously poll a region of the spectrum for the presence of a signal, while in a low power state. In this mode, the chip continuously cycles through sleep-detect-sleep states controlled by an internal state machine. Power savings are achieved by ensuring that the sleep duty cycle is greater than the "detect" duty cycle.

In the "sleep" state, the chip is in a minimal power consumption configuration where few functions are enabled. After a pre-determined period, the chip enters the "detect" state. In this state, the chip enables a receiver and performs a power measurement over a bandwidth and at a RX LO frequency determined by the user. If the measured power level in the bandwidth is greater than a user-determined threshold, the "Monitor Mode" state machine exits its cycle. Following the loop exit, an interrupt is provided via a GPIO pin to the user's baseband processor, and the entire receiver analog and digital chains within the ADRV9002 are powered up, assuming that normal signal reception resumes due to the detection of a channel.

If the power measured over the bandwidth is less than the user-determined threshold, the chip resumes its sleep-detect-sleep cycle. The sleep-detect duty cycle and durations, power measurement threshold, and RX LO are user-programmable, and are set before enabling monitor mode.

Note that frequency hopping can be combined with monitor mode, allowing the ADRV9002 to dynamically change the RX LO while performing the power measurement function.

#### **ADRV9003**

The ADRV9003 delivers all features offered by ADRV9002 transceiver. Differences between ADRV9002 and ADRV9003 include.

- RF IOs. The ADRV9003 offers one receiver and one transmitter.

- Digital predistortion functionality is not supported by the ADRV9003.

#### **ADRV9004**

The ADRV9004 delivers all features offered by ADRV9002 transceiver. Differences between ADRV9002 and ADRV9004 include.

Digital predistortion functionality is not supported by the ADRV9004.

### ADRV9001 EXAMPLE USE CASES

The intention of this section is to provide the reader with the overall idea how ADRV9001 integrated transceiver can operate as an RF front end in different applications. The provided list is not exhaustive, and there are other applications in which the ADRV9001 can serve.

Each example is accompanied with a table that explains the main limitations and highlights what the customer should look for when implementing the ADRV9001 in the end application.

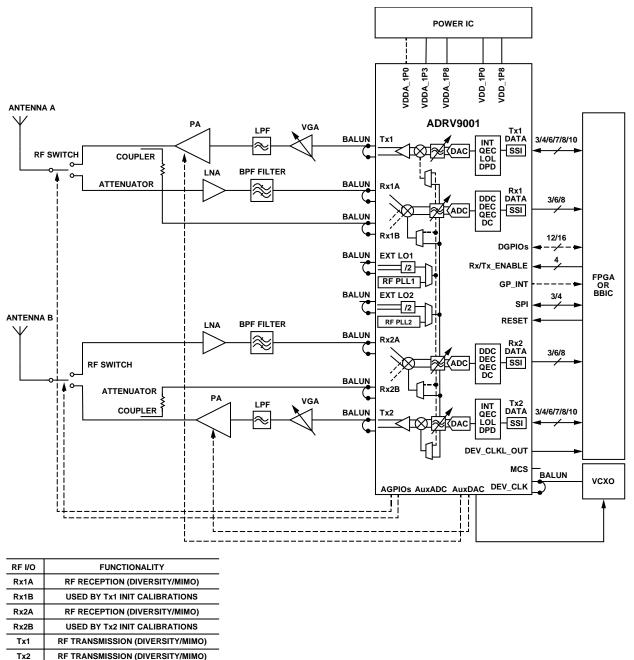

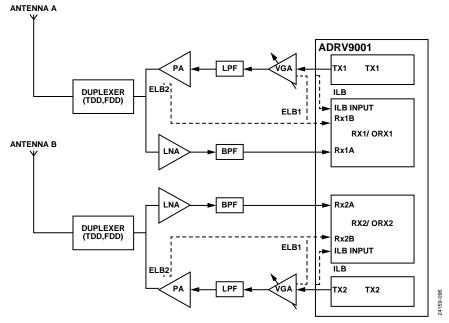

#### ADRV9001 IN A SINGLE-BAND 2RT2R FDD TYPE SMALL-CELL APPLICATION

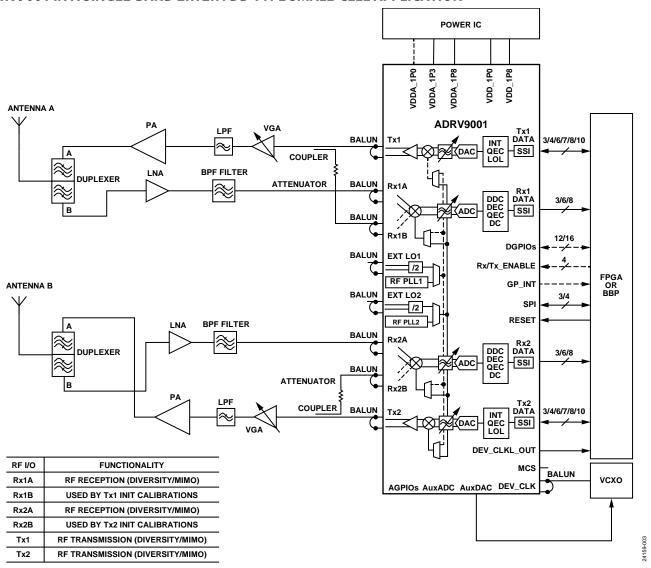

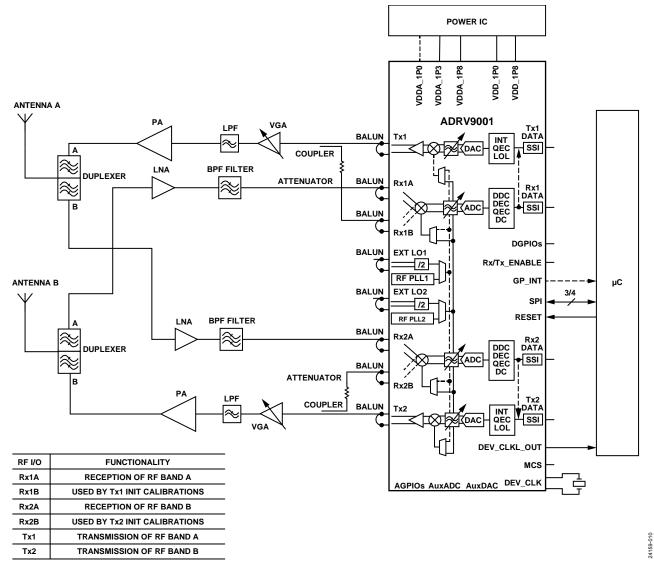

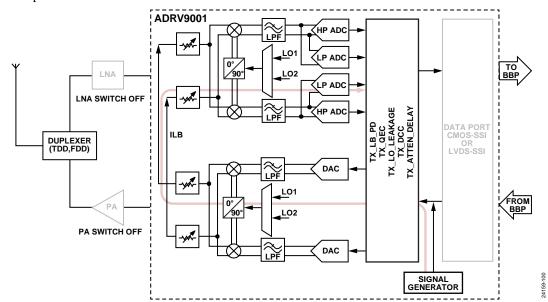

Figure 3. ADRV9001 in Single-Band 2T2R FDD Type Small Cell Application

With a minimum number of external components, the ADRV9001 transceiver can be used to build complete RF to bits signal chains that can serve as the RF front end in small cell type applications. The ADRV9001 dual Rx and Tx signal chains allow the user to implement MIMO or diversity in their system. The ADRV9001 internal AGC can be used to autonomously monitor and set appropriate gain levels for Rx signal chains. For non-time critical FDD type applications, control of the ADRV9001 TRx can be done through API commands that use the SPI interface.

Table 1. Constrains and Limitations in Single-Band 2T2R FDD Type Small-Cell Application

| Functionality           | Constrains and Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receiver Signal<br>Path | The user must ensure that appropriate level of isolation between Rx1 and Rx2 as well as Rx to Tx is provided at the system level. In the previously described example, the RxB inputs are used only during initialization calibrations. Ensure that the appropriate attenuation is present in line to prevent Rx being overloaded by Tx signal.                                                                                                                                                                                                                                                                                                   |

| Transmit Signal<br>Path | The user must ensure that appropriate level of isolation between Tx1 and Tx2 as well as Rx to Tx is provided at the system level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LO Generation           | In FDD type Small Cell application, ADRV9001 can use its internal LO to generate RF LO1 for uplink (Rx1 and Rx2) and RF LO2 for downlink (Tx1 and Tx2). It is also possible to use external LO inputs in this mode of operation. External LO1 operating at 2x RF LO can be used for uplink and External LO2 operating at 2x RF LO can be used for downlink.                                                                                                                                                                                                                                                                                       |

| RF Front End            | For LO generation, the ADRV9001 uses internal VCO that generates square wave type signal. A square wave LO would produce harmonics. For example: depending of RF matching used on the RF ports user 2nd LO harmonic can be as high as -50dBc and 3rd harmonic can be as high as –9 dBc. Therefore the RF filtering on the Rx and Tx path must ensure that signals at the LO harmonic frequencies (up to 9th in some cases) are not affecting overall system performance.                                                                                                                                                                          |

| DPD                     | The DPD functionality is not available when ADRV9001 operates in 2R2T FDD mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Calibrations            | During Rx initialization sequence user needs to ensure that there are no signals present at the Rx input (external LNA should be disabled) and appropriate termination should be present at LNA output to avoid reflections of Rx calibration tones. The maximum input signal amplitude must not exceed –82 dBm/MHz for wideband modes, TBD dBm/MHz for narrowband modes. During Tx initialization sequence user needs to ensure that the power amplifier is powered down to avoid unwanted emission of transmitter calibration tones at the antenna. No transmitter tracking calibrations are available when ADRV9001 operates in 2R2T FDD mode. |

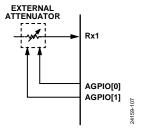

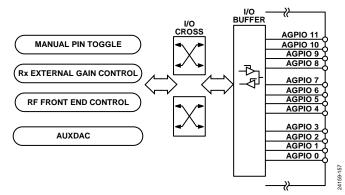

| AGPIOs                  | Analog GPIOs (operating at 1.8 V level) can be used as read or write digital levels of in the end user system. AGPIOs can be used to control states of external components or read back digital logic levels from external components.                                                                                                                                                                                                                                                                                                                                                                                                            |

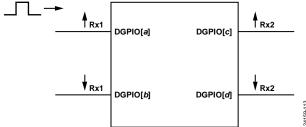

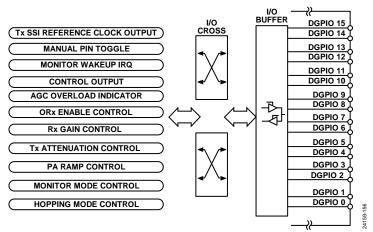

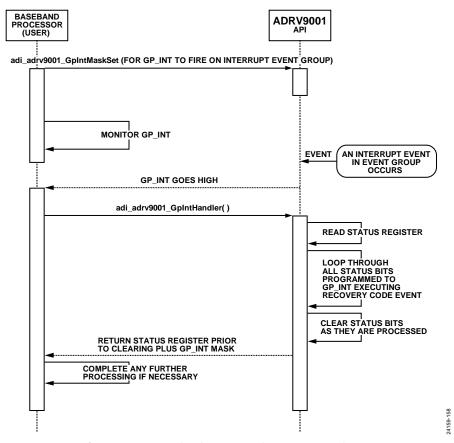

| DGPIOs                  | Digital GPIOs can be used to perform real-time monitoring of states of internal ADRV9001 blocks. Digital GPIOs operating as inputs can allow user to control Rx gain, Tx attenuation, AGC operation and other elements of ADRV9001 TRx. Depending on the ADRV9001 operation up to 4 GPIOs may be used by data port interface.                                                                                                                                                                                                                                                                                                                     |

| AuxADC                  | AuxADC can be used to monitor analog voltage (for example, temperature sensor). Maximum AuxADC input voltage must not exceed 0.9 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AuxDAC                  | AuxDAC can be used to control the VCXO responsible for generating the ADRV9001 device clock and control any circuitry that requires analog control voltage up to 1.8 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DEV_CLK_OUT             | ADRV9001 provides divided down version of DEV_CLK reference clock input signal on the DEV_CLK_OUT output. This output is intended to provide reference clock signal to the digital components in the overall system. This output can be configured to be active after power-up and before ADRV9001 configuration stage.                                                                                                                                                                                                                                                                                                                           |

| Multichip Sync          | If there is no need for multichip synchronization, the ADRV9001 can be initialized using API functions only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### ADRV9001 IN DUAL-BAND 2RT2R FDD TYPE SMALL-CELL APPLICATION

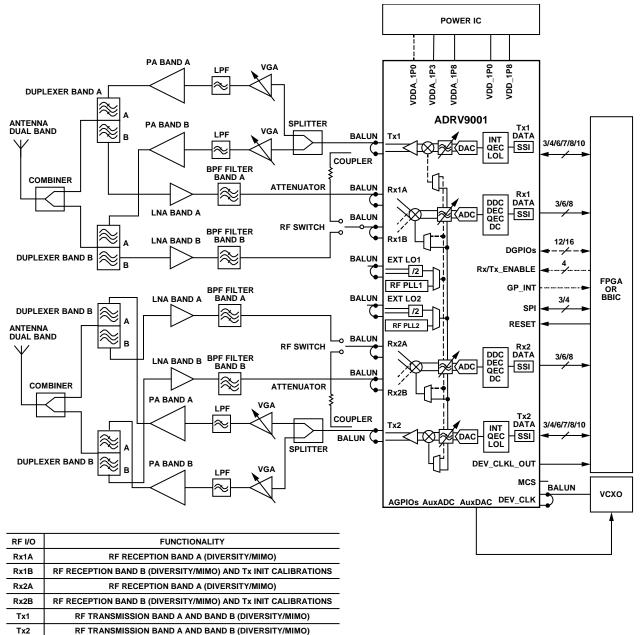

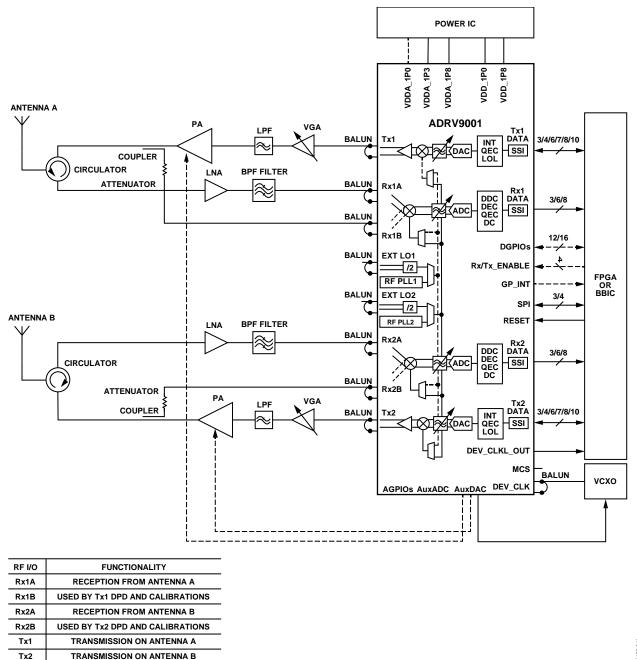

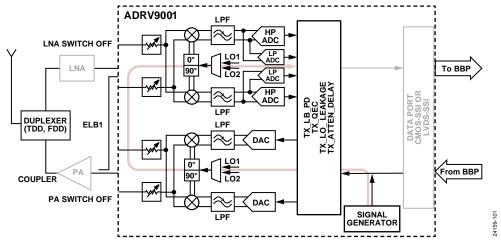

Figure 4. ADRV9001 in Dual-Band 2T2R FDD Type Small-Cell Application

159-004

#### **Dual-Band 2T2R FDD Overview**

With a minimum number of external components, the ADRV9001 transceiver can be used to build complete dual and RF-to-bits signal chain that can serve as RF front end in small cell type applications. Note that in proposed solution, only one band can be used at the time. ADRV9001 dual Rx and Tx signal chains enables user to implement MIMO or diversity in their system. ADRV9001 internal AGC can be used to autonomously monitor and set appropriate gain level for Rx signal chains. For none time critical FDD type applications control of the ADRV9001 TRx can be done thru API commands that use SPI interface.

Table 2. Constrains and Limitations in Dual-Band 2T2R FDD Type Small-Cell Application

| Functionality  | Constrains and Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

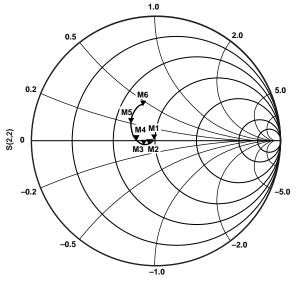

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rx Signal Path | The user must ensure that appropriate level of isolation between Rx1 and Rx2 as well as Rx to Tx is provided at the system level. In the previously described example, RxB inputs are used to work with Rx Band B signals as well as during initialization calibrations. In this scenario, RF Balun selected for RxB inputs must work with both Band B and Tx Bands. The user must ensure that appropriate attenuation is present in line to prevent Rx being overloaded by Tx signal.                                                                                                                                                                      |

| Tx Signal Path | The user must ensure that appropriate level of isolation between Tx1 and Tx2 as well as Rx to Tx is provided at the system level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LO Generation  | In FDD type small cell applications, ADRV9001 can use its internal LO to generate RF LO1 for uplink (Rx1 and Rx2) and RF LO2 for downlink (Tx1 and Tx2). It is also possible to use external LO inputs in this mode of operation. External LO1 operating at 2× RF LO can be used for uplink and External LO2 operating at 2× RF LO can be used for downlink. It should be noted that only one set of Rx inputs can be used at the time. This system can operate with two different FDD bands but only one of those bands can be active at particular moment in time.                                                                                        |

| RF Front End   | For LO generation, the ADRV9001 uses internal VCO that generates square wave type signal. A square wave LO would produce harmonics. For example: depending of RF matching used on the RF ports user $2^{nd}$ LO harmonic can be as high as $-50$ dBc and $3^{rd}$ harmonic can be as high as $-9$ dBc. Therefore, the RF filtering on the Rx and Tx path must ensure that signals at the LO harmonic frequencies (up to $9^{th}$ in some cases) are not affecting overall system performance.                                                                                                                                                               |

| DPD            | The DPD functionality is not available when ADRV9001 operates in 2R2T FDD mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Calibrations   | During Rx initialization sequence user needs to ensure that there are no signals at the Rx input (external LNA should be disabled) and appropriate termination should be present at LNA output to avoid reflections of Rx calibration tones. The maximum input signal amplitude must not exceed –82 dBm/MHz for wideband modes, TBD dBm/MHz for narrowband modes. During the transmitter initialization sequence, the user needs to ensure that the power amplifier is powered down to avoid unwanted emission of transmitter calibration tones at the antenna. No transmitter tracking calibrations are available when ADRV9001 operates in 2R2T FDD mode. |

| AGPIOs         | Analog GPIOs (operating at 1.8 V level) can be used as read or write digital levels of in the end user system. AGPIOs can be used to control states of external components or read back digital logic levels from external components.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DGPIOs         | Digital GPIOs can be used to perform real-time monitoring of states of internal ADRV9001 blocks. Digital GPIOs operating as inputs can allow user to control Rx gain, Tx attenuation, AGC operation and other elements of ADRV9001 TRx. Depending on the ADRV9001 operation up to 4 GPIOs may be used by data port interface.                                                                                                                                                                                                                                                                                                                               |

| AuxADC         | AuxADC can be used to monitor analog voltage (for example, temperature sensor). Maximum AuxADC input voltage must not exceed 0.9 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AuxDAC         | AuxDAC can be used to control the VCXO responsible for generating the ADRV9001 device clock, control any circuitry that requires analog control voltage up to 1.8 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DEV_CLK_OUT    | ADRV9001 provides divided down version of DEV_CLK reference clock input signal on the DEV_CLK_OUT output. This output is intended to provide a reference clock signal to the digital components in the overall system. This output can be configured to be active after power up and before the ADRV9001 configuration stage.                                                                                                                                                                                                                                                                                                                               |

| Multichip Sync | If there is no need for multichip synchronization, the ADRV9001 can be initialized using API functions only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

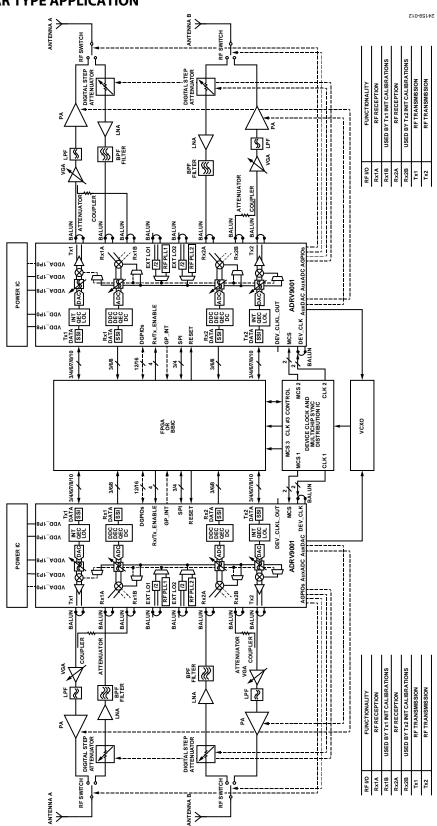

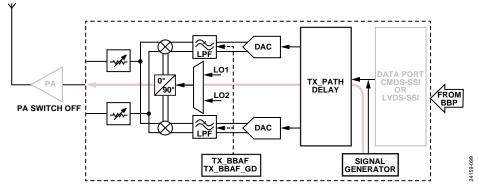

#### ADRV9001 IN SINGLE-BAND 2T2R TDD TYPE SMALL-CELL APPLICATION

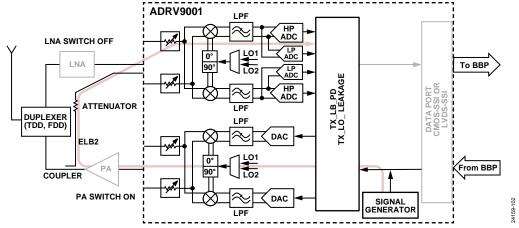

Figure 5. Single-Band 2T2R FDD Type Small-Cell Application

#### Single-Band 2T2R TDD Overview

With a minimum number of external components, the ADRV9001 transceiver can be used to build complete RF-to-bits signal chain that can serve as RF front end in TDD type small cell type applications. ADRV9001 dual Rx and Tx signal chains enables user to implement MIMO or diversity in their system. In TDD type applications, internal DPD block can be used to linearize external power amplifier and improve overall system efficiency. ADRV9001 internal AGC can be used to autonomously monitor and set appropriate gain level for Rx signal chains. For time critical TDD type applications control of the ADRV9001 TRx can be done by toggling control lines. ADRV9001 can control external Rx/Tx switch using its analog GPIOs as well as provide power amplifier bias voltage by utilizing AuxDAC outputs.

Table 3. Constrains and Limitations in Single-Band 2T2R FDD Type Small-Cell Application

| Functionality  | Constrains and Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LO Generation  | In TDD type small cell applications, ADRV9001 can use its internal LO to generate RF LO1 for both uplink and downlink. It is also possible to use external LO inputs in this mode of operation. External LO1 operating at 2× RF LO can be used for both uplink and downlink.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RF Front End   | For LO generation, the ADRV9001 uses internal VCO that generates a square wave type signal. A square wave LO would produce harmonics. For example: depending of RF matching used on the RF ports user 2nd LO harmonic can be as high as –50 dBc and 3rd harmonic can be as high as –9 dBc. Therefore, the RF filtering on the Rx and Tx path must ensure that signals at the LO harmonic frequencies (up to 9th in some cases) are not affecting overall system performance.                                                                                                                                                                                                                                                                                                                                                                           |

| DPD            | The DPD functionality can be used in the 2R2T TDD mode. Maximum channel bandwidth that DPD can support is limited by ADRV9001 RF bandwidth divided by 3 or by 5. The DPD operation can be performed by ADRV9001 or observation receiver data can be sent to the baseband processor via the receiver data port during transmit operation. The receiver path used during DPD operation to perform transmitter observation is also used by the transmitter tracking calibrations. In case of external DPD, the user must ensure that access to the receiver path during transmit slots is time-shared between DPD operation and transmitter calibrations.                                                                                                                                                                                                 |

| Calibrations   | During Rx initialization sequence user needs to ensure that there are no signals present at the Rx input (external LNA should be disabled) and appropriate termination should be present at LNA output to avoid reflections of Rx calibration tones. The maximum input signal amplitude must not exceed –82 dBm/MHz for wideband modes, TBD dBm/MHz for narrowband modes. During Tx initialization sequence, the user needs to ensure that Power Amplifier is powered down to avoid unwanted emission of Tx calibration tones at the antenna.  ADRV9001 needs to access Rx datapath during Tx time slots for Tx tracking calibration to operate. If user use Tx observation path with DPD functionality performed by baseband processor, then access to the Rx datapath during Tx slots must be time-shared between DPD operation and Tx calibrations. |

| AGPIOs         | Analog GPIOs (operating at 1.8 V level) can be used as read or write digital levels of in the end user system. AGPIOs can be used to control states of external components or read back digital logic levels from external components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DGPIOs         | Digital GPIOs can be used to perform real-time monitoring of states of internal ADRV9001 blocks. Digital GPIOs operating as inputs can allow user to control Rx gain, Tx attenuation, AGC operation and other elements of ADRV9001 TRx. Depending on the ADRV9001 operation up to 4 GPIOs may be used by data port interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AuxADC         | AuxADC can be used to monitor analog voltage (for example, temperature sensor). Maximum AuxADC input voltage must not exceed 0.9 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AuxDAC         | AuxDAC can be used to control the VCXO responsible for generating the ADRV9001 device clock, generate preconfigured ramp up/down signal that can be used to control power amplifier bias, control any circuitry that requires analog control voltage up to 1.8 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DEV_CLK_OUT    | The ADRV9001 provides divided down version of DEV_CLK reference clock input signal on the DEV_CLK_OUT output. This output is intended to provide reference clock signal to the digital components in the overall system. This output can be configured to be active after power up and before ADRV9001 configuration stage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Multichip Sync | If there is no need for multichip synchronization, the ADRV9001 can be initialized using API functions only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

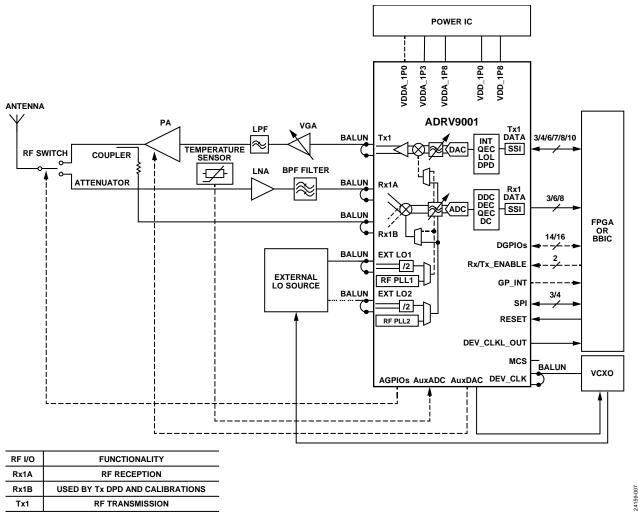

# ADRV9001 IN 1T1R FDD WITH DPD TYPE APPLICATION

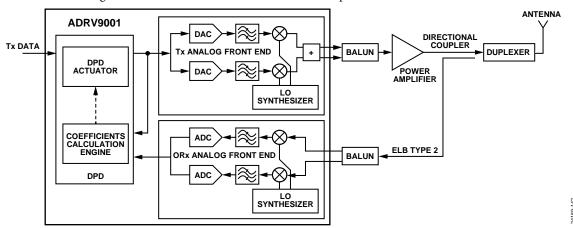

Figure 6. ADRV9001 in 1T1R FDD with DPD Type Application

#### 1T1R FDD with DPD Overview

With a minimum number of external components, the ADRV9001 transceiver can be used to build complete RF-to-bits signal chain that can serve as RF front end in FDD type applications that requires DPD. Internal DPD block can be used to linearize external power amplifier and improve overall system efficiency. For systems that demand superior LO phase noise performance, ADRV9001 allows user to apply eternal RF LO. ADRV9001 internal AGC can be used to autonomously monitor and set the appropriate gain level for Rx signal chain. ADRV9001 can control external LNA using its analog GPIOs as well as provide power amplifier bias voltage by utilizing AuxDAC outputs.

Table 4. Constrains and Limitations in 1T1R FDD with DPD Type Application

| Functionality  | Constrains and Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LO Generation  | In 1T1R FDD+DPD type applications, ADRV9001 can use its internal LO to generate RF LO1 for uplink and RF LO2 for downlink. For applications with stringent RF LO requirements, the user can use external LO inputs. External LO1 operating at 2× RF LO can be used for uplink and separate external LO2 operating at 2× RF LO for downlink.                                                                                                                                                                                                                                                                       |

| RF Front End   | For LO generation, the ADRV9001 uses internal VCO that generates square wave type signal. A square wave LO would produce harmonics. For example: depending of RF matching used on the RF ports user 2nd LO harmonic can be as high as –50 dBc and 3rd harmonic can be as high as –9 dBc. Therefore, the RF filtering on the Rx and Tx path must ensure that signals at the LO harmonic frequencies (up to 9th in some cases) are not affecting overall system performance.                                                                                                                                        |

| DPD            | The DPD functionality can be used in the 1T1R FDD mode with second Tx being disabled. Maximum channel bandwidth that DPD can support is limited by ADRV9001 RF bandwidth divided by 3 or by 5. The DPD operation can be performed by ADRV9001 or Rx data can be sent to baseband processor via Rx data port serving as observation Rx. Rx path used during DPD operation to perform Tx observation is also used by the Tx tracking calibrations. In case of external DPD, user must ensure that access to the Rx path during Tx slots is time-shared between external DPD operation and internal Tx calibrations. |

| Calibrations   | During Rx initialization sequence, the user needs to ensure that there are no signals present at the Rx input (external LNA should be disabled) and appropriate termination should be present at LNA output to avoid reflections of Rx calibration tones that are present at Rx input. The maximum input signal amplitude must not exceed –82 dBm/MHz for wideband modes, TBD dBm/MHz for narrowband modes.                                                                                                                                                                                                       |

|                | During Tx initialization sequence, user needs to ensure that Power Amplifier is power down to avoid unwanted emission of Tx calibration tones at the antenna. ADRV9001 needs to access Rx datapath during Tx time slots for Tx tracking calibration to operate. If user use Tx observation path with DPD functionality performed by baseband processor, then access to the Rx datapath during Tx slots must be time-shared between DPD operation and Tx calibrations.                                                                                                                                             |

| AGPIOs         | Analog GPIOs (operating at 1.8 V level) can be used as read or write digital levels of in the end user system. AGPIOs can be used to control states of external components (for example, RF Switch, LNA) or read back digital logic levels from external components.                                                                                                                                                                                                                                                                                                                                              |

| DGPIOs         | Digital GPIOs can be used to perform real-time monitoring of states of internal ADRV9001 blocks. Digital GPIOs operating as inputs can allow user to control Rx gain, Tx attenuation, AGC operation and other elements of ADRV9001 TRx. Depending on the ADRV9001 operation up to 4 GPIOs may be used by data port interface.                                                                                                                                                                                                                                                                                     |

| AuxADC         | AuxADC can be used to monitor analog voltage (for example, temperature sensor). Maximum AuxADC input voltage must not exceed 0.9 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AuxDAC         | AuxDAC can be used to control the VCXO responsible for generating the ADRV9001 device clock, generate preconfigured ramp up/down signal that can be used to control power amplifier bias or control any circuitry that requires analog control voltage up to 1.8 V.                                                                                                                                                                                                                                                                                                                                               |

| DEV_CLK_OUT    | ADRV9001 provides divided down version of DEV_CLK reference clock input signal on the DEV_CLK_OUT output. This output is intended to provide a reference clock signal to the digital components in the overall system. This output can be configured to be active after power up and before ADRV9001 configuration stage.                                                                                                                                                                                                                                                                                         |

| Multichip Sync | If there is no need for multichip synchronization, the ADRV9001 can be initialized using API functions only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

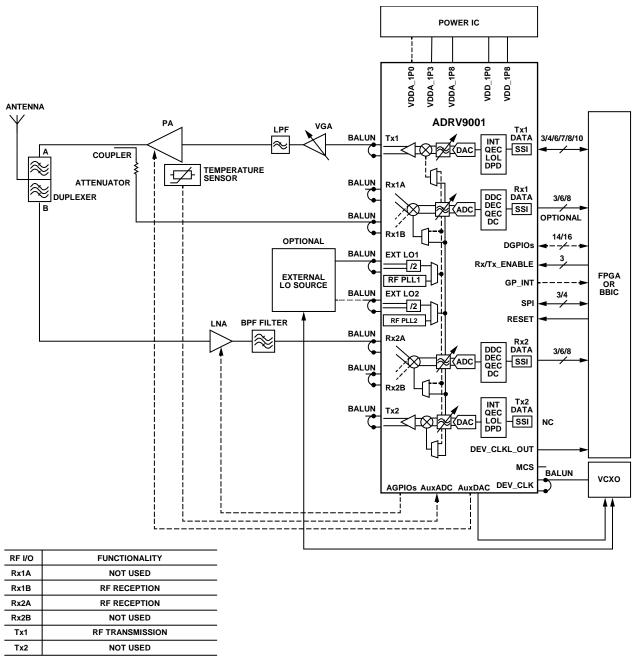

#### **ADRV9001 IN TETRA TYPE PORTABLE RADIO APPLICATION**

Figure 7. ADRV9001 in TETRA Type Portable Radio Application

#### **TETRA Type Portable Radio Overview**

With a minimum number of external components, the ADRV9001 transceiver can be used to build complete RF-to-bits signal chain that can serve as RF front end in TETRA type applications. Internal DPD block can be used to linearize external power amplifier and improve overall system efficiency. For systems that demand superior LO phase noise performance, ADRV9001 allows user to apply eternal RF LO. ADRV9001 internal AGC can be used to autonomously monitor and set appropriate gain level for Rx signal chain. For time critical TDD type applications control of the ADRV9001 TRx can be done by toggling control lines. ADRV9001 can control external Rx/Tx switch using its analog GPIOs as well as provide power amplifier bias voltage by utilizing AuxDAC outputs.

Table 5. Constrains and Limitations in TETRA Type Portable Radio Application

| Functionality | Constrains and Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LO Generation | In Portable Radio, TETRA type application, ADRV9001 can use its internal LO to generate RF LO1 for both uplink and downlink. For applications with stringent RF LO requirements, the user can use external LO inputs. External LO1 operating at 2× RF LO can be used for both uplink and downlink.                                                                                                                                                                           |

| RF Front End  | For LO generation, the ADRV9001 uses internal VCO that generates a square wave type signal. A square wave LO would produce harmonics. For example: depending of RF matching used on the RF ports user 2nd LO harmonic car be as high as –50 dBc and 3rd harmonic can be as high as –9 dBc. Therefore, the RF filtering on the Rx and Tx path must ensure that signals at the LO harmonic frequencies (up to 9th in some cases) are not affecting overall system performance. |

| Functionality  | Constrains and Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPD            | The DPD functionality can be used in the 1T1R TDD mode. Maximum channel bandwidth that DPD can support is limited by ADRV9001 RF bandwidth divided by 3 or by 5. The DPD operation can be performed by ADRV9001 or Rx data can be sent to baseband processor via Rx data port during Tx operation. Rx path used during DPD operation to perform Tx observation is also used by the Tx tracking calibrations. In case of external DPD, user must ensure that access to the Rx path during Tx slots is time-shared between external DPD operation and Tx calls.                                                                                                                                                                                                                                                                                              |

| Calibrations   | During Rx initialization sequence, the user needs to ensure that there are no signals present at the Rx input (external LNA should be disabled) and appropriate termination should be present at the LNA output to avoid reflections of Rx calibration tones. The maximum input signal amplitude must not exceed –82 dBm/MHz for wideband modes, TBD dBm/MHz for narrowband modes. During Tx initialization sequence, user needs to ensure that Power Amplifier is powered down to avoid unwanted emission of Tx calibration tones at the antenna. ADRV9001 needs to access Rx datapath during Tx time slots for Tx tracking calibration to operate. If user use Tx observation path with DPD functionality performed by baseband processor, then access to the Rx datapath during Tx slots must be time-shared between DPD operation and Tx calibrations. |

| AGPIOs         | Analog GPIOs (operating at 1.8 V level) can be used as read or write digital levels of in the end user system. AGPIOs can be used to control states of external components (for example, RF Switch) or read back digital logic levels from external components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DGPIOs         | Digital GPIOs can be used to perform real-time monitoring of states of internal ADRV9001 blocks. Digital GPIOs operating as inputs can allow user to control Rx gain, Tx attenuation, AGC operation and other elements of ADRV9001 TRx. Depending on the ADRV9001 operation up to 4 GPIOs may be used by data port interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AuxADC         | AuxADC can be used to monitor analog voltage (for example, temperature sensor). Maximum AuxADC input voltage must not exceed 0.9 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AuxDAC         | AuxDAC can be used to control the VCXO responsible for generating the ADRV9001 device clock, generate preconfigured ramp up/down signal that can be used to control power amplifier bias, control any circuitry that requires analog control voltage up to 1.8 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DEV_CLK_OUT    | ADRV9001 provides divided down version of DEV_CLK reference clock input signal on the DEV_CLK_OUT output. This output is intended to provide reference clock signal to the digital components in the overall system. This output can be configured to be active after power up and before ADRV9001 configuration stage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Multichip Sync | If there is no need for multichip synchronization, the ADRV9001 can be initialized using API functions only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

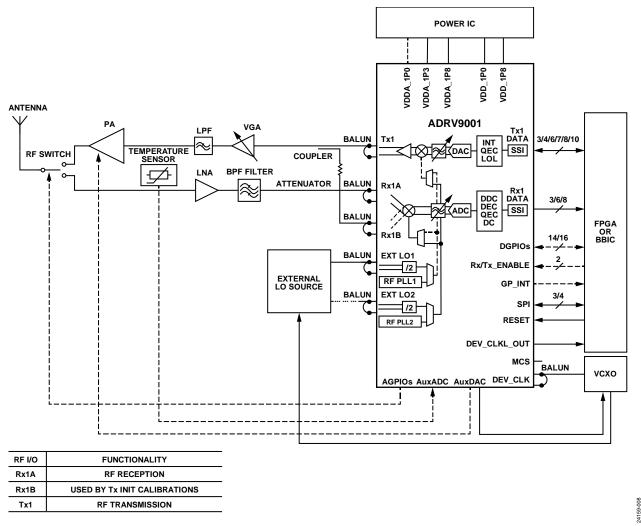

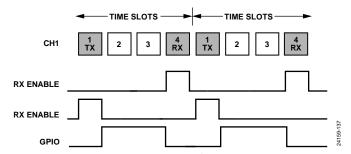

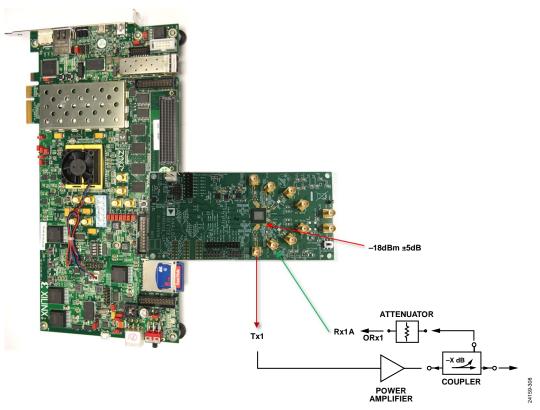

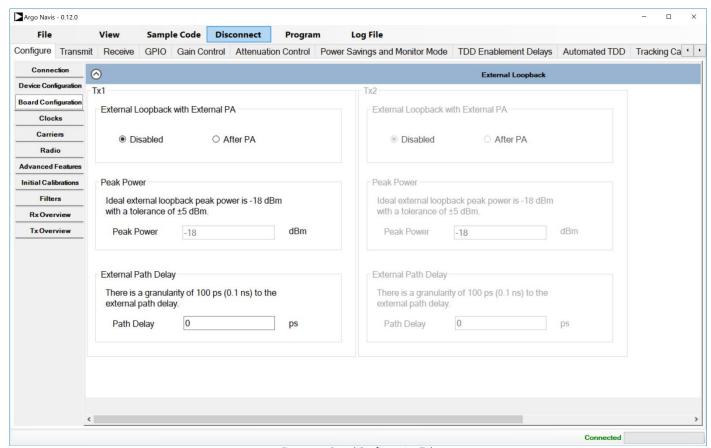

#### ADRV9001 IN DMR TYPE PORTABLE RADIO APPLICATION

Figure 8. ADRV9001 in DMR Type Portable Radio Application

#### DMR Type Portable Radio Overview

With a minimum number of external components, the ADRV9001 transceiver can be used to build complete RF-to-bits signal chain that can serve as RF front end in DMR type applications. For systems that demand superior LO phase noise performance, ADRV9001 allows user to apply eternal RF LO. ADRV9001 internal AGC can be used to autonomously monitor and set the appropriate gain level for the Rx signal chain. For time critical TDD type applications control of the ADRV9001 TRx can be done by toggling control lines. ADRV9001 can control external Rx/Tx switch using its analog GPIOs as well as provide power amplifier bias voltage by utilizing AuxDAC outputs.

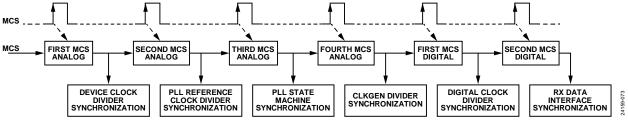

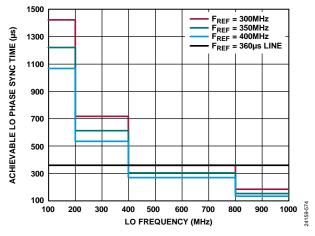

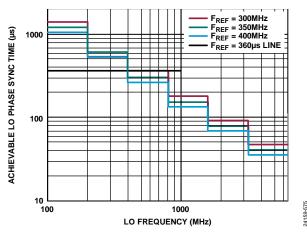

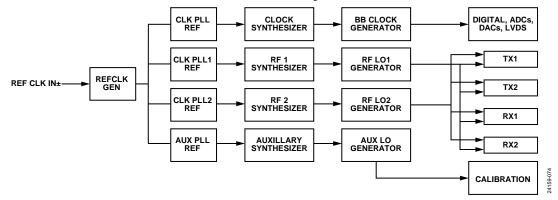

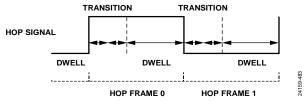

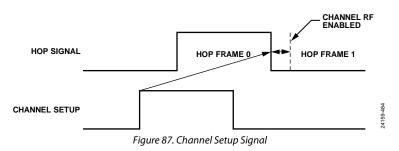

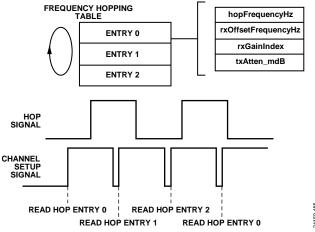

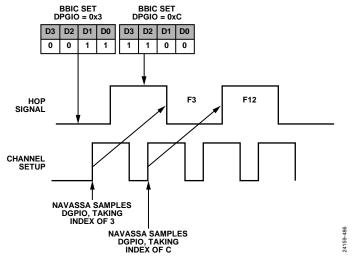

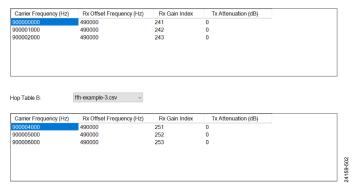

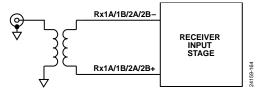

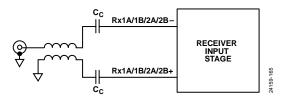

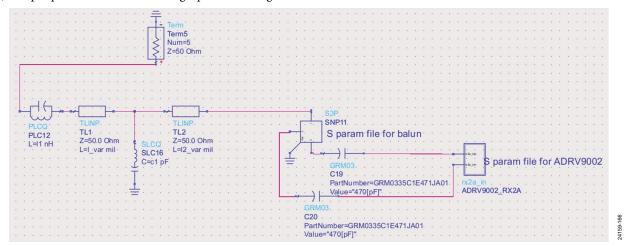

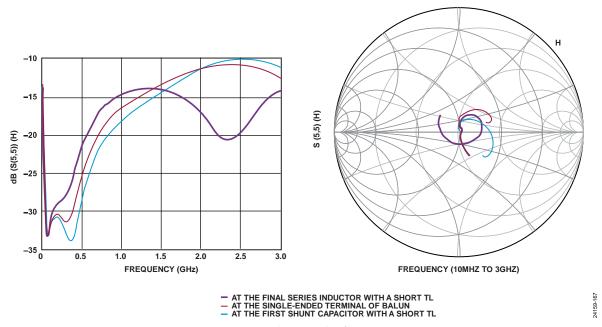

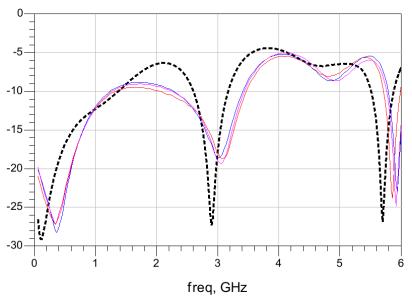

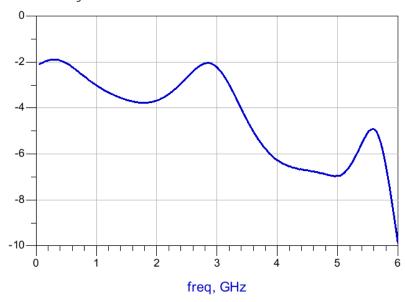

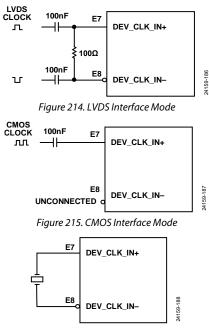

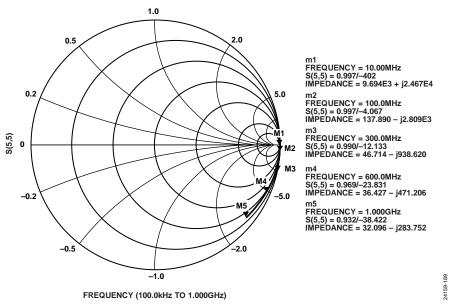

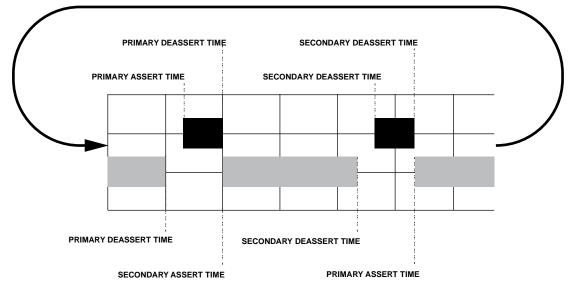

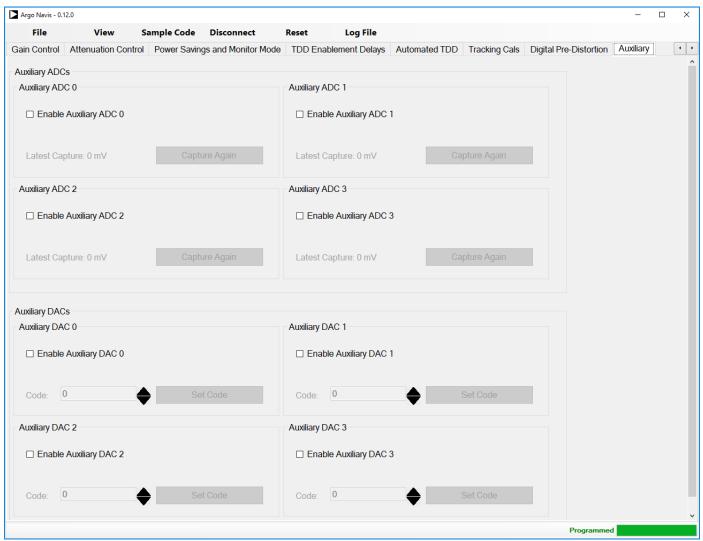

Table 6. Constrains and Limitations in DMR type Portable Radio Application