# SuperQ™ 200-V N-Channel Power MOSFET

#### **FEATURES**

- Wide SOA and current capability

- Robustness under fault conditions

- 100% UIS tested in production

- Low switching losses, Qsw and Eoss

- Easier parallelling with ± 0.5V gate threshold

#### **APPLICATIONS**

- Motor control

- Boost converters and SMPS control FETs

- Secondary side synchronous rectifier

#### **DESCRIPTION**

Engineered for SMPS and high-efficiency motor drives, this 200V SuperQ MOSFET delivers ultra-low conduction and switching losses in a robust TO-220 package. Featuring best-in-class R<sub>DS(on)</sub>, Q<sub>SW</sub> and E<sub>OSS</sub>, it minimizes heat dissipation at both full and partial loads.

#### PRODUCT SUMMARY

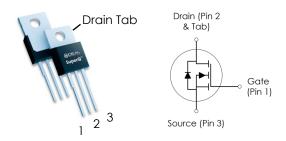

**TO-220**

| Parameter<br>T <sub>A</sub> = 25°C | Value | Unit |

|------------------------------------|-------|------|

| V <sub>DS</sub>                    | 200   | ٧    |

| R <sub>DS(on),max</sub>            | 25    | mΩ   |

| ID                                 | 40    | Α    |

| Q <sub>G</sub>                     | 26.5  | nC   |

| Qsw                                | 2.7   | nC   |

| Eoss                               | 1     | μJ   |

| ORDERING INFORMATION |         |            |           |  |

|----------------------|---------|------------|-----------|--|

| Part Number          | Package | Marking    | Packaging |  |

| iS20M028S1P          | TO-220  | iS20M028S1 | 50pc Tube |  |

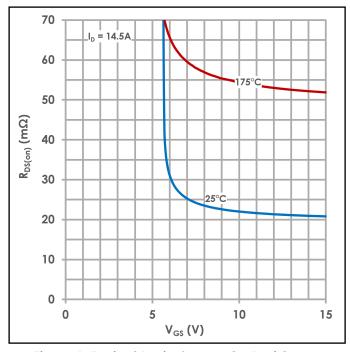

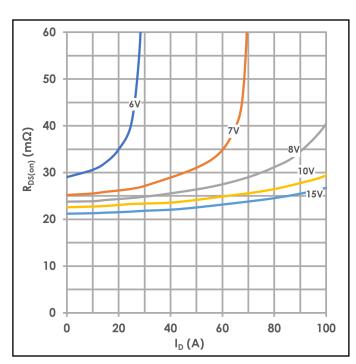

Figure 1: Typical Drain-Source On Resistance

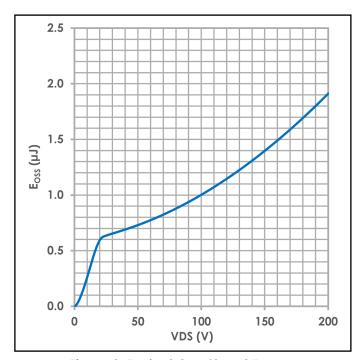

Figure 2: Typical Coss Stored Energy

| BSOLUTE MAXIMUM RATINGS |                                                                      |             |      |  |

|-------------------------|----------------------------------------------------------------------|-------------|------|--|

| SYMBOL                  | BOL PARAMETER (T <sub>A</sub> = 25°C unless otherwise specified)     |             | UNIT |  |

| V <sub>G</sub> s        | Gate-to-source voltage                                               | <u>+</u> 20 | V    |  |

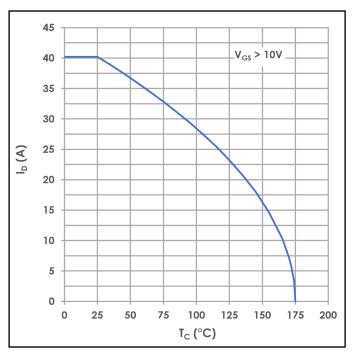

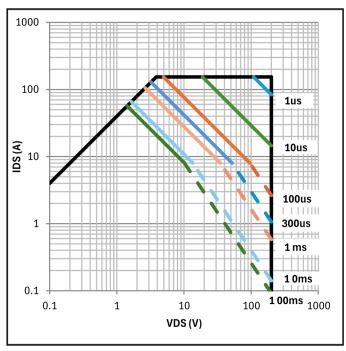

| l <sub>D</sub>          | Continuous drain current (silicon limited), T <sub>C</sub> = 25°C    | 40          | А    |  |

|                         | Continuous drain current (silicon limited), T <sub>C</sub> = 100°C   | 28          |      |  |

| I <sub>DM</sub>         | Pulsed drain current                                                 | 154         | Α    |  |

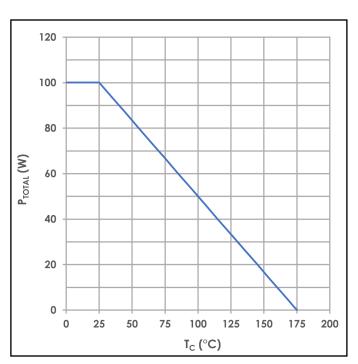

| P <sub>D</sub>          | Power dissipation, $T_C = 25^{\circ}C$                               | 100         | W    |  |

| TJ, Tstg                | Operating junction, storage temperature                              | -55 to 175  | °C   |  |

| Eas                     | Avalanche energy, single pulse $I_D$ = 17.8A, $R_{GS}$ = 25 $\Omega$ | 159         | mJ   |  |

| THERMAL CHARACTERISTICS                               |                                                              |       |     |     |      |

|-------------------------------------------------------|--------------------------------------------------------------|-------|-----|-----|------|

| SYMBOL PARAMETER (TA = 25°C unless otherwise specifie | DADAMETED II. 1990                                           | VALUE |     |     |      |

|                                                       | YARAMETER (I <sub>A</sub> = 25°C unless otherwise specified) | MIN   | TYP | MAX | UNIT |

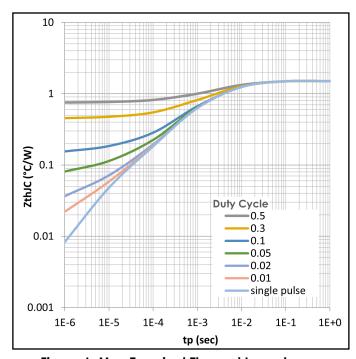

| R <sub>OJC</sub>                                      | Junction-to-case thermal resistance - TO-220                 | -     | -   | 1.5 | °C/W |

| R <sub>0</sub> JA                                     | Junction-to-ambient thermal resistance (1)                   |       | -   | 40  | °C/W |

| R <sub>0JA</sub>                                      | Junction-to-ambient thermal resistance, minimal footprint    | -     | -   | 62  | °C/W |

<sup>(1) 40</sup> mm x 40 mm x 1.5 mm epoxy PCB FR4 with 6 cm<sup>2</sup> (one layer, 70 µm thick) copper area for drain connection. PCB is vertical in still air.

| SYMBOL               | PARAMETER                        |                                                                          | VALUE |       |       |      |

|----------------------|----------------------------------|--------------------------------------------------------------------------|-------|-------|-------|------|

|                      |                                  | TEST CONDITIONS                                                          | MIN   | TYP   | MAX   | UNIT |

| STATIC CI            |                                  |                                                                          |       |       |       |      |

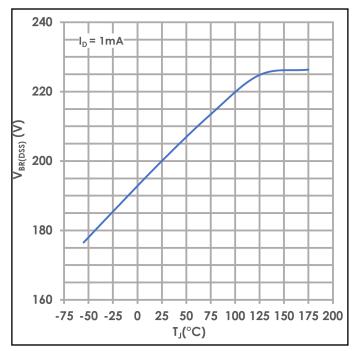

| BV <sub>DSS</sub>    | Drain-to-source voltage          | $V_{GS} = 0V$ , $I_D = 1mA$                                              | 200   | -     | -     | ٧    |

|                      | Danis to some la alimenta a mand | $V_{GS} = 0V$ , $V_{DS} = 160V$ , $T_{J} = 25$ °C                        | -     | 0.03  | 1     | μΑ   |

| I <sub>DSS</sub>     | Drain-to-source leakage current  | V <sub>GS</sub> = 0V, V <sub>DS</sub> = 160V, T <sub>J</sub> = 125°C (2) | -     | 13    | 100   |      |

| lgss                 | Gate-to-source leakage current   | $V_{DS} = 0V$ , $V_{GS} = 20V$                                           | -     | 0.4   | 100   | nA   |

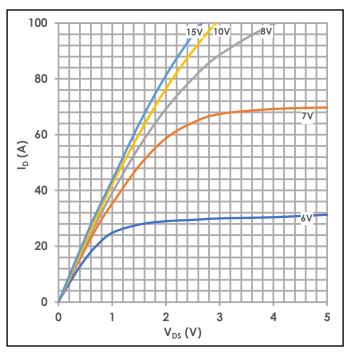

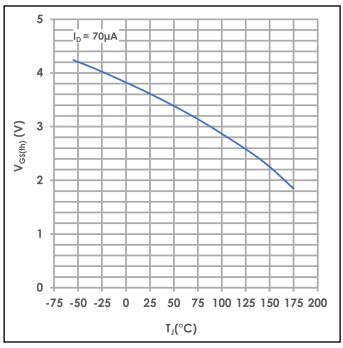

| V <sub>GS(th)</sub>  | Gate-to-source threshold voltage | $V_{DS} = V_{GS}$ , $I_D = 70\mu A$                                      | 3.1   | 3.6   | 4.1   | ٧    |

| R <sub>DS(on)</sub>  | Drain-to-source on-resistance    | V <sub>GS</sub> = 10V, I <sub>D</sub> = 14.5A                            | -     | 22    | 25    | mΩ   |

| <b>G</b> fs          | Transconductance (2)             | V <sub>DS</sub> = 10V, I <sub>D</sub> = 14.5A                            | 16    | 31    | -     | S    |

| DYNAMIC              | CHARACTERISTICS                  | ·                                                                        |       |       |       |      |

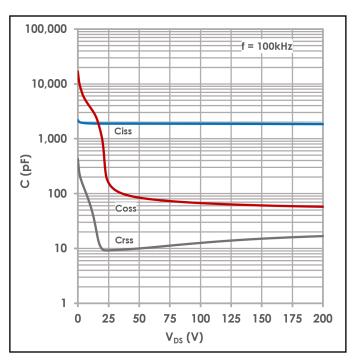

| Ciss                 | Input capacitance (2)            |                                                                          | -     | 1,865 | 2,425 |      |

| Crss                 | Reverse transfer capacitance (2) | $V_{GS} = 0V$ , $V_{DS} = 100V$ , $f = 100kHz$                           | -     | 12    | 16    | рF   |

| Coss                 | Output capacitance (2)           |                                                                          | -     | 67    | 86    |      |

| C <sub>o(er)</sub>   | Effective output capacitance     | V <sub>DS</sub> = 0 to 100V, V <sub>GS</sub> = 0V                        | -     | 197   | -     |      |

| R <sub>G</sub>       | Series gate resistance           | f = 1 MHz                                                                | -     | 4.5   | 6.8   | Ω    |

| t <sub>d(on)</sub>   | Turn-on delay time               |                                                                          | -     | 8.5   | -     |      |

| † <sub>r</sub>       | Rise time                        | $V_{DS} = 100V$ , $V_{GS} = 10V$ , $I_{DS} = 14.5A$ ,                    | -     | 1.9   | -     |      |

| t <sub>d(off)</sub>  | Turn-off delay time              | $R_{G,EXT} = 0 \Omega$                                                   | -     | 24.7  | -     | ns   |

| † <sub>f</sub>       | Fall time                        |                                                                          | -     | 11.3  | -     |      |

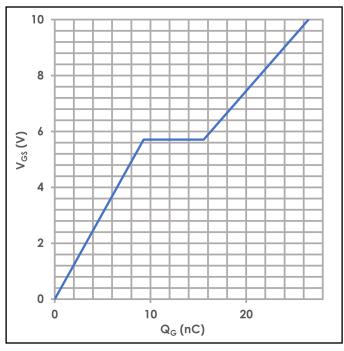

| GATE CH              | ARGE CHARACTERISTICS             | '                                                                        |       |       |       |      |

| Q <sub>g</sub>       | Gate charge total (2)            |                                                                          | -     | 26.5  | 34    |      |

| Qsw                  | Switching charge (3)             | $V_{DS} = 100V, I_{D} = 14.5A,$                                          | -     | 2.7   | -     | nC   |

| Q <sub>gd</sub>      | Gate to drain charge (2)         | V <sub>GS</sub> = 0 to 10V                                               | -     | 1.4   | 1.8   |      |

| V <sub>plateau</sub> | Gate plateau voltage             |                                                                          | -     | 5.7   | -     | V    |

| Qoss                 | Output charge (2)                |                                                                          | -     | 95    | 108   | nC   |

| E <sub>oss</sub>     | Capacitive stored energy         | $V_{DS} = 0$ to 100V, $V_{GS} = 0$ V                                     | -     | 1     | -     | μJ   |

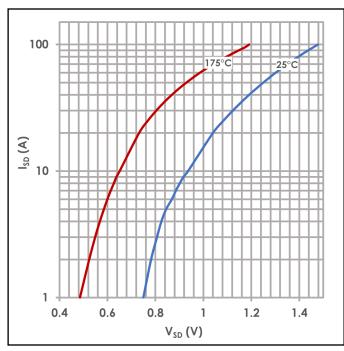

| DIODE CH             | IARACTERISTICS                   |                                                                          |       |       |       |      |

| V <sub>SD</sub>      | Diode forward voltage            | I <sub>SD</sub> = 14.5A, V <sub>GS</sub> = 0V                            | -     | 1.0   | 1.2   | V    |

| Q <sub>rr</sub>      | Reverse recovery charge          | V <sub>DS</sub> = 100V, I <sub>F</sub> = 14.5A,                          | -     | 425   | -     | nC   |

| † <sub>rr</sub>      | Reverse recovery time            | di/dt = 100A/µs                                                          | -     | 107   | -     | ns   |

<sup>(2)</sup> Defined by design. Not subject to production test.

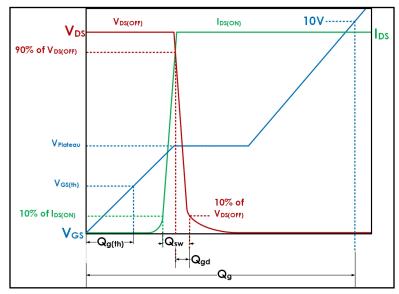

<sup>(3)</sup> Q<sub>SW</sub> should be used for switching loss calculations. See Figure 16 and Q<sub>SW</sub> application note on www.idealsemi.com

Figure 3: Drain Current

Figure 4: Power Dissipation

Figure 5: Safe Operating Area

Figure 6: Max Transient Thermal Impedance

Figure 7: Typical Output Characteristics

Figure 8: Typical Drain-Source On-Resistance

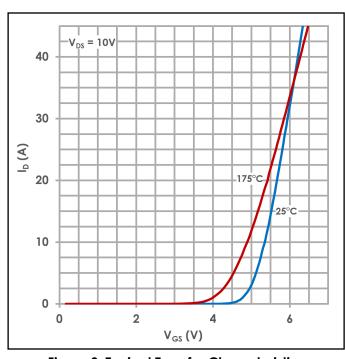

Figure 9: Typical Transfer Characteristics

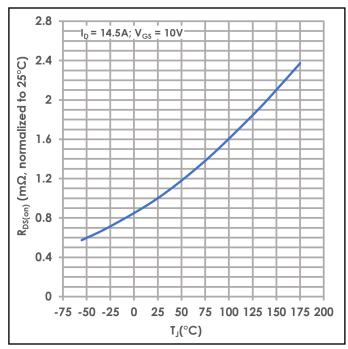

Figure 10: Normalized On-State Resistance vs.

Temperature

Figure 11: Typical Threshold Voltage

Figure 12: Typical Capacitances

Figure 13: Typical Diode Forward Voltage

Figure 14: Min Drain-Source Breakdown Voltage

Figure 15: Typical Gate Charge

Figure 16: Gate Charge Definitions

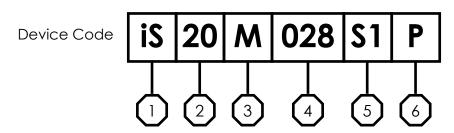

# **DEVICE DECODER RING**

- (1) iDEAL Semiconductor product

- Voltage rating divided by 10 (200V)

- M = N-Channel MOSFET, Standard Threshold

- 4 Maximum drain-to-source resistance

- 5 SuperQ™ Generation

- **6** P = TO-220

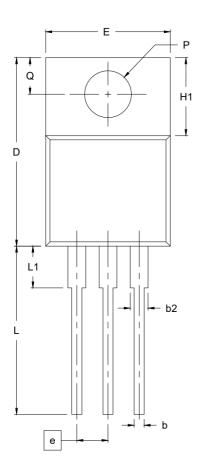

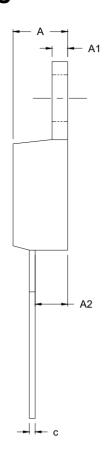

# **TO-220 Package Drawing**

| SYMBOL | MIN      | MAX   |

|--------|----------|-------|

| Α      | 4.19     | 4.82  |

| A1     | 1.14     | 1.40  |

| A2     | 2.38     | 2.92  |

| b      | 0.63     | 1.01  |

| b2     | 1.13     | 1.78  |

| С      | 0.31     | 0.64  |

| D      | 14.22    | 16.51 |

| Е      | 9.66     | 10.66 |

| е      | 2.54 BSC |       |

| H1     | 5.85     | 6.85  |

| L      | 12.70    | 14.73 |

| L1     | 2.39     | 4.42  |

| Р      | 3.54     | 4.08  |

| Q      | 2.54     | 3.42  |

| Markan |          | -     |

- All linear dimensions in millimeters

Dimensions D and E do not include mold flash or protrusions

| Revision History |                |                                                            |  |  |

|------------------|----------------|------------------------------------------------------------|--|--|

| Version          | Date           | Comments                                                   |  |  |

| 1.0              | July 2025      | Initial Release                                            |  |  |

| 1.1              | September 2025 | Gate charge characteristics table updated. Figure 16 added |  |  |

#### IMPORTANT NOTICE AND DISCLAIMER

IDEAL SEMICONDUCTOR DEVICES, INC. ("IDEAL") PROVIDES THE DATASHEET AND ALL SUPPORTING DESIGN RESOURCES, SAFETY INFORMATION, AND OTHER MATERIALS (THE "RESOURCES") "AS IS". IDEAL AND/OR ITS LICENSORS DO NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE RESOURCES OR THAT SUCH RESOURCES WILL BE SUITABLE FOR YOUR APPLICATION. IDEAL HEREBY DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, OR NON-INFRINGEMENT.

You are only permitted to use the Resources and any products provided by iDEAL ("Products") in accordance with the operating parameters set forth in the Resources and iDEAL's standard terms and conditions made available at the time of order placement. Please note that the Resources are intended for skilled, technically-trained developers. You are solely responsible for, and iDEAL disclaims all responsibility and liability for: (a) choosing the Products and evaluating the suitability of such Products for the intended application, as well as determining if the information in the Resources is complete for your application; (b) designing, validating and testing the Products in your system; and (c) ensuring your application meets applicable safety, security, regulatory or other industry requirements and standards. iDEAL assumes no liability for any damage or malfunction resulting from improper handling of Products, or use of Products and Resources outside of the specified parameters. You are responsible for consulting the latest datasheet before placing orders.

iDEAL reserves the right to make corrections, modifications, enhancements, improvements and other change to or otherwise discontinue its Resources and Products in its sole discretion at any time without notice. All Products are sold subject to iDEAL's standard terms and conditions made available at the time of order placement.

Mailing Address:

iDEAL Semiconductor Devices, Inc. 116 Research Drive Bethlehem, Pennsylvania, USA 18015 info@idealsemi.com