Data Sheet DMM-3537-2-B

The PUI Audio DMM-3537-2-B digital PDM output MEMS omni-directional microphone features a nominal -37dBFS sensitivity, 68dB(A) signal-to-noise ratio, and a bottom port.

### Features:

- 2.65mm x 3.50mm package

- 1.0mm height

- -37dBFS sensitivity

- 68dB (typical) signal-to-noise ratio

- Omni-directional polar response

**Specifications**  $V_{SUPP} = 1.8V_{DC}$ ,  $f_{IN} = 1$ kHz, Acoustic Input = 94dBSPL (1Pa), 0 dBV = 1V @ 1Pa, bandwidth (BW) = 20Hz  $\leq f \leq 20$ kHz, A-weighted, unless otherwise stated.

| Parameters                                                                   | Values                     | Units                                |                         |          |  |

|------------------------------------------------------------------------------|----------------------------|--------------------------------------|-------------------------|----------|--|

| Typical Sensitivity                                                          |                            | $f_{CLK} = 2.4MHz$                   | -37 ±1                  | dBFS     |  |

|                                                                              |                            | $f_{CLK} = 768 \text{kHz}$           | -21 ±1                  |          |  |

| Typical Signal-to-Noise Ratio 20Hz ≤ f ≤ 20kHz acoustic bandwidth A-weighted |                            | $f_{CLK} \le 2.4 MHz$                | 68                      | dB       |  |

|                                                                              |                            | $f_{CLK} = 768 \text{kHz}$           | 65                      | ub       |  |

| Typical Frequency Range                                                      |                            |                                      | $20 \le f \le 20,000$   | Hz       |  |

| Maximum Total Harmonic Distortion A-weighted $768kHz \le f_{CLK} \le 2.4MHz$ |                            |                                      | 0.15                    | %        |  |

| Typical Acoustic Overloa                                                     | d Point (AOP)              | $f_{CLK} = 2.4MHz$                   | 135                     | JDCDI    |  |

| THD = 10%                                                                    |                            | $f_{CLK} = 768 \text{kHz}$           | 118                     | dBSPL    |  |

| Operating Voltage Range                                                      |                            |                                      | $1.65 \le V_S \le 1.98$ | $V_{DC}$ |  |

| Typical Power Supply Current                                                 |                            | $f_{CLK} = 2.4MHz$                   | 310                     | μА       |  |

|                                                                              |                            | $f_{CLK} = 768kHz$                   | 150                     |          |  |

|                                                                              |                            | $f_{CLK} \le 200 \text{kHz}$         | 9                       |          |  |

| Directivity                                                                  | Omnidirectional            | -                                    |                         |          |  |

| Environmental Complian                                                       | ices                       |                                      | RoHS/Halogen Free       | -        |  |

| Typical Power Supply<br>Rejection (PSR)<br>100mV <sub>PP</sub>               |                            | $f_{NOISE} = 20$ Hz Sine Wave        | -99                     |          |  |

|                                                                              |                            | $f_{NOISE} = 1 \text{kHz Sine Wave}$ | -124                    |          |  |

|                                                                              | $f_{CLK} = 2.4MHz$         | $f_{NOISE} = 5kHz$ Sine Wave         | -105                    |          |  |

|                                                                              | ICLK - 2.4WIIIZ            | $f_{NOISE} = 10kHz$ Sine Wave        | -101                    | dBFS     |  |

|                                                                              |                            | $f_{NOISE} = 20kHz$ Sine Wave        | -99                     | ]        |  |

|                                                                              |                            | $f_{NOISE} = 217Hz$ Square Wave      | -105                    |          |  |

|                                                                              | $f_{CLK} = 768 \text{kHz}$ | $f_{NOISE} = 217Hz$ Square Wave      | -90                     |          |  |

**Specifications** (continued)  $V_{SUPP} = 1.8V_{DC}$ ,  $f_{IN} = 1$ kHz, Acoustic Input = 94dBSPL (1Pa), 0 dBV = 1V @ 1Pa, bandwidth (BW) = 20Hz  $\leq f \leq 20$ kHz, A-weighted, unless otherwise stated.

| Parameters                                                 |                       |                            |                                       | Values         | Units                 |          |  |

|------------------------------------------------------------|-----------------------|----------------------------|---------------------------------------|----------------|-----------------------|----------|--|

|                                                            |                       | <sub>ζ</sub> = 2.4MHz      | 82                                    | 1DEC           |                       |          |  |

| 200mVpp Sine Wave<br>f <sub>NOISE</sub> = 1kHz             |                       | $f_{CLI}$                  | < = 768kHz                            | 67             | - dBFS                |          |  |

| Clock Frequency                                            | Standar               | Standard operational mode  |                                       | Minimum        | 2.0                   | MHz      |  |

|                                                            | Standar               |                            |                                       | Maximum        | 4.8                   |          |  |

|                                                            | Low no                | Low power operational mode |                                       | Minimum        | 400                   |          |  |

|                                                            | доw ро                | wer operational in         | ouc                                   | Maximum        | 800                   |          |  |

|                                                            | Sleen m               | Sleep mode                 |                                       | Minimum        |                       | kHz      |  |

|                                                            | этеер п               |                            |                                       | Maximum        | 200                   | КПХ      |  |

| Logic-High Input Level (V <sub>IH</sub> )                  |                       |                            | Minimum                               | $(0.65)V_{DD}$ |                       |          |  |

| Logic-mgn mput Level                                       | (VIH)                 |                            |                                       | Maximum        |                       |          |  |

| Logic-Low Input Level (                                    | (V)                   |                            |                                       | Minimum        |                       |          |  |

| Logic-Low Input Level                                      | (VIL)                 |                            |                                       | Maximum        | $(0.35)V_{DD}$        |          |  |

| Logic-High Output Leve                                     | el (V <sub>OH</sub> ) |                            |                                       | Minimum        | $(0.70)V_{DD}$        | V        |  |

| $I_{OUT} = 0.5 \text{mA}$                                  |                       |                            |                                       | Maximum        |                       |          |  |

| Logic-Low Output Leve                                      | el (V <sub>OL</sub> ) |                            |                                       | Minimum        |                       |          |  |

| $I_{OUT} = 0.5 \text{mA}$                                  |                       |                            |                                       | Maximum        | (0.30)V <sub>DD</sub> | 1        |  |

|                                                            |                       |                            |                                       | Minimum        | 45                    |          |  |

| D. 01 1 D. 0 1 (D.                                         |                       | $f_{CLK} < 3.3 MHz$        | Maximum                               | 55             | %                     |          |  |

| Bit-Clock Duty-Cycle (D                                    |                       |                            | Minimum                               | TBD            |                       |          |  |

|                                                            | 3                     |                            | $3.3$ MHz $\leq f_{CLK} \leq 4.8$ MHz |                | TBD                   |          |  |

| Maximum Bit-Clock Ris                                      | e and Fall T          | Time                       |                                       | Maximum        | 6                     |          |  |

| Delay Time for Valid Da                                    |                       | $C_{LOAD} = 0 pF$          |                                       | Minimum        | 18                    |          |  |

| T2, T4 in Timing Diagram                                   |                       | $C_{LOAD} = 140 pF$        |                                       | Maximum        | 20                    | ns       |  |

| Delay Time for High-Z Logic Output                         |                       |                            | Minimum                               | 5              | 1 113                 |          |  |

| T1, T3 in Timing Diag                                      |                       |                            |                                       | Maximum        | 16                    |          |  |

| <u> </u>                                                   |                       |                            |                                       | Minimum        | 1                     | <u> </u> |  |

| Short-Circuit Logic Quitnut Current                        |                       |                            | Maximum                               | 20             | mA                    |          |  |

| Maximum Logic Output Capacitance Load                      |                       |                            | 140                                   | рF             |                       |          |  |

| Maximum Time to Activ                                      |                       |                            |                                       |                |                       | P        |  |

| f <sub>CLK</sub> ≥ 351kHz                                  |                       |                            |                                       | 6              |                       |          |  |

| Maximum Time to Activate Sleep State (T <sub>SLEEP</sub> ) |                       |                            |                                       | _              | ms                    |          |  |

| f <sub>CLK</sub> ≤ 1.0kHz                                  |                       |                            | 1                                     |                |                       |          |  |

| Maximum Mode Change Time (T <sub>CHANGE</sub> )            |                       |                            | 3.5                                   | 1              |                       |          |  |

| Weight                                                     |                       |                            | <0.3                                  | gm             |                       |          |  |

| Operating Temperature                                      |                       |                            | $-40 \le T_0 \le 105$                 | °C             |                       |          |  |

| Storage Temperature                                        |                       |                            | $-55 \le T_S \le 150$                 | °C             |                       |          |  |

| MSL (Moisture Sensitivity Level) Class*                    |                       |                            | 1                                     | -              |                       |          |  |

<sup>\*</sup>MSL level dependent on product remaining in sealed packaging until use

# **Absolute Maximum Ratings**

| Parameters                                                | Values                     | Units    |

|-----------------------------------------------------------|----------------------------|----------|

| Maximum Voltage on V <sub>DD</sub> with respect to Ground | $-0.3 \le V_{DD} \le 1.98$ | $V_{DC}$ |

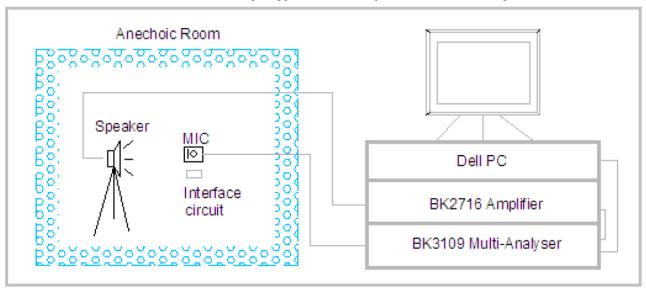

# $\textbf{Measurement Method} \ \textbf{Acoustic input applied to the microphone has a 94dBSPL amplitude}.$

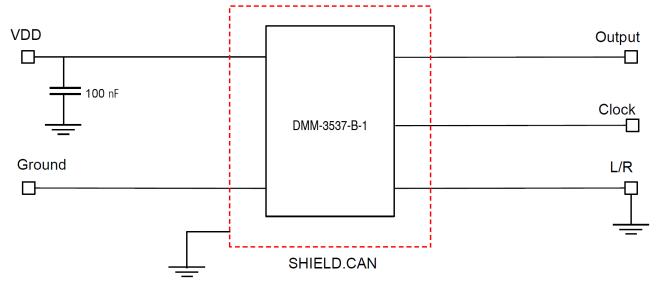

# **Recommended Drive Circuit**

©2025, PUI Audio Inc.

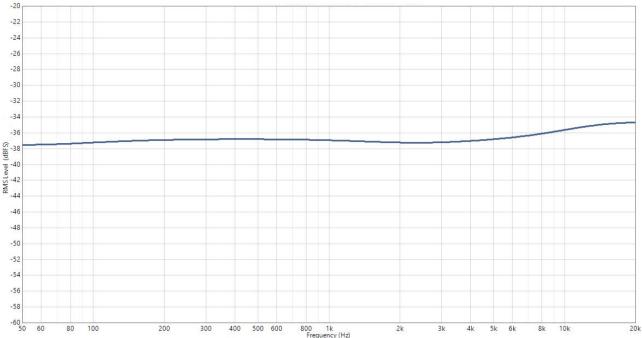

## **Typical Frequency Response** (94dBSPL acoustic input set at fin = 1kHz.)

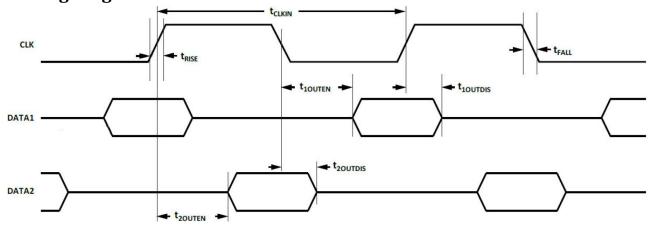

# **Timing Diagram**

$30ns \leq T_{10UTEN}, t_{20UTEN} \leq 70ns$   $5ns \leq T_{10UTDIS}, t_{20UTDIS} \leq 18ns$   $t_{RISE}, t_{FALL} \leq 25ns$

Typical Two-Channel Connection Diagram

VDD

L/R

Clock

Clock

Data-H

MIC

Data-L

MIC

Data-L

MIC

Output

**Reliability Testing** Microphone frequency response and sensitivity shall not deviate more than ±3 dB.

Ground

L/R

| Type of Test                         | Test Specifications                                                                                                                                                                                            |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Simulated Reflow<br>(Without Solder) | Samples for qualification testing require 3 passes 260±5 °C reflow solder profiles. 2 hours of setting time is required between each reflow profile test.                                                      |

| Static Humidity                      | Precondition at +25°C for 1 hour. Expose to +85°C with 85% relative humidity for 120 hours. Finally, dry at room ambient for 3±1 hour before taking final measurement.                                         |

| Temperature Shock                    | Each cycle shall consist of 30 minutes at -40°C, 30 minutes at +85°C with 5 minutes transition time. Test duration is for 30 cycles, starting from cold to hot temperature.                                    |

| ESD Sensitivity                      | Perform ESD sensitivity threshold measurements for each contact according to MIL-STD-883G, Method 3015.7 for Human Body Model. Identify the ESD threshold levels indicating passage of 8000V Human Body Model. |

| Vibration Test                       | Vibrate randomly along three perpendicular directions for 30 minutes in each direction, 4 cycles from 10Hz to 55 Hz with a peak acceleration of 20 Gs.                                                         |

| Shock Test                           | Subject samples to half-sine shock pulses (3000±15% Gs for 0.3ms) in each direction, for a total of 18 shocks.                                                                                                 |

| Drop Test                            | Drop samples from 1.5m height onto a steel surface, total 18 times and inspected for mechanical damage.                                                                                                        |

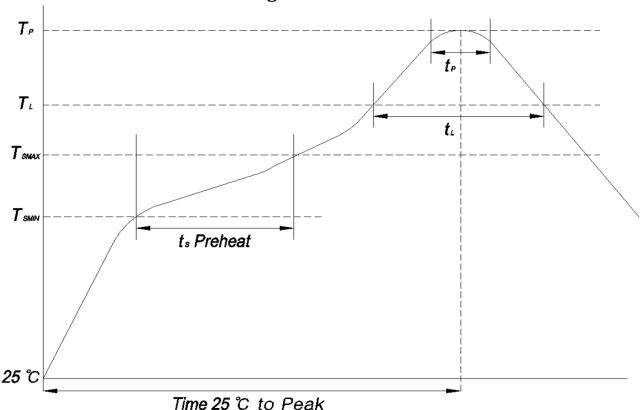

### **Recommended Reflow Soldering Procedure**

Profile Feature Lead(Pb) Free Solder Temperature min.(T<sub>SMIN</sub>) 150℃ **Preheat** Temperature max.(T<sub>SMAX</sub>) 200℃ Time (ts) 60-120 Seconds Temperature (T<sub>L</sub>) 217℃ Liquidus Time (t<sub>L</sub>) 60-150 Seconds Temperature (T<sub>P</sub>) 260℃ Peak Time within 5 °C of actual peak temperature (t<sub>P</sub>) 30 Seconds Max. Ramp up Average ramp up rate T<sub>SMAX</sub> to T<sub>P</sub> 3℃ / Second Max. Ramp down Average ramp down rate TP to TSMAX 6°C / Second Max. Time 25 ℃ to Peak temperature 8 Minutes Max.

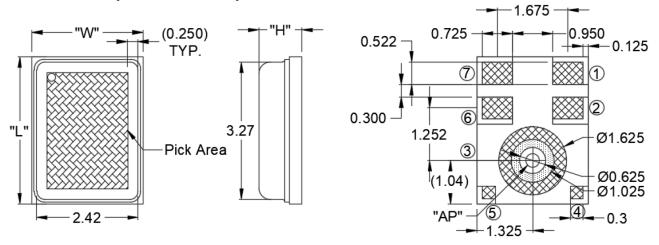

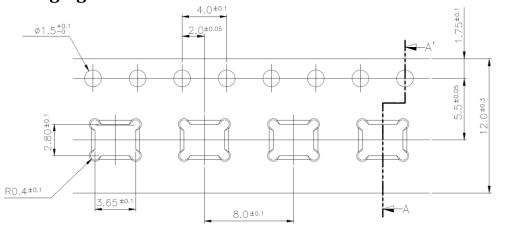

## **Dimensions** (±0.15mm tolerance)

| Item              | Dimension | Tolerance |

|-------------------|-----------|-----------|

| Length(L)         | 3.50      | ±0.10mm   |

| Width(W)          | 2.65      | ±0.10mm   |

| Height(H)         | 1.00      | ±0.10mm   |

| Acoustic Port(AP) | Ø0.325    | ±0.05mm   |

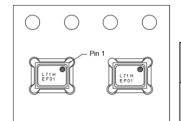

| PIN | NAME   | FUNCTION                                                                                         |  |  |

|-----|--------|--------------------------------------------------------------------------------------------------|--|--|

| 1   | Output | Digital Output                                                                                   |  |  |

| 2   | L/R    | Left or Right Channel Selection DATA1(Right): SELECT tied to GND DATA2(Left): SELECT tied to VDD |  |  |

| 3   | Ground | Ground                                                                                           |  |  |

| 4   | NC     | No connection                                                                                    |  |  |

| 5   | NC     | No connection                                                                                    |  |  |

| 6   | Clock  | Clock input to Microphone                                                                        |  |  |

| 7   | VDD    | VDD                                                                                              |  |  |

Note: Connect the "L/R" pin to ground when the microphone is used in a single-channel application.

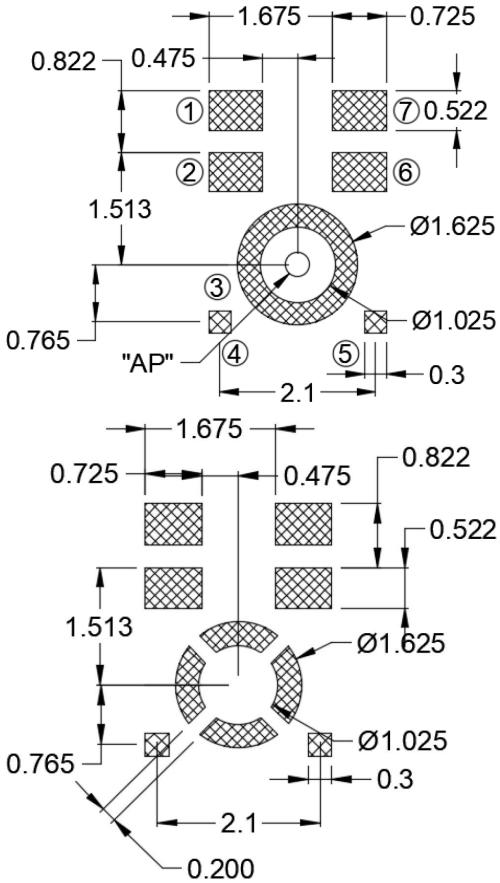

**PCB Land and Stencil Pattern** (This land pattern is advisory only and its use or adaptation is entirely voluntary. PUI Audio disclaims all liability of any kind associated with the use, application, or adaptation of this land pattern.)

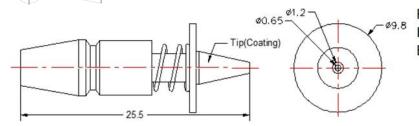

### **Pick and Place Tool Recommendations**

Note: Pick Area only extends to 0.25mm of any edge or hole unless otherwise specified.

Recommended Nozzle Model : CN065

Interner Diameter : Φ 0.65mm Externer Diameter : Φ1.2mm

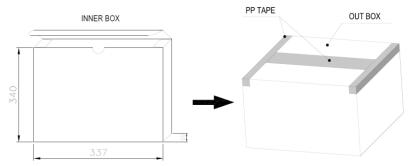

## **Packaging**

| Reel Diameter | Quantity Per Reel |

|---------------|-------------------|

| 13"           | 5,700             |

5,700PCS X 2BAG = 11,400PCS

CARTON SIZE: 330(W) X 350(L) X 355(H)

QUANTITY: 68,400 PCS

### **Specifications Revisions**

| Revision | Description                         | Date       | Approval |

|----------|-------------------------------------|------------|----------|

| A        | Datasheet released from Engineering | 04/21/2025 | KH       |

### Note:

- 1. Unless otherwise specified:

- A. All dimensions are in millimeters.

- B. Default tolerances are  $\pm 0.5$ mm and angles are  $\pm 3^{\circ}$ .

- 2. Specifications subject to change or withdrawal without notice.