# **SY89113U**

# 2.5V Low Jitter, Low Skew 1:12 LVDS Fanout Buffer with 2:1 Input MUX and Internal Termination

#### **Features**

- Selects between 1 of 2 Inputs, and Provides 12 Precision, Low Skew LVDS Output Copies

- Guaranteed AC Performance Overtemperature and Voltage:

- DC to >1 GHz Throughput

- <975 ps Propagation Delay CLK0-to-Q

- <250 ps Rise/Fall Time

- <25 ps Output-to-Output Skew

- Ultra-low Jitter Design:

- 130 fs RMS Phase Jitter (Typ)

- 0.7 ps<sub>RMS</sub> Crosstalk Induced Jitter

- Unique, Patent-pending 2:1 Input MUX Provides Superior Isolation to Minimize Channel-to-Channel Crosstalk

- CLK0 Input Features a Unique, Patent-pending Input Termination and VT Pin that Accepts ACand DC-coupled Inputs (CML, LVPECL, LVDS)

- · CLK1 Accepts Virtually Any Logic Standard:

- Single-ended: TTL/CMOS (Including 3.3V Logic), LVPECL

- Differential: LVPECL, LVDS, CML, HSTL

- · 325 mV LVDS-compatible Output Swing

- Power Supply: 2.5V ±5%

- Industrial Temperature Range –40°C to +85°C

- Available in 44-lead (7 mm × 7 mm) VQFN Package

#### **Applications**

- · Multi-processor Server

- · SONET/SDH Clock/Data Distribution

- · Fibre Channel Distribution

- · Gigabit Ethernet Clock Distribution

#### **General Description**

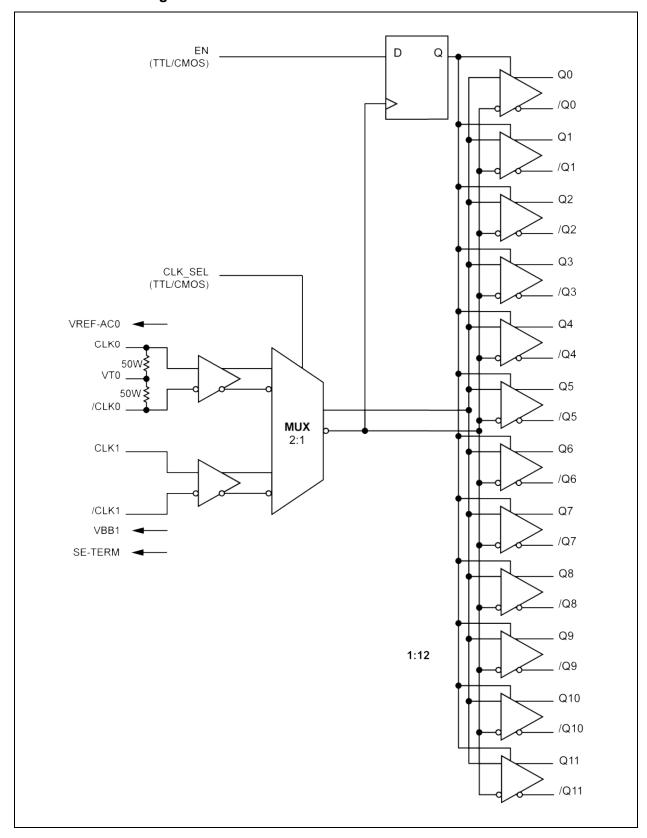

The SY89113U is a 2.5V low jitter, low skew, 1:12 LVDS fanout buffer optimized for precision telecom and enterprise server distribution applications. The input includes a 2:1 MUX for clock switchover applications. Unlike other multiplexers, this input includes a unique isolation design that minimizes channel-to-channel crosstalk. The SY89113U distributes clock frequencies from DC to >1 GHz guaranteed over temperature and voltage.

The SY89113U incorporates a synchronous output enable (EN) so that the outputs will only be enabled/disabled when they are already in the LOW state. CLK0 differential input includes Microchip's unique, 3-pin input termination architecture that directly interfaces to any differential signal (AC- or DC-coupled) as small as 100 mV (200 mV<sub>PP</sub>) without any level shifting or termination resistor networks in the signal path.

CLK1 differential input includes a new version of Microchip's unique, Any-Input architecture that directly interfaces with single-ended TTL/CMOS logic (including 3.3V logic), single-ended LVPECL, differential (AC- or DC-coupled) LVDS, HSTL, CML, and LVPECL logic levels as small as 200 mV (400 mV $_{\rm PP}$ ). CLK1 input requires external termination. LVDS output swing 325 mV into 100 $\Omega$  with extremely fast rise/fall time guaranteed to be less than 250 ps.

The SY89113U operates from a 2.5V±5% supply and is guaranteed over the full industrial temperature range of -40°C to +85°C. The SY89113U is part of Microchip's high-speed, Precision Edge® product line.

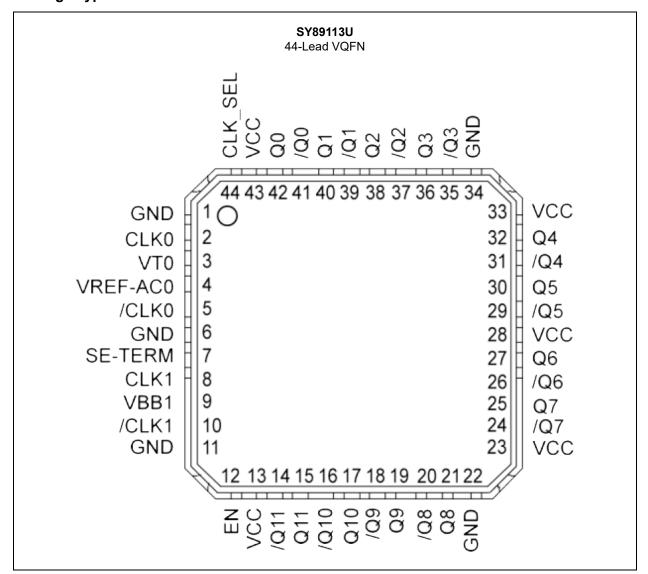

#### **Package Type**

# **Functional Block Diagram**

#### 1.0 ELECTRICAL CHARACTERISTICS

# Absolute Maximum Ratings<sup>†</sup>

| Supply Voltage (V <sub>CC</sub> )                                             |                         |

|-------------------------------------------------------------------------------|-------------------------|

| Input Voltage (Differential Input CLK0, CLK1)                                 | 0.5V to V <sub>CC</sub> |

| Current on Reference Voltage Outputs, source or sink current on VREF-AC0/VBB1 | ±2 mA                   |

| Termination Current, source or sink current on VT0                            | ±100 mA                 |

| Input Current, source or sink current on CLK0, /CLK0                          | ±50 mA                  |

# Operating Ratings<sup>††</sup>

Supply Voltage (V<sub>CC</sub>) ......+2.375V to +2.625V

TABLE 1-1: DC ELECTRICAL CHARACTERISTICS

| $T_A = -40$ °C to +85°C unless otherwise stated. (Note 1) |                      |                         |                         |                         |       |                               |  |

|-----------------------------------------------------------|----------------------|-------------------------|-------------------------|-------------------------|-------|-------------------------------|--|

| Parameter                                                 | Symbol               | Min.                    | Тур.                    | Max.                    | Units | Conditions                    |  |

| Power Supply                                              | V <sub>CC</sub>      | 2.375                   | _                       | 2.625                   | V     | _                             |  |

| Power Supply Current                                      | I <sub>CC</sub>      |                         | 240                     | 330                     | mA    | No load, max. V <sub>CC</sub> |  |

| Input Resistance (CLK0-to-VT)                             | R <sub>IN</sub>      | 45                      | 50                      | 55                      | Ω     | _                             |  |

| Differential Input Resistance (CLK0-to-/CLK0)             | R <sub>DIFF_IN</sub> | 90                      | 100                     | 110                     | Ω     | _                             |  |

| Input High Voltage (CLK0, /CLK0)                          |                      | 1.2                     | _                       | V <sub>CC</sub>         | ٧     | _                             |  |

| Input High Voltage                                        | $V_{IH}$             | 0.2                     | _                       | V <sub>CC</sub>         | V     | Note 2                        |  |

| (CLK1, /CLK1)                                             |                      | 1.2                     | _                       | 3.6                     | V     | Note 3                        |  |

| Input Low Voltage<br>(CLK0, /CLK0)                        |                      | 0.1                     | _                       | V <sub>CC</sub>         | V     | _                             |  |

| Input Low Voltage                                         | $V_{IL}$             | 0.2                     | _                       | _                       | V     | Note 2                        |  |

| (CLK1, /CLK1)                                             |                      | 0                       | _                       | _                       | V     | Note 3                        |  |

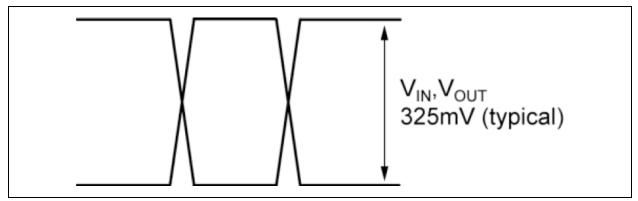

| Input Voltage Swing (CLK0, /CLK0)                         | V                    | 0.1                     | _                       | V <sub>CC</sub>         | V     | See Figure 8-1                |  |

| Input Voltage Swing (CLK1, /CLK1)                         | V <sub>IN</sub>      | 0.2                     | _                       | _                       | V     | See Figure 8-1                |  |

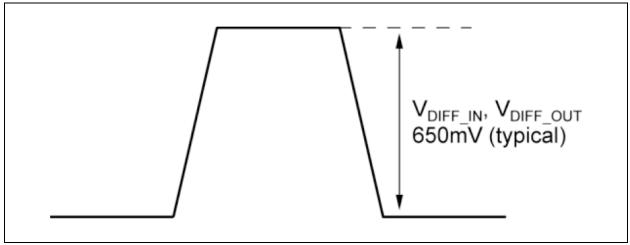

| Differential Input Voltage Swing  CLK0-to-/CLK0           | V                    | 0.2                     | _                       | _                       | ٧     | See Figure 8-2                |  |

| Differential Input Voltage Swing  CLK1-to-/CLK1           | V <sub>DIFF_IN</sub> | 0.4                     | _                       | _                       | ٧     | See Figure 8-2                |  |

| CLK0-to-VT0 (CLK0, /CLK0)                                 | V <sub>T0</sub>      | _                       | _                       | 1.28                    | V     | _                             |  |

| Output Reference Voltage                                  | V <sub>REF-AC0</sub> | V <sub>CC</sub> – 1.3   | V <sub>CC</sub> – 1.2   | V <sub>CC</sub> – 1.1   | V     | _                             |  |

| Output Neierence Voltage                                  | V <sub>BB1</sub>     | V <sub>CC</sub> – 1.525 | V <sub>CC</sub> – 1.425 | V <sub>CC</sub> – 1.325 | V     | _                             |  |

**Note 1:** The circuit is designed to meet the DC specifications shown in the above table after thermal equilibrium has been established.

<sup>&</sup>lt;sup>†</sup> **Notice:** Permanent device damage may occur if absolute maximum ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>\*\*\*</sup> Notice: The data sheet limits are not guaranteed if the device is operated beyond the operating ratings.

<sup>2:</sup> SE-TERM not connected.

<sup>3:</sup> Using single-ended TTL/CMOS input signals, SE-TERM connects to GND. See Figure 11-6.

#### TABLE 1-2: LVDS OUTPUTS DC ELECTRICAL CHARACTERISTICS

| $V_{CC}$ = +2.5V ±5%; $R_L$ = 100 $\Omega$ across the outputs pair; and $T_A$ = -40°C to +85°C, unless otherwise stated. (Note 1) |                       |       |      |       |       |                |  |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|------|-------|-------|----------------|--|

| Parameter                                                                                                                         | Symbol                | Min.  | Тур. | Max.  | Units | Conditions     |  |

| Output Voltage Swing (Q, /Q)                                                                                                      | V <sub>OUT</sub>      | 250   | 325  | _     | mV    | See Figure 8-1 |  |

| Differential Output Voltage Swing (Q, /Q)                                                                                         | V <sub>DIFF-OUT</sub> | 500   | 650  | _     | mV    | See Figure 8-2 |  |

| Output Common Mode Voltage                                                                                                        | $V_{OCM}$             | 1.125 | _    | 1.275 | V     | _              |  |

| Change in V <sub>OS</sub> between complementary output states                                                                     | ΔV <sub>OS</sub>      | _     | _    | 25    | mV    | _              |  |

**Note 1:** The circuit is designed to meet the DC specifications, shown in the above table, after thermal equilibrium has been established.

#### TABLE 1-3: LVTTL/CMOS DC ELECTRICAL CHARACTERISTICS

| $V_{CC}$ = +2.5V ±5%; $T_A$ = -40°C to +85°C, unless otherwise stated. (Note 1) |                 |      |      |      |       |            |  |

|---------------------------------------------------------------------------------|-----------------|------|------|------|-------|------------|--|

| Parameter                                                                       | Symbol          | Min. | Тур. | Max. | Units | Conditions |  |

| Input HIGH Voltage                                                              | V <sub>IH</sub> | 2.0  | _    | _    | V     | _          |  |

| Input LOW Voltage                                                               | $V_{IL}$        | _    | _    | 0.8  | V     | _          |  |

| Input HIGH Current                                                              | I <sub>IH</sub> | -125 | _    | 30   | μA    | _          |  |

| Input LOW Current                                                               | I <sub>IL</sub> | -300 | _    | _    | μA    | _          |  |

**Note 1:** The circuit is designed to meet the DC specifications, shown in the above table, after thermal equilibrium has been established.

TABLE 1-4: AC ELECTRICAL CHARACTERISTICS

| $V_{CC}$ = +2.5V ±5%; $R_L$ = 100 $\Omega$ across the outputs; and $T_A$ = -40°C to +85°C, unless otherwise stated. (Note 1) |                                 |      |      |      |                   |                                               |  |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|------|------|-------------------|-----------------------------------------------|--|

| Parameter                                                                                                                    | Symbol                          | Min. | Тур. | Max. | Units             | Conditions                                    |  |

| Maximum Operating Frequency                                                                                                  | f <sub>MAX</sub>                | 1    | _    | _    | GHz               | V <sub>OUT</sub> ≥ 200 mV                     |  |

| Propagation Delay, CLK0-to-Q                                                                                                 |                                 | 625  | 750  | 975  | ps                | V <sub>IN</sub> ≥ 100 mV                      |  |

| Propagation Delay, CLK1-to-Q                                                                                                 | t <sub>PD</sub>                 | 700  | 900  | 1200 | ps                | V <sub>IN</sub> ≥ 200 mV                      |  |

| Propagation Delay, CLK_SEL-to-Q                                                                                              |                                 | 500  | 700  | 900  | ps                | _                                             |  |

| Differential Propagation Delay<br>Temperature                                                                                | t <sub>PD</sub> Tempco          | _    | 90   | _    | fs/°C             | _                                             |  |

| Set-up Time, EN-to-CLK0                                                                                                      | 4                               | 100  | _    | _    | ps                | Note 2                                        |  |

| Set-up Time, EN-to-CLK1                                                                                                      | t <sub>S</sub>                  | 0    | _    | _    | ps                | Note 2                                        |  |

| Hold Time, CLK0-to-EN                                                                                                        | 4                               | 500  | _    | _    | ps                | Note 2                                        |  |

| Hold Time, CLK1-to-EN                                                                                                        | t <sub>H</sub>                  | 600  | _    | _    | ps                | Note 2                                        |  |

| Output-to-output Skew                                                                                                        |                                 | _    | _    | 25   | ps                | Note 3                                        |  |

| Part-to-part Skew CLK0                                                                                                       |                                 | _    | _    | 200  | ps                | Note 4                                        |  |

| Part-to-part Skew CLK1                                                                                                       | t                               | _    | _    | 250  | ps                | Note 4                                        |  |

| RMS Phase Jitter                                                                                                             | t <sub>SKEW</sub>               | _    | 130  | _    | fs                | Output = 622 MHz,                             |  |

| Adjacent Channel<br>Crosstalk-induced Jitter                                                                                 |                                 | _    | _    | 0.7  | ps <sub>RMS</sub> | Integration Range 12 kHz<br>– 20 MHz (Note 5) |  |

| Output Rise/Fall Time (20% to 80%)                                                                                           | t <sub>r</sub> , t <sub>f</sub> | 80   | 150  | 250  | ps                | At full output swing                          |  |

- **Note 1:** High-frequency AC-parameters are guaranteed by design and characterization.

- **2:** Set-up and hold times apply to synchronous applications that intend to enable/disable before the next clock cycle. For asynchronous applications, set-up and hold do not apply.

- 3: Output-to-output skew is measured between two different outputs under identical input transitions.

- **4:** Part-to-part skew is defined for two parts with identical power supply voltages at the same temperature and with no skew of the edges at the respective inputs.

- **5:** Crosstalk-induced jitter is defined as: the added jitter that results from signals applied to two adjacent channels. It is measured at the output while applying two similar, differential clock frequencies that are asynchronous with respect to each other at the inputs.

TABLE 1-5: TEMPERATURE SPECIFICATIONS

| Parameter                           | Symbol            | Min. | Тур. | Max. | Units | Conditions         |

|-------------------------------------|-------------------|------|------|------|-------|--------------------|

| Temperature Range                   |                   |      |      |      |       |                    |

| Operating Ambient Temperature       | T <sub>A</sub>    | -40  | _    | +85  | °C    | _                  |

| Lead Temperature                    | T <sub>LEAD</sub> | _    | +260 | _    | °C    | Soldering, 20 sec. |

| Storage Temperature                 | T <sub>S</sub>    | -65  | _    | +150 | °C    | _                  |

| Package Thermal Resistance (Note 1) |                   |      |      |      |       |                    |

| VQFN, Still Air                     | $\theta_{JA}$     |      | +24  | _    | °C/W  | _                  |

| VQFN, Junction-to-Board             | ΨJB               | _    | +8   | _    | °C/W  | _                  |

Note 1: Package thermal resistance assumes exposed pad is soldered (or equivalent) to the device's most negative potential on the PCB.  $\psi_{JB}$  and  $\theta_{JA}$  values are determined for a 4-layer board in still-air, unless otherwise stated.

# 2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

TABLE 2-1: PIN FUNCTION TABLE

| Pin Number            | Pin Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 6, 11, 22, 34      | GND,<br>Exposed<br>Pad | <b>Ground:</b> GND pins and exposed pad must both be connected to the most negative potential of chip the ground.                                                                                                                                                                                                                                                                                                                                                                                                 |

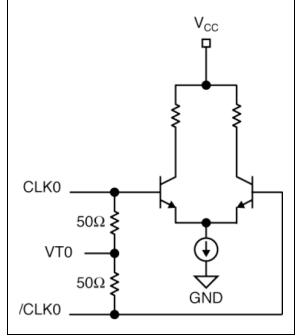

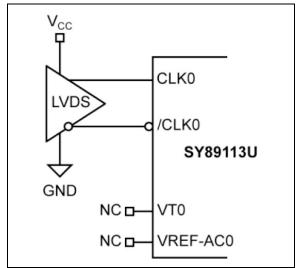

| 2, 5                  | CLK0,<br>/CLK0         | <b>Differential Inputs:</b> This input pair is a differential signal input to the device. Input accepts AC- or DC-coupled signals as small as 100 mV (200 mV <sub>PP</sub> ). Each pin of the pair internally terminates to a VT pin through $50\Omega$ . Note that this input defaults to an indeterminate state if left open. Please refer to Section 10.0, CLK0 Input Interface Applications for more details.                                                                                                 |

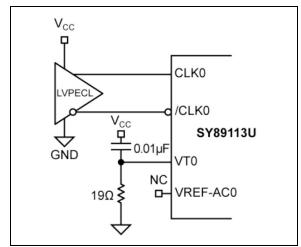

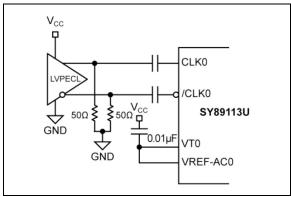

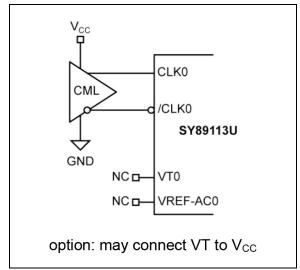

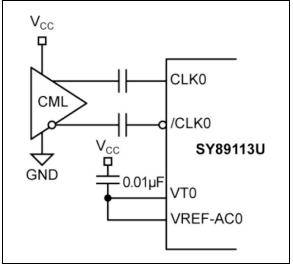

| 3                     | VT0                    | Input Termination Center-Tap: Each side of the differential input pair CLK0, /CLK0 terminates to the VT pin. The VT pin provides a center-tap to a termination network for maximum interface flexibility. See Section 10.0, CLK0 Input Interface Applications for more details. For DC-coupled CML or LVDS inputs, the VT pin is left floating.                                                                                                                                                                   |

| 4                     | VREF-AC0               | Reference Voltage: This output biases to VCC–1.2V. It is used when AC-coupling the input CLK0. For AC-coupled applications, connect VREF-AC0 to the VT0 pin and bypass with 0.01 µF low ESR capacitor to VCC. See Section 10.0, CLK0 Input Interface Applications for more details. Maximum sink/source current is ±1.5mA. Due to the limited drive capability, the VREF-AC0 pin is only intended to drive its respective input pin.                                                                              |

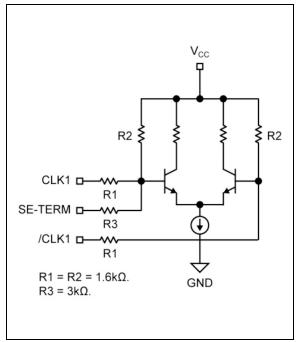

| 7                     | SE-TERM                | Input Termination Pin: When CLK1 is driven by a single-ended TTL/CMOS signal, tie this pin to GND. In all other modes, let this pin float. See Section 11.0, CLK1 Input Interface Applications for more details.                                                                                                                                                                                                                                                                                                  |

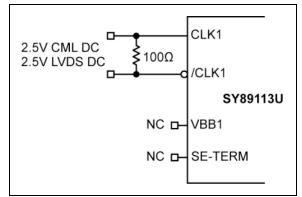

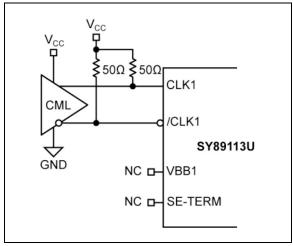

| 8, 10                 | CLK1,<br>/CLK1         | <b>Differential Inputs:</b> This input pair is a differential signal input to the device. This input accepts Any-Logic standard as small as 200 mV (400 mV <sub>PP</sub> ). Note that this input defaults to an indeterminate state if left open. Tie either the true or the complement input to ground while the other input is floating. This input can be used for single-ended signals (including TTL/CMOS signals from a 3.3V driver). See Section 11.0, CLK1 Input Interface Applications for more details. |

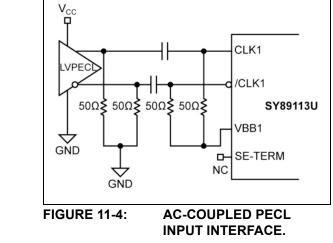

| 9                     | VBB1                   | Reference Voltage: This output biases to VCC–1.425V. VBB1 is designed to act as a switching reference for the CLK1 and /CLK1 inputs when configured in single-ended PECL input mode. VBB1 can be used for AC-coupling of CLK1, see Figure 11-4 for details. Maximum sink/source current is ±1.5mA. Due to the limited drive capability, the VBB1 pin is only intended to drive its respective input pin.                                                                                                          |

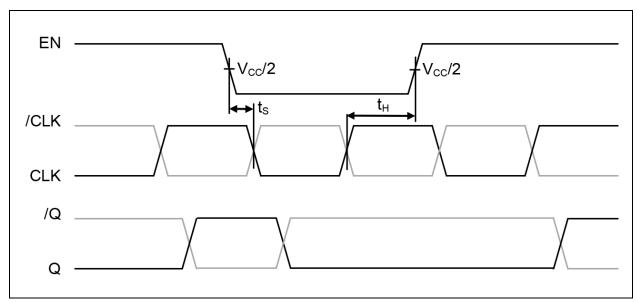

| 12                    | EN                     | Synchronous Output Enable: This single-ended, TTL/CMOS-compatible input functions as a synchronous output enable. The synchronous enable ensures that enable/disable will only occur when the outputs are in a logic LOW state. Note that this input is internally connected to a 25 k $\Omega$ pull-up resistor and will default to logic HIGH state (enable) if left open.                                                                                                                                      |

| 13, 23, 28, 33,<br>43 | VCC                    | <b>Positive Power Supply:</b> Bypass with 0.1 $\mu$ F    0.01 $\mu$ F low ESR capacitors and place as close to the VCC pins as possible.                                                                                                                                                                                                                                                                                                                                                                          |

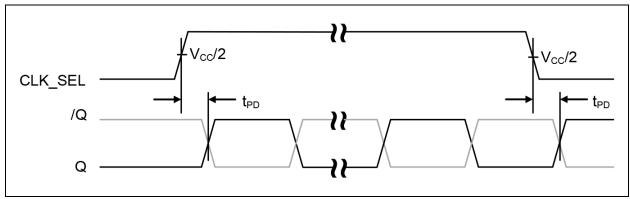

| 44                    | CLK_SEL                | <b>Multiplexer Inputs Selector:</b> This single-ended, TTL/CMOS-compatible input selects the inputs to the multiplexer. Note that this input is internally connected to a $25$ kΩ pull-up resistor and will default to logic HIGH state if open.                                                                                                                                                                                                                                                                  |

# SY89113U

TABLE 2-1: PIN FUNCTION TABLE (CONTINUED)

| Pin Number                                                                                                           | Pin Name                                                                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 42, 41<br>40, 39<br>38, 37<br>36, 35<br>32, 31<br>30, 29<br>27, 26<br>25, 24<br>21, 20<br>19, 18<br>17, 16<br>15, 14 | Q0, /Q0<br>Q1, /Q1<br>Q2, /Q2<br>Q3, /Q3<br>Q4, /Q4<br>Q5, /Q5<br>Q6, /Q6<br>Q7, /Q7<br>Q8, /Q8<br>Q9, /Q9<br>Q10, /Q10<br>Q11, /Q11 | <b>Differential LVDS Outputs:</b> These LVDS output pairs are the precision, low skew copies of the selected input. Please refer to Table 2-2 below for details. Unused output pairs should be terminated with 100 $\Omega$ across the pair. Each output is designed to drive 325 mV into 100 $\Omega$ . See Section 6.0, LVDS Output Interface Applications for more details. |

#### TABLE 2-2: TRUTH TABLE

| EN                                                                               | CLK_SEL | Q    | /Q    |  |  |  |

|----------------------------------------------------------------------------------|---------|------|-------|--|--|--|

| Н                                                                                | L       | CLK0 | /CLK0 |  |  |  |

| Н                                                                                | Н       | CLK1 | /CLK1 |  |  |  |

| L X L (Note 1) H (Note 1)                                                        |         |      |       |  |  |  |

| Note 1: Transition occurs on next negative transition of the non-inverted input. |         |      |       |  |  |  |

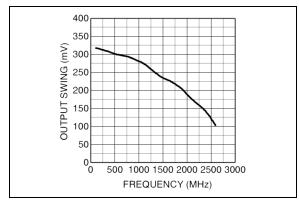

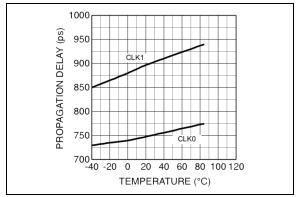

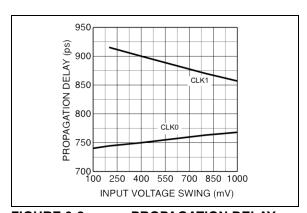

#### 3.0 TYPICAL PERFORMANCE CHARACTERISTICS

$V_{CC}$  = 2.5V; GND = 0V;  $V_{IN}$  = 400 mV;  $R_L$  = 100 $\Omega$  across the outputs; and  $T_A$  = 25°C, unless otherwise stated.

FIGURE 3-1: OUTPUT SWING VS. FREQUENCY.

FIGURE 3-3: PROPAGATION DELAY VS. TEMPERATURE.

FIGURE 3-2: PROPAGATION DELAY VS. INPUT VOLTAGE SWING.

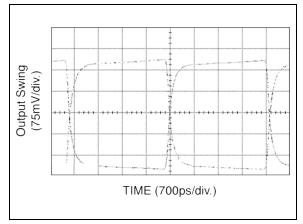

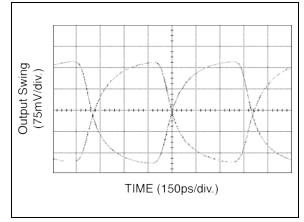

# 4.0 TYPICAL FUNCTIONAL CHARACTERISTICS

$V_{CC}$  = 2.5V; GND = 0V;  $V_{IN}$  = 400 mV;  $R_L$  = 100 $\Omega$  across the outputs; and  $T_A$  = 25°C, unless otherwise stated.

FIGURE 4-1: 200 MHZ OUTPUT.

FIGURE 4-2: 1 GHZ OUTPUT.

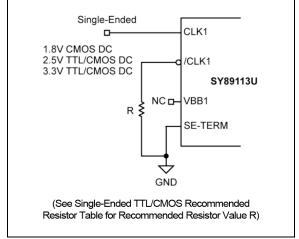

# 5.0 SINGLE-ENDED TTL/CMOS RECOMMENDED RESISTOR VALUE

The SY89113U can be driven by a TTL/CMOS input signal. See Figure 11-6. The resistor R, in Table 5-1 below, is calculated according to the following equation:

#### **EQUATION 5-1:**

$$R = 1.594 \times \left( \frac{1}{\left[ \frac{5.057 \times V_{CC}}{2 \times V_{CC} + V_{IH} + V_{IL}} \right] - 1} - 1 \right) \Omega$$

Equation 5-1 is used to determine the optimum value of R for best duty cycle.

TABLE 5-1: SINGLE-ENDED TTL/CMOS RECOMMENDED RESISTORS

| input Signal | Recommended R (Ω) |

|--------------|-------------------|

| 1.8V CMOS    | 261               |

| 2.5V CMOS    | 732               |

| 3.3V CMOS    | 1470              |

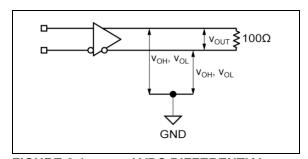

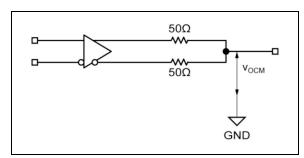

#### 6.0 LVDS OUTPUT INTERFACE APPLICATIONS

LVDS specifies a small swing of 325 mV typical on a nominal 1.2V common mode above ground. The common mode voltage has tight limits to permit large variations in ground between an LVDS driver and receiver. Also, change in common mode voltage, as a function of data input, is kept to a minimum to keep EMI low

FIGURE 6-1: LVDS DIFFERENTIAL MEASUREMENT.

FIGURE 6-2: LVDS COMMON MODE MEASUREMENT.

#### 7.0 TIMING DIAGRAMS

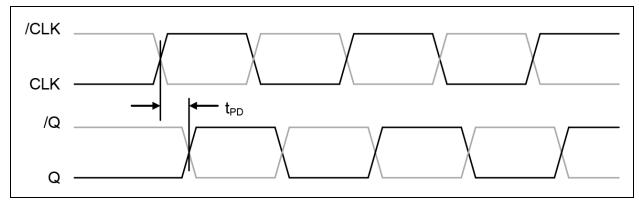

FIGURE 7-1: TIMING DIAGRAM: DIFFERENTIAL IN-TO-DIFFERENTIAL OUT.

FIGURE 7-2: TIMING DIAGRAM: CLK\_SEL-TO-DIFFERENTIAL OUT.

FIGURE 7-3: TIMING DIAGRAM: SETUP AND HOLD TIME EN-TO-DIFFERENTIAL IN.

# 8.0 SINGLE-ENDED AND DIFFERENTIAL SWINGS

FIGURE 8-1: SINGLE-ENDED VOLTAGE SWING CLK0.

FIGURE 8-2: DIFFERENTIAL VOLTAGE SWING CLK0.

# 9.0 INPUT AND OUTPUT STAGES

FIGURE 9-1: CLK1 DIFFERENTIAL INPUT BUFFER.

FIGURE 9-2: CLK0 DIFFERENTIAL INPUT STRUCTURE.

#### 10.0 CLK0 INPUT INTERFACE APPLICATIONS

FIGURE 10-1: DC-COUPLED LVPECL INPUT INTERFACE.

FIGURE 10-2: AC-COUPLED LVPECL INPUT INTERFACE.

FIGURE 10-3: DC-COUPLED CML INPUT INTERFACE.

FIGURE 10-4: AC-COUPLED CML INPUT INTERFACE.

FIGURE 10-5: DC-COUPLED LVDS INPUT INTERFACE.

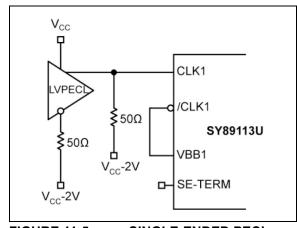

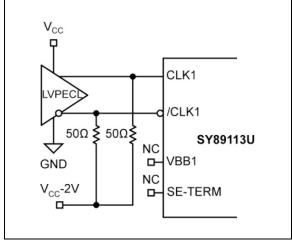

#### 11.0 CLK1 INPUT INTERFACE APPLICATIONS

FIGURE 11-1: DC-COUPLED CML, LVDS INPUT INTERFACE.

FIGURE 11-2: DC-COUPLED CML INPUT INTERFACE.

FIGURE 11-5: SINGLE-ENDED PECL INPUT INTERFACE.

FIGURE 11-3: DC-COUPLED PECL INPUT INTERFACE.

FIGURE 11-6: SINGLE-ENDED TTL/CMOS INPUT INTERFACE.

#### 12.0 PACKAGING INFORMATION

# 12.1 Package Marking Information

# Example\*

Legend: XX...X Product code or customer-specific information

W Week code

NNN Alphanumeric traceability code (week)

\* This package is Pb-free. The Pb-free JEDEC designator can be found on the outer packaging for this package.

Pin one index is identified by a dot

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. Package may or may not include

the corporate logo.

Underbar (\_) and/or Overbar (\_) symbol may not be to scale.

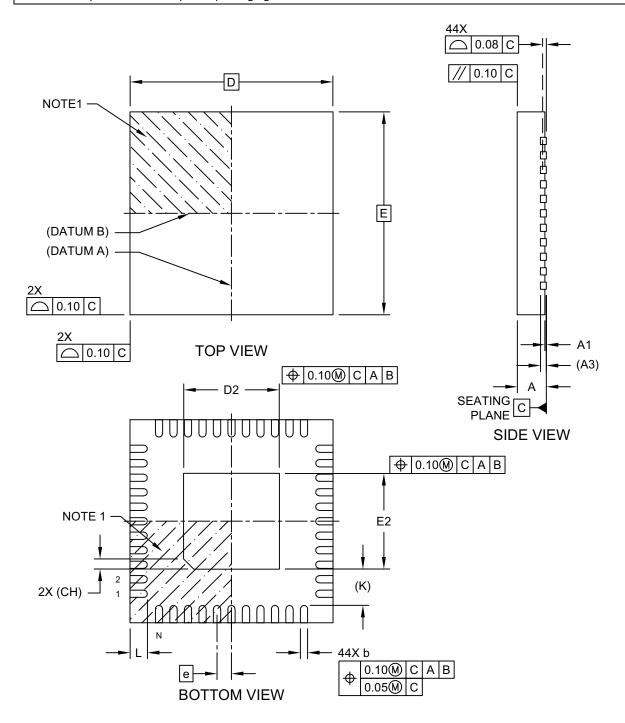

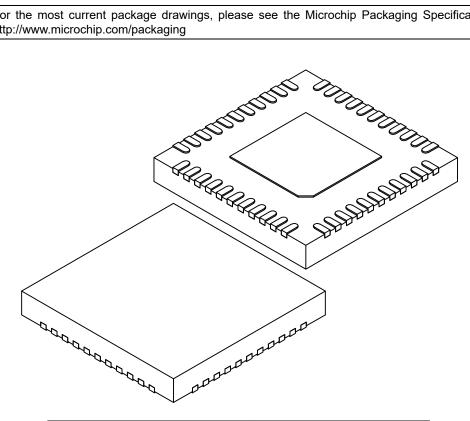

# 44-Lead 7 mm × 7 mm VQFN [QPA] Package Outline and Recommended Land Pattern

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-1291 Rev A Sheet 1 of 2

#### 44-Lead 7 mm × 7 mm VQFN [QPA] Package Outline and Recommended Land Pattern

For the most current package drawings, please see the Microchip Packaging Specification located at Note: http://www.microchip.com/packaging

|                            | MILLIMETERS      |          |          |      |  |

|----------------------------|------------------|----------|----------|------|--|

| Dimensior                  | Dimension Limits |          |          | MAX  |  |

| Number of Terminals        | N                |          | 44       |      |  |

| Pitch                      | е                |          | 0.50 BSC |      |  |

| Overall Height             | Α                | 0.80     | 0.90     | 1.00 |  |

| Standoff                   | A1               | 0.00     | 0.02     | 0.05 |  |

| Terminal Thickness         | A3               | 0.20 REF |          |      |  |

| Overall Length             | D                | 7.00 BSC |          |      |  |

| Exposed Pad Length         | D2               | 3.20     | 3.30     | 3.40 |  |

| Overall Width              | Е                |          | 7.00 BSC |      |  |

| Exposed Pad Width          | E2               | 3.20     | 3.30     | 3.40 |  |

| Terminal Width             | b                | 0.20     | 0.25     | 0.30 |  |

| Terminal Length            | L 0.50 0.60 0.70 |          |          | 0.70 |  |

| Terminal-to-Exposed-Pad    | K                | 0.20 REF |          |      |  |

| Exposed Pad Corner Chamfer | CH               |          | 0.35 REF |      |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-1291 Rev A Sheet 2 of 2

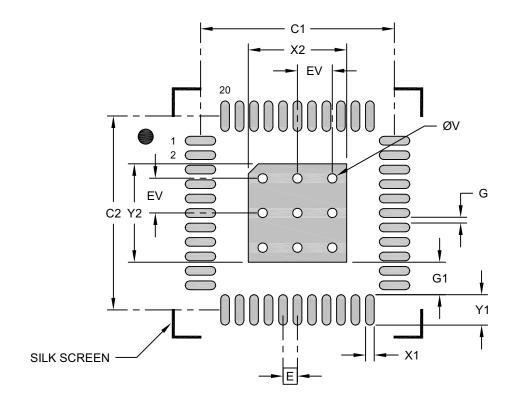

# 44-Lead 7 mm × 7 mm VQFN [QPA] Package Outline and Recommended Land Pattern

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                                  | MILLIMETERS |      |          |      |

|----------------------------------|-------------|------|----------|------|

| Dimension                        | MIN         | NOM  | MAX      |      |

| Contact Pitch                    | E           |      | 0.50 BSC |      |

| Center Pad Width                 | X2          |      |          | 3.40 |

| Center Pad Length                | Y2          |      |          | 3.40 |

| Contact Pad Spacing              | C1          |      | 6.70     |      |

| Contact Pad Spacing              | C2          |      | 6.70     |      |

| Contact Pad Width (Xnn)          | X1          |      |          | 0.30 |

| Contact Pad Length (Xnn)         | Y1          |      |          | 1.05 |

| Contact Pad to Center Pad (Xnn)  | G1          | 1.13 |          |      |

| Contact Pad to Contact Pad (Xnn) | G2          | 0.20 |          |      |

| Thermal Via Diameter             | V           |      | 0.33     | ·    |

| Thermal Via Pitch                | EV          |      | 1.20     |      |

#### Notes:

- 1. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-3291 Rev A

| S | Y | 8 | 9 | 1 | 1 | 3 | IJ |

|---|---|---|---|---|---|---|----|

| V |   | U | J |   |   | v | v  |

NOTES:

# APPENDIX A: REVISION HISTORY

# Revision A (February 2024)

- Converted Micrel data sheet for SY89113U to Microchip format as DS20006881A.

- Minor text changes throughout.

| S | Y | 8 | 9 | 1 | 1 | 3 | IJ |

|---|---|---|---|---|---|---|----|

| V |   | U | J |   |   | v | v  |

NOTES:

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

| PART NO.               | <u>X</u>                     | X    | <u>х</u> - <u>хх</u>                                                                                   |

|------------------------|------------------------------|------|--------------------------------------------------------------------------------------------------------|

| Device                 | Supply P<br>Voltage<br>Range | acka | nge Temperature Special<br>Range Processing                                                            |

| Device:                | SY89113                      | =    | 2.5V Low Jitter, Low Skew 1:12<br>LVDS Fanout Buffer with 2:1<br>Input MUX and Internal<br>Termination |

| Voltage<br>Option:     | U                            | =    | 2.5V                                                                                                   |

| Package:               | М                            | =    | 44-Lead VQFN                                                                                           |

| Temperature<br>Range:  | Υ                            | =    | –40°C to 85°C                                                                                          |

| Special<br>Processing: | <blank></blank>              | =    | 260/Tray<br>1,000/Reel                                                                                 |

#### Examples:

#### a) **SY89113UMY**

2.5V, 44-Lead VQFN, -40°C to 85°C, 260/Tray

#### b) **SY89113UMY-TR**

2.5V, 44-Lead VQFN,  $-40^{\circ}$ C to 85°C, 1,000/Reel

| S | Y | 8 | 9 | 1 | 1 | 3 | IJ |

|---|---|---|---|---|---|---|----|

| V |   | U | J |   |   | v | v  |

NOTES:

#### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable" Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">https://www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPlC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, TimeCesium, TimeHub, TimePictra, TimeProvider, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, EyeOpen, GridTime, IdealBridge, IGaT, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, MarginLink. maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mSiC, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, Power MOS IV, Power MOS 7, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, Turing, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2024, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

ISBN: 978-1-6683-4100-1

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

Atlanta Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983 Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou

Tel: 86-186-6233-1526 China - Wuhan

Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

**China - Xiamen** Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune

Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

**Korea - Daegu** Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

**Austria - Wels** Tel: 43-7242-2244-39

Fax: 43-7242-2244-393 **Denmark - Copenhagen**Tel: 45-4485-5910

Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-72400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

**Israel - Ra'anana** Tel: 972-9-744-7705

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

**Italy - Padova** Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

**Romania - Bucharest** Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820