# SY75608/612

# 8 or 12 Output Ultra-Low Additive Jitter PCIe 1/2/3/4/5/6 Clock Buffer

#### **Features**

- Eight (SY75608) and Twelve (SY75612) PCle 1.0, 2.0, 3.0, 4.0, 5.0, and 6.0 Compliant Outputs

- Ultra-Low Additive Jitter: 10 fs (PCIe Gen5)

- · Supports Frequencies of Up to 250 MHz

- · Transparent for Spread Spectrum

- Supports 1.8V ±10%, 2.5V ±10%, and 3.3V ±10%

Power Supplies

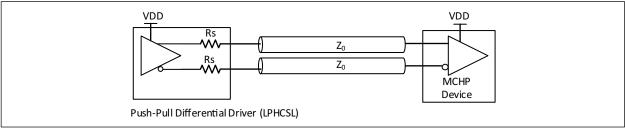

- Outputs Low Power HCSL with Embedded Termination Resistors

- Selectable Pin or I<sup>2</sup>C Bus Control

- Individual Glitch Free Output Enable (OExb) Control Pins

- Accepts DC-Coupled HCSL Input Signal and AC-Coupled PECL, LVDS, and CML Input Signals

- Extended Temperature Range: -40°C to +105°C

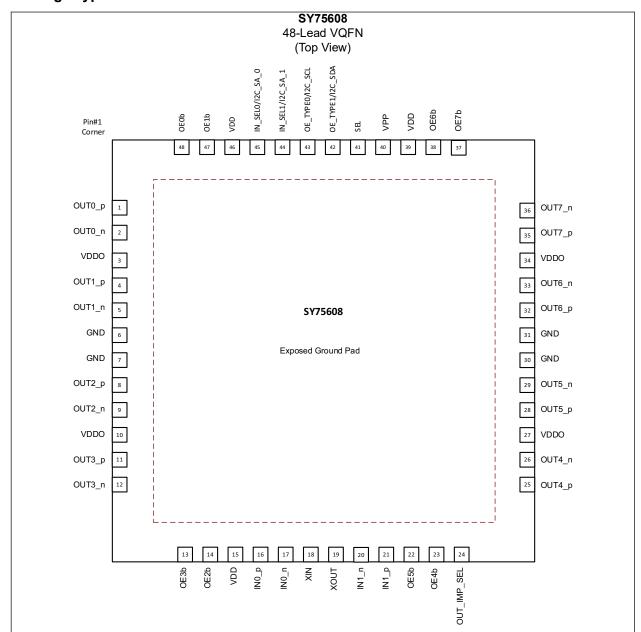

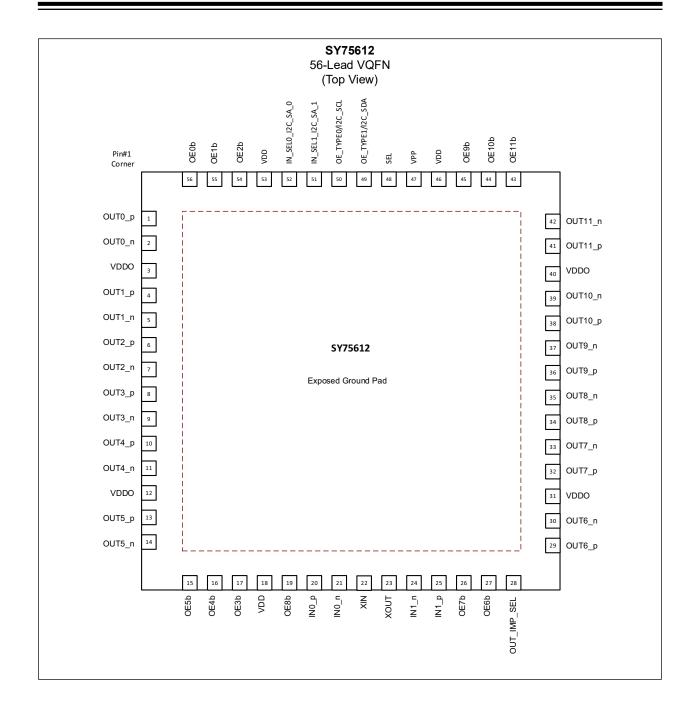

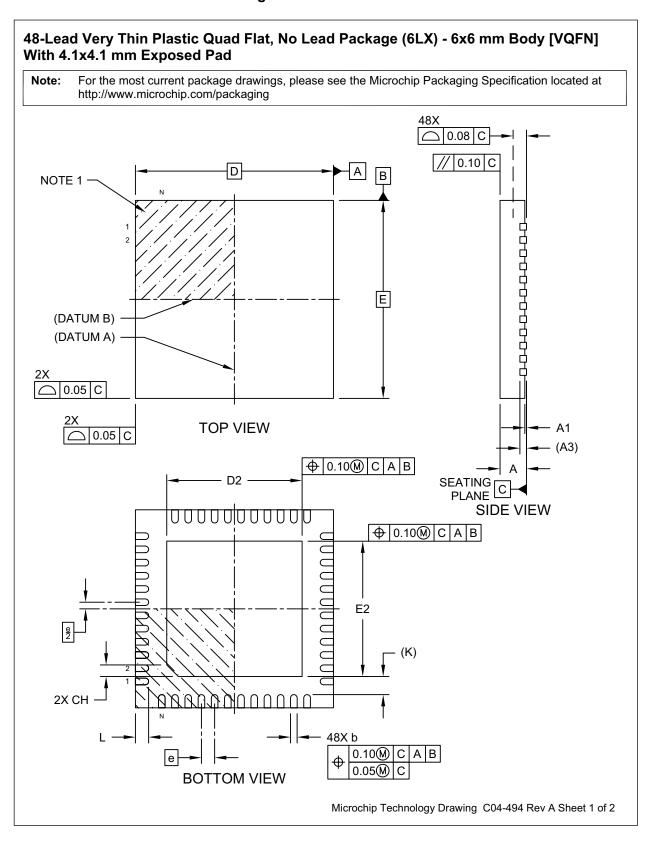

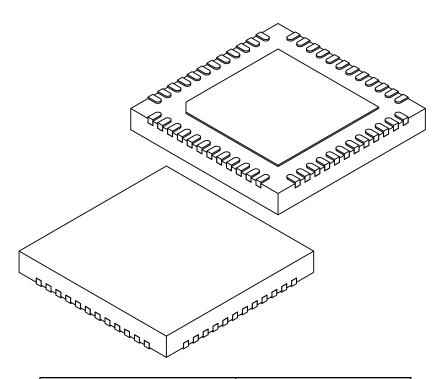

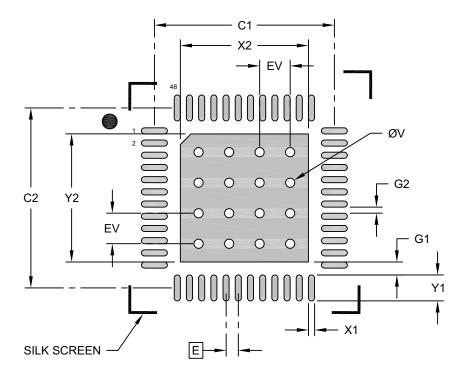

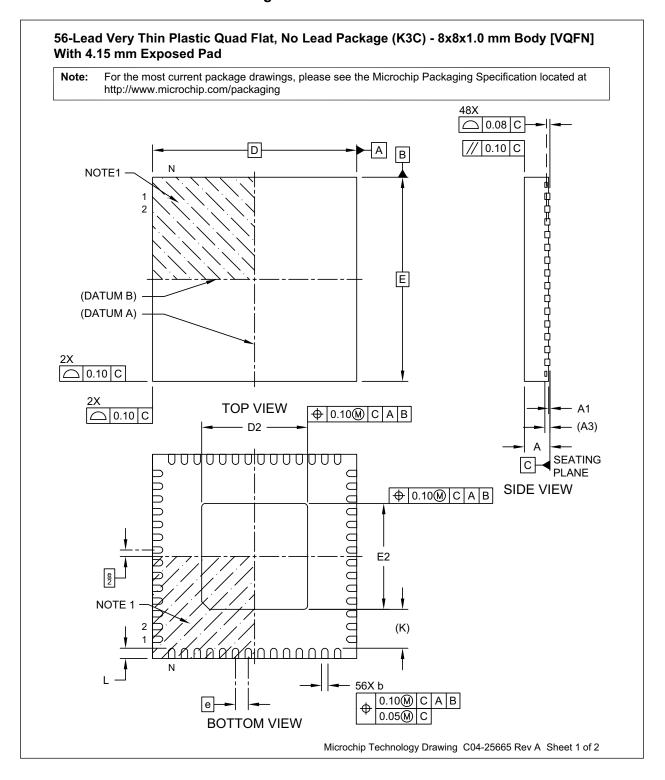

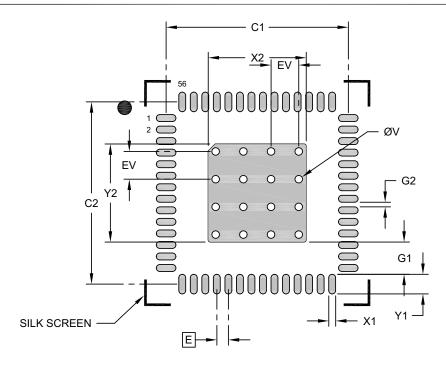

- 6 mm x 6 mm VQFN (SY75608) and 8 mm x 8 mm VQFN (SY75612) package

#### **Applications**

- · Cloud and High-Performance Computing

- · PCIe-Based SSD Drives

- · PCIe Switches

- Servers

#### **General Description**

The SY75608 and SY75612 are industry-leading PCle clock buffers with ultra-low additive jitter:

- 6 fs (PCle 6.0)

- 10 fs (PCle 5.0)

- 20 fs (PCIe 3.0/4.0)

- 52 fs in the 12 kHz to 20 MHz band

They can be used in all PCIe 1/2/3/4/5/6 common clock and SRIS applications.

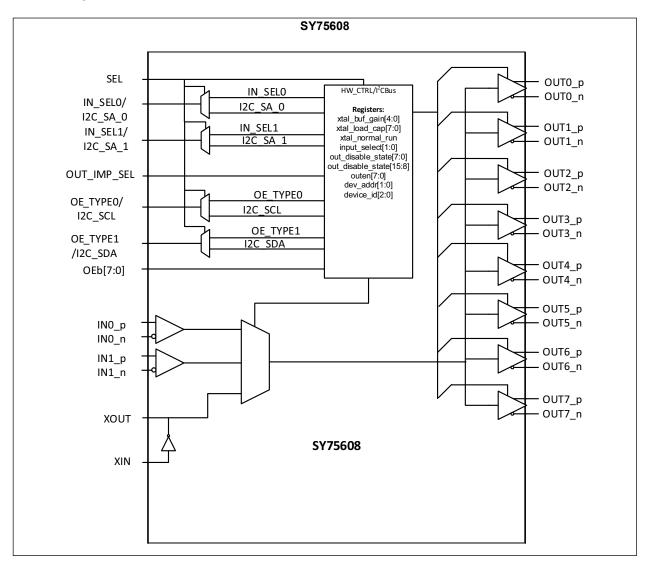

SY75608 and SY75612 are, respectively, eight and twelve output PCle clock buffers with glitch free per-output enable/disable control hardware pins. Devices are packaged in 6 mm x 6 mm VQFN (SY75608) and 8 mm x 8 mm VQFN (SY75612).

The SY75608/612 each have an embedded low-dropout regulator (LDO) for superior power noise supply rejection. They support 1.8V, 2.5V, and 3.3V supplies with a tolerance of  $\pm 10\%$ , which exceeds the  $\pm 9\%$  required by the PCIe Card Electro Mechanical Specification.

Both parts are available in the extended temperature range of –40°C to +105°C. Both parts are also available with customized configurations to meet the customer's needs. Please visit the ClockWorks Configurator to design your particular specifications.

## **Package Types**

## **Block Diagrams**

## 1.0 ELECTRICAL CHARACTERISTICS

# **Absolute Maximum Ratings †**

| Supply Voltage (V <sub>DD</sub> ) |    |

|-----------------------------------|----|

| Input Voltage (V <sub>IN</sub> )  |    |

| Input ESD Protection (HBM)        | 22 |

#### **Operating Ratings ‡**

| 1.8V Operating Voltage (V <sub>DD</sub> ) | +1.62V to +1.98V |

|-------------------------------------------|------------------|

| 2.5V Operating Voltage (V <sub>DD</sub> ) | +2.25V to +2.75V |

| 3.3V Operating Voltage (VDD)              | +2.97V to +3.63V |

**<sup>†</sup> Notice:** Permanent device damage may occur if absolute maximum ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum ratings conditions may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

| Electrical Characteristics: $V_{DD} = 3.3V \pm 10\%$ , $V_{DD} = 2.5V \pm 10\%$ , $V_{DD} = 1.8V \pm 10\%$ , $V_{A} = -40^{\circ}$ C to +105°C. |                           |                     |      |                     |       |                                                                                                                    |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------|------|---------------------|-------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Parameter                                                                                                                                       | Symbol                    | Min.                | Тур. | Max.                | Units | Conditions                                                                                                         |  |  |  |  |  |

| Current Consumption                                                                                                                             |                           |                     |      |                     |       |                                                                                                                    |  |  |  |  |  |

| Core Device Current                                                                                                                             | I <sub>DD</sub>           | _                   | 13   | 15                  | mA    | All outputs and XTAL disabled.<br>Both reference inputs fed with<br>100 MHz differential clock.                    |  |  |  |  |  |

| Core Device Current                                                                                                                             | I <sub>DD_XTAL</sub>      | 1                   | 13   | 15                  | mA    | All outputs disabled; XTAL circuit<br>enabled with 25 MHz Crystal<br>connected between XIN and XOUT                |  |  |  |  |  |

| Current Dissipation per LPHCSL Output (100Ω)                                                                                                    | I <sub>DD_HCSL_100Ω</sub> | _                   | 3.5  | 3.9                 | mA    | Note 1                                                                                                             |  |  |  |  |  |

| Current Dissipation per LPHCSL Output (85Ω)                                                                                                     | I <sub>DD_HCSL_85Ω</sub>  | _                   | 4.0  | 4.4                 | mA    | Note 1                                                                                                             |  |  |  |  |  |

| Power Supply Noise Rej                                                                                                                          | ection Ratio              |                     |      |                     |       |                                                                                                                    |  |  |  |  |  |

| Power Supply Noise<br>Rejection Ratio                                                                                                           | PSNRR <sub>HCSL</sub>     |                     | 70   |                     | dB    | 100 mV <sub>PP</sub> , 100 kHz noise injected to V <sub>DD</sub> . Clock Frequency 100 MHz, V <sub>DD</sub> = 3.3V |  |  |  |  |  |

| Input                                                                                                                                           |                           |                     |      |                     |       |                                                                                                                    |  |  |  |  |  |

| Input Slew Rate                                                                                                                                 | SR <sub>IN</sub>          | 0.6                 | _    | _                   | V/ns  | _                                                                                                                  |  |  |  |  |  |

| Differential Input High<br>Voltage                                                                                                              | V <sub>IH</sub>           | 0.15                | _    |                     | ٧     | _                                                                                                                  |  |  |  |  |  |

| Differential Input Low<br>Voltage                                                                                                               | V <sub>IL</sub>           | _                   | _    | -0.15               | V     | _                                                                                                                  |  |  |  |  |  |

| Input Voltage Swing                                                                                                                             | V <sub>ASWING</sub>       | 0.15                |      | _                   | V     | _                                                                                                                  |  |  |  |  |  |

| Absolute Crossing Point Voltage                                                                                                                 | V <sub>CROSS</sub>        | 0.25                | _    | 0.55                | V     | _                                                                                                                  |  |  |  |  |  |

| Variation of V <sub>CROSS</sub> Over All Edges                                                                                                  | V <sub>CROSSDELTA</sub>   | _                   | _    | 0.14                | ٧     | _                                                                                                                  |  |  |  |  |  |

| Voltage High for Control Inputs                                                                                                                 | V <sub>IH_OE</sub>        | 0.7*V <sub>DD</sub> | _    | _                   | V     | _                                                                                                                  |  |  |  |  |  |

| Voltage Low for Control Inputs                                                                                                                  | V <sub>IL_OE</sub>        | _                   | _    | 0.3*V <sub>DD</sub> | V     | _                                                                                                                  |  |  |  |  |  |

**<sup>‡</sup> Notice:** The data sheet limits are not guaranteed if the device is operated beyond the recommended operating conditions.

# **ELECTRICAL CHARACTERISTICS (CONTINUED)**

| Electrical Characteristics: $V_{DD} = 3.3V \pm 10\%$ , $V_{DD} = 2.5V \pm 10\%$ , $V_{DD} = 1.8V \pm 10\%$ , $V_{A} = -40$ °C to +105°C. |                    |      |      |      |       |                                                                                                           |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------|--|--|

| Parameter                                                                                                                                | Symbol             | Min. | Тур. | Max. | Units | Conditions                                                                                                |  |  |

| Input Leakage Current                                                                                                                    | I <sub>IL_IN</sub> | -5   | _    | 5    | μA    | $V_{IN} = V_{DD}, V_{IN} = GND$                                                                           |  |  |

| Input Capacitance                                                                                                                        | C <sub>IN</sub>    | _    | _    | 5    | pF    | _                                                                                                         |  |  |

| Input Leakage Current for OE Inputs                                                                                                      | I <sub>IL_OE</sub> | -5   | _    | 70   | μA    | V <sub>IN</sub> = V <sub>INMAX</sub> , V <sub>IN</sub> = GND; includes current due to pull down resistors |  |  |

| Single-Ended Input<br>Common Mode Voltage<br>(IN_p)                                                                                      | V <sub>SIC</sub>   | 0.25 | _    | 0.55 | V     | HCSL common mode                                                                                          |  |  |

| Single-Ended Input<br>Voltage Swing for IN_p                                                                                             | V <sub>SID</sub>   | 0.3  | _    | 1.45 |       | _                                                                                                         |  |  |

| Maximum Input Voltage                                                                                                                    | $V_{IN(MAX)}$      | _    | _    | 1.15 | V     | _                                                                                                         |  |  |

| Minimum Input Voltage                                                                                                                    | $V_{IN(MIN)}$      | -0.3 |      |      | V     | _                                                                                                         |  |  |

| Differential Input<br>Frequency                                                                                                          | f <sub>IN</sub>    | 0    | _    | 250  | MHz   | Note 2                                                                                                    |  |  |

| Single-Ended Input<br>Frequency                                                                                                          | f <sub>IN_SE</sub> | 0    | _    | 250  | MHz   | Note 2                                                                                                    |  |  |

| Input Duty Cycle                                                                                                                         | DC                 | 35   | _    | 65   | %     | _                                                                                                         |  |  |

| Input Multiplexer Isolation IN0_p/n to IN1_p/n and Vice Versa                                                                            | laa                | _    | -84  | _    | dBc   | f <sub>IN</sub> = 100 MHz, Note 2, Power on both inputs 0 dBm, f <sub>OFFSET</sub> >50 kHz                |  |  |

|                                                                                                                                          | 'SO                | _    | -82  | _    | ubc.  | f <sub>IN</sub> = 250 MHz, Note 2, Power on both inputs 0 dBm, f <sub>OFFSET</sub> >50 kHz                |  |  |

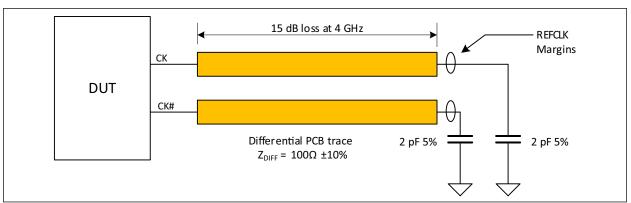

- Note 1: Tested with 100 MHz clock with outputs driving 4" long trace terminated with 2 pF Capacitors to ground.

- 2: Output Enable control (pin or register) is synchronous with the input clock and it takes four rising edges before output gets enabled or disabled. Hence the minimum input frequency is greater than 0 Hz. Once the outputs are enabled the input clock frequency can be reduced to 0 Hz.

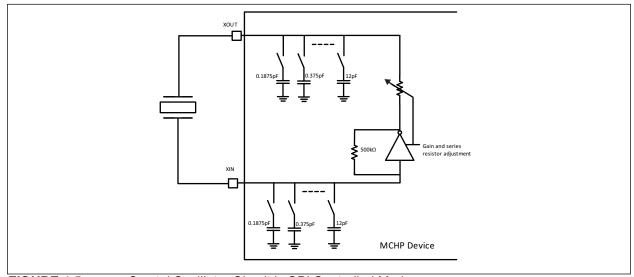

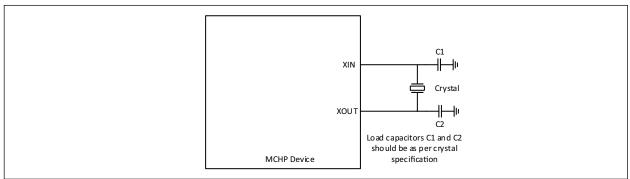

#### **CRYSTAL OSCILLATOR CHARACTERISTICS**

Electrical Characteristics:  $V_{DD}/V_{DDO} = 3.3V \pm 10\%$ ,  $V_{DD}/V_{DDO} = 2.5V \pm 10\%$ ,  $V_{DD}/V_{DDO} = 1.8V \pm 10\%$ ,  $V_{A} = -40^{\circ}$ C to  $\pm 105^{\circ}$ C.

| 10 + 105 C.                                                            |                |      |      |       |       |                                                                                                                                                   |

|------------------------------------------------------------------------|----------------|------|------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters                                                             | Symbol         | Min. | Тур. | Max.  | Units | Conditions                                                                                                                                        |

| Mode of Oscillation                                                    | _              | _    | _    | _     | _     | Fundamental                                                                                                                                       |

| Frequency                                                              | f              | 8    | _    | 160   | MHz   | High frequency crystal needs lower motion resistance. For example, the motion resistance for 156.25 MHz needs to be lower than $25\Omega$         |

| On-Chip Load<br>Capacitance in I <sup>2</sup> C Bus<br>Controlled Mode | C <sub>L</sub> | 0    | _    | 21.75 | pF    | The values are programmable. On the top of this, there are intrinsic pin capacitances and the capacitance of PCB trace connecting to the crystal. |

| On-Chip Load<br>Capacitance in Pin<br>Controlled Mode                  | _              | _    | 4    | _     | pF    | Fixed                                                                                                                                             |

| On-Chip Series Resistor in Pin Controlled Mode                         |                | _    | 150  | _     | Ω     | Fixed                                                                                                                                             |

| On-Chip Shunt Resistor                                                 | R              |      | 500  | _     | kΩ    | _                                                                                                                                                 |

# **CRYSTAL OSCILLATOR CHARACTERISTICS (CONTINUED)**

**Electrical Characteristics:**  $V_{DD}/V_{DDO} = 3.3V \pm 10\%$ ,  $V_{DD}/V_{DDO} = 2.5V \pm 10\%$ ,  $V_{DD}/V_{DDO} = 1.8V \pm 10\%$ ,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ .

| Parameters                              | Symbol          | Min. | Тур. | Max. | Units | Conditions                                                                                            |

|-----------------------------------------|-----------------|------|------|------|-------|-------------------------------------------------------------------------------------------------------|

| Frequency in Overdrive<br>Mode (Note 1) | f <sub>OV</sub> | 8    | _    | 160  | MHz   | Functional, but may not meet AC parameters. Minimum depends on AC coupling Capacitor (0.1 µF assumed) |

| Frequency in Bypass<br>Mode (Note 2)    | f <sub>BP</sub> | 0    | _    | 250  | MHz   | Functional, but may not meet AC parameters                                                            |

Note 1: Maximum input level is 2V.

2: Maximum output level is V<sub>DD</sub>.

## **OUTPUT ELECTRICAL CHARACTERISTICS**

**Electrical Characteristics:**  $V_{DD} = 3.3V \pm 10\%$ ,  $V_{DD} = 2.5V \pm 10\%$ ,  $V_{DD} = 1.8V \pm 10\%$ ,  $V_{A} = -40$ °C to +105°C, unless noted.  $C_{LOAD} = 2$  pF.

| noted. C <sub>LOAD</sub> = 2 pr.                               |                          |      |         |      |                  |                                                                    |  |  |  |

|----------------------------------------------------------------|--------------------------|------|---------|------|------------------|--------------------------------------------------------------------|--|--|--|

| Parameters                                                     | Symbol                   | Min. | Тур.    | Max. | Units            | Conditions                                                         |  |  |  |

| Rising Edge Rate                                               | _                        | 1    | 2.5     | 4    | V/ns             | Note 1, Note 2                                                     |  |  |  |

| Falling Edge Rate                                              | _                        | 1    | 2.5     | 4    | V/ns             | Note 1, Note 2                                                     |  |  |  |

| Differential Output High<br>Voltage                            | V <sub>OH</sub>          | 0.6  | _       | 0.9  | V                | Note 1                                                             |  |  |  |

| Differential Output Low<br>Voltage                             | V <sub>OL</sub>          | -0.9 | _       | -0.6 | V                | Note 1                                                             |  |  |  |

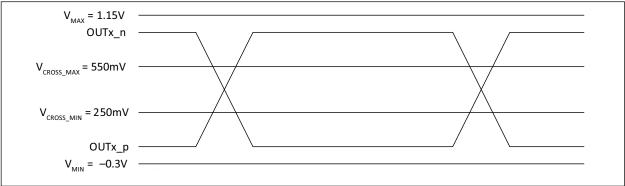

| Absolute Crossing<br>Voltage                                   | V <sub>CROSS</sub>       | 0.25 | _       | 0.55 | V                | Note 3, Note 4, Note 5                                             |  |  |  |

| Variation of V <sub>CROSS</sub> Over<br>All Rising Clock Edges | V <sub>CROSS_DELTA</sub> | _    | _       | 0.14 | V                | Note 3, Note 4, Note 6                                             |  |  |  |

| Ring Back Voltage<br>Margin                                    | V <sub>RB</sub>          | -0.1 | _       | 0.1  | V                | Note 1, Note 7                                                     |  |  |  |

| Time before V <sub>RB</sub> is Allowed                         | t <sub>STABLE</sub>      | 500  | _       | _    | ps               | Note 1, Note 7                                                     |  |  |  |

| Cycle-to-Cycle Additive<br>Jitter                              | t <sub>OCJITTER</sub>    | _    | 6.5     | 8.1  | ps <sub>PP</sub> | Note 1                                                             |  |  |  |

| Absolute Maximum Output Voltage                                | V <sub>MAX</sub>         | _    | _       | 1.15 | V                | Note 3, Note 8                                                     |  |  |  |

| Absolute Minimum<br>Output Voltage                             | V <sub>MIN</sub>         | -0.3 | _       | _    | V                | Note 3, Note 9                                                     |  |  |  |

| Output Duty Cycle                                              | ODC                      | 48   | 50      | 52   | %                | When input has 50% duty cycle and V <sub>IN</sub> ≥ 200 mV, Note 1 |  |  |  |

| Rising-to-Falling Edge<br>Matching                             | _                        | _    | _       | 15   | %                | Note 3, Note 10                                                    |  |  |  |

| Clock Source DC<br>Impedance (OUTx_p)                          | Z <sub>C-DC_OUT_p</sub>  | _    | 50/42.5 | _    | Ω                | OUT_IMP_SEL = low/high, Note 3, Note 11                            |  |  |  |

| Clock Source DC<br>Impedance (OUTx_n)                          | Z <sub>C-DC_OUT_n</sub>  | _    | 50/42.5 | _    | Ω                | OUT_IMP_SEL = low/high, Note 3, Note 11                            |  |  |  |

| Output Frequency                                               | f <sub>MAX</sub>         | 0    | _       | 250  | MHz              | _                                                                  |  |  |  |

| Output-to-Output Skew                                          | t <sub>oosk</sub>        | _    | 14      | 30   | ps               | _                                                                  |  |  |  |

# **OUTPUT ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Characteristics:**  $V_{DD}$  = 3.3V ±10%,  $V_{DD}$  = 2.5V ±10%,  $V_{DD}$  = 1.8V ±10%,  $T_A$  = -40°C to +105°C, unless noted.  $C_{LOAD}$  = 2 pF.

| Parameters                      | Symbol             | Min. | Тур. | Max. | Units  | Conditions |

|---------------------------------|--------------------|------|------|------|--------|------------|

| Device-to-Device Output<br>Skew | t <sub>DOOSK</sub> | _    | _    | 0.6  | ps     | _          |

| Input-to-Output Delay           | t <sub>IOD</sub>   | 1    | 1.4  | 2    | ns     | _          |

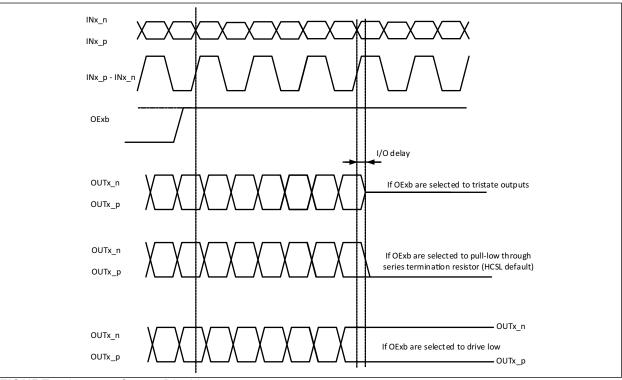

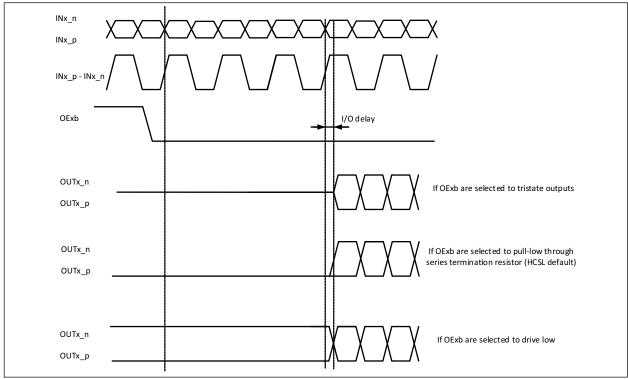

| Output Enable Time              | t <sub>EN</sub>    | _    | _    | 5    | cycles | Note 12    |

| Output Disable Time             | t <sub>DIS</sub>   | _    | _    | 6    | cycles | Note 12    |

- Note 1: Measurement taken from differential waveform.

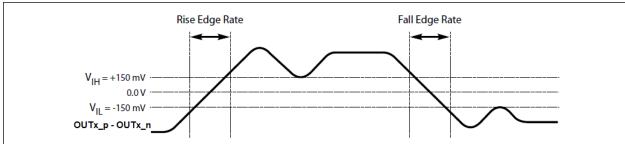

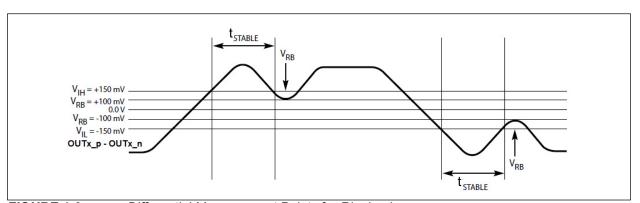

- 2: Measured from -150 mV to +150 mV on the differential waveform (derived from OUTx\_p to OUTx\_n). The signal must be monotonic through the measurement region for rise and fall time. The 300 mV measurement window is centered on the differential zero crossing. See Figure 1-5.

- 3: Measurement taken from single ended waveform.

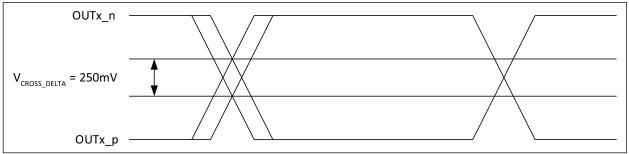

- **4:** Measured at crossing point where the instantaneous voltage value of the rising edge of OUTx\_p equals the falling edge of OUTx n. See Figure 1-1.

- 5: Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all crossing points for this measurement. See Figure 1-1.

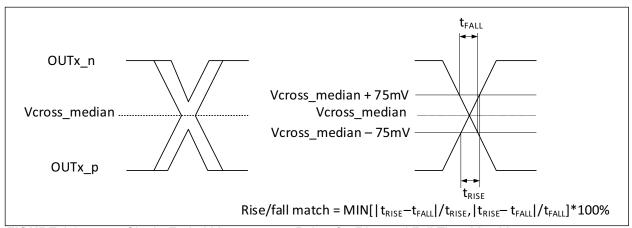

- **6:** Defined as the total variation of all crossing voltages of Rising OUTx\_p and Falling OUTx\_n. This is the maximum allowed variance in V<sub>CROSS</sub> for any particular system. See Figure 1-2.

- 7: t<sub>STABLE</sub> is the time the differential clock must maintain a minimum ±150 mV differential voltage after rising/falling edges before it is allowed to droop back into the V<sub>RB</sub> ±100 mV differential range. See Figure 1-6.

- 8: Defined as the maximum instantaneous voltage including overshoot. See Figure 1-1.

- 9: Defined as the minimum instantaneous voltage including undershoot. See Figure 1-1.

- 10: Matching applies to rising edge rate for OUTx\_p and falling edge rate for OUTx\_n. It is measured using a ±75 mV window centered on the median cross point where OUTx\_p rising meets OUTx\_n falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The Rise Edge Rate of OUTx\_p should be compared to the Fall Edge Rate of OUTx\_n; the maximum allowed difference should not exceed 20% of the slowest edge rate. See Figure 1-3.

- 11: System board compliance measurements must use the test load card described in Figure 1-7. OUTx\_p and OUTx\_n are to be measured at the load capacitors C<sub>LOAD</sub>. Single-ended probes must be used for measurements requiring single-ended measurements. Either single-ended probes with math or differential probe can be used for differential measurements. Test load C<sub>LOAD</sub> = 2 pF.

- 12: Output Enable control (pin or register) is synchronous with the input clock and it takes four rising edges before output gets enabled or disabled. Hence the minimum input frequency is greater than 0 Hz. Once the outputs are enabled the input clock frequency can be reduced to 0 Hz.

#### JITTER AND PHASE NOISE

| Parameters                                                       | Symbol                      | Min. | Тур. | Max. | Units             | Conditions     |

|------------------------------------------------------------------|-----------------------------|------|------|------|-------------------|----------------|

| Peak-to-Peak Additive<br>Jitter                                  | A <sub>JRMS_PP</sub>        | _    | 4    | 5.1  | ps                | Note 1, Note 2 |

| Additive Jitter per PCIe<br>1.0 (1.5 MHz to 22 MHz)              | tjPCle_1.0                  | _    | 0.7  | 0.9  | ps <sub>RMS</sub> | Note 1, Note 2 |

| Additive Jitter per PCIe<br>2.0 High Band (1.5 MHz<br>to 50 MHz) | t <sub>jPCle_2.0_high</sub> | _    | 79   | 100  | fs <sub>RMS</sub> | Note 1, Note 2 |

| Additive Jitter per PCIe<br>2.0 Low Band (10 kHz to<br>1.5 MHz)  | tjPCle_2.0_low              | _    | 16   | 21   | fs <sub>RMS</sub> | Note 1, Note 2 |

| Additive Jitter per PCIe<br>2.0 Mid Band (5 MHz to<br>16 MHz)    | tjPCle_2.0_mid              | _    | 62   | 79   | fs <sub>RMS</sub> | Note 1, Note 2 |

# **JITTER AND PHASE NOISE (CONTINUED)**

| Parameters                                                                              | Symbol                  | Min. | Тур. | Max. | Units             | Conditions                    |

|-----------------------------------------------------------------------------------------|-------------------------|------|------|------|-------------------|-------------------------------|

| Additive Jitter per PCIe<br>3.0 (PLL_BW = 2 MHz to<br>5 MHz, CDR = 10 MHz)              | t <sub>j</sub> PCle_3.0 | _    | 20   | 25   | fs <sub>RMS</sub> | Note 1, Note 2                |

| Additive Jitter per PCIe<br>4.0 (PLL_BW = 2 MHz to<br>5 MHz, CDR = 10 MHz)              | t <sub>jPCle_4.0</sub>  | _    | 20   | 25   | fs <sub>RMS</sub> | Note 1, Note 2                |

| Additive Jitter per PCIe<br>5.0 (PLL_BW = 0.5 MHz<br>to 1.8 MHz, CDR for 32<br>GT/s CC) | tjPCle_5.0              | _    | 8.2  | 10   | fs <sub>RMS</sub> | Note 2, Note 3                |

| Additive Jitter per PCIe<br>6.0 (PLL_BW = 0.5 MHz<br>to 1.0 MHz, CDR for 64<br>GT/s CC) | tjPCle_6.0              | _    | 5.2  | 6.2  | fs <sub>RMS</sub> | Note 2, Note 3                |

| Additive jitter per Intel QPI 9.6 Gbps                                                  | t <sub>jQPI</sub>       | _    | 35   | 45   | fs <sub>RMS</sub> | Note 1, Note 2                |

| Additive RMS Jitter in                                                                  | t                       |      | 53   | 67   | fs <sub>RMS</sub> | Note 1, Note 2, 100 MHz Clock |

| 1 MHz to 20 MHz Band                                                                    | t <sub>j_1M_20M</sub>   | _    | 41   | 56   | fs <sub>RMS</sub> | Note 1, Note 2, 133 MHz Clock |

| Additive RMS Jitter in                                                                  | t. 401 001              | _    | 51   | 64   | fs <sub>RMS</sub> | Note 1, Note 2, 100 MHz Clock |

| 12 kHz to 20 MHz Band                                                                   | t <sub>j_12k_20M</sub>  | _    | 39   | 54   | fs <sub>RMS</sub> | Note 1, Note 2, 133 MHz Clock |

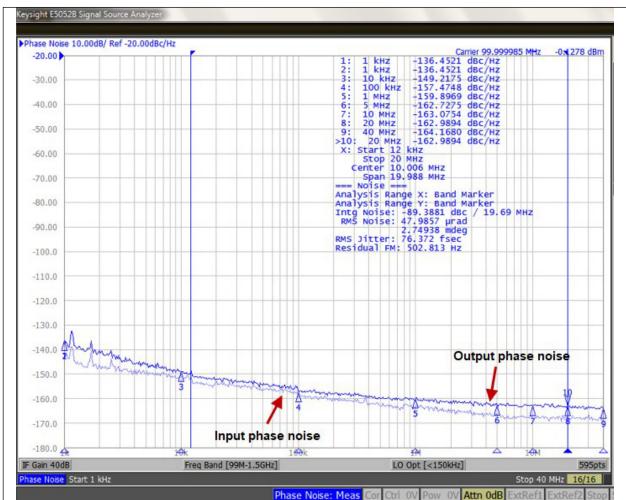

| Noise Floor                                                                             | N <sub>F</sub>          | _    | -165 | -163 | dBc/Hz            | Note 1, Note 2, 100 MHz Clock |

| TAOISC F IOOI                                                                           | INF                     | _    | -165 | -162 | dBc/Hz            | Note 1, Note 2, 133 MHz Clock |

- Note 1: Measured into AC test load as per Figure 1-7.

- 2: Measured from differential crossing point to differential crossing point.

- 3: Measured with  $50\Omega$  termination in instrument without a test load.

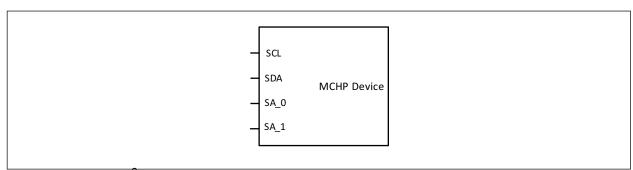

# I<sup>2</sup>C BUS ELECTRICAL CHARACTERISTICS

| Parameter                                        | Symbol              | Min. | Тур. | Max.                | Units               | Conditions                                       |

|--------------------------------------------------|---------------------|------|------|---------------------|---------------------|--------------------------------------------------|

| Nominal Bus Voltage                              | V <sub>DD_I2C</sub> | 1.62 | _    | 5.5                 | V                   | Note 1                                           |

| Input Low Voltage                                | V <sub>IL</sub>     | _    | _    | 0.6                 | V                   | _                                                |

| Input High Voltage                               | V <sub>IH</sub>     | 1.5  | _    | V <sub>DD_I2C</sub> | V                   | _                                                |

| Output Low Voltage                               | V <sub>OL</sub>     | _    | _    | 0.4                 | V                   | At I <sub>PULLUP,MAX</sub>                       |

| Input Leakage Current                            | I <sub>LEAK</sub>   | _    | _    | ±10                 | μA                  | _                                                |

| Current Sinking at V <sub>OL,MAX</sub>           | I <sub>PULLUP</sub> | 4    | _    | _                   | mA                  | _                                                |

| Pin Capacitive Load                              | C <sub>L</sub>      | _    | _    | 1                   | pF                  | _                                                |

| Signal Noise Immunity from 10 MHz to 100 MHz     | V <sub>NOISE</sub>  | 300  | _    | _                   | ${\sf mV}_{\sf PP}$ | _                                                |

| Noise Spike Suppression<br>Time                  | t <sub>SPIKE</sub>  | 0    | _    | 50                  | ns                  | Note 3                                           |

| I <sup>2</sup> C Bus Operating<br>Frequency      | f <sub>I2C</sub>    | 0    | _    | 400                 | kHz                 | _                                                |

| Bus Free Time Between Stop and Start Condition   | t <sub>BUF</sub>    | 1.3  |      |                     | μs                  | _                                                |

| Hold Time After<br>(Repeated) Start<br>Condition | t <sub>HD:STA</sub> | 0.6  | _    | _                   | μs                  | After this period, the first clock is generated. |

# I<sup>2</sup>C BUS ELECTRICAL CHARACTERISTICS (CONTINUED)

| Parameter                              | Symbol              | Min.           | Тур. | Max. | Units | Conditions |

|----------------------------------------|---------------------|----------------|------|------|-------|------------|

| Repeated Start Condition<br>Setup Time | t <sub>SU:STA</sub> | 0.6            | _    | _    | μs    | _          |

| Stop Condition Setup<br>Time           | t <sub>SU:STO</sub> | 0.6            | _    | _    | μs    | _          |

| Data Hold Time                         | t <sub>HD:DAT</sub> | 0              | _    | 0.9  | μs    | Note 4     |

| Data Setup Time                        | t <sub>SU:DAT</sub> | 100            | _    |      | ns    | _          |

| Clock Low Period                       | $t_{LOW}$           | 1.3            |      |      | μs    | _          |

| Clock High Period                      | t <sub>HIGH</sub>   | 0.6            | _    |      | μs    | _          |

| Clock/Data Fall Time                   | t <sub>F</sub>      | 20 +<br>0.1*Cb | _    | 250  | ns    | Note 2     |

| Clock/Data Rise Time                   | t <sub>R</sub>      | 20 +<br>0.1*Cb | _    | 250  | ns    | Note 2     |

- **Note 1:** 3V to 5V ±10%.

- 2: Rise and fall time is defined as follows:  $t_R = (V_{IL,MAX} 0.15)$  to  $(V_{IH,MIN} + 0.15)$ ;  $t_F = (V_{IH,MIN} 0.15)$  to  $(V_{IL,MAX} + 0.15)$

- 3: Devices must provide a means to reject noise spikes of a duration up to the maximum specified value.

- **4:** The maximum hold time has to be less than the maximum data valid or data valid acknowledge time as per Table 10, note [4] of I<sup>2</sup>C bus Rev. 6 specification.

#### **TEMPERATURE SPECIFICATIONS**

| Parameters                                                         | Sym.            | Min. | Тур. | Max. | Units | Conditions      |

|--------------------------------------------------------------------|-----------------|------|------|------|-------|-----------------|

| Temperature Ranges                                                 |                 |      |      |      |       |                 |

| Ambient Operating Temperature Range                                | T <sub>A</sub>  | -40  | _    | +105 | °C    | _               |

| Storage Temperature Range                                          | T <sub>S</sub>  | -65  | _    | +150 | °C    | _               |

| Package Thermal Resistances                                        |                 |      |      |      |       |                 |

| long stiens to Ameliant Theorem                                    |                 | _    | 29   | _    | °C/W  | Still-Air       |

| Junction to Ambient Thermal Resistance 6x6 VQFN-48Ld               | $\Theta_{JA}$   | _    | 24   | _    | °C/W  | 1 m/s airflow   |

| Tresistance one varive-rold                                        |                 | _    | 22   | _    | °C/W  | 2.5 m/s airflow |

| Junction to Board Thermal Resistance 6x6 VQFN-48Ld                 | $\Theta_{JB}$   | _    | 8    | _    | °C/W  | _               |

| Junction to Case Thermal Resistance<br>6x6 VQFN-48Ld               | θ <sub>JC</sub> | _    | 18   | _    | °C/W  | _               |

| Thermal Characterization, Junction to Top of Package 6x6 VQFN-48Ld | $\Psi_{JB}$     | _    | 1    | _    | °C/W  | Still-Air       |

|                                                                    |                 | _    | 28   | _    | °C/W  | Still-Air       |

| Junction to Ambient Thermal Resistance 8x8 VQFN-56Ld               | $\Theta_{JA}$   | _    | 23   | _    | °C/W  | 1 m/s airflow   |

| Tresistance one vol 14-50Eu                                        |                 | _    | 22   | _    | °C/W  | 2.5 m/s airflow |

| Junction to Board Thermal Resistance<br>8x8 VQFN-56Ld              | $\Theta_{JB}$   | _    | 8    | _    | °C/W  | _               |

| Junction to Case Thermal Resistance<br>8x8 VQFN-56Ld               | θ <sub>JC</sub> | _    | 14   | _    | °C/W  | _               |

| Thermal Characterization, Junction to Top of Package 8x8 VQFN-56Ld | $\Psi_{JB}$     | _    | 1    | _    | °C/W  | Still-Air       |

FIGURE 1-1: Single-Ended Measurement Points for Absolute Cross Point and Swing.

FIGURE 1-2: Single-Ended Measurement Points for Delta Cross Point.

FIGURE 1-3: Single-Ended Measurement Points for Rise and Fall Time Matching.

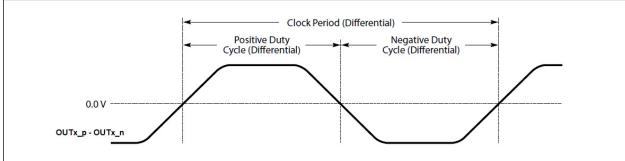

FIGURE 1-4: Differential Measurement Points for Duty Cycle and Period.

FIGURE 1-5: Differential Measurement Points for Rise and Fall Time.

FIGURE 1-6: Differential Measurement Points for Ringback.

FIGURE 1-7: PCIe Test Load.

#### 2.0 TYPICAL OPERATING CHARACTERISTICS

FIGURE 2-1: Typical Expected Phase Noise.

## 3.0 PIN DESCRIPTIONS

All device inputs and outputs are LPHCSL unless described otherwise. The Type column uses the following symbols:

- I: Input

- IPU: Input with 100  $k\Omega$  internal pull-up resistor

- IPD: Input with 100  $k\Omega$  internal pull-down resistor

- O: Output

- I/OOD: Input/Open-Drain Output

- NC: No ConnectP: Power Supply

The descriptions of the pins are listed in Table 3-1 and Table 3-2.

TABLE 3-1: SY75608 PIN FUNCTION TABLE

| Pin Number | Pin Name             | Pin Type |                                                                                | De                                                                  | scription                                                                                                                    |  |

|------------|----------------------|----------|--------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| 16         | IN0_p                |          | Differential/Sin                                                               | gle Ended Refer                                                     | ences 0 and 1                                                                                                                |  |

| 17         | IN0_n                |          |                                                                                |                                                                     | EO MUL                                                                                                                       |  |

| 21         | IN1_p                |          | Input frequency                                                                | range >0 Hz to 2                                                    | 50 MHZ                                                                                                                       |  |

| 20         | IN1_n                |          | pins (OEnb) nee                                                                | d four clock cycle                                                  | gher than DC. Output Enable control<br>es before the corresponding output get<br>ures glitch free transition of the outputs. |  |

| 1          | OUT0_p               |          |                                                                                |                                                                     |                                                                                                                              |  |

| 2          | OUT0_n               |          |                                                                                |                                                                     |                                                                                                                              |  |

| 4          | OUT1_p               |          |                                                                                |                                                                     |                                                                                                                              |  |

| 5          | OUT1_n               |          |                                                                                |                                                                     |                                                                                                                              |  |

| 8          | OUT2_p               |          | Ultra-Low Addit                                                                | tive .litter Differ                                                 | ential LPHCSL Outputs 0 to 7                                                                                                 |  |

| 9          | OUT2_n               |          | Ollia Low Addi                                                                 | are onto Dinor                                                      |                                                                                                                              |  |

| 11         | OUT3_p               |          | Output frequenc                                                                | y range >0 Hz to                                                    | 250 MHz                                                                                                                      |  |

| 12         | OUT3_n               | 0        | In I <sup>2</sup> C bus controlled mode (SEL pin pulled high) output enable is |                                                                     |                                                                                                                              |  |

| 25         | OUT4_p               |          | controlled via internal registers                                              |                                                                     |                                                                                                                              |  |

| 26         | OUT4_n               |          |                                                                                |                                                                     |                                                                                                                              |  |

| 28         | OUT5_p               |          |                                                                                | oin pulled low) output enable is                                    |                                                                                                                              |  |

| 29         | OUT5_n               |          | controlled by OE_n pins.                                                       |                                                                     |                                                                                                                              |  |

| 32         | OUT6_p               |          |                                                                                |                                                                     |                                                                                                                              |  |

| 33         | OUT6_n               |          |                                                                                |                                                                     |                                                                                                                              |  |

| 35         | OUT7_p               |          |                                                                                |                                                                     |                                                                                                                              |  |

| 36         | OUT7_n               |          |                                                                                |                                                                     |                                                                                                                              |  |

|            |                      |          | When SEL pin is I <sup>2</sup> C Bus. This pir                                 | s low, this pin is Ir<br>s high, this pin too<br>n is pulled down v | nput Select 0 hardware control input.<br>gether with pin 44 provides address for<br>with 100 kΩ resistor                     |  |

| 45         | IN_SEL0<br>/I2C_SA_0 | IPD      | IN_SEL1                                                                        | IN_SEL0                                                             | OUTN                                                                                                                         |  |

|            | /12U_3A_0            |          | 0                                                                              | 0                                                                   | Input 0 (IN0)                                                                                                                |  |

|            |                      |          | 0                                                                              | 1                                                                   | Input 1 (IN1)                                                                                                                |  |

|            |                      |          | 1                                                                              | 0                                                                   | Crystal Oscillator or Overdrive                                                                                              |  |

|            |                      |          | 1                                                                              | 1                                                                   | Crystal Bypass                                                                                                               |  |

| 44         | IN_SEL1<br>/I2C_SA_1 | IPD      | When SEL pin is When SEL pin is                                                | s high, this pin too                                                | ne Input apput Select 1 hardware control pin. gether with pin 45 provides address for with 100 $k\Omega$ resistor.           |  |

TABLE 3-1: SY75608 PIN FUNCTION TABLE (CONTINUED)

| Pin Number | Pin Name             | Pin Type |                                                                                                                                                                                                                                                                                                                               | De                                     | scription                                                                                      |  |  |

|------------|----------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------|--|--|

|            |                      |          |                                                                                                                                                                                                                                                                                                                               | Type or I <sup>2</sup> C Bus           | Clock pin 42 selects output type.                                                              |  |  |

|            |                      |          | OE_TYPE1                                                                                                                                                                                                                                                                                                                      | OE_TYPE0                               | Output [7:0] state when OE_n is high                                                           |  |  |

|            | OE TYPE0             |          | 0                                                                                                                                                                                                                                                                                                                             | 0                                      | Both p and n are pulled low via internal output termination resistors per standard HCSL (PCIe) |  |  |

| 43         | /I2C_SCL             | IPD/O    | 0                                                                                                                                                                                                                                                                                                                             | 1                                      | Drive Differential Low: p is pulled low and n is pulled high via output termination resistors  |  |  |

|            |                      |          | 1                                                                                                                                                                                                                                                                                                                             | 0                                      | Reserved                                                                                       |  |  |

| ı          |                      |          | 1                                                                                                                                                                                                                                                                                                                             | 1                                      | High-Z (disabled)                                                                              |  |  |

|            |                      |          | with 100 kΩ resi                                                                                                                                                                                                                                                                                                              | stor when SEL is                       |                                                                                                |  |  |

| 42         | OE_TYPE1/<br>I2C_SDA | IPD/OOD  | Output Signal Type or $I^2C$ Bus I/O Data When SEL pin is low, this pin and pin 43 selects output type. When SEL pin is high, this pin is an I/O pin (Input/Open-Drain) for $I^2C$ Bus. This pin is pulled down with 100 k $\Omega$ resistor when SEL is low.                                                                 |                                        |                                                                                                |  |  |

| 48         | OE0b                 |          | Output Enable Control When the SEL pin is low and OEnb is low, the output n where n = {0,,7 is active. When the SEL pin is low and OEnb is high, the output is dependent on OE_TYPE0/1 pins OEnb is synchronous and it need four clock cycles before the                                                                      |                                        |                                                                                                |  |  |

| 47         | OE1b                 |          |                                                                                                                                                                                                                                                                                                                               |                                        |                                                                                                |  |  |

| 14         | OE2b                 |          |                                                                                                                                                                                                                                                                                                                               |                                        |                                                                                                |  |  |

| 13         | OE3b                 | IDD      |                                                                                                                                                                                                                                                                                                                               |                                        |                                                                                                |  |  |

| 23         | OE4b                 | IPD      |                                                                                                                                                                                                                                                                                                                               |                                        |                                                                                                |  |  |

| 22         | OE5b                 |          |                                                                                                                                                                                                                                                                                                                               |                                        |                                                                                                |  |  |

| 38         | OE6b                 |          | corresponding output gets enabled/disabled.                                                                                                                                                                                                                                                                                   |                                        |                                                                                                |  |  |

| 37         | OE7b                 |          | OEnb pins are pulled-down with 100 k $\Omega$ resistor.                                                                                                                                                                                                                                                                       |                                        |                                                                                                |  |  |

| 18         | XIN                  | I        | Overdrive Mode                                                                                                                                                                                                                                                                                                                | 9                                      | stal Bypass Mode or Crystal  lown this pin or connect it to ground.                            |  |  |

| 19         | XOUT                 | 0        | Crystal Oscillat                                                                                                                                                                                                                                                                                                              | -                                      |                                                                                                |  |  |

| 41         | SEL                  | IPD      | Select Control When this pin is low, the device is controlled via hardware pins, IN_SEL0/1 and OE_TYPE0/1. When this pin is high, the device is controlled via $I^2C$ Bus port.  Any change of SEL pin value requires power cycle. Hence, SEL pin cannot be changed on the fly. This pin is pulled down with 100 kΩ resistor. |                                        |                                                                                                |  |  |

| 24         | OUT_IMP_SEL          | IPD      | Output Impedance Select When this pin is low, the output differential impedance is $100\Omega$ When this pin is high, the output differential impedance is $85\Omega$ This pin is pulled down with $100~k\Omega$ resistor.                                                                                                    |                                        |                                                                                                |  |  |

| 15         |                      |          | D. W. G.                                                                                                                                                                                                                                                                                                                      | V. 16                                  |                                                                                                |  |  |

| 39         | VDD                  | Р        | Positive Supply                                                                                                                                                                                                                                                                                                               | <b>/ Voltage</b><br>, 2.5V, or 1.8V su | innly                                                                                          |  |  |

| 46         |                      |          | Connect to 0.5 V                                                                                                                                                                                                                                                                                                              | , 2.0 v, 01 1.0 v 30                   | PK-17.                                                                                         |  |  |

TABLE 3-1: SY75608 PIN FUNCTION TABLE (CONTINUED)

| Pin Number | Pin Name | Pin Type | Description                                                                                                                                              |

|------------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3          |          |          |                                                                                                                                                          |

| 10         | VDDO     | Р        | Positive Supply Voltage for Differential Outputs                                                                                                         |

| 27         | VDDO     | P        | Connect to 3.3V, 2.5V or 1.8V supply. These pins power up differential outputs OUT[7:0] p/n.                                                             |

| 34         |          |          |                                                                                                                                                          |

| 40         | VPP      | Р        | Positive Supply Voltage for Programming OTP Memory This pin is used for generating custom configurations on ATE. Connect to ground for normal operation. |

| 6          |          |          |                                                                                                                                                          |

| 7          |          |          | 3d                                                                                                                                                       |

| 30         | GND      | Р        | Ground Connect to ground.                                                                                                                                |

| 31         |          |          | Confidence to ground.                                                                                                                                    |

| ePAD       |          |          |                                                                                                                                                          |

TABLE 3-2: SY75612 PIN FUNCTION TABLE

| Pin Number | Pin Name | Pin Type | Description                                                                                                                                                                                                           |

|------------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20         | IN0_p    |          | Differential/Single-Ended References 0 and 1                                                                                                                                                                          |

| 21         | IN0_n    |          |                                                                                                                                                                                                                       |

| 25         | IN1_p    | ı        | Input frequency range >0 Hz to 250 MHz                                                                                                                                                                                |

| 24         | IN1_n    | '        | Note: >0 Hz means frequency higher than DC. Output Enable control pins (OEnb) need four clock cycles before the corresponding output get enabled/disable. This feature ensures glitch free transition of the outputs. |

| 1          | OUT0_p   |          |                                                                                                                                                                                                                       |

| 2          | OUT0_n   |          |                                                                                                                                                                                                                       |

| 4          | OUT1_p   |          |                                                                                                                                                                                                                       |

| 5          | OUT1_n   |          |                                                                                                                                                                                                                       |

| 6          | OUT2_p   |          |                                                                                                                                                                                                                       |

| 7          | OUT2_n   |          |                                                                                                                                                                                                                       |

| 8          | OUT3_p   |          |                                                                                                                                                                                                                       |

| 9          | OUT3_n   |          |                                                                                                                                                                                                                       |

| 10         | OUT4_p   |          | Ultra-Low Additive Jitter Differential LPHCSL Outputs 0 to 11                                                                                                                                                         |

| 11         | OUT4_n   |          | ondia-Low Additive officer billerential Li 1100L outputs o to 11                                                                                                                                                      |

| 13         | OUT5_p   |          | Output frequency range >0 Hz to 250 MHz                                                                                                                                                                               |

| 14         | OUT5_n   | 0        | In I <sup>2</sup> C bus controlled mode (SEL pin pulled high) output enable is                                                                                                                                        |

| 29         | OUT6_p   |          | controlled via internal registers                                                                                                                                                                                     |

| 30         | OUT6_n   |          |                                                                                                                                                                                                                       |

| 32         | OUT7_p   |          | In Hardware control mode (SEL pin pulled low) output enable is                                                                                                                                                        |

| 33         | OUT7_n   |          | controlled by OE_n pins.                                                                                                                                                                                              |

| 34         | OUT8_p   |          |                                                                                                                                                                                                                       |

| 35         | OUT8_n   |          |                                                                                                                                                                                                                       |

| 36         | OUT9_p   |          |                                                                                                                                                                                                                       |

| 37         | OUT9_n   |          |                                                                                                                                                                                                                       |

| 38         | OUT10_p  |          |                                                                                                                                                                                                                       |

| 39         | OUT10_n  |          |                                                                                                                                                                                                                       |

| 41         | OUT11_p  |          |                                                                                                                                                                                                                       |

| 42         | OUT11_n  |          |                                                                                                                                                                                                                       |

TABLE 3-2: SY75612 PIN FUNCTION TABLE (CONTINUED)

| Pin Number | Pin Name             | Pin Type |                                                                                                                                                                                                                                                                         | De                                                                                                                                                        | scription                                                                                                                 |  |  |

|------------|----------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

|            |                      |          | When SEL pin is                                                                                                                                                                                                                                                         | s low, this pin is li<br>s high, this pin to                                                                                                              | nput Select 0 hardware control input.<br>gether with pin 51 provides address for<br>with 100 kΩ resistor when SEL is low. |  |  |

| 50         | IN_SEL0              | IDD      | IN_SEL1                                                                                                                                                                                                                                                                 | IN_SEL0                                                                                                                                                   | OUTN                                                                                                                      |  |  |

| 52         | /I2C_SA_0            | IPD      | 0                                                                                                                                                                                                                                                                       | 0                                                                                                                                                         | Input 0 (IN0)                                                                                                             |  |  |

|            |                      |          | 0                                                                                                                                                                                                                                                                       | 1                                                                                                                                                         | Input 1 (IN1)                                                                                                             |  |  |

|            |                      |          | 1                                                                                                                                                                                                                                                                       | 0                                                                                                                                                         | Crystal Oscillator or Overdrive                                                                                           |  |  |

|            |                      |          | 1                                                                                                                                                                                                                                                                       | 1                                                                                                                                                         | Crystal Bypass                                                                                                            |  |  |

| 51         | IN_SEL1<br>/I2C_SA_1 | IPD      | Input Select 1 or Serial Interface Input When SEL pin is low, this pin is Input Select 1 hardware control pin. When SEL pin is high, this pin together with pin 52 provides address f $I^2C$ Bus. This pin is pulled-down with 100 k $\Omega$ resistor when SEL is low. |                                                                                                                                                           |                                                                                                                           |  |  |

|            |                      |          | Output Signal 1<br>When SEL pin is                                                                                                                                                                                                                                      |                                                                                                                                                           | Clock<br>pin 49 selects output type.                                                                                      |  |  |

|            |                      |          | OE_TYPE1                                                                                                                                                                                                                                                                | OE_TYPE0                                                                                                                                                  | Output [11:0] state when OE_n is high                                                                                     |  |  |

| 50         | OE TYPE0             |          | 0                                                                                                                                                                                                                                                                       | 0                                                                                                                                                         | Both p and n are pulled low via internal output termination resistors per standard HCSL (PCIe)                            |  |  |