# **BMP581**

# Barometric Pressure Sensor

## BST-BMP581-DS004-13

Document revision 1.13

Document release date April 2025

Document number BST-BMP581-DS004-13

Sales Part Number 0 273 017 025

Notes Data and descriptions in this document are subject to change without notice. Product

photos and pictures are for illustration purposes only and may differ from the real

product appearance.

## 1 Basic Description

The BMP581 is an absolute barometric pressure sensor. Its small dimensions, its low power consumption and the highend performance allow the implementation in a wide range of applications.

#### **Key features:**

Pressure operating range: 30 .. 125 kPa Temperature operating range: -40 .. 85°C Ultra low noise and current consumption:

► Ultra low noise: < 0.1PaRMS natively (without low-pass filter enabled)

▶ 1.3 µA 1Hz in low power mode

Absolute pressure accuracy: ± 0.5 hPa (max)

Relative pressure accuracy: 0.06 hPa per 10kPa step Pressure Temperature-induced offset: ± 0.5 Pa/K

BMP581 provides true absolute pressure and temperature, due to on-chip linearization and temperaturecompensation

Primary digital interface with 12 MHz slave SPI (4-wire, 3-wire), 12.5MHz I3C and up to 1MHz I2C (Fm+)

Output data rates:

▶ up to 480 Hz in CONTINUOUS mode

▶ 0.125 .. 240 Hz in NORMAL mode

Wide power supply range: VDD 1.71 V ... 3.6 V and VDDIO 1.08 V ... 3.6 V, both independent

Programmable low-pass filtering

On-chip FIFO buffer for up to 32 pressure samples

Programmable interrupts, including pressure-changed detection

6 bytes user programmable non-volatile memory

Compact 10-pin metal-lid LGA package with a footprint of only 2.0 × 2.0 mm2 and max 0.8 mm package height.

RoHS compliant, halogen and lead free

#### **Typical applications:**

Enhancement of GPS navigation (e.g. time-to-first-fix improvement, dead-reckoning, slope detection)

Indoor navigation (floor detection, elevator detection)

Outdoor navigation

Sports applications like calorie counting, fitness activity identification

Emergency caller location

Weather forecast

Vertical velocity indication (e.g. rise/sink speed)

Altitude control of drones and flying toys

## **Target devices:**

Handsets such as mobile phones, tablet PCs, GPS devices

Navigation systems

Portable health care devices

Home weather stations

Drones and flying toys

Smart watches

Virtual and augmented reality devices

## **Table of Contents**

| 1 | Bas | ic Desc   | ription                                             |    |

|---|-----|-----------|-----------------------------------------------------|----|

| 2 | Spe | cificatio | on                                                  | 8  |

| 3 | Qui | ck start  | guide                                               | 14 |

|   | 3.1 | Senso     | or API and COINES                                   | 14 |

| 4 | Fun | ctional   | Description and Features                            | 14 |

|   | 4.1 |           | diagramdiagram                                      |    |

|   | 4.2 | Power     | r management                                        | 14 |

|   |     |           | r modes                                             |    |

|   |     | 4.3.1     | STANDBY mode                                        |    |

|   |     | 4.3.2     | DEEP STANDBY                                        |    |

|   |     | 4.3.3     | FORCED mode                                         |    |

|   |     | 4.3.4     | NORMAL mode                                         |    |

|   |     | 4.3.5     | Low Power NORMAL mode                               |    |

|   |     | 4.3.6     | CONTINUOUS mode                                     |    |

|   |     | 4.3.7     | Mode transitions                                    | 18 |

|   |     | 4.3.8     | Mode-depending register write restrictions          |    |

|   |     | 4.3.9     | Post-power-up procedure                             |    |

|   |     | 4.3.10    | Soft reset                                          | 18 |

|   | 4.4 | Meası     | urements                                            | 18 |

|   |     | 4.4.1     | Pressure and temperature measurement enable         | 18 |

|   |     | 4.4.2     | Pressure and temperature oversampling ratio (OSR)   | 19 |

|   |     | 4.4.3     | Configuration changes in NORMAL and CONTINUOUS mode | 19 |

|   |     | 4.4.4     | IIR filter                                          | 19 |

|   | 4.5 | Data r    | egisters                                            | 22 |

|   |     | 4.5.1     | Data Shadowing                                      | 22 |

|   | 4.6 | FIFO .    |                                                     | 22 |

|   |     | 4.6.1     | FIFO Configuration                                  |    |

|   |     | 4.6.2     | FIFO status                                         |    |

|   |     | 4.6.3     | FIFO data readout                                   | 23 |

|   |     | 4.6.4     | FIFO configuration changes                          | 25 |

|   | 4.7 | Interru   | ıpts                                                | 25 |

|   |     | 4.7.1     | Interrupt enabling                                  |    |

|   |     | 4.7.2     | Interrupt sources                                   |    |

|   |     | 4.7.3     | Interrupt pin                                       |    |

|   |     |           |                                                     |    |

|   | 4.8 NVM                 | Programmability                                                            | 29 |

|---|-------------------------|----------------------------------------------------------------------------|----|

|   | 4.8.1                   | NVM User Range                                                             | 29 |

|   | 4.9 Final               | test result                                                                | 30 |

| 5 | Digital Inte            | rface                                                                      | 31 |

|   | 5.1 Proto               | col Selection                                                              | 31 |

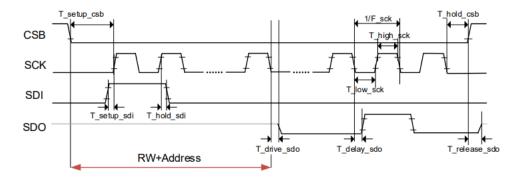

|   | 5.2 Interfa             | ace timing                                                                 | 31 |

|   | 5.2.1                   | Interface timing                                                           | 32 |

|   | 5.2.2                   | I2C timing specifications                                                  | 33 |

|   | 5.2.3                   | I3C timing specifications                                                  | 33 |

|   | 5.3 Pad d               | drive stength                                                              | 34 |

|   | 5.4 Read                | burst address increment                                                    | 36 |

|   | 5.5 SPI P               | Protocol                                                                   | 36 |

|   | 5.5.1                   | SPI3 Wire Mode                                                             | 36 |

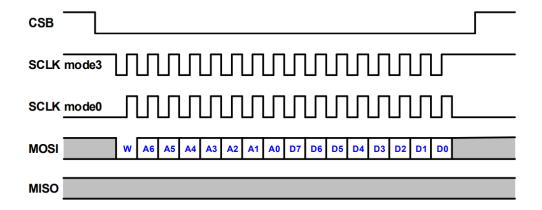

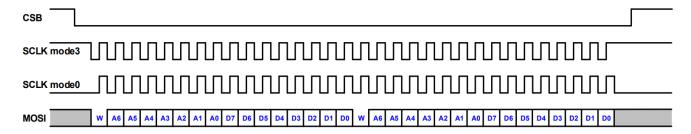

|   | 5.5.2                   | SPI Write Operation                                                        | 36 |

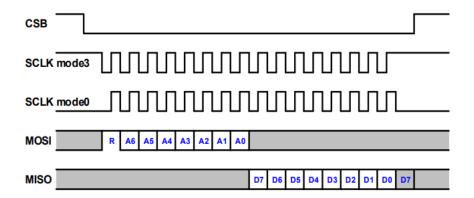

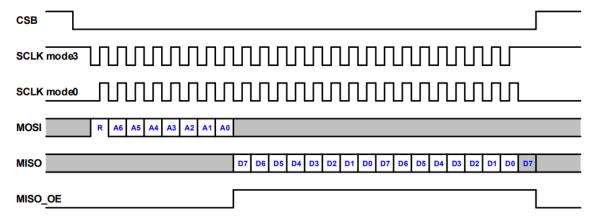

|   | 5.5.3                   | SPI read operation                                                         | 37 |

|   | 5.5.4                   | SPI hybrid bursts                                                          | 38 |

|   | 5.6 I <sup>2</sup> C pr | otocol                                                                     | 38 |

|   | 5.6.1                   | I <sup>2</sup> C write operation                                           | 39 |

|   | 5.6.2                   | I <sup>2</sup> C read operation                                            | 40 |

|   | 5.7 I3C P               | rotocol                                                                    | 42 |

|   | 5.7.1                   | I3C Identifiers                                                            | 42 |

|   | 5.7.2                   | I3C In-band Interrupts                                                     | 42 |

|   | 5.7.3                   | Common Command Codes (CCC)                                                 | 44 |

|   | 5.7.4                   | I3C SDR Operations                                                         | 45 |

|   | 5.7.5                   | S0/S1 error recovery                                                       | 45 |

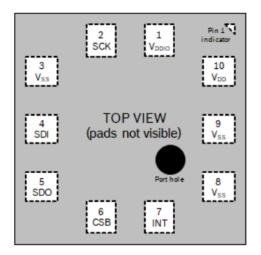

| 6 | Pin out and             | d connection diagrams                                                      | 46 |

|   | 6.1 Pin O               | ut                                                                         | 46 |

|   | 6.2 Conn                | ection Diagrams                                                            | 46 |

|   | 6.2.1                   | SPI 3-wire                                                                 | 47 |

|   | 6.2.2                   | SPI 4-wire                                                                 | 47 |

|   | 6.2.3                   | I <sup>2</sup> C                                                           |    |

|   | 6.2.4                   | I3C                                                                        |    |

|   | 6.2.5                   | SPI/I <sup>2</sup> C/I3C Configuration with VDD, VDDIO ramp-up time <10 μs | 49 |

| 7 | Register Ma             | ap                                                                         | 50 |

|   | 71 Regis                | ster (0x01) ASIC identification ID                                         | 51 |

| 7.2  | Register | (0x02) ASIC revision ID                                       | . 51 |

|------|----------|---------------------------------------------------------------|------|

| 7.3  | Register | (0x11) ASIC status register                                   | . 51 |

| 7.4  | Register | (0x13) Configure host interface related settings (NVM-backed) | . 52 |

| 7.5  | Register | (0x14) Interrupt configuration register                       | . 52 |

| 7.6  | Register | (0x15) INT source selection                                   | . 54 |

| 7.7  | Register | (0x16) FIFO configuration                                     | . 54 |

| 7.8  | Register | (0x17) Number of frames in FIFO                               | . 55 |

| 7.9  | Register | (0x18) FIFO selection configuration                           | . 55 |

| 7.10 | Register | (0x1C) Reserved                                               | . 56 |

| 7.11 | Register | (0x1D) Temperature XLSB                                       | . 56 |

| 7.12 | Register | (0x1E) Temperature LSB                                        | . 56 |

| 7.13 | Register | (0x1F) Temperature MSB                                        | . 56 |

| 7.14 | Register | (0x20) Pressure XLSB                                          | . 56 |

| 7.15 | Register | (0x21) Pressure LSB                                           | . 57 |

| 7.16 | Register | (0x22) Pressure MSB                                           | . 57 |

| 7.17 | Register | (0x23) Reserved                                               | . 57 |

| 7.18 | Register | (0x24) Reserved                                               | . 57 |

| 7.19 | Register | (0x25) Reserved                                               | . 57 |

| 7.20 | Register | (0x26) Reserved                                               | . 58 |

| 7.21 | Register | (0x27) Interrupt status register (clear-on-read)              | . 58 |

| 7.22 | Register | (0x28) Status register                                        | . 58 |

| 7.23 | Register | (0x29) FIFO output port                                       | . 59 |

| 7.24 | Register | (0x2B) NVM address                                            | . 60 |

| 7.25 | Register | (0x2C) NVM data (LSB)                                         | . 60 |

| 7.26 | Register | (0x2D) NVM data (MSB)                                         | . 60 |

| 7.27 | Register | (0x30) DSP configuration                                      | . 61 |

| 7.28 | Register | (0x31) DSP IIR configuration                                  | . 62 |

| 7.29 | Register | (0x32) Out-of-range (OOR) threshold for pressure (LSB)        | . 63 |

| 7.30 | Register | (0x33) Out-of-range (OOR) threshold for pressure (MSB)        | . 63 |

| 7.31 | Register | (0x34) Out-of-range (OOR) range configuration                 | . 63 |

| 7.32 | Register | (0x35) Out-of-range (OOR) configuration                       | . 63 |

|    | 7.33 Regis  | ter (0x36) Over-sampling rate (OSR) configuration           | 64 |

|----|-------------|-------------------------------------------------------------|----|

|    | 7.34 Regis  | ter (0x37) Output data rate (ODR) configuration             | 64 |

|    | 7.35 Regis  | ter (0x38) Effective over-sampling rate (OSR) configuration | 66 |

|    | 7.36 Regis  | ter (0x7E) Command Register                                 | 67 |

| 8  | Package     |                                                             | 68 |

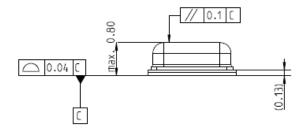

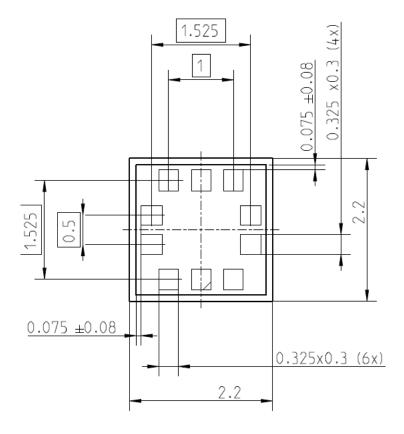

|    | 8.1 BMP5    | 581 Package Outline Dimensions                              | 68 |

|    | 8.1.1       | Top View                                                    | 68 |

|    | 8.1.2       | Bottom View                                                 | 68 |

|    | 8.1.3       | Side view                                                   | 69 |

|    | 8.2 Landi   | ng pattern                                                  | 69 |

|    | 8.3 Devic   | e Marking                                                   | 70 |

|    | 8.3.1       | Mass Production Devices                                     | 70 |

|    | 8.3.2       | Engineering Samples                                         | 70 |

|    | 8.4 Moist   | ure Sensitivity Level and Soldering                         | 71 |

|    | 8.4.1       | MSL and device storage                                      | 71 |

|    | 8.4.2       | Reflow Solder profile                                       | 71 |

|    | 8.5 Enviro  | onmental Safety                                             | 71 |

|    | 8.5.1       | RoHS                                                        | 71 |

|    | 8.5.2       | Halogen content                                             | 71 |

|    | 8.6 Intern  | al Package Structure                                        | 71 |

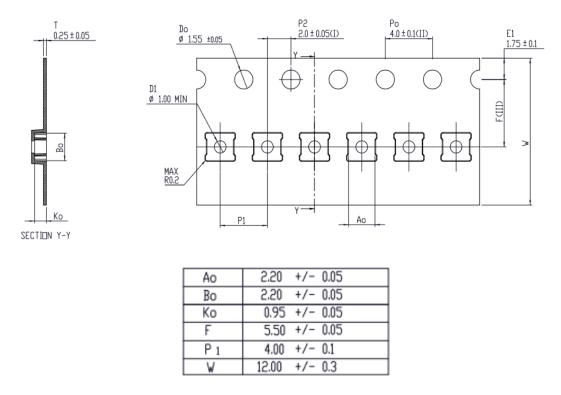

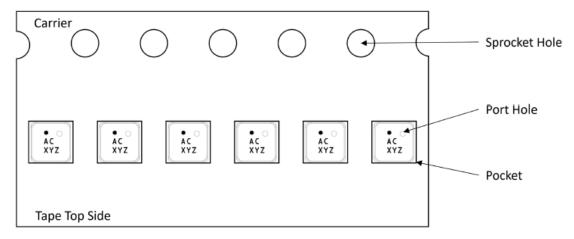

|    | 8.7 Tape    | and reel specification                                      | 72 |

|    | 8.7.1       | Dimensions                                                  | 72 |

|    | 8.7.2       | Orientation within the reel                                 | 72 |

| 9  | Legal discl | aimer                                                       | 73 |

| 10 | Document    | history and modification                                    | 74 |

## List of tables

| Table 1: Pressure Performance                                                                          |      |

|--------------------------------------------------------------------------------------------------------|------|

| Table 2: Temperature Performance                                                                       | . 10 |

| Table 3: Mechanical characteristics                                                                    | . 10 |

| Table 4: Electrical characteristics                                                                    |      |

| Table 5: Interface pin electrical characteristics                                                      |      |

| Table 6: Absolute maximum ratings                                                                      |      |

| Table 7: maximum nominal ODR setting per OSR settings in NORMAL mode                                   |      |

| Table 8: Maximum nominal ODR setting per OSR settings in NORMAL mode for temperature only measurements | .17  |

| Table 9: Oversampling settings                                                                         | . 19 |

| Table 10: IIR filter settings and bandwidth                                                            |      |

| Table 11: FIFO pressure and temperature frame (PT-fram                                                 |      |

| Table 12: FIFO temperature frame (T-frame)                                                             |      |

| Table 13: FIFO pressure frame (P-frame)                                                                |      |

| Table 14: FIFO empty frame                                                                             |      |

| Table 15: Final test result                                                                            |      |

| Table 16: Possible switches between interface modes                                                    |      |

| Table 17: General interface parameters                                                                 |      |

| Table 18: SPI timings                                                                                  | . 32 |

| Table 19: I3C timing limitations for VDDIO < 1.62 V                                                    |      |

| Table 20: Drive strength in IOH                                                                        |      |

| Table 21: Drive strengths for IOL                                                                      |      |

| Table 22: SPI interface pin usage                                                                      |      |

| Table 23: I3C provisional identifier                                                                   |      |

| Table 24: I3C device characteristics register (DCR)                                                    |      |

| Table 25: I3C bus characteristics registers (BCR)                                                      |      |

| Table 26: Content of IBI mandatory byte and IBI payload byte                                           |      |

| Table 27: List of I3C CCCs                                                                             |      |

| Table 28: Pin description                                                                              |      |

| Table 29: Package markings                                                                             |      |

| Table 30: Marking of engineering samples                                                               | . 70 |

## 2 Specification

If not stated otherwise,

- All values are valid over the full voltage range

- Minimum/maximum values are ±3 sigma values

- Typical values of currents and state machine timings are determined at 25 °C

- Minimum/maximum values of currents are valid for the temperature range from -40°C...+85°C

- Minimum/maximum values of timings are valid for the temperature range from -40°C...+85°C

- Environmental conditions like temperature, RF, humidity are constant, unless ranges for these are specified

Pressure performance is given in Table 1, temperature performance in Table 2. If not stated otherwise:

- Parameters are valid for the range 300 1100 hPa @  $-5 65 ^{\circ}\text{C}$

- Parameters are valid before soldering after storage in standard conditions according to Table 6.

- Performance parameters are derived without MSL1 preconditioning.

- "Post-solder " refers to 3x reflow soldering after storage in standard conditions.

Table 1: Pressure Performance<sup>1</sup>

| Parameter         | Symbol       | Comment      | Min | Тур   | Max | Unit |

|-------------------|--------------|--------------|-----|-------|-----|------|

| Pressure          | Р            |              | 30  |       | 125 | kPa  |

| measurement       |              |              |     |       |     |      |

| range             |              |              |     |       |     |      |

| Temperature       | TA           | Pressure     | -40 |       | 85  | °C   |

| range             |              | measured in  |     |       |     |      |

|                   |              | the entire   |     |       |     |      |

|                   |              | temperature  |     |       |     |      |

|                   |              | operational  |     |       |     |      |

|                   |              | range        |     |       |     |      |

| Relative pressure | $A_{p\_rel}$ | 700 – 1100   |     | ± 6   |     | Pa   |

| accuracy          |              | hPa, 15 –    |     |       |     |      |

|                   |              | 55 °C, 10    |     |       |     |      |

|                   |              | kPa steps    |     |       |     |      |

| Relative pressure | $A_{p\_rel}$ | 900 – 1100   |     | ± 0.4 |     | Pa   |

| accuracy          |              | hPa hPa,     |     |       |     |      |

|                   |              | 25 °C, 1 kPa |     |       |     |      |

|                   |              | steps        |     |       |     |      |

| Absolute Pressure | $A_{p\_abs}$ | 300 – 1100   |     | ± 30  |     | Pa   |

| accuracy          |              | hPa, -5 –    |     |       |     |      |

|                   |              | 65 °C,       |     |       |     |      |

|                   |              | including    |     |       |     |      |

|                   |              | TCO          |     |       |     |      |

| Absolute accuracy pressure <sup>2</sup> (full range) | $A_{p\_abs\_full\_range}$ | 300 – 1100<br>hPa, -40 –<br>85 °C, incl.<br>solder drift,<br>TCO after<br>qualification <sup>3</sup> | ± 75  |      | Ра    |

|------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------|-------|------|-------|

| Offset temperature coefficient                       | TCO                       | 300 - 1100<br>hPa, -5 -<br>65 °C, 10 K<br>steps                                                      | ± 0.5 |      | Pa/K  |

| Pressure data resolution                             | $A_{p\_res}$              |                                                                                                      | 1/64  |      | Pa    |

| Pressure noise                                       | $V_{p\_low\_power}$       | OSR set to<br>"lowest<br>power"                                                                      | 0.78  | 0.95 | PaRMS |

| Pressure noise                                       | $V_{p\_hi\_res}$          | OSR set to<br>"high<br>resolution"                                                                   | 0.21  | 0.25 | PaRMS |

| Pressure noise                                       | $V_{p\_high\_res}$        | OSR set to<br>"high<br>resolution"                                                                   | 0.08  |      | PaRMS |

| Long term drift                                      | $\Delta P_{stab\_long}$   | Drift during 1<br>year <sup>a</sup>                                                                  | ± 10  |      | Pa    |

| Short term drift                                     | $\Delta P_{stab\_short}$  | Drift during<br>24 h at<br>constant<br>pressure and<br>temperature                                   | ± 1.5 |      | Pa    |

| Solder Drift                                         |                           | 5x reflow<br>soldering<br>after storage<br>in standard<br>conditions<br>(25 °C / 100<br>kPa)         | ± 30  |      | Pa    |

a. HTOLderived from 1000h HTOL divided by 5

$<sup>^2</sup>$  Accuracy measured based on BST soldering process, in Bosch lab with dedicated pressure chamber and high-accuracy reference equipment

<sup>&</sup>lt;sup>3</sup> After 1000rhs HTOL and HTS see qualification report

Table 2: Temperature Performance

| Parameter                                | Symbol                | Comment                                                          | Min | Тур     | Max   | Unit |

|------------------------------------------|-----------------------|------------------------------------------------------------------|-----|---------|-------|------|

| Temperature<br>measurement<br>range      |                       | Temperature measured in the entire temperature operational range | -40 |         | 85    | °C   |

| Absolute accuracy temperature            | $A_{t\_abs}$          | -5 55°C                                                          |     | +/- 0.5 |       | К    |

| Absolute accuracy temperature full range | $A_{t_{a}bs_{f}full}$ | -40 85°C                                                         |     | +/- 0.5 |       | К    |

| Relative accuracy temperature            | $A_{t\_rel\_full}$    | -40 85°C,<br>20 K steps                                          |     |         |       | К    |

| Temperature data resolution              | $A_{t\_res}$          |                                                                  |     | 1/65536 | + 1.0 | °C   |

Table 3: Mechanical characteristics

| Parameter                    | Symbol | Comment                          | Min         | Тур       | Max         | Unit            |

|------------------------------|--------|----------------------------------|-------------|-----------|-------------|-----------------|

| Package footprint dimensions |        |                                  | 1.90 x 1.90 | 2.0 x 2.0 | 2.10 x 2.10 | mm <sup>2</sup> |

| Package height               |        |                                  | 0.7         | 0.75      | 0.8         | mm              |

| Number of pins               |        |                                  |             | 10        |             |                 |

| Package category             |        | Moisture<br>sensitivity<br>level |             | MSL1      |             |                 |

Table 4: Electrical characteristics

| Parameter                     | Symbol                  | Comment                                                          | Min   | Тур            | Max | Unit |

|-------------------------------|-------------------------|------------------------------------------------------------------|-------|----------------|-----|------|

| Power supply voltage          | VDD                     |                                                                  | 1.71  | 1.8 / 3.3      | 3.6 | V    |

| Power supply voltage I/Os     | VDDIO                   |                                                                  | 1.08  | 1.2/ 1.8 / 3.3 | 3.6 | V    |

| Supply ramp time              | t_VDDramp & t_VDDIOramp | 10% to 90% of target voltage                                     | 0.01ª |                | 10  | ms   |

| Operational temperature range | TOP_full                |                                                                  | -40   |                | 85  | °C   |

| ODR Accuracy                  |                         | -4085°C                                                          | -10   |                | +10 | %    |

| Power-up time                 | t_powup                 | Time to first<br>communication<br>after both VDD ><br>VDDmin and |       |                | 2   | ms   |

|                                  |                       | VEDIO               |     | 1        |      | T       |

|----------------------------------|-----------------------|---------------------|-----|----------|------|---------|

|                                  |                       | VDDIO >             |     |          |      |         |

| 0: : : :                         |                       | VDDIOmin            |     |          |      |         |

| Start-up time from               | t_startup             | Time from mode      |     |          | 3    | ms      |

| STANDBY                          |                       | change to start of  |     |          |      |         |

|                                  |                       | measurement         |     |          |      |         |

| Start-up time from               | $t_{startup\_deep}$   | Time from mode      |     |          | 4    | ms      |

| DEEP STANBDY                     |                       | change to start of  |     |          |      |         |

|                                  |                       | measurement         |     |          |      |         |

| Re-configuration                 | $t_{reconf}$          | Time from           |     |          | 3    | ms      |

| time                             |                       | configuration       |     |          |      |         |

|                                  |                       | change in           |     |          |      |         |

|                                  |                       | NORMAL or           |     |          |      |         |

|                                  |                       | CONTINUOUS          |     |          |      |         |

|                                  |                       | mode to start of    |     |          |      |         |

|                                  |                       | first measurement   |     |          |      |         |

| Re-configuration                 | $t_{reconf\_deep}$    | Time from           |     |          | 4    | ms      |

| time                             |                       | configuration       |     |          |      |         |

|                                  |                       | change in           |     |          |      |         |

|                                  |                       | NORMAL or           |     |          |      |         |

|                                  |                       | CONTINUOUS          |     |          |      |         |

|                                  |                       | mode to start of    |     |          |      |         |

|                                  |                       | first measurement   |     |          |      |         |

| Time to standby                  | <b>t</b> standby      | Time from any       |     |          | 2.5  | ms      |

|                                  |                       | mode to             |     |          |      |         |

|                                  |                       | STANDBY             |     |          |      |         |

| Soft reset duration              | t <sub>soft_res</sub> | Time from trigger   |     |          | 2    | ms      |

|                                  |                       | of soft reset until |     |          |      |         |

|                                  |                       | device ready        |     |          |      |         |

| I <sup>2</sup> C interface clock | f <sub>i2c</sub>      | Normal Mode &       | 100 |          | 1000 | kHz     |

|                                  |                       | Fast Mode @         |     |          |      |         |

|                                  |                       | Cbus < 550pF -      |     |          |      |         |

|                                  |                       | Fast Mode +         |     |          |      |         |

|                                  |                       | @Cbus < 100pF       |     |          |      |         |

| I3C interface                    | f <sub>i3C</sub>      | @ VDDIO > 1.62 V    | 0.1 | 12.5     | 12.9 | MHz     |

| clock                            |                       | - Normal Mode &     |     |          |      |         |

|                                  |                       | Fast Mode @         |     |          |      |         |

|                                  |                       | Cbus < 550pF -      |     |          |      |         |

|                                  |                       | Fast Mode +         |     |          |      |         |

|                                  |                       | @Cbus > 100pF       |     |          |      |         |

| I3C interface                    | f <sub>i3C_lowv</sub> | @ VDDIO < 1.62 V    | 0.1 |          | 2.5  | MHz     |

| clock low voltage                |                       | - Normal Mode &     |     |          |      |         |

|                                  |                       | Fast Mode @         |     |          |      |         |

|                                  |                       | Cbus < 550pF -      |     |          |      |         |

|                                  |                       | Fast Mode +         |     |          |      |         |

|                                  |                       | @Cbus > 100pF       |     |          |      |         |

| SPI interface                    | $f_{spi}$             | @ VDDIO ≥ 1.62      |     |          | 12   | MHz     |

| clock                            | -                     | V, Cbus ≤ 80 pF 4-  |     |          |      | _       |

|                                  |                       | wire/ 3-wire;       |     |          |      |         |

|                                  |                       | modes 0 and 3       |     |          |      |         |

| SPI interface                    | f <sub>spi_lowv</sub> | @ VDDIO ≤ 1.62      |     |          | 7    | MHz     |

| clock low voltage                | ster=1-4.4            | V, Cbus ≤ 40 pF 4-  |     |          |      | 1411.12 |

|                                  |                       | wire/ 3-wire;       |     |          |      |         |

|                                  |                       | modes 0 and 3       |     |          |      |         |

|                                  |                       |                     |     | <u> </u> |      |         |

| Peak current     | İ <sub>peak</sub>         | maximum DC         |            |      | 260 | μΑ            |

|------------------|---------------------------|--------------------|------------|------|-----|---------------|

|                  |                           | current            |            |      |     | ·             |

| Deep Standby     |                           | 25 °C and          |            | 0.55 |     | μA            |

| current          |                           | VDDIO=VDD=1.8      |            |      |     |               |

|                  |                           | V                  |            |      |     |               |

| Deep Standby     |                           | 25 °C and          |            | 0.55 |     | μA            |

| current          |                           | VDDIO=VDD=3.6      |            |      |     | μл            |

|                  |                           | V                  |            |      |     |               |

| Deep Standby     |                           | 55 °C and          |            | 1.5  |     | μA            |

| current          |                           | VDDIO=VDD=1.8      |            |      |     | μ, ,          |

|                  |                           | V                  |            |      |     |               |

| Standby current  |                           | 25 °C and          |            | 1.0  |     | μΑ            |

| -                |                           | VDDIO=VDD=1.8      |            |      |     | <b>F</b> ·    |

|                  |                           | V                  |            |      |     |               |

| Standby current  |                           | 55 °C and          |            | 3.5  |     | μA            |

| -                |                           | VDDIO=VDD=1.8      |            |      |     | <b>F</b> ** * |

|                  |                           | V                  |            |      |     |               |

| Current          |                           | OSR set to "lowest |            | 1.3  |     | μΑ            |

| consumption low  |                           | power" Low Power   |            |      |     | r "           |

| power mode       |                           | Mode ODR=1 Hz      |            |      |     |               |

|                  |                           | 25 °C              |            |      |     |               |

| Current          |                           | OSR set to "high   |            | 75   | 80  | μΑ            |

| consumption high |                           | resolution" ODR =  |            |      |     | ·             |

| resolution       |                           | 30 Hz 25°C         |            |      |     |               |

| INT pulse length | t <sub>int_pulse</sub>    | Pulse length in    | 90         | 105  | 121 | μs            |

|                  |                           | pulsed mode        |            |      |     | •             |

| INT minimum      | t <sub>int_deassert</sub> | Minimum time       | 90         | 105  | 121 | μs            |

| deassert time    |                           | between INT pin    |            |      |     | •             |

|                  |                           | assert             |            |      |     |               |

| Maximum output   |                           | in CONTINUOUS      |            | 489  |     | Hz            |

| rate (ODR)       |                           | mode, pressure     |            |      |     |               |

|                  |                           | and temperature    |            |      |     |               |

|                  |                           | measured           |            |      |     |               |

| Output data rate |                           | in NORMAL mode     | 0.125      |      | 240 | Hz            |

| (ODR) range      |                           |                    |            |      |     |               |

| Conversion time  | $t_{conv_p}$              | OSR = 1x           | -5%        | 1.0  | +5% | ms            |

| pressure         |                           | OSR = 2x           | -5%        | 1.7  | +5% | ms            |

|                  |                           | OSR = 4x           | -5%        | 2.9  | +5% | ms            |

|                  |                           | OSR = 8x           | -5%        | 5.4  | +5% | ms            |

|                  |                           | OSR = 16x          | -5%        | 10.4 | +5% | ms            |

|                  |                           | OSR = 32x          | -5%        | 20.4 | +5% | ms            |

|                  |                           | OSR = 64x          | -5%        | 40.4 | +5% | ms            |

|                  |                           | OSR = 128x         | -5%        | 80.4 | +5% |               |

| Conversion time  | t <sub>conv_t</sub>       | OSR = 1x           | -5%        | 1.0  | +5% | ms<br>ms      |

| temperature      | •conv_t                   | OSR = 2x           | -5%        | 1.1  | +5% |               |

| temperature      |                           | OSR = 4x           | -5%        | 1.5  | +5% | ms            |

|                  |                           |                    | -5%<br>-5% | 2.1  | +5% | ms            |

|                  |                           | OSR = 8x           |            |      |     | ms            |

|                  |                           | OSR = 16x          | -5%        | 3.3  | +5% | ms            |

|                  |                           | OSR = 32x          | -5%        | 5.8  | +5% | ms            |

|                  |                           | OSR = 64x          | -5%        | 10.8 | +5% | ms            |

|                  |                           | OSR = 128x         | -5%        | 20.8 | +5% | ms            |

| NVM user write      | N <sub>NVM_WRITE</sub> | Number of write |  | 10,000 | writes |

|---------------------|------------------------|-----------------|--|--------|--------|

| cycles <sup>b</sup> |                        | cycles to NVM   |  |        |        |

|                     |                        | user range      |  |        |        |

a. For supply ramps < 0.01 ms, a 10 Ohm resistor must be connected in series to the power supply (see 5.2.5).

Table 5: Interface pin electrical characteristics

| Parameter          | Symbol              | Comment                         | Min | Тур | Max | Unit |

|--------------------|---------------------|---------------------------------|-----|-----|-----|------|

| Input low voltage  | VIL                 | @VDDIO=1.2V/                    |     |     | 30  | %    |

| Input high voltage | VIH                 | 1.8V/3.3V+/-10%<br>@VDDIO=1.2V/ | 70  |     |     | %    |

| input high voltage | VIH                 | 1.8V/3.3V+/-10%                 | 70  |     |     | 70   |

| Input voltage      | VIHYST              | @VDDIO=1.2V/                    | 10  |     |     | %    |

| hysteresis         |                     | 1.8V/3.3V+/-10%                 |     |     |     |      |

| Output low voltage | $V_{OL}$            | @VDDIO=1.2V/                    |     |     | 20  | %    |

|                    |                     | 1.8V/3.3V+/-10%                 |     |     |     |      |

| Output high        | $V_{OH}$            | @VDDIO=1.2V/                    | 80  |     |     | %    |

| voltage            |                     | 1.8V/3.3V+/-10%                 |     |     |     |      |

| Pull-up resistance | R <sub>PU_CSB</sub> | I2C mode,                       | 74  | 100 | 131 | kOhm |

| at CSB pin         |                     | relevant for                    |     |     |     |      |

|                    |                     | interface mode                  |     |     |     |      |

|                    |                     | selection                       |     |     |     |      |

Table 6: Absolute maximum ratings

|                                  |        | Too orate maximan                                                |             |               |      |

|----------------------------------|--------|------------------------------------------------------------------|-------------|---------------|------|

| Parameter                        | Symbol | Comment                                                          | Min         | Max           | Unit |

| Storage temperature <sup>a</sup> |        | ≤ 65 % r.h.<br>Standard<br>conditions: +<br>25°C and<br>40% r.h. | -40         | +125          | °C   |

| Supply voltage VDD               |        |                                                                  | -0.3        | 4.3           | V    |

| Supply voltage VDDIO             |        |                                                                  | -0.3        | 4.3           | V    |

| Max Voltage at I/O Pins          |        |                                                                  | VSSIO-0.3 V | VDDIO + 0.3 V | V    |

a. Storage should occur at standard conditions. For short time periods, the device may be stored outside of this range, but must stay within above mentioned limits.

Stress above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

b. power supply must be stabe during the write sequency. Temperature must be in the range of 0 - 65  $^{\circ}$ C.

## 3 Quick start guide

This section describes quickly the steps to get the sensor running with an example configuration.

#### 3.1 Sensor API and COINES

An Application Programming Interface (API) called Sensor API is available for BMP581. It is available as C source code. The API provides higher-level functions, for example to switch power modes, or read and write the NVM. It is an abstraction layer, so that the user does not have to issue individual read and write transactions to sensor registers. The API still allows direct low-level register access to the sensor. The Sensor API also provides some basic examples of its usage.

The Sensor API is fully compatible with the COINES library, which provides the low-level functions for the sensor API. It is included in the COINES software package. More information, can be found on https://www.bosch-sensortec.com/.

## 4 Functional Description and Features

The BMP581 is a barometric pressure sensor that outputs to the host the absolute pressure in Pa. In addition, the absolute temperature in °C can be provided to the host.

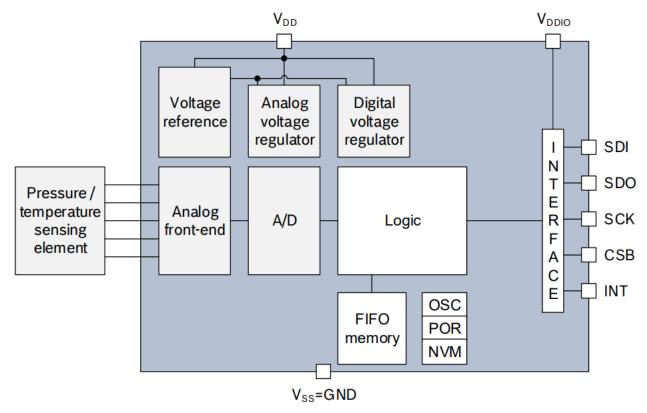

## 4.1 Block diagram

BMP581's key components are a pressure sensitive MEMS sensor element and an integrated circuit that drives and reads out the sensor element. Also it provides data and other functions to the host. The block diagram is shown in Figure 1.

Figure 1: BMP581 block diagram

### 4.2 Power management

The BMP581 has two separate power supply pins:

- ▶ VDD is the main power supply for all internal analog and digital regulator blocks

- ▶ VDDIO is a separate power supply pin, used for the supply of the digital interface

VDD and VDDIO pins can be energized in any order. A power-on reset generator is built in which resets the logic circuitry and the register values after the power-on sequence. The slope for ramp up time must be within the limits given by t\_- VDDramp and t\_VDDIOramp. After powering up, the sensor settles in standby mode (see also 3.3.9").

Holding any interface pin (SDI, SDO, SCK or CSB) at a logical high level when VDDIO is switched off can permanently damage the device due caused by excessive current flow through the ESD protection diodes.

#### 4.3 Power modes

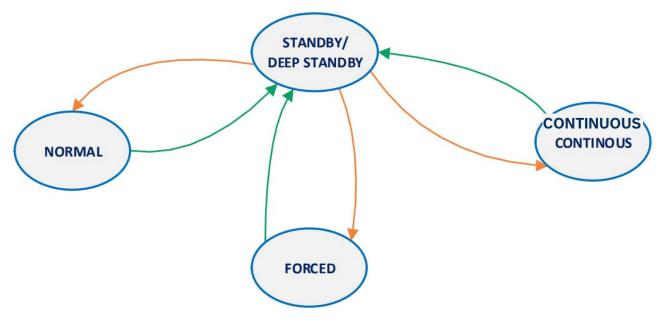

The power modes of BMP581 and transitions in between are depicted in Figure 2. After startup or soft-reset, the BMP581 will be in DEEP STANDBY mode. Transitions from one mode to another are only possible by entering Standby mode first.

Figure 2: Power modes diagram

#### 4.3.1 STANDBY mode

In STANDBY mode, no measurements are performed and power consumption is at a minimum. All registers are accessible for write and read. Mode transitions to other modes are possible. The pressure and temperature data registers PRESS\_DATA\_XXX and TEMP\_DATA\_XXX keep the values of the last measurement executed. The FIFO. if enabled, also maintains it's content and can be read.

#### 4.3.2 DEEP STANDBY

In order to further reduce the power consumption further, the BMP581 offers a DEEP\_STANDBY mode. In this case, power consumption is even lower than in STANDBY mode.

DEEP STANDBY will only be entered if also the following conditions apply:

- ► ODR\_CONFIG.deep\_dis = 0

- ► ODR\_CONFIG.odr < 5Hz

- ► FIFO\_SEL.fifo\_frame\_sel = DIS

- ► DSP\_IIR.set\_iir\_t = BYPASS

- ► DSP\_IIR.set\_iir\_p = BYPASS

If one of these settings is changed, the BMP581 transitions to STANDBY mode.

#### 4.3.3 FORCED mode

In FORCED mode, a single measurement is performed according to selected measurement and filter options. When the measurement is finished, the sensor returns to standby mode and the measurement results can be obtained from the data registers. For a next measurement, forced mode needs to be selected again. Forced mode is recommended for applications which require very low sampling rate or host-based synchronization. Forced mode may also be used if an ODR higher than 240 Hz is needed.

#### 4.3.4 NORMAL mode

Normal mode performs pressure measurements with a configurable frequency, which is the output data rate (ODR). The ODR can be set in ODR\_CONFIG.odr. Normal mode continuously cycles between an (active) measurement period and an (inactive) standby period. In normal mode, the most recent measurement result can be directly obtained from the data registers. Alternatively, the latest measurement results can be obtained from the FIFO.

Normal mode is recommended if pressure needs to be sampled in regular intervals, but none of the conditions apply where FORCED and CONTINUOUS mode may be favorable.

The ODR\_CONFIG.odr register field is used to define the output data rate (ODR) if the BMP581. Data rates of 0.125Hz up to 240 can be selected. For the full list of available ODRs, see the register description. Not all combinations of OSR and ODRs are valid, as measurement times may not fit into an ODR cycle. Table 7: maximum nominal ODR setting per OSR settings in NORMAL modeshows the maximum ODR for a given ODR setting.

| max  | ODR |        | OSR_T  |        |        |        |        |       |       |  |  |  |

|------|-----|--------|--------|--------|--------|--------|--------|-------|-------|--|--|--|

| [Hz] |     | 1      | 2      | 4      | 8      | 16     | 32     | 64    | 128   |  |  |  |

|      | 1   | 240.00 | 240.00 | 240.00 | 240.00 | 200.00 | 130.00 | 80.00 | 40.00 |  |  |  |

|      | 2   | 240.00 | 240.00 | 240.00 | 220.00 | 180.00 | 120.00 | 70.00 | 40.00 |  |  |  |

| _    | 4   | 220.00 | 220.00 | 200.00 | 180.00 | 140.00 | 100.00 | 70.00 | 40.00 |  |  |  |

| ايم  | 8   | 140.00 | 140.00 | 130.00 | 120.00 | 100.00 | 80.00  | 50.00 | 35.00 |  |  |  |

| 08   | 16  | 80.00  | 80.00  | 80.00  | 70.00  | 70.00  | 50.00  | 45.00 | 30.00 |  |  |  |

|      | 32  | 45.00  | 45.00  | 40.00  | 40.00  | 40.00  | 35.00  | 30.00 | 20.00 |  |  |  |

|      | 64  | 20.00  | 20.00  | 20.00  | 20.00  | 20.00  | 20.00  | 15.00 | 15.00 |  |  |  |

|      | 128 | 10.00  | 10.00  | 10.00  | 10.00  | 10.00  | 10.00  | 10.00 | 5.00  |  |  |  |

Table 7: maximum nominal ODR setting per OSR settings in NORMAL mode

Table 8: Maximum nominal ODR setting per OSR settings in NORMAL mode for temperature only measurements

| max ODR |        | OSR_T  |        |        |        |        |       |       |  |

|---------|--------|--------|--------|--------|--------|--------|-------|-------|--|

| [Hz]    | 1      | 2      | 4      | 8      | 16     | 32     | 64    | 128   |  |

|         | 240.00 | 240.00 | 240.00 | 240.00 | 200.00 | 130.00 | 80.00 | 40.00 |  |

|         |        |        |        |        |        |        |       |       |  |

Configuration Check. BMP581 has an automatic configuration checking, which is functional in NORMAL mode and when both temperature and pressure measurements are enabled. If a configuration is not valid, this will be indicated by the OSR\_EFF.odr\_is\_valid register field. If a measurement with an invalid setting is started, the BMP581 will run with the specified ODR, but use a default setting for the ODRs:

- ► For ODRs ≥ 160Hz, both OSRs will be set to 1

- ▶ For all ODRs <160Hz, both OSRs will be set to 2

The effective ODRs are available in the register fields OSR\_EFF.osr\_t\_eff and OSR\_EFF.osr\_p\_eff. This action of alignment and check is done in NORMAL mode only.

#### 4.3.5 Low Power NORMAL mode

If the conditions for deep standby apply, as described in 3.3.1 above, then NORMAL mode will automatically apply DEEP\_STANDY phase in between the measurements. This reduces power consumption even further. If one of these settings is changed, the BMP581 transitions back to NORMAL mode.

#### 4.3.6 CONTINUOUS mode

Continuous mode performs pressure measurements simular to NORMAL mode. However, the ODR setting is ignored. Sampling is performed with the maximum frequency that is possible with the selected oversampling settings. CONTINUOUS mode stays in the (active) measurement period and does not cycle to a standby period. The resulting

ODR is not necessarily a value that is selectable via the ODR register. The resulting ODRs for the recommended OSR settings are shown in Table 9.

#### 4.3.7 Mode transitions

To go in STANDBY status the user must write ODR\_CONFIG.pwr\_mode = 0b00. The maximum transition time to STANDBY is t<sub>standby</sub>. The effective status of the device is always observable reading back the same register. After a commanded switch to standby, the user either needs to wait for t<sub>standby</sub> or check the status register for a successful switch, before he can command the device to go to another mode, and before writing to any of the registers named in 3.3.8.

From STANDBY, it can be switched to CONTINUOS, FORCED or NORMAL mode by writing ODR\_CONFIG.pwr\_mode register. Directly after the transition to an active mode, the first measurement will be performed. It is recommended to set the desired measurement configuration, before switching the mode.

## 4.3.8 Mode-depending register write restrictions

A number of registers and register fields can only be updated when the device is in STANDBY mode. These are for example the registers for NVM operations (see 3.8), but also configuration registers for the FIFO and IIR configuration. The register descriptions state if this limitation applies to a register field. Write operations to these registers in a mode other than STANDBY are lost. It is generally recommended to write configurations before switching into the measurement mode.

## 4.3.9 Post-power-up procedure

After power up of the BMP581, it is available after t\_powerup. The host should not initiate any communication with the BMP581 before. Depending on the interface configuration, a dummy read should be the first access to the device (see 4.1).

It is recommended that the host checks the following status registers after a power-up:

- ▶ read out the CHIP\_ID register and check that it is not all 0

- ▶ read out the STATUS register and check that status\_nvm\_rdy==1, status\_nvm\_err == 0

- ▶ read out the INT\_STATUS.por register field and check that it is set to 1; that means INT\_STATUS==0x10

#### 4.3.10 Soft reset

BMP581 can be reset by writing 0xB6 to the CMD register. The BMP581 will come out of the reset after  $t_{soft\_res.}$  Softreset must not be triggered during a NVM user programming sequence.

#### 4.4 Measurements

#### 4.4.1 Pressure and temperature measurement enable

The BMP581 can either measure temperature only, or both temperature and pressure. Pressure-only measurement is not supported, as temperature data is needed for the temperature compensation of the pressure data.<sup>4</sup>

Pressure and temperature will be measured if any of these conditions is true:

- ► OSR\_CONFIG.press\_en ==1, or

- ► FIFO SEL.fifo frame sel == 0b10, or

- ► FIFO\_SEL.fifo\_frame\_sel == 0b11

If none of these settings is made, the sensor will measure temperature only.

<sup>&</sup>lt;sup>4</sup> However, the sensor can be configured to output the pressure only data to the FIFO, see Chapter 3.6.1

### 4.4.2 Pressure and temperature oversampling ratio (OSR)

Oversampling extends the measurement time per measurement by the oversampling factor. Higher oversampling factors offer decreased noise at the cost of higher power consumption.

Oversampling can be set individually for pressure and temperature in register fields OSR\_CONFIG.osr\_p and OSR\_CONFIG.osr\_t. The duration of the sampling phase, is given by  $t_{conv_p}$  and  $t_{conv_t}$ . Table 7: maximum nominal ODR setting per OSR settings in NORMAL mode shows the maximum ODR for each oversampling setting. Recommended settings are shown in Table 9: Oversampling settings .

| Oversampling setting | osr_p | Pressure     | Temperature  | Typical   | Typical ODR in |

|----------------------|-------|--------------|--------------|-----------|----------------|

|                      |       | oversampling | oversampling | pressure  | CONTINUOUS     |

|                      |       |              |              | RMS noise | mode           |

|                      |       |              |              | at 100kPa |                |

| Lowest power         | 000   | ×1           | ×1           | 0.78 Pa   | 498 Hz         |

|                      | 001   | ×2           | ×1           | 0.58 Pa   | 374 Hz         |

| Standard resolution  | 010   | ×4           | ×1           | 0.41 Pa   | 255 Hz         |

|                      | 011   | ×8           | ×1           | 0.30 Pa   | 155 Hz         |

| High resolution      | 100   | ×16          | ×1           | 0.21 Pa   | 87 Hz          |

|                      | 101   | ×32          | ×2           | 0.15 Pa   | 46 Hz          |

|                      | 110   | ×64          | ×4           | 0.11 Pa   | 24 Hz          |

| Highest resolution   | 111   | ×128         | ×8           | 0.08 Pa   | 12 Hz          |

Table 9: Oversampling settings

*Note:* The noise values refer to the sensor-intrinsic noise. Already at standard resolution, the noise or fluctuations of the air pressure itself may be higher than the noise of the sensor, and thus be dominant. This ambient noise is typically stronger at lower frequencies. Any increase of the ODR does not reduce this type of noise, because this frequency range is of interest for many applications and thus is not attenuated by the sensor. If low frequency noise is a problem in a use case, it is recommended to employ low pass filtering, for example by using the build-in IIR-filter.

#### 4.4.3 Configuration changes in NORMAL and CONTINUOUS mode

If any of these changes is applied during NORMAL and CONTINUOUS mode:

- ► OSR\_CONFIG.press\_en

- ► OSR\_CONFIG.osr\_t

- ► OSR\_CONFIG.osr\_p

- ► ODR CONFIG.odr (NORMAL mode only)

Measurements will restart with the new settings after  $t_{reconf}$ . If DEEP\_STANDBY is enabled in NORMAL mode, it will start after  $t_{reconf\_deep}$ .

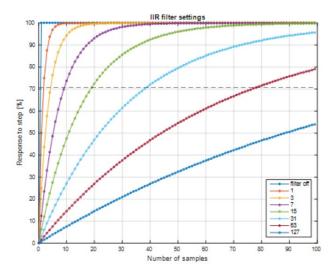

#### 4.4.4 IIR filter

The BMP581 has a dedicated IIR filter built-in, that can be used to reduce noise caused by ambient disturbances. This may for example be the opening of doors or windows, or wind blowing into the sensor. To suppress these disturbances in the output data, the IIR filter can be enabled.

Please note that IIR filtering, like all low pass filtering, also reduces the bandwidth of the signal.

The filter function is the following:

$$data_n = \frac{data_{n-1} \times filtercoefficient + data_{in}}{filtercoefficient + 1}$$

where  $data_{n-1}$  is the filtered data from the previous acquisition, and  $data_{in}$  is the unfiltered data from the current acquisition.

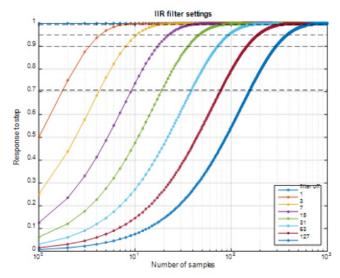

The step response of different filter settings is displayed in Figure 3 and Figure 4. Table 9 shows the available filter coefficient settings and the according normalized bandwidth (which corresponds to the 3dB cutoff frequency). The resulting bandwidth in Hz can be computed as follows:

$bandwidth_{Hz} = ODR_{Hz} x bandwidth_{normalized}$

Figure 3: Step response at different IIR filter settings

Figure 4: Step response at different IIR filter settings on log scale and different threshold limits in dashed lines (3dB, 90%, 95%, 99.5%, 100%)

| Pagistar value | Filter      | Normalized bandwidth ( |

|----------------|-------------|------------------------|

| Register value | coefficient | -3db cutoff frequency) |

| 0x0            | 0           | Bypass                 |

| 0x1            | 1           | 0.1147                 |

| 0x2            | 3           | 0.0459                 |

| 0x3            | 7           | 0.0212                 |

| 0x4            | 15          | 0.01025                |

| 0x5            | 31          | 0.005041               |

| 0x6            | 63          | 0.00250                |

| 0x7            | 127         | 0.00125                |

Table 10: IIR filter settings and bandwidth

The IIR filter can be independently programmed for temperature and pressure with the fields DSP\_IIR.set\_iir\_t and DSP\_IIR.set\_iir\_p. The value "0x0" is used to bypass the filter. The IIR filter is reset when a transition from standby mode to NORMAL or CONTINUOUS mode occurs. That means that the first measurment value will be the initial content of the filter. A manual reset of the filter, e.g. when using forced mode, can be triggered by asserting the register field DSP\_- CONFIG.iir\_flush\_forced\_en.

- ▶ shdw sel iir t: select source for temperature data register

- ▶ fifo sel iir t: select source for temperature FIFO

- ▶ shdw sel iir p: select source for pressure data register

- ▶ fifo sel iir p: select source for pressure FIFO

- ▶ oor sel iir p: select source for pressure out-of-range interrupt

## 4.5 Data registers

Data from the most recent measurement is present in data registers. The DSP\_CONFIG.swdw\_sel\_iir\_t and DSP\_CONFIG.swdw\_sel\_iir\_t select if IIR-filtered data or unfiltered data is presented in the data registers.

Temperature data is contained in the registers TEMP\_DATA\_MSB, TEMP\_DATA\_LSB, TEMP\_DATA\_XLSB. The registers shall be interpreted in the following way:

$$T[^{\circ}C] = (\frac{\text{TEMP\_DATA\_MSB,TEMP\_DATA\_LSB,TEMP\_DATA\_XLSB}}{2^{16}})$$

Pressure data is contained in the registers PRESS\_DATA\_MSB, PRESS\_DATA\_LSB, PRESS\_DATA\_XLSB. The registers shall be interpreted in the following way:

$$p[Pa] = \left(\frac{PRESS\_DATA\_MSB,PRESS\_DATA\_LSB,PRESS\_DATA\_XLSB}{2^6}\right)$$

In both equations, the divisions can be implemented by a simple and efficient bit-wise right shift operation. To read out data after a conversion, it is strongly recommended to use a burst read and not address every register individually.

#### 4.5.1 Data Shadowing

In normal mode, measurement timing is not necessarily synchronized to readout. This means that new measurement results may become available while the user is reading the results from the previous measurement. In this case, shadowing is performed in order to guarantee data consistency. Shadowing will only work if all data registers are read in a single burst read. Therefore, the user must use burst reads if he does not synchronize data readout with the measurement cycle. Using several independent read commands may result in inconsistent data.

If a new measurement is finished and the data registers are still being read, the new measurement results are transferred into shadow data registers. The content of shadow registers is transferred into data registers as soon as the user ends the burst read, even if not all data registers were read. Reading across several data registers can therefore only be guaranteed to be consistent within one measurement cycle if a single burst read command is used. After the end of the burst read, all user data registers are updated at once with the shadowed data.

## 4.6 FIFO

The BMP581 contains a first-in first-out (FIFO) data buffer. Pressure and temperature data is stored in the FIFO in frames. Each frame contains the data from one measurement. The maximum number of frames depends on which data is stored in the FIFO:

- ▶ 16 frames if both pressure and temperature are stored

- ▶ 32 frames if only pressure or temperature is stored

### 4.6.1 FIFO Configuration

The FIFO frame type is selected by FIFO\_SEL.fifo\_frame\_sel:

- ▶ 0b00: FIFO not enabled

- ▶ 0b01: Only Temperature data is stored (T-mode)

- ▶ 0b10: Only Pressure data is stored (P-mode)

- ▶ 0b11: Pressure and temperature data is stored (PT-mode)

The operational mode can be controlled via the FIFO\_CONFIG.cfg\_fifo\_mode register:

- ▶ 1'b0: streaming mode

- ▶ 1'b1: stop on full mode

The two modes differ in how the FIFO reacts to an overflow. A FIFO overflow occurs if the FIFO is full and a new measurement data is ready to be written to the FIFO. In streaming mode, the FIFO will delete the oldest frame, and write the new frame to the FIFO. As a result, the FIFO contains always the most recent frames.<sup>5</sup>

In stop-on-full mode, frames once written to the FIFO will not be discarded. Instead, new frames will not be written to the FIFO until there is space again.

**The FIFO decimation factor** (or downsampling) can be adjusted With FIFO\_SEL.cfg\_fifo\_dec\_sel. Only every n-th sample will be written to the FIFO, where:

$$n = 2^{FIFO}_{SEL.cfg_fifo_dec_sel}$$

**The FIFO threshold** can be set by FIFO\_CONFIG\_fifo\_threshold. If the fill level of the FIFO reaches the threshold, the FIFO threshold interrupt may be triggered (see Chapter 3.7.2.1). The meaning of the register field is the following:

- ▶ 0x00: FIFO threshold disablef

- ▶ 0x01..0x1F (or 1..31 decimal): threshold level

- ▶ 0x0F: 15 frames. This is the maximum setting in PT-mode. The most significant bit is ignored.

- ▶ 0x1F: 31 frames. This is the maximum setting in P- or T-mode.

#### 4.6.2 FIFO status

The fill level of the FIFO in number of frames can be obtained from FIFO\_COUNT.fifo\_count. FIFO watermark and FIFO full information can be obtain from the interrupt functionality (see Chapter 3.7.2.1).

## 4.6.3 FIFO data readout

The FIFO can be read out by reading in a burst from register FIFO\_DATA.

Reads should be performed in the granularity of the frame size (24 or 48 bit) according to the selected frame type. Frames that have been read incompletely will stay in the FIFO memory and will be retransmitted on the next read. The entire FIFO contents can be read in one single burst.

If the FIFO is empty, disabled or turns empty during a read, it will return the empty frame, which is 0x7f.

Table 10,

Table 11 and Table 13 show the frame formats for the three different frame kinds: PT, T and P. The empty frame is shown in Table 13.

Table 11: FIFO pressure and temperature frame (PT-fram

|             | 7               | 6               | 5 | 4         | 3        | 2 | 1 | 0 |  |  |  |

|-------------|-----------------|-----------------|---|-----------|----------|---|---|---|--|--|--|

| Temperature |                 |                 |   | temperatu | ıre XLSB |   |   |   |  |  |  |

|             |                 | temperature LSB |   |           |          |   |   |   |  |  |  |

|             | temperature MSB |                 |   |           |          |   |   |   |  |  |  |

| Pressure    |                 | pressure XLSB   |   |           |          |   |   |   |  |  |  |

|             |                 |                 |   | press     | LSB      |   |   |   |  |  |  |

<sup>2.</sup> In order to work properly, streaming mode requires that the clock frequency of host interface is 0.1MHz or above. Otherwise, the FIFO readout bandwidth could be slower than the FIFO write bandwidth, which will cause data loss.

|  | press MSB  |

|--|------------|

|  | DIESS WISD |

## Table 12: FIFO temperature frame (T-frame)

|             | 7 | 6               | 5 | 4         | 3        | 2 | 1 | 0 |  |  |  |

|-------------|---|-----------------|---|-----------|----------|---|---|---|--|--|--|

| Temperature |   |                 |   | temperatu | ire XLSB |   |   |   |  |  |  |

|             |   | temperature LSB |   |           |          |   |   |   |  |  |  |

|             |   | temperature MSB |   |           |          |   |   |   |  |  |  |

## Table 13: FIFO pressure frame (P-frame)

|          | 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|----------|---|---------------|---|---|---|---|---|---|--|--|--|

| Pressure |   | pressure XLSB |   |   |   |   |   |   |  |  |  |

|          |   | press LSB     |   |   |   |   |   |   |  |  |  |

|          |   | press MSB     |   |   |   |   |   |   |  |  |  |

## Table 14: FIFO empty frame

|       | 7 | 6 | 5 | 4   | 3 | 2 | 1 | 0 |

|-------|---|---|---|-----|---|---|---|---|

| Empty |   |   |   | 0x7 |   |   |   |   |

### 4.6.4 FIFO configuration changes

The FIFO is flushed on any of the following conditions:

- ▶ a change in the sensor configuration:

- OSR\_CONFIG.osr\_t

- OSR\_CONFIG.osr\_p

- o ODR\_CONFIG.odr

- o ODR\_CONFIG.pwr\_mode

- ▶ a change in the frame configuration:

- FIFO\_SEL.fifo\_frame\_sel

- FIFO\_SEL.cfg\_fifo\_dec\_sel

The flush will empty the FIFO, reset the FIFO COUNT register, and clear the interrupt conditions.

The completion of the FIFO flush is finished within t<sub>reconf</sub>, or t<sub>reconf\_deep</sub> if the device is in deep standby. The FIFO COUNT should not be read before the flush has been finished, as the result may be inconsistent.

If the register FIFO\_CONFIG\_fifo\_threshold is written, the resulting interrupt status bits will be immediately updated according to the new threshold.

The register FIFO SEL must only be changed in STANDBY mode.

A change of FIFO\_SEL.cfg\_fifo\_dec\_sel during NORMAL or CONTINUOUS mode will only be applied after a transition to STANDBY. It will also not flush the FIFO.

A change of FIFO\_SEL.fifo\_frame\_sel during NORMAL or CONTINUOUS mode may be ignored as well, depending on if the press\_en bit is also changed.

### 4.7 Interrupts

The BMP581 provides an interrupt pin (INT), which allows to signal certain events to the host processor. Different events can be mapped to the interrupt pin, which all are processed with a logical OR.

BMP581 also supports I3C's in-band interrupt (IBI). This is allows the use of interrupt functionality without the need of a dedicated INT signal line. For documentation of the I3C IBI functionality, see Chapter 4.7.2 "I3C In-band Interrupts".

The available interrupts are listed below, and will be detailed in following subsections:

- ► FIFO watermark interrupt

- ► FIFO full interrupt

- ► Data ready interrupt

- ▶ Pressure out-of-range interrupt

- ▶ Power-on reset (POR) interrupt

#### 4.7.1 Interrupt enabling

The individual interrupts sources can be enabled in the INT\_SOURCE register. An exception is the POR interrupt, which is always enabled. With enabled interrupt sources:

- ▶ their individual status is available from the INT\_STATUS register,

- ▶ I3C in-band interrupts can be used (see Chapter 4.7.2 "I3C In-band Interrupts"), and

- ▶ the interrupt pin can be used, see Chapter 3.7.3.

#### 4.7.2 Interrupt sources

## 4.7.2.1 FIFO interrupts

The FIFO provides two sources of interrupts:

- ▶ FIFO full: The fill level is at the maximum number of frames. This means 16 PT frames or 32 P or T frames, depending on the configuration of the FIFO.

- ▶ FIFO threshold reached: The fill level is at or above the FIFO threshold level (see Chapter 3.6.1).

Both interrupts will be asserted at the end of a measurement (when data is ready), when the respective condition is fulfilled. They will stay asserted as long as the corresponding condition is active. A read of the INT\_STATUS register will not change the FIFO interrupts. FIFO interrupts can only occur if the FIFO is enabled.

If a burst read from the FIFO causes the fill level to drop below the fill level that causes an interrupt, the interrupt will be deasserted at the end of the burst read.

The FIFO interrupts can be enabled by setting INT\_SOURCE.fifo\_full\_en and INT\_SOURCE.fifo\_ths\_en.

## 4.7.2.2 Data ready interrupt

The data ready interrupt and status register INT\_STATUS.drdy\_data\_reg is asserted when new pressure and/or temperature is available in the data registers (see Chapter 3.5 "Data registers"). Also, the new measurement data is available in the FIFO after the data ready interrupt.

The interrupt can be enabled by setting INT\_SOURCE.drdy\_data\_reg\_en.

### 4.7.2.3 Out-of-range interrupt

The out-of-range (OOR) interrupt is triggered when the pressure value is outside a defined range for a defined number of samples.

The benefit of this interrupt is that the host system does not need to read the sensor data continuously to detect of there is a significant change of the measured pressure. Instead the host can configure the interrupt, und read sensor data only if the interrupt triggered.

For the OOR interrupt, the BMP581 checks if the pressure value is within a window around a reference pressure. The reference pressure can be defined in [Pa] with a width of 17 bit, which covers the complete measurement range of the sensor. The reference values can be written by access the register fields OOR\_CONFIG.oor\_thr\_p\_16, OOR\_THR\_P\_MSB.oor\_thr\_p\_15\_8 and OOR\_THR\_P\_LSB.oor\_thr\_p\_7\_0.

The range is also given in [Pa] and can be defined via the register OOR\_RANGE.oor\_range\_p. As the register has a width of 8bit, the range can span up to +/- 255 Pa around the reference value.

The OOR is out of range if observed pressure P\_Pa in is:

$P_Pa > reference + window$

or

$P_Pa < referenc - window$

If one of these conditions is satisfied for the number of samples defined by OOR\_CONFIG.cnt\_lim, the interrupt will be triggered.

If subsequent measurements are still out of range, the interrupt will be re-triggered after each of those measurements.

**Example.** Assumed the user wants to get an interrupt if the pressure is outside the range of 97100 Pa - 97200 Pa. In this case, the reference should be set to the middle value 97150 Pa, which is 0x17B7E. The window value is half of the range, which is 50 Pa, or 0x32. This means that the registers need to be set to the following values:

- ► OOR CONFIG.oor thr p 16 = 0x1

- ► OOR\_THR\_P\_MSB.oor\_thr\_p\_15\_8 = 0x7B

- ► OOR THR P LSB.oor thr p 7 0 = 0x7E

- ▶ OOR\_RANGE.oor\_range\_p = 0x32

### 4.7.2.4 Power-on reset interrupt

The power-on rest (POR) interrupt is triggered each time the BMP581 comes out of a power-up reset. This can happen if the supply to the device is ramped up, or if the supply was so instable that the BMP581 performed a brown-out with subsequent power-up reset. The POR interrupt signals that the BMP581 is ready to use.

POR interrupts are not supported with I3C IBI, as the device is not in a state where I3C is initialized after power-up reset. Also, the interrupt pin will not flag an POR interrupt, as the interrupt pin is disabled after power-up. The status of the interrupt can be read from INT STATUS.por. A read of the INT STATUS will clear the status.

#### 4.7.3 Interrupt pin

The BMP581 provides an interrupt pin (INT), which allows to signal certain events to the host processor.

### 4.7.3.1 Interrupt pin configuration

The behavior of the interrupt pin can be configured in INT\_CONFIG with these fields:

- ▶ int\_mode: The interrupt mode can be "pulsed" or "latched". Latching determines when an interrupt is released (see Chapter 3.7.3.2 for details)

- int\_pol: The interrupt polarity can be configured to be either "active high" or "active low"

- int\_od: The interrupt pin can be configured to be "open-drain" or push-pull"

- ▶ int\_en: The interrupt pin can be enabled. With enabled interrupt pin, all interrupt sources configured in INT\_-SOURCE will be ORed on the interrupt pin.

## 4.7.3.2 Interrupt Timings

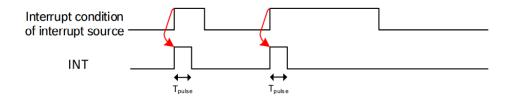

Interrupt timings depend strongly on the int\_mode setting:

**Pulsed mode.** In the pulsed mode the INT pin creates a pulse on the interrupt pin, each time an interrupt condition changes from FALSE to TRUE, and the interrupt source is enabled in INT\_SOURCE. Figure 5 shows the timing of pulsed mode.

The pulse length is t<sub>int\_pulse</sub>. Between two pulses, there is a minimum gap of t<sub>int\_deassert</sub> in which the pin will stay deasserted.

Figure 5: INT pin timing in pulsed mode

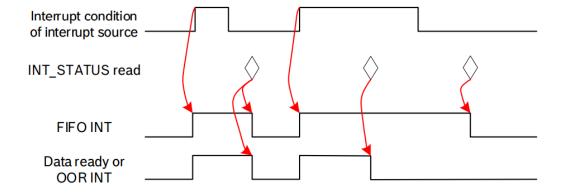

**Latched Mode.** In latched mode, the INT pin is asserted as long as an interrupt condition is TRUE, and the interrupt source is enabled in INT\_SOURCE. Between two adjacent assertions if the INT pin, there is a minimum gap of t<sub>int deassert</sub>. Figure 6 shows the timing of latched mode.

The deassertion of the INT pin in latched mode depends is handled in the following way:

- ► FIFO interrupts will be de-asserted when the interrupt condition does not apply any more. There is no dependency on the setting of INT STATUS.

- ▶ The data ready interrupt will be de-assered after reading the INT\_STATUS.

- ▶ The pressure out-of-range interrupt will be de-assered after reading the INT\_STATUS. If the data ready interrupt is asserted, a new measurement data becomes available, the INT pin will stay asserted. There is no de-assertion phase.

Figure 6: INT pin timing in latched mode

Exceptions. In the following cases, the minimal pulse length and minimal gap between pulses may be violated:

- ▶ If the FIFO gets disabled or is flushed (see Chapter 3.6.4 "FIFO configuration changes" for a description of the conditions that cause a FIFO flush), an asserted FIFO interrupt will be de-asserted immediately and the corresponding bits in INT\_STATUS will be cleared. This may cause a violation of tint\_pulse or tint\_deassert.

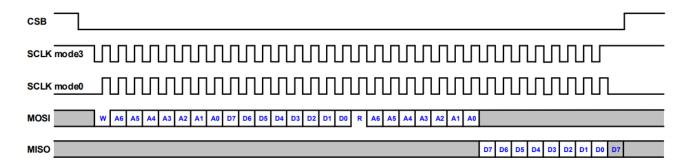

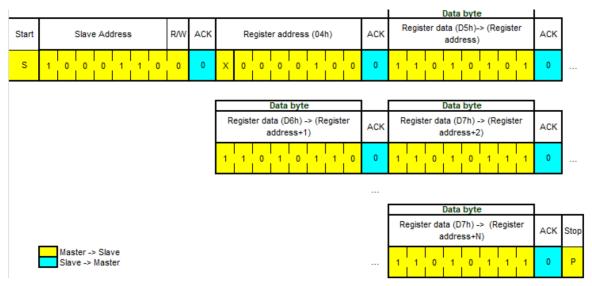

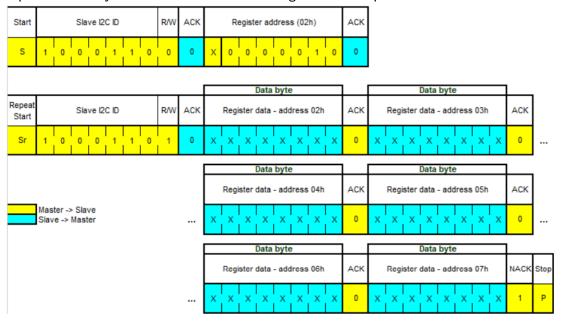

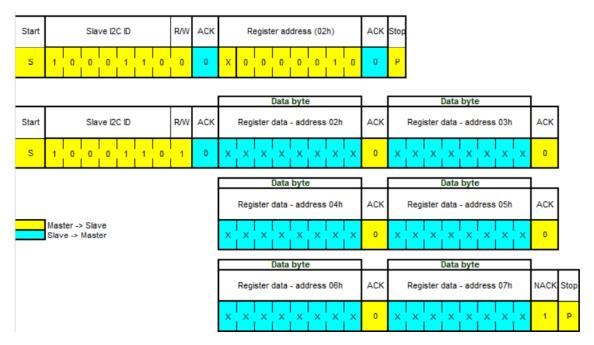

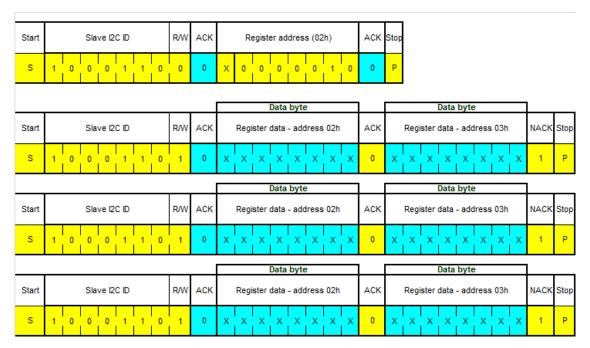

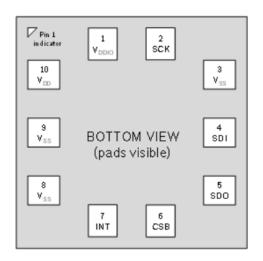

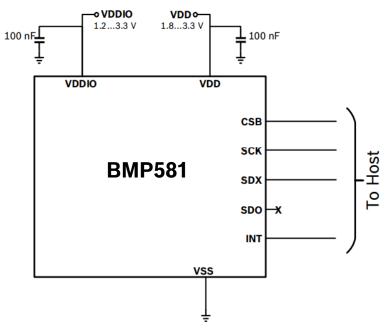

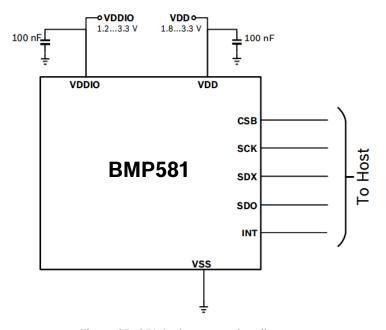

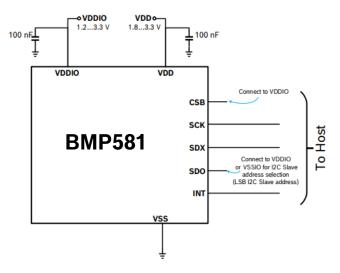

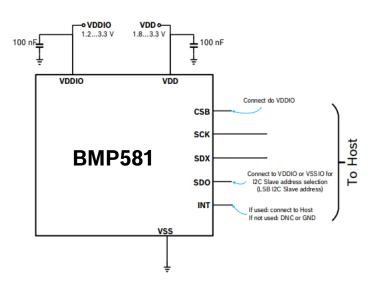

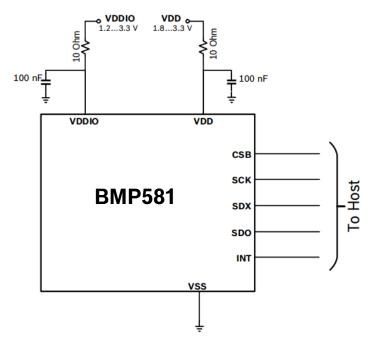

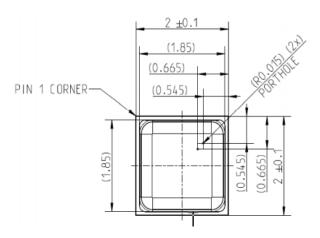

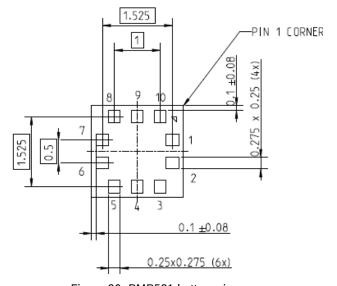

- ▶ If the conditions apply that would cause a FIFO flush, the behavior of an asserted out-of-range interrupt is the same as for the FIFO interrupt desribed above: the asserted interrupt will be de-asserted immediately and the corresponding bits in INT\_STATUS will be cleared. This may cause a violation of t<sub>int\_pulse</sub> or t<sub>int\_deassert</sub>.