# SHARC+ Single Core High Performance DSP (Up to 1 GHz)

### **Preliminary Technical Data**

### ADSP-21560/21561/21564/21568

#### **SYSTEM FEATURES**

Enhanced SHARC+ high performance floating-point core

Up to 1 GHz

5 Mb (640 kB) Level 1 (L1) SRAM memory with parity (optional ability to configure as cache)

32-bit, 40-bit, and 64-bit floating-point support 32-bit fixed point

Byte, short word, word, long word addressed

**Powerful DMA system**

**On-chip memory protection**

**Integrated safety features**

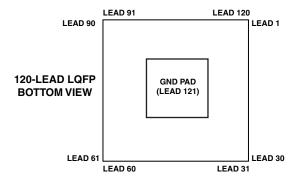

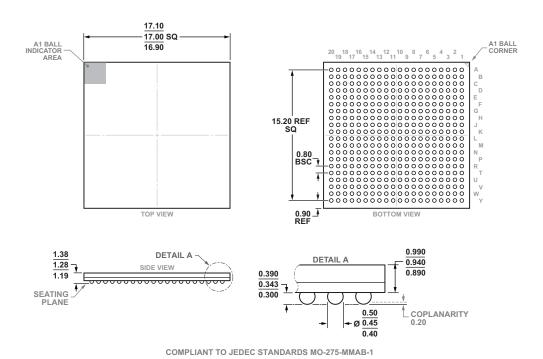

17 mm  $\times$  17 mm, 400-ball CSP\_BGA (0.8 mm pitch), RoHS compliant

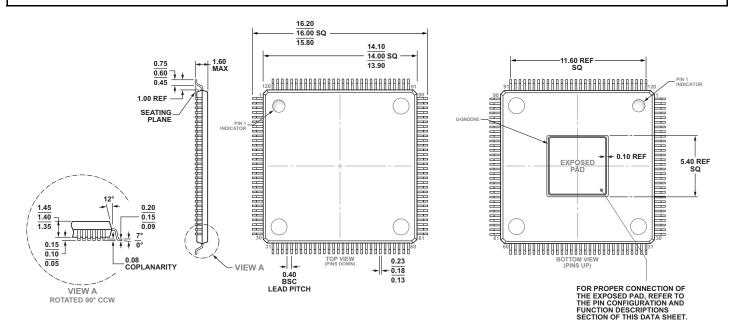

120-lead LQFP\_EP (0.4 mm pitch), RoHS compliant Low system power across automotive temperature range 3.3 V I/O with no power sequencing requirement

#### **MEMORY**

Large on-chip Level 2 (L2) SRAM with parity, up to 16 Mb (2 MB)

xSPI peripheral supports HyperBus connectivity to extend system memory

#### **ADDITIONAL FEATURES**

**Security and Protection**

Crypto hardware accelerators

Fast secure boot with IP protection

Enhanced FIR and IIR accelerators running up to 1 GHz

#### **APPLICATIONS**

Automotive: audio amplifier, head unit, ANC/RNC, rear seat entertainment, digital cockpit, ADAS

Consumer: speakers, sound bars, AVRs, conferencing systems, mixing consoles, microphone arrays, headphones

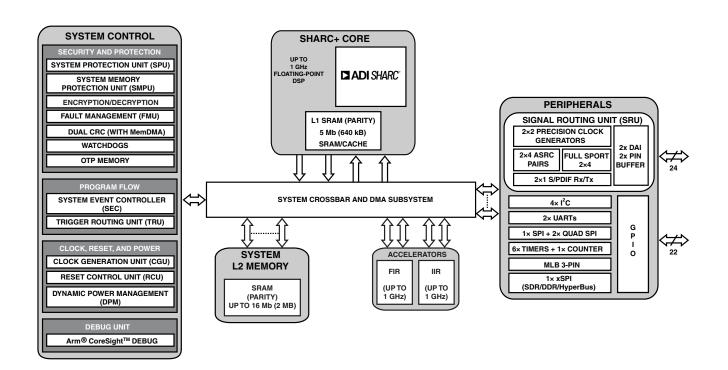

Figure 1. Processor Block Diagram

SHARC, SHARC+, and the SHARC logo are registered trademarks of Analog Devices, Inc.

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## **Preliminary Technical Data**

### **TABLE OF CONTENTS**

| System reatures                                                                   | ADSP-21500/21501/21504/21508 Designer Quick              |    |

|-----------------------------------------------------------------------------------|----------------------------------------------------------|----|

| Memory                                                                            | Reference                                                |    |

| Additional Features                                                               | Preliminary Specifications                               |    |

| Applications                                                                      | Preliminary Operating Conditions                         |    |

| Table of Contents                                                                 | Preliminary Electrical Characteristics                   | 33 |

| Revision History                                                                  | Absolute Maximum Ratings                                 | 36 |

| General Description                                                               | ESD Caution                                              | 36 |

| SHARC Processor                                                                   | Preliminary Timing Specifications                        | 37 |

| SHARC+ Core Architecture 6                                                        | Output Drive Currents                                    | 67 |

| System Infrastructure                                                             | Test Conditions                                          | 67 |

| System Memory Map 8                                                               | Environmental Conditions                                 | 68 |

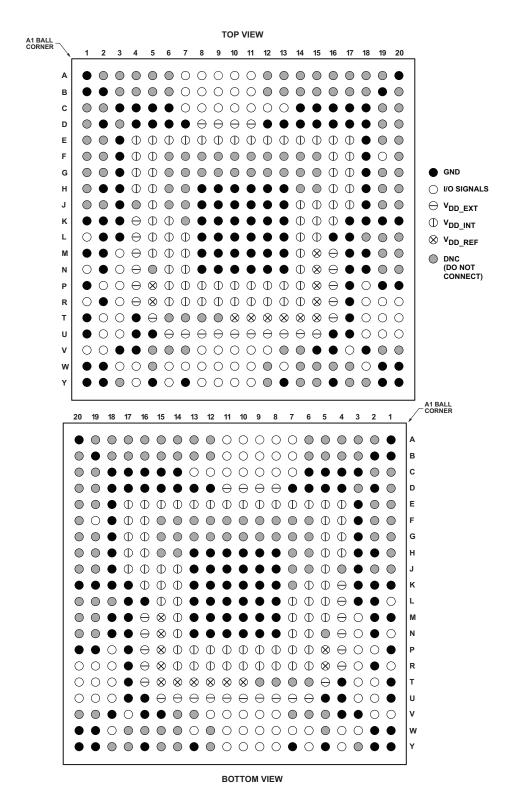

| Security Features                                                                 | ADSP-21568 400-Ball CSP_BGA Ball Assignments             | 69 |

| Security Features Disclaimer                                                      | Numerical by Ball Number                                 | 69 |

| Safety Features                                                                   | Alphabetical by Pin Name                                 | 72 |

| Processor Peripherals                                                             | Configuration of the 400-Ball CSP_BGA                    | 75 |

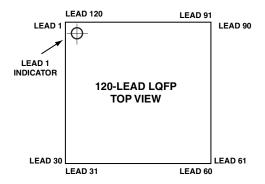

| System Acceleration                                                               | ADSP-21560/21561/21564 120-Lead LQFP Lead<br>Assignments | 76 |

| System Design                                                                     | Numerical by Lead Number                                 | 76 |

| System Debug                                                                      | Alphabetical by Pin Name                                 | 77 |

| Development Tools                                                                 | Configuration of the 120-Lead LQFP Lead                  |    |

| Additional Information                                                            | Configuration                                            | 78 |

| Related Signal Chains                                                             | Outline Dimensions                                       | 79 |

| ADSP-21560/21561/21564/21568 Detailed Signal Descriptions                         | Surface-Mount Design                                     | 80 |

| •                                                                                 | Planned Automotive Production Products                   | 81 |

| Signal Descriptions                                                               | Planned Production Products                              | 81 |

| GPIO Multiplexing                                                                 | Pre Release Products                                     | 81 |

| REVISION HISTORY                                                                  |                                                          |    |

| 3/2025—Rev. PrC to Rev. PrD                                                       | Changes to xSPI Port—Master Timing                       | 55 |

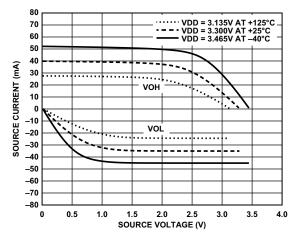

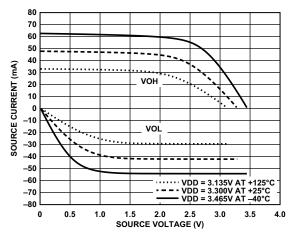

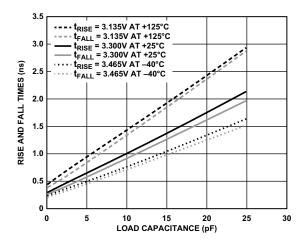

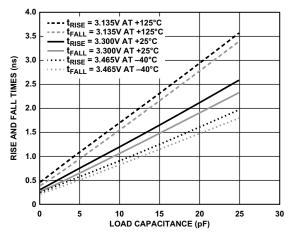

| Changed all processor speeds of 933 MHz to 1 GHz throughout data sheet.           | Updated Figures 35 and 36 in Output Drive Currents       |    |

| Added Internal Timer Signal Routing                                               | Updated Figures 40 and 41 in Capacitive Loading          |    |

| Added missing signals to ADSP-21560/21561/21564/21568                             | Added model to Pre Release Products                      | 81 |

| Designer Quick Reference                                                          |                                                          |    |

| Changes to Preliminary Operating Conditions                                       |                                                          |    |

| Changes to Clock Operating Conditions                                             |                                                          |    |

| Changes to Preliminary Electrical Characteristics 33                              |                                                          |    |

| Changes to I <sub>DD_INT_TOT</sub> equation in Total Internal Power Dissipation   |                                                          |    |

| Added specifications to Tables 16, 17, and 18 in Total Internal Power Dissipation |                                                          |    |

| Changes to Clock Current                                                          |                                                          |    |

### ADSP-21560/21561/21564/21568

### GENERAL DESCRIPTION

Reaching speeds of up to 1 GHz, the ADSP-21560/21561/21564/21568 processors are members of the SHARC® family of products. The ADSP-21560/21561/21564/21568 processors are based on the SHARC+® single core. The ADSP-21560/21561/21564/21568 SHARC processors are members of the SIMD SHARC family of digital signal processors (DSPs) that feature Analog Devices, Inc., Super Harvard Architecture. These 32-bit/40-bit/64-bit floating-point processors are optimized for high performance audio/floating-point applications with large on-chip static random-access memory (SRAM), multiple internal buses that eliminate input/output (I/O) bottlenecks, and innovative digital audio interfaces (DAI).

The SHARC+ core includes cache enhancements and branch prediction, while maintaining instruction set compatibility to previous SHARC products.

By integrating a rich set of industry-leading system peripherals and memory (see Table 1), the SHARC+ processor is the platform of choice for applications that require programmability similar to reduced instruction set computing (RISC), multimedia support, and leading edge signal processing in one integrated package. These applications span a wide array of markets, including automotive, professional audio, and industrial-based applications that require high floating-point performance.

**Table 1. Processor Features**

| Processor Feature                      | ADSP-21560             | ADSP-21561             | ADSP-21564             | ADSP-21568             |

|----------------------------------------|------------------------|------------------------|------------------------|------------------------|

| SHARC+ Core (MHz Maximum) <sup>1</sup> | 600, 800               | 800, 1000              | 800, 1000              | 1000                   |

| SHARC L1 SRAM (kB)                     | 640                    | 640                    | 640                    | 640                    |

| System Memory                          |                        |                        |                        |                        |

| L2 SRAM (kB)                           | 1024                   | 1536                   | 2048                   | 2048                   |

| HyperBus Support via xSPI              | Yes                    | Yes                    | Yes                    | Yes                    |

| DAI (Includes SRU)                     | 2                      | 2                      | 2                      | 2                      |

| Full SPORTs                            | 2×4                    | 2×4                    | 2×4                    | 2×4                    |

| S/PDIF Rx/Tx                           | 2×1                    | 2×1                    | 2×1                    | 2×1                    |

| ASRCs                                  | 2×4                    | 2×4                    | 2×4                    | 2×4                    |

| Precision Clock Generators             | 2×2                    | 2×2                    | 2×2                    | 2×2                    |

| Buffers                                | 2×12                   | 2×12                   | 2×12                   | 2×12                   |

| Hardware Accelerators                  |                        |                        |                        |                        |

| FIR/IIR                                | Yes                    | Yes                    | Yes                    | Yes                    |

| Security Crypto Engine                 | Yes                    | Yes                    | Yes                    | Yes                    |

| I <sup>2</sup> C (TWI)                 | 4                      | 4                      | 4                      | 4                      |

| SPI                                    | 1                      | 1                      | 1                      | 1                      |

| Quad SPI                               | 2                      | 2                      | 2                      | 2                      |

| xSPI                                   | 1                      | 1                      | 1                      | 1                      |

| UARTs                                  | 2                      | 2                      | 2                      | 2                      |

| General-Purpose Timer <sup>2</sup>     | 6                      | 6                      | 6                      | 6                      |

| General-Purpose Counter                | 1                      | 1                      | 1                      | 1                      |

| Watchdog Timer                         | 2                      | 2                      | 2                      | 2                      |

| MLB 3-pin                              | Automotive models only | Automotive models only | Automotive models only | Automotive models only |

| GPIO Ports                             | Port A to Port B       |

| GPIO + DAI Pins                        | 22 + 24                | 22 + 24                | 22 + 24                | 22 + 24                |

| Package Options                        | 120-lead LQFP_EP       | 120-lead LQFP_EP       | 120-lead LQFP_EP       | 400-ball CSP_BGA       |

<sup>&</sup>lt;sup>1</sup>The values refer to different speed grades.

<sup>&</sup>lt;sup>2</sup>Refer to Table 12 for internal timer signal routing.

### **Preliminary Technical Data**

#### **SHARC PROCESSOR**

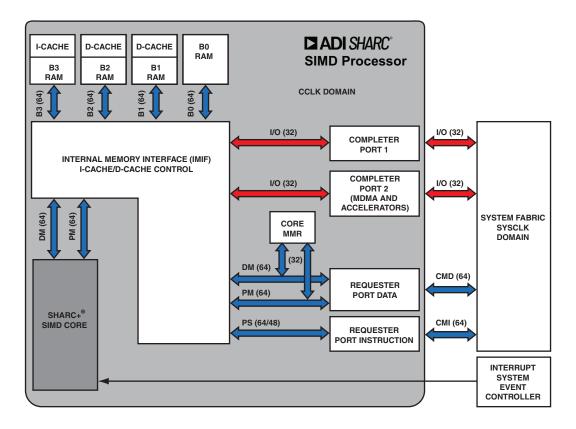

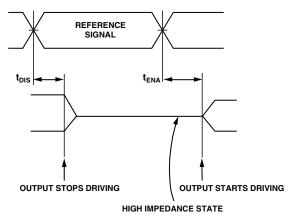

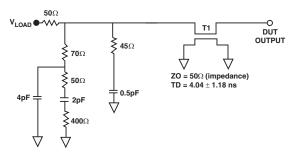

The SHARC processor integrates a SHARC+ SIMD core, L1 memory crossbar, I-cache/D-cache controller, L1 memory blocks, and the requester/completer ports, as shown in Figure 2. The SHARC+ SIMD core block diagram is shown in Figure 3.

The SHARC processor supports a modified Harvard architecture in combination with a hierarchical memory structure. L1 memories typically operate at the full processor speed with little or no latency.

Figure 2. SHARC Processor Block Diagram

#### L1 Memory

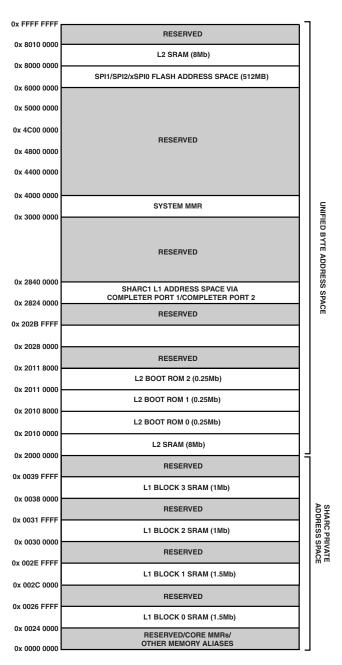

Figure 4 shows the ADSP-21560/21561/21564/21568 memory map. The SHARC+ core has a tightly coupled 5 Mb L1 SRAM. The SHARC+ core can access code and data in a single cycle from this memory space.

In the SHARC+ core private address space, the core has L1 memory.

SHARC+ core memory-mapped register (CMMR) address space is 0x0000 0000 through 0x0003 FFFF in normal word (32-bit). Each block can be configured for different combinations of code and data storage. Of the 5 Mb SRAM, up to 1 Mb can be configured for data memory (DM), program memory (PM), and instruction cache each. Each memory block supports single-cycle, independent accesses by the core processor and I/O processor. The memory architecture, in combination with its separate on-chip buses, allows two data transfers from the core and one from the direct memory access (DMA) engine in a single cycle.

The SRAM of the processor can be configured as a maximum of 160k words of 32-bit data, 320k words of 16-bit data, 106.7k words of 48-bit instructions (or 40-bit data), or combinations of different word sizes up to 5 Mb. All of the memory can be accessed as 8-bit, 16-bit, 32-bit, 48-bit, or 64-bit words. Support of a 16-bit floating-point storage format doubles the amount of data that can be stored on chip.

Conversion between the 32-bit floating-point and 16-bit floating-point formats is performed in a single instruction. Whereas each memory block can store combinations of code and data, accesses are most efficient when one block stores data using the DM bus for transfers, and the other block stores instructions and data using the PM bus for transfers.

Using the DM and PM buses, with each bus dedicated to a memory block, assures single-cycle execution with two data transfers. In this case, the instruction must be available in the cache. The system configuration is flexible, but a typical configuration is 512 kb DM, 128 kb PM, and 128 kb of instruction

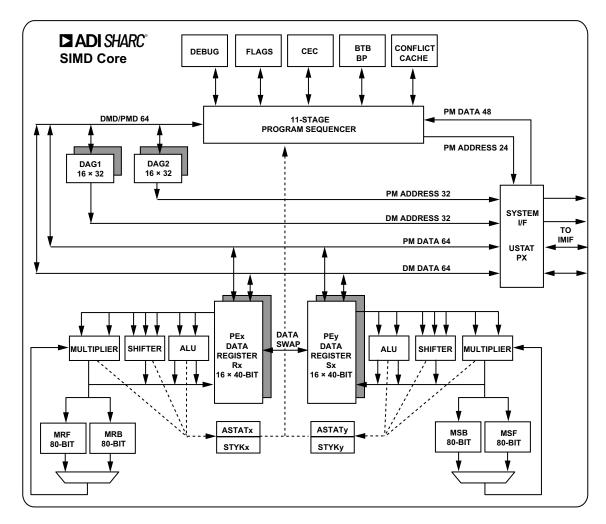

Figure 3. SHARC+ SIMD Core Block Diagram

cache, with the remaining L1 memory configured as SRAM. Each addressable memory space outside the L1 memory can be accessed either directly or via cache.

The memory map in Table 2 gives the L1 memory address space and shows multiple L1 memory blocks offering a configurable mix of SRAM and cache.

### **L1 Requester and Completer Ports**

The SHARC+ core has two requester/completer ports to and from the system fabric. One requester port fetches instructions. The second requester port drives data to the system world. Completer Port 1 together with Completer Port 2 memory direct memory access (high speed MDMA) run conflict free access to the individual memory blocks. For the completer port addresses, refer to the L1 memory address map in Table 2.

### L1 On-Chip Memory Bandwidth

The internal memory architecture allows programs to have four accesses at the same time to any of the four blocks, assuming no block conflicts. The total bandwidth is realized using both the DMD and PMD buses ( $2 \times 64$ -bits CCLK speed and  $2 \times 32$ -bit SYSCLK speed).

#### Instruction and Data Cache

The ADSP-21560/21561/21564/21568 processors also include a traditional instruction cache (I-cache) and two data caches (D-caches, one each for PM/DM) with parity support for all caches. These caches support one instruction access and two data accesses over the DM and PM buses per CCLK cycle. The cache controllers automatically manage the configured L1 memory. The system can configure part of the L1 memory for automatic management by the cache controllers. The sizes of these caches are independently configurable from 0 to 128 kB each. The memory not managed by the cache controllers is directly addressable by the processors. The controllers ensure the data

Figure 4. ADSP-21560/21561/21564/21568 Memory Map

coherence between the two data caches. The caches provide user controllable features such as full and partial locking, range bound invalidation, and flushing.

### **Core Memory-Mapped Registers (CMMR)**

The core memory-mapped registers control the L1 instruction and data cache, branch target buffer (BTB), parity error, system control, debug, and monitor functions.

#### SHARC+ CORE ARCHITECTURE

The ADSP-21560/21561/21564/21568 processors are assembly code compatible with all previous SHARC processors featuring the SHARC or SHARC+ core, beginning with the first generation ADSP-2106x SHARC processors and including the ADSP-2116x, ADSP-2126x, ADSP-213xx, ADSP-214xx, and ADSP-SC5xx/ADSP-215xx processors.

The SIMD architecture featured on the ADSP-21560/21561/21564processors is identical to all previous SIMD SHARC processors, namely the ADSP-2116x, ADSP-2126x, ADSP-213xx, ADSP-214xx, and ADSP-SC5xx/ADSP-215xx processors, as shown in Figure 3 and as described in the following sections.

### Single-Instruction, Multiple Data (SIMD) Computational Engine

The SHARC+ core contains two computational processing elements that operate as a single-instruction, multiple data (SIMD) engine.

The processing elements are referred to as PEx and PEy, each containing an arithmetic logic unit (ALU), multiplier, shifter, and register file. PEx is always active, and PEy is enabled by setting the PEYEN mode bit in the mode control register (MODE1).

SIMD mode allows the processors to execute the same instruction in both processing elements, but each processing element operates on different data. This architecture efficiently executes math intensive DSP algorithms. In addition to all the features of previous generation SHARC cores, the SHARC+ core also provides a new and simpler way to execute an instruction only on the PEy data register.

SIMD mode also doubles the bandwidth between memory and the processing elements, as required for sustained computational operation of two processing elements. When using the data address generators (DAGs) to transfer data in SIMD mode, two data values transfer with each memory or register file

### **Independent Parallel Computation Units**

Within each processing element is a set of pipelined computational units. The computational units consist of a multiplier, an ALU, and a shifter. These units are arranged in parallel, maximizing computational throughput. These computational units support IEEE 32-bit single-precision floating-point; 40-bit extended-precision floating-point; IEEE 64-bit double-precision floating-point; and 32-bit fixed-point data formats.

A multifunction instruction set supports parallel execution of ALU and multiplier operations. In SIMD mode, the parallel ALU and multiplier operations occur in both processing elements per core.

All processing operations take one cycle to complete. For all floating-point operations, the processor takes two cycles to complete in case of data dependency. Double-precision floating-point data take two to six cycles to complete. The processor stalls for the appropriate number of cycles for an interlocked pipeline plus data dependency check.

#### **Core Timer**

The SHARC+ processor core includes an extra timer. This extra timer is clocked by the internal processor clock and is typically used as a system tick clock for generating periodic operating system interrupts.

#### **Data Register File**

Each processing element contains a general-purpose data register file. The register files transfer data between the computation units and the data buses, and store intermediate results. These 10-port, 32-register register files (16 primary, 16 secondary), combined with the enhanced Harvard architecture of the processor, allow unconstrained data flow between computation units and internal memory. The registers in the PEx data register file are referred to as R0–R15 and in the PEy data register file as S0–S15.

#### **Context Switch**

Many of the registers of the processor have secondary registers that can activate during interrupt servicing for a fast context switch. The data, DAG, and multiplier result registers have secondary registers. The primary registers are active at reset, whereas control bits in MODE1 activate the secondary registers.

#### **Universal Registers**

General-purpose tasks use the universal registers. The four universal status (USTAT) registers allow easy bit manipulations (set, clear, toggle, test, XOR) for all control and status peripheral registers.

The data bus exchange register (PX) permits data to pass between the 64-bit PM data bus and the 64-bit DM data bus or between the 40-bit register file and the PM or DM data bus. These registers contain hardware to handle the data width difference.

### Data Address Generators (DAG) With Zero Overhead Hardware Circular Buffer Support

For indirect addressing and implementing circular data buffers in hardware, the ADSP-21560/21561/21564/21568 processors use two data address generators (DAGs). Circular buffers allow efficient programming of delay lines and other data structures required in digital signal processing and are commonly used in digital filters and fast Fourier transforms (FFT). The DAGs contain sufficient registers to allow the creation of up to 32 circular buffers (16 primary register sets and 16 secondary sets). The DAGs automatically handle address pointer wraparound, reduce overhead, increase performance, and simplify implementation. Circular buffers can start and end at any memory location.

#### Flexible Instruction Set Architecture (ISA)

The flexible instruction set architecture (ISA), a 48-bit instruction word, accommodates various parallel operations for concise programming. For example, the processors can conditionally execute a multiply, an add, and a subtract in both processing elements while branching and fetching up to four 32-bit values from memory—all in a single instruction.

### ADSP-21560/21561/21564/21568

Additionally, the double-precision floating-point instruction set is new to the SHARC+ core, as compared with the previous SHARC core.

#### Variable Instruction Set Architecture (VISA)

In addition to supporting the standard 48-bit instructions from previous SHARC core processors, the SHARC+ core processors support 16-bit and 32-bit opcodes for many instructions, formerly 48-bit in the ISA. This variable instruction set architecture (VISA) feature drops redundant or unused bits within the 48-bit instruction to create more efficient and compact code. The program sequencer supports fetching these 16-bit and 32-bit instructions from both internal and external memories. VISA is not an operating mode; rather, it is address dependent (refer to the ISA/VISA address spaces in Table 5). Finally, the processor allows jumps between ISA and VISA instruction fetches.

### Single-Cycle Fetch of Instructional Four Operands

The ADSP-21560/21561/21564/21568 processors feature an enhanced Harvard architecture in which the DM bus transfers data and the PM bus transfers both instructions and data.

With the separate program memory bus, data memory buses, and on-chip instruction conflict cache, the processor can simultaneously fetch four operands (two over each data bus) and one instruction from the conflict cache in a single cycle.

#### Core Event Controller (CEC)

The SHARC+ core event controller (CEC) can be configured to service various interrupts generated by the core (including arithmetic and circular buffer instruction flow exceptions) and system event controller (SEC) events (peripheral interrupt request, debug or monitor, and software-raised), responding only to interrupts enabled in the IMASK register. The output of the SEC is forwarded to the CEC to respond directly to any enabled system interrupts. For all SEC channels, the processor automatically stacks the arithmetic status (ASTATx and ASTATy) registers and mode (MODE1) register in parallel with interrupt servicing.

#### **Instruction Conflict Cache**

The processors include a 32-entry instruction cache that enables three-bus operation for fetching an instruction and four data values. The cache is selective—only the instructions that require fetches conflict with the PM bus data access cache. This cache allows full speed execution of core looped operations, such as digital filter multiply accumulates and FFT butterfly processing. The conflict cache serves for bus conflicts within the SHARC+ core only.

### **Addressing Spaces**

In addition to traditionally supported long word, normal word, extended precision word, and short word addressing aliases, the processors support byte addressing for the data and instruction accesses. The enhanced ISA/VISA provides new instructions for accessing all sizes of data from byte space, as well as converting word addresses to byte addresses and byte addresses to word addresses.

## 1564/21568 Preliminary Technical Data

### Branch Target Buffer (BTB)/Branch Predictor (BP)

Implementation of a hardware-based branch predictor (BP) and branch target buffer (BTB) reduce branch delay. The program sequencer supports efficient branching using the BTB for conditional and unconditional instructions.

#### SHARC Fabric

The FIR/IIR accelerators on the processors are integrated closely with the SHARC+ core with the help of a dedicated SHARC fabric and run at CCLK speed. This allows the FIR/IIR accelerator requester ports to directly access the SHARC L1 memory with reduced latency, as these accesses do not go through the main system fabric. These accesses are arbitrated between both the SHARC+ core completer ports. The SHARC+ core can also access the FIR/IIR accelerator MMR registers directly.

#### **Additional Features**

To enhance the reliability of the application, L1 data RAMs support parity error detection for every byte, and illegal opcodes are also detected (core interrupts flag both errors). Requester ports of the core also detect failed external accesses.

#### SYSTEM INFRASTRUCTURE

The following sections describe the system infrastructure of the ADSP-21560/21561/21564/21568 processors.

### System L2 Memory

A system L2 SRAM memory of up to 16 Mb (2 MB) is available to the SHARC+ core and the system DMA channels (see Table 3). The L2 SRAM block is subdivided into up to eight

banks to support concurrent access to the L2 memory ports. Memory accesses to the L2 memory space are multicycle accesses by the SHARC+ core.

The memory space is used for various situations including

- Accelerator and peripheral sources and destination memory to avoid accessing data in the external memory

- A location for DMA descriptors

- Storage for additional data for the SHARC+ core to avoid external memory latencies and reduce external memory bandwidth

- Storage for data coefficient tables cached by the SHARC+ core

See the System Memory Protection Unit (SMPU) section for options in limiting access by the core and DMA requesters.

### One Time Programmable Memory (OTP)

The processors feature 7 kb of one time programmable (OTP) memory that is memory-map accessible. This memory can be programmed with custom keys and supports secure boot and secure operation.

### I/O Memory Space

Mapped I/Os include SPI2 or xSPI0 memory address spaces (see Table 5).

#### **SYSTEM MEMORY MAP**

Table 2. L1 Block 0, Block 1, Block 2, and Block 3 SHARC+® Addressing Memory Map (Private Address Space)

| Memory          | Long Word (64 Bits) | Extended Precision/<br>ISA Code (48 Bits) | Normal Word (32 Bits) | Short Word/<br>VISA Code (16 Bits) | Byte Access (8 Bits) |

|-----------------|---------------------|-------------------------------------------|-----------------------|------------------------------------|----------------------|

| L1 Block 0 SRAM | 0x00048000-         | 0x00090000-                               | 0x00090000-           | 0x00120000-                        | 0x00240000-          |

| (1.5 Mb)        | 0x0004DFFF          | 0x00097FFF                                | 0x0009BFFF            | 0x00137FFF                         | 0x0026FFFF           |

| L1 Block 1 SRAM | 0x00058000-         | 0x000B0000-                               | 0x000B0000-           | 0x00160000-                        | 0x002C0000-          |

| (1.5 Mb)        | 0x0005DFFF          | 0x000B7FFF                                | 0x000BBFFF            | 0x00177FFF                         | 0x002EFFFF           |

| L1 Block 2 SRAM | 0x00060000-         | 0x000C0000-                               | 0x000C0000-           | 0x00180000-                        | 0x00300000-          |

| (1 Mb)          | 0x00063FFF          | 0x000C5554                                | 0x000C7FFF            | 0x0018FFFF                         | 0x0031FFFF           |

| L1 Block 3 SRAM | 0x00070000-         | 0x000E0000-                               | 0x000E0000-           | 0x001C0000-                        | 0x00380000-          |

| (1 Mb)          | 0x00073FFF          | 0x000E5554                                | 0x000E7FFF            | 0x001CFFFF                         | 0x0039FFFF           |

## ADSP-21560/21561/21564/21568

Table 3. L2 Memory Addressing Map

|                     | Byte Address Space    | Normal Word Address Space | VISA Address Space       | ISA Address Space        |

|---------------------|-----------------------|---------------------------|--------------------------|--------------------------|

| Memory <sup>1</sup> | SHARC+ Data Access    | SHARC+ Data Address       | SHARC+ Instruction Fetch | SHARC+ Instruction Fetch |

| L2 RAM (2 Mb)       | 0x200C0000-           | 0x08030000-               | 0x00BE0000-              | 0x005E0000-              |

|                     | 0x200FFFFF            | 0x0803FFFF                | 0x00BFFFFF               | 0x005EAAAA               |

| L2 RAM (4 Mb)       | 0x20080000-           | 0x08020000-               | 0x00BC0000-              | 0x005D5556-              |

|                     | 0x200FFFFF            | 0x0803FFFF                | 0x00BFFFFF               | 0x005EAAAA               |

| L2 RAM (8 Mb)       | 0x20000000-           | 0x08000000-               | 0x00B80000-              | 0x005C0000-              |

|                     | 0x200FFFFF            | 0x0803FFFF                | 0x00BFFFFF               | 0x005EAAAA               |

| L2 RAM (8 Mb)       | 0x80000000-           | 0x10000000-               | 0x00800000-              | 0x00400000-              |

|                     | 0x800FFFFF            | 0x1003FFFF                | 0x0087FFFF               | 0x0042AAAA               |

|                     | SHARC/DMA:            | 0x08040000-               | 0x00B20000-              | 0x00580000-              |

| L2 Boot ROM0        | 0x20100000-0x20107FFF | 0x08041FFF                | 0x00B23FFF               | 0x00581555               |

| L2 Boot ROM1        | 0x20108000-           | 0x08042000-               | 0x00B00000-              | 0x00500000-              |

|                     | 0x2010FFFF            | 0x08043FFF                | 0x00B03FFF               | 0x00501555               |

| L2 Boot ROM2        | 0x20110000-           | 0x08044000-               | 0x00B40000-              | 0x00540000-              |

|                     | 0x20117FFF            | 0x08045FFF                | 0x00B43FFF               | 0x00541555               |

<sup>1</sup> The L2 RAM blocks are subdivided into banks—the 8 Mb L2 models have eight banks, the 4 Mb models have four banks, and there are two banks for the 2 Mb models.

### Table 4. SHARC+® L1 Memory Space

|                                          | Memory<br>Block | Byte Address Space SHARC+ | Normal Word Address Space SHARC+ |

|------------------------------------------|-----------------|---------------------------|----------------------------------|

| L1 Memory Space Address via Completer 1/ | Block 0         | 0x28240000-0x2826FFFF     | 0x0A090000-0x0A09BFFF            |

| Completer 2 Port                         | Block 1         | 0x282C0000-0x282EFFFF     | 0x0A0B0000-0x0A0BBFFF            |

|                                          | Block 2         | 0x28300000-0x2831FFFF     | 0x0A0C0000-0x0A0C7FFF            |

|                                          | Block 3         | 0x28380000-0x2839FFFF     | 0x0A0E0000-0x0A0E7FFF            |

### Table 5. Memory Map of Mapped I/Os<sup>1</sup>

|                    | Byte Address Space<br>SHARC+ Data Access | Normal Word Address Space<br>SHARC+ Data Access | VISA Address Space<br>SHARC+ Instruction Fetch | ISA Address Space<br>SHARC+ Instruction Fetch |

|--------------------|------------------------------------------|-------------------------------------------------|------------------------------------------------|-----------------------------------------------|

| SPI1/SPI2/xSPI0    | 0x60000000-0x600FFFFF                    | F (                                             | 0x00F80000-0x00FFFFF                           | 0x00780000-0x007FFFF                          |

| Memory<br>(512 MB) | 0x60100000-0x602FFFFF                    | 0x04000000-0x07FFFFFF                           | Not applicable                                 | 0x00760000-0x007FFFF                          |

|                    | 0x60300000-0x6FFFFFF                     |                                                 | Not applicable                                 | Not applicable                                |

|                    | 0x70000000-0x7FFFFFF                     | Not applicable                                  | Not applicable                                 | Not applicable                                |

<sup>&</sup>lt;sup>1</sup>The SHARC+ VISA/ISA address space for instruction fetch and the normal word address space for data access do not cover the entire byte address space.

### System Crossbars (SCBs)

The system crossbars (SCBs) are the fundamental building blocks of a switch fabric style for on-chip system bus interconnection. The SCBs connect system bus requesters to system bus completers, providing concurrent data transfer between multiple bus requesters and multiple bus completers. A hierarchical model—built from multiple SCBs—provides a power and area efficient system interconnection.

The SCBs provide the following features:

- Highly efficient, pipelined bus transfer protocol for sustained throughput

- Full-duplex bus operation for flexibility and reduced latency

- Concurrent bus transfer support to allow multiple bus requesters to access bus completers simultaneously

- Protection model (secure) support for selective bus interconnect protection

#### **Direct Memory Access (DMA)**

The processors use direct memory access (DMA) to transfer data within memory spaces or between a memory space and a peripheral. The processors can specify data transfer operations and return to normal processing while the fully integrated DMA controller carries out the data transfers independent of processor activity.

DMA transfers can occur between memory and a peripheral or between one memory and another memory. Each memory to memory DMA stream uses two channels: the source channel and the destination channel.

All DMA channels can transport data to and from all on-chip and off-chip memories. Programs can use two types of DMA transfers: descriptor-based or register-based. Register-based DMA allows the processors to program DMA control registers directly to initiate a DMA transfer. On completion, the DMA control registers automatically update with original setup values for continuous transfer. Descriptor-based DMA transfers require a set of parameters stored within memory to initiate a DMA sequence. Descriptor-based DMA transfers allow multiple DMA sequences to be chained together. Program a DMA channel to set up and start another DMA transfer automatically after the current sequence completes.

The DMA engine supports the following DMA operations:

- A single linear buffer that stops on completion

- · A linear buffer with negative, positive, or zero stride length

- A circular autorefreshing buffer that interrupts when each buffer becomes full

- A similar circular buffer that interrupts on fractional buffers, such as at the halfway point

- The 1D DMA uses a set of identical ping pong buffers defined by a linked ring of two-word descriptor sets, each containing a link pointer and an address

- 1D and 2D fill block to initialize an array with constants

- 32-bit CRC signature of a block of memory or an MMR

### **Preliminary Technical Data**

- The 1D DMA uses a linked list of four-word descriptor sets containing a link pointer, an address, a length, and a configuration

- The 2D DMA uses an array of one-word descriptor sets, specifying only the base DMA address

- The 2D DMA uses a linked list of multiword descriptor sets, specifying all configurable parameters

#### Memory Direct Memory Access (MDMA)

The processor supports various memory direct memory access (MDMA) operations, including,

- Enhanced bandwidth MDMA channels with cyclic redundancy check (CRC) protection (32-bit bus width, run on SYSCLK)

- Enhanced bandwidth MDMA channel (32-bit bus width, runs on SYSCLK)

- Maximum bandwidth MDMA channel (64-bit bus width, runs on SYSCLK)

#### **Extended Memory DMA**

Extended memory DMA supports various operating modes, such as delay line (which allows processor reads and writes to external delay line buffers and to the external memory), with limited core interaction and scatter/gather DMA (writes to and from noncontiguous memory blocks).

### Cyclic Redundancy Check (CRC) Protection

The cyclic redundancy check (CRC) protection modules allow system software to calculate the signature of code, data, or both in memory, the content of memory-mapped registers, or periodic communication message objects. Dedicated hardware circuitry compares the signature with precalculated values and triggers appropriate fault events.

For example, the system software initiates the signature calculation of the entire memory contents every 100 ms and compares this with expected, precalculated values. If a mismatch occurs, a fault condition is generated through the processor core or the trigger routing unit.

The CRC is a hardware module based on a CRC32 engine that computes the CRC value of the 32-bit data-words presented to it. The source channel of the memory to memory DMA (in memory scan mode) provides data. The data can be optionally forwarded to the destination channel (memory transfer mode). The main features of the CRC peripheral are as follows:

- Memory scan mode

- Memory transfer mode

- · Data verify mode

- Data fill mode

- User-programmable CRC32 polynomial

- Bit and byte mirroring option (endianness)

- Fault and error interrupt mechanisms block

### **Event Handling**

The processors provide event handling that supports both nesting and prioritization. Nesting allows multiple event service routines to be active simultaneously. Prioritization ensures that servicing a higher priority event takes precedence over servicing a lower priority event.

The processors provide support for four different types of events:

- An emulation event causes the processors to enter emulation mode, allowing command and control of the processors through the JTAG interface.

- A reset event resets the processors.

- An exception event occurs synchronously to program flow (in other words, the exception is taken before the instruction is allowed to complete). Conditions triggered by the SHARC+ core, such as data alignment (SIMD or long word) or compute violations (fixed or floating point) and illegal instructions, cause core exceptions. Conditions triggered by the SEC, such as error correcting code (ECC), parity, watchdog, or system clock, cause system exceptions.

- An interrupt event occurs asynchronously to program flow. Interrupts are caused by input signals, timers, and other peripherals, as well as by an explicit software instruction.

### **System Event Controller (SEC)**

The SHARC+ core event controller receives interrupt requests from the system event controller (SEC). The SEC features include the following:

- Comprehensive system event source management, including interrupt enable, fault enable, priority, and source grouping

- A distributed programming model where each system event source control and all status fields are independent of each other

- Determinism where all system events have the same propagation delay and provide unique identification of a specific system event source

- A completer control port that provides access to all SEC registers for configuration, status, and interrupt and fault services

- Global locking that supports a register level protection model to prevent writes to locked registers

- Fault management including fault action configuration, time out, external indication, and system reset

### ADSP-21560/21561/21564/21568

#### Trigger Routing Unit (TRU)

The trigger routing unit (TRU) provides system level sequence control without core intervention. The TRU maps trigger generators to trigger receivers. Trigger receivers can be configured to respond to triggers in various ways. Common applications enabled by the TRU include,

- Automatically triggering the start of a DMA sequence after a sequence from another DMA channel completes

- · Software triggering

- Synchronization of concurrent activities

#### **SECURITY FEATURES**

The following sections describe the security features of the ADSP-21560/21561/21564/21568 processors.

### **Cryptographic Hardware Accelerators**

The ADSP-21560/21561/21564/21568 processors support standards-based hardware accelerated encryption, decryption, authentication, and true random number generation.

Support for the hardware accelerated cryptographic ciphers includes the following:

- AES in ECB, CBC, ICM, and CTR modes with 128-bit, 192-bit, and 256-bit keys

- DES in ECB and CBC mode with 56-bit key

- 3DES in ECB and CBC mode with 3x 56-bit key

- ARC4 in stateful, stateless mode, up to 128-bit key

Support for the hardware accelerated hash functions includes the following:

- SHA-1

- · SHA-2 with 224-bit and 256-bit digests

- · HMAC transforms for SHA-1 and SHA-2

- MD5

Public key accelerator (PKA) is available to offload computation intensive public key cryptography operations.

Both a hardware-based nondeterministic random number generator and pseudorandom number generator are available.

Secure boot is also available with 224-bit and 256-bit elliptic curve digital signatures ensuring integrity and authenticity of the boot stream. Optionally, ensuring confidentiality through AES-128 encryption is available.

### **Preliminary Technical Data**

Password protected secure debug is also available to allow only trusted users to access the system with debug tools.

### CAUTION

This product includes security features that can be used to protect embedded nonvolatile memory contents and prevent execution of unauthorized code. When security is enabled on this device (either by the ordering party or the subsequent receiving parties), the ability of Analog Devices to conduct failure analysis on returned devices is limited. Contact Analog Devices for details on the failure analysis limitations for this device.

### System Protection Unit (SPU)

The system protection unit (SPU) guards against accidental or unwanted access to an MMR space of the peripheral by providing a write protection mechanism. The user can choose and configure the protected peripherals as well as configure which of the three system MMR requesters (SHARC+ core, memory DMA, and Arm<sup>®</sup> CoreSight<sup>™</sup> debug) the peripherals are guarded against.

The SPU is also part of the security infrastructure. Along with providing write protection functionality, the SPU is employed to define which resources in the system are secure or nonsecure as well as block access to secure resources from nonsecure requesters.

#### System Memory Protection Unit (SMPU)

The system memory protection unit (SMPU) provides memory protection against read and/or write transactions to defined regions of memory. There are SMPU units in the ADSP-21560/21561/21564/21568 processors for each memory space, except for SHARC L1 memory.

The SMPU is also part of the security infrastructure. It allows the user to protect against arbitrary read and/or write transactions and allows regions of memory to be defined as secure and prevent nonsecure requesters from accessing those memory regions.

### **SECURITY FEATURES DISCLAIMER**

Analog Devices does not guarantee that the Security Features described herein provide absolute security. ACCORDINGLY, ANALOG DEVICES HEREBY DISCLAIMS ANY AND ALL EXPRESS AND IMPLIED WARRANTIES THAT THE SECURITY FEATURES CANNOT BE BREACHED, COMPROMISED, OR OTHERWISE CIRCUMVENTED AND IN NO EVENT SHALL ANALOG DEVICES BE LIABLE FOR ANY LOSS, DAMAGE, DESTRUCTION, OR RELEASE OF DATA, INFORMATION, PHYSICAL PROPERTY, OR INTELLECTUAL PROPERTY.

#### **SAFETY FEATURES**

The ADSP-21560/21561/21564/21568 processors are designed to support functional safety applications. Whereas the level of safety is mainly dominated by the system concept, the following primitives are provided by the processors to build a robust safety concept.

### **Multiparity Bit Protected SHARC+ Core L1 Memories**

In the SHARC+ core L1 memory space, whether SRAM or cache, multiple parity bits protect each word to detect the single event upsets that occur in all RAMs. Parity also protects the cache tags and BTB.

### **Parity Protected L2 Memories**

Even parity protection is added to the whole of L2 memories. There is one parity bit for each 32-bit data, which is used to detect odd number of erroneous bits in the data retrieved from the memory.

### **Parity Protected Peripheral Memories**

Parity protection is added to the following peripheral memories:

- ASRC

- IIR

- FIR

- CRYPTO

- MLB

#### Cyclic Redundancy Check (CRC) Protected Memories

Whereas parity bit and ECC protection mainly protect against random soft errors in L1 and L2 memory cells, the CRC engines can protect against systematic errors (pointer errors) and static content (instruction code) of L1 and L2 memories. The processors feature two CRC engines that are embedded in the memory to memory DMA controllers.

CRC checksums can be calculated or compared automatically during memory transfers. Alternatively, single or multiple memory regions can be continuously scrubbed by a single DMA work unit as per DMA descriptor chain instructions. The CRC engine also protects data loaded during the boot process.

### Signal Watchdogs

The 10 general-purpose timers feature modes to monitor offchip signals. The watchdog period mode monitors whether external signals toggle with a period within an expected range. The watchdog width mode monitors whether the pulse widths of external signals are within an expected range. Both modes help detect undesired toggling or lack of toggling of system level signals.

### System Event Controller (SEC)

Besides system events, the system event controller (SEC) further supports fault management, including fault action configuration as timeout, internal indication by system interrupt, or external indication through the SYS\_FAULT pin and system reset.

### Memory Error Controller (MEC)

The memory error controller (MEC) manages memory parity/ECC errors and warnings from the cores and peripherals and sends out interrupts and triggers.

#### **PROCESSOR PERIPHERALS**

The following sections describe the peripherals of the ADSP-21560/21561/21564/21568 processors.

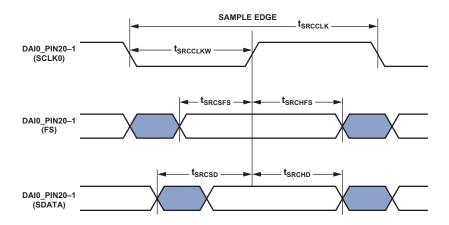

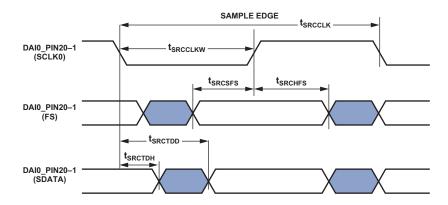

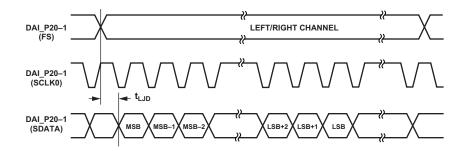

### Digital Audio Interface (DAI)

The processors support two digital audio interface (DAI) units. The DAI can connect various peripherals to any of the DAI pins.

The application code makes these connections using the signal routing unit (SRU), shown in Figure 1.

The SRU is a matrix routing unit (or group of multiplexers) that enables the peripherals provided by the DAI to interconnect under software control. This functionality allows easy use of the DAI associated peripherals for a wider variety of applications by using a larger set of algorithms than is possible with nonconfigurable signal paths.

The DAI includes the peripherals described in the following sections (SPORTs, ASRC, S/PDIF, and PCG). DAI Pin Buffer 20 and DAI Pin Buffer 19 can change the polarity of the input signals. Most signals of the peripherals belonging to different DAIs cannot be interconnected, with few exceptions.

The DAI\_PINx pin buffers may also be used as GPIO pins. DAI input signals allow the triggering of interrupts on the rising edge, falling edge, or both.

See the ADSP-21560/21561/21564/21568 SHARC+ Processor Hardware Reference manual for complete information on the use of the DAIs and SRUs.

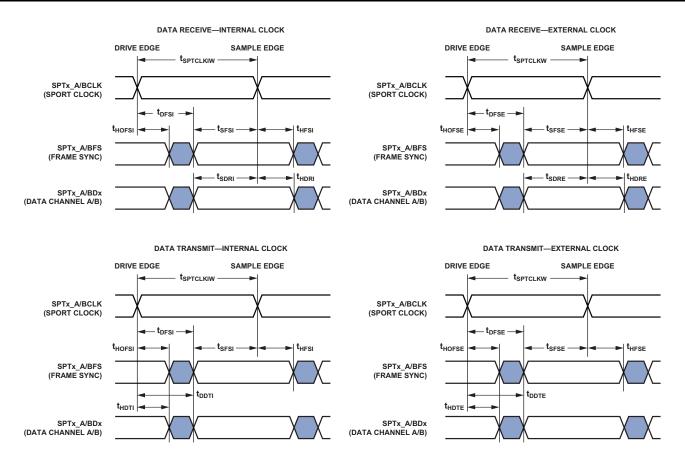

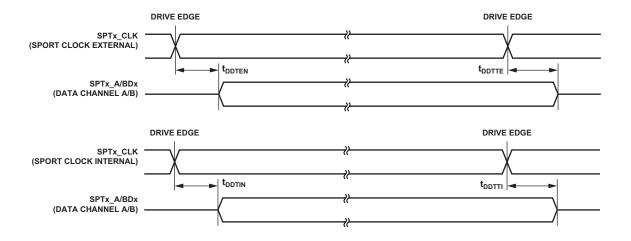

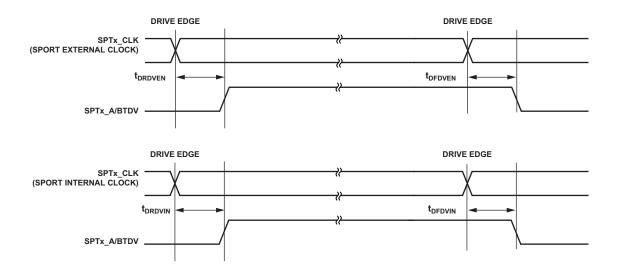

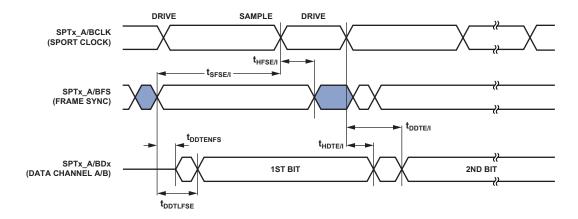

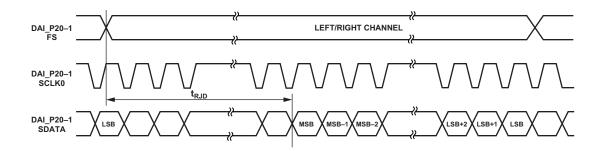

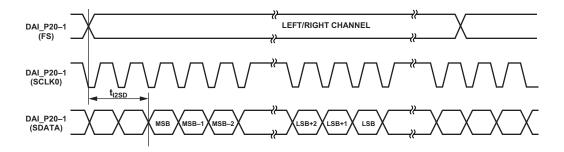

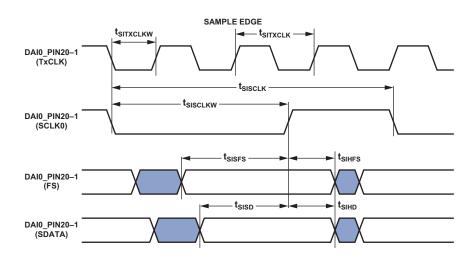

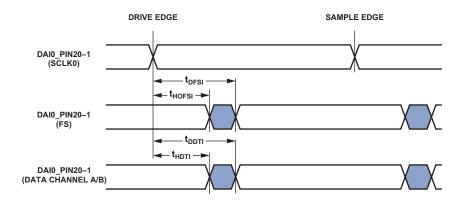

### Serial Port (SPORT)

The processors feature eight synchronous serial ports (SPORTs), providing an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices. These devices include Analog Devices AD19xx and ADAU19xx families of audio codecs, analog-to-digital converters (ADCs) and digital-to-analog converters (DACs). Two data lines, a clock, and a frame sync comprise a SPORT half. The data lines can be programmed to either transmit or receive data, and each SPORT half has a dedicated DMA channel.

An individual SPORT module consists of two independently configurable SPORT halves with identical functionality. Two bidirectional data lines—primary (0) and secondary (1)—are available per SPORT half and are configurable as either transmitters or receivers. Therefore, each SPORT half permits two unidirectional streams into or out of the same SPORT. This bidirectional functionality provides greater flexibility for serial communications. For full-duplex configuration, one half SPORT provides two transmit data signals, and the other half SPORT provides two receive data signals. The frame sync and clock are shared.

### ADSP-21560/21561/21564/21568

Serial ports operate in the following six modes:

- Standard DSP serial mode

- Multichannel time division multiplexing (TDM) mode

- I<sup>2</sup>S mode

- Packed I<sup>2</sup>S mode

- · Left justified mode

- · Right justified mode

### Asynchronous Sample Rate Converter (ASRC)

The asynchronous sample rate converter (ASRC) contains eight ASRC blocks. The ASRC provides up to 140 dB signal-to-noise ratio (SNR). The ASRC block performs synchronous or asynchronous sample rate conversion across independent stereo channels, without using internal processor resources. The ASRC blocks can also be configured to operate together to convert multichannel audio data without phase mismatches. Finally, the ASRC can clean up audio data from jittery clock sources such as the S/PDIF receiver.

### S/PDIF-Compatible Digital Audio Receiver/Transmitter

The Sony/Philips Digital Interface Format (S/PDIF) is a standard audio data transfer format that allows the transfer of digital audio signals from one device to another. There are two S/PDIF transmit/receive blocks on the processor. The digital audio interface carries three types of information: audio data, nonaudio data (compressed data), and timing information.

The S/PDIF interface supports one stereo channel or compressed audio streams. The S/PDIF transmitter and receiver are AES3 compatible and support the sample rate from 24 kHz to 192 kHz. The S/PDIF receiver supports professional jitter standards.

The S/PDIF receiver/transmitter has no separate DMA channels. The S/PDIF transmitter receives audio data in serial format and converts it into a biphase encoded signal. The serial data input to the transmitter can be formatted as left justified, I²S, or right justified with word widths of 16, 18, 20, or 24 bits. The S/PDIF receiver converts a biphase encoded signal into I²S serial format. The serial data, clock, and frame sync outputs/inputs from/to the S/PDIF receiver/transmitter are routed through the SRU. They can be connected to various peripherals, such as the SPORTs, external pins, and the precision clock generators (PCGs), and are controlled by the SRU control registers.

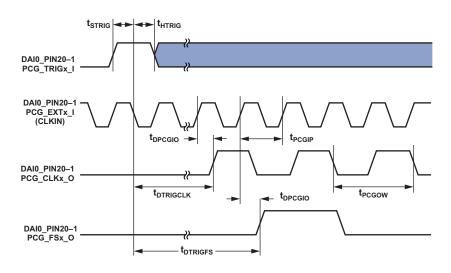

### **Precision Clock Generators (PCG)**

The precision clock generators (PCG) consist of four units: Unit A and Unit B located in the DAI0 block, and Unit C and Unit D located in the DAI1 block. The PCG can generate a pair of signals (clock and frame sync) derived from a clock input signal (SCLK0, SYS\_CLKIN0, or DAI pin buffer). Each unit can also output to the pin buffers of the opposite DAI unit. All units are identical in functionality and operate independently of each other. The two signals generated by each unit are normally used as a serial bit clock/frame sync pair.

## **Preliminary Technical Data**

### Universal Asynchronous Receiver/Transmitter (UART) Ports

The processors provide full-duplex universal asynchronous receiver/transmitter (UART) ports, fully compatible with PC standard UARTs. Each UART port provides a simplified UART interface to other peripherals or hosts, supporting full-duplex, DMA supported, asynchronous transfers of serial data. A UART port includes support for five to eight data bits as well as no parity, even parity, or odd parity.

Optionally, an additional address bit can be transferred to interrupt only addressed nodes in multidrop bus (MDB) systems. A frame is terminated by a configurable number of stop bits.

The UART ports support automatic hardware flow control through the clear to send (CTS) input and request to send (RTS) output with programmable assertion first in, first out (FIFO) levels.

To help support the Local Interconnect Network (LIN) protocols, a special command causes the transmitter to queue a break command of programmable bit length into the transmit buffer. Similarly, the number of stop bits can be extended by a programmable interframe space.

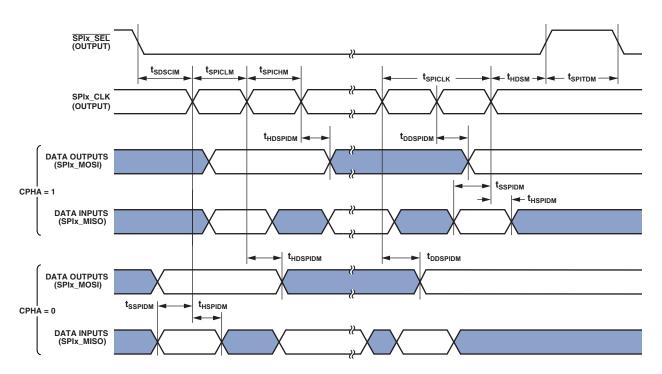

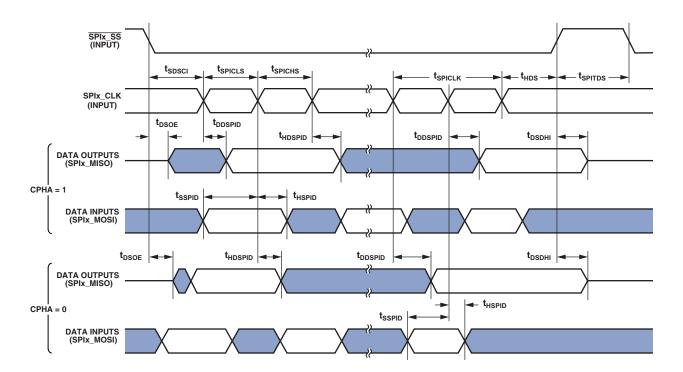

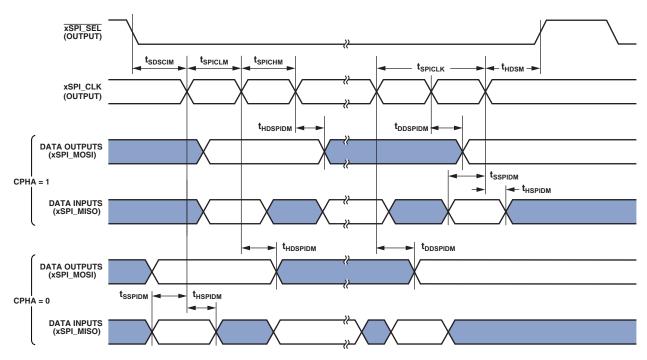

### Serial Peripheral Interface (SPI) Ports

The processors have three industry-standard SPI-compatible ports that allow the processors to communicate with multiple SPI-compatible devices.

The baseline SPI peripheral is a synchronous, 4-wire interface consisting of two data pins, one device select pin, and a gated clock pin. The two data pins allow full-duplex operation to other SPI-compatible devices. An extra two (optional) data pins are provided to support quad-SPI operation. Enhanced modes of operation, such as flow control, fast mode, and dual-I/O mode (DIOM), are also supported. DMA mode allows for transferring several words with minimal central processing unit (CPU) interaction.

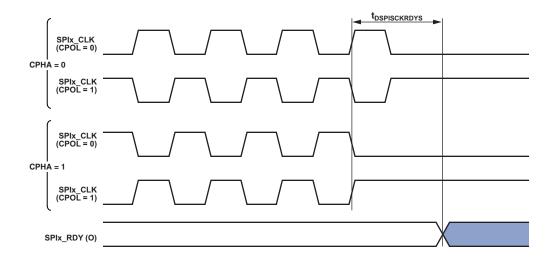

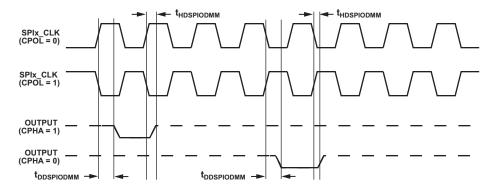

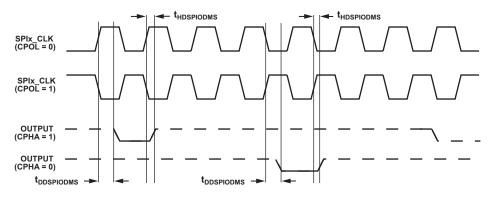

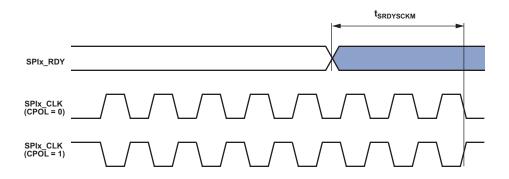

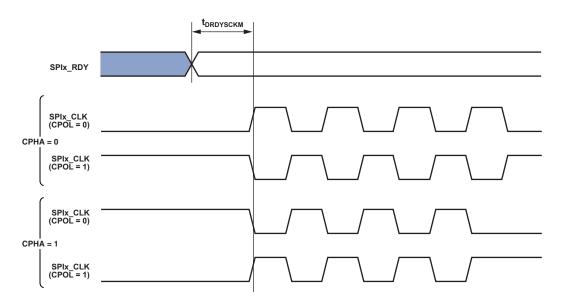

With a range of configurable options, the SPI ports provide a glueless hardware interface with other SPI-compatible devices in master mode, slave mode, and multimaster environments. The SPI peripheral includes programmable baud rates, clock phase, and clock polarity. The peripheral can operate in a multimaster environment by interfacing with several other devices, acting as either a master device or a slave device. In a multimaster environment, the SPI peripheral uses open-drain outputs to avoid data bus contention. The flow control features enable slow slave devices to interface with fast master devices by providing an SPI ready pin (SPI\_RDY), which flexibly controls the transfers.

The baud rate and clock phase and polarities of the SPI port are programmable. The port has integrated DMA channels for both transmit and receive data streams.

### xSPI with Octal and HyperBus Support

The octal serial peripheral interface (xSPI0/HyperBus) port provides an increased external memory data bus width (up to eight bits in parallel). The xSPI0 port supports dual data rate (DDR) modes of operation, which enables the transfer of up to 16 bits

of data each clock cycle. The xSPI0 port provides overall data throughput and performance improvement, including faster boot time.

Features of the xSPI0/HyperBus port include:

- Support for single-, dual-, quad-, or octal-I/O transfers

- Can be interfaced with octal flash, octal RAM, Hyper-Flash, and HyperRAM devices

- Can be interfaced with legacy flash devices including quad and SPINAND

- · Auto-command engine and minicontroller

- Multithreading support

- Support for execute in place (XIP): continuous mode

- Programmable page and block sizes

- Programmable write protected regions

- Programmable memory timing

- Support for DDR commands

- Support for PHY mode of operation to enable high-speed transfers

- Support for DQS to increase robustness of data sampling at higher speeds

#### **Timers**

The processors include several timers that are described in the following sections.

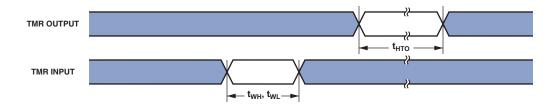

#### **General-Purpose (GP) Timers (TIMER)**

There is one general-purpose (GP) timer unit, providing 10 general-purpose programmable timers. Each timer has an external pin that can be configured as PWM or timer output, as an input to clock the timer, or as a mechanism for measuring pulse widths and periods of external events. These timers can be synchronized to an external clock input on the TM\_TMR[n] pins, an external TM\_CLK input pin, or to the internal SCLK0.

These timer units can be used in conjunction with the UARTs to measure the width of the pulses in the data stream to provide a software autobaud detect function for the respective serial channels.

The GP timers can generate interrupts to the processor core, providing periodic events for synchronization to either the system clock or to external signals. Timer events can also trigger other peripherals via the TRU (for instance, to signal a fault). Each timer can also be started and stopped by any trigger generator without core intervention.

#### Watchdog Timer (WDT)

Two on-chip software watchdog timers (WDT) can be used by the SHARC+ core. A software watchdog can improve system availability by forcing the processors to a known state, via a general-purpose interrupt, or a fault, if the timer expires before being reset by software.

The programmer initializes the count value of the timer, enables the appropriate interrupt, then enables the timer. Thereafter, the software must reload the counter before it counts down to

zero from the programmed value, protecting the system from remaining in an unknown state where software that normally resets the timer stops running due to an external noise condition or software error.

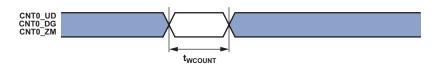

### **General-Purpose Counters (CNT)**

A 32-bit general-purpose counter (CNT) is provided that can operate in general-purpose up/down count modes and can sense 2-bit quadrature or binary codes as typically emitted by industrial drives or manual thumbwheels. Count direction is controlled by a level-sensitive input pin or by two edge detectors.

A third counter input can provide flexible zero marker support and can input the push button signal of thumbwheel devices. All three CNT0 pins have a programmable debouncing circuit.

Internal signals forwarded to a GP timer enable the timer to measure the intervals between count events. Boundary registers enable auto-zero operation or simple system warning by interrupts when programmed count values are exceeded.

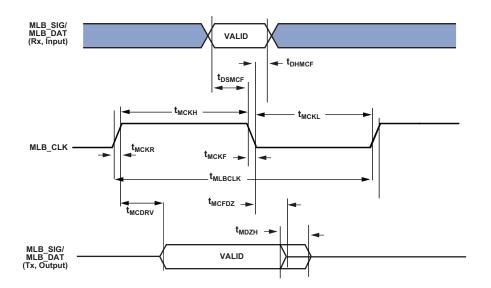

### Media Local Bus (MediaLB)

The automotive models have a MediaLB (MLB) device interface that allows the processors to function as a media local bus device. It includes support for 3-pin media local bus protocols. The MLB 3-pin configuration supports speeds up to  $1024 \times FS$ . The MLB also supports up to 64 logical channels with up to 468 bytes of data per MLB frame.

The MLB interface supports MOST25, MOST50, and MOST150 data rates and operates in device mode only.

### 2-Wire Controller Interface (TWI)

The processors include 2-wire interface (TWI) modules that provide a simple exchange method of control data between multiple devices. The TWI module is compatible with the widely used I<sup>2</sup>C bus standard. The TWI module offers the capabilities of simultaneous controller and target operation and support for both 7-bit addressing and multimedia data arbitration. The TWI interface utilizes two pins for transferring clock (TWI\_SCL) and data (TWI\_SDA) and supports the protocol at speeds up to 400 kbps. The TWI interface pins are compatible with 3.3 V logic levels.

Additionally, the TWI module is fully compatible with serial camera control bus (SCCB) functionality for easier control of various CMOS camera sensor devices.

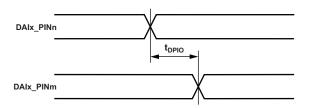

#### General-Purpose I/O (GPIO)

Each general-purpose port pin can be individually controlled by manipulating the port control, status, and interrupt registers:

- The GPIO direction control register specifies the direction of each individual GPIO pin as input or output.

- GPIO control and status registers have a write-one-to-modify mechanism that allows any combination of individual GPIO pins to be modified in a single instruction, without affecting the level of any other GPIO pins.

### ADSP-21560/21561/21564/21568

- GPIO interrupt mask registers allow each individual GPIO pin to function as an interrupt to the processors. GPIO pins defined as inputs can be configured to generate hardware interrupts, whereas output pins can be triggered by software interrupts.

- GPIO interrupt sensitivity registers specify whether individual pins are level or edge sensitive and specify, if edge sensitive, whether the rising edge or both the rising and falling edges of the signal are significant.

### Pin Interrupts

Every port pin on the processors can request interrupts in either an edge sensitive or a level sensitive manner with programmable polarity. Interrupt functionality is decoupled from GPIO operation. Two system-level interrupt channels (PINT0–PINT1) are reserved for this purpose. Each of these interrupt channels can manage up to 32 interrupt pins. The assignment from pin to interrupt is not performed on a pin by pin basis. Rather, groups of eight pins (half ports) are flexibly assigned to interrupt channels.

Every pin interrupt channel features a special set of 32-bit memory-mapped registers that enable half port assignment and interrupt management. This functionality includes masking, identification, and clearing of requests. These registers also enable access to the respective pin states and use of the interrupt latches, regardless of whether the interrupt is masked. Most control registers feature multiple MMR address entries to write-one-to-set or write-one-to-clear them individually.

#### SYSTEM ACCELERATION

The following sections describe the system acceleration blocks of the ADSP-21560/21561/21564/21568 processors.

### Finite Impulse Response (FIR) Accelerator

The finite impulse response (FIR) accelerator consists of a 1024 word coefficient memory, a 1024 word deep delay line for the data, and four multiplier-accumulator (MAC) units. A controller manages the accelerator. The FIR accelerator runs at the core clock frequency. The FIR accelerator can access all memory spaces and can run concurrently with the IIR accelerator on the processor.

### Infinite Impulse Response (IIR) Accelerator

The infinite impulse response (IIR) accelerator consists of a 1440 word coefficient memory for storage of biquad coefficients, a data memory for storing the intermediate data, and one MAC unit. A controller manages the accelerator. The IIR accelerator runs at the core clock frequency. The IIR accelerator can access all memory spaces and run concurrently with the other accelerators on the processor.

In addition to operating at core clock, the FIR/IIR accelerators support various enhanced features, including the ability to halt the accelerator for dynamic queuing of unlimited FIR/IIR channels, selective interrupt generation for each channel, and trigger requester/completer support.

#### **SYSTEM DESIGN**

The following sections provide an introduction to system design features and power supply issues.

#### **Clock Management**

The processors provide three operating modes, each with a different performance and power profile. Control of clocking to each of the processor peripherals reduces power consumption. The processors do not support any low power operation modes. Control of clocking to each of the processor peripherals can reduce the power consumption.

### Reset Control Unit (RCU)

Reset is the initial state of the whole processor, or the core, and is the result of a hardware or software triggered event. In this state, all control registers are set to default values and functional units are idle. Exiting a full system reset begins with the core ready to boot.

The reset control unit (RCU) controls how all the functional units enter and exit reset. Differences in functional requirements and clocking constraints define how reset signals are generated. Programs must guarantee that none of the reset functions put the system into an undefined state or cause resources to stall. This requirement is particularly important when the core resets (programs must ensure that there is no pending system activity involving the core when it is reset).

From a system perspective, reset is defined by both the reset target and the reset source.

The reset target is defined as the following:

- System reset—all functional units except the RCU are set to default states.

- Hardware reset—all functional units are set to default states without exception. History is lost.

- Core only reset—affects the core only. When in reset state, the core is not accessed by any bus requester.

The reset source is defined as the following:

- System reset—can be triggered by software (writing to the RCU\_CTL register) or by another functional unit, such as the dynamic power management (DPM) unit or any of the SEC, TRU, or emulator inputs.

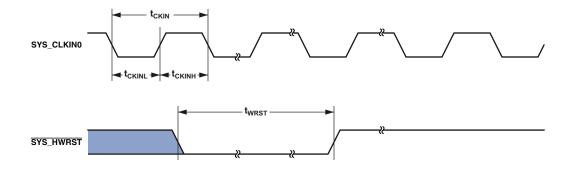

- Hardware reset—the SYS\_HWRST input signal asserts active (pulled down).

- Core only reset—affects only the core. The core is not accessed by any bus requester when in reset state.

- Trigger request (peripheral).

### **Clock Generation Unit (CGU)**

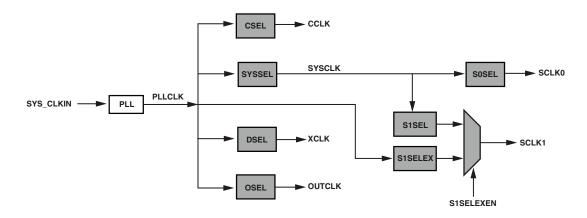

The ADSP-21560/21561/21564/21568 processors support one PLL. The PLL is part of a clock generation unit (CGU). The CGU is driven externally by the same clock source, thus providing flexibility in determining the internal clocking frequencies for each clock domain.

### **Preliminary Technical Data**

Frequencies generated by the CGU are derived from a common multiplier with different divider values available for each output.

The CGU generates all on-chip clocks and synchronization signals. Multiplication factors are programmed to define the PLLCLK frequency.

Programmable values divide the PLLCLK frequency to generate the core clock (CCLK), the system clocks, and the output clock (OCLK). For more information on clocking, see the ADSP-21560/21561/21564/21568 SHARC+ Processor Hardware Reference manual.

Writing to the CGU control registers does not affect the behavior of the PLL immediately. Registers are first programmed with a new value and the PLL logic executes the changes to ensure a smooth transition from the current conditions to the new conditions.

### **System Crystal Oscillator**

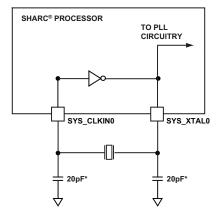

The processor can be clocked by an external crystal (see Figure 5), a sine wave input, or a buffered, shaped clock derived from an external clock oscillator. If using an external clock, it must be compatible with the  $V_{\rm IHCLKIN}$  and  $V_{\rm ILCLKIN}$  specifications and must not be halted, changed, or operated below the specified frequency during normal operation (see the Preliminary Operating Conditions section). When using an external clock, the clock signal is connected to the SYS\_CLKIN0 pin of the processor and the SYS\_XTAL0 pin must be left unconnected. The external clock signal driving SYS\_CLKIN0 must not exceed the internal (VDD\_INT) voltage level. Alternatively, because the processor includes an on-chip oscillator circuit, an external crystal can be used.

For fundamental frequency operation, use the circuit shown in Figure 5. A parallel resonant, fundamental frequency, microprocessor grade crystal is connected across the SYS\_CLKIN0 pin and the SYS\_XTAL0 pin.

NOTE: VALUES MARKED WITH \* MUST BE CUSTOMIZED, DEPENDING ON THE CRYSTAL AND LAYOUT. ANALYZE CAREFULLY. VALID FREQUENCY RANGE IS 20 MHz TO 30 MHz FOR SYS\_CLKINO.

Figure 5. External Crystal Connection

The two capacitors, shown in Figure 5, fine tune phase and amplitude of the sine frequency. The capacitor values shown in Figure 5 are typical values only. The capacitor values are dependent upon the load capacitance recommendations of the crystal manufacturer and the physical layout of the printed circuit board (PCB). The user must verify the customized values based on careful investigations on multiple devices over the required temperature range.

#### **Clock Distribution Unit (CDU)**

The clock generation unit provides output that feeds a clock distribution unit (CDU). The clock output CLKO0 and the clock generation unit outputs are connected to various targets. For more information, refer to the ADSP-21560/21561/21564/21568 SHARC+ Processor Hardware Reference manual.

#### Clock Out/External Clock

The SYS\_CLKOUT output pin has programmable options to output divided down versions of the on-chip clocks. By default, the SYS\_CLKOUT pin drives a buffered version of the SYS\_CLKINO input. Refer to the ADSP-21560/21561/21564/21568 SHARC+ Processor Hardware Reference manual to change the default mapping of clocks.

### **Booting**

The processors have several mechanisms for automatically loading internal and external memory after a reset. The boot mode is defined by the SYS\_BMODE[n] input pins. There are two categories of boot modes. In flash boot modes, the processors actively load data from serial memories. In external host boot modes, the processors receive data from external host devices.

The boot modes are shown in Table 6. These modes are implemented by the SYS\_BMODE[n] bits of the reset configuration register and are sampled during power-on resets and software initiated resets.

Table 6. Boot Modes

| SYS_BMODE[n] Setting | Boot Mode   |

|----------------------|-------------|

| 000                  | No boot     |

| 001                  | SPI2 flash  |

| 010                  | SPI2 host   |

| 011                  | UARTO host  |

| 100                  | Reserved    |

| 101                  | xSPI0 flash |

| 110                  | SPI1 flash  |

| 111                  | Reserved    |

In the ADSP-21560/21561/21564/21568 processors, the SHARC+ core controls the boot process, including loading all internal and external memory. The option for secure boot is available on all models.

### ADSP-21560/21561/21564/21568

### **Power Supplies**

The processors have separate power supply connections for

- Internal (VDD\_INT)

- External I/O (VDD\_EXT)

- PLL and OTP high voltage power supplies (VDD\_REF)

### **Power Management**

As shown in Table 7, the processors support three different power domains, which maximizes flexibility while maintaining compliance with industry standards and conventions.

The power dissipated by a processor is largely a function of the clock frequency and the square of the operating voltage. For example, reducing the clock frequency by 25% results in a 25% reduction in dynamic power dissipation.

**Table 7. Power Domains**

| Power Domain                                                         | V <sub>DD</sub> Range |

|----------------------------------------------------------------------|-----------------------|

| All Internal Logic                                                   | V <sub>DD_INT</sub>   |

| All Other I/O (Includes SYS, JTAG, and Ports Pins Except SYS_CLKINO) | V <sub>DD_EXT</sub>   |

| SYS_CLKIN0                                                           | V <sub>DD_INT</sub>   |

| PLL, OTP                                                             | V <sub>DD_REF</sub>   |

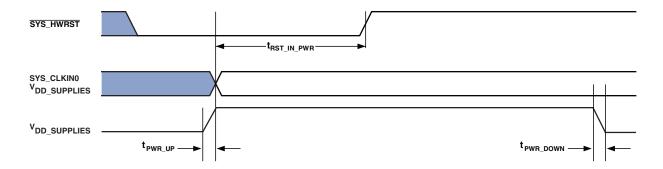

### Power-Up

SYS\_XTAL0 oscillations (SYS\_CLKIN0) start when power is applied to the VDD\_INT and VDD\_EXT pins. The rising edge of \$\overline{SYS}\_HWRST\$ initiates the PLL locking sequence. The deassertion must apply only if all voltage supplies and SYS\_CLKIN0 oscillations are valid (refer to the Power-Up Reset Timing section).

### **Target Board JTAG Emulator Connector**

The Analog Devices DSP tools product line of JTAG emulators uses the IEEE 1149.1 JTAG test access port of the processors to monitor and control the target board processor during emulation. The Analog Devices DSP tools product line of JTAG emulators provides emulation at full processor speed, allowing inspection and modification of memory, registers, and processor stacks. The processor JTAG interface ensures the emulator does not affect target system loading or timing.

For information on JTAG emulator operation, see the appropriate emulator hardware user's guide at SHARC Processors Software and Tools.

#### **SYSTEM DEBUG**

The processors include a feature that allows easy system debug. This is described in the following section.

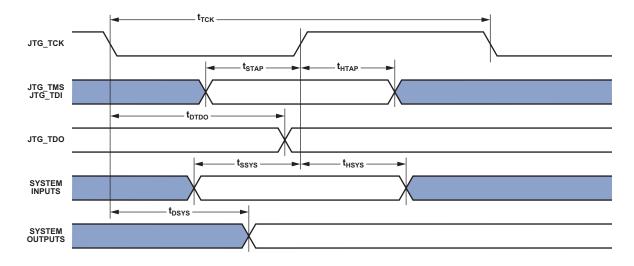

#### Debug Access Port (DAP)

The debug access port (DAP) provides IEEE 1149.1 JTAG interface support through the JTAG debug.

### **Preliminary Technical Data**

#### **DEVELOPMENT TOOLS**

Analog Devices supports its processors with a complete line of software and hardware development tools, including an integrated development environment, evaluation products, emulators, and a variety of software add-ins.

### **Integrated Development Environments (IDEs)**

For C/C++ software writing and editing, code generation, and debug support, Analog Devices offers the CrossCore<sup>®</sup> Embedded Studio (CCES) integrated development environment (IDE).

CCES is based on the Eclipse framework. Supporting most Analog Devices processor families, CCES is the IDE of choice for processors, including multicore devices.

CCES seamlessly integrates available software add-ins to support real-time operating systems, file systems, TCP/IP stacks, USB stacks, algorithmic software modules, and evaluation hardware board support packages (BSPs). For more information, visit www.analog.com/cces.

### **EZ-KIT Evaluation System**

For processor evaluation, Analog Devices provides EZ-KIT<sup>®</sup> evaluation systems, which are comprised of a System on Module (SOM) board and a SOM carrier board.

The SOM board (EV-21568-SOM) is small and low-cost, featuring the audio processor, QSPI flash memories, FTDI USB-to-UART, and USB power. SOM boards also include a JTAG debug connection such that they can be used standalone for debug/development using either the ADZS-ICE-2000 or ADZS-ICE-1000 in-circuit emulator (ICE).

The EV-SOMCRR-EZLITE SOM carrier board can be used in conjunction with the EV-21568-SOM and comes with a power supply and feature high-speed connectors for the SOM, a comprehensive set of peripherals, and an on-board emulator. The USB controller on the carrier board connects to the USB port of the user's PC, enabling CCES to emulate the on-board processor in-circuit. This permits users to download, execute, and debug programs, as well as in-circuit program the on-board flash memory device to store user-specific boot code, thus enabling standalone operation.

Each EZ-KIT purchased includes an evaluation license for CCES. The CCES evaluation license type restricts CCES features to specific evaluation systems. With the full CCES license type (sold separately), engineers can develop software for any of the CCES-supported evaluation boards (including the SOM when used standalone or when connected to a different carrier board) or any custom system designed around supported Analog Devices processors. The full CCES license type also enables higher-performance debug capabilities via JTAG using an ICE.

For further information, see:

- www.analog.com/cces