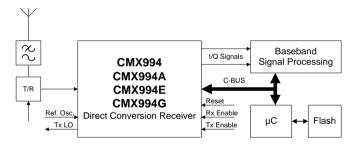

# CMX994/CMX994A/CMX994E /CMX994G Direct Conversion Receivers

# CMX994 / CMX994A (lower power options) / CMX994E (enhanced performance) / CMX994G (enhanced performance)

**DATASHEET**

D/994\_994A\_994E\_994G/7 November 2020

Provisional

#### **Features**

- Direct conversion receiver family

- CMX994 Standard and low power mode

- CMX994A Standard and additional low power modes

- CMX994E Enhanced, standard and low power modes

- CMX994G Enhanced, 30MHz guaranteed performance

- Rx single conversion to zero IF, near-zero IF or low IF; zero

IF eliminates image responses

- Very high mixer IIP2 for practical zero IF receiver

- 100MHz to 1GHz I/Q demodulator (CMX994A/E/G)

100MHz to 940MHz I/Q demodulator (CMX994)

Extended operation down to 30MHz and up to 1.218GHz

- LNA with gain control

- Local Oscillator

LO synthesiser VCO negative resistance amplifier Rx LO divide by 2, 4 or 6 modes

Tx LO Output with divide by 1, 2, 4, or 6 modes

- Precise filtering with 1:2:4 bandwidth select control

- 3.0V 3.6V Low power Operation

- Small size 40-pin VQFN Package

# **Applications**

- Analogue/digital multi-mode radio

- Software Defined Radio (SDR)

- Data telemetry modems

- Satellite communications

- Constant envelope and linear modulation

- Rx function compatible with CMX998 Cartesian Feedback Loop Transmitter

- Narrowband e.g. 25kHz, 12.5kHz, 6.25kHz

- Wideband Data e.g. >1MHz bandwidth

# 1 Brief Description

The CMX994/CMX994A/CMX994E/CMX994G is a family of direct conversion receiver ICs with PowerTrade™, the ability to dynamically select power vs. performance modes to optimise operating trade-offs. All four devices include a broadband LNA with gain control followed by a high dynamic range, very high IIP2, I/Q demodulator. The receiver baseband section includes amplifiers and precise, configurable bandwidth, baseband filter stages. LO generation is provided by an integer-N PLL and a VCO negative resistance amplifier; an external LO may also be used. LO dividers are provided for flexible multi-band operation. The devices operate from a single 3.3V supply over a temperature range of −40°C to +85°C and are available in a small 40-pin VQFN (Q4) package.

Relative to the CMX994 the CMX994A enables a significant reduction in power by allowing LO phase correction to be turned off. A further reduction is possible by disabling either the I or Q channel in a channel monitoring mode. The CMX994E includes all the features of the CMX994A and adds an enhanced performance mode for improved intermodulation in the receive mixers. The CMX994G has been introduced for radios operating down to 30MHz with guaranteed down-converter performance. **Throughout this datasheet, descriptions and features for the CMX994E also apply to the CMX994G, unless otherwise stated.**

© 2020 CML Microsystems Plc D/994\_A\_E\_G/7

# **CONTENTS**

| <u>Section</u> |                                                               | <u>Page</u> |

|----------------|---------------------------------------------------------------|-------------|

| 1              | Brief Description                                             | 1           |

| 2              | History                                                       | 5           |

| 3              | Block Diagram                                                 | 6           |

| 4              | Pin and Signal List                                           | 7           |

| 4.1            | Signal Definitions                                            | 8           |

| 4.2            | Connection of Unused Pins                                     | 8           |

| 5              | External Components                                           | 9           |

| 5.1            | Power Supply and Decoupling                                   | 9           |

| 5.2            | Receiver                                                      | 10          |

| 5.2.1          | LNA                                                           | 10          |

| 5.2.2          | Mixers and Baseband Section                                   |             |

| 5.3            | Local Oscillator                                              |             |

| 5.3.1          | Local Oscillator Input                                        |             |

| 5.3.2          | VCO and PLL                                                   |             |

| 5.4            | RESETN                                                        |             |

| 6              | General Description                                           | 18          |

| 6.1            | General Operation                                             |             |

| 6.1.1          | Rx/Tx Enable                                                  |             |

| 6.2            | Receiver Operation                                            |             |

| 6.2.1          | DC Offset Correction                                          |             |

| 6.2.2          | Receiver Filters and Bandwidth Options                        |             |

| 6.2.3          | Baseband Filter Design and Required Correction                |             |

| 6.2.4          | Operation at Wider Bandwidths                                 |             |

| 6.3            | Local Oscillator Operation                                    |             |

| 6.3.1          | PLL                                                           |             |

| 6.3.2          | PLL Enable                                                    |             |

| 7              | C-BUS Interface and Register Descriptions                     | 25          |

| 7.1            | General Reset: \$10 (no data)                                 |             |

| 7.2            | General Control Register                                      |             |

| 7.2.1          | General Control: \$11 - 8-bit write only                      |             |

| 7.2.2          | General Control: \$E1 - 8-bit read only                       |             |

| 7.3            | Rx Control Register                                           |             |

| 7.3.1          | Rx Control: \$12 – 8-bit write only                           |             |

| 7.3.2          | Rx Control: \$E2 – 8-bit read only                            |             |

| 7.4            | Rx Offset Register                                            |             |

| 7.4.1          | Rx Offset: \$13 – 8-bit write only                            |             |

| 7.4.2          | Rx Offset: \$E3 - 8-bit Read only                             |             |

| 7.5            | LNA Intermodulation Control Register                          |             |

| 7.5.1          | LNA IM Control: \$14 – 8-bit write only                       |             |

| 7.5.2          | LNA IM Control: \$E4 – 8-bit read only                        |             |

| 7.5.2          | Options Control Register – CMX994A and CMX994E only           |             |

| 7.6<br>7.6.1   | Options Control: \$15 – 8-bit write only                      |             |

| 7.6.2          | Options Control: \$15 – 8-bit write only                      |             |

| 7.6.2<br>7.7   | Rx Gain Register                                              |             |

| 7.7<br>7.7.1   | Rx Gain: \$16 – 8-bit write only                              |             |

| 7.7.2          | Rx Gain: \$16 – 8-bit write only                              |             |

| 7.7.2          | Extended Rx Offset Register – CMX994A and CMX994E only        |             |

| 7.0            | EXTERIOR IN OTISEL NEGISTEL - CIVIN 3344 ALIA CIVIN 334E OHIY |             |

| 7.8.1  | Extended Rx Offset: \$17 – 16-bit write only       | 33 |

|--------|----------------------------------------------------|----|

| 7.8.2  | Extended Rx Offset: \$E7 – 16-bit read only        |    |

| 7.9    | PLL M Divider Register                             |    |

| 7.9.1  | PLL M Divider: \$22 - \$20 – 8-bit write only      |    |

| 7.9.2  | PLL M Divider: \$D2-\$D0 - 8-bit read only         |    |

| 7.10   | PLL R Divider Register                             |    |

| 7.10.1 | PLL R Divider: \$24 - \$23 – 8-bit write only      |    |

| 7.10.2 | PLL R Divider: \$D4-\$D3 – 8-bit read only         |    |

| 7.11   | VCO Control Register                               |    |

| 7.11.1 | VCO Control: \$25 - 8-bit write only               |    |

| 7.11.2 | VCO Control: \$D5 - 8-bit read only                | 36 |

| 8      | Application Notes                                  |    |

| 8.1    | Typical Receiver Performance                       | 37 |

| 8.1.1  | System Performance                                 |    |

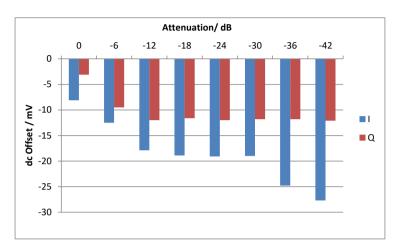

| 8.1.2  | DC Offsets                                         | 38 |

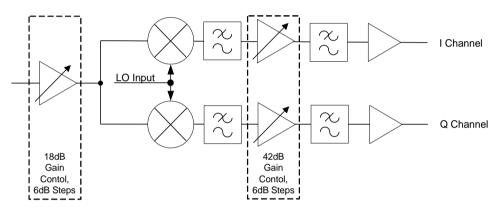

| 8.1.3  | Gain Control                                       |    |

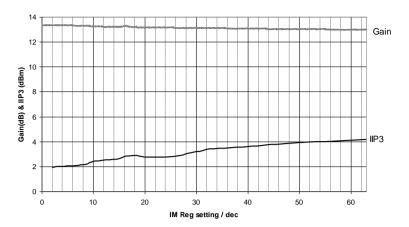

| 8.1.4  | LNA Intermodulation Optimisation                   |    |

| 8.1.5  | Low Power Mode                                     |    |

| 8.1.6  | I/Q Filter Response                                |    |

| 8.1.7  | Baseband Intermodulation                           |    |

| 8.1.8  | LO Pulling                                         |    |

| 8.1.9  | Rx Mixer Output (Broadband Operation)              |    |

| 8.1.10 | Power Saving Modes                                 | 47 |

| 8.1.11 | Spurious Responses                                 |    |

| 8.2    | Operation Below 100MHz                             | 48 |

| 8.3    | Operation 1GHz to 1.218GHz                         |    |

| 8.4    | Transmitter LO Output                              | 50 |

| 8.5    | Modem Solutions                                    |    |

| 8.6    | Zero IF, near-zero IF and low IF I/Q architectures | 51 |

| 9      | Performance Specification                          |    |

| 9.1    | Electrical Performance                             |    |

| 9.1.1  | Absolute Maximum Ratings                           |    |

| 9.1.2  | Operating Limits                                   |    |

| 9.1.3  | Operating Characteristics                          |    |

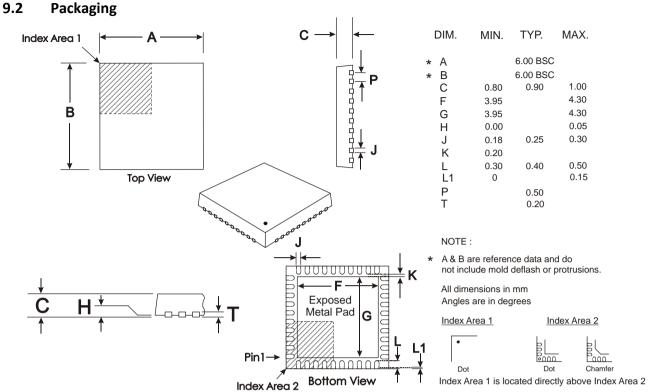

| 9.2    | Packaging                                          | 64 |

| <u>Table</u>                                                                                    | <u>Page</u> |

|-------------------------------------------------------------------------------------------------|-------------|

| Table 1 Definition of Power Supply and Reference Voltages                                       | 8           |

| Table 2 Decoupling Components                                                                   | 9           |

| Table 3 LNA $S_{11}$ and $S_{22}$ Impedances and Parallel Equivalent Circuit in $50\Omega$ Mode | 11          |

| Table 4 LNA S11 and S22 Impedances and Parallel Equivalent Circuit in $100\Omega$ Mode          | 12          |

| Table 5 150MHz LNA and Inter-stage Components (100Ω output mode)                                | 12          |

| Table 6 450MHz LNA and Inter-stage Components (100Ω output mode)                                | 12          |

| Table 7 900MHz LNA and Inter-stage Components (50Ω output mode)                                 | 13          |

| Table 8 CMX994 Rx Mixer Input Impedances and Parallel Equivalent Circuit                        | 13          |

| Table 9 CMX994A/CMX994E Rx Mixer Input Impedances and Parallel Equivalent Circuit               | 14          |

| Table 10 1218MHz Mixer Input Matching Components                                                | 14          |

| Table 11 Receiver Components                                                                    | 15          |

| Table 12 Internal VCO Amplifier Tank Circuit for 440MHz Operation                               | 17          |

| Table 13 3rd Order Loop Filter Circuit Values                                                   | 17          |

| Table 14 Tx (or Rx) Enable Operation                                                            | 19          |

| Table 15 DC Offset Correction Adjustments                                                       | 20          |

| Table 16 Typical LNA Gain Step Sizes at 100MHz, $Z_0$ =100 $\Omega$                             | 41          |

| Table 17 Typical LNA Gain Step Sizes at 450MHz, $Z_0$ =100 $\Omega$                             | 42          |

| Table 18 Typical LNA Gain Step Sizes at 940MHz, Z <sub>0</sub> =50Ω                             | 43          |

| Table 19 Typical Current Consumption in Various Modes                                           | 47          |

| Table 20 50MHz LNA and Inter-stage Components (100Ω mode)                                       | 48          |

| Table 21 Summary of Results for the Complete Rx Chain at 50MHz                                  | 48          |

| Table 22 1218MHz LNA and Inter-stage Components (50Ω output mode)                               | 49          |

| Table 23 Summary of Results for the LNA at 1218MHz                                              | 49          |

| Table 24 Summary of Results for the Complete Rx Chain at 1218MHz                                | 49          |

| Table 25 Modulation/Modem Combinations                                                          | 51          |

| Figure                                                                                          | Page        |

| Figure 1 Block Diagram                                                                          |             |

| Figure 2 Recommended Power Supply Connections and Decoupling                                    |             |

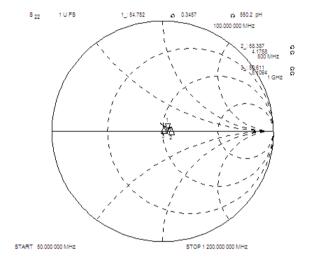

| Figure 3 LNA S <sub>11</sub> (50Ω Mode)                                                         |             |

| Figure 4 LNA S <sub>22</sub> (50Ω Mode)                                                         |             |

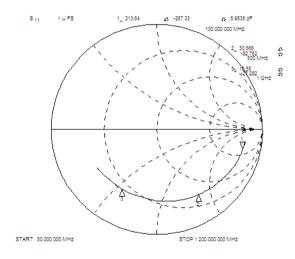

| Figure 5 LNA S <sub>11</sub> (100Ω Mode)                                                        |             |

| Figure 6 LNA S <sub>22</sub> (100Ω mode)                                                        |             |

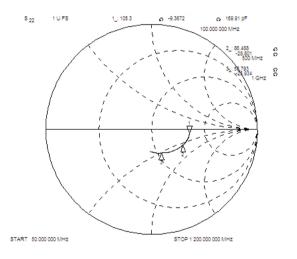

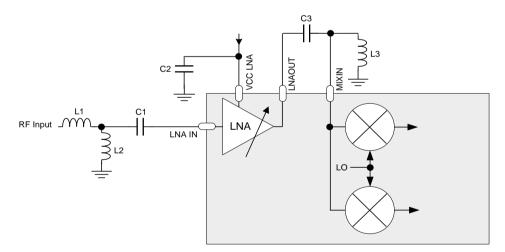

| Figure 7 Recommended LNA Configuration and Inter-stage Match                                    |             |

| Figure 8 Rx Mixer Input Impedance                                                               |             |

| Figure 9 1218MHz Recommended Mixer Input Configuration                                          |             |

| Figure 10 Recommended Receiver Circuit                                                          |             |

| Figure 11 Example External Components – VCO External Tank Circuit                               |             |

| Figure 12 Example External Components – PLL Loop Filter                                         |             |

| Figure 13 Simplified Schematic of How DC Offset Corrections are Applied                         |             |

| Figure 14 Baseband I/Q Filtering                                                                |             |

|                                                                                                 |             |

| Figure 15 Schematic Representation of Filters used in the I and Q Paths                         |             |

| _                                                                                               |             |

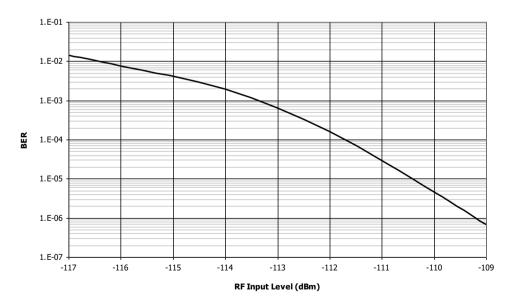

| Figure 19. CANYOOA and CANY716A with FL 2. Typical A FSK Sansitivity (10.3khps)                 |             |

| Figure 18 CMX994 and CMX7164 with FI-2 – Typical 4-FSK Sensitivity (19.2kbps)                   |             |

| Figure 19 I/Q Path dc Offsets                                                                   |             |

| Figure 20 Example Variation in Voffset with Gain Control Setting                                | 39          |

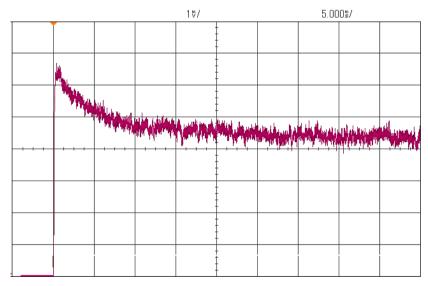

| Figure 21 Typical Transient Response, Differential Q Channel, 20°C, no input signal       | 39 |

|-------------------------------------------------------------------------------------------|----|

| 0 - 7 - 7 - 7 - 7 - 7 - 7 - 7 - 7 - 7 -                                                   |    |

| Figure 22 Gain Control                                                                    | 40 |

| Figure 23 Variation of LNA Gain and IMD with IM Register Setting, 450MHz                  | 44 |

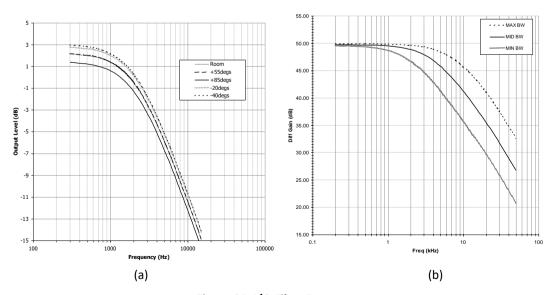

| Figure 24 I/Q Filter Response                                                             | 44 |

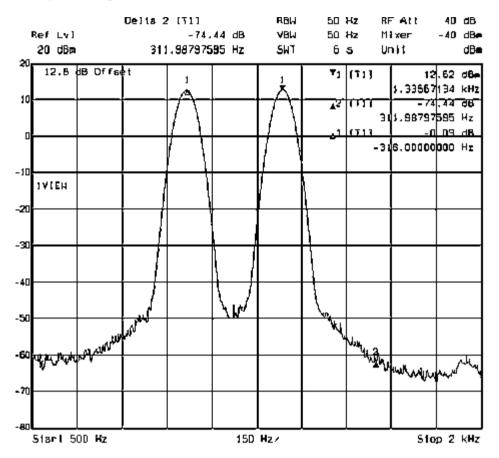

| Figure 25 Baseband Intermodulation Test at circa 6Vp-p Differential Output                | 45 |

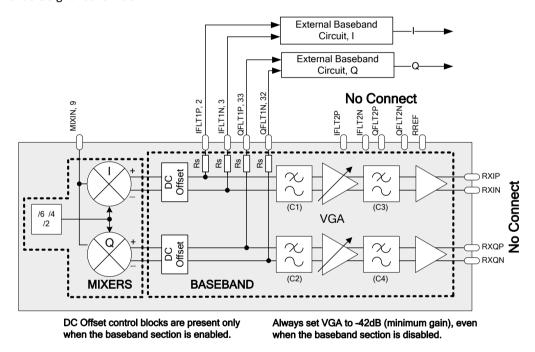

| Figure 26 External Baseband Circuit Connections to Mixer                                  | 46 |

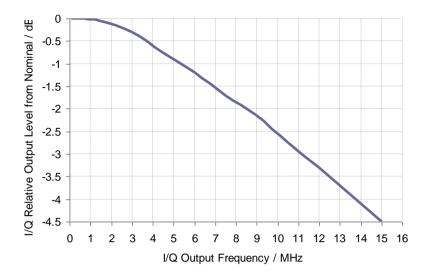

| Figure 27 Rx Mixer Output Bandwidth                                                       | 47 |

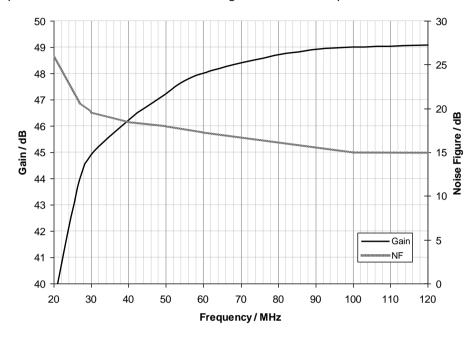

| Figure 28 Typical Gain and NF Variation of Demodulator Stages at Low Frequencies          |    |

| Figure 29 Typical LNA Configuration and Inter-stage Match for 1218MHz                     | 49 |

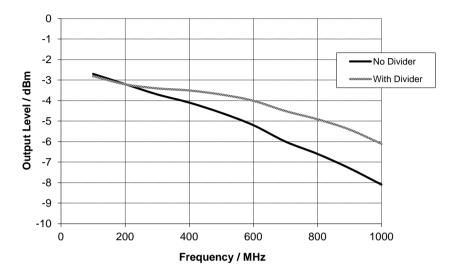

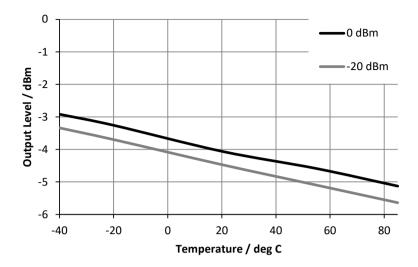

| Figure 30 Tx Output Level vs. Frequency                                                   | 50 |

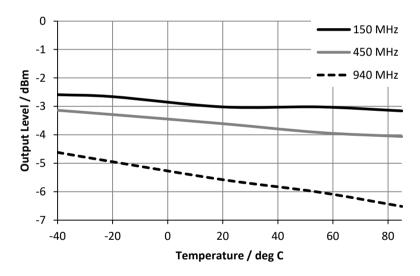

| Figure 31 Typical Tx Output Level (With Divider) vs. Temperature                          | 50 |

| Figure 32 Typical Tx Output Level (No Divider) vs. Temperature for Varying LO Input Level | 51 |

| Figure 33 C-BUS Timing                                                                    | 63 |

| Figure 34 Q4 Mechanical Outline                                                           | 64 |

# 2 History

| Version | Changes                                                                                           | Date                           |

|---------|---------------------------------------------------------------------------------------------------|--------------------------------|

| 7       | Section 9.1.3: I/Q demodulator maximum noise figure in Enhanced mode changed to 17 dB at 450 MHz. | 30 <sup>th</sup> November 2020 |

|         | Section 9.1.3: I/Q demodulator gain changed to 52 dB (V/V).                                       |                                |

| 6       | Section 9.1.3: Maximum I/Q amplitude balance changed from                                         | 15 <sup>th</sup> January 2020  |

|         | ±0.15dB to ±0.2dB.                                                                                |                                |

| 5       | Section 9.2: Updated Q4 package diagram                                                           | December 2019                  |

| 4       | CMX994G version added with guaranteed performance down to                                         | July 2019                      |

|         | 30MHz. Section 9.1.3 and 8.2 have been updated.                                                   |                                |

| 3       | Mixer operation extended to 1.218GHz:                                                             | November 2016                  |

|         | Section 5.2.2: Added Figure 9 (1218MHz Recommended Mixer Input                                    |                                |

|         | Configuration) and associated table of matching components                                        |                                |

| 2       | Section 7.9: details of device type reporting in register \$D2 added                              | November 2015                  |

|         | Section 8.1.2: more details of dc offsets added                                                   |                                |

| 1       | First published document as Provisional status                                                    | August 2015                    |

It is recommended that you check for the latest product datasheet version from the Product page of the CML website: [www.cmlmicro.com].

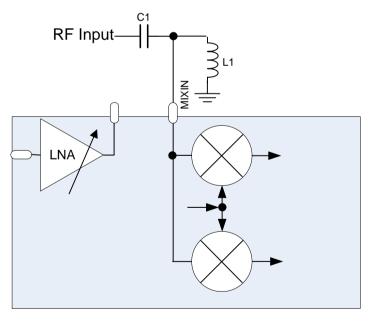

# 3 Block Diagram

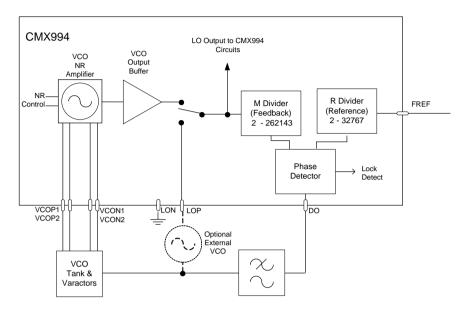

Figure 1 Block Diagram

# 4 Pin and Signal List

| Pin No            | Pin Name | Туре | Pin Function                                                             |

|-------------------|----------|------|--------------------------------------------------------------------------|

| 1                 | IFLT2N   | IP   | I channel 2 <sup>nd</sup> filter capacitor negative                      |

| 2                 | IFLT1P   | IP   | I channel 1 <sup>st</sup> filter capacitor positive                      |

| 3                 | IFLT1N   | IP   | I channel 1 <sup>st</sup> filter capacitor negative                      |

| 4                 | VCCRXIF  | PWR  | Supply for baseband circuits                                             |

| 5                 | VCCLNA   | PWR  | Supply for LNA                                                           |

| 6                 | LNAIN    | IP   | LNA input                                                                |

| 7                 | LNAOUT   | OP   | LNA output                                                               |

| 8                 | VCCRF    | PWR  | Supply for RF circuits                                                   |

| 9                 | MIXIN    | IP   | Rx mixer input                                                           |

| 10                | TXLO     | OP   | LO output for Tx                                                         |

| 11                | VCCLO    | PWR  | Supply for LO sections                                                   |

| 12                | LOP      | IP   | PLL LO positive input                                                    |

| 13                | LON      | IP   | PLL LO negative input                                                    |

| 14                | VCOP1    | IP   | PLL VCO positive input 1                                                 |

| 15                | VCOP2    | IP   | PLL VCO positive input 2                                                 |

| 16                | VCON1    | IP   | PLL VCO1 negative input 1                                                |

| 17                | VCON2    | IP   | PLL VCO1 negative input 2                                                |

| 18                | VCCSYNTH | PWR  | Supply to Integer N PLL                                                  |

| 19                | FREF     | IP   | Reference frequency input                                                |

| 20                | DO       | OP   | PLL Charge Pump output                                                   |

| 21                | DGND     | PWR  | Digital ground                                                           |

| 22                | TXEN     | IP   | Tx Enable                                                                |

| 23                | RXEN     | IP   | Rx Enable                                                                |

| 24                | CSN      | IP   | C-BUS Chip Select                                                        |

| 25                | RDATA    | TSOP | C-BUS Data output                                                        |

| 26                | SCLK     | IP   | C-BUS Clock input                                                        |

| 27                | CDATA    | IP   | C-BUS Data input                                                         |

| 28                | RESETN   | IP   | C-BUS/Device Reset (Reset when pin Low)                                  |

| 29                | DVDD     | PWR  | Supply to digital circuits                                               |

| 30                | VDDIO    | PWR  | Supply to C-BUS circuits                                                 |

| 31                | RREF     | IP   | Reference resistor for I/Q Filters                                       |

| 32                | QFLT1N   | IP   | Q channel 1 <sup>st</sup> filter capacitor negative                      |

| 33                | QFLT1P   | IP   | Q channel 1 <sup>st</sup> filter capacitor positive                      |

| 34                | QFLT2N   | IP   | Q channel 2 <sup>nd</sup> filter capacitor negative                      |

| 35                | QFLT2P   | IP   | Q channel 2 <sup>nd</sup> filter capacitor positive                      |

| 36                | RXQP     | OP   | RxQ positive output                                                      |

| 37                | RXQN     | OP   | RxQ negative output                                                      |

| 38                | RXIP     | OP   | RxI positive output                                                      |

| 39                | RXIN     | OP   | Rxl negative output                                                      |

| 40                | IFLT2P   | IP   | I channel 2 <sup>nd</sup> filter capacitor positive                      |

| EXPOSED METAL PAD | AGND     | PWR  | The exposed metal pad must be electrically connected to analogue ground. |

Total = 41 Pins (40 pins and central, exposed metal ground pad)

| Notes: | I/P | = | Input         | T/S | = | 3-state Output |

|--------|-----|---|---------------|-----|---|----------------|

|        | O/P | = | Output        | NC  | = | No Connection  |

|        | BI  | = | Bidirectional | PWR | = | Power          |

# 4.1 Signal Definitions

| Signal Name            | Pins                                              | Usage                                                                   |

|------------------------|---------------------------------------------------|-------------------------------------------------------------------------|

| $V_{max}$              |                                                   | The maximum value of the supplies DV <sub>DD</sub> and AV <sub>DD</sub> |

| $AV_{DD}$              | VCCRF, VCCRXIF, VCCSYNTH, VCCLO VCCLNA (see note) | Power supply for analogue circuits                                      |

| $DV_DD$                | DVDD                                              | Power supply for digital circuits                                       |

| VDD <sub>IO</sub>      | VDDIO                                             | Power supply voltage for digital interface (C-BUS)                      |

| DV <sub>SS</sub> (GND) | DGND                                              | Ground for digital circuits                                             |

| AV <sub>SS</sub> (GND) | AGND                                              | Ground for analogue circuits                                            |

Table 1 Definition of Power Supply and Reference Voltages

Note: The LNA has a separate power connection pin to provide isolation of non-differential signals. This may be connected to a common external supply with suitable de-coupling.

# 4.2 Connection of Unused Pins

If the CMX994/CMX994A/CMX994E/CMX994G/CMX994G VCO and PLL functions are not used then pins FREF, DO, VCOP1, VCOP2, VCON1 and VCON2 may be left unconnected.

# 5 External Components

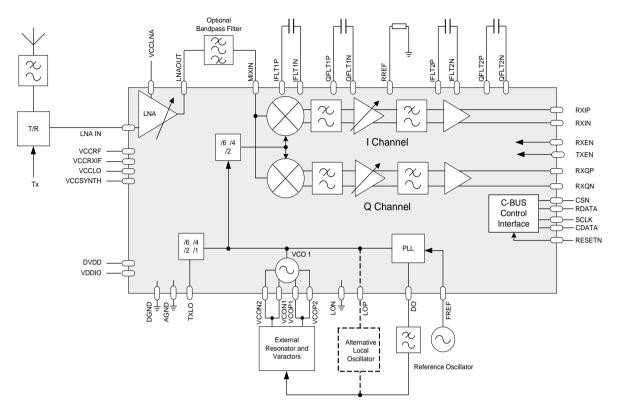

# 5.1 Power Supply and Decoupling

The CMX994/CMX994A/CMX994E/CMX994G have separate supply pins for the analogue and digital circuitry; a 3.3V nominal supply is recommended for all circuits but the data interface can run at a lower voltage than the rest of the device by setting the VDD<sub>IO</sub> supply to the required interface voltage.

Figure 2 Recommended Power Supply Connections and Decoupling

| C1 | 10nF       | R1 | 10Ω  |

|----|------------|----|------|

| C2 | 10nF       | R2 | 3.3Ω |

| C3 | 33pF//10nF | R3 | 3.3Ω |

| C4 | 10nF       | R4 | 3.3Ω |

| C5 | 10nF       | R5 | 3.3Ω |

| C6 | 10nF       | R6 | 10Ω  |

| C7 | 10nF       | R7 | 10Ω  |

**Table 2 Decoupling Components**

# Notes:

- 1. Maximum Tolerances: Resistors  $\pm 5\%$ , capacitors  $\pm 20\%$ .

- 2. It is expected that any low-frequency interference on the 3.3 Volt supply will be removed by active regulation; a large capacitor is an alternative but may require more board space and so may not be preferred. It is particularly important to ensure that there is no interference from the VDD<sub>IO</sub> (which supplies the digital I/O) or from any other circuit that may use the DV<sub>DD</sub> supply (such as a microprocessor), to sensitive analogue supplies (AV<sub>DD</sub>). It is therefore advisable to use separate power supplies for digital and analogue circuits.

- 3. The supply decoupling shown is intended for RF noise suppression. It is necessary to have a small series impedance prior to the decoupling capacitor for the decoupling to work well. This may be achieved cost effectively by using the resistor and capacitor values shown. The use of resistors results in small dc voltage drops (up to approx 0.1V). Choosing resistor values approximately inversely proportional to the dc current requirements of each supply ensures the dc voltage drop on each supply is reasonably matched. In any case, the resultant dc voltage change is well within the design tolerance of the device. If higher impedance resistors are used (not recommended) then greater care will be needed to ensure the supply voltages are maintained within tolerance, even when parts of the device are enabled or disabled.

- 4. It is advisable to have separate ground planes for analogue and digital circuits.

- 5. Separate regulators for local oscillator sections (VCCLO, VCCSYNTH) may be beneficial depending on circuit noise and type of regulator and this is why two AV<sub>DD</sub> connections are shown.

# 5.2 Receiver

# 5.2.1 LNA

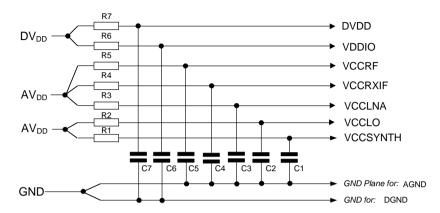

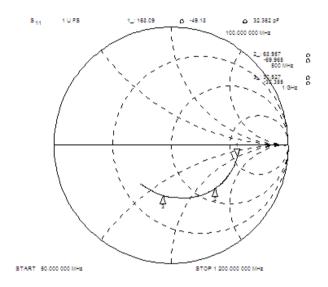

The following sections show plots and tables of the LNA input ( $S_{11}$ ) and output ( $S_{22}$ ) impedance. Separate data is shown for the  $50\Omega$  and  $100\Omega$  output modes which are selected by LNAZ<sub>0</sub> bit in the Rx Gain Register (b3, \$16; see section 7.7.1).

Note that at low frequencies capacitive loads on the LNA output are not recommended, a high-pass matching network is preferred.

# <u>50Ω Mode</u>

Figure 3 LNA S<sub>11</sub> (50Ω Mode)

Figure 4 LNA S<sub>22</sub> (50Ω Mode)

|               | S                     | 11                                    | S <sub>22</sub>       |                                    |  |

|---------------|-----------------------|---------------------------------------|-----------------------|------------------------------------|--|

| Freq<br>(MHz) | Impedance<br>(Ω-/+jΩ) | Equivalent Parallel<br>Circuit (R//C) | Impedance<br>(Ω-/+jΩ) | Equivalent Parallel Circuit (R//C) |  |

| 50            | 347 – j296            | 598.9R // 4.5pF                       | 54.4 – j2.4           | 54.5R // 2.6pF                     |  |

| 100           | 208 – j263            | 540.7R // 3.7pF                       | 54.8 + j0.4           | 54.8R                              |  |

| 150           | 129 – j217            | 496R // 3.6pF                         | 55.3 + j1.7           | 55.4R                              |  |

| 200           | 93 – j181             | 444.5R // 3.5pF                       | 56.1 + j2.9           | 56.3R                              |  |

| 250           | 72 – j154             | 401.1R // 3.4pF                       | 56.9 + j3.5           | 57.1R                              |  |

| 300           | 58 – j130             | 351R // 3.4pF                         | 57.4 + j3.9           | 57.6R                              |  |

| 350           | 49 – j114             | 318R // 3.4pF                         | 57.7 + j4.0           | 58.0R                              |  |

| 400           | 42 – j102             | 286.5R // 3.3pF                       | 58.1 + j3.9           | 58.4R                              |  |

| 450           | 37.7 – j91            | 256.3R // 3.3pF                       | 58.4 + j4.0           | 58.7R                              |  |

| 500           | 33.9 – j83            | 235.3R // 3.3pF                       | 58.4 + j4.2           | 58.7R                              |  |

| 550           | 29.7 – j74            | 211.8R // 3.4pF                       | 58.3 + j4.1           | 58.6R                              |  |

| 600           | 27.0 – j66            | 190.6R // 3.4pF                       | 57.9 + j3.9           | 58.2R                              |  |

| 650           | 24.7 – j61            | 173.1R // 3.5pF                       | 57.3 + j3.8           | 57.6R                              |  |

| 700           | 22.8 – j55            | 154.9R // 3.5pF                       | 56.7 + j3.9           | 57.0R                              |  |

| 750           | 21.3 – j50            | 136.7R // 3.6pF                       | 55.9 + j3.7           | 56.1R                              |  |

| 800           | 19.9 – j45            | 121.5R // 3.7pF                       | 55.3 + j3.6           | 55.5R                              |  |

| 850           | 18.7 – j41            | 107R // 3.8pF                         | 54.3 + j3.6           | 54.5R                              |  |

| 900           | 17.2 – j37.0          | 96.7R // 3.9pF                        | 52.8 + j3.9           | 53.1R                              |  |

| 950           | 15.7 – j32.9          | 84.6R // 4.1pF                        | 51.5 + j4.7           | 51.9R                              |  |

| 1000          | 14.8 – j29.1          | 72R // 4.3pF                          | 50.7 + j5.1           | 51.2R                              |  |

Table 3  $\,$  LNA  $S_{11}$  and  $S_{22}$  Impedances and Parallel Equivalent Circuit in  $50\Omega$  Mode

# 100Ω Mode

Figure 5 LNA  $S_{11}$  (100 $\Omega$  Mode)

Figure 6 LNA S<sub>22</sub> (100Ω mode)

|            |                       | S <sub>11</sub>                    | S <sub>22</sub>       |                                    |  |

|------------|-----------------------|------------------------------------|-----------------------|------------------------------------|--|

| Freq (MHz) | Impedance<br>(Ω-/+jΩ) | Equivalent Parallel Circuit (R//C) | Impedance<br>(Ω-/+jΩ) | Equivalent Parallel Circuit (R//C) |  |

| 50         | 355 – j291            | 592.6R // 4.4pf                    | 106 – j7.35           | 106.6R // 2.1pF                    |  |

| 100        | 210 – j267            | 549.1R // 3.7pF                    | 105 – j9.5            | 106R // 1.4pF                      |  |

| 150        | 128 – j222            | 510.6R // 3.6pF                    | 104 – j2.8            | 105.7R // 1.2pF                    |  |

| 200        | 92 – j186             | 469.9R // 3.4pF                    | 103 – j15.7           | 105.3R // 1.2pF                    |  |

| 250        | 70 – j157             | 422.4R // 3.4pF                    | 101 – j18.6           | 104.4R // 1.1pF                    |  |

| 300        | 56 – j134             | 376.9R // 3.4pF                    | 98 – j21.4            | 103R // 1.1pF                      |  |

| 350        | 45 – j117             | 345.3R // 3.4pF                    | 96 – j23.9            | 101.5R // 1.1pF                    |  |

| 400        | 38 – j103             | 313.1R // 3.4pF                    | 93 – j26.2            | 99.9R // 1.1pF                     |  |

| 450        | 34.1 – j91            | 279.2R // 3.4pF                    | 90 – j27.8            | 98.3R // 1.1pF                     |  |

| 500        | 30.5 – j82            | 253R // 3.4pF                      | 87 – j28.9            | 96.1R // 1.1pF                     |  |

| 550        | 26.4 – j73            | 228.9R // 3.5pF                    | 83 – j29.7            | 93.7R // 1.1pF                     |  |

| 600        | 24.0 – j66            | 203.6R // 3.6pF                    | 80 – j30.5            | 91.3R // 1.1pF                     |  |

| 650        | 21.7 – j59            | 183.3R // 3.7pF                    | 76 – j30.7            | 88.6R // 1.1pF                     |  |

| 700        | 19.9 – j53            | 162.3R // 3.8pF                    | 73 – j30.5            | 85.6R // 1.1pF                     |  |

| 750        | 18.7 – j47.7          | 140.8R // 3.9pF                    | 69 – j30.5            | 82.6R // 1.1pF                     |  |

| 800        | 17.5 – j42.8          | 122.2R // 4pF                      | 66 – j30.0            | 79.7R // 1.1pF                     |  |

| 850        | 16.5 – j38.3          | 105.5R // 4.1pF                    | 63 – j29.5            | 76.7R // 1.2pF                     |  |

| 900        | 15.4 – j34.4          | 92.2R // 4.3pF                     | 60 – j28.4            | 73R // 1.2pF                       |  |

| 950        | 14.2 – j30.5          | 79.6R // 4.5pF                     | 57 – j27.1            | 69.5R // 1.2pF                     |  |

| 1000       | 13.4 – j26.7          | 66.6R // 4.8pF                     | 54 – j26.0            | 66.3R // 1.2pF                     |  |

Table 4 LNA S11 and S22 Impedances and Parallel Equivalent Circuit in  $100\Omega$  Mode

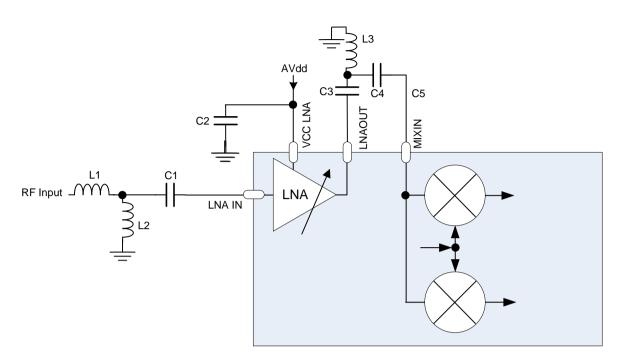

Figure 7 Recommended LNA Configuration and Inter-stage Match

| C1 | 1nF          | L1 | 150nH             |

|----|--------------|----|-------------------|

| C2 | 33pF // 10nF | L2 | 2.7pF (capacitor) |

| C3 | 18pF         | L3 | 150nH             |

Table 5 150MHz LNA and Inter-stage Components (100 $\Omega$  output mode)

| C1 | 1nF          | L1 | 39nH |

|----|--------------|----|------|

| C2 | 33pF // 10nF | L2 | 82nH |

| C3 | 10pF         | L3 | 27nH |

Table 6 450MHz LNA and Inter-stage Components (100 $\Omega$  output mode)

| C1 | 100pF       | L1 | 12nH  |

|----|-------------|----|-------|

| C2 | 33pF //10nF | L2 | 8.7nH |

| C3 | 4.7pF       | L3 | 5.6nH |

Table 7 900MHz LNA and Inter-stage Components (50Ω output mode)

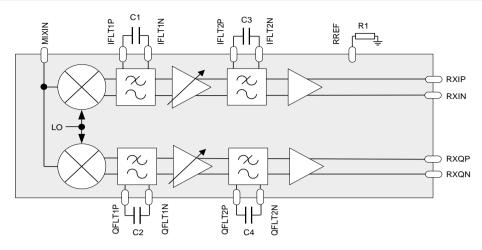

# 5.2.2 Mixers and Baseband Section

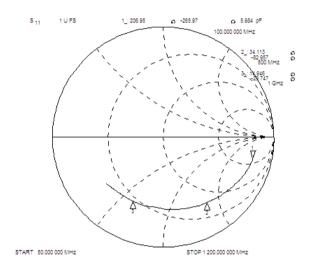

Figure 8 is a plot of the typical Rx Mixer input impedance; Table 8 gives the measured impedances and the equivalent parallel circuit at some particular frequencies.

Figure 8 Rx Mixer Input Impedance

| Frequency<br>(MHz) | Impedance<br>(Ω-/+jΩ) | Parallel Equivalent<br>Circuit (R // pF) |

|--------------------|-----------------------|------------------------------------------|

| 50                 | 180 – j35.2           | 186.6R // 3.34pF                         |

| 100                | 168 – j49.1           | 182.4R // 2.6pF                          |

| 150                | 153 – j64             | 180.1R// 2.5pF                           |

| 200                | 138 – j73             | 176.4R // 2.4pF                          |

| 250                | 124 – j77             | 171.4R // 2.3pF                          |

| 300                | 108 – j79             | 165.8R // 2.3pF                          |

| 350                | 96 – j79              | 160R // 2.3pF                            |

| 400                | 85 – j77              | 154.1R // 2.3pF                          |

| 450                | 76 – j74              | 147.3R // 2.3pF                          |

| 500                | 69 – j70              | 139.8R // 2.3pF                          |

| 550                | 61 – j66              | 131.5R // 2.4pF                          |

| 600                | 55 – j62              | 124R // 2.4pF                            |

| 650                | 50 – j58              | 116R // 2.4pF                            |

| 700                | 46.1 – j53            | 107.1R // 2.4pF                          |

| 750                | 42.7 – j48.9          | 98.9R // 2.5pF                           |

| 800                | 39.8 – j45.3          | 91.4R // 2.5pF                           |

| 850                | 37.2 – j41.6          | 83.7R // 2.5pF                           |

| 900                | 34.8 – j38.1          | 76.6R // 2.5pF                           |

| 950                | 32.3 – j34.9          | 70.2R // 2.6pF                           |

| 1000               | 30.3 – j31.6          | 63.2R // 2.6pF                           |

Table 8 CMX994 Rx Mixer Input Impedances and Parallel Equivalent Circuit

| Frequency | Impedance     | Parallel Equivalent |

|-----------|---------------|---------------------|

| (MHz)     | (Ω-/+jΩ)      | Circuit (R // pF)   |

| 50        | 172.74-j31.22 | 178.38R//3.23pF     |

| 100       | 162.72-j47.25 | 176.44R//2.62pF     |

| 150       | 148.61-j59.99 | 172.83R//2.48pF     |

| 200       | 132.91-j69.33 | 169.07R//2.46pF     |

| 250       | 116.95-j74.15 | 163.96R//2.46pF     |

| 300       | 101.79-j75.64 | 158R//2.5pF         |

| 350       | 88.21-j74.62  | 151.33R//2.54pF     |

| 400       | 76.188-j71.96 | 144.15R//2.61pF     |

| 450       | 66.61-j69.13  | 138.36R//2.65pF     |

| 500       | 58.42-j65.09  | 130.94R//2.71pF     |

| 550       | 52.03-j61.31  | 124.28R//2.74pF     |

| 600       | 46.01-j57.03  | 116.7R//2.82pF      |

| 650       | 41.25-j52.94  | 109.19R//2.88pF     |

| 700       | 37.19-j49.13  | 102.15R//2.94pF     |

| 750       | 34.2-j45.37   | 94.39R//2.98pF      |

| 800       | 31.82-j41.75  | 86.6R//3.01pF       |

| 850       | 29.54-j38.33  | 79.28R//3.06pF      |

| 900       | 27.05-j35.15  | 72.73R//3.16pF      |

| 950       | 24.62-j31.62  | 65.23R//3.3pF       |

| 1000      | 22.89-j28.17  | 57.56R//3.4pF       |

| 1050      | 21.58-j24.89  | 50.29R//3.48pF      |

| 1100      | 20.55-j21.44  | 42.92R//3.52pF      |

| 1150      | 19.56-j18.01  | 36.14R//3.53pF      |

| 1200      | 18.55-j14.59  | 30.03R//3.47pF      |

Table 9 CMX994A/CMX994E Rx Mixer Input Impedances and Parallel Equivalent Circuit

Figure 9 1218MHz Recommended Mixer Input Configuration

| C1 | 8.2pF | L1 | 1.8nH |

|----|-------|----|-------|

Table 10 1218MHz Mixer Input Matching Components

Figure 10 Recommended Receiver Circuit

| C1 | 1.5nF | C4 | 3.9nF |

|----|-------|----|-------|

| C2 | 1.5nF | R1 | 10kΩ  |

| C3 | 3.9nF |    |       |

**Table 11 Receiver Components**

The bandwidth of the first baseband filters is set by capacitors C1 and C2. Capacitors C3 and C4 together with the reference resistor R1 set the bandwidth of the second baseband filters. Component selection will vary depending on the desired filter bandwidths. For further details see sections 6.2.2 and 6.2.3.

#### 5.3 Local Oscillator

### 5.3.1 Local Oscillator Input

LON and LOP signals form a differential signal pair however the LO input may be driven by a single-ended source, in which case pin LOP should be connected to the LO signal and LON may be connected directly to ground. The inputs have internal ac coupling, so external dc blocking capacitors are not required.

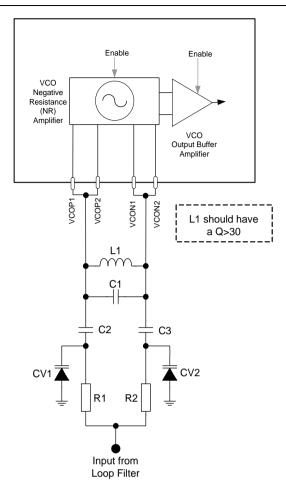

#### 5.3.2 VCO and PLL

A typical configuration for using the internal VCO negative resistance amplifier at 440MHz is shown in Figure 11. For the other external components required to complete the PLL (the loop filter components) see Figure 12 which shows a third-order loop filter. Typical values for a 500Hz bandwidth are given in Table 13.

VCOP1 should be shorted directly to VCOP2 and similarly VCON1 to VCON2 in order to form the negative resistance loop. It is recommended that the parallel LC tank (L1/C1) is situated as close to the package as possible, with the L closest to the device pins. Also the shorting of VCOP1 to VCOP2 and of VCON1 to VCON2 occurs as close as possible to the tank circuit – this minimises the effects of series inductance on the oscillator behaviour.

Figure 11 Example External Components – VCO External Tank Circuit

| L1 | 8.2nH (Note 1) | CV1 | SMV1705-079LF |

|----|----------------|-----|---------------|

| C1 | 8.2pF (Note 2) | CV2 | SMV1705-079LF |

| C2 | 22pF           | R1  | 10kΩ          |

| C3 | 22pF           | R2  | 10kΩ          |

Table 12 Internal VCO Amplifier Tank Circuit for 440MHz Operation

Note 1: Tolerance of 2% or better recommended Note 2: Tolerance of 5% or better recommended

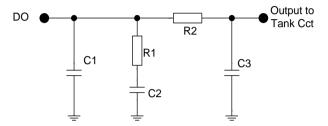

Figure 12 Example External Components – PLL Loop Filter

| C1 | 150nF  | R1 | 1.5kΩ |

|----|--------|----|-------|

| C2 | 1000nF | R2 | 2.4kΩ |

| C3 | 15nF   |    |       |

**Table 13 3rd Order Loop Filter Circuit Values**

# 5.4 RESETN

The RESETN pin generates a reset signal when low. The RESETN pin has an internal pull-up resistor of  $100k\Omega$  connected to VDD<sub>IO</sub>.

# 6 General Description

The architecture of the CMX994/CMX994A/CMX994E/CMX994G devices is shown in Figure 1. The CMX994/CMX994A/CMX994E/CMX994G are receiver ICs featuring very high IIP2 I/Q demodulators intended for use as a direct conversion receiver to zero IF, near-zero IF and low IF. The device has flexible LO inputs, integer-N PLL and an on-chip negative resistance amplifier which, with the addition of suitable external components, provides a VCO.

The receiver is fully integrated with a Low Noise Amplifier (LNA) preceding the down-converter section. The LNA may be configured with one of two possible output impedance settings ( $100\Omega$  or  $50\Omega$ ). With the  $50\Omega$  mode selected, there is more gain available but the circuit will consume an additional 2mA of current. The  $50\Omega$  mode has primarily been included for use at frequencies of 450MHz or higher. It should be noted that as the output impedance is not the same for each setting, the required matching components between the LNA and mixer will be different for each case.

The high-linearity down-converting mixers are immediately followed by a baseband filter stage. The bandwidth of this section is set by external capacitors. This first stage of filtering is designed to remove offchannel blocking signals prior to baseband amplification. Following these filters, gain is applied via a variable gain amplifier. Further filtering is then applied and again the bandwidth of the filters is determined by external capacitors. A reference resistor must also be fitted; this is used to calibrate the internal filter circuits to ensure the cut-off point of the filters is accurately controlled. This system allows effective correction for the analogue response to be applied in signal processing following CMX994/CMX994A/CMX994E/CMX994G. The output of the CMX994/CMX994A/CMX994E/CMX994G is differential I/Q signals; these may be applied to analogue-to-digital converters such as those in the CMX983, CMX910, CMX7163 or the CMX7164 ICs.

The receiver I/Q chain includes the facility to correct for inherent dc offsets in the hardware. This process is intended to optimise the dynamic range of the system and must be controlled by the microprocessor or DSP that processes the I/Q signals from the CMX994/CMX994A/CMX994E/CMX994G. DC offsets are a well-known issue with direct conversion receivers. In dynamic signal environments dc offset removal algorithms will be required to track and remove dc offsets generated by off-channel signals. Very high I/Q mixer IIP2 performance minimises such offsets. The receiver sections have a low power mode that reduces current. This mode may be used when reduced intermodulation performance is acceptable.

The Local Oscillator section features an integer-N Phase Locked Loop (PLL). This may be used with the on-chip VCO or with an external VCO. The on-chip VCO consists of a negative resistance amplifier and buffers, which allows an external inductor together with external varactor diodes to determine the operating frequency and tuning range. The use of external components allows optimum phase noise to be achieved. The Rx LO signal may be divided by 2, 4 or 6. There is also a Tx LO output provided and the Tx LO signal may be divided by 1, 2, 4 or 6. Alternatively the on-chip PLL and VCO can be disabled and an external LO source supplied.

All features of the CMX994/CMX994A/CMX994E/CMX994G may be controlled by the C-BUS control interface.

The following sections describe specific features of the CMX994/CMX994A/CMX994E/CMX994G.

#### 6.1 General Operation

#### 6.1.1 Rx/Tx Enable

The CMX994/CMX994A/CMX994E/CMX994G has Tx Enable and Rx Enable pins and the same function can be accessed via C-BUS using the General Control Register (section 7.2). The logical signals 'Tx ON' and 'Rx ON' are the ORed combination of the C-BUS signal and the hardware signals as shown in Table 14. Thus either C-BUS or hardware enable signals may be used, with the unused mode being set to 'O'.

| Tx (or Rx) Enable Pin | C-BUS Tx (or Rx) Enable | 'Tx ON' (or 'Rx ON') Result |

|-----------------------|-------------------------|-----------------------------|

| 0                     | 0                       | 0                           |

| 1                     | 0                       | 1                           |

| 0                     | 1                       | 1                           |

| 1                     | 1                       | 1                           |

Table 14 Tx (or Rx) Enable Operation

'Tx ON' enables the following sections of the device:

• Tx divider (see also Figure 1 and section 7.11.1.

'Rx ON' enables the following sections of the device:

- INA

- Down-converters and I/Q baseband amplifiers

- Rx LO divider

# 6.2 Receiver Operation

#### 6.2.1 DC Offset Correction

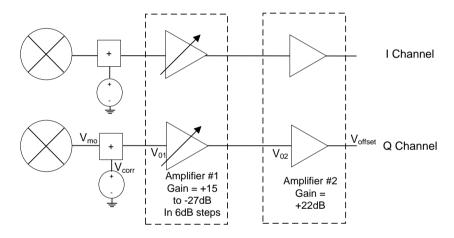

Digitally-controlled dc offset correction is provided which is capable of reducing the offset to 25mV or less for errors of up to +/-200mV¹ for CMX994 or up to +/-800mV for CMX994A/CMX994E. This represents a reduction in dynamic range of about 0.1dB for a typical ADC input signal range (2Vp-p) and is therefore negligible. The required correction must be measured externally as such measurements are application specific. The correction is applied close to the start of the I/Q baseband chain and therefore maximises dynamic range in the analogue sections.

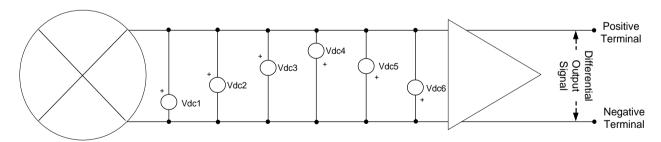

The correction is applied in a differential manner so positive and negative corrections are possible; see Figure 13. This allows the dc to be corrected to the nominal dc bias level. The voltage sources are scaled in a binary fashion so multiple sources can be added to provide the desired correction. The same arrangement applies independently on both I and Q channels. The CMX994 scheme, shown in Figure 13 / Table 15 is extended in the CMX994A/CMX994E with four additional sources to increase correction range.

Figure 13 Simplified Schematic of How DC Offset Corrections are Applied

<sup>&</sup>lt;sup>1</sup> This can be doubled to 400mV using bit 2 of the Rx Control Register (see section 7.3.1) although this also halves the resolution available.

| Source | Voltage Correction at Output<br>for Maximum Gain in<br>Baseband Amplifiers | Correction Polarity                                       |

|--------|----------------------------------------------------------------------------|-----------------------------------------------------------|

| Vdc1   | 25mV                                                                       | Positive terminal increase,<br>Negative terminal decrease |

| Vdc2   | 50mV                                                                       | Positive terminal increase,<br>Negative terminal decrease |

| Vdc3   | 100mV                                                                      | Positive terminal increase,<br>Negative terminal decrease |

| Vdc4   | 25mV                                                                       | Negative terminal increase,<br>Positive terminal decrease |

| Vdc5   | 50mV                                                                       | Negative terminal increase,<br>Positive terminal decrease |

| Vdc6   | 100mV                                                                      | Negative terminal increase,<br>Positive terminal decrease |

**Table 15 DC Offset Correction Adjustments**

#### 6.2.2 Receiver Filters and Bandwidth Options

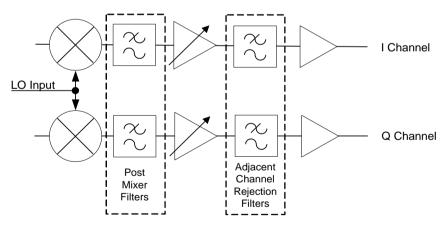

The I and Q channels incorporate two stages of filtering to reduce blocking signals and to attenuate nearby channels. This allows the wanted signal to be maximised without significant distortion being introduced as a result of unwanted larger signals saturating the later amplification stages.

The CMX994/CMX994A/CMX994E/CMX994G supports multiple channel bandwidths, providing scalable filtering in the baseband (I/Q) chain. Two filter stages are provided. The post mixer filter provides rejection of large off-channel signals such as those typically used in blocking tests. With this protection in place some gain is provided before narrower filters that provide rejection of the adjacent channel. Following this filter, the remainder of the receiver gain is provided. Both filter stages have single-pole characteristics, having -3dB frequency points set by separate external capacitors.

Figure 14 Baseband I/Q Filtering

After setting the second filter stage bandwidth via external capacitors, the bandwidth can then be scaled under serial control to allow multiple channel bandwidths to be supported by the CMX994/CMX994A/CMX994E/CMX994G. A typical requirement is to support 6.25kHz, 12.5kHz and 25kHz channels, so the scaling of the Adjacent Channel Rejection (ACR) filter is 1 : 2 : 4 via a bandwidth mode control. Using the recommended external capacitors for a 6.25kHz design (see 5.2.2), the ACR filter bandwidth (-3dB) is 2kHz. This provides 9dB rejection of the adjacent channel and 15dB rejection at 12.5kHz. Using the bandwidth scaling control, the 2kHz filter bandwidth can then be changed to 4kHz or 8kHz (see Rx Control Register, section 7.3), without changing external components. See also section 8.1.6.

The ACR filter may introduce some deterministic distortion in the signal passband, this distortion can be compensated by using filters external to the CMX994/CMX994A/CMX994E/CMX994G; see section 6.2.3 for further information.

The scaling of the post-mixer filter is less critical. The bandwidth (-3dB), using the recommended values, is approximately 88kHz (at maximum gain). This should be suitable for all the channel bandwidths up to 25kHz, so no scaling is provided. Note that the bandwidth of this section will reduce by 30% (typ.) as gain is reduced in the baseband section.

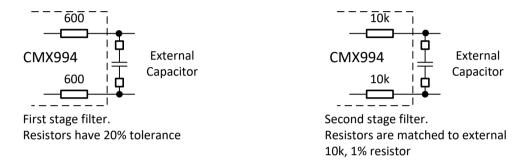

#### 6.2.3 Baseband Filter Design and Required Correction

The pole frequencies of the filter stages are set by the addition of external capacitors (see also section 5.2.2); the resistors are internal to the chip and those on the second filter stage are trimmed so as to match the external  $10k\Omega$  reference resistor<sup>2</sup>.

Figure 15 Schematic Representation of Filters used in the I and Q Paths

Filtering close to the passband distorts the signal and increases the BER, so it is necessary to provide correction for the filter distortion in subsequent external digital filtering.

Both filter stages are single-pole filters. The first filter stage is designed to reduce blocking signals and it will typically be set at 4 x the maximum required channel spacing. As a result, tolerance is not particularly critical and it is usually not necessary to compensate the wanted signal for this filter. The second filter is designed to operate close to, or within, the passband. It is therefore important that compensation is provided for the wanted signal.

Different modulation schemes occupy different bandwidths within a channel, so optimisation of the filter positioning will vary depending on the modulation scheme. Some experimentation may be required to get the best results but, as a guide, the second filter stage should have its frequency set to between 30% and 40% of the channel spacing. The aim is to reduce adjacent and close-in channels as much as possible. Provided the filter effects are compensated for later, the lowering of the signal amplitude at the band edges is usually well tolerated, although the extent of this will depend on the modulation scheme used.

The CMX994/CMX994A/CMX994E/CMX994G allows up to three different channel spacings to be selected via the C-BUS interface. So if, for example, the three channel spacings required are 6.25kHz, 12.5kHz and 25kHz, then the first filter should be set at a nominal desired frequency to ensure large blocking signals are rejected, typically a cut off frequency around 100kHz would be suitable. If only two channel spacings are required, of 6.25kHz and 12.5kHz for example, then it would be slightly beneficial to set the post mixer filter bandwidth to 50kHz.

Note that the three channel spacings are always in a 1:2:4 ratio relative to the smallest channel spacing, which is set by external components.

© 2020 CML Microsystems Plc D/994\_A\_E\_G/7

Page 21

<sup>&</sup>lt;sup>2</sup> The external resistor should be 1% tolerance or better.

The second stage filter capacitor should be selected for the smallest bandwidth requirement. The calculation for the capacitor value is as follows:

$$C = \frac{1}{2\pi f \, 20,000}$$

Where f = filter pole frequency (-3dB point).

So a capacitor of 4nF would yield a frequency pole of 1989Hz. This may be a typical figure when using a channel spacing of 6.25kHz. To maintain the accuracy of the compensation the capacitor must have a low temperature coefficient and tolerance better than or equal to 2%.

A compensation filter would need to be applied in the digital domain having the inverse characteristic. This would be:

$$H(s) = 1 + \frac{s}{2\pi f}$$

This would normally be implemented as a FIR filter. It should be followed with another non-critical FIR that rolls off the signal when out of band. This second filter may be part of a required channel filter.

Selecting 2x or 4x bandwidth will require the compensation filter to be adjusted in proportion.

The first stage filter capacitor may be calculated in a similar way:

$$C = \frac{1}{2\pi f 1200}$$

Where f = filter pole frequency (-3dB point).

So a capacitor of 1.5nF would yield a frequency pole of 88.4kHz. This may be a typical figure if the maximum channel spacing required were 25kHz. There is a wider tolerance on this, as the internal resistors are not trimmed. Consequently it is not required to have a low tolerance value on the first stage filter capacitor.

Should it be required to have this closer to the passband then a correction filter may be required. This would have the same form as for the correction filter for the second stage. In general a margin of at least 50% between the filter cut-off and wanted channel is recommended to allow for the resistor tolerances and bandwidth change with gain settings noted in section 6.2.2.

Because both filter stages are handling large dynamic signals, the linearity of the external capacitors is important. Use of good dielectric materials is recommended; poor linearity could result in a degradation of the on-channel signal in the presence of large off-channel interferers.

# 6.2.4 Operation at Wider Bandwidths

It is possible to use a much wider channel bandwidth than those used as examples elsewhere in this document. For maximum I/Q bandwidth (1.6MHz) capacitors C1, C2, C3 and C4 in Figure 10 should be removed. In this case the filter calibration circuit should be disabled using b7 of the VCO Control Register (\$25); see section 7.11.1.

For systems that require greater bandwidths the output should be taken before the baseband amplifiers and filters; see section 8.1.9.

### 6.3 Local Oscillator Operation

The CMX994/CMX994A/CMX994E/CMX994G can use either an external Local Oscillator (LO) source or the on-chip VCO and PLL. The on-chip integer-N PLL can also be used with an external VCO connected to the LO input.

#### 6.3.1 PLL

The CMX994/CMX994A/CMX994E/CMX994G provides an integer-N PLL that can be used to create the local oscillator; see Figure 16. The CMX994/CMX994A/CMX994E/CMX994G provides a VCO negative resistance amplifier, so only a tank circuit needs to be implemented externally. Alternatively, this amplifier can be bypassed and an external VCO can be used.

Figure 16 Local Oscillator

The integer-N PLL has programmable M and R dividers as shown in Figure 16. The phase detector provides a charge pump output which requires a suitable loop filter to convert this signal into a control voltage for a VCO. The phase detector can be turned off (high impedance mode) and the PLL section disabled if an external LO is to be used; see section 6.3.2 and 7.9 for control details.

The output frequency of the PLL is set by the following calculation:

$$f_{out} = f_{ref} x (M/R)$$

where:

f<sub>out</sub> = The desired output frequency in MHz

$f_{ref}$  = The reference frequency supplied to the PLL on pin FREF in MHz

M = Divider value programmed in the M divider register (see section 7.9.1)

R = Divider value programmed in the R divider register (see section 7.10.1)

The PLL only supports VCOs with a positive tuning slope, i.e. a higher tuning voltage from DO results in a higher oscillation frequency from the VCO.

The PLL has a lock-detect function that can be evaluated using register \$D2, b6 (section 7.9.2).

The VCO amplifier is a negative resistance amplifier requiring an external tank circuit (see section 5.3.2). The amplifier has two control bits available in the VCO control register (section 7.11.1 register \$25, b2 - b3). These bits can be used to optimise performance for a particular tank circuit depending on its Q value.

When using the CMX994/CMX994A/CMX994E/CMX994G PLL, spurious products (spurs) in the receiver I/Q output may be observed. The frequency of the spurs is linked to the PLL M divider value and which of the divide-by-2, 4 or 6 modes is selected for the receiver LO circuits. Operation in divide-by-2 and divide-by-6 modes is most predictable: all even division ratios are problem free and all odd division ratios will give a spurious product at:

$$f_{snur} = f_{lo} / (M * 2)$$

In divide-by-4 mode most odd divisions will produce a spur although at low frequencies (circa 100MHz) operation is spur-free. At circa 300MHz and above some even divisions are also problematic (in divide-by-4 mode).

It is recommended that for safe operation of the CMX994/CMX994E/CMX994G PLL, receiver LO divide-by-2 or divide-by-6 modes, with even division ratios, should be used.

When using the CMX994/CMX994A/CMX994E/CMX994G PLL, spurious can also be observed in the output from the TXLO pin. In this case the spurs are at small offsets from the wanted signal – the offset is linked to the PLL comparison frequency. The level of these spurs is typically at a very low (< -80 dBc) and less problematic than in the receiver.

#### 6.3.2 PLL Enable

The PLL block can be enabled from the General Control Register \$11, b2 (section 7.2.1) and the PLL M Divider Register \$22, b7 (section 7.9.1). An AND function is performed on these two bits (see table below).

| General Control<br>Register \$11, b2 | PLL M Divider<br>Register \$22, b7 | PLL Enable |

|--------------------------------------|------------------------------------|------------|

| 0                                    | 0                                  | No         |

| 0                                    | 1                                  | No         |

| 1                                    | 0                                  | No         |

| 1                                    | 1                                  | Yes        |

With the PLL disabled an external local oscillator may be supplied to the CMX994/CMX994A/CMX994E/CMX994G.

# 7 C-BUS Interface and Register Descriptions

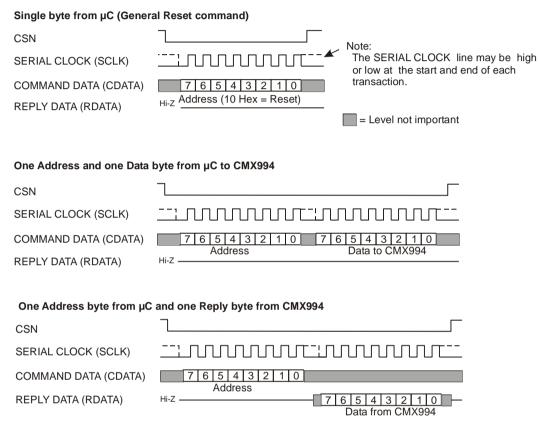

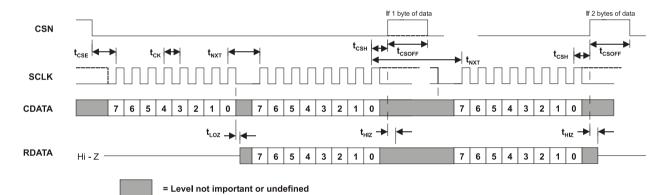

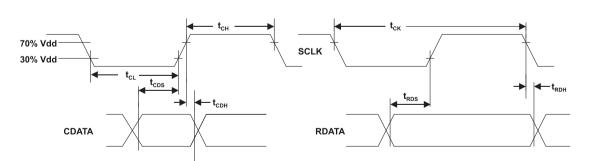

The C-BUS serial interface supports the transfer of data and control or status information between the CMX994/CMX994A/CMX994E/CMX994G's internal registers and an external host. Each C-BUS transaction consists of the host sending a single Register Address byte, which may then be followed by zero or more data bytes that are written into the corresponding CMX994/CMX994A/CMX994E/CMX994G register, as illustrated in Figure 17.

Data sent from the host on the Command Data (CDATA) line is clocked into the CMX994/CMX994A/CMX994E/CMX994G on the rising edge of the Serial Clock (SCLK) input. The C-BUS interface is compatible with common  $\mu$ C/DSP serial interfaces and may also be easily implemented with general purpose I/O pins controlled by a simple software routine. Section gives the detailed C-BUS timing requirements.

Whether a C-BUS register is of the read or write type, it is fixed for a given C-BUS register address thus one cannot both read and write the same C-BUS register address. The CMX994/CMX994A/CMX994E/CMX994G supports several pairs of C-BUS register addresses in order to read and write the same information.

In order to provide ease of addressing when using this device with the CMX998 (Cartesian Feed-back Loop Transmitter IC), the C-BUS addresses below are arranged so as not to overlap those used on the CMX998. Thus, a common chip select (CSN) signal can be used, as well as common CDATA (SDI on CMX998), RDATA (SDO on CMX998) and SCLK signals. Also note that the General Reset (\$10) command on the CMX994/CMX994A/CMX994E/CMX994G differs from other CML devices (such as CMX998), which use \$01 for this General Reset function. This allows the CMX994/CMX994E/CMX994G and CMX998 to be connected to the same interface pins, including chip select, assuming the drive capabilities of the host are adequate.

#### **C-BUS Write-only Registers**

| HEX<br>ADDRESS | REGISTER                                       | WORD SIZE<br>(BITS) |

|----------------|------------------------------------------------|---------------------|

| \$10           | General Reset Register (Address only, no data) | 0                   |

| \$11           | General Control Register, write only           | 8                   |

| \$12           | Rx Control Register, write only                | 8                   |

| \$13           | Rx Offset Register, write only                 | 8                   |

| \$14           | LNA IM Control Register, write only            | 8                   |

| \$15           | Options Control Register, write only           | 8                   |

| \$16           | Rx Gain Register, write only                   | 8                   |

| \$17           | Extended Rx Offset Register, write only        | 16                  |

| \$20-\$22      | PLL M Divider Register, write only             | 8                   |

| \$23-\$24      | PLL R Divider Register, write only             | 8                   |

| \$25           | VCO Control Register, write only               | 8                   |

#### **C-BUS Read-only Registers**

| HEX<br>ADDRESS | REGISTER                               | WORD SIZE<br>(BITS) |  |  |  |

|----------------|----------------------------------------|---------------------|--|--|--|

| \$E1           | General Control Register, read only    | 8                   |  |  |  |

| \$E2           | Rx Control Register, read only         | 8                   |  |  |  |

| \$E3           | Rx Offset Register, read only          | 8                   |  |  |  |

| \$E4           | LNA IM Control Register, read only     | 8                   |  |  |  |

| \$E5           | Options Control Register, read only    | 8                   |  |  |  |

| \$E6           | Rx Gain Register, read only            | 8                   |  |  |  |

| \$E7           | Extended Rx Offset Register, read only | 16                  |  |  |  |

| \$D0-\$D2      | PLL M Divider Register, read only      | 8                   |  |  |  |

| \$D3-\$D4      | PLL R Divider Register, read only 8    |                     |  |  |  |

| \$D5           | VCO Control Register, read only 8      |                     |  |  |  |

CMX994A and CMX994E. Specific bits control CMX994E features only. See register descriptions for details. CMX994A and CMX994E only

© 2020 CML Microsystems Plc D/994\_A\_E\_G/7

#### Notes:

- All registers will retain data if DVDD and VDDIO pins are held high, even if all other power supply pins are disconnected.

- If clock and data lines are shared with other devices, DVDD and VDDIO must be maintained in their normal operating ranges otherwise ESD protection diodes may cause a problem with loading the signals connected to SCLK, CDATA and RDATA pins, preventing correct programming of other devices. Other supplies may be turned off and all circuits on the device may be powered down without causing this problem.

Figure 17 C-BUS Transactions

# 7.1 General Reset: \$10 (no data)

A command to this register resets the device and clears all bits of all registers. The General Reset command places the device into powersave mode.

Whenever power is applied to the DVDD pin, a built-in power-on-reset circuit ensures that the device powers up into the same state as follows a General Reset command. The RESETN pin on the device will also reset the device to the same state.

# 7.2 General Control Register

#### 7.2.1 General Control: \$11 - 8-bit write only

This register controls general features such as powersave. All bits of this register are cleared to '0' by a General Reset command.

| 7       | 6     | 5     | 4  | 3     | 2     | 1    | 0    |

|---------|-------|-------|----|-------|-------|------|------|

| En Bias | Freq2 | Freq1 | LP | VCOEN | PLLEN | RXEN | TXEN |

#### b7 and 4-0:

These bits control power up/power down of the various blocks of the IC. In all cases '1' = power up, '0' = power down.

- b7 Enables BIAS generator

- b4 Enables low power mode. When b4 = '0' the device is operating normally, when b4= '1' the device will have reduced power consumption and reduced intermodulation performance. See also section 8.1.5 regarding other CMX994A/CMX994E low power modes.

- b3 Enables VCO: When b3 ='1' the setting of the VCO Control Register (\$25) takes effect. For details of VCO Control Register see section 7.11.

- b2 PLL Enable: This bit enables the PLL and is ANDed with PLL M-Divider Register (\$22) b7 section 7.9.1 See also section 6.3.2.

- b1 C-BUS Rx Enable; see section 6.1.1

- b0 C-BUS Tx Enable; see section 6.1.1

#### b6. b5

These bits optimise the amplitude of the local oscillator path within the device in order to maintain phase balance and noise performance of the receiver mixers over the full range of operating frequencies.

| b6 | b5 | Operation                                           |

|----|----|-----------------------------------------------------|

| 0  | 0  | 100MHz <sup>†</sup> – 150MHz                        |

| 0  | 1  | 150MHz – 300MHz                                     |

| 1  | 0  | 300MHz – 700MHz                                     |

| 1  | 1  | 700MHz – 1000MHz<br>(700MHz - 940MHz for<br>CMX994) |

#### Notes:

# 7.2.2 General Control: \$E1 - 8-bit read only

This register reads the value in register \$11; see section 7.2.1 for details of bit functions.

<sup>&</sup>lt;sup>†</sup> 30MHz for CMX994G.

# 7.3 Rx Control Register

#### 7.3.1 Rx Control: \$12 – 8-bit write only

This register controls general features of the receiver such as Powersave. All bits of this register are cleared to '0 by a General Reset command.

| 7       | 6      | 5       | 4        | 3        | 2        | 1    | 0    |

|---------|--------|---------|----------|----------|----------|------|------|

| Mix Pwr | IQ Pwr | LNA Pwr | ACR Flt2 | ACR Flt1 | DC Range | DIV2 | DIV1 |

b7-5 These bits control power up/power down of the various blocks of the IC. In all cases '0' = power up, '1' = power down.

| b7 | Disable receiver mixers and divider (see note)    |

|----|---------------------------------------------------|

| b6 | Disable baseband amplifier and filters (see note) |

| b5 | Disable LNA (see note)                            |

Note: These control signals disable the appropriate blocks of the receiver when 'Rx ON' is active. If 'Rx ON' is not active all receiver circuits will be in powersave mode.

b4,3 The baseband I/Q chain provides a narrow filter for rejecting adjacent channel signals. The bandwidth of this filter may be scaled using these bits. For further details see sections 6.2.2, 6.2.3 and 8.1.6.

| b4 | b3 | Function               |

|----|----|------------------------|

| 0  | 0  | Minimum bandwidth      |

| 0  | 1  | Intermediate bandwidth |

| 1  | 0  | Maximum bandwidth      |

| 1  | 1  | reserved, do not use   |

- When b2 = '0' the range of DC correction of the I/Q output is nominal (see sections 6.2.1 and 7.4). With b2 = '1' the total correction range is twice the nominal specified in section 7.4 with all steps doubled in value. Note: CMX994A/CMX994E provide an alternative method of achieving increased correction range without losing resolution using the Extended Rx Offset Register (\$17); see section 7.8.

- b1,0 Receiver LO divider control

| b1 | b0 | Function             |

|----|----|----------------------|

| 0  | 0  | LO divided by 2      |

| 0  | 1  | LO divided by 4      |

| 1  | 0  | LO divided by 6      |

| 1  | 1  | reserved, do not use |

#### 7.3.2 Rx Control: \$E2 - 8-bit read only

This read-only register mirrors the value in register \$12; see section 7.3.1 for details of bit functions.

# 7.4 Rx Offset Register

# 7.4.1 Rx Offset: \$13 – 8-bit write only

**Note:** Increased correction range is available in the CMX994A/CMX994E using register \$17; see section 7.8. The bits in registers \$13 and \$17 control the same hardware functions with the most recent write to \$17 or \$13 being applicable at any given time; if \$13 is written then QDC5, QDC4, IDC5 and IDC4 in \$17 are automatically set to '0'. All bits of registers \$13 and \$17 are cleared to '0' by a General Reset command.

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| QDC3 | QDC2 | QDC1 | QDC0 | IDC3 | IDC2 | IDC1 | IDC0 |

b7-0 I/Q DC offset correction; see section 6.2.1 for further details. The step size can be doubled using the Rx Control Register (\$12), b2; see section 7.3.1.

The values in the table below are the effects of the offset at the maximum VGA gain (minimum attenuation) setting. They are proportionately lower for lower gain settings (as set by the Rx Gain Register (b2 – b0). The aim of this Rx Offset Register is to allow output offsets to be reduced sufficiently (typically <25mV) to avoid any significant reduction in the dynamic range of any subsequent ADC. It is expected that demodulation software in the baseband processor would be required to correct for the remaining offset as part of the demodulation process.

See also section 8.1.2.

| b3 | b2 | b1 | b0 | I Channel at maximum gain |

|----|----|----|----|---------------------------|

| b7 | b6 | b5 | b4 | Q Channel at maximum gain |

| 1  | 1  | 1  | 1  | -175mV                    |

| 1  | 1  | 1  | 0  | -150mV                    |

| 1  | 1  | 0  | 1  | -125mV                    |

| 1  | 1  | 0  | 0  | -100mV                    |

| 1  | 0  | 1  | 1  | -75mV                     |

| 1  | 0  | 1  | 0  | -50mV                     |

| 1  | 0  | 0  | 1  | -25mV                     |

| 1  | 0  | 0  | 0  | No correction             |

| 0  | 1  | 1  | 1  | +175mV                    |

| 0  | 1  | 1  | 0  | +150mV                    |

| 0  | 1  | 0  | 1  | +125mV                    |

| 0  | 1  | 0  | 0  | +100mV                    |

| 0  | 0  | 1  | 1  | +75mV                     |

| 0  | 0  | 1  | 0  | +50mV                     |

| 0  | 0  | 0  | 1  | +25mV                     |

| 0  | 0  | 0  | 0  | No correction             |

# 7.4.2 Rx Offset: \$E3 - 8-bit Read only

This read-only register mirrors the value in register \$13; see section 7.4.1 for details of bit functions.

# 7.5 LNA Intermodulation Control Register

# 7.5.1 LNA IM Control: \$14 – 8-bit write only

This register controls features of the receiver that support intermodulation optimisation. All bits of this register are cleared to '0' by a General Reset command.

| 7 | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

|---|---|-----|-----|-----|-----|-----|-----|

| 0 | 0 | IM5 | IM4 | IM3 | IM2 | IM1 | IM0 |

b7,6 reserved, clear to '0'

b5-0 These bits allow the user to adjust the intermodulation performance of the LNA. The default value is '0' for all the bits. Improved intermodulation can be achieved with a particular value in these bits. For further details see section 8.1.4.

# 7.5.2 LNA IM Control: \$E4 – 8-bit read only

This read-only register mirrors the value in register \$14; see section 7.5.1 for details of bit functions.

# 7.6 Options Control Register – CMX994A and CMX994E only

# 7.6.1 Options Control: \$15 – 8-bit write only

This register controls options features added in the CMX994A and CMX994E devices only. All bits of this register are cleared to '0' by a General Reset command.

| 7    | 6        | 5        | 4        | 3   | 2   | 1     | 0     |

|------|----------|----------|----------|-----|-----|-------|-------|