# CMX885 Marine VHF Audio and Signalling Processor

D/885/4 June 2017

## Audio and Signalling Processing, DTMF, DSC/ATIS and NOAA with Auxiliary Functions for use in Marine VHF Systems

#### **Features**

- Concurrent Audio/Signalling/Data Operations

- Complete Audio-band Processing:

- Selectable Audio Processing Order

- o Pre and De-emphasis

- Selectable 2.55/3.0 kHz Filtering

- Limiter

- DSC/ATIS Modem for Marine Applications

- Programmable Voice Scrambler

- Inband Signalling: DTMF, NOAA NWR

- C-BUS Serial Interface to Host µController

- DTMF and Audio Tone Encoder/Decoder

- Small VQFN and LQFP Packages

- Dual Auxiliary ADC, 4 Multiplexed Inputs

- 4 x Auxiliary DACs

- Dual Programmable System Clock Outputs

- Tx Outputs for Single, Two-Point Modulation

- 3 x Analogue Inputs (Mic or Discriminator)

- Digital Gain Adjustment

- Default 3.6864MHz Xtal/Clock

- Flexible Powersave Modes

- Low-power 3.0V to 3.6V Operation

#### 1 Brief Description

The CMX885 is a half-duplex, audio, signalling and data processing IC for use in Marine VHF radio systems.

Comprehensive audio processing facilities include complete audio processing, filtering, pre- or deemphasis and frequency inversion scrambling. Signal routing and filtering is included to assist host  $\mu$ C based signal encoding/decoding applications.

1200bps Digital Selcall (DSC) or Automatic Transmitter Identification System (ATIS) modem with protocol support and NWR decoding are supported.

A DTMF encoder/decoder, a full complement of auxiliary ADCs and DACs and dual synthesised clock outputs are included in this low power PMR processor. The device also has flexible powersaving modes and is available in 48-pin VQFN and LQFP packages.

### **CONTENTS**

| Sect | <u>lion</u>                                       | Page |

|------|---------------------------------------------------|------|

| 1    | Brief Description                                 |      |

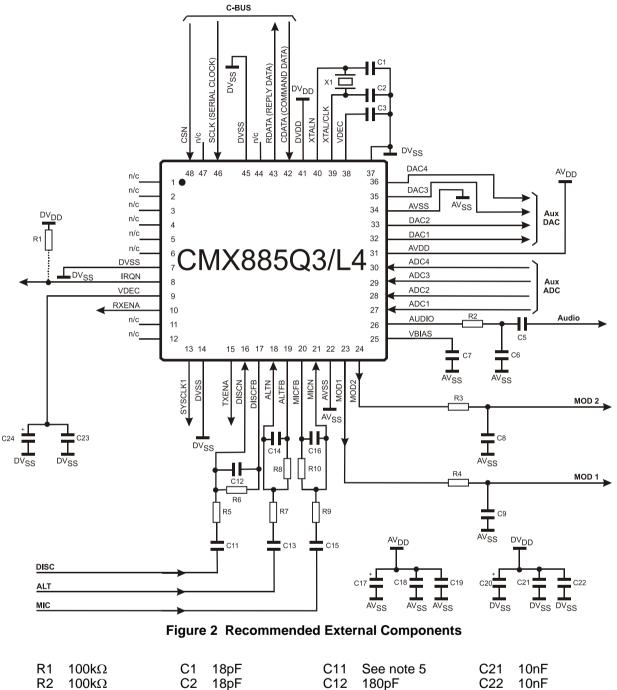

| 2    | Block Diagram                                     | 8    |

| 3    | Signal and Pin List                               | c    |

|      | 3.1 Signal Definitions                            |      |

| 4    | External Components                               |      |

| 5    | PCB Layout Guidelines and Power Supply Decoupling |      |

|      |                                                   |      |

| 6    | General Description                               |      |

| 7    | Detailed Descriptions                             |      |

|      | 7.1 Device Ident Code                             |      |

|      | 7.2 Xtal Frequency                                |      |

|      | 7.3 Host Interface                                |      |

|      | 7.4.1 Signal Routing                              |      |

|      | 7.4.2 Mode Control                                |      |

|      | 7.5 Audio Functions                               |      |

|      | 7.5.1 Audio Receive Mode                          |      |

|      | 7.5.2 Audio Transmit Mode                         |      |

|      | 7.6 Inband Signalling                             |      |

|      | 7.6.1 Receiving DTMF Tones                        |      |

|      | 7.6.2 Transmitting DTMF Tones                     |      |

|      | 7.7 DSC modem - (FSK 1200bps)                     |      |

|      | 7.7.1 Receiving DSC Signals                       | 27   |

|      | 7.7.2 Transmitting DSC Signals                    | 28   |

|      | 7.8 NOAA/NWR SAME and WAT Decoding                | 29   |

|      | 7.8.1 Message Code Format                         | 30   |

|      | 7.8.2 WAT Detection                               | 31   |

|      | 7.8.3 SAME Decoding                               | 31   |

|      | 7.9 Auxiliary ADC Operation                       |      |

|      | 7.10 Auxiliary DAC/RAMDAC Operation               |      |

|      | 7.11 Digital System Clock Generator               |      |

|      | 7.11.1 Main Clock Operation                       |      |

|      | 7.11.2 System Clock Operation                     |      |

|      | 7.12 GPIO                                         |      |

|      | 7.13 Signal Level Optimisation                    |      |

|      | 7.13.1 Transmit Path Levels                       |      |

|      | 7.13.2 Receive Path Levels                        |      |

|      | 7.14 C-BUS Interface                              |      |

|      | 7.14.1 Interrupt Operation                        |      |

| _    |                                                   |      |

| 8    | Configuration Guide                               |      |

|      | 8.1 C-BUS Register Summary                        |      |

|      | 8.1.1 Reset Operations                            | 37   |

|        | 8.1.2    | General Reset – \$01 write                         | 37          |

|--------|----------|----------------------------------------------------|-------------|

|        | 8.1.3    | AuxADC and Tx MOD Mode – \$A7 write                | 38          |

|        | 8.1.4    | AuxDAC Control/Data – \$A8 write                   | 39          |

|        | 8.1.5    | AuxADC1 Data – \$A9 read                           | 40          |

|        | 8.1.6    | AuxADC2 Data – \$AA read                           | 40          |

|        | 8.1.7    | SYSCLK1 and SYSCLK2 PLL Data – \$AB, \$AD write    | 41          |

|        | 8.1.8    | SYSCLK1 and SYSCLK2 REF – \$AC and \$AE write      | 41          |

|        | 8.1.9    | Analogue Output Gain – \$B0 write                  | 42          |

|        | 8.1.10   | Input Gain and Output Signal Routing – \$B1 write  | 43          |

|        | 8.1.11   | Reserved – \$B2 write                              | 44          |

|        | 8.1.12   | Reserved – \$B3 write                              | 44          |

|        | 8.1.13   | Reserved – \$B4 8-bit read                         | 44          |

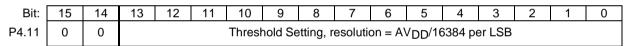

|        | 8.1.14   | AuxADC Threshold Data – \$B5 write                 | 44          |

|        | 8.1.15   | Reserved – \$B6 write                              | 44          |

|        | 8.1.16   | NWR Status and Data – \$BB read                    | 44          |

|        | 8.1.17   | Powerdown Control – \$C0 write                     | 44          |

|        | 8.1.18   | Mode Control – \$C1 write                          | 45          |

|        | 8.1.19   | Audio Control – \$C2 write                         | 46          |

|        | 8.1.20   | Tx Inband Tones – \$C3 write                       | 46          |

|        | 8.1.21   | Rx Data 1 – \$C5 read                              | 46          |

|        | 8.1.22   | Status – \$C6 read                                 | 47          |

|        | 8.1.23   | Modem Configuration – \$C7 write                   | 48          |

|        | 8.1.24   | Programming Register – \$C8 write                  | 48          |

|        | 8.1.25   | Tx Data 1 – \$CA write                             | 48          |

|        | 8.1.26   | Tone Status – \$CC read                            | 49          |

|        | 8.1.27   | Audio Tone – \$CD write                            | 50          |

|        | 8.1.28   | Interrupt Mask – \$CE write                        | 52          |

|        | 8.1.29   | Reserved – \$CF write                              | 53          |

| 8.     | 2 Pro    | ogramming Register Operation                       | 54          |

|        | 8.2.1    | Program Block 0 – Modem Configuration              | 55          |

|        | 8.2.2    | Program Block 1 – Inband Tone Setup                | 56          |

|        | 8.2.3    | Program Block 2 – reserved                         | 56          |

|        | 8.2.4    | Program Block 3 – AuxDAC, RAMDAC and Clock Control | 56          |

|        | 8.2.5    | Program Block 4 – Gain and Offset Setup            | 57          |

|        | 8.2.6    | Initialisation of the Program Blocks               | 61          |

| 9 P    | erforman | nce Specification                                  | 62          |

| 9.     |          | ectrical Performance                               |             |

|        | 9.1.1    | Absolute Maximum Ratings                           |             |

|        | 9.1.2    | Operating Limits                                   |             |

|        | 9.1.3    | Operating Characteristics                          |             |

|        | 9.1.4    | Parametric Performance                             |             |

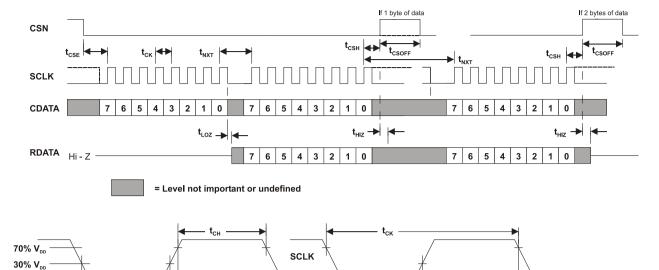

| 9.     | 2 C-I    | BUS Timing                                         |             |

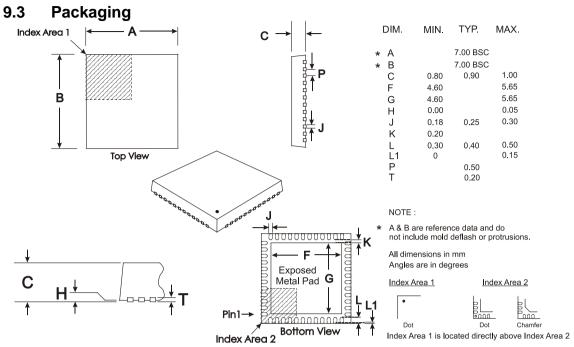

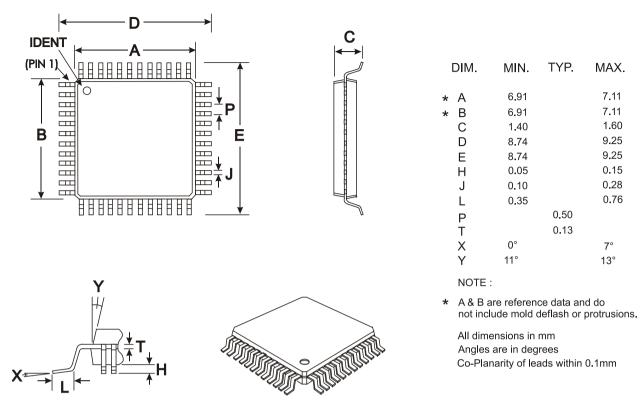

| 9.     |          | ckaging                                            |             |

| able   |          |                                                    | <u>Page</u> |

|        | 4 D-0-1  | San of Davis County and Defender Welling           | _           |

|        |          | tion of Power Supply and Reference Voltages        |             |

|        |          | ock Frequency Settings for Program Block 3         |             |

| i adie | 3 DIMP   | Tone Pairs                                         | 26          |

<u>Table</u>

| Table 4 Reset Operations                                      | 37          |

|---------------------------------------------------------------|-------------|

| Table 5 Voice Level Attenuation                               |             |

| Table 6 Output 1 and 2 Level Attenuation                      | 51          |

| Table 7 Program Block Selection                               | 54          |

| Table 8 RAMDAC Values                                         | 57          |

| Table 9 Output 1 and 2 Level Attenuation                      | 58          |

| <u>Figure</u>                                                 | <u>Page</u> |

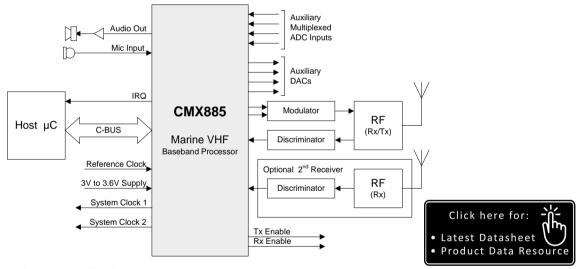

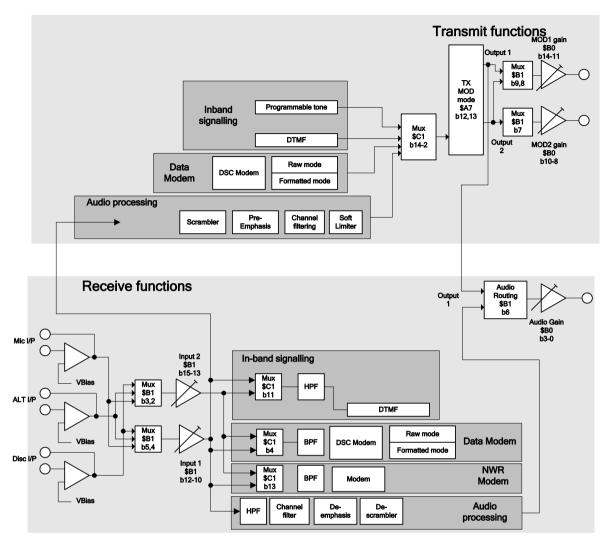

| Figure 1 Block Diagram                                        | 8           |

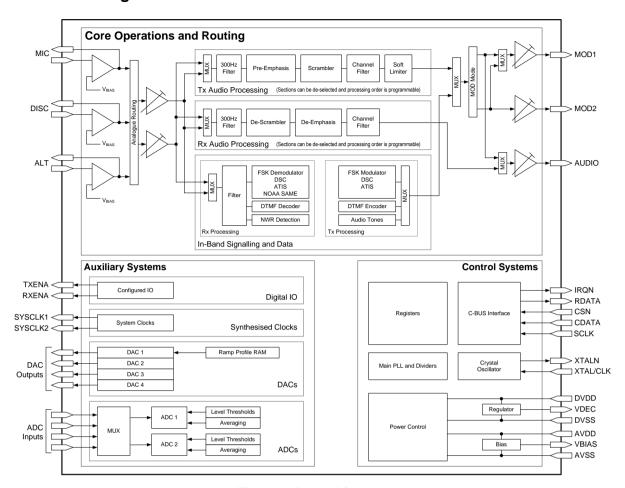

| Figure 2 Recommended External Components                      | 12          |

| Figure 3 Power Supply and De-coupling                         | 14          |

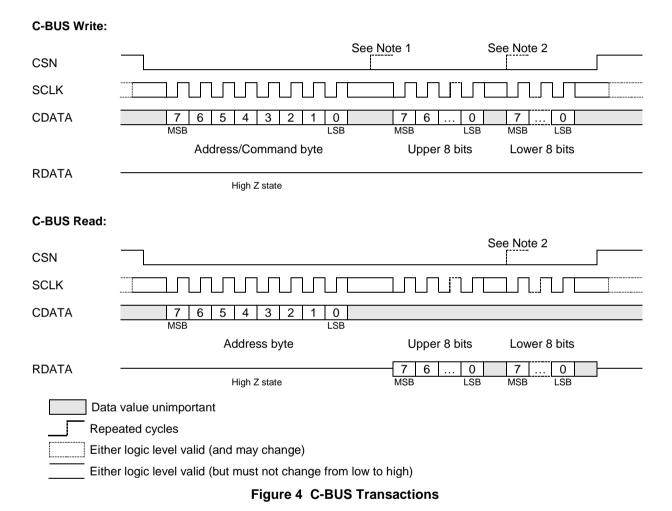

| Figure 4 C-BUS Transactions                                   | 17          |

| Figure 5 Signal Routing                                       | 19          |

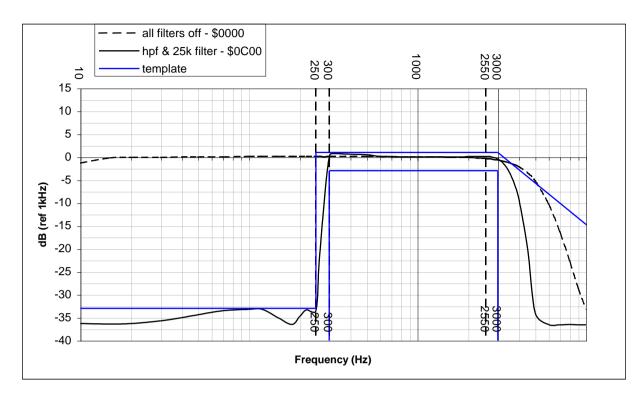

| Figure 6 Rx 25kHz Channel Audio Filter Frequency Response     | 21          |

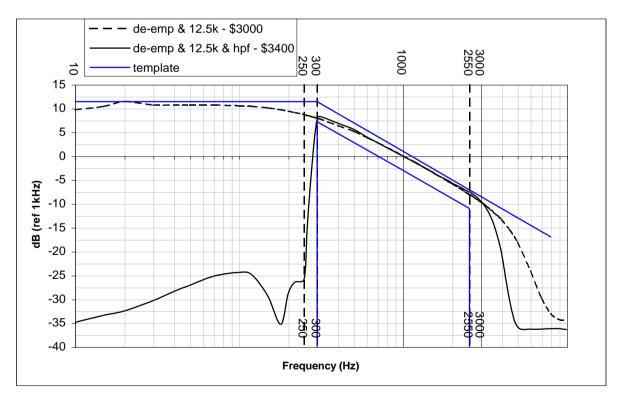

| Figure 7 De-emphasis Curve for TIA/EIA-603 Compliance         | 21          |

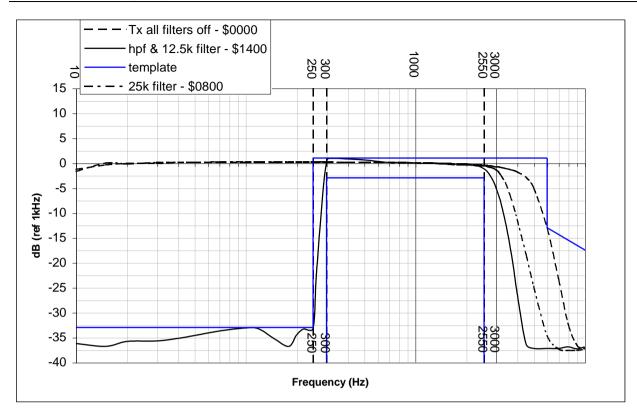

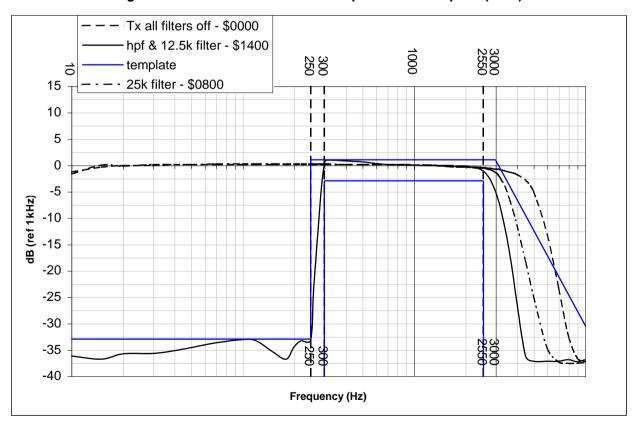

| Figure 8 Tx Channel Audio Filter Response and Template (ETSI) | 23          |

| Figure 9 Tx Channel Audio Filter Response and Template (TIA)  | 23          |

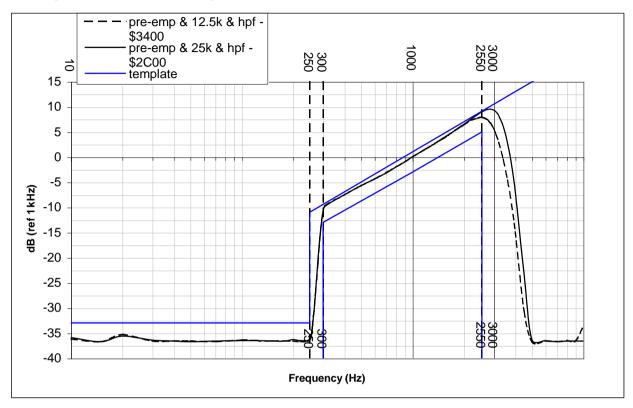

| Figure 10 Audio Frequency Pre-emphasis                        | 24          |

| Figure 11 DSC format                                          | 26          |

| Figure 12 DSC character format                                | 27          |

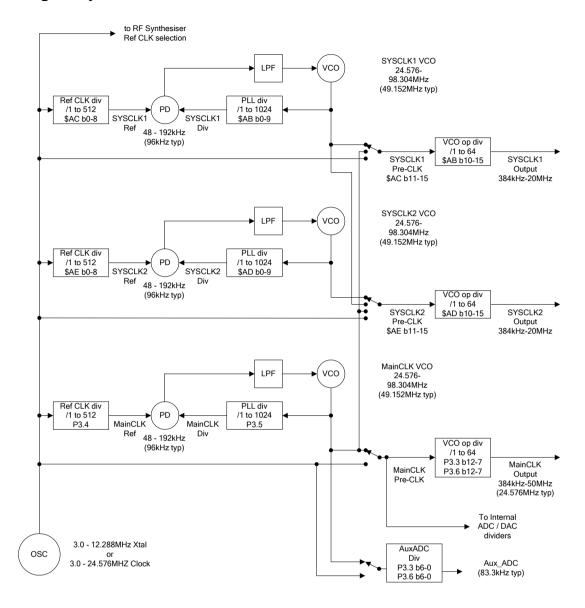

| Figure 13 Digital Clock Generation Schemes                    | 33          |

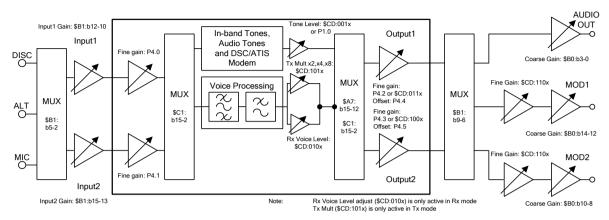

| Figure 14 Level Adjustments                                   | 35          |

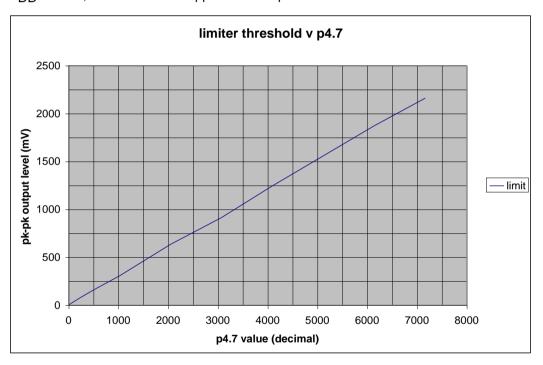

| Figure 15 Limiter Values                                      | 59          |

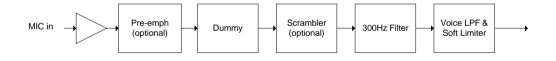

| Figure 16 Default Tx Audio Filter Line-up                     | 60          |

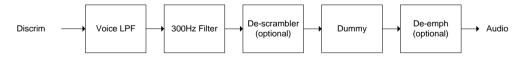

| Figure 17 Default Rx Audio Filter Line-up                     | 60          |

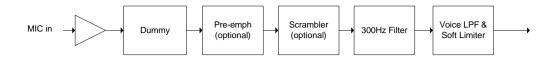

| Figure 18 Preferred Tx Audio Filter Line-up                   | 61          |

| Figure 19 Preferred Rx Audio Filter Line-up                   | 61          |

| Figure 20 C-BUS Timing                                        | 70          |

| Figure 21 Mechanical Outline of 48-pin VQFN (Q3)              | 71          |

| Figure 22 Mechanical Outline of 48-pin LOFP (L4)              | 72          |

It is always recommended that you check for the latest product datasheet version from the CML website: <a href="www.cmlmicro.com">www.cmlmicro.com</a>].

## 1.1 History

| <ul> <li>Version Changes</li> <li>Figure 1 (Block Diagram): 'Voice Filter' corrected to '300l processing</li> <li>Section 8.1.18: Removed statement regarding illegal sett same time</li> <li>Section 8.2.5: Description for \$C8 (P4.9) rewritten and Fimprove clarity for default and preferred options for Tx au</li> <li>Section 8.2.5: Figure 16 is updated and removed CTCSS previously incorrectly included</li> <li>Section 7.13.1: Maximum allowable input signal at MICF 54mV pk-pk (previously stated as 54mV rms)</li> <li>Section 8.1.27: Table 6 added, providing output 1 and 2 in Section 8.2.5: \$C8, P4.2-P4.3: Table added, providing out figures</li> <li>Section 9.1.3: AuxSYSCLK 1 and 2 output timing data active section 9.1: Device ident code (\$8850) added to description Section 8.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 sh not change</li> <li>Section 8.1.10: Added recommendation to introduce a performance of the previous part of t</li></ul>                                          | ing of b3 and b2 at the gure 16-18 updated to dio filter line-ups input that was B pin corrected to ine gain figures atput 1 and 2 fine gain ded ion t enhanced by own as reserved, do priod of >700µs option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16/06/17   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| <ul> <li>Section 8.1.18: Removed statement regarding illegal sett same time</li> <li>Section 8.2.5: Description for \$C8 (P4.9) rewritten and Frimprove clarity for default and preferred options for Tx au</li> <li>Section 8.2.5: Figure 16 is updated and removed CTCSS previously incorrectly included</li> <li>Section 7.13.1: Maximum allowable input signal at MICF 54mV pk-pk (previously stated as 54mV rms)</li> <li>Section 8.1.27: Table 6 added, providing output 1 and 2 in Section 8.1.27: Table 6 added, providing output 1 and 2 in Section 8.2.5: \$C8, P4.2-P4.3: Table added, providing output section 9.1.3: AuxSYSCLK 1 and 2 output timing data and section 9.1.3: AuxSYSCLK 1 and 2 output timing data and section 9.1.3: AuxSYSCLK 1 and 2 output timing data and section 8.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 sh not change</li> <li>Section 8.1.10: Added recommendation to introduce a performance of the section 8.1.14: Added AuxADC2 reference to b15 descriptions.</li> <li>Section 7.5.1: Footnote added concerning use of an audion of Section 9.1.14: Added AuxADC2 reference to b15 descriptions.</li> <li>Clarified operation of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified operation of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified operation of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified the need for observing C-BUS latency when write commands in section 7.3.</li> <li>Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.</li> <li>Changed "Modem Control" to "Modem Cofiguration" regions.</li> <li>Bit references changed to "\$C1:b12" style, for consistence Changed name of \$C1:b2 to "Modem Enable" and \$C!:b0.</li> <li>Deleted other references to "processing" in the description.</li> </ul>                                                                                             | gure 16-18 updated to dio filter line-ups input that was B pin corrected to ine gain figures atput 1 and 2 fine gain ded ion t enhanced by own as reserved, do priod of >700 µs option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| <ul> <li>same time</li> <li>Section 8.2.5: Description for \$C8 (P4.9) rewritten and Fi improve clarity for default and preferred options for Tx au</li> <li>Section 8.2.5: Figure 16 is updated and removed CTCSS previously incorrectly included</li> <li>Section 7.13.1: Maximum allowable input signal at MICF 54mV pk-pk (previously stated as 54mV rms)</li> <li>Section 8.1.27: Table 6 added, providing output 1 and 2 in Section 8.1.27: Table 6 added, providing output 1 and 2 in Section 8.2.5: \$C8, P4.2-P4.3: Table added, providing output 1 signares</li> <li>Section 7.6: DCS corrected to DSC</li> <li>Section 9.1.3: AuxSYSCLK 1 and 2 output timing data and section 9.1.3: AuxSYSCLK 1 and 2 output timing data and section 8.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 sh not change</li> <li>Section 8.1.10: Added recommendation to introduce a performance of the section 7.5.1: Footnote added concerning use of an audion section 7.5.1: Footnote added concerning use of an audion section 7.5.1: Footnote added concerning use of an audion section 7.3.</li> <li>Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.</li> <li>Changed "Modem Control" to "Modem Cofiguration" region Bit references changed to "\$C1:b12" style, for consistence Changed name of \$C1:b2 to "Modem Enable" and \$C!:b. Deleted other references to "processing" in the description of the processing of the description of the processing of the processing of the description of the processing of the processing of the description of the processing of the description of the processing of the processing of the description of the processing of the description of the processing of the processing of the description of the processing of the processing of the description of the processing of the processing of the processing of the processing of the</li></ul> | gure 16-18 updated to dio filter line-ups input that was B pin corrected to ine gain figures atput 1 and 2 fine gain ded ion t enhanced by own as reserved, do priod of >700 µs option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| <ul> <li>Section 8.2.5: Description for \$C8 (P4.9) rewritten and F improve clarity for default and preferred options for Tx au</li> <li>Section 8.2.5: Figure 16 is updated and removed CTCSS previously incorrectly included</li> <li>Section 7.13.1: Maximum allowable input signal at MICF 54mV pk-pk (previously stated as 54mV rms)</li> <li>Section 8.1.27: Table 6 added, providing output 1 and 2 in Section 8.2.5: \$C8, P4.2-P4.3: Table added, providing out figures</li> <li>Section 7.6: DCS corrected to DSC</li> <li>Section 9.1.3: AuxSYSCLK 1 and 2 output timing data action 5.2.1: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 shot change</li> <li>Section 8.1.10: Added recommendation to introduce a perfection of the section of the secti</li></ul>   | dio filter line-ups input that was  3 pin corrected to ine gain figures itput 1 and 2 fine gain  Ided ion t enhanced by own as reserved, do priod of >700µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| improve clarity for default and preferred options for Tx au Section 8.2.5: Figure 16 is updated and removed CTCSS previously incorrectly included Section 7.13.1: Maximum allowable input signal at MICF 54mV pk-pk (previously stated as 54mV rms) Section 8.1.27: Table 6 added, providing output 1 and 2 is Section 8.2.5: \$C8, P4.2-P4.3: Table added, providing output figures Section 7.6: DCS corrected to DSC Section 9.1.3: AuxSYSCLK 1 and 2 output timing data act Section 7.1: Device ident code (\$8850) added to descript Section 8.1.27: Description of audio tone level adjustment additional text and added examples Section 8.2.4: Default values of P3.8, P3.9 and P3.10 sh not change Section 8.1.10: Added recommendation to introduce a perfect between enabling Tx mode and enabling Tx function Section 8.1.14: Added AuxADC2 reference to b15 description 5.1: Footnote added concerning use of an audion Clarified operation of Data End bit (b7) for DSC Rx mode Clarified the need for observing C-BUS latency when write commands in section 7.3. Minor typographical corrections in table of section 8.1.27 values in section 8.2.5. Changed "Modem Control" to "Modem Cofiguration" regions are section 8.2.5. Changed name of \$C1:b2 to "Modem Enable" and \$C!:ba Deleted other references to "processing" in the description of Deleted other references to "processing" in the description of Deleted other references to "processing" in the description of Deleted other references to "processing" in the description of Deleted other references to "processing" in the description of Deleted other references to "processing" in the description of Deleted other references to "processing" in the description of Deleted other references to "processing" in the description of Deleted other references to "processing" in the description of Deleted other references to "processing" in the description of Deleted other references to "processing" in the description of Deleted other references to "processing" in the description of Deleted other references to "processing"            | dio filter line-ups input that was  3 pin corrected to ine gain figures itput 1 and 2 fine gain  Ided ion t enhanced by own as reserved, do priod of >700µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| <ul> <li>Section 8.2.5: Figure 16 is updated and removed CTCSS previously incorrectly included</li> <li>Section 7.13.1: Maximum allowable input signal at MICF 54mV pk-pk (previously stated as 54mV rms)</li> <li>Section 8.1.27: Table 6 added, providing output 1 and 2 in Section 8.2.5: \$C8, P4.2-P4.3: Table added, providing out figures</li> <li>Section 7.6: DCS corrected to DSC</li> <li>Section 9.1.3: AuxSYSCLK 1 and 2 output timing data and section 7.1: Device ident code (\$8850) added to description of audio tone level adjustment additional text and added examples</li> <li>Section 8.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 sh not change</li> <li>Section 8.1.10: Added recommendation to introduce a perfect between enabling Tx mode and enabling Tx function</li> <li>Section 8.1.14: Added AuxADC2 reference to b15 descriptions.</li> <li>Section 7.5.1: Footnote added concerning use of an audion content of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified operation of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified the need for observing C-BUS latency when write commands in section 7.3.</li> <li>Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.</li> <li>Changed "Modem Control" to "Modem Cofiguration" regions.</li> <li>Bit references changed to "\$C1:b12" style, for consistence Changed name of \$C1:b2 to "Modem Enable" and \$C!:base Deleted other references to "processing" in the description.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | input that was  input that was  input that was  input that was  input to a principle of the |            |

| previously incorrectly included  Section 7.13.1: Maximum allowable input signal at MICF 54mV pk-pk (previously stated as 54mV rms)  Section 8.1.27: Table 6 added, providing output 1 and 2 section 8.2.5: \$C8, P4.2-P4.3: Table added, providing of figures  Section 7.6: DCS corrected to DSC  Section 9.1.3: AuxSYSCLK 1 and 2 output timing data aces section 7.1: Device ident code (\$8850) added to descript Section 8.1.27: Description of audio tone level adjustment additional text and added examples  Section 8.2.4: Default values of P3.8, P3.9 and P3.10 shot change  Section 8.1.10: Added recommendation to introduce a perfect between enabling Tx mode and enabling Tx function  Section 8.1.14: Added AuxADC2 reference to b15 descriptions and Section 7.5.1: Footnote added concerning use of an audion Clarified operation of Data End bit (b7) for DSC Rx mode Clarified the need for observing C-BUS latency when write commands in section 7.3.  Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.  Changed "Modem Control" to "Modem Cofiguration" regions are references changed to "\$C1:b12" style, for consistence Changed name of \$C1:b2 to "Modem Enable" and \$C1:base Deleted other references to "processing" in the description of the processing of the provided           | B pin corrected to ine gain figures itput 1 and 2 fine gain ided ion it enhanced by own as reserved, do priod of >700µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| <ul> <li>Section 7.13.1: Maximum allowable input signal at MICF 54mV pk-pk (previously stated as 54mV rms)</li> <li>Section 8.1.27: Table 6 added, providing output 1 and 2 section 8.2.5: \$C8, P4.2-P4.3: Table added, providing of figures</li> <li>Section 7.6: DCS corrected to DSC</li> <li>Section 9.1.3: AuxSYSCLK 1 and 2 output timing data acesection 7.1: Device ident code (\$8850) added to description 5 section 8.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 shot change</li> <li>Section 8.1.10: Added recommendation to introduce a perbetween enabling Tx mode and enabling Tx function</li> <li>Section 8.1.14: Added AuxADC2 reference to b15 descriptions.</li> <li>Section 7.5.1: Footnote added concerning use of an audion Clarified operation of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified operation of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified the need for observing C-BUS latency when write commands in section 7.3.</li> <li>Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.</li> <li>Changed "Modem Control" to "Modem Cofiguration" regions.</li> <li>Bit references changed to "\$C1:b12" style, for consistence Changed name of \$C1:b2 to "Modem Enable" and \$C1:base Deleted other references to "processing" in the description.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ine gain figures atput 1 and 2 fine gain  Ided ion t enhanced by own as reserved, do ariod of >700µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

| <ul> <li>54mV pk-pk (previously stated as 54mV rms)</li> <li>Section 8.1.27: Table 6 added, providing output 1 and 2 in Section 8.2.5: \$C8, P4.2-P4.3: Table added, providing output 1 gigures</li> <li>Section 7.6: DCS corrected to DSC</li> <li>Section 9.1.3: AuxSYSCLK 1 and 2 output timing data and in Section 7.1: Device ident code (\$8850) added to description of audio tone level adjustment additional text and added examples</li> <li>Section 8.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 sh not change</li> <li>Section 8.1.10: Added recommendation to introduce a probetween enabling Tx mode and enabling Tx function</li> <li>Section 8.1.14: Added AuxADC2 reference to b15 descriptions.</li> <li>Section 7.5.1: Footnote added concerning use of an audion of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified operation of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified the need for observing C-BUS latency when write commands in section 7.3.</li> <li>Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.</li> <li>Changed "Modem Control" to "Modem Cofiguration" regions.</li> <li>Bit references changed to "\$C1:b12" style, for consistence of Changed name of \$C1:b2 to "Modem Enable" and \$C1:b2.</li> <li>Deleted other references to "processing" in the description.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ine gain figures atput 1 and 2 fine gain  Ided ion t enhanced by own as reserved, do ariod of >700µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

| <ul> <li>Section 8.1.27: Table 6 added, providing output 1 and 2 section 8.2.5: \$C8, P4.2-P4.3: Table added, providing of figures</li> <li>Section 7.6: DCS corrected to DSC</li> <li>Section 9.1.3: AuxSYSCLK 1 and 2 output timing data at Section 7.1: Device ident code (\$8850) added to description 8.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 sh not change</li> <li>Section 8.1.10: Added recommendation to introduce a perfect between enabling Tx mode and enabling Tx function</li> <li>Section 8.1.14: Added AuxADC2 reference to b15 descriptions.</li> <li>Section 7.5.1: Footnote added concerning use of an audion of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified operation of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified the need for observing C-BUS latency when write commands in section 7.3.</li> <li>Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.</li> <li>Changed "Modem Control" to "Modem Cofiguration" regions in the section 8.2.5.</li> <li>Changed name of \$C1:b2 to "Modem Enable" and \$C1:b0.</li> <li>Deleted other references to "processing" in the description</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ided Ided Ided Iden Iden Ided Iden Iden                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| <ul> <li>Section 8.2.5: \$C8, P4.2-P4.3: Table added, providing or figures</li> <li>Section 7.6: DCS corrected to DSC</li> <li>Section 9.1.3: AuxSYSCLK 1 and 2 output timing data action 7.1: Device ident code (\$8850) added to description 8.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 shot change</li> <li>Section 8.1.10: Added recommendation to introduce a perfect between enabling Tx mode and enabling Tx function</li> <li>Section 8.1.14: Added AuxADC2 reference to b15 descriptions.</li> <li>Section 7.5.1: Footnote added concerning use of an audion of Clarified operation of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified the need for observing C-BUS latency when write commands in section 7.3.</li> <li>Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.</li> <li>Changed "Modem Control" to "Modem Cofiguration" regions in the section 8.1.27 values in section 8.2.5.</li> <li>Changed name of \$C1:b2 to "Modem Enable" and \$C!:b0.</li> <li>Deleted other references to "processing" in the description</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ided Ided Ided Iden Iden Ided Iden Iden                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| figures  Section 7.6: DCS corrected to DSC  Section 9.1.3: AuxSYSCLK 1 and 2 output timing data actorized to Section 7.1: Device ident code (\$8850) added to description 8.1.27: Description of audio tone level adjustment additional text and added examples  Section 8.1.27: Default values of P3.8, P3.9 and P3.10 shot change  Section 8.2.4: Default values of P3.8, P3.9 and P3.10 shot change  Section 8.1.10: Added recommendation to introduce a per between enabling Tx mode and enabling Tx function  Section 8.1.14: Added AuxADC2 reference to b15 descriptions and the section 7.5.1: Footnote added concerning use of an audical collision of Data End bit (b7) for DSC Rx modes and clarified the need for observing C-BUS latency when write commands in section 7.3.  Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.  Changed "Modem Control" to "Modem Cofiguration" regions and the section 1.5 to "Modem Cofiguration" regions and the section 1.5 to "Modem Enable" and \$C!: b-1.5 to "Modem Enable" and \$C!: b-1.5 to "Modem Enable" and \$C!: b-1.5 to "Deleted other references to "processing" in the description of the processing in the processing in the description of the processing in the processing in t           | Ided ion t enhanced by own as reserved, do priod of >700 \mus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

| <ul> <li>Section 7.6: DCS corrected to DSC</li> <li>Section 9.1.3: AuxSYSCLK 1 and 2 output timing data actorized to section 7.1: Device ident code (\$8850) added to description 6.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 shot change</li> <li>Section 8.1.10: Added recommendation to introduce a perbetween enabling Tx mode and enabling Tx function</li> <li>Section 8.1.14: Added AuxADC2 reference to b15 descriptions.</li> <li>Section 7.5.1: Footnote added concerning use of an audion of Clarified operation of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified the need for observing C-BUS latency when write commands in section 7.3.</li> <li>Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.</li> <li>Changed "Modem Control" to "Modem Cofiguration" regions and the processing of the description of the description of processing of the description of the des</li></ul>    | t enhanced by  own as reserved, do  riod of >700µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| <ul> <li>Section 9.1.3: AuxSYSCLK 1 and 2 output timing data ad Section 7.1: Device ident code (\$8850) added to descript Section 8.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 shot change</li> <li>Section 8.1.10: Added recommendation to introduce a perbetween enabling Tx mode and enabling Tx function</li> <li>Section 8.1.14: Added AuxADC2 reference to b15 descriptions.</li> <li>Section 7.5.1: Footnote added concerning use of an audion of Clarified operation of Data End bit (b7) for DSC Rx modes.</li> <li>Clarified the need for observing C-BUS latency when write commands in section 7.3.</li> <li>Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.</li> <li>Changed "Modem Control" to "Modem Cofiguration" regions are section 8.2.5.</li> <li>Changed name of \$C1:b2 to "Modem Enable" and \$C!:b0.</li> <li>Deleted other references to "processing" in the description</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t enhanced by  own as reserved, do  riod of >700µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| <ul> <li>Section 7.1: Device ident code (\$8850) added to description of section 8.1.27: Description of audio tone level adjustment additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 shot change</li> <li>Section 8.1.10: Added recommendation to introduce a perbetween enabling Tx mode and enabling Tx function</li> <li>Section 8.1.14: Added AuxADC2 reference to b15 descriptions.</li> <li>Section 7.5.1: Footnote added concerning use of an audion of Clarified operation of Data End bit (b7) for DSC Rx moders.</li> <li>Clarified the need for observing C-BUS latency when write commands in section 7.3.</li> <li>Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.</li> <li>Changed "Modem Control" to "Modem Cofiguration" regions and section 8.2.5.</li> <li>Changed name of \$C1:b2 to "Modem Enable" and \$C!:b0.</li> <li>Deleted other references to "processing" in the description</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t enhanced by  own as reserved, do  riod of >700µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| <ul> <li>Section 8.1.27: Description of audio tone level adjustmer additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 sh not change</li> <li>Section 8.1.10: Added recommendation to introduce a perbetween enabling Tx mode and enabling Tx function</li> <li>Section 8.1.14: Added AuxADC2 reference to b15 descriction Section 7.5.1: Footnote added concerning use of an audion of Clarified operation of Data End bit (b7) for DSC Rx moders of Clarified the need for observing C-BUS latency when write commands in section 7.3.</li> <li>Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.</li> <li>Changed "Modem Control" to "Modem Cofiguration" regions in the section 8.1.27 values in section 8.2.5.</li> <li>Changed name of \$C1:b2 to "Modem Enable" and \$C!:b0.</li> <li>Deleted other references to "processing" in the description</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | t enhanced by  own as reserved, do  riod of >700µs  otion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

| <ul> <li>additional text and added examples</li> <li>Section 8.2.4: Default values of P3.8, P3.9 and P3.10 sh not change</li> <li>Section 8.1.10: Added recommendation to introduce a perbetween enabling Tx mode and enabling Tx function</li> <li>Section 8.1.14: Added AuxADC2 reference to b15 descrition</li> <li>Section 7.5.1: Footnote added concerning use of an audition of Clarified operation of Data End bit (b7) for DSC Rx moderical commands in section 7.3.</li> <li>Minor typographical corrections in table of section 8.1.27 values in section 8.2.5.</li> <li>Changed "Modem Control" to "Modem Cofiguration" regions and the processing of the processing of the description of the processing of the processing of the processing of the description of the processing of the proce</li></ul>     | own as reserved, do<br>riod of >700µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |