#### Table of Contents-

| 1. | GENE  | ERAL DES                                                                         | CRIPTION                                                     | 4  |  |

|----|-------|----------------------------------------------------------------------------------|--------------------------------------------------------------|----|--|

| 2. |       |                                                                                  |                                                              |    |  |

| 3. | ORDI  | ER INFORI                                                                        | MATION                                                       | 4  |  |

| 4. | KEY   | KEY PARAMETERS                                                                   |                                                              |    |  |

| 5. | PIN C | ONFIGUR                                                                          | ATION                                                        | 6  |  |

| 6. | PIN D | DESCRIPTI                                                                        | ON                                                           | 7  |  |

| 7. | BLOC  | CK DIAGRA                                                                        | ۱M                                                           | 8  |  |

| 8. | FUNC  | CTIONAL D                                                                        | ESCRIPTION                                                   | 9  |  |

|    | 8.1   | Power Up Sequence                                                                |                                                              |    |  |

|    | 8.2   | Commar                                                                           | nd Function                                                  |    |  |

|    |       | 8.2.1                                                                            | Bank Activate Command                                        |    |  |

|    |       | 8.2.2                                                                            | Bank Precharge Command                                       | 10 |  |

|    |       | 8.2.3                                                                            | Precharge All Command                                        | 10 |  |

|    |       | 8.2.4                                                                            | Write Command                                                | 10 |  |

|    |       | 8.2.5                                                                            | Write with Auto-precharge Command                            | 10 |  |

|    |       | 8.2.6                                                                            | Read Command                                                 | 10 |  |

|    |       | 8.2.7                                                                            | Read with Auto-precharge Command                             | 10 |  |

|    |       | 8.2.8                                                                            | Mode Register Set Command                                    | 11 |  |

|    |       | 8.2.9                                                                            | Extended Mode Register Set Command                           | 11 |  |

|    |       | 8.2.10                                                                           | No-Operation Command                                         | 11 |  |

|    |       | 8.2.11                                                                           | Burst Read Stop Command                                      | 11 |  |

|    |       | 8.2.12                                                                           | Device Deselect Command                                      | 11 |  |

|    |       | 8.2.13                                                                           | Auto Refresh Command                                         | 11 |  |

|    |       | 8.2.14                                                                           | Self Refresh Entry Command                                   | 12 |  |

|    |       | 8.2.15                                                                           | Self Refresh Exit Command                                    | 12 |  |

|    |       | 8.2.16                                                                           | Data Write Enable /Disable Command                           | 12 |  |

|    | 8.3   | Read Op                                                                          | eration                                                      | 12 |  |

|    | 8.4   | Write Op                                                                         | eration                                                      | 13 |  |

|    | 8.5   | Precharg                                                                         | je                                                           | 13 |  |

|    | 8.6   | Burst Te                                                                         | rmination                                                    | 13 |  |

|    | 8.7   | Refresh                                                                          | Operation                                                    | 13 |  |

|    | 8.8   | Power Down Mode<br>Input Clock Frequency Change during Precharge Power Down Mode |                                                              |    |  |

|    | 8.9   |                                                                                  |                                                              |    |  |

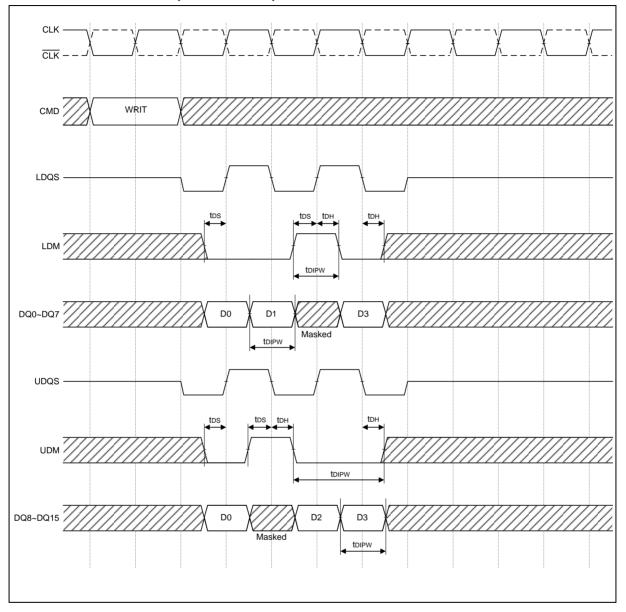

|    | 8.10  | Mode Re                                                                          | gister Operation                                             |    |  |

|    |       | 8.10.1                                                                           | Burst Length field (A2 to A0)                                |    |  |

|    |       | 8.10.2                                                                           | Addressing Mode Select (A3)                                  |    |  |

|    |       | 8.10.3                                                                           | CAS Latency field (A6 to A4)                                 | 16 |  |

|    |       | 8.10.4                                                                           | DLL Reset bit (A8)                                           | 16 |  |

|    |       | 8.10.5                                                                           | Mode Register /Extended Mode register change bits (BA0, BA1) | 16 |  |

|     |       | 8.10.6 Extended Mode Register field                                       |         |

|-----|-------|---------------------------------------------------------------------------|---------|

|     |       | 8.10.7 Reserved field                                                     |         |

| 9.  | OPER  | RATION MODE                                                               | 17      |

|     | 9.1   | Simplified Truth Table                                                    | 17      |

|     | 9.2   | Function Truth Table                                                      |         |

|     | 9.3   | Function Truth Table for CKE                                              | 21      |

|     | 9.4   | Simplified Stated Diagram                                                 | 22      |

| 10. | ELEC  | TRICAL CHARACTERISTICS                                                    |         |

|     | 10.1  | Absolute Maximum Ratings                                                  |         |

|     | 10.2  | Recommended DC Operating Conditions                                       | 23      |

|     | 10.3  | Capacitance                                                               | 24      |

|     | 10.4  | Leakage and Output Buffer Characteristics                                 | 24      |

|     | 10.5  | DC Characteristics                                                        | 25      |

|     | 10.6  | AC Characteristics and Operating Condition                                |         |

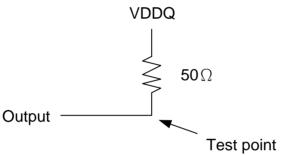

|     | 10.7  | AC Test Conditions                                                        | 27      |

| 11. | SYSTI | EM CHARACTERISTICS FOR DDR SDRAM                                          | 29      |

|     | 11.1  | Table 1: Input Slew Rate for DQ, DQS, and DM                              |         |

|     | 11.2  | Table 2: Input Setup & Hold Time Derating for Slew Rate                   |         |

|     | 11.3  | Table 3: Input/Output Setup & Hold Time Derating for Slew Rate            | 29      |

|     | 11.4  | Table 4: Input/Output Setup & Hold Derating for Rise/Fall Delta Slew Rate |         |

|     | 11.5  | Table 5: Output Slew Rate Characteristics (x16 Devices only)              |         |

|     | 11.6  | Table 6: Output Slew Rate Matching Ratio Characteristics                  | 30      |

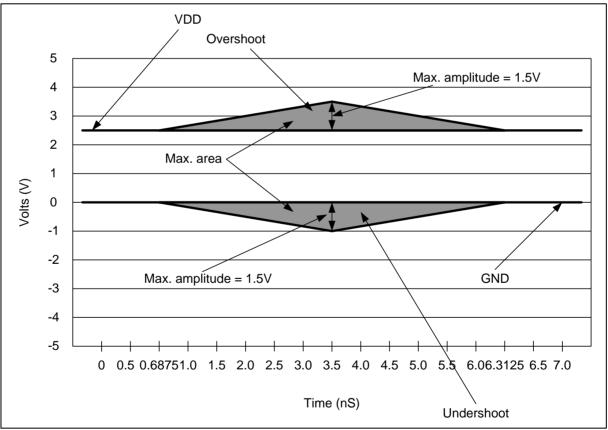

|     | 11.7  | Table 7: AC Overshoot/Undershoot Specification for Address and Control    | Pins 30 |

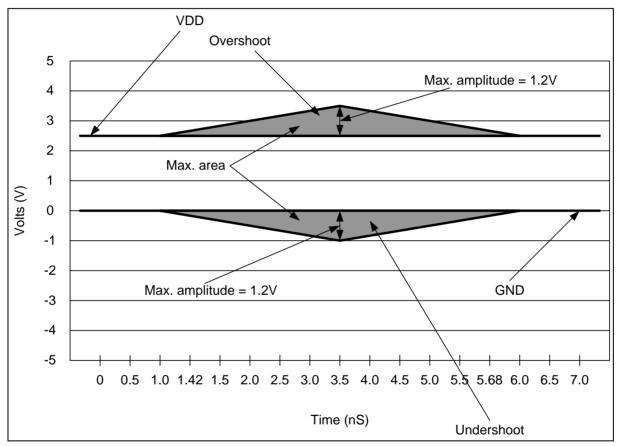

|     | 11.8  | Table 8: Overshoot/Undershoot Specification for Data, Strobe, and Mask F  |         |

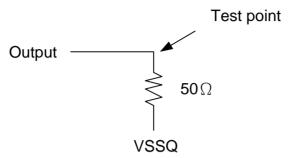

|     | 11.9  | System Notes:                                                             | 32      |

| 12. | TIMIN | IG WAVEFORMS                                                              | 34      |

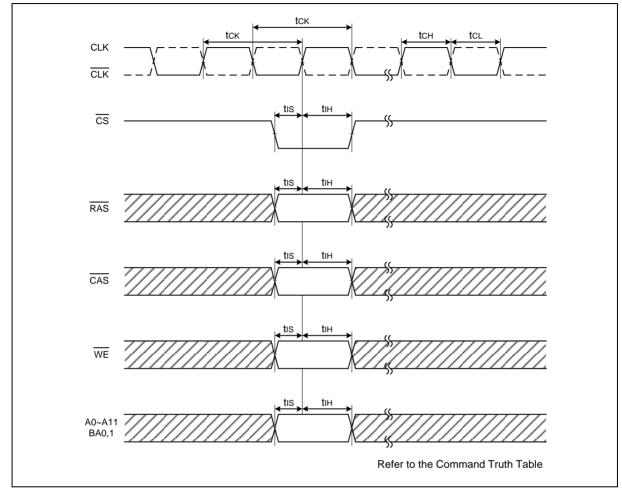

|     | 12.1  | Command Input Timing                                                      | 34      |

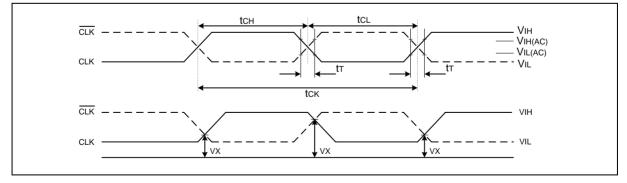

|     | 12.2  | Timing of the CLK Signals                                                 |         |

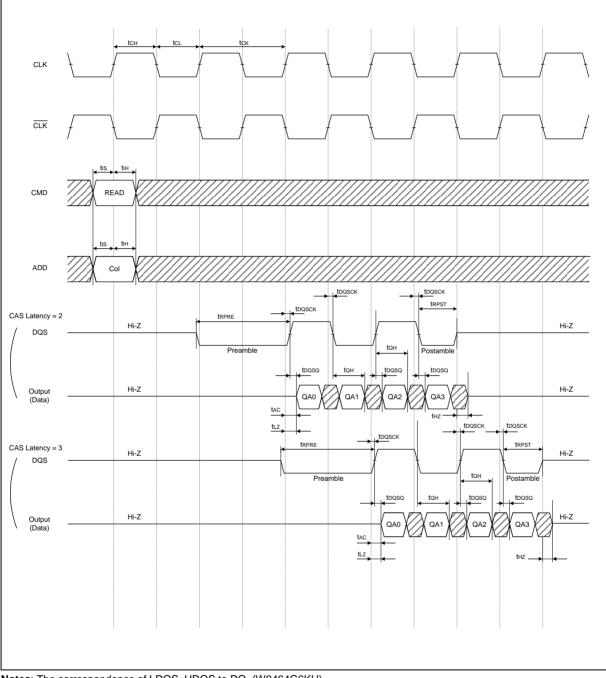

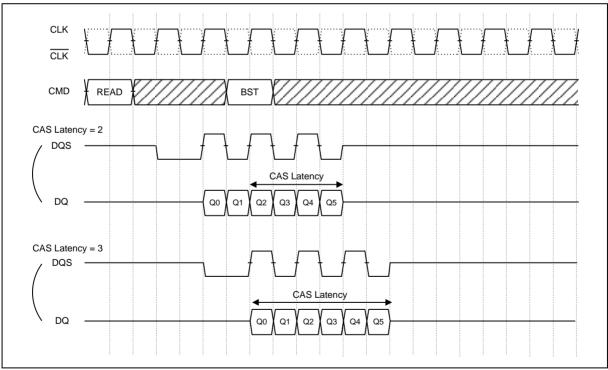

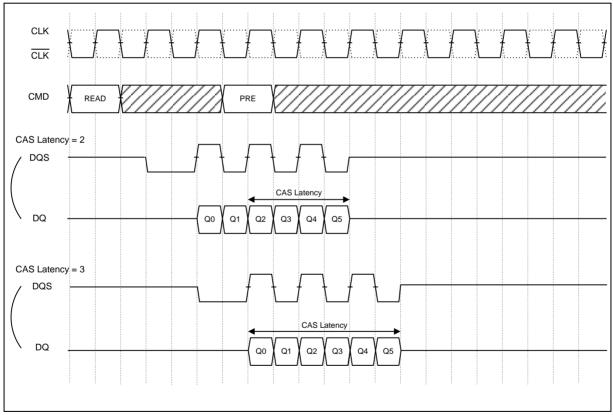

|     | 12.3  | Read Timing (Burst Length = 4)                                            |         |

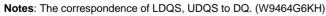

|     | 12.4  | Write Timing (Burst Length = 4)                                           |         |

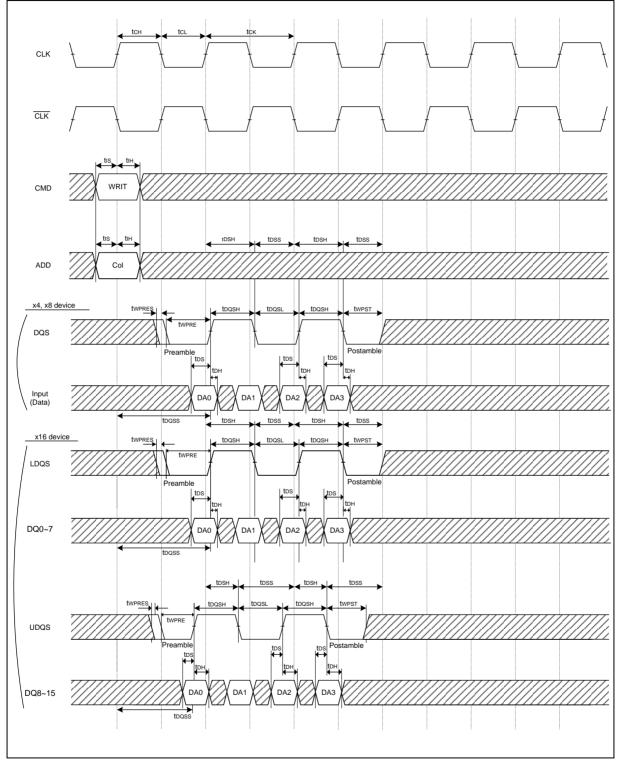

|     | 12.5  | DM, DATA MASK (W9464G6KH)                                                 |         |

|     | 12.6  | Mode Register Set (MRS) Timing                                            |         |

|     | 12.7  | Extend Mode Register Set (EMRS) Timing                                    |         |

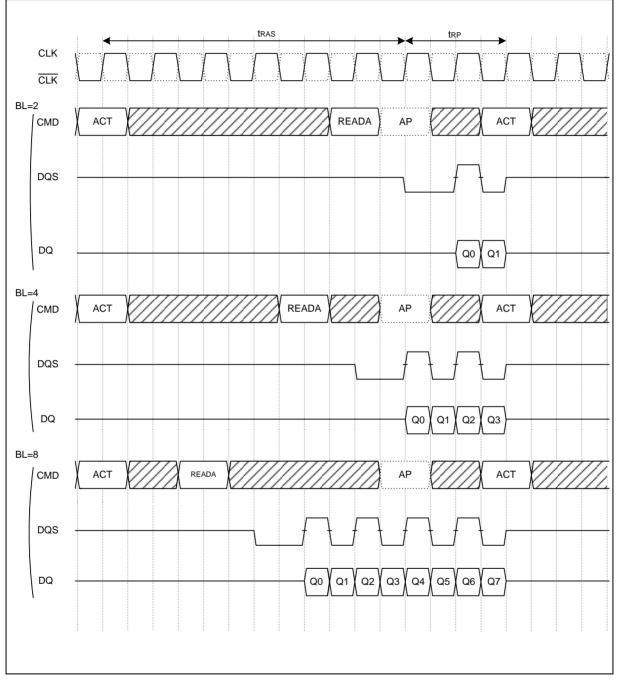

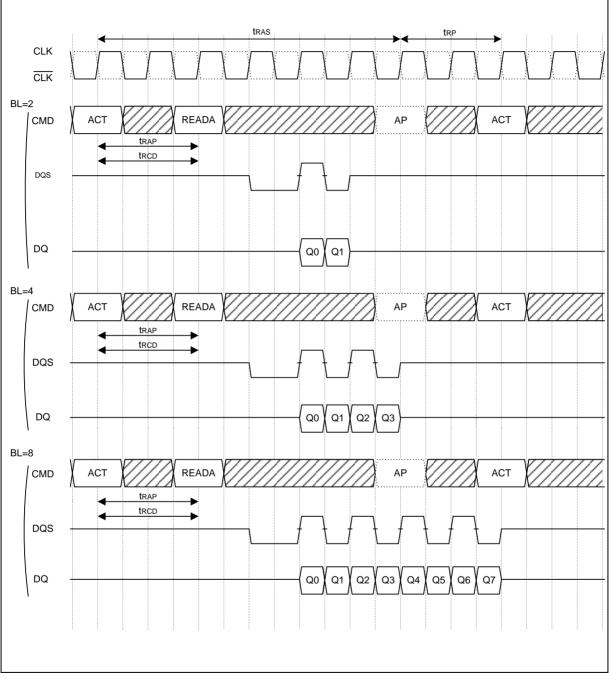

|     | 12.8  | Auto-precharge Timing (Read Cycle, CL = 2)                                |         |

|     | 12.9  | Auto-precharge Timing (Read cycle, CL = 2), continued                     |         |

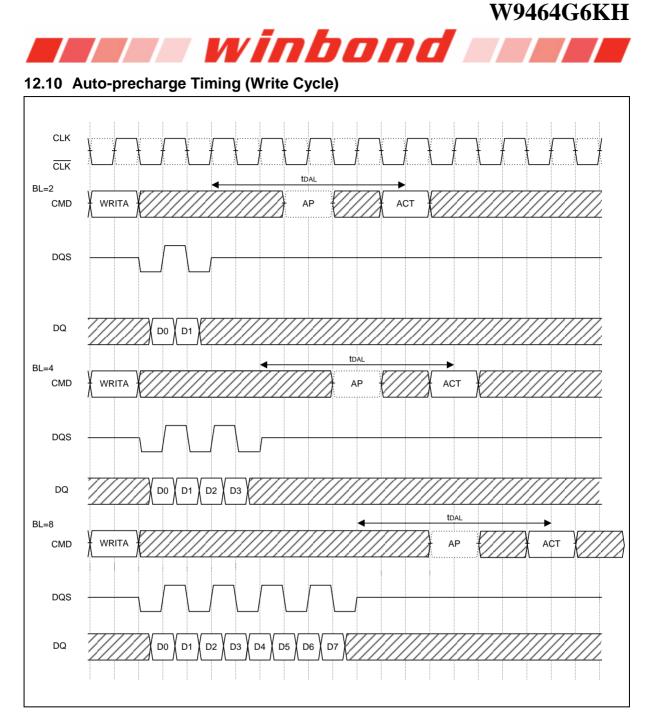

|     | 12.10 |                                                                           |         |

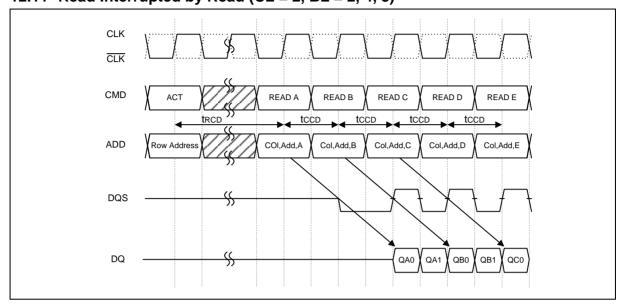

|     | 12.11 | Read Interrupted by Read ( $CL = 2$ , $BL = 2$ , 4, 8)                    |         |

|     | 12.12 |                                                                           |         |

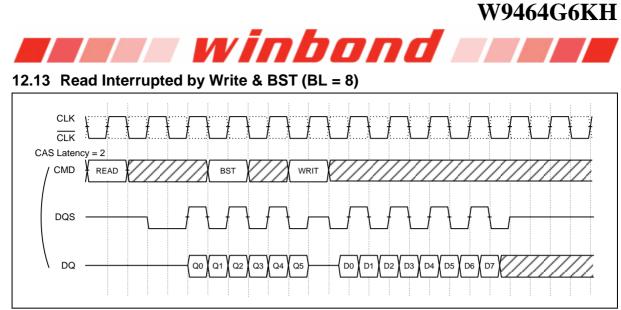

|     | 12.13 |                                                                           |         |

|     | 12.14 |                                                                           |         |

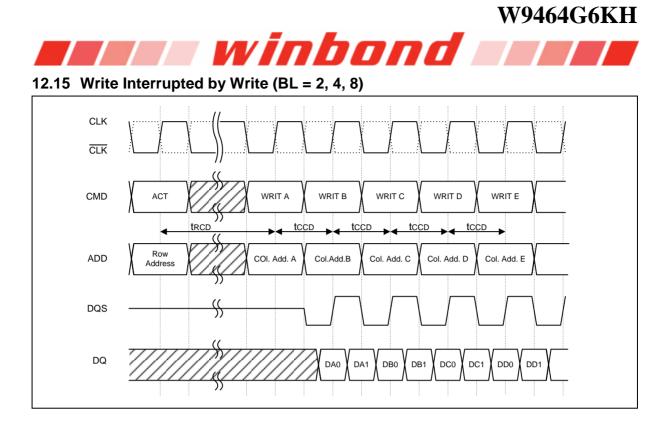

|     | 12.15 |                                                                           |         |

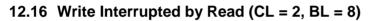

|     | 12.16 |                                                                           |         |

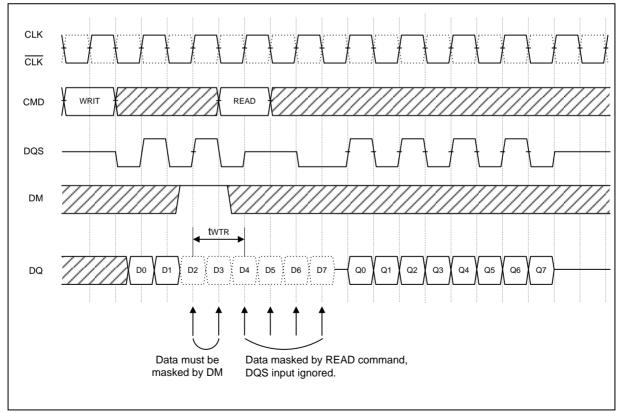

|     | 12.17 |                                                                           |         |

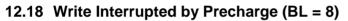

|     | 12.18 |                                                                           |         |

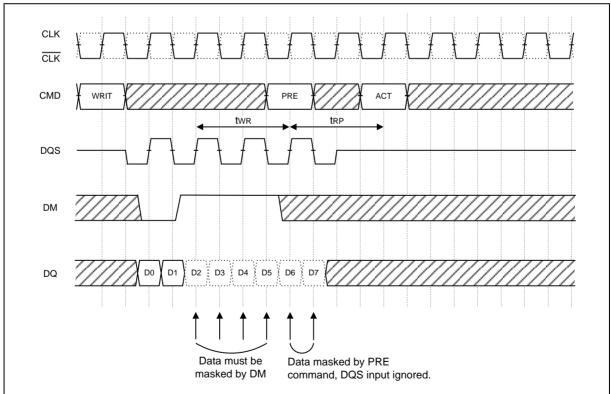

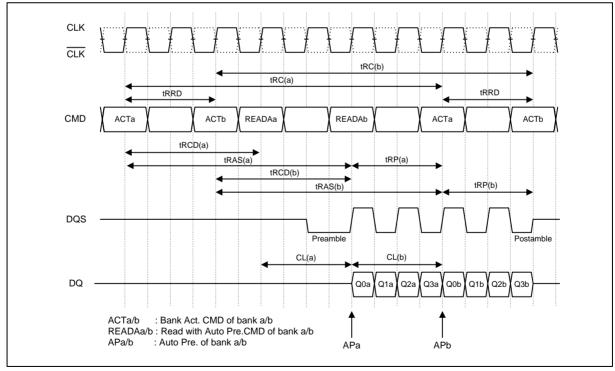

|     | 12.19 | 2 Bank Interleave Read Operation (CL = 2, BL = 2)                         |         |

.

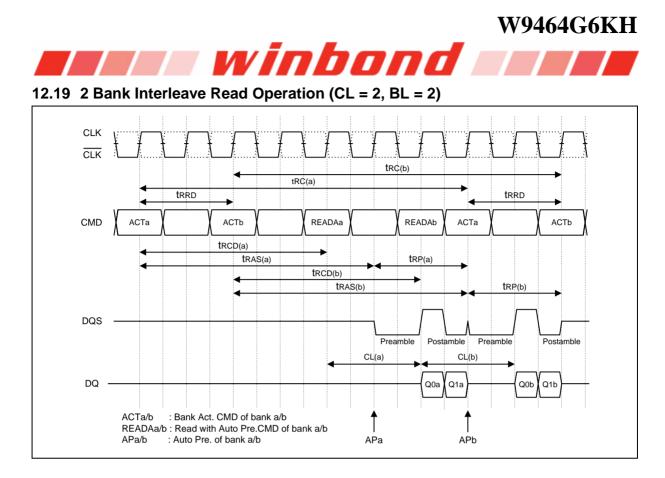

|       |        | winbond see                                                          |    |

|-------|--------|----------------------------------------------------------------------|----|

|       | 12.20  | 2 Bank Interleave Read Operation (CL = 2, BL = 4)                    | 47 |

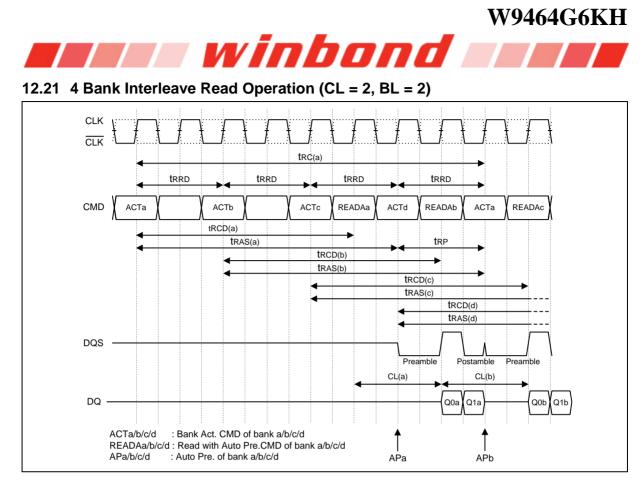

|       | 12.21  | 4 Bank Interleave Read Operation (CL = 2, BL = 2)                    | 48 |

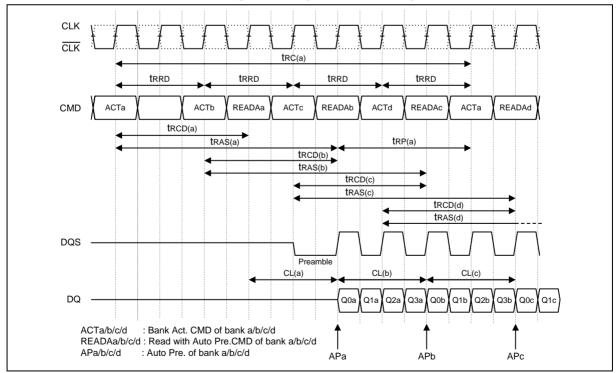

|       | 12.22  | 4 Bank Interleave Read Operation (CL = 2, BL = 4)                    | 48 |

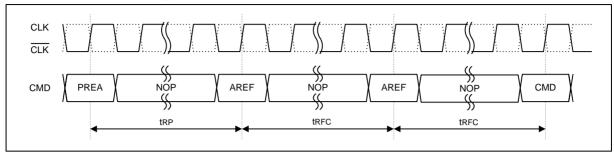

|       | 12.23  | Auto Refresh Cycle                                                   | 49 |

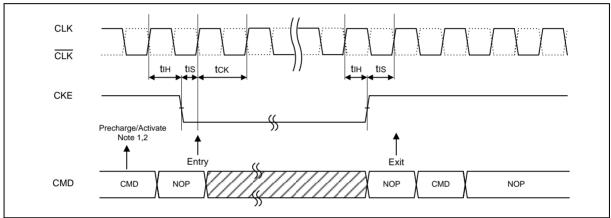

|       | 12.24  | Precharge/Activate Power Down Mode Entry and Exit Timing             | 49 |

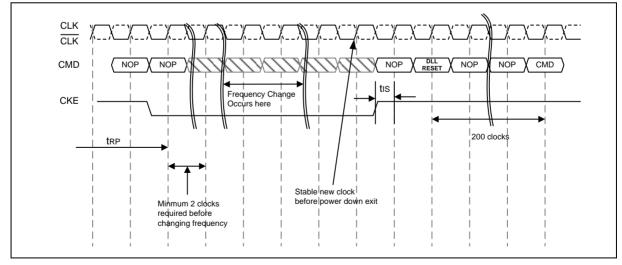

|       | 12.25  | Input Clock Frequency Change during Precharge Power Down Mode Timing | 49 |

|       | 12.26  | Self Refresh Entry and Exit Timing                                   | 50 |

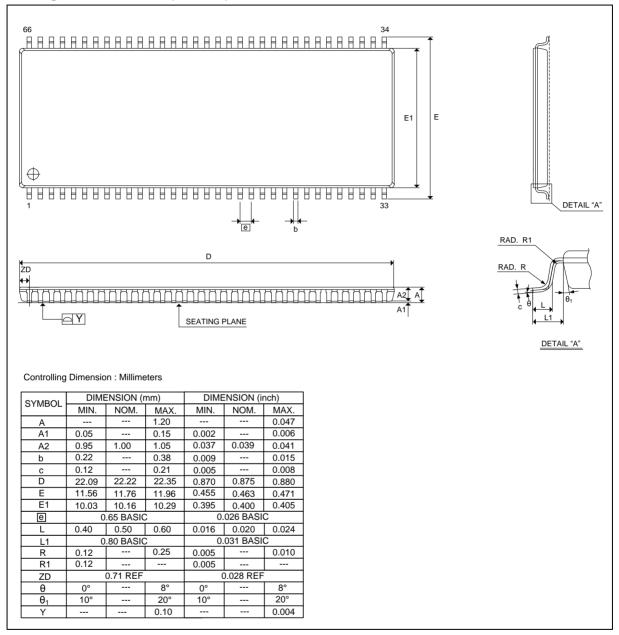

| 13. I | Packag | e Specification                                                      | 51 |

| 14. I | REVISI | ON HISTORY                                                           | 52 |

**FEES winbond**

#### 1. GENERAL DESCRIPTION

W9464G6KH is a CMOS Double Data Rate synchronous dynamic random access memory (DDR SDRAM); organized as 1M words  $\times$  4 banks  $\times$  16 bits. W9464G6KH delivers a data bandwidth of up to 400M words per second. To fully comply with the personal computer industrial standard, W9464G6KH is sorted into two speed grades: -5 and -5I. The -5 and -5I is compliant to the DDR400/CL3 specification (the -5I industrial grade which is guaranteed to support -40°C ~ 85°C).

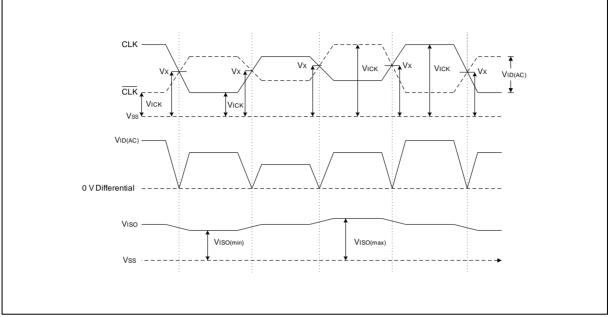

All Inputs reference to the positive edge of CLK (except for DQ, DM and CKE). The timing reference point for the differential clock is when the CLK and  $\overline{CLK}$  signals cross during a transition. Write and Read data are synchronized with the both edges of DQS (Data Strobe).

By having a programmable Mode Register, the system can change burst length, latency cycle, interleave or sequential burst to maximize its performance. W9464G6KH is ideal for any high performance applications.

#### 2. FEATURES

- 2.5V ± 0.2V Power Supply for DDR400

- Up to 200 MHz Clock Frequency

- Double Data Rate architecture; two data transfers per clock cycle

- Differential clock inputs (CLK and  $\overline{\text{CLK}}$ )

- DQS is edge-aligned with data for Read; center-aligned with data for Write

- CAS Latency: 2, 2.5 and 3

- Burst Length: 2, 4 and 8

- Auto Refresh and Self Refresh

- Precharged Power Down and Active Power Down

- Write Data Mask

- Write Latency = 1

- 15.6µS Refresh interval (4K/64 mS Refresh)

- Maximum burst refresh cycle: 8

- Interface: SSTL\_2

- Packaged in TSOP II 66-pin, using Lead free materials with RoHS compliant

#### 3. ORDER INFORMATION

| PART NUMBER  | SPEED      | SELF REFRESH<br>CURRENT (MAX.) | OPERATING<br>TEMPERATURE |

|--------------|------------|--------------------------------|--------------------------|

| W9464G6KH-5  | DDR400/CL3 | 2 mA                           | 0°C ~ 70°C               |

| W9464G6KH-5I | DDR400/CL3 | 2 mA                           | -40°C ~ 85°C             |

# \_\_\_\_winbond

#### 4. KEY PARAMETERS

| SYMBOL | DESCRIPTION                                  |             | MIN./MAX. | -5/-51 |

|--------|----------------------------------------------|-------------|-----------|--------|

|        |                                              | CL = 2      | Min.      | 7.5 nS |

|        |                                              | 0L = 2      | Max.      | 10 nS  |

| tCK    |                                              | CL = 2.5    | Min.      | 6 nS   |

| ICK    | Clock Cycle Time                             | CL = 2.5    | Max.      | 10 nS  |

|        |                                              |             | Min.      | 5 nS   |

|        |                                              | CL = 3      | Max.      | 10 nS  |

| tRAS   | Active to Precharge Command Period           |             | Min.      | 40 nS  |

| tRC    | Active to Ref/Active Command Period          |             | Min.      | 55 nS  |

| IDD0   | Operating Current: One Bank Active-Precharge |             | Max.      | 45 mA  |

| IDD1   | Operating Current: One Bank Active-Read      | d-Precharge | Max.      | 55 mA  |

| IDD2F  | Precharge floating standby current           |             | Max.      | 25 mA  |

| IDD2Q  | Precharge quiet standby current              |             | Max.      | 25 mA  |

| IDD4R  | Burst Operation Read Current                 |             | Max.      | 100 mA |

| IDD4W  | Burst Operation Write Current                |             | Max.      | 95 mA  |

| IDD5   | Auto Refresh Current                         |             | Max.      | 60 mA  |

| IDD6   | Self Refresh Current                         |             | Max.      | 2 mA   |

### 5. PIN CONFIGURATION

| VDD    | 1 66           | Vss           |

|--------|----------------|---------------|

|        | 2 65           | V\$\$<br>DQ15 |

|        | 3 64           | Vssq          |

|        | 4 63           | V330<br>DQ14  |

|        | 5 62           | DQ13          |

| VssQ   | 6 61           |               |

| DQ3    | 7 60           | DQ12          |

| DQ4    | 8 59           | <br>DQ11      |

| VDDQ   | 9 58           | Vssq          |

| DQ5    | 10 57          | <br>DQ10      |

| DQ6    | 11 56          | <br>DQ9       |

| Vssq   | 12 55          | να            |

| DQ7    | 13 54          | DQ8           |

| NC     | 14 53          |               |

| VDDQ   | 15 52          | Vssq          |

| LDQS   | 16 51          | UDQS          |

| NC     | 17 50          | NC            |

| VDD    | 18 49          | VREF          |

| NC     | 19 48          | Vss           |

| LDM    | 20 47          | UDM           |

| WE     | 21 46          |               |

|        | 22 45          | СГК           |

| RAS    | 23 44          | СКЕ           |

|        | 24 43          | NC            |

|        | 25 42          | NC            |

| BA0    | 26 41          | A11           |

| BA1    | 27 40          | A9            |

| A10/AP | 28 39<br>29 38 | A8<br>A7      |

| AU     | 29 38<br>30 37 | A7<br>A6      |

| A1     | 30 37<br>31 36 | A6<br>A5      |

| A2     | 32 35          | A3<br>A4      |

|        | 33 34          | Vss           |

|        |                |               |

|        |                |               |

|        |                |               |

### 6. PIN DESCRIPTION

| PIN NUMBER                                                      | PIN<br>NAME                                     | FUNCTION                     | DESCRIPTION                                                                                                                                                                              |

|-----------------------------------------------------------------|-------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28 – 32,<br>35 – 41                                             | A0 – A11                                        | Address                      | Multiplexed pins for row and column address.<br>Row address: A0 – A11.<br>Column address: A0 – A7. (A10 is used for Auto-precharge)                                                      |

| 26, 27                                                          | BA0, BA1                                        | Bank Select                  | Select bank to activate during row address latch time, or bank to read/write during column address latch time.                                                                           |

| 2, 4, 5, 7, 8, 10,<br>11, 13, 54, 56, 57,<br>59, 60, 62, 63, 65 | DQ0 –<br>DQ15                                   | Data Input/ Output           | The DQ0 – DQ15 input and output data are synchronized with both edges of DQS.                                                                                                            |

| 16,51                                                           | LDQS,<br>UDQS                                   | Data Strobe                  | DQS is Bi-directional signal. DQS is input signal during write operation and output signal during read operation. It is Edge-<br>aligned with read data, Center-aligned with write data. |

| 24                                                              | CS                                              | Chip Select                  | Disable or enable the command decoder. When command decoder is disabled, new command is ignored and previous operation continues.                                                        |

| 23, 22, 21                                                      | $\overline{RAS}, \overline{CAS}, \overline{WE}$ | Command Inputs               | Command inputs (along with $\overline{CS}$ ) define the command being entered.                                                                                                           |

| 20, 47                                                          | LDM, UDM                                        | Write Mask                   | When DM is asserted "high" in burst write, the input data is masked. DM is synchronized with both edges of DQS.                                                                          |

| 45, 46                                                          | CLK,<br>CLK                                     | Differential Clock<br>Inputs | All address and control input signals are sampled on the crossing of the positive edge of CLK and negative edge of $\overrightarrow{\text{CLK}}$ .                                       |

| 44                                                              | CKE                                             | Clock Enable                 | CKE controls the clock activation and deactivation. When CKE is low, Power Down mode, Suspend mode, or Self Refresh mode is entered.                                                     |

| 49                                                              | Vref                                            | Reference Voltage            | VREF is reference voltage for inputs.                                                                                                                                                    |

| 1, 18, 33                                                       | Vdd                                             | Power                        | Power for logic circuit inside DDR SDRAM.                                                                                                                                                |

| 34, 48, 66                                                      | Vss                                             | Ground                       | Ground for logic circuit inside DDR SDRAM.                                                                                                                                               |

| 3, 9, 15, 55, 61                                                | Vddq                                            | Power for I/O<br>Buffer      | Separated power from VDD, used for output buffer, to improve noise.                                                                                                                      |

| 6, 12, 52, 58, 64                                               | Vssq                                            | Ground for I/O<br>Buffer     | Separated ground from Vss, used for output buffer, to improve noise.                                                                                                                     |

| 14, 17, 19, 25,<br>42, 43, 50, 53                               | NC                                              | No Connection                | No connection                                                                                                                                                                            |

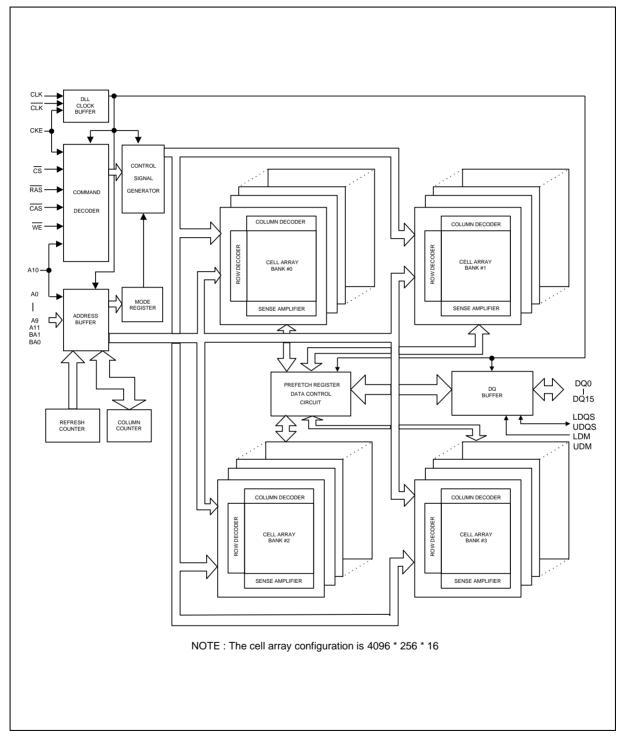

7. BLOCK DIAGRAM

8. FUNCTIONAL DESCRIPTION

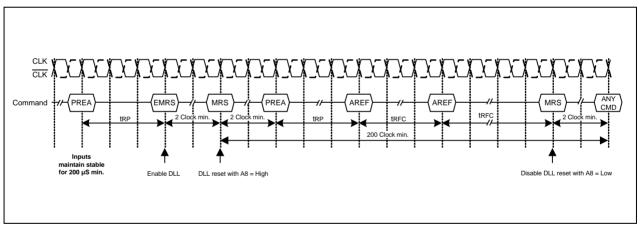

#### 8.1 Power Up Sequence

(1) Apply power and attempt to CKE at a low state ( $\leq 0.2V$ ), all other inputs may be undefined

winbond

- 1) Apply VDD before or at the same time as VDDQ.

- 2) Apply VDDQ before or at the same time as VTT and VREF.

- (2) Start Clock and maintain stable condition for 200 µS (min.).

- (3) After stable power and clock, apply NOP and take CKE high.

- (4) Issue precharge command for all banks of the device.

- (5) Issue EMRS (Extended Mode Register Set) to enable DLL and establish Output Driver Type.

- (6) Issue MRS (Mode Register Set) to reset DLL and set device to idle with bit A8.

(An additional 200 cycles(min) of clock are required for DLL Lock before any executable

- command applied.)

- (7) Issue precharge command for all banks of the device.

- (8) Issue two or more Auto Refresh commands.

- (9) Issue MRS-Initialize device operation with the reset DLL bit deactivated A8 to low.

Initialization sequence after power-up

8.2 Command Function

#### 8.2.1 Bank Activate Command

$(\overline{RAS} = "L", \overline{CAS} = "H", \overline{WE} = "H", BA0, BA1 = Bank, A0 to A11 = Row Address)$

The Bank Activate command activates the bank designated by the BA (Bank address) signal. Row addresses are latched on A0 to A11 when this command is issued and the cell data is read out of the sense amplifiers. The maximum time that each bank can be held in the active state is specified as tRAS (max). After this command is issued, Read or Write operation can be executed.

winbond seems

#### 8.2.2 Bank Precharge Command

$(\overline{RAS} = "L", \overline{CAS} = "H", \overline{WE} = "L", BA0, BA1 = Bank, A10 = "L", A0 to A9, A11 = Don't Care)$

The Bank Precharge command percharges the bank designated by BA. The precharged bank is switched from the active state to the idle state.

#### 8.2.3 Precharge All Command

$(\overline{RAS} = "L", \overline{CAS} = "H", \overline{WE} = "L", BA0, BA1 = Don't Care, A10 = "H", A0 to A9, A11 = Don't Care)$

The Precharge All command precharges all banks simultaneously. Then all banks are switched to the idle state.

#### 8.2.4 Write Command

$(\overline{RAS} = "H", \overline{CAS} = "L", \overline{WE} = "L", BA0, BA1 = Bank, A10 = "L", A0 to A7 = Column Address)$

The write command performs a Write operation to the bank designated by BA. The write data are latched at both edges of DQS. The length of the write data (Burst Length) and column access sequence (Addressing Mode) must be in the Mode Register at power-up prior to the Write operation.

#### 8.2.5 Write with Auto-precharge Command

$(\overline{RAS} = "H", \overline{CAS} = "L", \overline{WE} = "L", BA0, BA1 = Bank, A10 = "H", A0 to A7 = Column Address)$

The Write with Auto-precharge command performs the Precharge operation automatically after the Write operation. This command must not be interrupted by any other commands.

#### 8.2.6 Read Command

$(\overline{RAS} = "H", \overline{CAS} = "L", \overline{WE} = "H", BA0, BA1 = Bank, A10 = "L", A0 to A7 = Column Address)$

The Read command performs a Read operation to the bank designated by BA. The read data are synchronized with both edges of DQS. The length of read data (Burst Length), Addressing Mode and CAS Latency (access time from  $\overline{CAS}$  command in a clock cycle) must be programmed in the Mode Register at power-up prior to the Read operation.

#### 8.2.7 Read with Auto-precharge Command

$(\overline{RAS} = "H", \overline{CAS} = "L", \overline{WE} = "H", BA0, BA1 = Bank, A10 = "H", A0 to A7 = Column Address)$

The Read with Auto-precharge command automatically performs the Precharge operation after the Read operation.

**The set of the set of**

1. READA  $\geq$  tRAS (min) – (BL/2) x tCK

Internal precharge operation begins after BL/2 cycle from Read with Auto-precharge command.

2. tRCD(min)  $\leq$  READA < tRAS(min) – (BL/2) x tCK

Data can be read with shortest latency, but the internal Precharge operation does not begin until after tRAS (min) has completed.

This command must not be interrupted by any other command.

#### 8.2.8 Mode Register Set Command

$(\overline{RAS} = "L", \overline{CAS} = "L", \overline{WE} = "L", BA0 = "L", BA1 = "L", A0 to A11 = Register Data)$

The Mode Register Set command programs the values of CAS Latency, Addressing Mode, Burst Length and DLL reset in the Mode Register. The default values in the Mode Register after power-up are undefined, therefore this command must be issued during the power-up sequence. Also, this command can be issued while all banks are in the idle state. Refer to the table for specific codes.

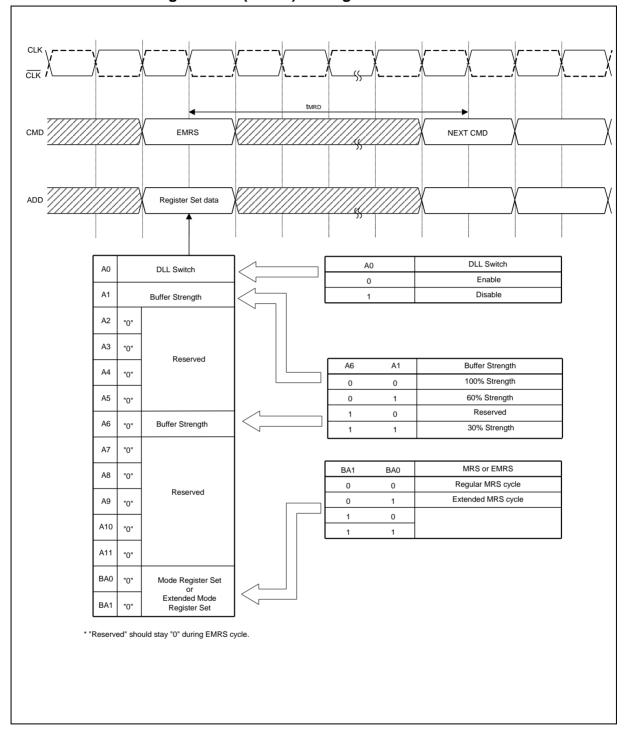

#### 8.2.9 Extended Mode Register Set Command

$$(\overline{RAS} = "L", \overline{CAS} = "L", \overline{WE} = "L", BA0 = "H", BA1 = "L", A0 to A11 = Register data)$$

The Extended Mode Register Set command can be implemented as needed for function extensions to the standard (SDR-SDRAM). Currently the only available mode in EMRS is DLL enable/disable, decoded by A0. The default value of the extended mode register is not defined; therefore this command must be issued during the power-up sequence for enabling DLL. Refer to the table for specific codes.

#### 8.2.10 No-Operation Command

$(\overline{RAS} = "H", \overline{CAS} = "H", \overline{WE} = "H")$

The No-Operation command simply performs no operation (same command as Device Deselect).

#### 8.2.11 Burst Read Stop Command

$(\overline{RAS} = "H", \overline{CAS} = "H", \overline{WE} = "L")$

The Burst stop command is used to stop the burst operation. This command is only valid during a Burst Read operation.

#### 8.2.12 Device Deselect Command

$(\overline{CS} = "H")$

The Device Deselect command disables the command decoder so that the  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and Address inputs are ignored. This command is similar to the No-Operation command.

#### 8.2.13 Auto Refresh Command

$(\overline{RAS} = "L", \overline{CAS} = "L", \overline{WE} = "H", CKE = "H", BA0, BA1, A0 to A11 = Don't Care)$

AUTO REFRESH is used during normal operation of the DDR SDRAM and is analogous to CAS– BEFORE–RAS (CBR) refresh in previous DRAM types. This command is non persistent, so it must be issued each time a refresh is required.

The refresh addressing is generated by the internal refresh controller. This makes the address bits "Don't Care" during an AUTO REFRESH command. The DDR SDRAM requires AUTO REFRESH cycles at an average periodic interval of tREFI (maximum).

**\_\_\_\_** winbond **\_\_\_**

To allow for improved efficiency in scheduling and switching between tasks, some flexibility in the absolute refresh interval is provided. A maximum of eight AUTO REFRESH commands can be posted to any given DDR SDRAM, and the maximum absolute interval between any AUTO REFRESH command and the next AUTO REFRESH command is 8 \* tREFI.

#### 8.2.14 Self Refresh Entry Command

$(\overline{RAS} = "L", \overline{CAS} = "L", \overline{WE} = "H", CKE = "L", BA0, BA1, A0 to A11 = Don't Care)$

The SELF REFRESH command can be used to retain data in the DDR SDRAM, even if the rest of the system is powered down. When in the self refresh mode, the DDR SDRAM retains data without external clocking. The SELF REFRESH command is initiated like an AUTO REFRESH command except CKE is disabled (LOW). The DLL is automatically disabled upon entering SELF REFRESH, and is automatically enabled upon exiting SELF REFRESH. Any time the DLL is enabled a DLL Reset must follow and 200 clock cycles should occur before a READ command can be issued. Input signals except CKE are "Don't Care" during SELF REFRESH. Since CKE is an SSTL 2 input, VREF must be maintained during SELF REFRESH.

#### 8.2.15 Self Refresh Exit Command

$(CKE = "H", \overline{CS} = "H" \text{ or } CKE = "H", \overline{RAS} = "H", \overline{CAS} = "H")$

The procedure for exiting self refresh requires a sequence of commands. First, CLK must be stable prior to CKE going back HIGH. Once CKE is HIGH, the DDR SDRAM must have NOP commands issued for tXSNR because time is required for the completion of any internal refresh in progress. A simple algorithm for meeting both refresh and DLL requirements is to apply NOPs for 200 clock cycles before applying any other command.

The use of SELF REFREH mode introduces the possibility that an internally timed event can be missed when CKE is raised for exit from self refresh mode. Upon exit from SELF REFRESH an extra auto refresh command is recommended.

#### 8.2.16 Data Write Enable /Disable Command

(DM = "L/H" or LDM, UDM = "L/H")

During a Write cycle, the DM or LDM, UDM signal functions as Data Mask and can control every word of the input data. The LDM signal controls DQ0 to DQ7 and UDM signal controls DQ8 to DQ15.

#### 8.3 Read Operation

Issuing the Bank Activate command to the idle bank puts it into the active state. When the Read command is issued after tRCD from the Bank Activate command, the data is read out sequentially, synchronized with both edges of DQS (Burst Read operation). The initial read data becomes available after CAS Latency from the issuing of the Read command. The CAS Latency must be set in the Mode Register at power-up.

When the Precharge Operation is performed on a bank during a Burst Read and operation, the Burst operation is terminated.

When the Read with Auto-precharge command is issued, the Precharge operation is performed automatically after the Read cycle then the bank is switched to the idle state. This command cannot be interrupted by any other commands. Refer to the diagrams for Read operation.

#### 8.4 Write Operation

Issuing the Write command after tRCD from the bank activate command. The input data is latched sequentially, synchronizing with both edges(rising & falling) of DQS after the Write command (Burst write operation). The burst length of the Write data (Burst Length) and Addressing Mode must be set in the Mode Register at power-up.

**The set winbond**

When the Precharge operation is performed in a bank during a Burst Write operation, the Burst operation is terminated.

When the Write with Auto-precharge command is issued, the Precharge operation is performed automatically after the Write cycle, then the bank is switched to the idle state, The Write with Auto-precharge command cannot be interrupted by any other command for the entire burst data duration.

Refer to the diagrams for Write operation.

#### 8.5 Precharge

There are two Commands, which perform the precharge operation (Bank Precharge and Precharge All). When the Bank Precharge command is issued to the active bank, the bank is precharged and then switched to the idle state. The Bank Precharge command can precharge one bank independently of the other bank and hold the unprecharged bank in the active state. The maximum time each bank can be held in the active state is specified as tRAS (max). Therefore, each bank must be precharged within tRAS(max) from the bank activate command.

The Precharge All command can be used to precharge all banks simultaneously. Even if banks are not in the active state, the Precharge All command can still be issued. In this case, the Precharge operation is performed only for the active bank and the precharge bank is then switched to the idle state.

#### 8.6 Burst Termination

When the Precharge command is used for a bank in a Burst cycle, the Burst operation is terminated. When Burst Read cycle is interrupted by the Precharge command, read operation is disabled after clock cycle of (CAS Latency) from the Precharge command. When the Burst Write cycle is interrupted by the Precharge command, the input circuit is reset at the same clock cycle at which the precharge command is issued. In this case, the DM signal must be asserted "high" during tWR to prevent writing the invalided data to the cell array.

When the Burst Read Stop command is issued for the bank in a Burst Read cycle, the Burst Read operation is terminated. The Burst read Stop command is not supported during a write burst operation. Refer to the diagrams for Burst termination.

#### 8.7 Refresh Operation

Two types of Refresh operation can be performed on the device: Auto Refresh and Self Refresh. By repeating the Auto Refresh cycle, each bank in turn refreshed automatically. The Refresh operation must be performed 4096 times (rows) within 64mS. The period between the Auto Refresh command and the next command is specified by tRFC.

Self Refresh mode enters issuing the Self Refresh command (CKE asserted "low") while all banks are in the idle state. The device is in Self Refresh mode for as long as CKE held "low". In the case of distributed Auto Refresh commands, distributed auto refresh commands must be issued every 15.6  $\mu$ S and the last distributed Auto Refresh commands must be performed within 15.6  $\mu$ S before entering the self refresh mode. After exiting from the Self Refresh mode, the refresh operation must be performed within 15.6  $\mu$ S. In Self Refresh mode, all input/output buffers are disabled, resulting in lower power dissipation (except CKE buffer). Refer to the diagrams for Refresh operation.

# **The second second**

#### 8.8 Power Down Mode

Two types of Power Down Mode can be performed on the device: Active Standby Power Down Mode and Precharge Standby Power Down Mode.

When the device enters the Power Down Mode, all input/output buffers are disabled resulting in low power dissipation (except CKE buffer).

Power Down Mode enter asserting CKE "low" while the device is not running a burst cycle. Taking CKE "high" can exit this mode. When CKE goes high, a No operation command must be input at next CLK rising edge. Refer to the diagrams for Power Down Mode.

#### 8.9 Input Clock Frequency Change during Precharge Power Down Mode

DDR SDRAM input clock frequency can be changed under following condition:

DDR SDRAM must be in precharged power down mode with CKE at logic LOW level. After a minimum of 2 clocks after CKE goes LOW, the clock frequency may change to any frequency between minimum and maximum operating frequency specified for the particular speed grade. During an input clock frequency change, CKE must be held LOW. Once the input clock frequency is changed, a stable clock must be provided to DRAM before precharge power down mode may be exited. The DLL must be RESET via EMRS after precharge power down exit. An additional MRS command may need to be issued to appropriately set CL etc. After the DLL relock time, the DRAM is ready to operate with new clock frequency.

#### 8.10 Mode Register Operation

The mode register is programmed by the Mode Register Set command (MRS/EMRS) when all banks are in the idle state. The data to be set in the Mode Register is transferred using the A0 to A11 and BA0, BA1 address inputs.

The Mode Register designates the operation mode for the read or write cycle. The register is divided into five filed: (1) Burst Length field to set the length of burst data (2) Addressing Mode selected bit to designate the column access sequence in a Burst cycle (3) CAS Latency field to set the assess time in clock cycle (4) DLL reset field to reset the DLL (5) Regular/Extended Mode Register filed to select a type of MRS (Regular/Extended MRS). EMRS cycle can be implemented the extended function (DLL enable/Disable mode).

The initial value of the Mode Register (including EMRS) after power up is undefined; therefore the Mode Register Set command must be issued before power operation.

#### 8.10.1 Burst Length field (A2 to A0)

This field specifies the data length for column access using the A2 to A0 pins and sets the Burst Length to be 2, 4 and 8 words.

| A2 | A1 | A0 | BURST LENGTH |

|----|----|----|--------------|

| 0  | 0  | 0  | Reserved     |

| 0  | 0  | 1  | 2 words      |

| 0  | 1  | 0  | 4 words      |

| 0  | 1  | 1  | 8 words      |

| 1  | x  | х  | Reserved     |

# **\_\_\_\_** winbond **\_\_\_**

#### 8.10.2 Addressing Mode Select (A3)

The Addressing Mode can be one of two modes; Interleave mode or Sequential Mode, When the A3 bit is "0", Sequential mode is selected. When the A3 bit is "1", Interleave mode is selected. Both addressing Mode support burst length 2, 4 and 8 words.

| A3 | ADDRESSING MODE |

|----|-----------------|

| 0  | Sequential      |

| 1  | Interleave      |

#### 8.10.2.1. Addressing Sequence of Sequential Mode

A column access is performed by incrementing the column address input to the device. The address is varied by the Burst Length as the following.

| DATA   | ACCESS ADDRESS | BURST LENGTH                         |

|--------|----------------|--------------------------------------|

| Data 0 | n              | 2 words (address bits is A0)         |

| Data 1 | n + 1          | not carried from A0 to A1            |

| Data 2 | n + 2          | 4 words (address bit A0, A1)         |

| Data 3 | n + 3          | Not carried from A1 to A2            |

| Data 4 | n + 4          |                                      |

| Data 5 | n + 5          | 8 words (address bits A2, A1 and A0) |

| Data 6 | n + 6          | Not carried from A2 to A3            |

| Data 7 | n + 7          | ν                                    |

#### Addressing Sequence of Sequential Mode

#### 8.10.2.2. Addressing Sequence for Interleave Mode

A Column access is started from the inputted column address and is performed by interleaving the address bits in the sequence shown as the following.

| DATA   | ACCESS ADDRESS             | BURST LENGTH |

|--------|----------------------------|--------------|

| Data 0 | A8 A7 A6 A5 A4 A3 A2 A1 A0 | 2 words      |

| Data 1 | A8 A7 A6 A5 A4 A3 A2 A1 A0 |              |

| Data 2 | A8 A7 A6 A5 A4 A3 A2 A1 A0 | 4 words      |

| Data 3 | A8 A7 A6 A5 A4 A3 A2 A1 A0 |              |

| Data 4 | A8 A7 A6 A5 A4 A3 A2 A1 A0 | 8 words      |

| Data 5 | A8 A7 A6 A5 A4 A3 A2 A1 A0 |              |

| Data 6 | A8 A7 A6 A5 A4 A3 A2 A1 A0 |              |

| Data 7 | A8 A7 A6 A5 A4 A3 A2 A1 A0 | ٧            |

#### Addressing Sequence of Interleave Mode

#### 8.10.3 CAS Latency field (A6 to A4)

This field specifies the number of clock cycles from the assertion of the Read command to the first data read. The minimum values of CAS Latency depend on the frequency of CLK.

| A6 | A5 | A4 | CAS LATENCY |

|----|----|----|-------------|

| 0  | 0  | 0  | Reserved    |

| 0  | 0  | 1  | Reserved    |

| 0  | 1  | 0  | 2           |

| 0  | 1  | 1  | 3           |

| 1  | 0  | 0  | Reserved    |

| 1  | 0  | 1  | Reserved    |

| 1  | 1  | 0  | 2.5         |

| 1  | 1  | 1  | Reserved    |

#### 8.10.4 DLL Reset bit (A8)

This bit is used to reset DLL. When the A8 bit is "1", DLL is reset.

#### 8.10.5 Mode Register /Extended Mode register change bits (BA0, BA1)

These bits are used to select MRS/EMRS.

| BA1 | BA0 | A11-A0             |

|-----|-----|--------------------|

| 0   | 0   | Regular MRS Cycle  |

| 0   | 1   | Extended MRS Cycle |

| 1   | x   | Reserved           |

#### 8.10.6 Extended Mode Register field

1) DLL Switch field (A0)

This bit is used to select DLL enable or disable

| A0 | DLL     |

|----|---------|

| 0  | Enable  |

| 1  | Disable |

#### 2) Output Driver Strength Control field (A6, A1)

The 100%, 60% and 30% or matched impedance driver strength are required Extended Mode Register Set (EMRS) as the following:

| A6 | A1 | BUFFER STRENGTH |

|----|----|-----------------|

| 0  | 0  | 100% Strength   |

| 0  | 1  | 60% Strength    |

| 1  | 0  | Reserved        |

| 1  | 1  | 30% Strength    |

#### 8.10.7 Reserved field

- Test mode entry bit (A7)

- This bit is used to enter Test mode and must be set to "0" for normal operation.

- Reserved bits (A9, A10, A11) These bits are reserved for future operations. They must be set to "0" for normal operation.

**FEES winbond**

#### 9. OPERATION MODE

The following table shows the operation commands.

#### 9.1 Simplified Truth Table

| SYM.  | COMMAND                       | DEVICE<br>STATE       | CKEn-1 | CKEn | DM <sup>(4)</sup> | BA0,<br>BA1 | A10 | A0-A9<br>,A11 | cs | RAS | CAS | WE |

|-------|-------------------------------|-----------------------|--------|------|-------------------|-------------|-----|---------------|----|-----|-----|----|

| ACT   | Bank Active                   | Idle <sup>(3)</sup>   | Н      | Х    | Х                 | V           | V   | V             | L  | L   | Н   | Н  |

| PRE   | Bank Precharge                | Any <sup>(3)</sup>    | Н      | Х    | Х                 | V           | L   | Х             | L  | L   | Н   | L  |

| PREA  | Precharge All                 | Any                   | Н      | Х    | Х                 | Х           | Н   | Х             | L  | L   | Н   | L  |

| WRIT  | Write                         | Active <sup>(3)</sup> | Н      | Х    | Х                 | V           | L   | V             | L  | Н   | L   | L  |

| WRITA | Write with Auto-<br>precharge | Active <sup>(3)</sup> | Н      | Х    | Х                 | V           | Н   | V             | L  | н   | L   | L  |

| READ  | Read                          | Active <sup>(3)</sup> | Н      | Х    | Х                 | V           | L   | V             | L  | Н   | L   | Н  |

| READA | Read with Auto-<br>precharge  | Active <sup>(3)</sup> | Н      | Х    | Х                 | V           | Н   | V             | L  | н   | L   | Н  |

| MRS   | Mode Register Set             | Idle                  | Н      | Х    | Х                 | L, L        | С   | С             | L  | L   | L   | L  |

| EMRS  | Extended Mode<br>Register Set | Idle                  | Н      | Х    | Х                 | H, L        | V   | V             | L  | L   | L   | L  |

| NOP   | No Operation                  | Any                   | Н      | Х    | Х                 | Х           | Х   | Х             | L  | Н   | Н   | Н  |

| BST   | Burst Read Stop               | Active                | Н      | Х    | Х                 | Х           | Х   | Х             | L  | Н   | Н   | L  |

| DSL   | Device Deselect               | Any                   | Н      | Х    | Х                 | Х           | Х   | Х             | Н  | Х   | Х   | Х  |

| AREF  | Auto Refresh                  | Idle                  | Н      | Н    | Х                 | Х           | Х   | Х             | L  | L   | L   | Н  |

| SELF  | Self Refresh<br>Entry         | ldle                  | Н      | L    | Х                 | Х           | х   | х             | L  | L   | L   | Н  |

| SELEX | Self Refresh Exit             | Idle (Self            |        | Н    | х                 | х           | х   | х             | Н  | Х   | Х   | Х  |

| SELEA | Sell Refresh Exit             | Refresh)              | L      | п    | ~                 | ~           | ^   | ^             | L  | Н   | Н   | Х  |

| PD    | Power Down                    | Idle/                 | Н      | L    | х                 | х           | х   | х             | Н  | Х   | Х   | Х  |

| PD    | Mode Entry                    | Active <sup>(5)</sup> | п      | L    | ~                 | ~           | ^   | ^             | L  | Н   | Н   | Х  |

|       | Power Down                    | Any                   |        |      |                   |             |     |               | Н  | Х   | Х   | Х  |

| PDEX  | Mode Exit                     | (Power<br>Down)       | L      | Н    | Х                 | Х           | Х   | Х             | L  | н   | Н   | Х  |

| WDE   | Data Write Enable             | Active                | Н      | Х    | L                 | Х           | Х   | Х             | Х  | Х   | Х   | Х  |

| WDD   | Data Write Disable            | Active                | Н      | Х    | Н                 | Х           | Х   | Х             | Х  | Х   | Х   | Х  |

Notes:

1. V = Valid X = Don't Care L = Low level H = High level

2. CKEn signal is input level when commands are issued.

CKEn-1 signal is input level one clock cycle before the commands are issued.

3. These are state designated by the BA0, BA1 signals.

4. LDM, UDM (W9464G6KH).

5. Power Down Mode can not entry in the burst cycle.

#### 9.2 Function Truth Table

(Note 1)

| CURRENT<br>STATE | cs | RAS | CAS | WE | ADDRESS     | COMMAND    | ACTION                               | NOTES |

|------------------|----|-----|-----|----|-------------|------------|--------------------------------------|-------|

|                  | Н  | Х   | Х   | Х  | Х           | DSL        | NOP                                  |       |

|                  | L  | Н   | Н   | Х  | Х           | NOP/BST    | NOP                                  |       |

|                  | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA | ILLEGAL                              | 3     |

| Idle             | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA | ILLEGAL                              | 3     |

| luie             | L  | L   | Н   | Н  | BA, RA      | ACT        | Row activating                       |       |

|                  | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | NOP                                  |       |

|                  | L  | L   | L   | н  | Х           | AREF/SELF  | Refresh or Self refresh              | 2     |

|                  | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | Mode register accessing              | 2     |

|                  | н  | Х   | Х   | Х  | Х           | DSL        | NOP                                  |       |

|                  | L  | Н   | н   | Х  | Х           | NOP/BST    | NOP                                  |       |

|                  | L  | Н   | L   | н  | BA, CA, A10 | READ/READA | Begin read: Determine AP             | 4     |

| Row Active       | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA | Begin write: Determine AP            | 4     |

| NOW ACTIVE       | L  | L   | н   | н  | BA, RA      | ACT        | ILLEGAL                              | 3     |

|                  | L  | L   | н   | L  | BA, A10     | PRE/PREA   | Precharge                            | 5     |

|                  | L  | L   | L   | н  | Х           | AREF/SELF  | ILLEGAL                              |       |

|                  | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                              |       |

|                  | н  | Х   | Х   | Х  | Х           | DSL        | Continue burst to end                |       |

|                  | L  | н   | н   | н  | Х           | NOP        | Continue burst to end                |       |

|                  | L  | Н   | н   | L  | Х           | BST        | Burst stop                           |       |

|                  | L  | Н   | L   | н  | BA, CA, A10 | READ/READA | Term burst, new read: Determine AP   | 6     |

| Read             | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA | ILLEGAL                              |       |

|                  | L  | L   | н   | н  | BA, RA      | ACT        | ILLEGAL                              | 3     |

|                  | L  | L   | н   | L  | BA, A10     | PRE/PREA   | Term burst, precharging              |       |

|                  | L  | L   | L   | Н  | Х           | AREF/SELF  | ILLEGAL                              |       |

|                  | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                              |       |

|                  | Н  | Х   | Х   | Х  | Х           | DSL        | Continue burst to end                |       |

|                  | L  | Н   | н   | н  | Х           | NOP        | Continue burst to end                |       |

|                  | L  | Н   | Н   | L  | Х           | BST        | ILLEGAL                              |       |

|                  | L  | Н   | L   | н  | BA, CA, A10 | READ/READA | Term burst, start read: Determine AP | 6, 7  |

| Write            | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA | Term burst, start read: Determine AP | 6     |

|                  | L  | L   | Н   | Н  | BA, RA      | ACT        | ILLEGAL                              | 3     |

|                  | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | Term burst, precharging              | 8     |

|                  | L  | L   | L   | н  | Х           | AREF/SELF  | ILLEGAL                              |       |

|                  | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                              |       |

| Function Truth Table, continued |  |

|---------------------------------|--|

|---------------------------------|--|

| CURRENT<br>STATE | cs | RAS | CAS | WE | ADDRESS     | COMMAND    | ACTION                      | NOTES |

|------------------|----|-----|-----|----|-------------|------------|-----------------------------|-------|

|                  | Н  | Х   | Х   | Х  | Х           | DSL        | Continue burst to end       |       |

|                  | L  | Н   | Н   | Н  | Х           | NOP        | Continue burst to end       |       |

|                  | L  | Н   | Н   | L  | х           | BST        | ILLEGAL                     |       |

| Read with        | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA | ILLEGAL                     |       |

| Auto-            | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA | ILLEGAL                     | 3     |

| precharge        | L  | L   | Н   | Н  | BA, RA      | ACT        | ILLEGAL                     | 3     |

|                  | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | ILLEGAL                     |       |

|                  | L  | L   | L   | Н  | Х           | AREF/SELF  | ILLEGAL                     |       |

|                  | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                     |       |

|                  | Н  | Х   | Х   | Х  | Х           | DSL        | Continue burst to end       |       |

|                  | L  | Н   | Н   | Н  | Х           | NOP        | Continue burst to end       |       |

|                  | L  | Н   | Н   | L  | Х           | BST        | ILLEGAL                     |       |

| Write with       | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA | ILLEGAL                     |       |

| Auto-            | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA | ILLEGAL                     |       |

| precharge        | L  | L   | Н   | Н  | BA, RA      | ACT        | ILLEGAL                     | 3     |

|                  | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | ILLEGAL                     | 3     |

|                  | L  | L   | L   | Н  | Х           | AREF/SELF  | ILLEGAL                     |       |

|                  | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                     |       |

|                  | Н  | Х   | Х   | Х  | Х           | DSL        | NOP-> Idle after tRP        |       |

|                  | L  | Н   | Н   | Н  | Х           | NOP        | NOP-> Idle after tRP        |       |

|                  | L  | Н   | Н   | L  | Х           | BST        | ILLEGAL                     |       |

|                  | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA | ILLEGAL                     | 3     |

| Precharging      | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA | ILLEGAL                     | 3     |

|                  | L  | L   | Н   | Н  | BA, RA      | ACT        | ILLEGAL                     | 3     |

|                  | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | Idle after tRP              |       |

|                  | L  | L   | L   | Н  | Х           | AREF/SELF  | ILLEGAL                     |       |

|                  | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                     |       |

|                  | Н  | Х   | Х   | Х  | х           | DSL        | NOP-> Row active after tRCD |       |

|                  | L  | Н   | Н   | н  | Х           | NOP        | NOP-> Row active after tRCD |       |

|                  | L  | Н   | Н   | L  | Х           | BST        | ILLEGAL                     |       |

|                  | L  | н   | L   | Н  | BA, CA, A10 | READ/READA | ILLEGAL                     | 3     |

| Row              | L  | н   | L   | L  | BA, CA, A10 | WRIT/WRITA | ILLEGAL                     | 3     |

| Activating       | L  | L   | Н   | н  | BA, RA      | ACT        | ILLEGAL                     | 3     |

|                  | L  | L   | Н   | L  | BA, A10     | PRE/PREA   | ILLEGAL                     | 3     |

|                  | L  | L   | L   | н  | х           | AREF/SELF  | ILLEGAL                     |       |

|                  | L  | L   | L   | L  | Op-Code     | MRS/EMRS   | ILLEGAL                     |       |

# Function Truth Table, continued

| CURRENT<br>STATE         | cs | RAS | CAS | WE | ADDRESS     | COMMAND                             | ACTION                         | NOTES |

|--------------------------|----|-----|-----|----|-------------|-------------------------------------|--------------------------------|-------|

|                          | Н  | Х   | Х   | Х  | Х           | DSL                                 | NOP->Row active after twr      |       |

|                          | L  | Н   | Н   | Н  | х           | NOP                                 | NOP->Row active after twr      |       |

|                          | L  | Н   | Н   | L  | х           | BST                                 | ILLEGAL                        |       |

|                          | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA                          | ILLEGAL                        | 3     |

| Write<br>Recovering      | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA                          | ILLEGAL                        | 3     |

| Recovering               | L  | L   | Н   | Н  | BA, RA      | ACT                                 | ILLEGAL                        | 3     |

|                          | L  | L   | Н   | L  | BA, A10     | PRE/PREA                            | ILLEGAL                        | 3     |

|                          | L  | L   | L   | Н  | х           | AREF/SELF                           | ILLEGAL                        |       |

|                          | L  | L   | L   | L  | Op-Code     | MRS/EMRS                            | ILLEGAL                        |       |

|                          | Н  | Х   | Х   | Х  | х           | DSL                                 | NOP->Enter precharge after twR |       |

|                          | L  | Н   | Н   | Н  | х           | NOP                                 | NOP->Enter precharge after twR |       |

|                          | L  | Н   | Н   | L  | х           | BST                                 | ILLEGAL                        |       |

| Write                    | L  | н   | L   | Н  | BA, CA, A10 | READ/READA                          | ILLEGAL                        | 3     |

| Recovering<br>with Auto- | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA                          | ILLEGAL                        | 3     |

| precharge                | L  | L   | Н   | Н  | BA, RA      | ACT                                 | ILLEGAL                        | 3     |

|                          | L  | L   | Н   | L  | BA, A10     | PRE/PREA                            | ILLEGAL                        | 3     |

|                          | L  | L   | L   | Н  | х           | AREF/SELF                           | ILLEGAL                        |       |

|                          | L  | L   | L   | L  | Op-Code     | MRS/EMRS                            | ILLEGAL                        |       |

|                          | Н  | Х   | Х   | Х  | Х           | DSL                                 | NOP->Idle after tRC            |       |

|                          | L  | н   | Н   | Н  | х           | NOP                                 | NOP->Idle after tRC            |       |

| Refreshing               | L  | Н   | Н   | L  | х           | BST                                 | ILLEGAL                        |       |

| Reliesning               | L  | н   | L   | Н  | х           | READ/WRIT                           | ILLEGAL                        |       |

|                          | L  | L   | Н   | Х  | х           | ACT/PRE/PREA                        | ILLEGAL                        |       |

|                          | L  | L   | L   | Х  | х           | AREF/SELF/MRS/EMRS                  | ILLEGAL                        |       |

|                          | Н  | Х   | Х   | Х  | Х           | DSL                                 | NOP->Row after tMRD            |       |

|                          | L  | н   | Н   | н  | Х           | NOP                                 | NOP->Row after tMRD            |       |

| Mode<br>Register         | L  | н   | Н   | L  | Х           | BST                                 | ILLEGAL                        |       |

| Accessing                | L  | н   | L   | Х  | Х           | READ/WRIT                           | ILLEGAL                        |       |

|                          | L  | L   | х   | х  | х           | ACT/PRE/PREA/ARE<br>F/SELF/MRS/EMRS | ILLEGAL                        |       |

Notes:

1. All entries assume that CKE was active (High level) during the preceding clock cycle and the current clock cycle.

2. Illegal if any bank is not idle.

3. Illegal to bank in specified states; Function may be legal in the bank indicated by Bank Address (BA), depending on the state of that bank.

- 4. Illegal if tRCD is not satisfied.

- 5. Illegal if tRAS is not satisfied.

- 6. Must satisfy burst interrupt condition.

- 7. Must avoid bus contention, bus turn around, and/or satisfy write recovery requirements.

- 8. Must mask preceding data which don't satisfy twr

Remark: H = High level, L = Low level, X = High or Low level (Don't Care), V = Valid data

#### 9.3 Function Truth Table for CKE

| CURRENT                                 | CK  | Έ | cs      |     | CAS |    | ADDRESS | ACTION                              | NOTES |

|-----------------------------------------|-----|---|---------|-----|-----|----|---------|-------------------------------------|-------|

| STATE                                   | n-1 | n | CS      | RAS | CAS | WE | ADDRESS | ACTION                              | NOTES |

| H X X X X X                             |     | Х | INVALID |     |     |    |         |                                     |       |

|                                         | L   | Н | н       | Х   | Х   | Х  | Х       | Exit Self Refresh->Idle after txsnR |       |

| Self Refresh                            | L   | Н | L       | н   | Н   | Х  | Х       | Exit Self Refresh->Idle after txsnR |       |

| Sell Refresh                            | L   | Н | L       | Н   | L   | Х  | Х       | ILLEGAL                             |       |

|                                         | L   | Н | L       | L   | Х   | Х  | Х       | ILLEGAL                             |       |

|                                         | L   | L | Х       | Х   | Х   | Х  | Х       | Maintain Self Refresh               |       |

|                                         | н   | Х | Х       | Х   | Х   | Х  | Х       | INVALID                             |       |

| Power Down                              | L   | Н | Х       | Х   | Х   | Х  | Х       | Exit Power down->Idle after tis     |       |

|                                         | L   | L | Х       | Х   | Х   | Х  | Х       | Maintain power down mode            |       |

|                                         | н   | Н | Х       | Х   | Х   | Х  | Х       | Refer to Function Truth Table       |       |

|                                         | н   | L | Н       | Х   | Х   | Х  | Х       | Enter Power down                    | 2     |

|                                         | н   | L | L       | Н   | Н   | Х  | Х       | Enter Power down                    | 2     |

| All banks Idle                          | н   | L | L       | L   | L   | н  | Х       | Self Refresh                        | 1     |

|                                         | н   | L | L       | н   | L   | Х  | Х       | ILLEGAL                             |       |

|                                         | н   | L | L       | L   | Х   | Х  | Х       | ILLEGAL                             |       |

|                                         | L   | Х | Х       | Х   | Х   | Х  | Х       | Power down                          |       |

|                                         | н   | Н | Х       | Х   | Х   | Х  | Х       | Refer to Function Truth Table       |       |

|                                         | н   | L | н       | Х   | Х   | Х  | Х       | Enter Power down                    | 3     |

|                                         | н   | L | L       | н   | Н   | Х  | Х       | Enter Power down                    | 3     |

| Row Active                              | н   | L | L       | L   | L   | Н  | Х       | ILLEGAL                             |       |

|                                         | н   | L | L       | н   | L   | Х  | Х       | ILLEGAL                             |       |

|                                         | н   | L | L       | L   | Х   | Х  | Х       | ILLEGAL                             |       |

|                                         | L   | Х | Х       | Х   | Х   | Х  | Х       | Power down                          |       |

| Any State<br>Other Than<br>Listed Above | н   | Н | х       | х   | х   | х  | Х       | Refer to Function Truth Table       |       |

#### Notes:

1. Self refresh can enter only from the all banks idle state.

2. Power Down occurs when all banks are idle; this mode is referred to as precharge power down.

3. Power Down occurs when there is a row active in any bank; this mode is referred to as active power down.

Remark: H = High level, L = Low level, X = High or Low level (Don't Care), V = Valid data

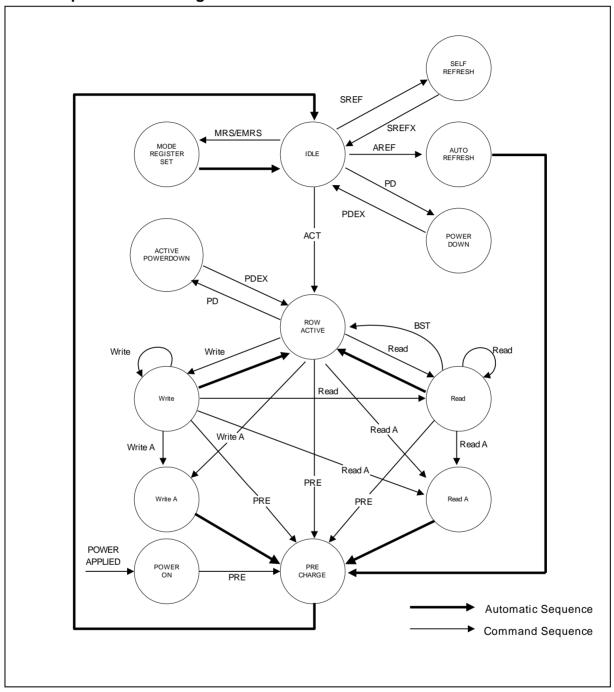

#### 9.4 Simplified Stated Diagram

# **FEES winbond**

#### **10. ELECTRICAL CHARACTERISTICS**

#### **10.1 Absolute Maximum Ratings**

| PARAMETER                              | SYMBOL    | RATING           | UNIT |

|----------------------------------------|-----------|------------------|------|

| Voltage on I/O Pins Relative to VSS    | Vin, Vout | -0.5 ~ VDDQ +0.5 | V    |

| Voltage on Input Pins Relative to VSS  | VIN       | -1 ~ 3.6         | V    |

| Voltage on VDD Supply Relative to VSS  | Vdd       | -1 ~ 3.6         | V    |

| Voltage on VDDQ Supply Relative to VSS | Vddq      | -1 ~ 3.6         | V    |

| Operating Temperature (-5)             | Topr      | 0 ~ 70           | °C   |

| Operating Temperature (-5I)            | Topr      | -40 ~ 85         | °C   |

| Storage Temperature                    | Тѕтс      | -55 ~ 150        | °C   |

| Soldering Temperature (10s)            | TSOLDER   | 260              | °C   |

| Power Dissipation                      | PD        | 1                | W    |

| Short Circuit Output Current           | Ιουτ      | 50               | mA   |

Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **10.2 Recommended DC Operating Conditions**

(TA = 0 to 70°C for -5, TA = -40 to 85°C for -5I)

| SYM.      | PARAMETER                                              | MIN.         | TYP.        | MAX.         | UNIT | NOTES  |

|-----------|--------------------------------------------------------|--------------|-------------|--------------|------|--------|

| Vdd       | Power Supply Voltage (for -5/-5I)                      | 2.3          | 2.5         | 2.7          | V    | 2      |

| Vddq      | I/O Buffer Supply Voltage (for -5/-5I)                 | 2.3          | 2.5         | 2.7          | V    | 2      |

| Vref      | Input reference Voltage                                | 0.49 x Vddq  | 0.50 x Vddq | 0.51 x Vddq  | V    | 2, 3   |

| Vtt       | Termination Voltage (System)                           | Vref - 0.04  | Vref        | Vref + 0.04  | V    | 2, 8   |

| VIH (DC)  | Input High Voltage (DC)                                | Vref + 0.15  | -           | Vddq + 0.3   | V    | 2      |

| VIL (DC)  | Input Low Voltage (DC)                                 | -0.3         | -           | Vref - 0.15  | V    | 2      |

| VICK (DC) | Differential Clock DC Input Voltage                    | -0.3         | -           | Vddq + 0.3   | V    | 15     |

| VID (DC)  | Input Differential Voltage.<br>CLK and CLK inputs (DC) | 0.36         | -           | VDDQ + 0.6   | V    | 13, 15 |

| VIH (AC)  | Input High Voltage (AC)                                | Vref + 0.31  | -           | -            | V    | 2      |

| VIL (AC)  | Input Low Voltage (AC)                                 | -            | -           | Vref - 0.31  | V    | 2      |

| VID (AC)  | Input Differential Voltage.<br>CLK and CLK inputs (AC) | 0.7          | -           | Vddq + 0.6   | V    | 13, 15 |

| VX (AC)   | Differential AC input Cross Point Voltage              | Vddq/2 - 0.2 | -           | Vddq/2 + 0.2 | V    | 12, 15 |

| VISO (AC) | Differential Clock AC Middle Point                     | Vddq/2 - 0.2 | -           | VDDQ/2 + 0.2 | V    | 14, 15 |

Notes: VIH (DC) and VIL (DC) are levels to maintain the current logic state. VIH (AC) and VIL (AC) are levels to change to the new logic state.

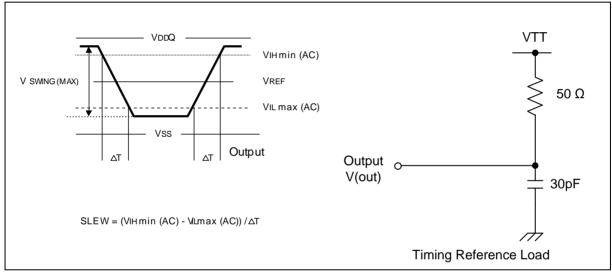

#### 10.3 Capacitance

(VDD = VDDQ = 2.5V ± 0.2V, f = 1 MHz, TA = 25°C, VOUT (DC) = VDDQ/2, VOUT (Peak to Peak) = 0.2V)

| SYMBOL | PARAMETER                               | MIN. | MAX. | DELTA<br>(MAX.) | UNIT |

|--------|-----------------------------------------|------|------|-----------------|------|

| CIN    | Input Capacitance (except for CLK pins) | 2.0  | 3.0  | 0.5             | pF   |

| CCLK   | Input Capacitance (CLK pins)            | 2.0  | 3.0  | 0.25            | pF   |

| Cı/o   | DQ, DQS, DM Capacitance                 | 4.0  | 5.0  | 0.5             | pF   |

| CNC    | NC Pin Capacitance                      | -    | 1.5  | -               | pF   |

winbond \_\_\_\_

Notes: These parameters are periodically sampled and not 100% tested.

The NC pins have additional capacitance for adjustment of the adjacent pin capacitance.

#### **10.4 Leakage and Output Buffer Characteristics**

| SYMBOL   | PARAMETER                                                                                                                         | MIN.      | MAX.      | UNIT | NOTES |

|----------|-----------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|------|-------|

| lı (L)   | Input Leakage Current<br>Any input $0V \le VIN \le VDD$ , VREF Pin $0V \le VIN \le 1.35V$<br>(All other pins not under test = 0V) | -2        | 2         | μA   |       |

| IO (L)   | Output Leakage Current (Output disabled, $0V \le VOUT \le VDDQ$ )                                                                 | -5        | 5         | μΑ   |       |

| Vон      | Output High Voltage<br>(under AC test load condition)                                                                             | Vtt +0.76 | -         | V    |       |

| Vol      | Output Low Voltage<br>(under AC test load condition)                                                                              | -         | Vtt -0.76 | V    |       |

| Іон      | Output Levels: Full drive option<br>High Current<br>(VOUT = VDDQ - 0.373V, min. VREF, min. VTT                                    | -15       | -         | mA   | 4, 6  |

| lol      | Low Current<br>(Vout = 0.373V, max. VREF, max. VTT)                                                                               | 15        | -         | mA   | 4, 6  |

| Iohr     | Output Levels: Reduced drive option - 60%<br>High Current<br>(Vout = Vddq - 0.763V, min. VREF, min. VTT                           | -9        | -         | mA   | 5     |

| Iolr     | Low Current<br>(Vout = 0.763V, max. VREF, max. Vtt)                                                                               | 9         | -         | mA   | 5     |

| IOHR(30) | Output Levels: Reduced drive option - 30%<br>High Current<br>(VOUT = VDDQ - 1.056V, min. VREF, min. VTT                           | -4.5      | -         | mA   | 5     |

| IOLR(30) | Low Current<br>(Vout = 1.056V, max. VREF, max. VTT)                                                                               | 4.5       | -         | mA   | 5     |

#### **10.5 DC Characteristics**

| SYM.  | PARAMETER                                                                          | MAX.<br>-5/-5I | UNIT | NOTES |

|-------|------------------------------------------------------------------------------------|----------------|------|-------|

|       |                                                                                    | -5/-51         |      |       |

|       | Operating current: One Bank Active-Precharge;<br>tRc = tRc min; tcк = tcк min;     |                |      |       |

| IDD0  | DQ, DM and DQS inputs changing once per clock cycle;                               | 45             |      | 7     |

|       | Address and control inputs changing once every two clock cycles                    |                |      |       |

|       | Operating current: One Bank Active-Read-Precharge;                                 |                |      |       |

| IDD1  | Burst = 4; trc = trc min; $CL = 3$ ; tck = tck min; $IOUT = 0$ mA;                 | 55             |      | 7, 9  |

|       | Address and control inputs changing once per clock cycle                           |                |      |       |

| DD2P  | Precharge Power Down standby current:<br>All Banks Idle; Power down mode;          | 5              |      |       |

| IDDZI | CKE $\leq$ VIL max; tck = tck min; Vin = VREF for DQ, DQS and DM                   | Ŭ              |      |       |

|       | Idle standby current:                                                              |                |      |       |

|       | $\overline{CS} \ge V_{H}$ min; All Banks Idle; CKE $\ge V_{H}$ min; tck = tck min; | 05             |      |       |

| IDD2N | Address and other control inputs changing once per clock cycle;                    | 25             |      |       |

|       | Vin ≥ VIH min or Vin ≤ VI∟ max for DQ, DQS and DM                                  |                |      |       |

|       | Idle floating standby current:                                                     |                |      |       |

| DD2F  | CS ≥ VIH min; All Banks Idle; CKE ≥ VIH min;                                       | 25             |      | 7     |

| IDDZI | Address and other control inputs changing once per clock cycle;                    | 20             |      |       |

|       | Vin = VREF for DQ, DQS and DM                                                      |                |      |       |

|       | Idle quiet standby current:                                                        |                |      |       |

| DD2Q  | CS ≥ VIH min; All Banks Idle; CKE ≥ VIH min;                                       | 25             |      | 7     |

|       | Address and other control inputs stable at > VIH min or $\leq$ VIL max;            |                |      |       |

|       | Vin ≥ VREF for DQ, DQS and DM                                                      |                |      |       |

|       | Active Power Down standby current:<br>One Bank Active; Power down mode;            |                |      |       |

| IDD3P | $CKE \le V_{IL}$ max; tck = tck min                                                | 15             | mA   |       |

|       | Vin = $V_{REF}$ for DQ, DQS and DM                                                 |                |      |       |

|       | Active standby current:                                                            |                |      |       |

|       | $\overline{CS} \ge V_{IH}$ min; CKE $\ge V_{IH}$ min; One Bank Active-Precharge;   |                |      |       |

| IDD3N | tRC = tRAS max; tCK = tCK min;                                                     | 30             |      | 7     |

|       | DQ, DM and DQS inputs changing twice per clock cycle;                              |                |      |       |