# ZCU1285 Characterization Board

# **User Guide**

UG1348 (v1.0) July 16, 2019

# **Revision History**

The following table shows the revision history for this document.

| Section                | Revision Summary |  |

|------------------------|------------------|--|

| 07/16/2019 Version 1.0 |                  |  |

| Initial release.       | N/A              |  |

# Table of Contents

| Revision History                                  | 2  |

|---------------------------------------------------|----|

| Chapter 1: 7011285 Board Features and Operation   | -  |

| Chapter 1: ZCU1285 Board Features and Operation   |    |

| Electrostatic Discharge Caution                   |    |

| Zynq UltraScale+ RFSoC Compatibility              |    |

| ZCU1285 Board Features                            |    |

| Board Component Locations                         |    |

| Power Management                                  |    |

| Analog Power Module                               |    |

| Serial Transceiver Power Modules                  |    |

| Zynq UltraScale+ RFSoC                            |    |

| Quad SPI Flash Memory                             |    |

| SD Card                                           |    |

| DDR3 Memory                                       |    |

| RF Data Converters and Sampling Clocks            |    |

| Serial Transceivers and Reference Clocks          |    |

| SuperClock-2 Module                               |    |

| SuperClock-RF2 Module                             |    |

| Balun Board                                       |    |

| FPGA Mezzanine Card Interface                     |    |

| System Controller                                 | 50 |

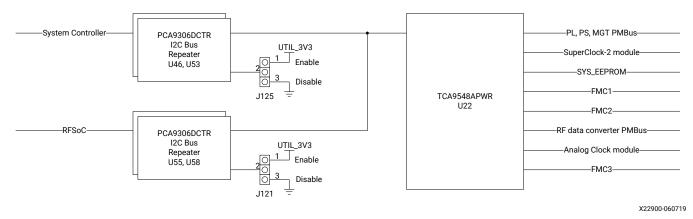

| I2C Bus Management                                | 50 |

| USB to Quad-UART Bridge                           | 52 |

| Default Jumper and Switch Positions               |    |

| Active Heat Sink and Power Connector              | 53 |

| Appendix A: Regulatory and Compliance Information | 56 |

| CE Information                                    |    |

| Compliance Markings                               |    |

| Appendix B: Default Jumper Settings               | 58 |

| Appendix C: VITA 57.1 FMC Connector Pinouts       | 60 |

| Appendix D: Master Constraints File Listing        | 62 |

|----------------------------------------------------|----|

| Appendix E: System Controller                      | 63 |

| Connecting the System Controller User Interface    |    |

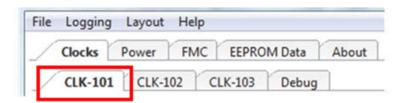

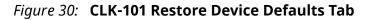

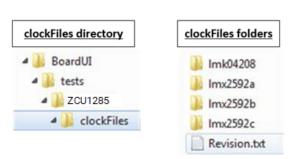

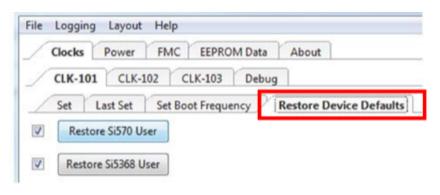

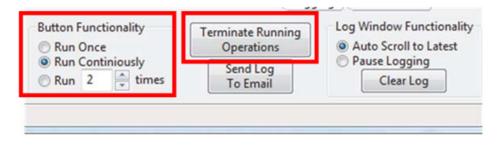

| Programmable Clocks Tab                            | 65 |

| Power Tab                                          |    |

| Read a Single Power Rail                           | 74 |

| Read Multiple Power Rails                          | 75 |

| Read Power Rails Continuously                      | 76 |

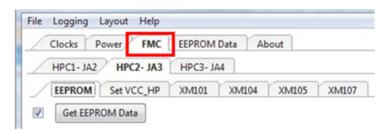

| FMC Tab                                            | 77 |

| EEPROM Data Tab                                    | 79 |

| Write Board EEPROM Data                            |    |

| Read Board EEPROM Data                             | 81 |

| Appendix F: Additional Resources and Legal Notices | 83 |

| Xilinx Resources                                   | 83 |

| Documentation Navigator and Design Hubs            | 83 |

| References                                         | 84 |

| Please Read: Important Legal Notices               | 84 |

# **XILINX**.

# ZCU1285 Board Features and Operation

This user guide describes the components, features, and operation of the Xilinx<sup>®</sup> Zynq<sup>®</sup> UltraScale+<sup>™</sup> RFSoC ZCU1285 characterization kit. The ZCU1285 kit provides the hardware environment for characterizing and evaluating the radio frequency data converter subsystem (RF-ADC/RF-DAC) and high-speed serial transceivers (GTY/PS-GTR) available on the XCZU39DR-2FFVF1760I Zynq UltraScale+ RFSoC. The ZCU1285 schematic, bill of material (BOM), and Allegro board files are in the XTP document package on the Zynq UltraScale+ RFSoC ZCU1285 Characterization Kit website.

## **Electrostatic Discharge Caution**

**CAUTION!** ESD can damage electronic components when they are improperly handled, and can result in total or intermittent failures. Always follow ESD-prevention procedures when removing and replacing components.

To prevent ESD damage:

- Use an ESD wrist or ankle strap and ensure that it makes skin contact. Connect the equipment end of the strap to an unpainted metal surface on the chassis.

- Avoid touching the adapter against your clothing. The wrist strap protects components from ESD on the body only.

- Handle the adapter by its bracket or edges only. Avoid touching the printed circuit board or the connectors.

- Put the adapter down only on an antistatic surface such as the bag supplied in your kit.

- If you are returning the adapter to Xilinx<sup>®</sup> Product Support, place it back in its antistatic bag immediately.

## Zynq UltraScale+ RFSoC Compatibility

The ZCU1285 board is provided with the XCZU39DR-2FFVF1760I Zynq UltraScale+ RFSoC. There are no other pin-compatible devices in this package.

## **ZCU1285 Board Features**

- XCZU39DR-2FFVF1760I Zynq UltraScale+ RFSoC

- Samtec Bulls Eye<sup>®</sup> cable access to all 16 radio frequency analog-to-digital converter (RF-ADC) channels

- Samtec Bulls Eye cable access to all 16 radio frequency digital-to-analog converter (RF-DAC) channels

- Samtec Bulls Eye cable access to all 16 GTY transceivers

- Samtec Bulls Eye cable access to all four PS-GTR transceivers

- Onboard power supplies for all necessary voltages

- Connectors for external power supplies

- SMA connectors for probing RF-ADC/RF-DAC power rails, GTY/PS-GTR power rails, and VCCINT/VCCO\_HP/VCCO\_HD power rails

- Embedded USB-to-JTAG programming port

- JTAG programming header

- Programmable logic (PL) JTAG connector connected to HPIO bank 66

- System Controller (Zynq-7000 SoC XC7Z010-CLG225)

- One analog power module supporting RF data converter power requirements

- One power module to support GTY transceiver power requirements

- One power module to support PS-GTR transceiver power requirements

- 300 MHz LVDS oscillator connected to HPIO global clock (GC) pins on bank 66

- 33.3333333 MHz LVCMOS oscillator connected to processing system (PS) bank 503 PS\_REF\_CLK pin

- Two pairs of SMA connectors connected to HPIO global clock (GC) pins on bank 66

- SuperClock-RF2 Module (HW-CLK-103) supporting RF data converter clock requirements

- SuperClock-2 Module (HW-CLK-101) supporting GTY/PS-GTR reference clock requirements

- General purpose DIP switches, LEDs, pushbuttons, and test I/O

- One VITA 57.1 FPGA mezzanine card (FMC) high pin count (HPC) connector

- One VITA 57.1 FPGA mezzanine card low pin count (LPC) connector

- USB-to-UART bridge connected to PL, PS, and System Controller

- Inter IC (I2C) interface

- 4x 4 Gb DDR3 SDRAM PS memory

- 1 Gb Quad SPI flash PS memory

- PMBus connectivity to the board's digital power supplies

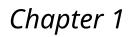

## **Block Diagram**

The ZCU1285 block diagram is shown in the following figure.

#### Figure 1: Block Diagram

X22890-060719

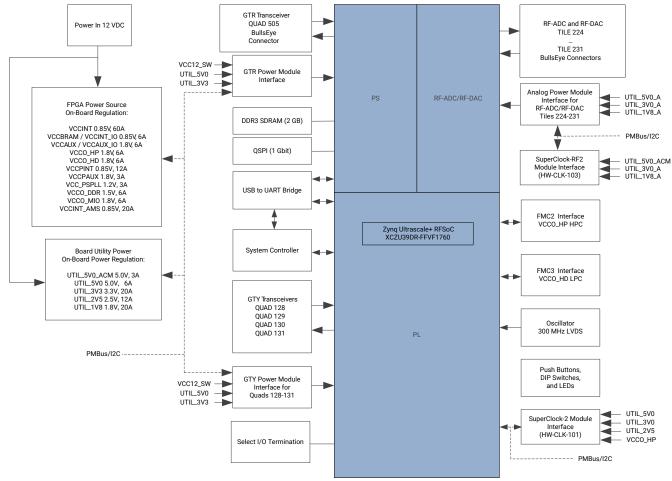

## **Board Component Locations**

The following figure shows the ZCU1285 board component locations. Each numbered component shown in the figure is keyed to the table in **Board Component Descriptions**.

**CAUTION!** Do not remove the rubber feet from the board. The feet provide clearance to prevent short circuits on the back side of the board.

**IMPORTANT!** The following figure is for reference only and might not reflect the current revision of the board.

Figure 2: Board Component Locations

X22891-060619

#### **Board Component Descriptions**

#### Table 1: Board Component Descriptions

| Callout | Reference Designator                                | Feature Description                                                                                               |

|---------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 1       | SW1                                                 | Power Switch                                                                                                      |

| 2       | J28                                                 | 12V Mini-Fit connector (12V Input Power)                                                                          |

| 3       | J27                                                 | 12V external power supply connector (12V Input Power, Using<br>External Power Sources)                            |

| 4       | J73                                                 | ATX power connector (12V Input Power)                                                                             |

| 5       | J1                                                  | USB to Quad-UART Bridge (Micro-B receptacle)                                                                      |

| 6       | J36                                                 | SuperClock-2 Module (HW-CLK-101-SCLK2)                                                                            |

| 7       | J3                                                  | System Controller JTAG connector                                                                                  |

| 8       | J69                                                 | USB-to-JTAG connector (Micro-B receptacle) (RFSoC Configuration)                                                  |

| 9       | J2                                                  | Platform USB JTAG connector (alternate access for programming cables) (RFSoC Configuration)                       |

| 10      | SW4, DS12, DS16, DS27, DS1                          | System Controller status LEDs and POR pushbutton (System Controller Reset, System Controller Status LEDs)         |

| 11      | J4, J145, J154, J8                                  | Serial transceiver power module PMBus connectors and isolation selection headers (Monitoring Voltage and Current) |

| 12      | J163, J164, J166, J165                              | Boot Mode Selection Headers                                                                                       |

| 13      | J121, J125                                          | I2C bus master selection headers (I2C Bus Management)                                                             |

| 14      | J160, J275                                          | VTT_HP external connector and selection header                                                                    |

| 15      | SW15, SW14                                          | PS_POR_B Pushbutton and PS_SRST_B Pushbutton                                                                      |

| 16      | J250, J251                                          | VCCINT power probe SMA                                                                                            |

| 17      | J276, J277                                          | VCCINT_AMS power probe SMA                                                                                        |

| 18      | J158, J159, J156, J194                              | PS-GTR ref clock SMAs (Serial Transceivers and Reference Clocks)                                                  |

| 19      | 199                                                 | Active Heat Sink and Power Connector                                                                              |

| 20      | J181                                                | VCCINT external power connector and voltage sense header                                                          |

| 21      | DS18, DS2                                           | 12V and Power Good LEDs (Power Switch)                                                                            |

| 22      | SW2                                                 | Power regulation inhibitor switch for onboard regulators (Using External Power Sources)                           |

| 23      | DS4–DS11, DS13–DS15, DS28– DS38,<br>DS42–DS45, DS49 | Status LEDS for RFSoC logic, processor, transceiver, data converter, and utility power                            |

| 24      | J149, J148, J147                                    | GTY voltage sense headers                                                                                         |

| 25      | J174, J155                                          | GTY power module (Serial Transceiver Power Modules)                                                               |

| 26      | J150                                                | GTY external power supply connector                                                                               |

| 27      | J63, J62                                            | PS-GTR voltage sense headers                                                                                      |

| 28      | J138, J93                                           | PS-GTR power module (Serial Transceiver Power Modules)                                                            |

| 29      | J67                                                 | PS-GTR external power supply connector                                                                            |

| 30      | J151, J96                                           | RFSoC logic and processor external power supply connectors                                                        |

| 31      | J146, J144, J143, J142, J64, J23, J19, J18,<br>J177 | RFSoC logic and processor voltage sense headers                                                                   |

| 32      | J21                                                 | PMBus connector (Monitoring Voltage and Current)                                                                  |

| Callout | Reference Designator                                          | Feature Description                                                                                           |

|---------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 33      | J39                                                           | PS-GTR transceiver connector pad, bank 505 (Serial Transceivers and Reference Clocks)                         |

| 34      | J117, J118, J280, J281                                        | GTY transceiver connector pads Q128, Q129, Q130, and Q131                                                     |

| 35      | U1                                                            | XCZU39DR-2FFVF1760I, Zynq UltraScale+ RFSoC                                                                   |

| 36      | J124, J278, J129, J279                                        | RF-ADC and RF-DAC Bulls Eye connector pads, tiles 224–231 (RF Data Converters and Sampling Clocks)            |

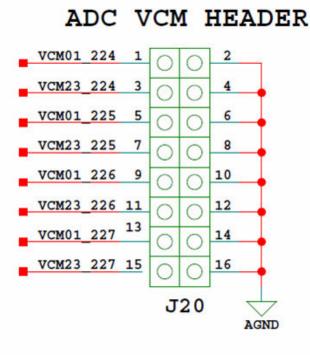

| 37      | J20                                                           | RF-ADC VCM connector                                                                                          |

| 38      | J75, J76, J78, J81, J79                                       | RF-ADC and RF-DAC voltage sense headers                                                                       |

| 39      | J46, J43, J60, J25                                            | RF-ADC and RF-DAC PMBus connector and selection headers<br>(Monitoring Voltage and Current)                   |

| 40      | J114, J115, J116, J107, J113                                  | RF-ADC and RF-DAC external power supply connectors                                                            |

| 41      | J131, J119, J120                                              | Analog Power Module                                                                                           |

| 42      | J170                                                          | SuperClock-RF2 Module(HW-CLK-103)                                                                             |

| 43      | SW16, SW17, J95, SW3, DS22– DS26,<br>DS46–DS48                | User configurable I/O header, DIP switch, LEDs, and pushbuttons (User LEDs, User DIP Switches and I/O Header) |

| 44      | SW7                                                           | RFSoC PROGRAM Pushbutton                                                                                      |

| 45      | DS40, DS39, DS17, DS3                                         | RFSoC DONE LED, INIT LED, STATUS LED, and ERROR LED                                                           |

| 46      | J106, J216                                                    | VTT_HP external connector and selection header                                                                |

| 47      | J190, J189, J188, J187, J192, J191, J257,<br>J256, J162, J161 | Power probe SMAs for DAC_AVCC, DAC_AVTT, DAC_AVCCAUX, ADC_AVCC, and ADC_AVCCAUX                               |

| 48      | J243, J242                                                    | RF-DAC SYSREF SMA                                                                                             |

| 49      | J84, J85, J83, J86                                            | SMA connectors to differential GC pins on RFSoC (Differential SMA Pin Inputs)                                 |

| 50      | ]5                                                            | PL JTAG connector tied to RFSoC I/O pins                                                                      |

| 51      | J254, J255, J253, J252                                        | Power probe SMAs for VCCO_HP and VCCO_HD                                                                      |

| 52      | J287                                                          | RFSoC SD Cardslot (bottom side of board)                                                                      |

| 53      | JA3                                                           | FMC2 HPC connector tied to VCCO_HP banks (FPGA Mezzanine Card Interface, FMC Tab)                             |

| 54      | JA4                                                           | FMC3 LPC connector tied to VCCO_HD banks (FPGA Mezzanine Card Interface, FMC Tab)                             |

| Table 1: | <b>Board Component</b> | <b>Descriptions</b> (cont'd) |

|----------|------------------------|------------------------------|

|----------|------------------------|------------------------------|

## **Power Management**

#### **12V Input Power**

The ZCU1285 board receives 12V main power through J28 (callout 2, Figure 2: Board Component Locations) using the 12V AC adapter included with the ZCU1285 characterization kit. J28 is a 6-pin (2 x 3), right angle, Mini-Fit connector.

**CAUTION!** When supplying 12V through J28, use only the power supply provided for use with this board (Xilinx part number 3800033).

CAUTION! Do NOT use a 6-pin, PC ATX power supply connector with J28. The pinout of the 6-pin, PC ATX connector is not compatible with J28 and the board will be damaged if an attempt is made to power it from a PC ATX power supply connector.

12V power can also be provided through:

- Connector J73 (callout 4, Figure 2: Board Component Locations) which accepts an ATX hard drive 4-pin power plug

- Connector J27 (callout 3, Figure 2: Board Component Locations) which can be connected to a bench-top power supply

- **CAUTION!** Because connector J73 provides no reverse polarity protection, use a power supply with a current limit set at 6A maximum.

**CAUTION!** Do NOT apply 12V power to more than a single input source. For example, do not apply power to J73 and J27 at the same time.

**CAUTION!** If J73 or J27 is used to supply the 12V input power, be careful that board power consumption does not exceed 75W (this includes the RFSoC).

#### **Power Switch**

The ZCU1285 board main power is turned on or off using switch SW1 (callout 1, Figure 2: Board Component Locations). When the switch is in the ON position, power is applied to the board and the power good LED DS18 illuminates green (callout 21, Figure 2: Board Component Locations).

## **Onboard Power Regulation**

#### ZCU1285 Power Supply Block Diagram

The following figure shows the onboard power supply architecture.

| V PWR    | Maxim 20751<br>MultiPhase Master                          | U23  |                                      |    |  |  |  |

|----------|-----------------------------------------------------------|------|--------------------------------------|----|--|--|--|

|          | Maxim VT1697SBFXQ                                         | U118 |                                      |    |  |  |  |

|          | 0.85V at 20A max<br>Maxim VT1697SBFXQ<br>0.85V at 20A max | U137 | VCCINT                               | •  |  |  |  |

|          | Maxim VT1697SBFXQ<br>0.85V at 20A max                     | U138 |                                      |    |  |  |  |

|          | Maxim 15303                                               | U24  | VCCAUX / VCCAUX_IO                   |    |  |  |  |

|          | 1.8V at 6A max                                            |      | VCCBRAM / VCCINT_10                  |    |  |  |  |

|          | Maxim 15303<br>0.85V at 6A max                            | U47  | VCCO_HP                              |    |  |  |  |

| $\vdash$ | Maxim 15303<br>1.8V at 6A max                             | U29  |                                      |    |  |  |  |

| ┝        | Maxim 15303<br>1.8V at 6A max                             | U31  | VCCO_HD                              | -> |  |  |  |

| $\vdash$ | Maxim 15301<br>0.85V at 12A max                           | U28  | VCCPINT                              | •  |  |  |  |

|          | Maxim 15303<br>1.8V at 3A max                             | U48  | VCCPAUX                              | •  |  |  |  |

|          | Maxim 15303                                               | U27  | VCC_PSPL                             | -  |  |  |  |

|          | 1.2V at 3A max<br>Maxim 15303                             | U11  | VCCO_DDR                             | -> |  |  |  |

|          | 1.5V at 6A max<br>Maxim 15303                             | U96  | VCC0_MI0                             | -  |  |  |  |

|          | 1.8V at 6A max<br>Maxim 20751<br>MultiPhase Master        | U89  |                                      |    |  |  |  |

|          | Maxim VT1697SBFXQ                                         | U20  | VCCINT_AMS                           | -  |  |  |  |

|          | 0.85V at 20A max<br>Maxim VT1697SBFXQ<br>0.85V at 20A max | U17  |                                      |    |  |  |  |

|          | Maxim 15301<br>1.8V at 20A max                            | U50  | UTIL_1V8                             | -> |  |  |  |

|          | Maxim 15301<br>2.5V at 12A max                            | U51  | UTIL_2V5                             | -  |  |  |  |

|          | Maxim 15301<br>3.3V at 20A max                            | U30  | UTIL_3V3                             | -> |  |  |  |

|          | Maxim 15303                                               | U102 | UTIL_5V0                             | -  |  |  |  |

|          | 5.0V at 6A max                                            |      | GTY Power Module<br>Quads 128-131    |    |  |  |  |

|          |                                                           |      | 0.9V at 12.0A max MGTAVCC            | -> |  |  |  |

|          |                                                           |      |                                      | -  |  |  |  |

|          |                                                           |      | 1.8V at 2.5A max                     | -  |  |  |  |

|          |                                                           |      | GTR Power Module                     |    |  |  |  |

|          |                                                           |      | Quad 505<br>0.85V at 12.0A max       |    |  |  |  |

|          |                                                           |      | MGTAVTT_GTR                          |    |  |  |  |

|          |                                                           |      |                                      |    |  |  |  |

|          |                                                           |      | Analog Power Module<br>Tiles 224-231 |    |  |  |  |

|          |                                                           |      | 0.925V at 2.0A max ADC_AVCC          | -> |  |  |  |

|          |                                                           |      | 1.8V at 2A max                       | -> |  |  |  |

|          |                                                           |      | 0.925V at 3.5A max                   | •  |  |  |  |

|          |                                                           |      | 1.8V at 2.0A max                     | •  |  |  |  |

|          |                                                           |      | 2.5V or 3.0V at 2.0A max             | -  |  |  |  |

|          | TI LMZ31503                                               | U155 | Linear Tech LT1764 U154 UTIL_5V0_ACM |    |  |  |  |

#### Figure 3: Board Power Supply Block Diagram

X22892-071519

#### **Onboard Power System Devices**

The ZCU1285 board uses power regulators and PMBus-compliant pulse width modulation (PWM) digital controllers from Maxim Integrated to supply the RFSoC logic and utility voltages listed in the following table. The board can also be configured to use an external bench power supply for each voltage. See Using External Power Sources.

The output voltages of the controllers in the table can be reprogrammed using the Maxim InTune Digital PowerTool.

Note: The MAX20751EKX device has limited nonvolatile memory reprogramming saves (four counts).

**CAUTION!** Be extremely careful when attempting to modify any of the onboard regulators, because an incorrectly programmed regulator can damage onboard components.

| Device Part Number             | Reference<br>Designator(s) | Description                                                                                 | Power Rail Net<br>Name | Voltage |

|--------------------------------|----------------------------|---------------------------------------------------------------------------------------------|------------------------|---------|

| RFSoC Logic                    |                            |                                                                                             |                        |         |

| Maxim MAX20751EKX <sup>1</sup> | U23                        | Multiphase master with<br>PMBus interface controller<br>(60A three phases at 20A/<br>phase) | VCCINT                 | 0.85V   |

| Maxim MAX15303                 | U24                        | InTune digital point of load<br>(PoL) controller, 6A                                        | VCCAUX / VCCAUX_IO     | 1.8V    |

| Maxim MAX15303                 | U47                        | InTune digital point of load<br>(PoL) controller, 6A                                        | VCCBRAM / VCCINT_IO    | 0.85V   |

| Maxim MAX15303                 | U29                        | InTune digital point of load<br>(PoL) controller, 6A                                        | VCCO_HP                | 1.8V    |

| Maxim MAX15303                 | U31                        | InTune digital point of load<br>(PoL) controller, 6A                                        | VCCO_HD                | 1.8V    |

| Processor                      |                            |                                                                                             | •                      |         |

| Maxim MAX15301                 | U28                        | InTune digital point of load<br>(PoL) controller, 12A                                       | VCCPINT                | 0.85V   |

| Maxim MAX15303                 | U48                        | InTune digital point of load<br>(PoL) controller, 3A                                        | VCCPAUX                | 1.8V    |

| Maxim MAX15303                 | U27                        | InTune digital point of load<br>(PoL) controller, 3A                                        | VCC_PSPLL              | 1.2V    |

| Maxim MAX15303                 | U11                        | InTune digital point of load<br>(PoL) controller, 6A                                        | VCCO_DDR               | 1.5V    |

| Maxim MAX15303                 | U96                        | InTune digital point of load<br>(PoL) controller, 6A                                        | VCCO_MIO               | 1.8V    |

| RF Data Converters             |                            |                                                                                             |                        |         |

| Maxim MAX20751EKX <sup>1</sup> | U89                        | Multiphase master with<br>PMBus interface controller<br>(40A two                            | VCCINT_AMS             | 0.85V   |

|                                |                            | phases at 20A/phase)                                                                        |                        |         |

| INA226                         | U60                        | Current shunt and power monitor with I2C interface                                          | ADC_AVCC               | 0.925V  |

#### Table 2: Onboard Power System Devices

| Table 2: | Onboard | Power | System | <b>Devices</b> (cont'd) |

|----------|---------|-------|--------|-------------------------|

|----------|---------|-------|--------|-------------------------|

| Device Part Number  | Reference<br>Designator(s) | Description                                           | Power Rail Net<br>Name | Voltage         |  |

|---------------------|----------------------------|-------------------------------------------------------|------------------------|-----------------|--|

| INA226              | U61                        | Current shunt and power monitor with I2C interface    | ADC_AVCCAUX            | 1.8V            |  |

| INA226              | U63                        | Current shunt and power monitor with I2C interface    | DAC_AVCC               | 0.925V          |  |

| INA226              | U64                        | Current shunt and power monitor with I2C interface    | DAC_AVTT               | 1.8V            |  |

| INA226              | U65                        | Current shunt and power monitor with I2C interface    | DAC_AVCCAUX            | 2.5V or<br>3.0V |  |

| GTY Transceivers    |                            |                                                       | •                      |                 |  |

| INA226              | U141                       | Current shunt and power monitor with I2C interface    | MGTAVCC                | 0.9V            |  |

| INA226              | U142                       | Current shunt and power monitor with I2C interface    | MGTAVTT                | 1.2V            |  |

| INA226              | U143                       | Current shunt and power monitor with I2C interface    | MGTVCCAUX              | 1.8V            |  |

| PS-GTR Transceivers |                            |                                                       |                        |                 |  |

| INA226              | U99                        | Current shunt and power monitor with I2C interface    | MGTAVCC_GTR            | 0.85V           |  |

| INA226              | U97                        | Current shunt and power monitor with I2C interface    | MGTAVTT_GTR            | 1.8V            |  |

| Utility             |                            |                                                       |                        | •               |  |

| Maxim MAX15301 U50  |                            | InTune digital point of load<br>(PoL) controller, 20A | UTIL_1V8               | 1.8V            |  |

| Maxim MAX15301      | U51                        | InTune digital point of load<br>(PoL) controller, 12A | UTIL_2V5               | 2.5V            |  |

| Maxim MAX15301      | U30                        | InTune digital point of load<br>(PoL) controller, 20A | UTIL_3V3               | 3.3V            |  |

| Maxim MAX15301      | U102                       | InTune digital point of load<br>(PoL) controller, 12A | UTIL_5V0               | 5.0V            |  |

| LMZ31503            | U155                       | DC/DC converter, 3A                                   | UTIL_5V4               | 5.4V            |  |

| LT1764              | U154                       | Fixed LDO regulator                                   | UTIL_5V0_ACM           | 5.0V            |  |

| System Controller   |                            |                                                       |                        | -               |  |

| Maxim MAX15053      | U13                        | Fixed LDO regulator                                   | SYS_1V0                | 1.0V            |  |

| Maxim MAX15027      | U25                        | Fixed LDO regulator                                   | VCC_1V2                | 1.2V            |  |

| Maxim MAX15027      | U33                        | Fixed LDO regulator                                   | VCC_1V8                | 1.8V            |  |

Notes:

1. The MAX20751EKX device has limited nonvolatile memory reprogramming saves (four counts).

#### **Using External Power Sources**

Each voltage rail for the RFSoC logic, multi-gigabit transceivers (MGTs), and RF data converters has an associated Euro-Mag spring-clamp terminal block (callout 3, 14, 20, 26, 29, 30, 40, and 46, Figure 2: Board Component Locations), which can be used to provide power from an external source (see the following table).

**CAUTION!** Do NOT apply power to any of the RFSoC logic external power supply connectors without first disabling the associated regulator or regulators. Failing to disable the regulator can damage the board.

Each onboard RFSoC logic regulator can be disabled using its respective power regulation inhibit DIP switch (callout 22, Figure 2: Board Component Locations). A regulator is enabled when the power regulation inhibitor switch is set to the ENABLED position. The following table lists the external power connectors for the different power rails.

|                           | Power Rail Net Name | External<br>Supply<br>Connector(s) | Remote Sense<br>Header |

|---------------------------|---------------------|------------------------------------|------------------------|

|                           | VCCINT              | J181                               | J22                    |

|                           | VCCBRAM             |                                    | J74                    |

|                           | VCCAUX              |                                    | J23                    |

|                           | VCCO_HP             | J96                                | J19                    |

|                           | VCCO_HD             |                                    | J18                    |

| RFSoC Logic and Processor | VCCPINT             |                                    | J177                   |

|                           | VCCPAUX             |                                    | J146                   |

|                           | VCC_PSPLL           |                                    | J144                   |

|                           | VCCO_DDR            | J151                               | J143                   |

|                           | VCCO_MIO            |                                    | J142                   |

|                           | VCCINT_AMS          |                                    | J64                    |

|                           | MGTAVCC             |                                    | J147                   |

| GTY Transceivers          | MGTAVTT             | J150                               | J148                   |

|                           | MGTVCCAUX           |                                    | J149                   |

| PS-GTR Transceivers       | MGTAVCC_GTR         | 167                                | J62                    |

| PS-GTR Transceivers       | MGTAVTT_GTR         | J67                                | J63                    |

|                           | ADC_AVCC            | J114                               | J79                    |

|                           | ADC_AVCCAUX         | J115                               | J81                    |

| RF Data Converters        | DAC_AVCC            | J116                               | J75                    |

|                           | DAC_AVTT            | J107                               | J76                    |

|                           | DAC_AVCCAUX         | J113                               | J78                    |

#### Table 3: RFSoC Logic and Serial Transceiver Rails

Notes:

1. The serial transceiver or analog power module must be removed before providing external power to any of the transceiver or data converter rails (see Serial Transceiver Power Modules).

#### Monitoring Voltage and Current

Voltage and current monitoring and control for the Maxim power system is available through either the ZCU1285 System Controller or via the Maxim PowerTool software GUI.

The ZCU1285 System Controller is the simplest and most convenient way to monitor the voltage and current values for the power rails listed in Onboard Power System Devices. For details on how to use this built-in feature, see Power Tab.

The ZCU1285 board includes these PMBus connectors:

- J21 (callout 32, Figure 2: Board Component Locations), for use with the Maxim USB-to-PMBus interface dongle (Maxim part number MAXPOWERTOOL002) and the Maxim PowerTool GUI.

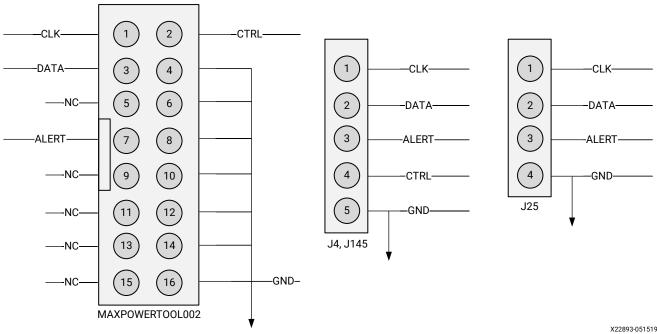

- J4 and J145 (callout 11, Figure 2: Board Component Locations) are used to connect to the serial transceiver power module's PMBus. The pinouts for J4 and J145 are shown in the following figure

- J25 (callout 39, Figure 2: Board Component Locations) is used to connect to the analog power module PMBus. The pinout for J25 is shown in the following figure.

#### Figure 4: PMBus Connector Pinouts

The onboard Maxim power controllers by default are isolated from the serial transceiver power module's PMBus. However, the two interfaces can be linked by removing the shunt on J8 or J154 (serial transceiver PMBus isolation). This configuration is required when using Maxim PowerTool to monitor and control both the RFSoC power rails and the serial transceiver power rails using the Maxim InTune Digital PowerTool GUI.

## **Analog Power Module**

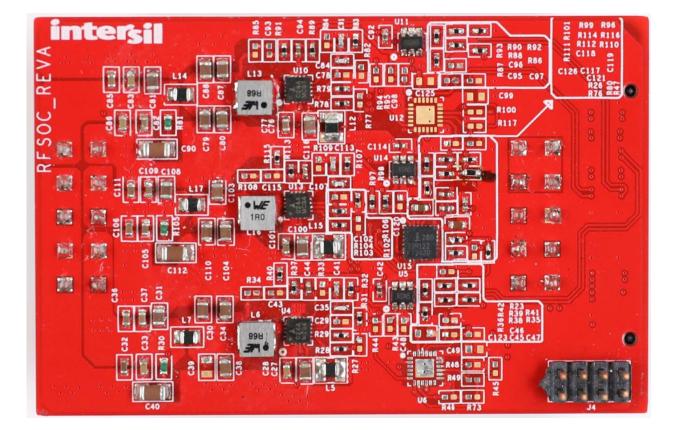

There is one analog power module interface for connecting an analog power module (callout 41, Figure 2: Board Component Locations). The analog power module supplies power to the ADC\_AVCC, ADC\_AVCCAUX, DAC\_AVCC, DAC\_AVTT, and DAC\_AVCCAUX rails, which power the RFSoC RF data converters. The analog power module connects to J131, J119, and J120. Two analog power modules are provided with the ZCU1285 board for evaluation. One module is made by Intersil with part number ISL8024DEMO2Z and the other is made by MPS with part number EVREF0102A. See the following two figures.

Figure 5: Intersil Analog Power Module

*Figure 6:* MPS Analog Power Module

The following table lists the nominal voltage values for the ADC\_AVCC, ADC\_AVCCAUX, DAC\_AVCC, DAC\_AVTT, and DAC\_AVCCAUX power rails. It also lists the maximum current rating for each rail supplied by the analog power modules included with the ZCU1285 characterization kit.

| Table 4: | Analog | Power | Module |

|----------|--------|-------|--------|

|----------|--------|-------|--------|

| Analog Rail Net Name | Nominal Voltage (V) | Maximum Current Rating (A) |

|----------------------|---------------------|----------------------------|

| ADC_AVCC             | 0.925               | 2.00                       |

| ADC_AVCCAUX          | 1.8                 | 2.00                       |

| DAC_AVCC             | 0.925               | 3.5                        |

| DAC_AVCCAUX          | 1.8                 | 2.00                       |

| DAC_AVTT             | 2.5 or 3.0          | 2.00                       |

The analog power rails can also be supplied externally. The external supply connectors are listed in the table in Using External Power Sources.

**CAUTION!** The analog power module MUST be removed when providing external power to the RF data converter rails.

Information about the analog power modules included with the ZCU1285 characterization kit is available from the vendor websites Renesas Power Management and Monolithic Power Systems

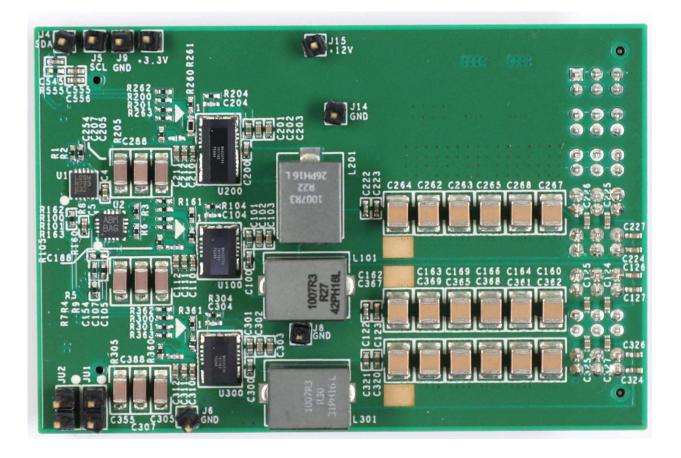

## **Serial Transceiver Power Modules**

There is one GTY transceiver power module interface (callout 25, Figure 2: Board Component Locations). The GTY transceiver power module supplies the MGTAVCC, MGTAVTT, and MGTVCCAUX power rails, which connect to the RFSoC GTY transceivers. In the ZCU1285 characterization kit, there is one GTY transceiver power module from Maxim Integrated provided for evaluation, part number MAXREFDES87#. The GTY transceiver power module is labeled GTY and connects to J174 and J155.

There is one PS-GTR transceiver power module interface (callout 28, Figure 2: Board Component Locations). The PS-GTR transceiver power module supplies the MGTAVCC\_GTR and MGTAVTT\_GTR power rails, which connect the RFSoC PS-GTR transceivers. In the ZCU1285 characterization kit, there is one PS-GTR transceiver power module from Maxim Integrated provided for evaluation, part number MAXREFDES87#. The PS-GTR power module is labeled PS-GTR and connects to J138 and J93.

#### Figure 7: Maxim Integrated Serial Transceiver Power Module

The following table lists the nominal voltage values for the MGTAVCC, MGTAVTT, MGTVCCAUX, MGTAVCC\_GTR, and MGTAVTT\_GTR power rails. It also lists the maximum current rating for each rail supplied by serial transceiver modules included with the ZCU1285 board.

| Table 5: Serial Transceiver Power Mo | odules |

|--------------------------------------|--------|

|--------------------------------------|--------|

| Serial Transceiver Rail Net<br>Name | Nominal Voltage (V) | Maximum Current Rating (A) |

|-------------------------------------|---------------------|----------------------------|

| MGTAVCC                             | 0.9                 | 12                         |

| MGTAVTT                             | 1.2                 | 20                         |

| MGTVCCAUX                           | 1.8                 | 2.5                        |

| MGTAVCC_GTR                         | 0.85                | 12                         |

| MGTAVTT_GTR                         | 1.8                 | 2.5                        |

The serial transceiver power rails can also be supplied externally. The external supply connectors are listed in the table in Using External Power Sources.

**CAUTION!** The serial transceiver power module MUST be removed when providing external power to the GTY or PS-GTR transceiver rails.

*Note*: For information about the serial transceiver power modules, contact Maxim technical support and ask about the MAXREFDES87#.

## Zynq UltraScale+ RFSoC

The ZCU1285 board is populated with the XCZU39DR-2FFVF1760I Zynq UltraScale+ RFSoC at U1 (callout 35, Figure 2: Board Component Locations). For further information on Zynq UltraScale+ RFSoCs, see the UltraScale Architecture and Product Data Sheet: Overview (DS890).

#### **RFSoC Configuration**

The RFSoC is configured using one of the following options:

- Digilent embedded USB JTAG connector (callout 8, Figure 2: Board Component Locations)

- Xilinx Platform Cable USB II JTAG cable connector (callout 9, Figure 2: Board Component Locations)

The ZCU1285 board comes with an embedded USB-to-JTAG configuration module (Digilent, J69) which allows a host computer to access the board JTAG chain using a Standard A to Micro-B USB cable. Alternately, a JTAG connector (J2) is available to provide access to the JTAG chain using the Xilinx Platform Cable USB II or compatible configuration cable.

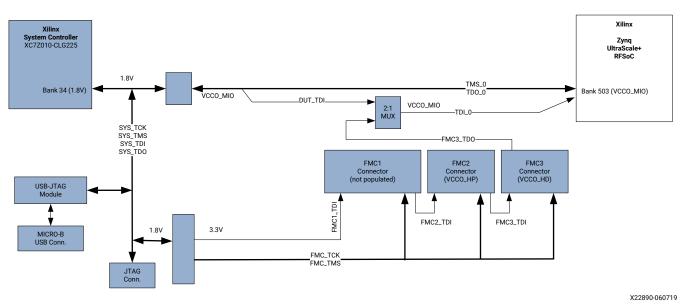

The JTAG chain of the board is illustrated in the following figure. By default, only the RFSoC is in the chain. Installing a shunt at J6 adds the FMC interfaces to the chain.

Figure 8: JTAG Chain

#### **PROGRAM** Pushbutton

Pressing the PROGRAM pushbutton SW7 (callout 44, Figure 2: Board Component Locations) asserts the active-Low program pin of the RFSoC.

## DONE LED

The DONE LED DS17 (callout 45, Figure 2: Board Component Locations) indicates the state of the DONE pin of the RFSoC. When the DONE pin is High, DS17 lights up, indicating the RFSoC is successfully configured.

#### **INIT LED**

The dual-color INIT LED DS3 (callout 45, Figure 2: Board Component Locations) indicates the RFSoC initialization status. During RFSoC initialization the INIT LED illuminates red. When RFSoC initialization has completed, the LED illuminates green.

## STATUS LED

The STATUS LED DS39 (callout 45, Figure 2: Board Component Locations) indicates a secure lockdown state. When the PS\_ERROR\_STATUS pin is High, DS39 lights up.

#### ERROR LED

The ERROR LED DS40 (callout 45, Figure 2: Board Component Locations) indicates an accidental loss of power, an error, or an exception in the RFSoC processor PMU. When the PS\_ERROR\_OUT pin is High, DS40 lights up.

## **PS\_POR\_B** Pushbutton

Pressing the PS\_POR\_B pushbutton SW14 (callout 15, Figure 2: Board Component Locations) asserts the active-Low PS\_POR\_B pin of the RFSoC processor.

## PS\_SRST\_B Pushbutton

Pressing the PS\_SRST\_B pushbutton SW15 (callout 15, Figure 2: Board Component Locations) asserts the active-Low PS\_SRST\_B pin of the RFSoC processor.

## **Boot Mode Selection Headers**

Four 3-pin headers are provided for mode pin selection to set the boot mode for the RFSoC processor (callout 12, Figure 2: Board Component Locations). Install a jumper across pins 1–2 (MIO\_BUS) to set a 1, and pins 2–3 (GND) to set a 0. See the following table for a complete list of boot mode settings.

| Boot Mode            | MODE 3 (J163) | MODE 2 (J164) | MODE 1 (J166) | MODE 0 (J165) |

|----------------------|---------------|---------------|---------------|---------------|

| JTAG                 | 0             | 0             | 0             | 0             |

| QSPI24               | 0             | 0             | 0             | 1             |

| QSPI32               | 0             | 0             | 1             | 0             |

| SD0 <sup>1</sup>     | 0             | 0             | 1             | 1             |

| NAND <sup>1</sup>    | 0             | 1             | 0             | 0             |

| SD1 <sup>1</sup>     | 0             | 1             | 0             | 1             |

| eMMC_18 <sup>1</sup> | 0             | 1             | 1             | 0             |

| USB 0 <sup>1</sup>   | 0             | 1             | 1             | 1             |

| PJTAG_0 <sup>1</sup> | 1             | 0             | 0             | 0             |

| PJTAG_1 <sup>1</sup> | 1             | 0             | 0             | 1             |

| SD1-LS               | 1             | 1             | 1             | 0             |

#### Table 6:Boot Mode Selection

Notes:

1. These boot modes are not directly supported by the ZCU1285 board.

#### **RFSoC Processor Reference Clock**

A free-running 33.3333333 MHz clock (U12) is the clock source for the RFSoC processor (PS\_REF\_CLK).

## 300 MHz LVDS Oscillator

A 300 MHz LVDS oscillator U145 (SiTime SIT9107AI-243N25E300.0000) connects to global clock (GC) pins on the RFSoC. The following table lists the RFSoC pin connections to the LVDS oscillator.

#### Table 7: LVDS Oscillator GC Connections

| RFSoC (U1) |                   |           | Schematic       | Device (U145) |     |                            |           |

|------------|-------------------|-----------|-----------------|---------------|-----|----------------------------|-----------|

| Pin        | Function          | Direction | I/O<br>Standard | Net Name      | Pin | Function                   | Direction |

| AP22       | SYSTEM<br>CLOCK_P | Input     | LVDS            | LVDS_OSC_P    | 4   | 300 MHz LVDS<br>oscillator | Output    |

| AR22       | SYSTEM<br>CLOCK_N | Input     | LVDS            | LVDS_OSC_N    | 5   | 300 MHz LVDS<br>oscillator | Output    |

#### **Differential SMA Pin Inputs**

Two pairs of SMA connectors (callout 49, Figure 2: Board Component Locations) provide access to global clock (GC) pins on the RFSoC. The GC pins are connected to the SMA connectors as shown in the following table.

Table 8: Differential SMA Clock Connections

|      | RI             | FSoC (U1) |            | Schematic Net | SMA Connector   |  |

|------|----------------|-----------|------------|---------------|-----------------|--|

| Pin  | Function       | Direction | IOSTANDARD | Name          | Sivia connector |  |

| AP26 | USER CLOCK_1_P | Input     | LVDS       | CLK_DIFF_1_P  | J84             |  |

| AR26 | USER CLOCK_1_N | Input     | LVDS       | CLK_DIFF_1_N  | J85             |  |

| AT23 | USER CLOCK_2_P | Input     | LVDS       | CLK_DIFF_2_P  | J83             |  |

| AT24 | USER CLOCK_2_N | Input     | LVDS       | CLK_DIFF_2_N  | J86             |  |

#### **User LEDs**

Eight active-High LEDs, DS22 through DS26, and DS46 through DS48 (callout 43, Figure 2: Board Component Locations), are connected to GPIO pins on the RFSoC. These LEDs can be used to indicate status or other functions. Their pinout is listed in the following table.

|      | R        | FSoC (U1) |            | Schematic Net | Reference  |  |

|------|----------|-----------|------------|---------------|------------|--|

| Pin  | Function | Direction | IOSTANDARD | Name          | Designator |  |

| AM25 | USER LED | Output    | LVCMOS18   | APP_LED1      | DS26       |  |

| AL24 | USER LED | Output    | LVCMOS18   | APP_LED2      | DS22       |  |

| AK22 | USER LED | Output    | LVCMOS18   | APP_LED3      | DS23       |  |

| AJ22 | USER LED | Output    | LVCMOS18   | APP_LED4      | DS24       |  |

| AN25 | USER LED | Output    | LVCMOS18   | APP_LED5      | DS25       |  |

| AN24 | USER LED | Output    | LVCMOS18   | APP_LED6      | DS46       |  |

| AM23 | USER LED | Output    | LVCMOS18   | APP_LED7      | DS47       |  |

| AL23 | USER LED | Output    | LVCMOS18   | APP_LED8      | DS48       |  |

#### Table 9: User LEDs

#### User DIP Switches and I/O Header

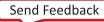

The DIP switch SW3 (callout 43, Figure 2: Board Component Locations) provides a set of eight active-High switches that connect to user I/O pins on the RFSoC as shown in the following table. Use these pins to set control pins or for any other purpose. The eight I/Os also map to test header J95 (callout 43, Figure 2: Board Component Locations), providing external access for these pins. The I/O pins can be connected to the onboard System Controller as additional GPIO between the two devices.

Note: Install J7 to connect the user DIP switches to the System Controller.

|      | RFSoC (U1)  |           |            | Schematic | DIP Switch              | J95 Test   | Device    |

|------|-------------|-----------|------------|-----------|-------------------------|------------|-----------|

| Pin  | Function    | Direction | IOStandard | Net Name  | Reference<br>Designator | Header Pin | (U38) Pin |

| AV25 | User Switch | Input     | LVCMOS18   | USER_SW1  |                         | 1          | F12       |

| AU25 | User Switch | Input     | LVCMOS18   | USER_SW2  |                         | 3          | E13       |

| AV23 | User Switch | Input     | LVCMOS18   | USER_SW3  |                         | 5          | E11       |

| AU23 | User Switch | Input     | LVCMOS18   | USER_SW4  | SW3                     | 7          | E12       |

| AW24 | User Switch | Input     | LVCMOS18   | USER_SW5  | 5003                    | 9          | F13       |

| AV24 | User Switch | Input     | LVCMOS18   | USER_SW6  |                         | 11         | F14       |

| BA22 | User Switch | Input     | LVCMOS18   | USER_SW7  |                         | 13         | G15       |

| AY22 | User Switch | Input     | LVCMOS18   | USER_SW8  |                         | 15         | F15       |

#### Table 10: User DIP Switches

The following figure shows the user I/O connector J95 (callout 43, Figure 2: Board Component Locations).

Figure 9: User I/O Connector J95

#### **User Pushbuttons**

SW16 and SW17 (callout 43, Figure 2: Board Component Locations) are active-High user pushbuttons that are connected to RFSoC I/O pins as shown in the following table. These pushbuttons can be used for any user-determined purpose.

Table 11: User Pushbuttons

|      | RI              | Schematic Net | Reference  |          |            |

|------|-----------------|---------------|------------|----------|------------|

| Pin  | Function        | Direction     | IOSTANDARD | Name     | Designator |

| AM22 | User pushbutton | Input         | LVCMOS18   | USER_PB1 | SW16       |

| AN26 | User pushbutton | Input         | LVCMOS18   | USER_PB2 | SW17       |

## System Monitor

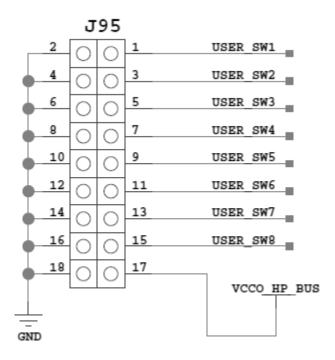

The System Monitor (SYSMON) monitors the physical environment using on-chip temperature and supply sensors, up to 17 external analog inputs, and an integrated analog-to-digital converter (ADC). There is a separate SYSMON for the PL and the PS. The PS SYSMON is powered using the on-chip reference voltage ( $V_{REF}$ ), and the PL SYSMON is powered using an external 1.25V regulator. See the following figure for connection details. More information about the system monitor is available in the UltraScale Architecture System Monitor User Guide (UG580).

#### Figure 10: PL and PS SYSMON Power Connections

## **Quad SPI Flash Memory**

A single quad SPI device (MT25QU01GBBB8ESF-0SIT 1.8V) is available for booting the RFSoC. To enable QSPI, boot shunts must be installed as indicated in the table in Boot Mode Selection Headers.

## **SD** Card

An SD card slot is provided (callout 52, Figure 2: Board Component Locations) for booting the RFSoC. The ZCU1285 board supports SD 3.0 and has an SD 3.0 compliant voltage level shifter. To enable SD boot, shunts must be installed for SD1-LS boot mode as indicated in the table in Boot Mode Selection Headers.

## **DDR3 Memory**

The board provides 2 GB of DDR3 memory utilizing a 64-bit bus and running at 2133 Mb/s. The memory system is composed of four x16 Samsung 4 Gb, 1.5V K4B4G1646D-BCNB devices. The memory is accessible through the processing system (PS) of the Zynq UltraScale+ RFSoC.

## **RF Data Converters and Sampling Clocks**

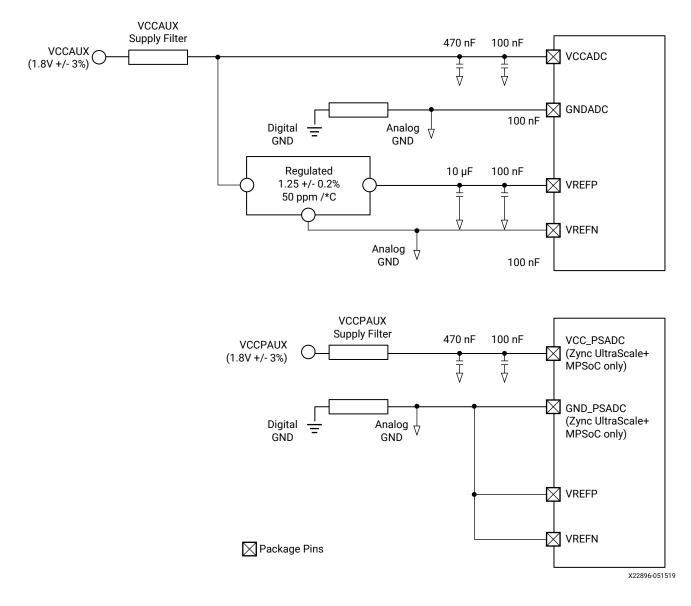

The ZCU1285 board provides access to all of the RFSoC RF-ADC and RF-DAC signal and clock pins. Each RF-ADC and RF-DAC is designed with –70 db isolation at 3 GHz. The four RF-ADC tiles (224, 225, 226, and 227) are brought out to two Bulls Eye connectors and a header for the VCM pins (callout 36 and 37, Figure 2: Board Component Locations). The four RF-DAC tiles (228, 229, 230, and 231) are brought out to two Bulls Eye connectors and an SMA pair for SYSREF (callout 36 and 48, Figure 2: Board Component Locations). The pinouts for the RF-ADC and RF-DAC Bulls Eye connectors, and the pinout for the VCM connector are shown in the following figures.

## *Figure 11:* A: Bulls Eye Connector Pad. B: RF-ADC Connector Pinout. C: RF-DAC Connector Pinout

#### **RF-ADC Pins**

The information for each RF-ADC pin is listed in the following table.

#### Table 12: **RF-ADC Pins**

| RFSoC (U1) | Net Name       | Tile | Connector | Trace Length (mils) |

|------------|----------------|------|-----------|---------------------|

| AU5        | ADC_VIN0_224_P | 224  | J124      | 3283.024            |

| AU4        | ADC_VIN0_224_N | 224  | J124      | 3280.721            |

| AU2        | ADC_VIN1_224_P | 224  | J124      | 3138.125            |

| AU1        | ADC_VIN1_224_N | 224  | J124      | 3135.787            |

| AR5        | ADC_VIN2_224_P | 224  | J124      | 3277.759            |

| AR4        | ADC_VIN2_224_N | 224  | J124      | 3275.53             |

| AR2        | ADC_VIN3_224_P | 224  | J124      | 3164.561            |

| AR1        | ADC_VIN3_224_N | 224  | J124      | 3162.691            |

| BA3        | ADC_CLK_224_P  | 224  | J124      | 3283.463            |

| BB3        | ADC_CLK_224_N  | 224  | J124      | 3279.967            |

| AJ11       | VCM01_224      | 224  | J20       | -                   |

| AJ10       | VCM23_224      | 224  | J20       | -                   |

| AF9        | ADC_REXT_224   | 224  | J127      | -                   |

| AN5        | ADC_VIN0_225_P | 225  | J124      | 3309.41             |

| AN4        | ADC_VIN0_225_N | 225  | J124      | 3307.012            |

| AN2        | ADC_VIN1_225_P | 225  | J124      | 3196.802            |

| AN1        | ADC_VIN1_225_N | 225  | J124      | 3194.401            |

| AL5        | ADC_VIN2_225_P | 225  | J124      | 3342.156            |

| AL4        | ADC_VIN2_225_N | 225  | J124      | 3339.779            |

| AL2        | ADC_VIN3_225_P | 225  | J124      | 3223.9              |

| AL1        | ADC_VIN3_225_N | 225  | J124      | 3221.624            |

| AW4        | ADC_CLK_225_P  | 225  | J124      | 3280.453            |

| AY4        | ADC_CLK_225_N  | 225  | J124      | 3279.826            |

| AH11       | VCM01_225      | 225  | J20       | -                   |

| AH10       | VCM23_225      | 225  | J20       | -                   |

| AJ5        | ADC_VIN0_226_P | 226  | J278      | 3360.63             |

| AJ4        | ADC_VIN0_226_N | 226  | J278      | 3358.274            |

| AJ2        | ADC_VIN1_226_P | 226  | J278      | 3242.988            |

| AJ1        | ADC_VIN1_226_N | 226  | J278      | 3240.685            |

| AG5        | ADC_VIN2_226_P | 226  | J278      | 3376.291            |

| AG4        | ADC_VIN2_226_N | 226  | J278      | 3374.059            |

| AG2        | ADC_VIN3_226_P | 226  | J278      | 3253.421            |

| AG1        | ADC_VIN3_226_N | 226  | J278      | 3253.248            |

| BA5        | ADC_CLK_226_P  | 226  | J278      | 3091.053            |

| BB5        | ADC_CLK_226_N  | 226  | J278      | 3088.424            |

| RFSoC (U1) | Net Name       | Tile | Connector | Trace Length (mils) |

|------------|----------------|------|-----------|---------------------|

| AJ8        | VCM01_226      | 226  | J20       | -                   |

| AJ7        | VCM23_226      | 226  | J20       | -                   |

| AE5        | ADC_VIN0_227_P | 227  | J278      | 3393.677            |

| AE4        | ADC_VIN0_227_N | 227  | J278      | 3391.355            |

| AE2        | ADC_VIN1_227_P | 227  | J278      | 3274.172            |

| AE1        | ADC_VIN1_227_N | 227  | J278      | 3272.253            |

| AC5        | ADC_VIN2_227_P | 227  | J278      | 3399.961            |

| AC4        | ADC_VIN2_227_N | 227  | J278      | 3397.632            |

| AC2        | ADC_VIN3_227_P | 227  | J278      | 3288.831            |

| AC1        | ADC_VIN3_227_N | 227  | J278      | 3286.82             |

| AW6        | ADC_CLK_227_P  | 227  | J278      | 3095.716            |

| AY6        | ADC_CLK_227_N  | 227  | J278      | 3099.089            |

| AH8        | VCM01_227      | 227  | J20       | -                   |

| AH7        | VCM23_227      | 227  | J20       | -                   |

#### Table 12: **RF-ADC Pins** (cont'd)

#### **RF-DAC Pins**

The information for each RF-DAC pin is listed in the following table.

| RFSoC (U1) | Net Name        | Tile | Connector | Trace Length (mils) |

|------------|-----------------|------|-----------|---------------------|

| Y5         | DAC_VOUT0_228_P | 228  | J129      | 3366.712            |

| Y4         | DAC_VOUT0_228_N | 228  | J129      | 3364.991            |

| Y2         | DAC_VOUT1_228_P | 228  | J129      | 3209.197            |

| Y1         | DAC_VOUT1_228_N | 228  | J129      | 3207.209            |

| V5         | DAC_VOUT2_228_P | 228  | J129      | 3349.961            |

| V4         | DAC_VOUT2_228_N | 228  | J129      | 3347.9              |

| V2         | DAC_VOUT3_228_P | 228  | J129      | 3192.969            |

| V1         | DAC_VOUT3_228_N | 228  | J129      | 3190.879            |

| B3         | DAC_CLK_228_P   | 228  | J129      | 3340.507            |

| A3         | DAC_CLK_228_N   | 228  | J129      | 3343.285            |

| D2         | SYSREF_228_P    | 228  | J242      | -                   |

| D1         | SYSREF_228_N    | 228  | J243      | -                   |

| U9         | DAC_REXT_228    | 228  | J128      | -                   |

| T5         | DAC_VOUT0_229_P | 229  | J129      | 3319.868            |

| T4         | DAC_VOUT0_229_N | 229  | J129      | 3317.681            |

| T2         | DAC_VOUT1_229_P | 229  | J129      | 3178.213            |

| T1         | DAC_VOUT1_229_N | 229  | J129      | 3176.101            |

#### Table 13: **RF-DAC Pins**

| RFSoC (U1) | Net Name        | Tile | Connector | Trace Length (mils) |

|------------|-----------------|------|-----------|---------------------|

| P5         | DAC_VOUT2_229_P | 229  | J129      | 3320.982            |

| P4         | DAC_VOUT2_229_N | 229  | J129      | 3319.001            |

| P2         | DAC_VOUT3_229_P | 229  | J129      | 3163.2              |

| P1         | DAC_VOUT3_229_N | 229  | J129      | 3165.4              |

| D4         | DAC_CLK_229_P   | 229  | J129      | 3556.617            |

| C4         | DAC_CLK_229_N   | 229  | J129      | 3560.447            |

| M5         | DAC_VOUT0_230_P | 230  | J279      | 3267.684            |

| M4         | DAC_VOUT0_230_N | 230  | J279      | 3265.525            |

| M2         | DAC_VOUT1_230_P | 230  | J279      | 3152.804            |

| M1         | DAC_VOUT1_230_N | 230  | J279      | 3150.782            |

| K5         | DAC_VOUT2_230_P | 230  | J279      | 3287.039            |

| K4         | DAC_VOUT2_230_N | 230  | J279      | 3284.711            |

| K2         | DAC_VOUT3_230_P | 230  | J279      | 3141.679            |

| K1         | DAC_VOUT3_230_N | 230  | J279      | 3139.098            |

| B5         | DAC_CLK_230_P   | 230  | J279      | 3615.019            |

| A5         | DAC_CLK_230_N   | 230  | J279      | 3619.695            |

| H5         | DAC_VOUT0_231_P | 231  | J279      | 3265.511            |

| H4         | DAC_VOUT0_231_N | 231  | J279      | 3263.254            |

| H2         | DAC_VOUT1_231_P | 231  | J279      | 3111.166            |

| H1         | DAC_VOUT1_231_N | 231  | J279      | 3108.992            |

| F5         | DAC_VOUT2_231_P | 231  | J279      | 3243.78             |

| F4         | DAC_VOUT2_231_N | 231  | J279      | 3241.56             |

| F2         | DAC_VOUT3_231_P | 231  | J279      | 3071.556            |

| F1         | DAC_VOUT3_231_N | 231  | J279      | 3069.35             |

| D6         | DAC_CLK_231_P   | 231  | J279      | 3834.883            |

| C6         | DAC_CLK_231_N   | 231  | J279      | 3835.078            |

#### Table 13: **RF-DAC Pins** (cont'd)

## **Serial Transceivers and Reference Clocks**

The ZCU1285 board provides access to all GTY and PS-GTR transceiver and reference clock pins of the RFSoC (callout 33 and 34, Figure 2: Board Component Locations). The serial transceivers are grouped into five sets of four TX-RX lanes, referred to as Quads. There are four GTY Quads (Q128 –Q131), and one PS-GTR Quad (bank 505).

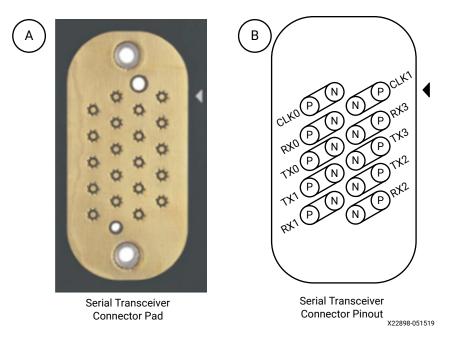

All GTY and PS-GTR Quads and their associated reference clocks (CLKO and CLK1) are brought out to a connector pad, which interfaces with Samtec Bulls Eye connectors used with the Samtec RSP-200723-02-BEYE cable assembly. Contact Samtec, Inc. for information about this or other cable assemblies. In the following figure, A shows the connector pad and B shows the connector pinout.

#### *Figure 13:* Serial Transceiver Connector Pad and Pinout

PS-GTR bank 505 has two additional reference clocks (CLK2 and CLK3) which are brought out to two pairs of SMA connectors (callout 18, Figure 2: Board Component Locations).

#### **GTY Transceiver Pins**

The information for each GTY transceiver pin is shown in the following table.

| RFSoC (U1) | Net Name  | Quad | Connector | Trace Length<br>(mils) |

|------------|-----------|------|-----------|------------------------|

| AC42       | 128_RX0_N | 128  | J117      | 2707.458               |

| AC41       | 128_RX0_P | 128  | J117      | 2707.296               |

| AB40       | 128_RX1_N | 128  | J117      | 3507.681               |

| AB39       | 128_RX1_P | 128  | J117      | 3508.445               |

| AA42       | 128_RX2_N | 128  | J117      | 2940.702               |

| AA41       | 128_RX2_P | 128  | J117      | 2938.24                |

| Y40        | 128_RX3_N | 128  | J117      | 2644.503               |

| Y39        | 128_RX3_P | 128  | J117      | 2647.811               |

#### Table 14: GTY Transceiver Pins

| Table 14: | GTY Transceiver F | Pins (cont'd) |

|-----------|-------------------|---------------|

|-----------|-------------------|---------------|

| RFSoC (U1) | Net Name  | Quad | Connector | Trace Length<br>(mils) |

|------------|-----------|------|-----------|------------------------|

| V39        | 128_TX0_N | 128  | J117      | 3148.266               |

| V38        | 128_TX0_P | 128  | J117      | 3147.413               |

| U37        | 128_TX1_N | 128  | J117      | 3228.503               |

| U36        | 128_TX1_P | 128  | J117      | 3229.157               |

| T39        | 128_TX2_N | 128  | J117      | 3053.346               |

| T38        | 128_TX2_P | 128  | J117      | 3057.162               |

| R37        | 128_TX3_N | 128  | J117      | 2914.568               |

| R36        | 128_TX3_P | 128  | J117      | 2917.948               |

| W42        | 129_RX0_N | 129  | J118      | 2336.327               |

| W41        | 129_RX0_P | 129  | J118      | 2336.177               |

| U42        | 129_RX1_N | 129  | J118      | 2915.189               |

| U41        | 129_RX1_P | 129  | J118      | 2915.033               |

| R42        | 129_RX2_N | 129  | J118      | 2660.231               |

| R41        | 129_RX2_P | 129  | J118      | 2663.549               |

| N42        | 129_RX3_N | 129  | J118      | 2191.652               |

| N41        | 129_RX3_P | 129  | J118      | 2194.96                |

| P39        | 129_TX0_N | 129  | J118      | 2580.324               |

| P38        | 129_TX0_P | 129  | J118      | 2579.92                |

| N37        | 129_TX1_N | 129  | J118      | 2828.966               |

| N36        | 129_TX1_P | 129  | J118      | 2829.422               |

| M39        | 129_TX2_N | 129  | J118      | 2684.658               |

| M38        | 129_TX2_P | 129  | J118      | 2688.416               |

| L37        | 129_TX3_N | 129  | J118      | 2565.464               |

| L36        | 129_TX3_P | 129  | J118      | 2564.925               |

| L42        | 130_RX0_N | 130  | J280      | 2169.162               |

| L41        | 130_RX0_P | 130  | J280      | 2168.011               |

| J42        | 130_RX1_N | 130  | J280      | 2753.85                |

| J41        | 130_RX1_P | 130  | J280      | 2753.847               |

| G42        | 130_RX2_N | 130  | J280      | 2708.119               |

| G41        | 130_RX2_P | 130  | J280      | 2710.988               |

| F40        | 130_RX3_N | 130  | J280      | 2298.952               |

| F39        | 130_RX3_P | 130  | J280      | 2302.779               |

| K39        | 130_TX0_N | 130  | J280      | 2503.962               |

| K38        | 130_TX0_P | 130  | J280      | 2502.727               |

| J37        | 130_TX1_N | 130  | J280      | 2738.854               |

| J36        | 130_TX1_P | 130  | J280      | 2738.821               |

| H39        | 130_TX2_N | 130  | J280      | 2660.143               |

| H38        | 130_TX2_P | 130  | J280      | 2659.72                |

| RFSoC (U1) | Net Name  | Quad | Connector | Trace Length<br>(mils) |

|------------|-----------|------|-----------|------------------------|

| G37        | 130_TX3_N | 130  | J280      | 2877.072               |

| G36        | 130_TX3_P | 130  | J280      | 2877.059               |

| E42        | 131_RX0_N | 131  | J281      | 2585.706               |

| E41        | 131_RX0_P | 131  | J281      | 2585.352               |

| D40        | 131_RX1_N | 131  | J281      | 3037.05                |

| D39        | 131_RX1_P | 131  | J281      | 3034.196               |

| C42        | 131_RX2_N | 131  | J281      | 3275.72                |

| C41        | 131_RX2_P | 131  | J281      | 3274.21                |

| B40        | 131_RX3_N | 131  | J281      | 2676.92                |

| B39        | 131_RX3_P | 131  | J281      | 2675.781               |

| F35        | 131_TX0_N | 131  | J281      | 2940.112               |

| F34        | 131_TX0_P | 131  | J281      | 2939.226               |

| E37        | 131_TX1_N | 131  | J281      | 3346.063               |

| E36        | 131_TX1_P | 131  | J281      | 3345.916               |

| C37        | 131_TX2_N | 131  | J281      | 3431.684               |

| C36        | 131_TX2_P | 131  | J281      | 3432.171               |

| A37        | 131_TX3_N | 131  | J281      | 3180.526               |

| A36        | 131_TX3_P | 131  | J281      | 3181.286               |

Table 14: **GTY Transceiver Pins** (cont'd)

#### **GTY Transceiver Reference Clock Inputs**

Information for each GTY transceiver clock input is shown in the following table.

Table 15: GTY Transceiver Reference Clock Inputs

| RFSoC (U1) | Net Name      | Quad | Connector |

|------------|---------------|------|-----------|

| AA36       | 128_REFCLK0_N | 128  | J117      |

| AA37       | 128_REFCLK0_P | 128  | J117      |

| Y34        | 128_REFCLK1_N | 128  | J117      |

| Y35        | 128_REFCLK1_P | 128  | J117      |

| V34        | 129_REFCLK0_N | 129  | J118      |

| V35        | 129_REFCLK0_P | 129  | J118      |

| T34        | 129_REFCLK1_N | 129  | J118      |

| T35        | 129_REFCLK1_P | 129  | J118      |

| P34        | 130_REFCLK0_N | 130  | J280      |

| P35        | 130_REFCLK0_P | 130  | J280      |

| M34        | 130_REFCLK1_N | 130  | J280      |

| M35        | 130_REFCLK1_P | 130  | J280      |

| RFSoC (U1) | Net Name      | Quad | Connector |

|------------|---------------|------|-----------|

| K34        | 131_REFCLK0_N | 131  | J281      |

| K35        | 131_REFCLK0_P | 131  | J281      |

| H34        | 131_REFCLK1_N | 131  | J281      |

| H35        | 131_REFCLK1_P | 131  | J281      |

| Table 15: | GTY Transceiver Reference Clock Inputs (cont'd) |

|-----------|-------------------------------------------------|

|-----------|-------------------------------------------------|

#### **PS-GTR Transceiver Pins**

Information for each PS-GTR transceiver pin is shown in the following table.

| RFSoC (U1) | Net Name | Bank | Connector | Trace Length<br>(mils) |

|------------|----------|------|-----------|------------------------|

| AJ42       | PS_RX0_N | 505  | J39       | 3920.298               |

| AJ41       | PS_RX0_P | 505  | J39       | 3918.182               |

| AH40       | PS_RX1_N | 505  | J39       | 4537.184               |

| AH39       | PS_RX1_P | 505  | J39       | 4537.361               |

| AG42       | PS_RX2_N | 505  | J39       | 4299.2                 |

| AG41       | PS_RX2_P | 505  | J39       | 4302.524               |

| AE42       | PS_RX3_N | 505  | J39       | 3174.371               |

| AE41       | PS_RX3_P | 505  | J39       | 3173.868               |

| AH36       | PS_TX0_N | 505  | J39       | 3400.509               |

| AH35       | PS_TX0_P | 505  | J39       | 3399.45                |

| AG38       | PS_TX1_N | 505  | J39       | 3468.187               |

| AG37       | PS_TX1_P | 505  | J39       | 3467.251               |

| AF40       | PS_TX2_N | 505  | J39       | 3721.249               |

| AF39       | PS_TX2_P | 505  | J39       | 3724.655               |

| AE38       | PS_TX3_N | 505  | J39       | 3301.206               |

| AE37       | PS_TX3_P | 505  | J39       | 3304.523               |

#### Table 16: PS-GTR Transceiver Pins

#### **PS-GTR Transceiver Reference Clock Inputs**

Information for each PS-GTR transceiver clock input is shown in the following table.

| Table 17: | <b>PS-GTR Transceiver Reference Clock Inputs</b> |

|-----------|--------------------------------------------------|

|-----------|--------------------------------------------------|

| RFSoC (U1) | Net Name     | Bank | Connector |

|------------|--------------|------|-----------|

| AF34       | PS_REFCLK0_P | 505  | J39       |

| AF35       | PS_REFCLK0_N | 505  | J39       |

| AD34       | PS_REFCLK1_P | 505  | J39       |

| RFSoC (U1) | Net Name     | Bank | Connector |

|------------|--------------|------|-----------|

| AD35       | PS_REFCLK1_N | 505  | J39       |

| AC36       | PS_REFCLK2_P | 505  | J194      |

| AC37       | PS_REFCLK2_N | 505  | J156      |

| AB34       | PS_REFCLK3_P | 505  | J158      |

| AB35       | PS_REFCLK3_N | 505  | J159      |

| Table 17: | PS-GTR Transceiver Reference Clock Inputs (cont'd) | ) |

|-----------|----------------------------------------------------|---|

|           |                                                    | / |

# SuperClock-2 Module

The SuperClock-2 Module (callout 6, Figure 2: Board Component Locations) connects to the clock module interface connector (J36) and provides a programmable, low-noise and low-jitter clock source for use with the GTY and PS-GTR transceivers. The clock module maps to the RFSoC by way of two I2C signals, two LVDS pairs, and one global clock pair. The following table lists the RFSoC mapping for the SuperClock-2 Module interface. To program the SuperClock-2 Module using the System Controller, see Appendix E: System Controller. To connect to the SuperClock-2 Module using the I2C bus, see I2C Bus Management.

|      | RFSoC (U1)     |           |                | Schematic Net                 |     | J36 Pin        |           |

|------|----------------|-----------|----------------|-------------------------------|-----|----------------|-----------|

| Pin  | Function       | Direction | IOSTANDAR<br>D | Name                          | Pin | Function       | Direction |

| L28  | Clock recovery | Input     | LVDS           | CM_LVDS1_P                    | 1   | Clock recovery | Output    |

| L29  | Clock recovery | Input     | LVDS           | CM_LVDS1_N                    | 3   | Clock recovery | Output    |

| H10  | Clock recovery | Input     | LVDS           | CM_LVDS2_P                    | 9   | Clock recovery | Output    |

| H9   | Clock recovery | Input     | LVDS           | CM_LVDS2_N                    | 11  | Clock recovery | Output    |

| AP24 | Global clock   | Input     | LVDS           | CM_GCLK_P                     | 25  | Global clock   | Output    |

| AR24 | Global clock   | Input     | LVDS           | CM_GCLK_N                     | 27  | Global clock   | Output    |

| AM26 | Control I/O    | Bidir     | LVCMOS         | CM_I2C_SCL/<br>DUT_PMBUS_CLK  | 62  | I2C            | Bidir     |

| AP23 | Control I/O    | Bidir     | LVCMOS         | CM_I2C_SDA/<br>DUT_PMBUS_DATA | 64  | I2C            | Bidir     |

#### Table 18: SuperClock-2 Interface Connections

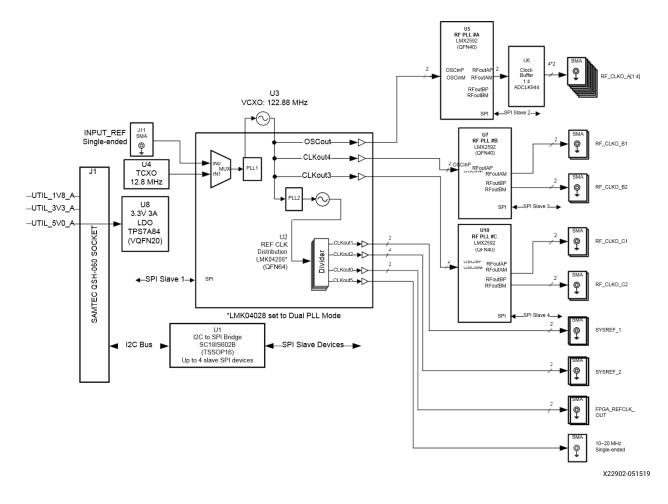

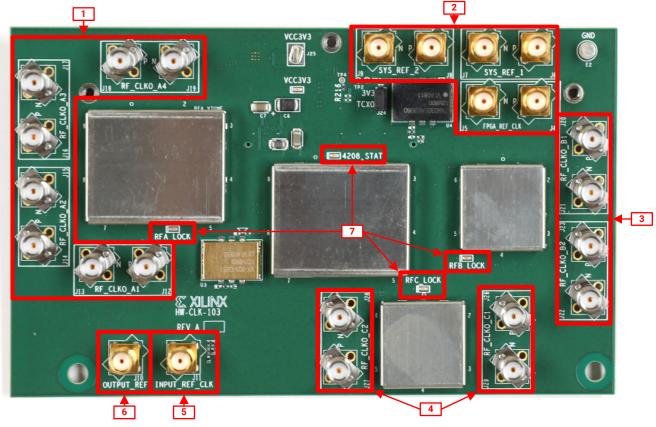

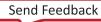

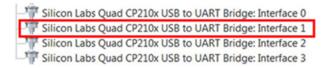

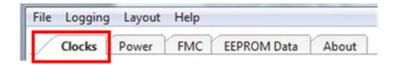

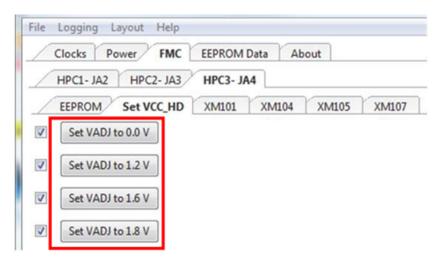

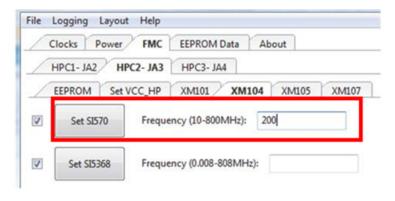

## SuperClock-RF2 Module