# 10G Ethernet PCS/PMA v6.0

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG068 February 4, 2021

# **Table of Contents**

**Chapter 1: Overview**

## **IP Facts**

| Standards       11         Performance       11         Resource Utilization       13         Port Descriptions       13         Register Space       33         Chapter 3: Designing with the Core         General Design Guidelines       77         Clocking       78         Resets       83         Shared Logic       83         Interfacing to the Core       86         DRP Interface       97         Receiver Termination       99         Special Design Considerations       99         Chapter 4: Design Flow Steps         Customizing and Generating the Core       104         Constraining the Core       109         Simulation       111         Synthesis and Implementation       112                                                                                                                                                   | •                                     |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------|

| Applications       8         Unsupported Features       9         Licensing and Ordering       9         Chapter 2: Product Specification         Standards       11         Performance       11         Resource Utilization       13         Port Descriptions       13         Register Space       33         Chapter 3: Designing with the Core         General Design Guidelines       77         Clocking       78         Resets       83         Shared Logic       83         Interfacing to the Core       86         DRP Interface       97         Receiver Termination       99         Special Design Considerations       99         Chapter 4: Design Flow Steps         Customizing and Generating the Core       104         Constraining the Core       109         Simulation       111         Synthesis and Implementation       112 | Navigating Content by Design Process  | <br>5    |

| Unsupported Features       9         Licensing and Ordering       9         Chapter 2: Product Specification       11         Standards       11         Performance       11         Resource Utilization       13         Port Descriptions       13         Register Space       33         Chapter 3: Designing with the Core       77         General Design Guidelines       77         Clocking       78         Resets       83         Shared Logic       83         Interfacing to the Core       86         DRP Interface       97         Receiver Termination       99         Special Design Considerations       99         Chapter 4: Design Flow Steps         Customizing and Generating the Core       104         Constraining the Core       109         Simulation       111         Synthesis and Implementation       112            | Core Overview                         | <br>5    |

| Licensing and Ordering       9         Chapter 2: Product Specification       11         Standards       11         Performance       11         Resource Utilization       13         Port Descriptions       13         Register Space       33         Chapter 3: Designing with the Core       5         General Design Guidelines       77         Clocking       78         Resets       83         Shared Logic       83         Interfacing to the Core       86         DRP Interface       97         Receiver Termination       99         Special Design Considerations       99         Chapter 4: Design Flow Steps         Customizing and Generating the Core       104         Constraining the Core       109         Simulation       111         Synthesis and Implementation       112                                                  | Applications                          | <br>8    |

| Chapter 2: Product Specification       11         Standards       11         Performance       11         Resource Utilization       13         Port Descriptions       13         Register Space       33         Chapter 3: Designing with the Core       5         General Design Guidelines       77         Clocking.       78         Resets       83         Shared Logic       83         Interfacing to the Core.       86         DRP Interface       97         Receiver Termination.       99         Special Design Considerations       99         Chapter 4: Design Flow Steps         Customizing and Generating the Core       104         Constraining the Core       109         Simulation       111         Synthesis and Implementation       112                                                                                      | Unsupported Features                  | <br>9    |

| Standards       11         Performance       11         Resource Utilization       13         Port Descriptions       13         Register Space       33         Chapter 3: Designing with the Core         General Design Guidelines       77         Clocking       78         Resets       83         Shared Logic       83         Interfacing to the Core       86         DRP Interface       97         Receiver Termination       99         Special Design Considerations       99         Chapter 4: Design Flow Steps         Customizing and Generating the Core       104         Constraining the Core       109         Simulation       111         Synthesis and Implementation       112                                                                                                                                                   | Licensing and Ordering                | <br>9    |

| Performance       11         Resource Utilization       13         Port Descriptions       13         Register Space       33         Chapter 3: Designing with the Core         General Design Guidelines       77         Clocking       78         Resets       83         Shared Logic       83         Interfacing to the Core       86         DRP Interface       97         Receiver Termination       99         Special Design Considerations       99         Chapter 4: Design Flow Steps         Customizing and Generating the Core       104         Constraining the Core       109         Simulation       111         Synthesis and Implementation       112                                                                                                                                                                              | Chapter 2: Product Specification      |          |

| Resource Utilization       13         Port Descriptions       13         Register Space       33         Chapter 3: Designing with the Core       77         General Design Guidelines       77         Clocking       78         Resets       83         Shared Logic       83         Interfacing to the Core       86         DRP Interface       97         Receiver Termination       99         Special Design Considerations       99         Chapter 4: Design Flow Steps         Customizing and Generating the Core       104         Constraining the Core       109         Simulation       111         Synthesis and Implementation       112                                                                                                                                                                                                  | Standards                             | <br>. 11 |

| Port Descriptions       13         Register Space       33         Chapter 3: Designing with the Core       77         General Design Guidelines       77         Clocking       78         Resets       83         Shared Logic       83         Interfacing to the Core       86         DRP Interface       97         Receiver Termination       99         Special Design Considerations       99         Chapter 4: Design Flow Steps         Customizing and Generating the Core       104         Constraining the Core       109         Simulation       111         Synthesis and Implementation       112                                                                                                                                                                                                                                        | Performance                           | <br>. 11 |

| Register Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Resource Utilization                  | <br>. 13 |

| Chapter 3: Designing with the Core  General Design Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Port Descriptions                     | <br>. 13 |

| General Design Guidelines 77 Clocking. 78 Resets 83 Shared Logic 83 Interfacing to the Core 86 DRP Interface 97 Receiver Termination 99 Special Design Considerations 99 Chapter 4: Design Flow Steps Customizing and Generating the Core 104 Constraining the Core 109 Simulation 111 Synthesis and Implementation 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Register Space                        | <br>. 33 |

| Clocking. 78 Resets 83 Shared Logic 83 Interfacing to the Core 86 DRP Interface 97 Receiver Termination 99 Special Design Considerations 99 Chapter 4: Design Flow Steps Customizing and Generating the Core 104 Constraining the Core 109 Simulation 111 Synthesis and Implementation 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chapter 3: Designing with the Core    |          |

| Resets 83 Shared Logic 83 Interfacing to the Core 86 DRP Interface 97 Receiver Termination 99 Special Design Considerations 99 Chapter 4: Design Flow Steps Customizing and Generating the Core 104 Constraining the Core 109 Simulation 111 Synthesis and Implementation 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | General Design Guidelines             | <br>. 77 |

| Shared Logic 83 Interfacing to the Core 86 DRP Interface 97 Receiver Termination 99 Special Design Considerations 99 Chapter 4: Design Flow Steps Customizing and Generating the Core 104 Constraining the Core 109 Simulation 111 Synthesis and Implementation 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Clocking                              | <br>. 78 |

| Interfacing to the Core. 86 DRP Interface 97 Receiver Termination. 99 Special Design Considerations 99 Chapter 4: Design Flow Steps Customizing and Generating the Core 104 Constraining the Core 109 Simulation 111 Synthesis and Implementation 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Resets                                | <br>. 83 |

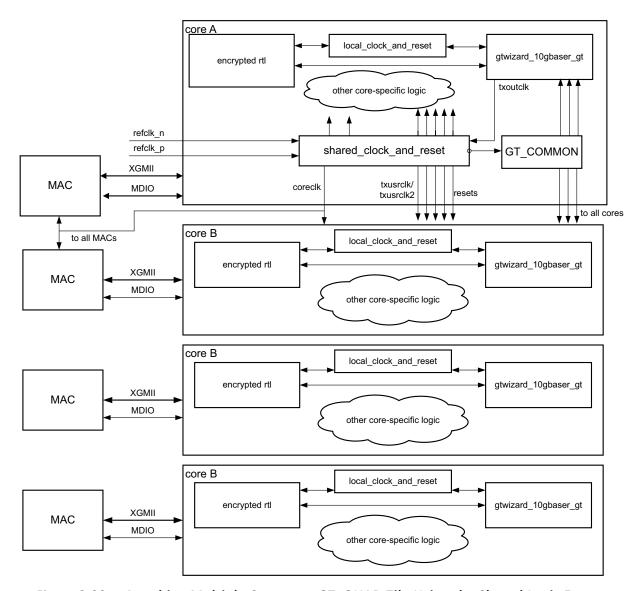

| DRP Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Shared Logic                          | <br>. 83 |

| Receiver Termination. 99 Special Design Considerations 99 Chapter 4: Design Flow Steps Customizing and Generating the Core 104 Constraining the Core 109 Simulation 111 Synthesis and Implementation 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Interfacing to the Core               | <br>. 86 |

| Special Design Considerations 99  Chapter 4: Design Flow Steps  Customizing and Generating the Core 104  Constraining the Core 109  Simulation 111  Synthesis and Implementation 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DRP Interface                         | <br>. 97 |

| Chapter 4: Design Flow Steps  Customizing and Generating the Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Receiver Termination                  | <br>. 99 |

| Customizing and Generating the Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Special Design Considerations         | <br>. 99 |

| Constraining the Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Chapter 4: Design Flow Steps          |          |

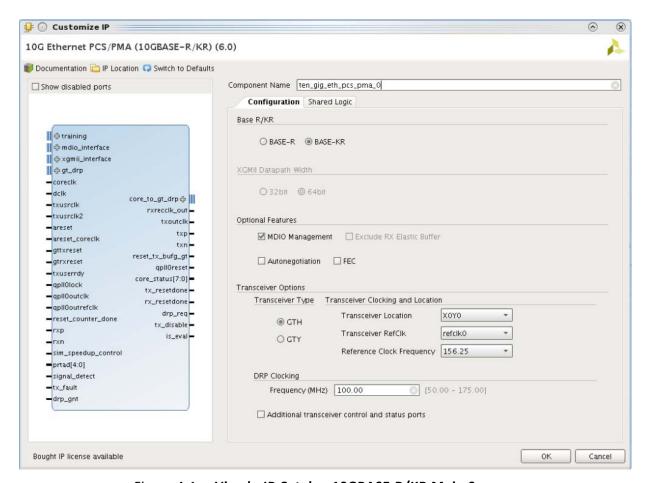

| Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Customizing and Generating the Core   | <br>104  |

| Synthesis and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Constraining the Core                 | <br>109  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Simulation                            | <br>111  |

| Chapter 5: Detailed Example Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Synthesis and Implementation          | <br>112  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Chapter 5: Detailed Example Design    |          |

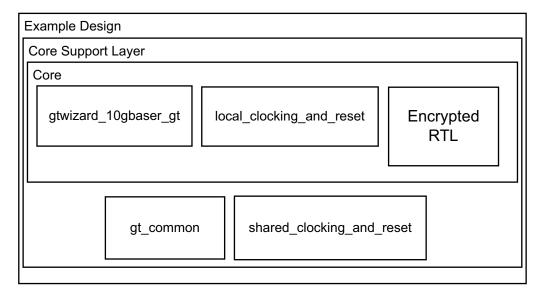

| Example Design and Core Support Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Example Design and Core Support Layer | <br>113  |

| Shared Logic and the Core Support Layer                     | 114 |

|-------------------------------------------------------------|-----|

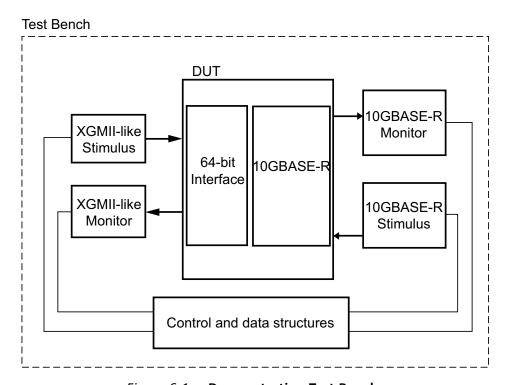

| Chapter 6: Test Bench                                       |     |

| Appendix A: Verification, UNH Testing, and Interoperability |     |

| Simulation                                                  | 116 |

| Hardware Verification                                       | 116 |

| Testing                                                     | 117 |

| Appendix B: Upgrading                                       |     |

| Migrating                                                   | 118 |

| Upgrading in the Vivado Design Suite                        | 118 |

| Appendix C: Debugging                                       |     |

| Finding Help on Xilinx.com                                  | 122 |

| Debug Tools                                                 | 123 |

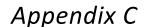

| Simulation Debug                                            | 125 |

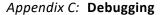

| Hardware Debug                                              | 126 |

| Appendix D: PRBS Testing                                    |     |

| Appendix E: Additional Resources and Legal Notices          |     |

| Xilinx Resources                                            | 135 |

| Documentation Navigator and Design Hubs                     | 135 |

| References                                                  | 135 |

| Revision History                                            | 136 |

| Please Read: Important Legal Notices                        | 129 |

# Introduction

The LogiCORE™ IP 10G Ethernet Physical Coding Sublayer/Physical Medium Attachment (PCS/PMA) core forms a seamless interface between the Xilinx 10G Ethernet Media Access Controller (MAC) core and a 10 Gb/s-capable PHY, enabling the design of high-speed Ethernet systems and subsystems.

# **Features**

- Designed to 10 Gigabit Ethernet specification IEEE Standard 802.3-2012 clause 49, 72, 73, 74

- Optional Management Data Interface (MDIO) to manage PCS/PMA registers

- Supports 10GBASE-SR, -LR and -ER optical links in Zynq-7000, UltraScale<sup>™</sup>, Virtex-7, and Kintex-7 devices (LAN mode only)

- Supports 10GBASE-KR backplane links in UltraScale, and Virtex-7 devices, including Auto-Negotiation (AN), Training and Forward Error Correction (FEC)

- 10 Gigabit Ethernet Media Independent Interface (XGMII) connects seamlessly to the Xilinx 10 Gigabit Ethernet MAC

- A 64-bit or 32-bit data width option is available for the 10GBASE-R standard. The 10GBASE-KR standard is always provided with a 64-bit data width.

|                                                  | LogiCORE IP Facts Table                                                                              |  |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|

|                                                  | Core Specifics                                                                                       |  |  |

| Supported<br>Device<br>Family <sup>(1)</sup> (2) | <b>10GBASE-R</b> : UltraScale <sup>™</sup><br>Zynq®-7000 SoC,<br>Virtex®-7, Kintex®-7 <sup>(3)</sup> |  |  |

|                                                  | <b>10GBASE-KR</b> : UltraScale <sup>™</sup> ,<br>Virtex-7 <sup>(4)</sup>                             |  |  |

| Supported User<br>Interfaces                     | MDIO, XGMII                                                                                          |  |  |

| Resources                                        | Performance and Resource Utilization web page                                                        |  |  |

|                                                  | Provided with Core                                                                                   |  |  |

| Design Files                                     | Encrypted RTL                                                                                        |  |  |

| Example Design                                   | Verilog and VHDL                                                                                     |  |  |

| Test Bench                                       | Verilog and VHDL                                                                                     |  |  |

| Constraints File                                 | Xilinx Design Constraint (XDC)                                                                       |  |  |

| Simulation<br>Model                              | Verilog or VHDL source HDL Model                                                                     |  |  |

| Supported<br>S/W Driver                          | See the 10 Gigabit Ethernet Subsystem Product<br>Guide (PG157) [Ref 3]                               |  |  |

|                                                  | Tested Design Flows <sup>(5)</sup>                                                                   |  |  |

| Design Entry                                     | Vivado® Design Suite                                                                                 |  |  |

| Simulation                                       | For supported simulators, see the Xilinx Design Tools: Release Notes Guide.                          |  |  |

| Synthesis                                        | Vivado Synthesis                                                                                     |  |  |

| Support                                          |                                                                                                      |  |  |

| Release Notes<br>and Known<br>Issues             | Master Answer Record: 54669                                                                          |  |  |

| All Vivado IP<br>Change Logs                     | Master Vivado IP Change Log: 72775                                                                   |  |  |

| Xilinx Support web page                          |                                                                                                      |  |  |

#### Notes:

- Some packages and speedgrades might not support the 10 Gb/s line rate. For a complete list of supported devices, see the Vivado IP catalog. For new designs in the UltraScale/ UltraScale+™ portfolio, see the 10G/25G Ethernet Subsystem webpage.

- 2. For 10GBASE-KR channel analysis, contact your local Xilinx representative.

- 3. -2, -2L or -3.

- 4. GTHE2 transceivers only.

- 5. For the supported versions of third-party tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

# **Navigating Content by Design Process**

Xilinx® documentation is organized around a set of standard design processes to help you find relevant content for your current development task. This document covers the following design processes:

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, subsystem functional simulation, and evaluating the Vivado timing, resource and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Port Descriptions

- Register Space

- Clocking

- Resets

- Interfacing to the Core

- Special Design Considerations

- Customizing and Generating the Core

- Detailed Example Design

# **Core Overview**

10GBASE-R/KR is a 10 Gb/s serial interface. It is intended to provide the Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA) functionality between the 10 Gigabit Media Independent Interface (XGMII) interface on a Ten Gigabit Ethernet Media Access Controller (MAC) and a Ten Gigabit Ethernet network physical-side interface (PHY).

The 10GBASE-KR core is distinguished from the 10GBASE-R core by the addition of a Link Training block as well as optional Auto-Negotiation (AN) and Forward Error Correction (FEC) features, to support a 10 Gb/s data stream across a backplane.

#### **10GBASE-R**

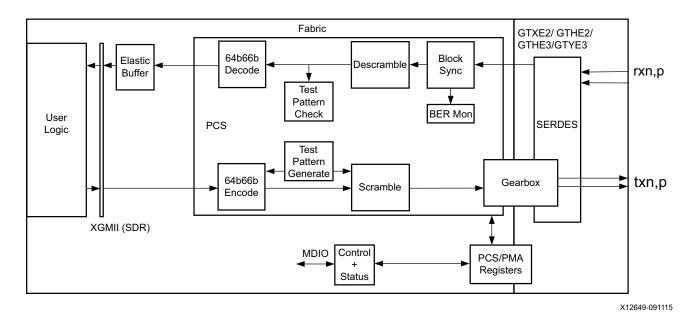

For Zynq®-7000, UltraScale™, Virtex®-7, and Kintex®-7 devices, all of the PCS and management blocks illustrated are implemented in logic, except for part of the Gearbox and SERDES. Figure 1-1 shows the architecture.

Figure 1-1: Implementation of the 10GBASE-R Core

The major functional blocks include the following:

- XGMII interface, designed for simple attachment of 10 Gigabit Ethernet MAC

- Transmit path, including scrambler, 64b/66b encoder and Gearbox

- Receive path, including block synchronization, descrambler, decoder and BER (Bit Error Rate) monitor

- Elastic buffer in the receive datapath.

The elastic buffer is 32 words deep (1 word = 64bits data + 8 control). (For 32-bit 10GBASE-R cores, the elastic buffer is twice the depth and half the width, but has the same properties.) If the buffer empties, local fault codes are inserted instead of data. This allows you to collect up to 64 clock correction (CC) sequences before the buffer overflows (and words are dropped). The buffer normally fills up to one half and then deletes CC sequences when over half full, and inserts CC sequences when under one half full. So from a half-full state, you can (conservatively) accept an extra 360 KB of data (that is, receiving at +200 ppm) without dropping any. From a half-full state you can cope with another 360 KB of data without inserting local faults (for -200 ppm).

- Test pattern generation and checking

- Serial interface to optics

Management registers (PCS/PMA) with optional MDIO interface

#### **10GBASE-KR**

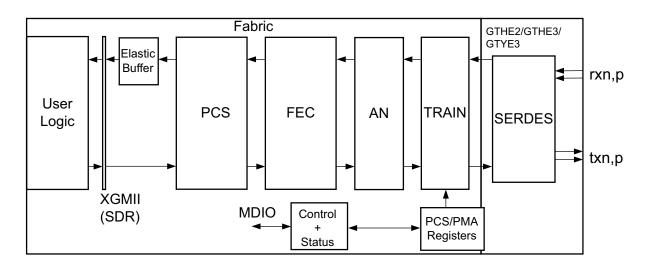

Figure 1-2 illustrates a block diagram of the 10GBASE-KR core implementation. The major functional blocks include the following:

- XGMII interface, designed for simple attachment of 10 Gigabit Ethernet MAC

- Transmit path, including scrambler, 64b/66b encoder, FEC, AN and Training

- Receive path, including block synchronization, descrambler, decoder and BER (Bit Error Rate) monitor, FEC, AN and Training

- Elastic buffer in the receive datapath.

The elastic buffer is 32 words deep (1 word = 64bits data + 8 control). If the buffer empties, local fault codes are inserted instead of data. This allows you to collect up to 64 clock correction (CC) sequences before the buffer overflows (and words are dropped). The buffer normally fills up to one half and then deletes CC sequences when over half full, and inserts CC sequences when under one half full. So from a half-full state, you can (conservatively) accept an extra 360 KB of data (that is, receiving at +200 ppm) without dropping any. From a half-full state you can cope with another 360 KB of data without inserting local faults (for -200 ppm).

- Test pattern generation and checking

- Serial interface to backplane connector

- Management registers (PCS/PMA) with optional MDIO interface

Figure 1-2: Implementation of the BASE-KR Core

# **Applications**

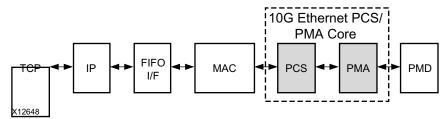

Figure 1-3 shows a typical Ethernet system architecture and the core within it. The MAC and all the blocks to the right are defined in *IEEE Std 802.3* [Ref 1].

Figure 1-3: Typical Ethernet System Architecture

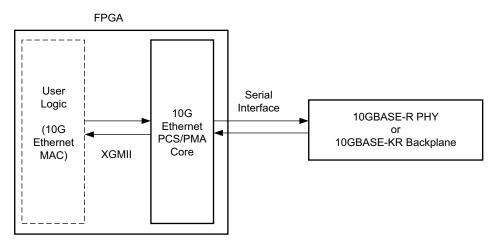

Figure 1-4 shows the 10G Ethernet PCS/PMA core connected on one side to a 10G Ethernet MAC and on the other to an optical module (BASE-R) or backplane (BASE-KR) using a serial interface. The optional WAN Interface Sublayer (WIS) part of the 10GBASE-R standard is not implemented in this core.

The 10G Ethernet PCS/PMA core is designed to be attached to the Xilinx IP 10G Ethernet MAC core over XGMII. More details are provided in Chapter 3, Designing with the Core.

Figure 1-4: Core Connected to MAC Core Using XGMII Interface

# **Unsupported Features**

The following features are not supported in this release of the core.

While the Training Protocol is supported natively by the core, no logic is provided that controls the far-end transmitter adaptation based on analysis of the received signal quality. This is because extensive testing has shown that to be unnecessary.

However, a training interface is provided on the core that allows access to all core registers and to the DRP port on the transceiver. You can employ this interface to implement your own Training Algorithm for 10GBASE-KR, if required.

# **Licensing and Ordering**

## **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado design tools have several license check points for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following tools:

- Vivado Synthesis

- Vivado Implementation

- write bitstream (Tcl command)

**IMPORTANT:** IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.

# **License Type**

# 10G Ethernet PCS/PMA (10GBASE-R)

This Xilinx LogiCORE™ IP module is provided at no additional cost with the Xilinx Vivado® Design Suite under the terms of the Xilinx End User License. Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

For more information, visit the 10 Gigabit Ethernet PCS/PMA (10GBASE-R) <u>product web page</u>.

## 10G Ethernet PCS/PMA with FEC/Auto-Negotiation (10GBASE-KR)

This Xilinx LogiCORE IP module is provided under the terms of the Xilinx Core License Agreement. The module is shipped as part of the Vivado Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information about pricing and availability.

For more information, visit the 10 Gigabit Ethernet PCS/PMA with FEC/Auto-Negotiation (10GBASE-KR) <u>product web page</u>. The 10G/25GBASE-KR/CR license key is bundled with this product. For more information, visit the 10G/25G Ethernet Subsystem <u>product web page</u>.

Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# **Product Specification**

# **Standards**

The 10GBASE-R/KR core is designed to the standard specified in clauses 45, 49, 72, 73, and 74 of the 10 Gigabit Ethernet specification IEEE Std 802.3 [Ref 1].

# **Performance**

# **Transceiver Latency**

See the 7 Series Transceivers User Guide (UG476) [Ref 4], the UltraScale Architecture GTH Transceivers User Guide (UG576) [Ref 5], and the UltraScale Architecture GTY Transceivers User Guide (UG578) [Ref 6] for information on the transceiver latency.

## 64-Bit Data Width

## Latency

These measurements are for the core only; they do not include the latency through the transceiver. The latency through the transceiver can be obtained from the relevant user guide.

#### Transmit Path Latency

As measured from the input port xgmii\_txd[63:0] of the transmitter side XGMII (until that data appears on gt\_txd[31:0] on the transceiver interface), the latency through the 7 series core for the XGMII interface configuration in the transmit direction is 20 periods of txoutclk. When the optional FEC functionality is included in the core and enabled, this increases to 26 periods of txoutclk.

Measuring in the same way for an UltraScale<sup>™</sup> device for 10GBASE-R, the transmit latency is six periods of the 156.25 MHz transmit clock, which increases to 12 periods when FEC is included and enabled. The latency for UltraScale devices for 10GBASE-KR is 20 periods of

txoutclk. When the optional FEC functionality is included in the core and enabled, this increases to 26 periods of txoutclk.

#### **Receive Path Latency**

Latency in the receive direction is variable and depends mainly on the fill level of the receive elastic buffer.

Measured from the input into the core on gt\_rxd[31:0] until the data appears on xgmii\_rxd[63:0] of the receiver side XGMII interface, the latency through the 7 series core in the receive direction is nominally equal to 1831 UI, or 27.75 cycles of coreclk, increasing to 2723 UI, or 41.26 cycles of coreclk when the elastic buffer is at its fullest possible level. The exact latency depends on sync bit alignment position and data positioning within the transceiver 4-byte interface. For UltraScale devices in 10GBASE-R configuration, excluding the elastic buffer, the latency through the core in the receive direction is nominally equal to seven cycles of the 156.25 MHz receive clock. The latency through the elastic buffer is the same as calculated for 7 series devices (the number of cycles is for the 156.25 MHz receive clock). For UltraScale devices in 10GBASE-KR configuration the latency is same as calculated for 7 series cores.

When the optional FEC functionality is included in the core the UltraScale core has a single extra cycle of the 156.25 MHz receive clock and this increases for all devices by 70 cycles of rxrecclk\_out when FEC is enabled and if error reporting to the PCS layer is enabled, there is an extra 66 cycles of rxrecclk\_out latency.

### 32-Bit Data Width

#### Latency

These measurements are for the core only; they do not include the latency through the transceiver. The latency through the transceiver can be obtained from the relevant user guide. There is a margin of error of 33 UI (a single 32-bit XGMII word) with these numbers.

#### Transmit Path Latency

As measured from the input port xgmii\_txd[31:0] of the transmitter side XGMII (until that data appears on gt\_txd[31:0] on the transceiver interface), the latency through the core for the XGMII interface configuration in the transmit direction for 7 series devices is 14 periods of txoutclk. For UltraScale devices this is eight periods of the 312.5 MHz transmit clock.

#### **Receive Path Latency**

Latency in the Receive direction is variable and depends mainly on the fill level of the receive elastic buffer.

Measured from the input into the core on gt\_rxd[31:0] until the data appears on xgmii\_rxd[31:0] of the receiver side XGMII interface, the latency through the core in the receive direction for 7 series devices is nominally equal to 1472 UI, or 44.6 cycles of coreclk, increasing to ~72 cycles of coreclk when the elastic buffer is at its fullest possible level. The exact latency depends on sync bit alignment position and data positioning within the transceiver 4-byte interface. For UltraScale devices, excluding the elastic buffer, the latency is eight cycles of the 312.5 MHz receive clock.

# **Resource Utilization**

For details about resource utilization, visit Performance and Resource Utilization.

# **Port Descriptions**

This section provides information about the ports for the XGMII interface and for the serial data interface. Additionally, information is provided about the ports for the management interface (MDIO) and its alternative, the vector-based configuration and status signals. Information is also provided about the clock and reset signals, the DRP training interface ports, the transceiver debug ports and miscellaneous core signals.

# **XGMII Interface Signals**

For 10GBASE-R, the core provides the option of a 64-bit or a 32-bit XGMII data width (the selected data width also applies internally to the core). For the 10GBASE-KR option, only the 64-bit option is available.

#### 64-Bit XGMII

When the 64-bit datapath is selected, the MAC (or client) side of the core has a 64-bit datapath plus eight control bits implementing an XGMII interface. Table 2-1 defines the signals, which are all synchronous to a 156.25 MHz clock source; the relevant clock port is dependent upon the family and core permutation. It is designed to be connected to either user logic within the FPGA or, by using SelectIO™ technology Double Data Rate (DDR) registers in your own top-level design, to provide an external 32-bit DDR XGMII, defined in clause 46 of *IEEE Std 802.3*. TX clock source and RX clock source are defined in Table 3-1.

Table 2-1: MAC-Side Interface Ports

| Signal Name     | Direction | Clock Domain    | Description                 |

|-----------------|-----------|-----------------|-----------------------------|

| xgmii_txd[63:0] | In        | TX clock source | 64-bit transmit data word   |

| xgmii_txc[7:0]  | In        | TX clock source | 8-bit transmit control word |

Table 2-1: MAC-Side Interface Ports

| Signal Name     | Direction | Clock Domain    | Description                |

|-----------------|-----------|-----------------|----------------------------|

| xgmii_rxd[63:0] | Out       | RX clock source | 64-bit receive data word   |

| xgmii_rxc[7:0]  | Out       | RX clock source | 8-bit receive control word |

#### 32-bit XGMII

When the 32-bit datapath is selected, the MAC (or client) side of the core has a 32-bit datapath plus four control bits implementing an XGMII interface. Table 2-2 defines the signals, which are all synchronous to a 312.5 MHz clock source; the relevant clock port is dependent upon the family and core permutation. It is designed to be connected to user logic within the FPGA. TX clock source and RX clock source are defined in Table 3-1.

Table 2-2: MAC-Side Interface Ports

| Signal Name     | Direction | Clock Domain    | Description                 |

|-----------------|-----------|-----------------|-----------------------------|

| xgmii_txd[31:0] | ln        | TX clock source | 32-bit transmit data word   |

| xgmii_txc[3:0]  | In        | TX clock source | 4-bit transmit control word |

| xgmii_rxd[31:0] | Out       | RX clock source | 32-bit receive data word    |

| xgmii_rxc[3:0]  | Out       | RX clock source | 4-bit receive control word  |

## **Serial Data Ports**

The serial data ports should be connected to the PMD which is either an optical module or a backplane.

Table 2-3: Serial Data Ports

| Signal Name | Direction | Description                       |

|-------------|-----------|-----------------------------------|

| txn, txp    | Out       | Serial data to optics/backplane   |

| rxn, rxp    | In        | Serial data from optics/backplane |

# **Optical Module Interface Ports**

The status and control interface to an attached optical module is a simple pin-to-pin interface on those pins that need to be connected. The signals are described in Table 2-4. See Chapter 3, Designing with the Core for details on connecting an optical module to the 10GBASE-R core. For 10GBASE-KR, it is recommended to tie  $signal_detect$  to 1,  $tx_fault$  to 0, and leave  $tx_disable$  unconnected.

**Table 2-4:** Optical Module Interface Ports

| Signal Name   | Direction | Description                                                   |

|---------------|-----------|---------------------------------------------------------------|

| signal_detect | In        | Status signal from attached optical module. <sup>(1)</sup>    |

| tx_fault      | In        | Status signal from attached optical module. <sup>(2)(3)</sup> |

| tx_disable    | Out       | Control signal to attached optical module                     |

- 1. When an optical module is present, the logical NOR of MODDEF0 and LOS (Loss of Signal) outputs should be used to create the signal\_detect input to the core.

- 2. This signal is not connected inside this version of the core. You should handle these inputs and reset your design as required.

- 3. Connect to SFP+ tx\_fault signal, or XFP MOD\_NR signal, depending on which is present.

# **Management Interface (MDIO) Ports**

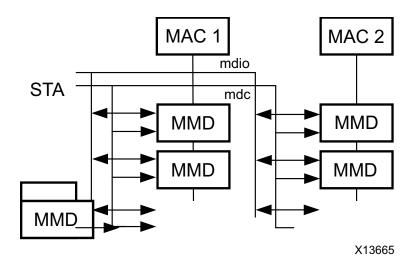

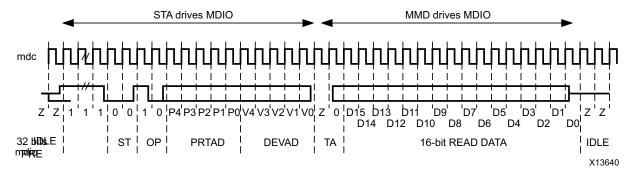

The optional MDIO interface is a simple low-speed two-wire interface for management of the 10G Ethernet PCS/PMA core, consisting of a clock signal and a bidirectional data signal. The interface is defined in clause 45 of the *IEEE 802.3-2012* standard.

In this core, the MDIO interface is an optional block. If implemented, the bidirectional data signal MDIO is implemented as three unidirectional signals. These can be used to drive a 3-state buffer either in the FPGA IOB or in a separate device.

Where a single point-to-point connection to a MAC is required, connect mdio\_in on the 10G Ethernet PCS/PMA core to mdio\_out on the MAC and vice versa, leaving the mdio\_tri output unconnected. The mdio\_tri signal is not required for a point-to-point connection.

**Table 2-5:** MDIO Management Interface Ports

| Signal Name  | Direction | Description                                                                                                                         |

|--------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------|

| mdc          | In        | Management clock                                                                                                                    |

| mdio_in      | In        | MDIO Input                                                                                                                          |

| mdio_out     | Out       | MDIO Output                                                                                                                         |

| mdio_tri     | Out       | MDIO 3-state control.                                                                                                               |

| maio_tri Out |           | 1 disconnects the output driver from the MDIO bus.                                                                                  |

| prtad[4:0]   | ln        | MDIO port address. When multiple MDIO-managed ports appear on the same bus, this input can be used to set the address of each port. |

## **Clock and Reset Ports**

The clock and reset ports are described in this section for both Shared Logic options.

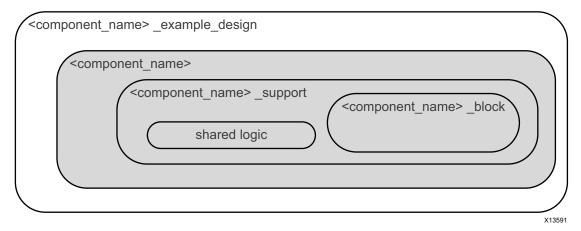

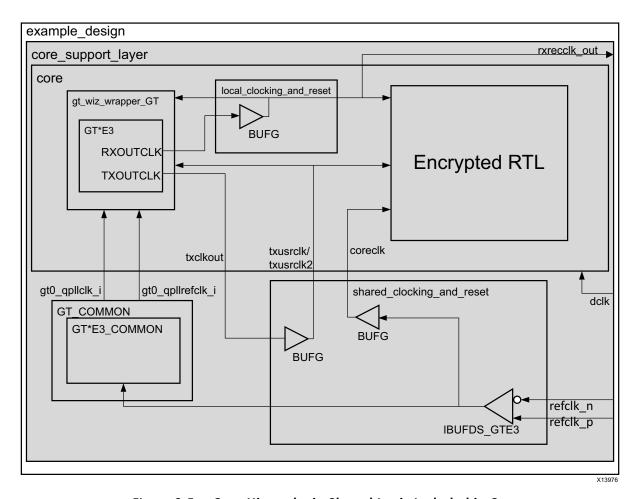

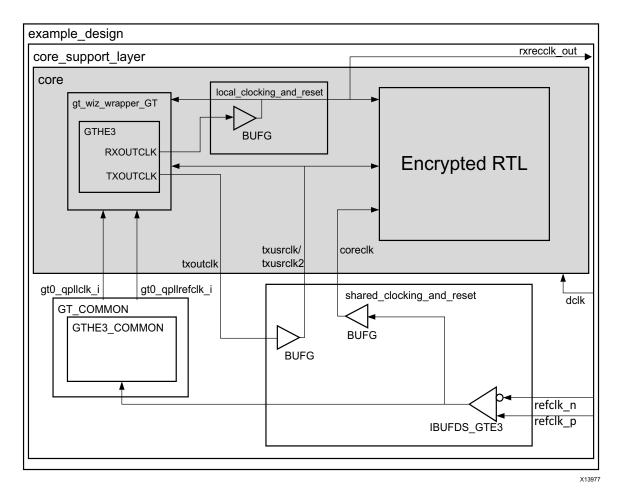

#### Shared Logic Included in Example Design

If **Include Shared Logic in example design** is selected during the core customization, circuits for clock and reset management are included in the top-level example design sources. These can include clock generators, reset synchronizers, or other circuits that can be useful in your particular application. Table 2-6 shows the ports on the core that are associated with clocks and resets.

Table 2-6: Clock and Reset Ports—Shared Logic in Example Design

| Signal Name         | Direction | Description                                                                                                                                                                                                                                                                |

|---------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| coreclk             | In        | This clock is used to clock the TX datapath and management logic in 7 series devices and for 10GBASE-KR in UltraScale devices. In UltraScale devices for 10GBASE-R this clock is used only as a free running clock source for reset logic associated with the transceiver. |

| txusrclk, txusrclk2 | In        | Connected to the TXUSRCLK and TXUSRCLK2 input ports of the transceiver, these clocks are derived from the TXOUTCLK from the transceiver. In UltraScale devices for 10GBASE-R txusrclk2 is used to clock the transmit datapath and management logic.                        |

| dclk <sup>(1)</sup> | In        | Management/DRP clock: this clock can be any rate that is valid for the applicable transceiver DRPCLK.                                                                                                                                                                      |

| areset              | In        | Asynchronous (master) reset <sup>(2)</sup>                                                                                                                                                                                                                                 |

| txoutclk            | Out       | TXOUTCLK from the transceiver used in the shared clock generation logic                                                                                                                                                                                                    |

| rxrecclk_out        | Out       | RXOUTCLK from the transceiver                                                                                                                                                                                                                                              |

| areset_coreclk      | In        | Synchronous reset in the coreclk domain                                                                                                                                                                                                                                    |

| gttxreset           | In        | Transceiver TX reset signal in the coreclk domain                                                                                                                                                                                                                          |

| gtrxreset           | In        | Transceiver RX reset signal in the coreclk domain                                                                                                                                                                                                                          |

| qplllock            | In        | Transceiver QPLL Lock signal for 7 series devices                                                                                                                                                                                                                          |

| qplloutclk          | In        | Transceiver QPLL clock for 7 series devices                                                                                                                                                                                                                                |

| qplloutrefclk       | In        | Transceiver QPLL refclk for 7 series devices                                                                                                                                                                                                                               |

| qpll0lock           | In        | Transceiver QPLL lock signal for UltraScale devices                                                                                                                                                                                                                        |

| qpll0outclk         | In        | Transceiver QPLL clock for UltraScale devices                                                                                                                                                                                                                              |

| qpll0outrefclk      | In        | Transceiver QPLL refclk for UltraScale devices                                                                                                                                                                                                                             |

| reset_counter_done  | In        | Indication that 500 ns have passed after configuration was complete                                                                                                                                                                                                        |

| tx_resetdone        | Out       | Transceiver TX reset-done                                                                                                                                                                                                                                                  |

| rx_resetdone        | Out       | Transceiver RX reset-done                                                                                                                                                                                                                                                  |

| reset_tx_bufg_gt    | Out       | Control from core to the BUFG_GT in the shared logic. Only for 64-bit datapath cores on UltraScale devices                                                                                                                                                                 |

Table 2-6: Clock and Reset Ports—Shared Logic in Example Design (Cont'd)

| Signal Name | Direction | Description                                                                                   |

|-------------|-----------|-----------------------------------------------------------------------------------------------|

| qpll0reset  | Out       | For UltraScale devices, a reset signal from the core to the QPLL located in the shared logic. |

- 1. For UltraScale devices the DCLK must be free-running and the frequency must be kept less than or equal to the maximum DRPCLK frequency specified for the transceiver type or the TXUSRCLK2 frequency, which is 156.25 MHz for 64-bit datapaths.

- 2. This reset also resets all management registers.

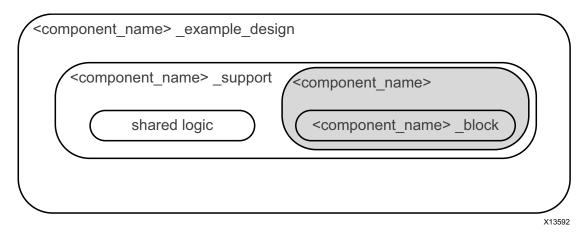

## Shared Logic Included in Core

If **Include Shared Logic in core** is selected during core customization, most of the clocking and reset blocks are included within the core. Table 2-7 shows the ports on the core that are associated with these clocks and resets, which can be reused by other user logic or IP cores.

Table 2-7: Clock and Reset Ports—Shared Logic in Core

| Signal Name         | Direction | Description                                                                                                                                                                                                                                                          |

|---------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| refclk_p, refclk_n  | In        | Differential clock input (for transceiver)                                                                                                                                                                                                                           |

| dclk <sup>(1)</sup> | In        | Management/DRP clock: this clock can be any rate that is valid for the applicable transceiver drpclk                                                                                                                                                                 |

| reset               | In        | Asynchronous master reset <sup>(2)</sup>                                                                                                                                                                                                                             |

| resetdone_out       | Out       | Combined transceiver reset-done indication (in the coreclk_out domain)                                                                                                                                                                                               |

| coreclk_out         | Out       | This is used to clock the TX datapath and management logic in 7 series devices and for 10GBASE-KR in UltraScale devices. In UltraScale devices for 10GBASE-R this clock is used only as a free running clock source for reset logic associated with the transceiver. |

| qplllock_out        | Out       | Lock indication from QPLL block in core for 7 series devices                                                                                                                                                                                                         |

| qplloutclk_out      | Out       | QPLL output clock from QPLL block in core for 7 series devices                                                                                                                                                                                                       |

| qplloutrefclk_out   | Out       | QPLL output reference clock from QPLL block in core for 7 series devices                                                                                                                                                                                             |

| qpll0lock_out       | Out       | Lock indication from QPLL block in core for UltraScale architecture                                                                                                                                                                                                  |

| qpll0outclk_out     | Out       | QPLL output clock from QPLL in core for UltraScale architecture                                                                                                                                                                                                      |

| qpll0outrefclk_out  | Out       | QPLL output reference clk from QPLL in core for UltraScale architecture                                                                                                                                                                                              |

| txusrclk_out        | Out       | txusrclk from shared logic block in core                                                                                                                                                                                                                             |

| txusrclk2_out       | Out       | txusrclk2 from shared logic block in core. This is used to clock the TX datapath and management logic in UltraScale devices for 10GBASE-R designs.                                                                                                                   |

| rxrecclk_out        | Out       | RXOUTCLK from the GT output which is used to clock the receive datapath in the core.                                                                                                                                                                                 |

Table 2-7: Clock and Reset Ports—Shared Logic in Core (Cont'd)

| Signal Name            | Direction | Description                                                                                                                                                                                                                   |

|------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| areset_datapathclk_out | Out       | reset signal synchronized to the TX datapath clock which is the free-running coreclk_out for 7 series devices and 10GBASE-KR designs for UltraScale devices or the txusrclk2_out for UltraScale devices in 10GBASE-R designs. |

| areset_coreclk_out     | Out       | reset signal synchronized to the free-running coreclk_out;<br>UltraScale devices only                                                                                                                                         |

| gttxreset_out          | Out       | Signal that is used to reset the TX side of the transceiver, synchronized to coreclk_out                                                                                                                                      |

| gtrxreset_out          | Out       | Signal that is used to reset the RX side of the transceiver, synchronized to coreclk_out                                                                                                                                      |

| txuserrdy_out          | Out       | Transceiver control signal equivalent to the QPLLLOCK signal, synchronized to txusrclk2_out                                                                                                                                   |

| reset_counter_done_out | Out       | Indication that 500 ns have passed after configuration or 'master' reset, synchronized to coreclk_out                                                                                                                         |

- 1. For UltraScale devices the DCLK must be free-running and the frequency must be kept less than or equal to the maximum DRPCLK frequency specified for the transceiver type or the TXUSRCLK2 frequency, which is 156.25 MHz for 64-bit datapaths.

- 2. This reset also resets all management registers.

# **10GBASE-KR Training Interface**

In Virtex-7, and UltraScale devices, in 10GBASE-KR only, an external training algorithm can optionally be connected to the training interface, which allows access to both the 802.3 registers in the core and the DRP registers in the transceiver. Table 2-8 shows the ports on the core that are associated with that interface.

**Table 2-8:** Training Interface Ports

| Signal Name           | Direction | Description                                                                                                                                                                                                         |  |

|-----------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| training_enable       | In        | Signal from external training algorithm to enable the training interface. This should not be confused with the IEEE register 1.150.1–Training Enable. A rising edge on training_enable initiates a register access. |  |

| training_addr[20:0]   | ln        | Register address from training algorithm – bits [20:16] are the DEVAD for 802.3 registers                                                                                                                           |  |

| training_rnw          | In        | Read/Write_bar signal from training algorithm                                                                                                                                                                       |  |

| training_ipif_cs      | In        | Select access to 802.3 registers in the core <sup>(1)</sup>                                                                                                                                                         |  |

| training_drp_cs       | In        | Select access to DRP registers in the transceiver                                                                                                                                                                   |  |

| training_rddata[15:0] | Out       | Read data from DRP or 802.3 registers                                                                                                                                                                               |  |

| training_rdack        | Out       | Read Acknowledge signal to external training algorithm                                                                                                                                                              |  |

Table 2-8: Training Interface Ports (Cont'd)

| Signal Name    | Direction | Description                                             |

|----------------|-----------|---------------------------------------------------------|

| training_wrack | Out       | Write Acknowledge signal to external training algorithm |

1. This signal has no meaning or effect when the core is created without an MDIO interface because all registers are exposed through the configuration and status vectors. This should be tied to 0 in that case. Access to transceiver DRP registers through the training interface is unaffected.

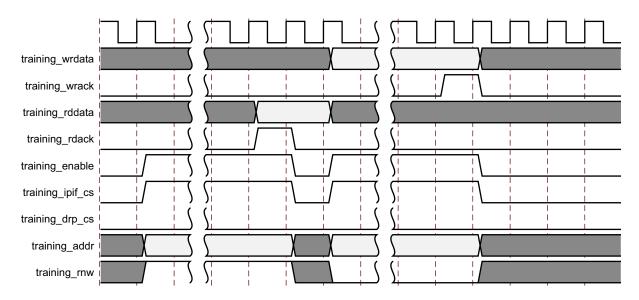

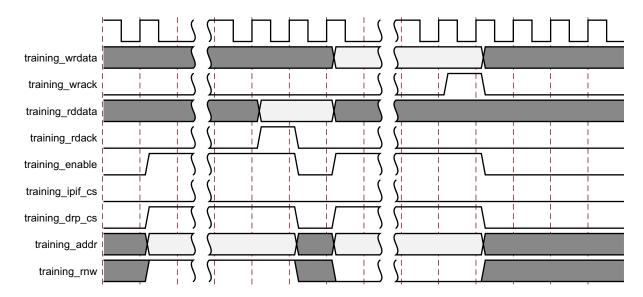

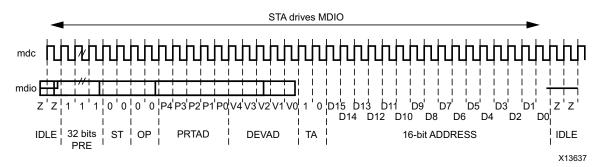

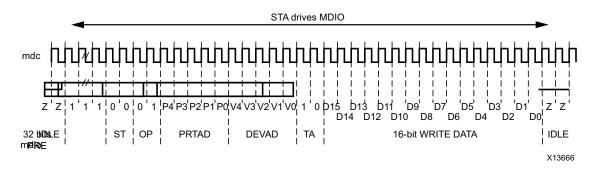

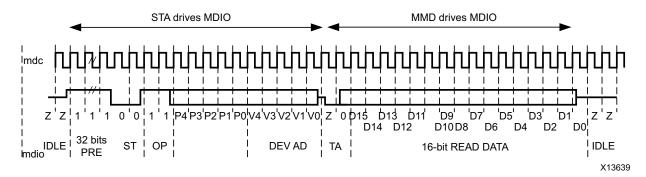

Figure 2-1 and Figure 2-2 show the timing diagrams for using the training interface to access internal core registers and transceiver registers through the DRP port. As shown, training\_drp\_cs, training\_ipif\_cs, and training\_enable should be brought Low between read or write accesses. The clock for Figure 2-1 and Figure 2-2 can be determined from Table 3-1.

Figure 2-1: Using the Training Interface to Access Internal Core Registers

Figure 2-2: Using the Training Interface to Access Transceiver Registers through the DRP Port

## **DRP Interface Ports**

## Zynq-7000, Virtex-7, and Kintex-7 Devices

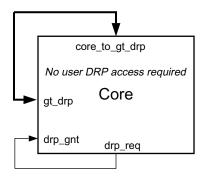

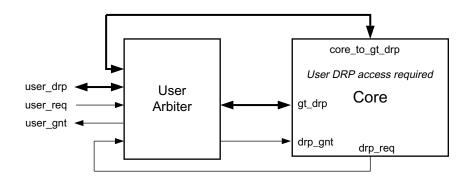

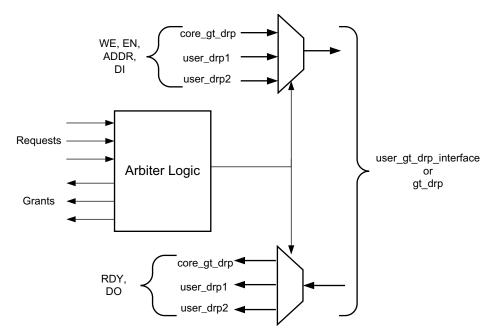

To facilitate the connection of user logic to the DRP interface of the transceiver, the interface between the core logic and the transceiver is brought out to an interface which can be connected to an external Arbiter block. The interface direct to the transceiver DRP is also provided.

If no user logic or arbiter is required, the <code>core\_gt\_drp\_interface</code> can be connected directly to the <code>user\_gt\_drp\_interface</code> and <code>drp\_req</code> can be connected directly to <code>drp\_gnt</code>.

All signals in Table 2-9 are synchronous to the dclk input of the core.

Table 2-9: DRP Interface Ports

| Signal Name        | Direction | Interface             | Description                                                                                                                                                                 |

|--------------------|-----------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| drp_req            | Out       | N/A                   | This active-High signal can be used on an external arbiter, to request and hold onto access to the DRP.                                                                     |

| drp_gnt            | In        | N/A                   | This signal should be driven High when access is granted to the DRP by an external arbiter. If no external arbiter is present, connect this directly to the drp_req signal. |

| drp_daddr_o [15:0] | Out       | core_gt_drp_interface | This vector is driven by the core and is eventually used on the DADDR port on the transceiver.                                                                              |

Table 2-9: DRP Interface Ports (Cont'd)

| Signal Name       | Direction | Interface             | Description                                                                                                                 |  |

|-------------------|-----------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| drp_den_o         | Out       | core_gt_drp_interface | This signal is driven by the core and is eventually used on the DEN port on the transceiver.                                |  |

| drp_di_o[15:0]    | Out       | core_gt_drp_interface | This vector is driven by the core and is eventually used on the DI port on the transceiver.                                 |  |

| drp_dwe_o         | Out       | core_gt_drp_interface | This signal is driven by the core and is eventually used on the DWE port on the transceiver.                                |  |

| drp_drpdo_i[15:0] | In        | core_gt_drp_interface | This vector is driven by an external arbiter, or by drp_drpdo_o and is eventually used by the core.                         |  |

| drp_drdy_i        | In        | core_gt_drp_interface | This signal is driven by an external arbiter, or by drp_drdy_o and is eventually used by the core.                          |  |

| drp_daddr_i[15:0] | ln        | user_gt_drp_interface | This vector is driven by an external arbiter or by drp_daddr_o and is eventually used on the DADDR port on the transceiver. |  |

| drp_den_i         | In        | user_gt_drp_interface | This signal is driven by an external arbiter or by drp_den_o and is eventually used on the DEN port on the transceiver.     |  |

| drp_di_i[15:0]    | In        | user_gt_drp_interface | This vector is driven by an external arbiter or by drp_di_o and is eventually used on the DI port on the transceiver.       |  |

| drp_dwe_i         | In        | user_gt_drp_interface | This signal is driven by an external arbiter or by drp_dwe_o and is eventually used on the DWE port on the transceiver.     |  |

| drp_drpdo_o[15:0] | Out       | user_gt_drp_interface | This vector is driven by the DO port on the transceiver.                                                                    |  |

| drp_drdy_o        | Out       | user_gt_drp_interface | This signal is driven by the DRDY port on the transceiver.                                                                  |  |

#### **UltraScale Architecture**

To facilitate the connection of user logic to the DRP interface of the transceiver, the interface between the core logic and the transceiver is brought out to an interface that can be connected to an external Arbiter block. The interface directly to the transceiver DRP is also provided.

If no user logic or arbiter is required, the <code>core\_to\_gt\_drp</code> interface can be connected directly to the <code>gt\_drp</code> interface and the <code>drp\_req</code> can be connected directly to <code>drp\_gnt</code>.

All signals in Table 2-10 are synchronous to the dclk input of the core.

Table 2-10: DRP Interface Signals

| Signal Name              | Direction | Interface      | Description                                                                                                                                                                 |

|--------------------------|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| drp_req                  | Out       | N/A            | This active-High signal can be used on an external arbiter to request and hold onto access to the DRP.                                                                      |

| drp_gnt                  | ln        | N/A            | This signal should be driven High when access is granted to the DRP by an external arbiter. If no external arbiter is present, connect this directly to the drp_req signal. |

| core_to_gt_drpaddr[15:0] | Out       | core_to_gt_drp | This vector is driven by the core and is eventually used on the DADDR port on the transceiver.                                                                              |

| core_to_gt_drpen         | Out       | core_to_gt_drp | This signal is driven by the core and is eventually used on the DEN port on the transceiver.                                                                                |

| core_to_gt_drpdi[15:0]   | Out       | core_to_gt_drp | This vector is driven by the core and is eventually used on the DI port on the transceiver.                                                                                 |

| core_to_gt_drpwe         | Out       | core_to_gt_drp | This signal is driven by the core and is eventually used on the DWE port on the transceiver.                                                                                |

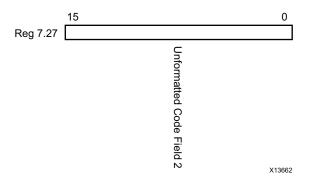

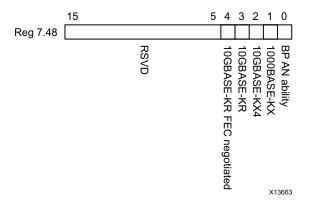

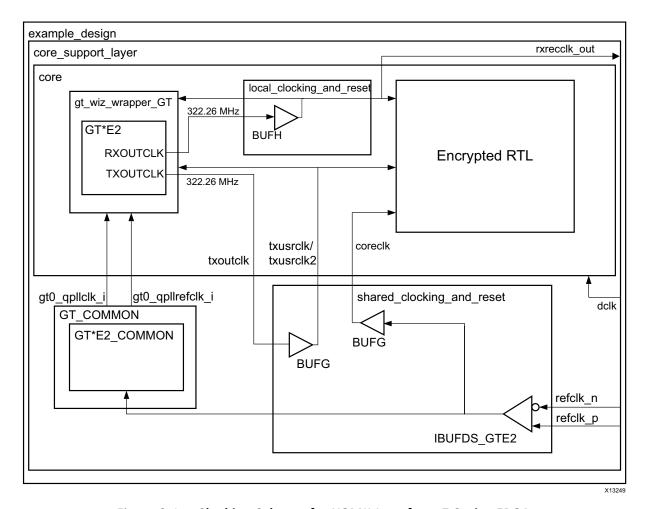

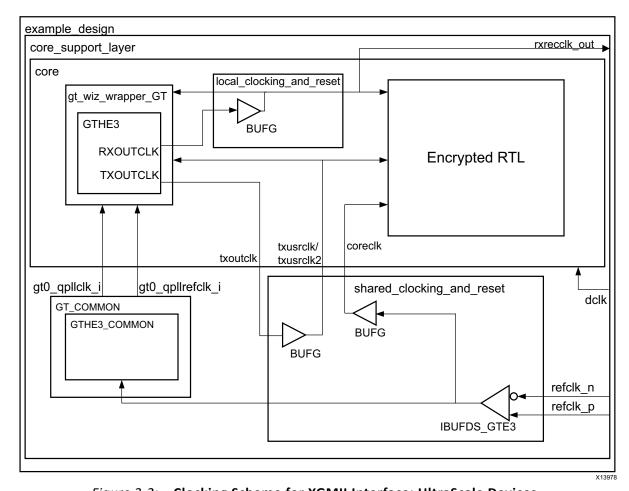

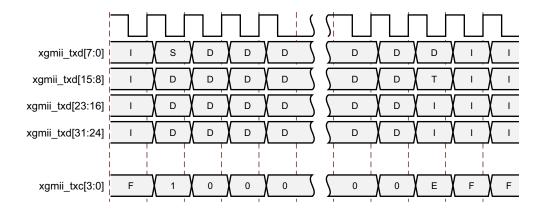

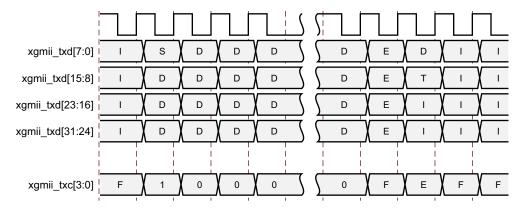

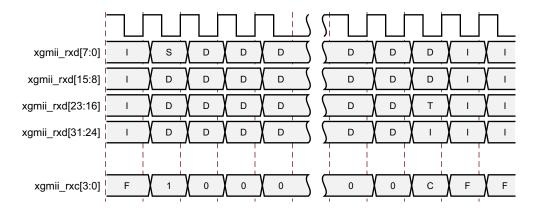

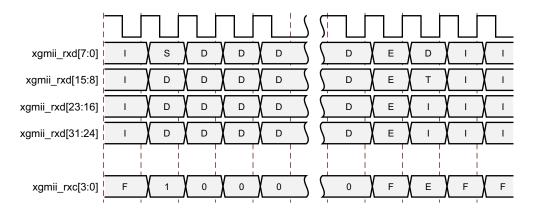

| core_to_gt_drpdo[15:0]   | In        | core_to_gt_drp | This vector is driven by an external arbiter, or by gt_drpdo and is eventually used by the core.                                                                            |