# LogiCORE IP LTE MIMO Encoder

PB017 (v4.0) November 18, 2015

**Product Brief**

#### Introduction

The Xilinx® LogiCORE™ IP 3GPP LTE MIMO Encoder core implements multiple-input, multiple-output (MIMO) encoding for LTE eNodeB applications as defined in the 3GPP TS 36.211 v.9.1 specification [Ref 1]. It represents one IP component in the Xilinx broader LTE baseband platform.

### **Additional Documentation**

A product guide is available for this core. Access to this material can be requested by clicking on this registration link:

www.xilinx.com/member/lte\_mimo\_enc\_eval/index.htm

#### **Features**

- AXI4-Stream compliant interfaces

- Implements layer mapping and precoding as defined in the 3GPP TS 36.211 v.9.1 specification [Ref 1]

- Supports both Transmit Diversity and Spatial Multiplexing encoding schemes

- Cyclic Delay Diversity option

- Supports 2 and 4 antennas

- Maximum theoretical throughput supported for systems with up to 20 MHz bandwidth

- Parameterizable input/output data precision

| LogiCORE IP Facts Table                     |                                                                                                 |  |

|---------------------------------------------|-------------------------------------------------------------------------------------------------|--|

| Core Specifics                              |                                                                                                 |  |

| Supported<br>Device Family <sup>(1)</sup>   | UltraScale+™ Families<br>UltraScale™ Architecture<br>Zynq®-7000 All Programmble SoC<br>7 Series |  |

| Supported User<br>Interfaces                | AXI4-Stream                                                                                     |  |

|                                             | Provided with Core                                                                              |  |

| Design Files                                | Encrypted RTL                                                                                   |  |

| Example Design                              | Not Provided                                                                                    |  |

| Test Bench                                  | Not Provided                                                                                    |  |

| Constraints File                            | Not Provided                                                                                    |  |

| Simulation<br>Model                         | VHDL Behavioral<br>Verilog and VHDL Structural Model<br>and C Model                             |  |

| Supported<br>S/W Driver                     | Not Applicable                                                                                  |  |

| Tested Design Flows(2)                      |                                                                                                 |  |

| Design Entry                                | Vivado® Design Suite                                                                            |  |

| Simulation                                  | For supported simulators, see the Xilinx Design Tools: Release Notes Guide.                     |  |

| Synthesis                                   | Not Applicable                                                                                  |  |

| Support                                     |                                                                                                 |  |

| Provided by Xilinx @ www.xilinx.com/support |                                                                                                 |  |

#### **Notes:**

- For a complete listing of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

© Copyright 2014–2015 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are trademarks of ARM in the EU and other countries. All other trademarks are the property of their respective owners.

# **Applications**

The 3GPP LTE MIMO Encoder can be used in base station applications implementing eNodeB following the 3GPP TS 36.211 v.9.1 specification [Ref 1]. The LTE MIMO Encoder can perform the MIMO encoding functions for downlink transmission.

# **Theory of Operation**

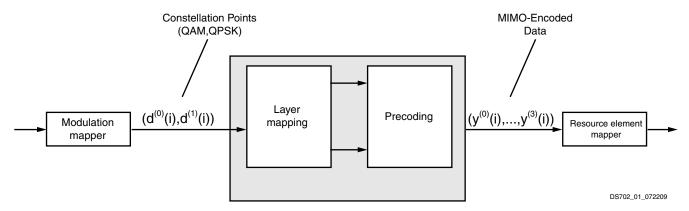

The LTE MIMO Encoder is to be part of the eNodeB, the downlink baseband processing that encompasses layer mapping and precoding as defined in [Ref 1]. Figure 1 shows a high-level view of the functionality included in this product.

Figure 1: LTE MIMO Encoder v4.0 Functionality

#### **C Model**

The LTE 3GPP MIMO Encoder core has a bit accurate C model designed for system modeling. The model is bit accurate but not cycle-accurate, so it produces exactly the same output data as the core on a code-word by code-word basis. However, it does not model the core latency or interface signals.

The bit accurate behavioral C model of the LTE MIMO Encoder v4.0 and associated product guide are available to customers. The C model is provided as a dynamically linked library for Windows 32-bit and 64-bit Linux platforms. A README.txt file describes the contents of the installed directory structure and any further platform-specific installation instructions.

# **Technical Support**

Xilinx provides technical support at <a href="www.xilinx.com/support">www.xilinx.com/support</a> for this LogiCORE IP product when used as described in the product documentation. Xilinx cannot guarantee timing, functionality, or support of product if implemented in devices that are not defined in the documentation, if customized beyond that allowed in the product documentation, or if changes are made to any section of the design labeled DO NOT MODIFY.

For Answer Records related to the LTE 3GPP MIMO Encoder core, see AR: <u>54469</u>.

# **Licensing and Ordering Information**

A free evaluation version of the core is provided with the Xilinx Vivado Design Suite, which lets you assess the core functionality and demonstrates the various interfaces of the core in simulation. To access the evaluation version visit the 3GPP LTE MIMO Encoder IP Evaluation page.

This Xilinx LogiCORE IP module is provided under the terms of the Xilinx Core License Agreement. The module is shipped as part of the Vivado Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your <u>local Xilinx sales representative</u> for information about pricing and availability.

For more information, visit the 3GPP LTE MIMO Encoder product page.

Information about other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your <u>local Xilinx sales representative</u>.

### References

1. Third Generation Partnership Projects (3GPP); Evolved Universal Radio Access (E-UTRA); Physical Channels and Modulation (Release 9), 3GPP TS 36.211 V9.1.0 (2010-03).

# **Revision History**

The following table shows the revision history for this document:

| Date       | Version | Revision                                               |

|------------|---------|--------------------------------------------------------|

| 11/18/2015 | 4.0     | UltraScale+ device support added.                      |

| 06/04/2014 | 4.0     | Initial Xilinx release. This document replaces XMP026. |

# **Please Read: Important Legal Notices**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of Xilinx's limited warranty, please refer to Xilinx's Terms of Sale which can be viewed at <a href="http://www.xilinx.com/legal.htm#tos">http://www.xilinx.com/legal.htm#tos</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in such critical applications, please refer to Xilinx's Terms of Sale which can be viewed at <a href="http://www.xilinx.com/legal.htm#tos">http://www.xilinx.com/legal.htm#tos</a>.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Xilinx:

EF-DI-MIMOENC-LTE-SITE