# RClamp0524PQ Low Capacitance RailClamp® 4-Line Surge and ESD Protection

### **PROTECTION PRODUCTS**

### Description

RailClamp<sup>®</sup> TVS arrays are ultra low capacitance ESD protection devices designed to protect high speed data interfaces. This series has been specifically designed to protect sensitive components which are connected to high-speed data and transmission lines from overvoltage caused by ESD (electrostatic discharge), CDE (Cable Discharge Events), and EFT (electrical fast transients).

RClamp0524PQ has a typical capacitance of only 0.3 pF between I/O pins. This allows it to be used on circuits operating in excess of 3GHz with no significant signal attenuation. ESD characteristics are highlighted by high ESD withstand voltage (+/-15kV per IEC 61000-4-2) and low dynamic resistance (0.43 Ohms typical). Each device will protect four lines operating at 5 volts

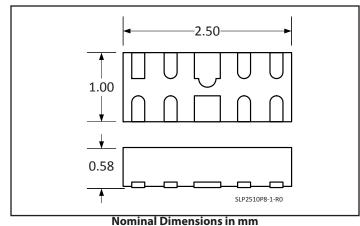

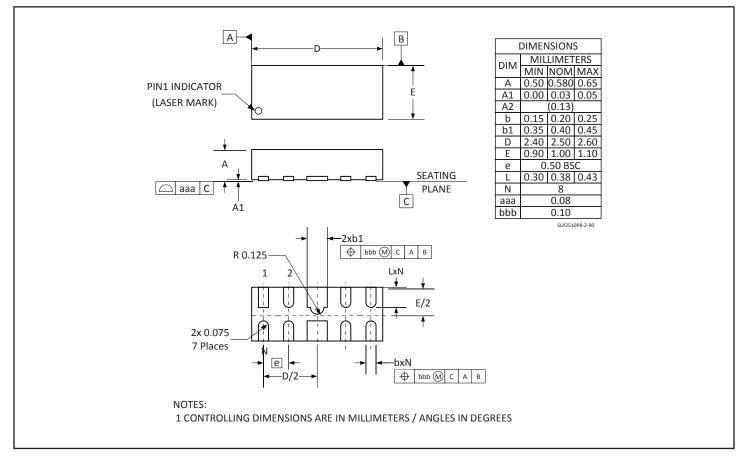

RClamp0524PQ is in a 10-pin SLP2510P8 package and is qualified to AEC-Q100, Grade 1 (-40 to +125 °C) for automotive applications. It measures 2.5 x 1.0 mm with a nominal height of only 0.58 mm. The leads are finished with lead-free NiPdAu. The flow- through package design simplifies PCB layout.

### **Features**

- Transient Protection to

- IEC 61000-4-2 (ESD) 25kV (Air), 15kV (Contact)

- IEC 61000-4-4 (EFT) 4kV (5/50ns)

- IEC 61000-4-5 (Lightning) 5A (8/20μs)

- ISO-10605 (ESD) 20kV (Air), 12kV (Contact)

- Qualified to AEC-Q100, Grade 1

- Protects four High-Speed Data Lines

- Working Voltage: 5V

- Low Capacitance: 0.8 pF Maximum (I/O to GND)

- Dynamic Resistance: 0.43 Ohms (Typ)

- Solid-State Silicon-Avalanche Technology

### **Mechanical Characteristics**

- SLP2510P8 Package

- Pb-Free, Halogen Free, RoHS/WEEE Compliant

- Nominal Dimensions: 2.5 x 1.0 x 0.58 mm

- Lead Finish: NiPdAu

- Molding Compound Flammability Rating: UL 94V-0

- Marking : Marking Code + Date Code

- Packaging : Tape and Reel

### **Applications**

- Automotive Applications

- Industrial Equipment

- HDMI

- Digital Visual Interface

- MDDI Ports

- PCI Express

### **Nominal Dimension**

Rev 2.0 June 22, 2015

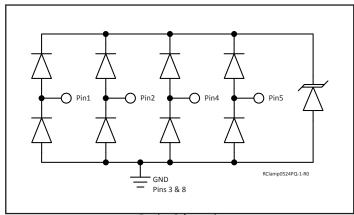

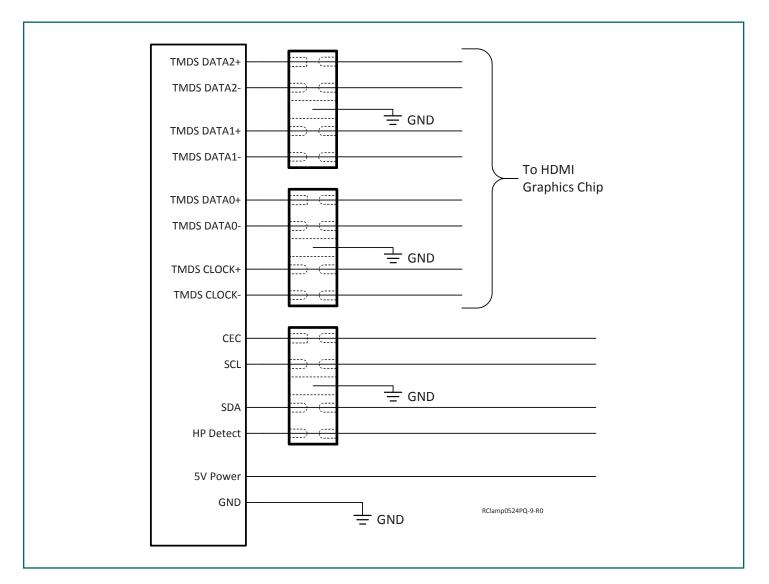

### **Functional Schematic**

**Device Schematic**

### **Absolute Maximum Rating**

| Rating                                                                                       | Symbol           | Value       | Units |

|----------------------------------------------------------------------------------------------|------------------|-------------|-------|

| Peak Pulse Power (tp = 8/20µs)                                                               | P <sub>PK</sub>  | 75          | W     |

| Peak Pulse Current (tp = $8/20\mu$ s)                                                        | I <sub>PP</sub>  | 5           | A     |

| ESD per IEC 61000-4-2 (Contact) <sup>(1)</sup><br>ESD per IEC 61000-4-2 (Air) <sup>(1)</sup> | V <sub>ESD</sub> | ±15<br>±25  | kV    |

| ESD per ISO-10605 (Contact) <sup>(2)</sup><br>ESD per ISO-10605 (Air) <sup>(2)</sup>         | V <sub>ESD</sub> | ±12<br>±20  | kV    |

| Operating Temperature                                                                        | T,               | -40 to +125 | °C    |

| Storage Temperature                                                                          | T <sub>STG</sub> | -55 to +150 | °C    |

# **Electrical Characteristics (T=25°C unless otherwise specified)**

| Parameter                              | Symbol           | Conditions                                                  |                   | Min. | Тур. | Max. | Units |

|----------------------------------------|------------------|-------------------------------------------------------------|-------------------|------|------|------|-------|

| Reverse Stand-Off Voltage              | V <sub>RWM</sub> | -40°C to 125°C<br>Any I/O pin to GND                        |                   |      |      | 5    | V     |

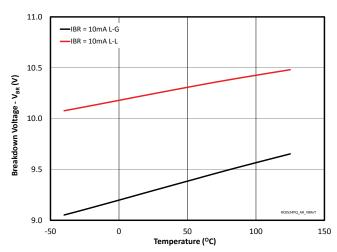

| Reverse Breakdown Voltage              | V <sub>BR</sub>  | I <sub>t</sub> = 10mA,<br>Any I/O pin to GND                | -40°C to<br>125°C | 6.5  | 9    | 11   | V     |

| Reverse Leakage Current                | I <sub>R</sub>   | $V_{RWM} = 5V$                                              | $T = 25^{\circ}C$ |      |      | 0.1  | μΑ    |

|                                        |                  |                                                             | T = 125°C         |      |      | 0.25 | μΑ    |

| Clamping Voltage <sup>(3)</sup>        | V <sub>c</sub>   | $I_{pp} = 1A$ , tp = 8/20µs,<br>Any I/O pin to GND          |                   |      |      | 12   | V     |

| Clamping Voltage <sup>(3)</sup>        | V <sub>c</sub>   | I <sub>pp</sub> = 5A, tp = 8/20μs,<br>Any I/O pin to GND    |                   |      |      | 15   | V     |

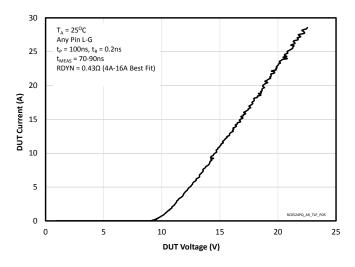

| ESD Clamping Voltage <sup>(4)</sup>    | V <sub>c</sub>   | $I_{PP} = 4A$ , tp = 0.2/100ns (TLP)<br>Any I/O pin to GND  |                   |      | 12   |      | V     |

| ESD Clamping Voltage <sup>(4)</sup>    | V <sub>c</sub>   | $I_{pp} = 16A$ , tp = 0.2/100ns (TLP)<br>Any I/O pin to GND |                   |      | 17   |      | V     |

| Dynamic Resistance <sup>(4), (5)</sup> | R <sub>DYN</sub> | tp = 0.2/100ns (TLP)<br>Any I/O pin to GND                  |                   |      | 0.43 |      | Ohms  |

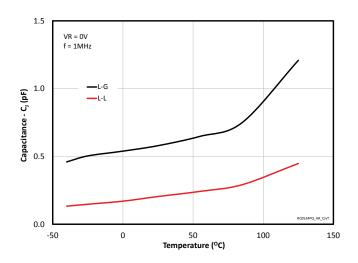

| Junction Capacitance                   | C,               | $V_{R} = 0V, f = 1MHz$<br>Any I/O pin to GND                | T = 25°C          |      | 0.4  | 0.8  | - pF  |

|                                        |                  |                                                             | T=125°C           |      | 1.2  | 1.5  |       |

|                                        |                  | V <sub>R</sub> = 0V, f = 1MHz<br>Between I/O pins           | T = 25°C          |      | 0.3  | 0.4  |       |

|                                        |                  |                                                             | T = 125°C         |      | 0.5  | 0.7  |       |

Notes:

(1): ESD Gun return path to Ground Reference Plane (GRP)

(2): ESD Gun return path to Horizontal Coupling Plane (HCP); Test conditions: 330 pF, 330 \Omega.

(3): Measured using an 8/20us constant current source.

(4): Transmission Line Pulse Test (TLP) Settings: tp = 100ns, tr = 0.2ns,  $I_{TLP}$  and  $V_{TLP}$  averaging window:  $t_1 = 70$ ns to  $t_2 = 90$ ns.

(5): Dynamic resistance calculated from  $I_{TLP} = 4A$  to  $I_{TLP} = 16A$

# **Typical Characteristics**

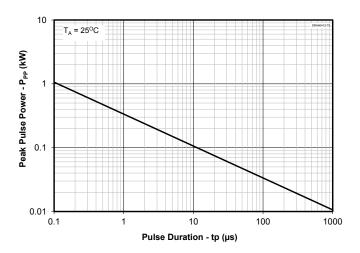

#### Non-Repetitive Peak Pulse Power vs. Pulse Time

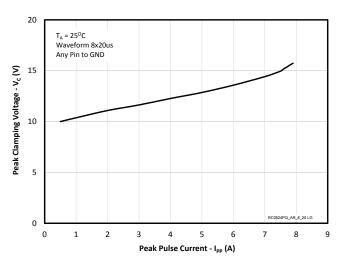

8/20us Surge Clamping Characteristic

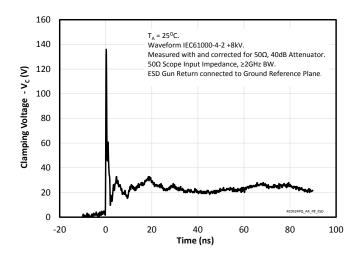

ESD Clamping (+8kV Contact per IEC 61000-4-2)

**TLP IV Curve (Positive Pulse)**

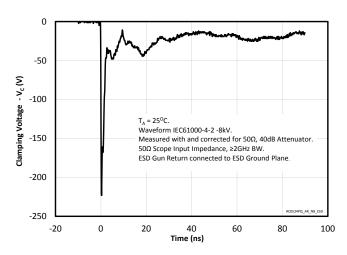

ESD Clamping (-8kV Contact per IEC 61000-4-2)

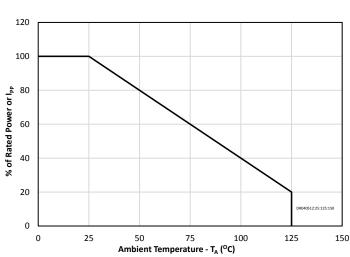

Power Derating Curve

RClamp0524PQ Final Datasheet Revision Date

# **Typical Characteristics (Continued)**

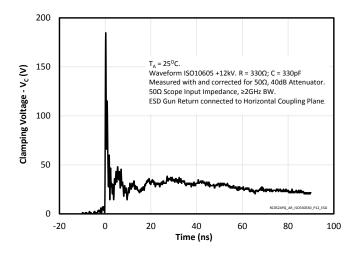

ESD Clamping (+12kV Contact per ISO-10605 330pF, 330Ω)

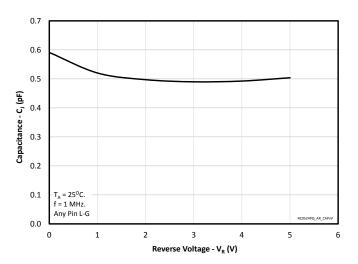

**Capacitance vs. Reverse Voltage**

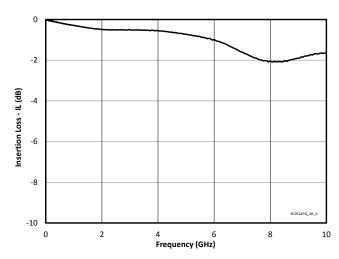

**Insertion Loss - S21**

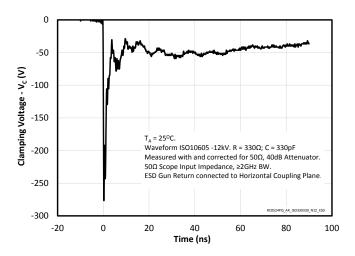

ESD Clamping (-12kV Contact per ISO-10605 330pF, 330Ω)

**Capacitance vs. Temperature**

Breakdown Voltage (VBR) vs. Temperature

#### RClamp0524PQ Final Datasheet Revision Date

## **Applications Information**

### **Assembly Guidelines**

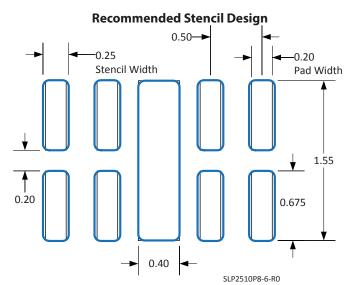

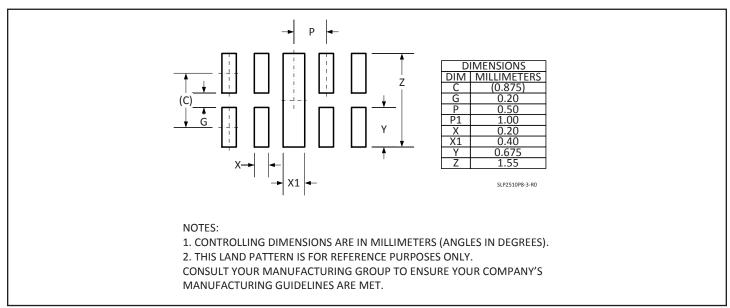

The small size of this device means that some care must be taken during the mounting process to insure reliable solder joint. The figure at the right details Semtech's recommended mounting pattern. Recommended assembly guidelines are shown in Table 2. Note that these are only recommendations and should serve only as a starting point for design since there are many factors that affect the assembly process. Exact manufacturing parameters will require some experimentation to get the desired solder application. Semtech's recommended mounting pattern is based on the following design guidelines:

#### **Land Pattern**

The recommended land pattern follows IPC standards and is designed for maximum solder coverage. Detailed dimensions are shown elsewhere in this document.

#### Solder Stencil

Stencil design is one of the key factors which will determine the volume of solder paste which is deposited onto the land pad. The area ratio of the stencil aperture will determine how well the stencil will print. The area ratio takes into account the aperture shape, aperture size, and stencil thickness. The area ratio of a rectangular aperture is given as:

Area Ratio = (L \* W) / (2 \* (L + W) \* T)

Where: L = Aperture Length W = Aperture Width T = Stencil Thickness

Semtech recommends a stencil thickness of 0.100mm - 0.125mm for this device. The stencil should be laser cut with electro-polished finish. The stencil should have a positive taper of approximately 5 degrees. Electro polishing and tapering the walls results in reduced surface friction and better paste release. Due to the small aperture size, a solder paste with Type 4 or smaller particles is recommended. Assuming a 125um thick stencil, the aperture dimensions shown will yield an area ratio of 0.72 for the small pads and 1.25 for the large.

| Table 2 - Recommended Assembly Guidelines |                               |  |  |  |

|-------------------------------------------|-------------------------------|--|--|--|

| Assembly Parameter                        | Recommendation                |  |  |  |

| Solder Stencil Design                     | Laser Cut, Electro-Polished   |  |  |  |

| Aperture Shape                            | Rectangular                   |  |  |  |

| Solder Stencil Thickness                  | 0.100mm (0.004″) -            |  |  |  |

|                                           | 0.125mm (0.005")              |  |  |  |

| Solder Paste Type                         | Type 4 size sphere or smaller |  |  |  |

| Solder Reflow Profile                     | Per JEDEC J-STD-020           |  |  |  |

| PCB Solder pad Design                     | Non-Solder Mask Defined       |  |  |  |

| PCB Pad Finish                            | OSP or NiAu                   |  |  |  |

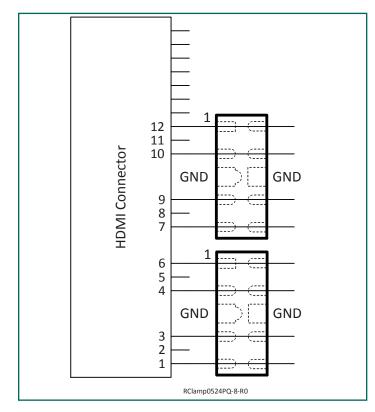

**Design Recommendations for HDMI Protection**

Adding external ESD protection to HDMI ports can be challenging. First, ESD protection devices have an inherent junction capacitance and adding even a small amount of capacitance will cause the impedance of the differential pair to drop. Second, large packages and land pattern requirements cause discontinuities that adversely affect signal integrity. The RClamp0524PQ is specifically designed for protection of high-speed interfaces such as HDMI. It presents <0.4pF capacitance between the pairs while being rated to handle  $>\pm 8kV$ ESD contact discharges (>±15kV air discharge) as outlined in IEC 61000-4-2. Each device is in a leadless SLP package that is less than 1.1mm wide. It is designed such that the traces flow straight through the device. The narrow package and flow-through design reduces discontinuities and minimizes impact on signal integrity. This becomes more critical as signal speeds increase.

# **Applications Information**

### **Pin Configuration**

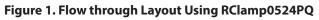

Figure 1 is an example of how to route the high speed differential traces through the RClamp0524PQ. The solid line represents the PCB trace. The PCB traces are used to connect the pin pairs for each line (pin 1 to pin 10, pin 2 to pin 9, pin 4 to pin 7, pin 5 to pin 6). For example, line 1 enters at pin 1 and exits at Pin 10 and the PCB trace connects pin 1 and 10 together. This is true for lines connected at pins 2, 4, and 5 also. Ground is connected at pins 3 and 8. One large ground pad should be used in lieu of two separate pads.

#### **TDR Measurements for HDMI**

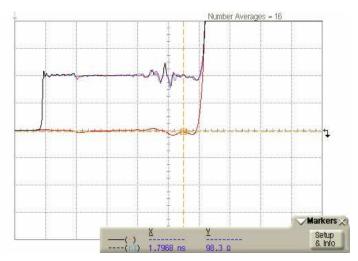

The combination of low capacitance, small package, and flow-through design means it is possible to use these devices to meet the HDMI impedance requirements of 100 Ohms  $\pm 15\%$  without any PCB board modification. Figure 3 shows a typical impedance test result for a TDR risetime of 200ps using a Semtech evaluation board with 100 Ohm traces throughout. Measurements were taken using a TDR method as outlined in the HDMI Compliance Test Specification (CTS). In each case, the device meets the HDMI CTS requirement of 100 Ohm  $\pm 15\%$  with plenty of margin (98.3 $\Omega$  at 1.79 ns).

Figure 2 - TDR Measurement with 200ps risetime using Semtech Evaluation Board

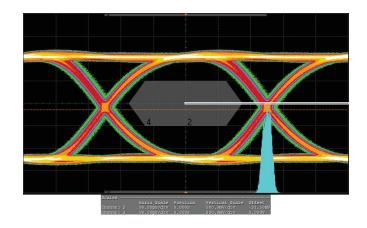

Figure 3 shows a typical HDMI 1.4 eye pattern at 1080p resolution. As shown there are no violations of the eye pattern with RClamp0524PQ in the circuit. The RClamp0524PQ may also be used to protect the remaining lines (I2C, CEC, and hot plug).

RClamp0524PQ Final Datasheet Revision Date

## **Applications Information**

### Layout Guidelines for Optimum ESD Protection

Good circuit board layout is critical not only for signal integrity, but also for effective suppression of ESD induced transients. For optimum ESD protection, the following guidelines are recommended:

- Place the device as close to the connector as possible. this practice restricts ESD coupling into adjacent traces and reduces parasitic inductance.

- The ESD transient return path to ground should be kept as short as possible. Whenever possible, use multiple micro vias connected directly from the device ground pad to the ground plane.

- Avoid running critical signals near board edges.

#### Figure 4. HDMI 1.4 Application using RClamp0524PQ

### **Outline Drawing - SLP2510P8**

### Land Pattern - SLP2510P8

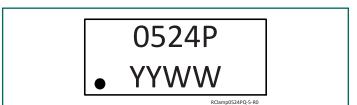

# **Marking Code**

Notes: Dot indicates pin 1 location

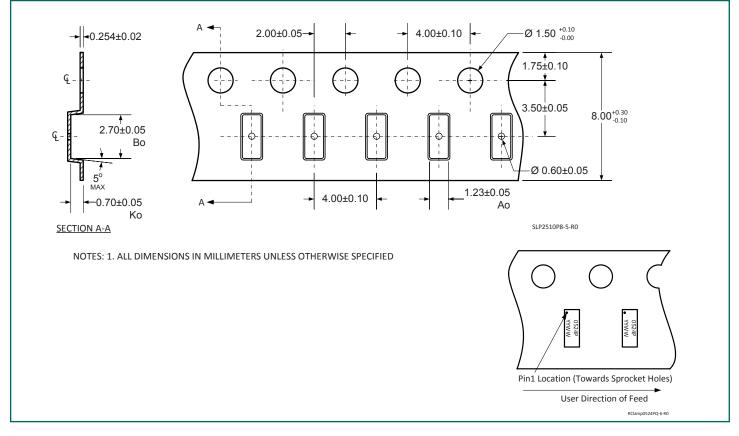

# **Tape and Reel Specification**

### **Ordering Information**

| Part Number     | Qty per Reel | Reel Size |

|-----------------|--------------|-----------|

| RClamp0524PQTCT | 3,000        | 7″        |

#### **IMPORTANT NOTICE**

Information relating to this product and the application or design described herein is believed to be reliable, however such information is provided as a guide only and Semtech assumes no liability for any errors in this document, or for the application or design described herein. Semtech reserves the right to make changes to the product or this document at any time without notice. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. Semtech warrants performance of its products to the specifications applicable at the time of sale, and all sales are made in accordance with Semtech's standard terms and conditions of sale.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS, OR IN NUCLEAR APPLICATIONS IN WHICH THE FAILURE COULD BE REASONABLY EXPECTED TO RESULT IN PERSONAL INJURY, LOSS OF LIFE OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

The Semtech name and logo are registered trademarks of the Semtech Corporation. All other trademarks and trade names mentioned may be marks and names of Semtech or their respective companies. Semtech reserves the right to make changes to, or discontinue any products described in this document without further notice. Semtech makes no warranty, representation or guarantee, express or implied, regarding the suitability of its products for any particular purpose. All rights reserved.

© Semtech 2015

#### **Contact Information**

Semtech Corporation 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111, Fax: (805) 498-3804 www.semtech.com

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Semtech: RCLAMP0524PQTCT