# MLX75024 Time-of-Flight Sensor Array

Datasheet

## Features & Benefits

- 1/3" optical Time-of-Flight sensor (optical area = 4.8 x 3.6 mm<sup>2</sup>)

- QVGA resolution, 320 x 240 pixels

- 15 x 15 µm DepthSense<sup>™</sup> pixels

- Demodulation frequency up to 40 MHz

- Two dual channel analog outputs

- Pixel rate up to 80 MSPS

- 960 us minimum image acquisition and readout time

- Gain modes for amplified signal

- 22% external quantum efficiency (850 nm wavelength)

- 13% external quantum efficiency (940 nm wavelength)

- Over 87% AC contrast (20 MHz modulation frequency)

- Over 85% AC contrast (40 MHz modulation frequency)

- Built-in temperature sensor

- Wafer level glass BGA package (Dimensions : 6.6 x 5.5 x 0.6 mm)

- AEC-Q100 qualified (grade 2)

- Ambient operating temperature ranges of -20 +85°C to -40 to +105°C

## Description

MLX75024 is an optical time-of-flight (TOF) image sensor. Potential use cases include gesture recognition, automotive in-cabin monitoring, surveillance, people counting and robot vision. The sensor features 320 x 240 (QVGA) time-of-flight pixels based on DepthSense® pixel technology. MLX75024 is the successor of MLX75023, with enhanced sensitivity and reduced power consumption. In combination with MLX75123BA, Melexis's dedicated ToF companion chip, the chipset provides a complete ToF sensor solution. The sensor is available in automotive and industrial grades, both in a small glass BGA wafer level package form factor which offers many integration possibilities.

Figure 1: MLX75024 top (left) and bottom (right)

# Contents

| Features & Benefits                                     | 1  |

|---------------------------------------------------------|----|

| Description                                             | 1  |

| 1. Datasheet Changelog                                  | 4  |

| 2. Glossary of terms                                    | 4  |

| 3. Ordering Information                                 | 5  |

| 4. Cover tape removal                                   | 5  |

| 5. Application System Architecture                      | 6  |

| 6. Pinout Description                                   | 7  |

| 7. Typical Connection Diagram                           | 8  |

| 8. Block diagram                                        | 9  |

| 9. Electrical Characteristics                           | 10 |

| 9.1. Absolute Maximum Ratings                           | 10 |

| 9.2. ESD Ratings                                        | 10 |

| 9.3. Digital IO Characteristics                         | 10 |

| 9.4. Current consumption in operating conditions        | 11 |

| 9.5. Dynamic Characteristics                            | 12 |

| 9.6. Temperature sensor characteristics                 | 12 |

| 9.7. Sensor Optical and Physical Characteristics        | 13 |

| 9.7.1. PDNU and PNNU global calculation                 | 13 |

| 9.7.2. PDNU and PNNU local calculation                  | 14 |

| 9.7.3. Demodulation contrast & ARRAYBIAS voltage        | 14 |

| 9.7.4. Demodulation contrast & R <sub>AB</sub>          | 15 |

| 9.7.5. Demodulation contrast & ARRAYBIAS current        | 15 |

| 9.7.6. Demodulation contrast & MIXH voltage             | 16 |

| 9.7.7. ARRAYBIAS voltage and current consumption        | 16 |

| 9.8. Signal Chain, Noise and Gain Modes Characteristics | 17 |

| 10. Device programming interface                        | 18 |

| 10.1. Configuration latches                             | 18 |

| 10.2. Signal Gain function                              | 19 |

| 10.3. Image flip & mirror modes                         | 19 |

| 11. Interface                                           | 20 |

| 11.1. Timing Diagrams                                   | 20 |

| 11.2. Power Up and Initialization                       | 22 |

| 11.3. Latch Programming22               |

|-----------------------------------------|

| 11.4. Reset                             |

| 11.5. Integration22                     |

| 11.6. Read-out                          |

| 11.7. Test Rows Specification           |

| 11.8. Test Columns Specification        |

| 12. Depth & Confidence Calculation      |

| 12.1. Correlation Measurement           |

| 12.2. Active Illumination               |

| 13. Package information                 |

| 13.1. Mechanical Dimensions             |

| 13.2. Moisture sensitivity level        |

| 13.3. PCB Footprint Recommendations31   |

| 13.4. PCB Trace Layout Recommendation32 |

| 13.5. Sensor Reflow Profile             |

| Disclaimer                              |

### **1. Datasheet Changelog**

| Version | Date        | Changes                                                                                                                                                                                                                                                       |

|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.10.6  | 13/Dec/2018 | Preliminary release version.                                                                                                                                                                                                                                  |

| 0.10.7  | 03/Jan/2019 | Addition of PDNU and PNNU formulas.                                                                                                                                                                                                                           |

| 1.0     | 09/Apr/2019 | ROI drawback related to gain mode updated.<br>MLX75123BA FLIP_MIRROR mode & temperature readout limitation added.                                                                                                                                             |

| 1.1     | 18/Apr/2019 | Change of the ARRAYBIAS current value without serial resistor.<br>Addition of Dem. Contrast VS ARRAYBIAS voltage & MIXH voltage graphs.                                                                                                                       |

| 1.2     | 02/Jan/2020 | Modification of chapter 10 with details on timings and updated description of the<br>different timing periods.<br>Several grammar corrections.<br>Addition of the DepthSense trademark disclaimer.<br>Updated shelf life duration for samples with covertape. |

| 1.3     | 23/Jul/2020 | Updated disclaimer.<br>Added covertape removal instructions.<br>Updated VDDD maximum current.                                                                                                                                                                 |

Table 1: Changelog

### 2. Glossary of terms

| Term                  | Definition                                                                                                                                                                                                                                     |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAPD                  | Current Assisted Photonic Demodulator.                                                                                                                                                                                                         |

| DC contrast           | Capability of the sensor to demodulate signals under a constant light source.                                                                                                                                                                  |

| AC contrast           | Capability of the sensor to demodulate signals under a modulated light source.                                                                                                                                                                 |

| Full well capacity    | Maximum number of electrons which can be collected on a single tap of the pixel.                                                                                                                                                               |

| T <sub>INT</sub>      | Integration time. Period of time when DMIX signals are toggling, illumination is activated and electrons are captured in the pixels.                                                                                                           |

| T <sub>COOLDOWN</sub> | Period of time after integration when illumination is off.                                                                                                                                                                                     |

| T <sub>READ</sub>     | Period of time required to readout the values of all the pixels of the array.                                                                                                                                                                  |

| PDNU                  | Pixel depth non uniformity. This metric is calculated on a depth map generated from the sensor's output data. It defines how much deviation is present between pixels (in distance) for a flat field measurement. PDNU is expressed in [m].    |

| PNNU                  | Pixel norm non uniformity. This metric is calculated on a norm/confidence map generated from the sensor's output data. It defines how much contrast difference is present between pixels for a flat field measurement. PNNU is expressed in %. |

Table 2: Glossary of terms

# **3. Ordering Information**

```

Ordering example: MLX75024RTF-GAA-001-TR<sup>1</sup>

```

| Product  | Temperature Code | Package | Option Code | Packing Form |

|----------|------------------|---------|-------------|--------------|

| MLX75024 | R                | TF      | GAA-000     | TR           |

| MLX75024 | S                | TF      | GAA-000     | TR           |

| MLX75024 | R                | TF      | GAA-001     | TR           |

| MLX75024 | S                | TF      | GAA-001     | TR           |

Table 3: Product ordering code(s)

#### Legend:

| Temperature Code | R : -40°C to 105°C<br>S : -20°C to 85°C                                |

|------------------|------------------------------------------------------------------------|

| Package Code     | TF : Glass BGA Package, 44pins                                         |

| Option Code      | GAA-000 : without cover tape<br>GAA-001 : with cover tape <sup>2</sup> |

| Packing Form     | TR : Tray                                                              |

Table 4: Option code(s)

### 4. Cover tape removal

Covertape is used to protect the optical sensor array after testing at Melexis from scratches or contamination during shipment to customer. It is strongly recommended to avoid any horizontal movement to protect the optical sensor from glue residues.

Figure 2: Grab the flag of the covertape and peel it off in an angle of 180° as much as possible.

<sup>&</sup>lt;sup>1</sup> Parts with covertape are now standard delivery versions.

<sup>&</sup>lt;sup>2</sup> The properties of the covertape are guaranteed for 1 year after shipping date considering the devices are stored in appropriate conditions according the device MSL rating.

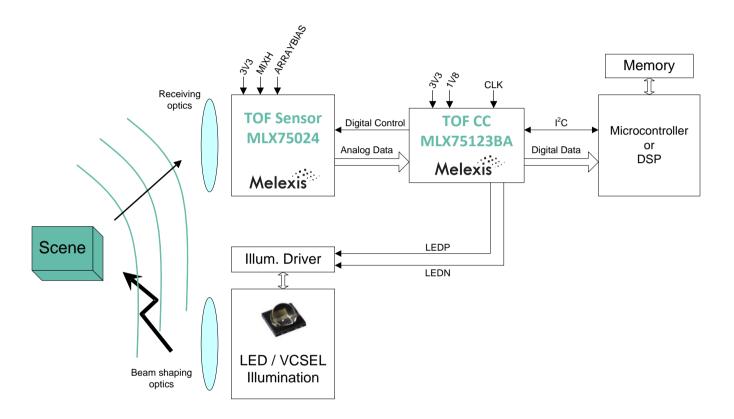

### **5. Application System Architecture**

A complete TOF system or camera module typically includes the following main components:

- MLX75123 + MLX75024 TOF chipset

- An infrared (NIR) illumination source (LED or laser) with fast response and relaxation time.

- Beam shaping optics for the light distribution

- A receiving sensor lens, optimized for maximum NIR transmittance

- A microcontroller or DSP to calculate and process the data

Figure 3: System architecture

# 6. Pinout Description

| Designator                                                                                                   | Pin #                                              | Function                        | Description                                                                                              |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------|

| ROW[7]<br>ROW[6]<br>ROW[5]<br>ROW[4]<br>ROW[3]<br>ROW[2]<br>ROW[1]<br>ROW[0]                                 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8               | Digital Input                   | These inputs are used to apply the pixel row address of the pixel array controlled by the MLX75123BA.    |

| ARRAYBIAS                                                                                                    | 9                                                  | Voltage Bias                    | Negative bias voltage.                                                                                   |

| PIXELVDD                                                                                                     | 10                                                 | Pixel voltage pin               | Internally regulated pixel supply voltage pin.                                                           |

| VDDA                                                                                                         | 11                                                 | Analog Supply                   |                                                                                                          |

| AGND                                                                                                         | 12                                                 | Ground                          |                                                                                                          |

| OUT3                                                                                                         | 13                                                 | Analog Output                   |                                                                                                          |

| OUT2                                                                                                         | 14                                                 | Analog Output                   |                                                                                                          |

| OUT0                                                                                                         | 15                                                 | Analog Output                   |                                                                                                          |

| OUT1                                                                                                         | 16                                                 | Analog Output                   |                                                                                                          |

| LATCH_ENABLE                                                                                                 | 17                                                 | Digital Input                   | Enables the configuration of the sensor. Active high.                                                    |

| –<br>PIXELFLUSH                                                                                              | 18                                                 | Digital Input                   | Control to clear charges in pixels. Active low.                                                          |

| CORE_RESET                                                                                                   | 19                                                 | Digital Input                   | Detector reset signal.                                                                                   |

| SHUTTER                                                                                                      | 20                                                 | Digital Input                   | Enable global shutter.                                                                                   |

| CS                                                                                                           | 21                                                 | Digital Input                   | Chip select. Active High.                                                                                |

| DGND                                                                                                         | 22                                                 | Ground                          | entre englished and                                                                                      |

| VDDD<br>COLUMN[0]<br>COLUMN[1]<br>COLUMN[2]<br>COLUMN[3]<br>COLUMN[4]<br>COLUMN[5]<br>COLUMN[6]<br>COLUMN[7] | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31 | Digital Supply<br>Digital Input | These inputs are used to apply the pixel column address of the pixel array controlled by the MLX75123BA. |

| DGND                                                                                                         | 32                                                 | Ground                          |                                                                                                          |

| VDDD                                                                                                         | 33                                                 | Digital Supply                  |                                                                                                          |

| DMIX[1]<br>DMIX[0]                                                                                           | 34<br>35                                           | Digital Input                   | Modulation signals. Active High. Pulled-down internally.                                                 |

| DGND                                                                                                         | 36                                                 | Ground                          |                                                                                                          |

| MIXH                                                                                                         | 37                                                 | Supply                          | Supply voltage for the demodulator                                                                       |

| MIXH                                                                                                         | 38                                                 | Supply                          | Supply voltage for the demodulator                                                                       |

| DGND                                                                                                         | 39                                                 | Ground                          |                                                                                                          |

| DGND                                                                                                         | 40                                                 | Ground                          |                                                                                                          |

| MIXH                                                                                                         | 41                                                 | Supply                          | Supply voltage for the demodulator                                                                       |

| MIXH                                                                                                         | 42                                                 | Supply                          | Supply voltage for the demodulator                                                                       |

| DGND                                                                                                         | 43                                                 | Ground                          |                                                                                                          |

| VDDD                                                                                                         | 44                                                 | Digital Supply                  |                                                                                                          |

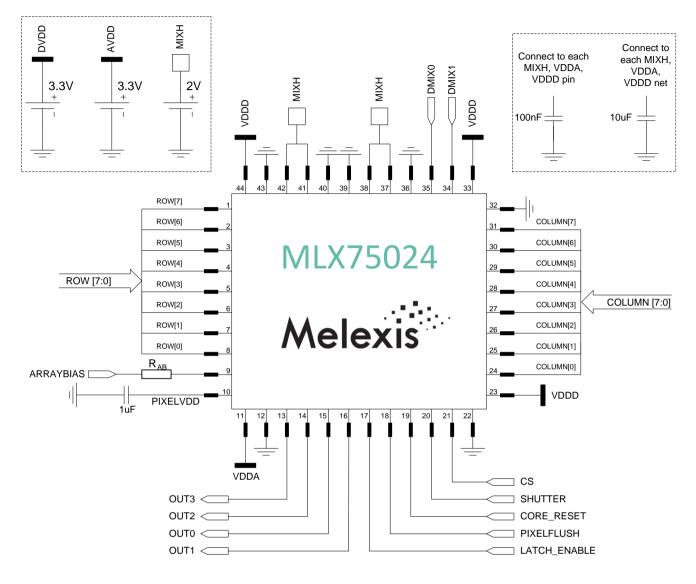

### 7. Typical Connection Diagram

Figure 4: Typical connection diagram<sup>3</sup>

$<sup>^{3}</sup>$  R<sub>AB</sub> value will influence the demodulation contrast of the sensor. Please refer to chapters 9.7.3, 9.7.4 and 9.7.5 for additional information. The performance of the MLX75024 has been tested with 68 $\Omega$  resistor for R<sub>AB</sub> and -3.3V for the ARRAYBIAS voltage.

MLX75024 Time-of-Flight Sensor Array Datasheet

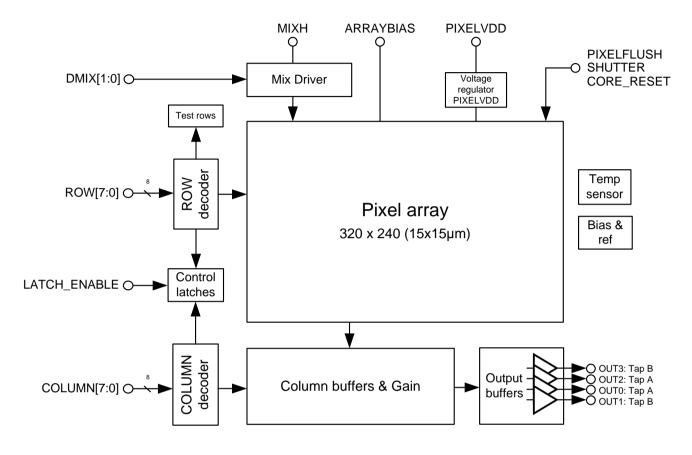

# 8. Block diagram

Figure 5: MLX75024 block diagram

# 9. Electrical Characteristics

#### 9.1. Absolute Maximum Ratings

Absolute maximum ratings must not be exceeded to prevent permanent damage to the device. The device is not guaranteed to be functional while applying the absolute maximum stress.

| Parameter             | Symbol            | Min. | Max. | Unit |

|-----------------------|-------------------|------|------|------|

| 3V3 DC input voltages | V <sub>DDX</sub>  | -0.3 | 4.5  | V    |

| MIXH input voltage    | V <sub>MIXH</sub> |      | 2.5  | V    |

| Storage temperature   | T <sub>stg</sub>  | -50  | 125  | °C   |

| Junction temperature  | T,                |      | 125  | °C   |

Table 6: Absolute maximum ratings

#### 9.2. ESD Ratings

| Parameter                                                                                   | Symbol               | Max.   | Unit |

|---------------------------------------------------------------------------------------------|----------------------|--------|------|

| Electrostatic discharge, human-body model (HBM)<br>according to AEC-Q100-002                | V <sub>ESD_HBM</sub> | ± 2000 | V    |

| Electrostatic discharge, charged-device model (CDM),<br>according to ANSI/ESDA/JEDEC JS-002 | $V_{ESD\_CDM}$       | ±500   | V    |

Table 7: ESD ratings

### 9.3. Digital IO Characteristics

| Parameter                          | Symbol            | Min.           | Тур. | Max.                 | Unit |

|------------------------------------|-------------------|----------------|------|----------------------|------|

| Digital input threshold level high | V <sub>IH</sub>   | $0.7* V_{DDD}$ |      |                      | V    |

| Digital input threshold level low  | V <sub>IL</sub>   |                |      | $0.3*V_{\text{DDD}}$ | V    |

| Input hysteresis                   | $V_{\text{HYST}}$ | 0.5            |      |                      | V    |

| Digital input leakage current      | I <sub>DIN</sub>  |                |      | 1                    | μΑ   |

| Digital input pin capacitance      | C <sub>DIN</sub>  |                |      | 10                   | pF   |

| Pull down resistor at DMIX         | $R_{PD_MIX}$      |                | 50   |                      | kΩ   |

Table 8: Digital IO characteristics

### 9.4. Current consumption in operating conditions

If not mentioned, typical conditions for measurement of the following values are:  $V_{DDA} = 3.3V$ ,  $V_{DDD} = 3.3V$ , ambient temperature = 27°C.

| Parameter                     | Condition                                                        | Symbol                              | Min. | Тур. | Max. | Unit |

|-------------------------------|------------------------------------------------------------------|-------------------------------------|------|------|------|------|

| VDDA supply voltage           |                                                                  | V <sub>DDA</sub>                    | 3.0  | 3.3  | 3.6  | V    |

| VDDA supply current           | Integration                                                      | I_VDDA <sub>INTEGRATION_CS_H</sub>  |      | 38   |      | mA   |

| VDDA supply current           | Readout, OUT_SR_2X = 0 <sup>4</sup>                              | I_VDDA <sub>READOUT_SR_L</sub>      |      | 47   |      | mA   |

| VDDA supply current           | Readout, OUT_SR_2X = 1 <sup>4</sup>                              | I_VDDA <sub>READOUT_SR_H</sub>      |      | 70   |      | mA   |

| VDDA supply current           | Readout, CS low                                                  | I_VDDA <sub>READOUT_CS_L</sub>      |      | 22   |      | mA   |

| VDDA supply current           | POWER_DOWN                                                       | I_VDDA <sub>POWER_DOWN</sub>        |      | 15   |      | uA   |

| VDDD supply voltage           |                                                                  | V <sub>DDD</sub>                    | 3.0  | 3.3  | 3.6  | V    |

| VDDD supply current           | During Idle time, before<br>or after readout                     |                                     |      | 2    |      | μΑ   |

| VDDD supply current           | Integration,<br>$f_{MIX}$ = 20 MHz                               | I_VDDD <sub>INTEGRATION_20MHZ</sub> |      | 8    | 10   | mA   |

| VDDD supply current           | Integration,<br>f <sub>MIX</sub> = 40 MHz                        | I_VDDD <sub>INTEGRATION_40MHZ</sub> |      | 16   | 30   | mA   |

| VDDD supply current           | Readout                                                          | I_VDDD <sub>READOUT</sub>           |      | 300  |      | uA   |

| ARRAYBIAS supply voltage      |                                                                  | V <sub>ArrayBias</sub>              | -5   | -3.3 | 0    | V    |

| ARRAYBIAS supply current      | $V_{MIXH} = 2V,$<br>$V_{ArrayBias} = -3.3V$<br>$68\Omega R_{AB}$ | I <sub>ArrayBias</sub>              |      | 17   |      | mA   |

| MIXH supply voltage           |                                                                  | V <sub>MIXH</sub>                   | 1.5  | 2    | 2.5  | V    |

| MIXH supply current           | Integration, $V_{MIXH} = 1.5V$                                   | I <sub>MIXH_1.5V</sub>              |      | 480  | 900  | mA   |

| MIXH supply current           | Integration, $V_{MIXH} = 2V$                                     | I <sub>MIXH_2.0V</sub>              |      | 720  | 1000 | mA   |

| MIXH supply current           | Integration, $V_{MIXH} = 2.5V$                                   | I <sub>MIXH_2.5V</sub>              |      | 760  | 1100 | mA   |

| PIXELVDD voltage <sup>5</sup> | GAIN_CTRL = 00b                                                  | $PIX_{VDD}_{GAIN1}$                 |      | 2.85 |      | V    |

| PIXELVDD voltage <sup>5</sup> | GAIN_CTRL = 11b                                                  | $PIX_{VDD\_GAIN\_bypass}$           |      | 2.7  |      | V    |

Table 9: Current consumption table in operation conditions

$<sup>^4</sup>$  See 10.1 for additional information about the slew rate parameter.

$<sup>^{\</sup>rm 5}$  PIXELVDD is non usable as a voltage output pin.

### 9.5. Dynamic Characteristics

| Parameter                                    | Condition                     | Symbol                       | Min. | Тур. | Max.            | Unit |

|----------------------------------------------|-------------------------------|------------------------------|------|------|-----------------|------|

| Column addressing frequency                  | $OUT_SR_2X = 0^6$             | $\mathbf{f}_{\text{COLUMN}}$ |      |      | 25 <sup>7</sup> | MSPS |

| Column addressing frequency                  | $OUT_SR_2X = 1^7$             | $\mathbf{f}_{\text{COLUMN}}$ |      |      | 40              | MSPS |

| Row addressing frequency                     |                               | $f_{\text{ROW}}$             |      |      | 0.5             | MSPS |

| DMIX frequency                               |                               | f <sub>MIX</sub>             |      | 20   | 40              | MHz  |

| Delay row/column to analog output<br>settled | $OUT_SR_2X = 0^6$             | $t_{VAL}$                    |      | 26   | 30              | ns   |

| Delay row/column to analog output<br>settled | $OUT_SR_2X = 1^7$             | $t_{VAL}$                    |      | 18.2 | 25              | ns   |

| Output ready after CS high                   |                               | $T_{\text{SETTLE}}$          |      |      | 60              | ns   |

| OUTx output swing                            |                               | RANGEOUT                     |      | 1.55 |                 | V    |

| OUTx output voltage                          |                               | V <sub>OUT</sub>             | 0    |      | 1.9             | V    |

| OUTx load capacitance                        | $OUT_DRIVE_2X = 0^8$          | C <sub>OUT</sub>             |      |      | 20              | pF   |

| OUTx load capacitance                        | OUT_DRIVE_2X = 1 <sup>8</sup> | C <sub>OUT</sub>             |      |      | 40              | pF   |

Table 10: Dynamic characteristics

#### 9.6. Temperature sensor characteristics

| Parameter                               | Condition                     | Symbol                    | Min.  | Тур.  | Max. | Unit |

|-----------------------------------------|-------------------------------|---------------------------|-------|-------|------|------|

| Gain of temperature sensor              |                               | K <sub>ptat</sub>         | 1.74  | 1.79  | 1.85 | mV/K |

| Differential PTAT output voltage        | Calibrated at 35°C            | V <sub>PTAT</sub>         |       | 563.5 |      | mV   |

| Temperature error with 35°C calibration | T <sub>JUNCTION</sub> = 35°C  | ERROR <sub>TEMP_35</sub>  | -3.00 |       | 3.00 | К    |

| Temperature error with 35°C calibration | T <sub>JUNCTION</sub> = 85°C  | ERROR <sub>TEMP_85</sub>  | -4.80 |       | 4.80 | К    |

| Temperature error with 35°C calibration | T <sub>JUNCTION</sub> = 105°C | ERROR <sub>TEMP_105</sub> | -5.50 |       | 5.50 | К    |

| Temperature error with 35°C calibration | $T_{JUNCTION} = 0^{\circ}C$   | $ERROR_{TEMP_0}$          | -4.10 |       | 4.10 | К    |

| Temperature error with 35°C calibration | $T_{JUNCTION} = -40^{\circ}C$ | ERROR <sub>TEMP40</sub>   | -5.50 |       | 5.50 | К    |

Table 11: Temperature sensor characteristics

<sup>&</sup>lt;sup>6</sup> See chapter 10.1 for additional information about the slew rate.

<sup>&</sup>lt;sup>7</sup> High slew rate (OUT\_SR\_2X) must be used in case of 25 MSPS <  $f_{COL}$  < 40 MSPS. This will increase the power consumption of the sensor. See Table 9 for power consumption values. Setting OUT\_DRIVE\_2X = 1 and OUT\_SR\_2X = 1 at the same time will only enable high slew rate mode without affecting the driving capability of the output buffer. OUT\_DRIVE\_2X should be set to zero when enabling high slew rate mode to reduce the power consumption of the sensor.

<sup>&</sup>lt;sup>8</sup> See chapter 10.1 for additional information about the driving capability of the output buffer.

### 9.7. Sensor Optical and Physical Characteristics

| Parameter                      | Symbol                           | Condition                         | Min. | Тур.              | Max. | Unit |

|--------------------------------|----------------------------------|-----------------------------------|------|-------------------|------|------|

| External quantum<br>efficiency | EQE <sub>850</sub>               | 850 nm                            |      | 23                |      | %    |

| External quantum<br>efficiency | EQE <sub>940</sub>               | 940 nm                            |      | 13                |      | %    |

| DC contrast                    | C <sub>DC_850</sub>              | 850 nm                            |      | 95                |      | %    |

| AC contrast                    | <b>C</b> <sub>AC_850_20MHz</sub> | 850 nm, f <sub>MIX</sub> = 20 MHz |      | 87                |      | %    |

| AC contrast                    | <b>C</b> <sub>AC_850_40MHz</sub> | 850 nm, f <sub>MIX</sub> = 40 MHz |      | 85                |      | %    |

| DC contrast                    | C <sub>DC_940</sub>              | 940 nm                            |      | 95                |      | %    |

| AC contrast                    | <b>C</b> <sub>AC_940_20MHz</sub> | 940 nm, f <sub>MIX</sub> = 20 MHz |      | 87                |      | %    |

| AC contrast                    | <b>C</b> <sub>AC_940_40MHz</sub> | 940 nm, f <sub>MIX</sub> = 40 MHz |      | 85                |      | %    |

| Full well capacity             | $FWC_{GAIN\_bypass}$             | GAIN_CTRL = 11b                   |      | 458               |      | ke-  |

| Full well capacity             | $FWC_{GAIN_1}$                   | GAIN_CTRL = 00b                   |      | 483               |      | ke-  |

| Full well capacity             | $FWC_{GAIN_2}$                   | GAIN_CTRL = 01b                   |      | 246               |      | ke-  |

| Full well capacity             | $FWC_{GAIN_3}$                   | GAIN_CTRL = 10b                   |      | 137               |      | ke-  |

| PDNU local                     | PDNULOCAL_20MHZ                  | 20 MHz                            |      | 0.38              |      | cm   |

| PDNU global                    | PDNU <sub>GLOBAL_20MHZ</sub>     | 20 MHz                            |      | 7.41 <sup>9</sup> |      | cm   |

| PDNU local                     | PDNULOCAL_40MHZ                  | 40 MHz                            |      | 0.34              |      | cm   |

| PDNU global                    | PDNU <sub>GLOBAL_40MHZ</sub>     | 40 MHz                            |      | 9.59 <sup>9</sup> |      | cm   |

| PNNU local                     | PNNULOCAL_20MHZ                  | 20 MHz                            |      | 1.2               |      | %    |

| PNNU global                    | PNNU <sub>GLOBAL_20MHZ</sub>     | 20 MHz                            |      | 7                 |      | %    |

| PNNU local                     | PNNULOCAL_40MHZ                  | 40 MHz                            |      | 1.05              |      | %    |

| PNNU global                    | PNNU <sub>GLOBAL_40MHZ</sub>     | 40 MHz                            |      | 11.9              |      | %    |

Table 12: Optical & physical characteristics

#### 9.7.1. PDNU and PNNU global calculation

PDNU global and PNNU global are metrics calculated by dividing the image in blocks of 10 by 10 pixels and calculating the mean distance and mean norm values of these blocks.

PDNU will be the difference of the maximum and the minimum mean value of the distance of the blocks. It is expressed in centimetres.

PNNU will be the difference of the maximum and the minimum mean value of the amplitude of the blocks, divided by the mean of the complete image. It is expressed in percent.

<sup>&</sup>lt;sup>9</sup> This value is for uncalibrated distance map. This non uniformity is constant for each device and can be calibrated.

#### 9.7.2. PDNU and PNNU local calculation

PDNU local and PNNU local are using 3 by 3 pixels cells, a pixel and its neighbours. For every 3 by 3 pixels cluster (there are 8480 clusters of 3 by 3 pixels on a QVGA image) two factors are calculated:

$$Dn = \frac{\sum_{i=1}^{9} (CONFIDENCE_i - AVERAGE(CONFIDENCE[3 \times 3]))^2}{9}$$

$$Dp = \frac{\sum_{i=1}^{9} (Phase_i - AVERAGE(Phase[3 \times 3]))^2}{9}$$

Then:  $PDNU_{LOCAL} = \sqrt{\frac{\sum_{j=1}^{8480} Dp_j}{8480}}$  and  $PNNU_{LOCAL} = \sqrt{\frac{\sum_{j=1}^{8480} Dn_j}{8480}}$

#### 9.7.3. Demodulation contrast & ARRAYBIAS voltage

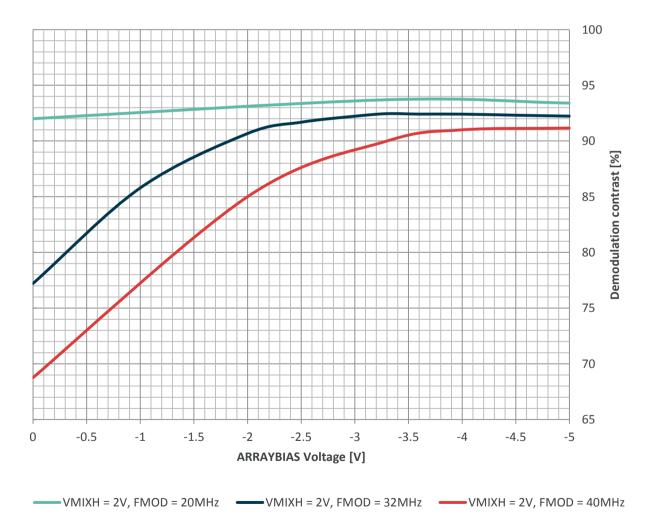

# Figure 6: Typical demodulation contrast versus V<sub>ArrayBias</sub> at 25°C, 2V V<sub>MIXH</sub> and 68 Ohm R<sub>AB</sub> with three different modulation frequencies.

#### 9.7.4. Demodulation contrast & RAB

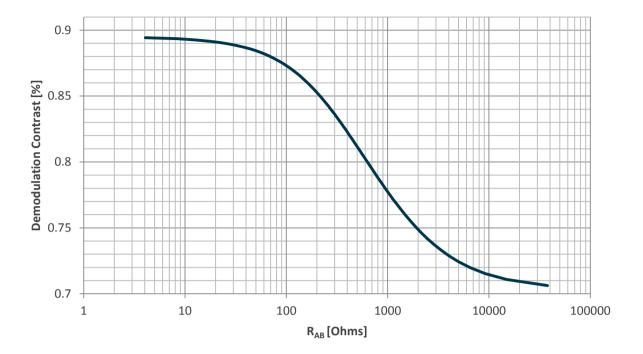

Figure 7: Typical demodulation contrast versus  $R_{AB}$  resistor at 25°C, 2V  $V_{MIXH}$ , 40 MHz modulation frequency and -3.3 ARRAYBIAS voltage.

#### 9.7.5. Demodulation contrast & ARRAYBIAS current

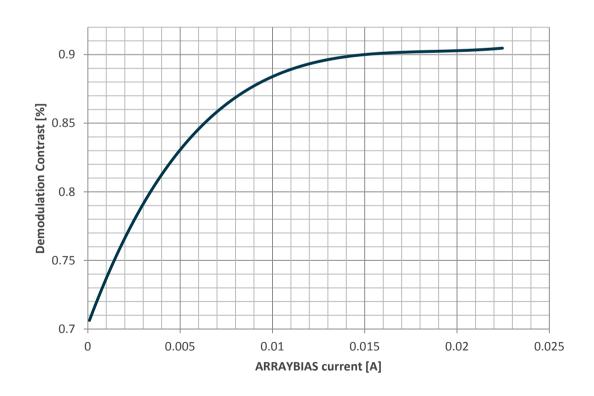

Figure 8: Typical demodulation contrast versus ARRAYBIAS current at 25 °C, 2V V<sub>MIXH</sub> and 68 Ohm R<sub>AB</sub>, 40 MHz modulation frequency and -3.3 ARRAYBIAS voltage.

#### 9.7.6. Demodulation contrast & MIXH voltage

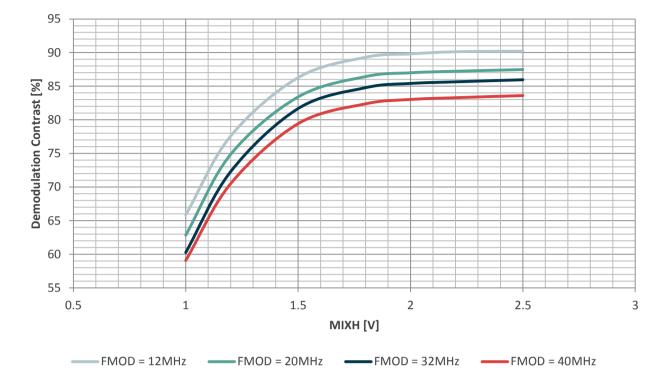

Figure 9: Typical demodulation contrast versus  $V_{MIXH}$  at 25°C, -3V3  $V_{ArrayBias}$  and 68 Ohm  $R_{AB}$  with 4 different modulation frequencies.

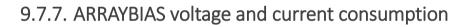

Figure 10: Typical current consumption on the ARRAYBIAS pin depending on the ARRAYBIAS voltage applied.

### 9.8. Signal Chain, Noise and Gain Modes Characteristics

| Parameter           | Symbol                        | Condition        | Min. | Тур. | Max. | Unit  |

|---------------------|-------------------------------|------------------|------|------|------|-------|

| Camera gain         | C_GAIN <sub>GAIN_bypass</sub> | GAIN_CTRL = 11b  |      | 3.47 |      | uV/e- |

| Camera gain         | $C_{GAIN_{GAIN_1}}$           | GAIN_CTRL = 00b  |      | 3.2  |      | uV/e- |

| Camera gain         | $C_GAIN_{GAIN_2}$             | GAIN _CTRL = 01b |      | 5.9  |      | uV/e- |

| Camera gain         | $C_GAIN_{GAIN_3}$             | GAIN _CTRL = 10b |      | 10.3 |      | uV/e- |

| Dark voltage        | V_DARK <sub>GAIN_bypass</sub> | GAIN _CTRL = 11b |      | 1.75 |      | V     |

| Dark voltage        | $V_DARK_{GAIN_1}$             | GAIN _CTRL = 00b |      | 1.7  |      | V     |

| Dark voltage        | $V_DARK_{GAIN_2}$             | GAIN _CTRL = 01b |      | 1.65 |      | V     |

| Dark voltage        | $V_DARK_{GAIN_3}$             | GAIN _CTRL = 10b |      | 1.55 |      | V     |

| Bright voltage      | $V\_BRIGHT_{GAIN\_bypass}$    | GAIN _CTRL = 11b |      | 0.2  |      | V     |

| Bright voltage      | $V\_BRIGHT_{GAIN\_1}$         | GAIN _CTRL = 00b |      | 0.2  |      | V     |

| Bright voltage      | $V\_BRIGHT_{GAIN_2}$          | GAIN _CTRL = 01b |      | 0.2  |      | V     |

| Bright voltage      | $V\_BRIGHT_{GAIN_3}$          | GAIN _CTRL = 10b |      | 0.2  |      | V     |

| Analog output swing | $SWING_{GAIN\_bypass}$        | GAIN _CTRL = 11b |      | 1.55 |      | V     |

| Analog output swing | $SWING_{GAIN_1}$              | GAIN _CTRL = 00b |      | 1.5  |      | V     |

| Analog output swing | $SWING_{GAIN_2}$              | GAIN _CTRL = 01b |      | 1.45 |      | V     |

| Analog output swing | $SWING_{GAIN_3}$              | GAIN _CTRL = 10b |      | 1.35 |      | V     |

| Dark noise          | $DN_{GAIN\_bypass}$           | GAIN _CTRL = 11b |      | 130  |      | e-    |

| Dark noise          | $DN_{GAIN_1}$                 | GAIN _CTRL = 00b |      | 156  |      | e-    |

| Dark noise          | $DN_{GAIN_2}$                 | GAIN _CTRL = 01b |      | 135  |      | e-    |

| Dark noise          | $DN_{GAIN_3}$                 | GAIN _CTRL = 10b |      | 128  |      | e-    |

Table 13 : Signal chain, noise and gain modes characteristics.

### **10. Device programming interface**

### 10.1. Configuration latches

LATCH\_ENABLE allows to program latches which control the general behaviour of the circuitry.

When LATCH\_ENABLE is set to high, the ROW[7:0] and COLUMN[7:0] inputs are the latch inputs.

There exist 16 latches (8 on the row address lines and 8 on the column lines) which generally configure some functions of the device. The definition of the latches inputs are described in the following tables:

| Latch input | Function                                                          | Function name   |

|-------------|-------------------------------------------------------------------|-----------------|

| ROW[0]      | Power down mode of the image sensor                               | POWER_DOWN      |

| ROW[1]      | Columns 0 to 3 and 316 to 319 will be replaced by the test pixels | TEST_COLUMN_OUT |

| ROW[2]      | GAIN control bit 0                                                | GAIN_CTRL<0>    |

| ROW[3]      | GAIN control bit 1                                                | GAIN_CTRL<1>    |

| ROW[4]      | High power mode of analog output buffer <sup>10</sup>             | OUT_DRIVE_2X    |

| ROW[5]      | High slew rate mode of analog output buffer <sup>11</sup>         | OUT_SR_2X       |

| ROW[6]      | Reserved – Set to zero                                            | Reserved        |

| ROW[7]      | Power down mode of the image sensor                               | POWER_DOWN      |

#### Table 14: Column Latch definition table

| Latch input | Function                                         | Function name  |

|-------------|--------------------------------------------------|----------------|

| COLUMN[0]   | Reserved – Set to zero                           | Reserved       |

| COLUMN[1]   | Reserved – Set to zero                           | Reserved       |

| COLUMN[2]   | Reserved – Set to zero                           | Reserved       |

| COLUMN[3]   | Reserved – Set to zero                           | Reserved       |

| COLUMN[4]   | Reserved – Set to zero                           | Reserved       |

| COLUMN[5]   | Shall be set to 1 when reading rows backward.    | REVERSE_ROW    |

| COLUMN[6]   | Reset and initialization                         | INIT           |

| COLUMN[7]   | Shall be set to 1 when reading columns backward. | REVERSE_COLUMN |

Table 15: Row Latch definition table

<sup>&</sup>lt;sup>10</sup> OUT\_DRIVE\_2X is used to double the driving capability of the output buffer in order to be able to drive 40 pF load compared to standard 20 pF load. It is necessary in situations where one MLX75123 companion chip is driving 2 MLX75024 sensors where PCB trace load is expected to be higher than in standard mode.

<sup>&</sup>lt;sup>11</sup> High slew rate (OUT\_SR\_2X) must be used in case of 25 MSPS <  $f_{COL}$  < 40 MSPS. This will increase the power consumption of the sensor. See Table 9 for power consumption values. Setting OUT\_DRIVE\_2X = 1 and OUT\_SR\_2X = 1 at the same time will only enable high slew rate mode without affecting the driving capability of the output buffer. OUT\_DRIVE\_2X should be set to zero when enabling high slew rate mode to reduce the power consumption of the sensor.

### 10.2. Signal Gain function

The MLX75024 features an active gain of the pixel output signal. ROW[3:2] = GAIN\_CTRL[1:0] enables the gain settings:

- GAIN\_CTRL[1:0] = 00b: GAIN\_Mode = 1

- GAIN\_CTRL[1:0] = 01b: GAIN\_Mode = 2

- GAIN\_CTRL[1:0] = 10b: GAIN\_Mode = 3

- GAIN\_CTRL[1:0] = 11b: Gain function is bypassed or GAIN\_Bypass = 1

Changing the gain setting of the signal path will change the camera gain and dynamic range of the sensor. The affected performance parameters of the GAIN\_CTRL setting are listed in Table 12 and Table 13.

Based on application conditions the following setting can be applied:

- GAIN\_Bypass = 1 bypasses the active gain signal path. The mode has the best performance in regards to noise and signal range but the fixed pixel to pixel variance of the dark voltage is higher than for GAIN\_MODE =1.

- GAIN\_Mode = 1 sets the active gain of the pixel signal to one. The fixed pixel to pixel variance of the dark voltage is lower but the noise is slightly higher than for GAIN\_Bypass = 1 (refer to Table 12 and Table 13). The GAIN\_Mode = 1 is the preferred operating mode.

- GAIN\_MODE = 2 and GAIN\_MODE = 3 increases the camera gain but decreases the dynamic range. Due to the increased camera gain the impact of disturbances and noise in the signal path including ADC is lowered. The system is more perceptive to dark objects but less robust in regards to sunlight.

### 10.3. Image flip & mirror modes

The MLX75024 has specific features to cope with the flip and mirror modes of the MLX7513BA companion chip. COLUMN[5] and COLUMN[7] enables the REVERSE\_ROW and REVERSE\_COLUMN functions. Correct settings of the MLX75024 & MLX75123BA are explained in the table below:

| MLX75123BA<br>function          | MLX75123BA<br>Tx_FLIP_MIRROR value | MLX75024 corresponding<br>function | MLX75123BA corresponding<br>Tx_Bx_LATCH value |

|---------------------------------|------------------------------------|------------------------------------|-----------------------------------------------|

| FLIP (along<br>horizontal axis) | 2'b01                              | REVERSE_ROW                        | 0x2000                                        |

| MIRROR (along vertical axis)    | 2'b10                              | REVERSE_COLUMN                     | 0x8000                                        |

| FLIP & MIRROR                   | 2'b11                              | REVERSE_ROW &<br>REVERSE_COLUMN    | 0xA000                                        |

When using FLIP & MIRROR mode, there is no possibility of reading out the MLX75024 temperature data using the MetaData.

# **11. Interface**

### **11.1. Timing Diagrams**

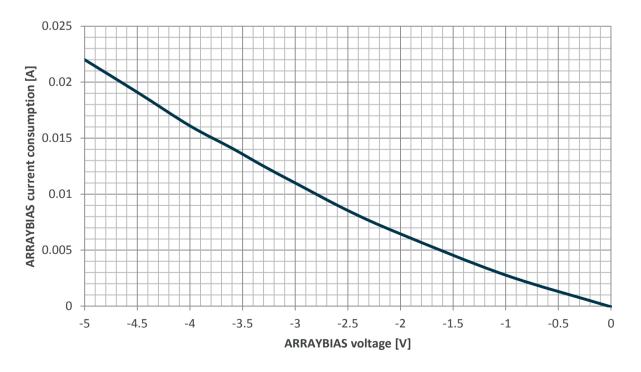

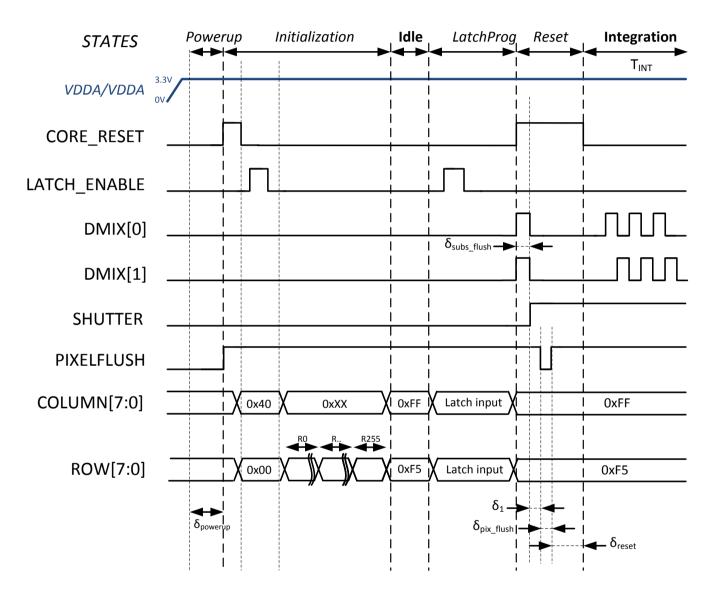

This timing diagram is a typical communication and timing flow to control the MLX75024. The MLX75123BA is managing all these timings and durations automatically by the use of programmable registers.

Figure 11: Global timing diagram from power up to integration. Each phase consists of a reset period, an integration period and a read-out period.

Figure 12: Global timing diagram from integration to power down. Each phase consists of a reset period, an integration period and a read-out phase. The last LatchProg phase here is used to put the sensor in Power Down mode.

| Timing parameter       | Condition                                  |

|------------------------|--------------------------------------------|

| $\delta_{powerup}$     | $\delta_{powerup} \ge 5 ms$                |

| $\delta_{subs\_flush}$ | $\delta_{subs_{flush}} \ge 100 \text{ ns}$ |

| δ1                     | $\delta_1 \ge 0.1 \text{ us}$              |

| $\delta_{pix_{flush}}$ | $\delta_{pix_{flush}} = 5 \text{ us}$      |

| δ <sub>reset</sub>     | δ <sub>reset</sub> ≥ 5 us                  |

| δ2                     | δ₂≥ <b>0.1 us</b>                          |

| δ <sub>3</sub>         | δ <sub>3</sub> ≥ 1 us                      |

Table 16: Timing parameters table

#### **11.2.** Power Up and Initialization

The power up period shall last at least for a period of time equal to  $\delta_{powerup}$  (defined in Table 16) after the supply reached the nominal value. This is indicated on the timing diagram by the  $\delta_{powerup}$  value. After this power up period, the MLX75024 will be able to be programmed using the configuration latches<sup>12</sup>. A code of 0x00 must be applied to the ROW[X] bus and 0x40 to the COLUMN[X] bus at the falling edge of LATCH\_ENABLE signal. Setting COLUMN[6] (INIT, see Table 15) during LATCH\_EN falling edge prepares the image sensor for normal operation. This procedure ensures proper functionality and performance. The initialization period requires 256 ROW[7:0] counts as shown in Figure 11. Output data will be invalid during the initialization period. If the described initialization period has not been respected, the output data will also be invalid.

Note, that COLUMN[6] (INIT, see Table 15) during LATCH\_EN falling edge 0 always starts the initialization period of the device and the content of the following 256 ROW counts must be neglected.

#### **11.3. Latch Programming**

Re-configuration changes the behaviour of the MLX75024 by using the LATCH\_ENABLE input. It is recommended that latch programming period is executed before each integration period. The gain can be programmed during this phase, for example.

#### **11.4. Reset**

The Reset period will happen at the beginning of every phase capture. The electronic shutter shall be opened by setting SHUTTER to HIGH.

• Step 1 : Substrate flush

During step 1, mix signals DMIX0 and DMIX1 are pulled HIGH for a period of time equal to  $\delta_{subs_flush}$  (see Table 16).

The step ends by pulling DMIX0 and DMIX1 terminal LOW.

• Step 2 : Pixel flush

The second step implements a flushed reset by switching PIXELFLUSH low during a period of time equal to  $\delta_{pix flush}$  (see Table 16) and with CORE\_RESET HIGH.

• Step 3 : Reset

The  $3^{rd}$  step of the reset period lasts for a period of time equal to  $\delta_{reset}$  (see Table 16), where the PIXELFLUSH is asserted.

During the 2<sup>nd</sup> and 3<sup>rd</sup> phase of the reset, DMIX0 and DMIX1 states shall be LOW.

#### 11.5. Integration

After the reset period, the integration period is started. The electronic shutter shall be kept open (keep SHUTTER HIGH). The mix signals DMIX[0] and DMIX[1] are alternated using the Time-of-Flight modulation

<sup>&</sup>lt;sup>12</sup> See 10.1 for additional details about the programming of the device.

Melexis

Datasheet

pattern. These two signals are in opposition of phase. DMIX[0] is high when DMIX[1] is low and vice versa. When the integration is completed, the mix signals DMIX[0] and DMIX[1] shall be again put in idle state LOW. The electronic shutter must be closed by setting SHUTTER to LOW.

#### 11.6. Read-out

Reading out the sensor is done by toggling both Row and Column addresses. Both addresses have 8 bit width. The Row binary word is directly mapped to the row number. The column binary word is toggled from 00h to 9Fh (0 to 159).

When selecting column 1, OUTO/3 offer the data from pixel 1, while OUT1/2 offer the data from pixel 9. When selecting column 8, OUTO/3 offer the data from pixel 16, while OUT1/2 offer the data from pixel 24. As such when selecting column N, the data at

| Column kinom          |                     |                     |

|-----------------------|---------------------|---------------------|

| Column binary<br>word | OUT0/3 :<br>Pixel # | OUT1/2 :<br>Pixel # |

| 0                     | 0                   | 8                   |

| 1                     | 1                   | 9                   |

|                       |                     |                     |

| 6                     | 6                   | 14                  |

| 7                     | 7                   | 15                  |

| 8                     | 16                  | 24                  |

| 9                     | 17                  | 25                  |

|                       |                     |                     |

| 15                    | 23                  | 31                  |

| 16                    | 32                  | 40                  |

| 17                    | 33                  | 41                  |

|                       |                     |                     |

OUT0/3 is output of pixel (N MOD 8) + 16\*FLOOR(N/8) OUT1/2 is output of pixel (N MOD 8) + 16\*FLOOR(N/8) + 8

#### Table 17: Read-out table

For gain operation (GAIN\_Mode = 1, 2, 3. See 10.2), the column addressing needs to toggle for proper operation, so it is required to toggle the column already when addressing the first row (ROW[0]), even though there might be no meaningful data (Dummy) shifted out. The MLX75123BA ToFCC is taking care of this automatically. This is not required in GAIN\_Bypass = 1 mode.

The minimum number of columns which needs to be read out is 80 columns in GAIN\_Mode = 1, 2 or 3. This is not required in GAIN\_Bypass = 1 mode.

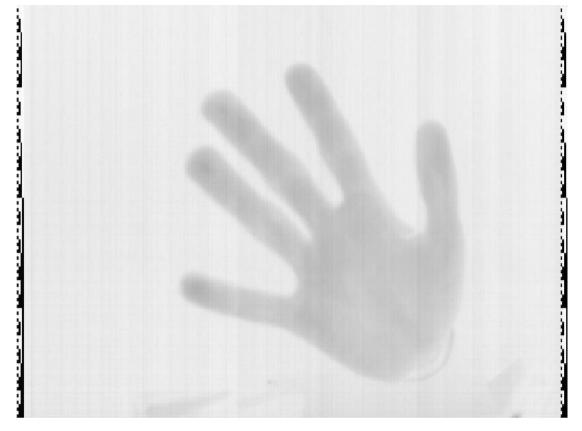

#### **11.7. Test Rows Specification**

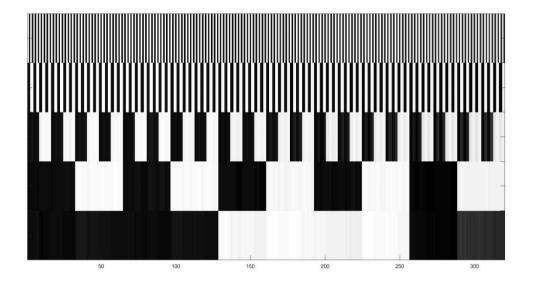

MLX75024 has built in test patterns (the first 5 rows of the 8 test rows) that can be used to debug the analog to digital conversion or verify if the chipset and communication between the MLX75024 and the MLX75123 is working properly. Test rows are always enabled and can be read-out and addressed like any other pixel row. The test rows patterns will represent the column number presented in a binary way. It is used to test the column decoder. The pattern is described in the following table and shown in the images below:

| Row No.           | Figure 3 | Col 0                     | Col 1       | <br>Col 255      | Col 256      | <br>Col319      |

|-------------------|----------|---------------------------|-------------|------------------|--------------|-----------------|

| 240               | Тар А    | ! COLUMN[0] <sup>13</sup> | ! COLUMN[0] | <br>! COLUMN [0] | ! COLUMN [0] | <br>! COLUMN[0] |

| 241               | Тар А    | COLUMN[1]                 | COLUMN[1]   | <br>COLUMN[1]    | COLUMN[1]    | <br>COLUMN[1]   |

| 242               | Тар А    | COLUMN[3]                 | COLUMN[3]   | <br>COLUMN[3]    | COLUMN[3]    | <br>COLUMN[3]   |

| 243               | Тар А    | COLUMN[5]                 | COLUMN[5]   | <br>COLUMN[5]    | COLUMN[5]    | <br>COLUMN[5]   |

| 244 <sup>14</sup> | Тар А    | COLUMN[7]                 | COLUMN[7]   | <br>COLUMN[7]    | COLUMN[7]    | <br>COLUMN[7]   |

|                   |          |                           |             |                  |              |                 |

| 240               | Тар В    | COLUMN[8]                 | COLUMN[8]   | <br>COLUMN[8]    | COLUMN[8]    | <br>COLUMN[8]   |

| 241               | Тар В    | COLUMN[0]                 | COLUMN[0]   | <br>COLUMN[0]    | COLUMN[0]    | <br>COLUMN[0]   |

| 242               | Тар В    | COLUMN[2]                 | COLUMN[2]   | <br>COLUMN[2]    | COLUMN[2]    | <br>COLUMN[2]   |

| 243               | Тар В    | COLUMN[4]                 | COLUMN[4]   | <br>COLUMN[4]    | COLUMN[4]    | <br>COLUMN[4]   |

| 244 <sup>13</sup> | Тар В    | COLUMN[6]                 | COLUMN[6]   | <br>COLUMN[6]    | COLUMN[6]    | <br>COLUMN[6]   |

Table 18: Test row description

$<sup>^{13}</sup>$  The test pattern of row 240 represents the opposite value of the LSB of the column index.

<sup>&</sup>lt;sup>14</sup> Test row 244 test pattern can only be read-out in reverse mode using the REVERSE\_ROW option setting the COLUMN[5] latch control bit to 1. See Configuration latches for additional information.

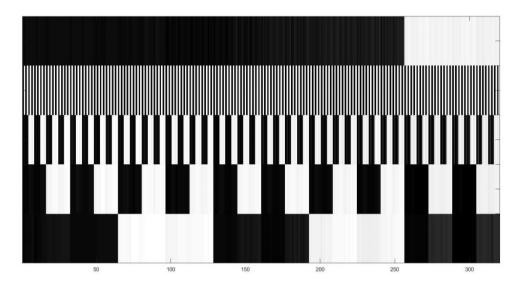

Figure 13 : Raw tap A image of the test rows readout in reverse mode. Top row being row 240, bottom one being row 244.

Figure 14: Raw tap B image of the test rows readout in reverse mode. Top row being row 240, bottom one being row 244.

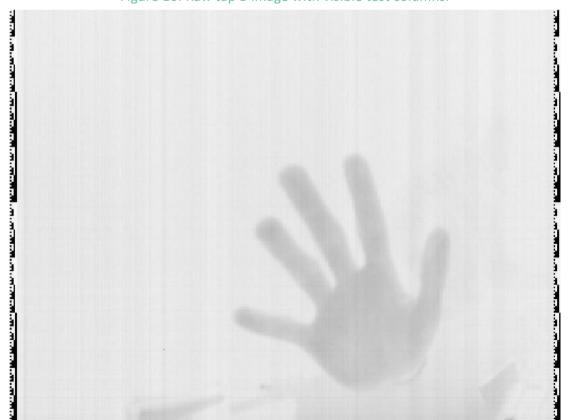

### **11.8. Test Columns Specification**

When TEST\_COLUMN\_OUT (ROW[1] latch control bit, see 10.1) is high, the first 4 columns of the array will be switched into the row ID addresses, or the row number presented in a binary way. It is used to test the row decoder.

The last 4 columns of the pixel array will also be switched into the row ID addresses, or the row number presented in a binary way. The reason to duplicate this is to be able to read the pattern with another set of the output terminals.

| Col No. |       | Row 0  | Row 1  | <br>Row 200 | Row 201 | Row 202 | <br>Row 239 |

|---------|-------|--------|--------|-------------|---------|---------|-------------|

| 0       | Тар А | ROW[1] | ROW[1] | <br>ROW[1]  | ROW[1]  | ROW[1]  | <br>ROW[1]  |

| 1       | Тар А | ROW[3] | ROW[3] | <br>ROW[3]  | ROW[3]  | ROW[3]  | <br>ROW[3]  |

| 2       | Тар А | ROW[5] | ROW[5] | <br>ROW[5]  | ROW[5]  | ROW[5]  | <br>ROW[5]  |

| 3       | Тар А | ROW[7] | ROW[7] | <br>ROW[7]  | ROW[7]  | ROW[7]  | <br>ROW[7]  |

|         |       |        |        |             |         |         |             |

| 316     | Тар А | ROW[1] | ROW[1] | <br>ROW[1]  | ROW[1]  | ROW[1]  | <br>ROW[1]  |

| 317     | Тар А | ROW[3] | ROW[3] | <br>ROW[3]  | ROW[3]  | ROW[3]  | <br>ROW[3]  |

| 318     | Тар А | ROW[5] | ROW[5] | <br>ROW[5]  | ROW[5]  | ROW[5]  | <br>ROW[5]  |

| 319     | Тар А | ROW[7] | ROW[7] | <br>ROW[7]  | ROW[7]  | ROW[7]  | <br>ROW[7]  |

| Col No. |       | Row 0  | Row 1  | ••• | Row 200 | Row 201 | Row 202 | <br>Row 239 |

|---------|-------|--------|--------|-----|---------|---------|---------|-------------|

| 0       | Тар В | ROW[0] | ROW[0] |     | ROW[0]  | ROW[0]  | ROW[0]  | <br>ROW[0]  |

| 1       | Тар В | ROW[2] | ROW[2] |     | ROW[2]  | ROW[2]  | ROW[2]  | <br>ROW[2]  |

| 2       | Тар В | ROW[4] | ROW[4] |     | ROW[4]  | ROW[4]  | ROW[4]  | <br>ROW[4]  |

| 3       | Тар В | ROW[6] | ROW[6] |     | ROW[6]  | ROW[6]  | ROW[6]  | <br>ROW[6]  |

|         |       |        |        |     |         |         |         |             |

| 316     | Тар В | ROW[0] | ROW[0] |     | ROW[0]  | ROW[0]  | ROW[0]  | <br>ROW[0]  |

| 317     | Тар В | ROW[2] | ROW[2] |     | ROW[2]  | ROW[2]  | ROW[2]  | <br>ROW[2]  |

| 318     | Тар В | ROW[4] | ROW[4] |     | ROW[4]  | ROW[4]  | ROW[4]  | <br>ROW[4]  |

| 319     | Тар В | ROW[6] | ROW[6] |     | ROW[6]  | ROW[6]  | ROW[6]  | <br>ROW[6]  |

Datasheet

Figure 15: Raw tap A image with visible test columns.

Figure 16: Raw tap B image with visible test columns.

### **12. Depth & Confidence Calculation**

#### **12.1.** Correlation Measurement

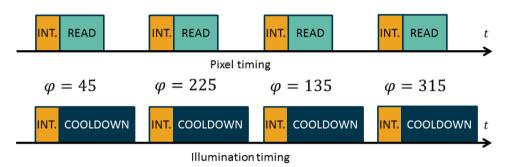

A depth and confidence measurement can be realized by a sequence of 4 correlation measurements, followed by a digital processing step. In one implementation, a single correlation measurement is realized by synchronous demodulation of the light signal of the active illumination source: during the integration time  $T_{int}$ , the active illumination must be turned on while the TOF pixel responsivity and the light signal are amplitude modulated at a frequency  $f_{MIX}$ . Between the illumination source and the TOF pixel modulation signal, a fixed phase delay  $\phi \in \{45, 225, 135, 315\}$  degrees should be applied per correlation measurement. After each integration time, the light source should be switched off to cool down for a time  $T_{cooldown}$ . During this cool down time, there is a time  $T_{read}$  to read out the TOF pixel correlation values  $S_{\phi}$ .

Figure 17 shows the sequence of 4 correlation measurements and the synchronization between the pixel and active illumination timings.

Figure 17: Pixel and illumination timing sequence(s)

The MLX75024 features a two-tap TOF pixel design. One tap measures the in-phase correlation, while the other tap measures the counter phase correlation. Following the described sequence, there will be 8 correlation values available per depth measurement sequence, per pixel:  $S_{k,\phi}$  where  $k \in \{0,1\}$  denotes the in-phase and counter phase correlation respectively, and  $\phi \in \{45, 225, 135, 315\}$ .

Two dual-ended outputs deliver the information from the MLX75024. The dual ended output terminal pairs are (OUT0, OUT3, respectively outputting TapA and TapB) and (OUT1, OUT2, respectively outputting TapB and TapA). During readout of the sensor, each dual ended pair will output the voltages of a two-tap pixel. Each output pair can be assigned to readout one half of the pixel array. For columns 0 ... 7, 16 ... 23, ... :

$$OUT_0 \rightarrow S_{0,\phi} (TapA)$$

$OUT_3 \rightarrow S_{1,\phi} (TapB)$

For columns 8 ... 15, 24 ... 33, ... :

$OUT_1 \rightarrow S_{1,\phi} (TapB)$  $OUT_2 \rightarrow S_{0,\phi} (TapA)$

Datasheet

The MLX75024 also features digital mix input terminals DMIX[0] (pin 35) and DMIX[1] (pin 34). During the integration time  $T_{int}$ , the modulation reference signal must be applied differentially to these terminals. During the remainder of the time, the timing requirements as detailed in Section 11.1 should be followed.

### **12.2.** Active Illumination

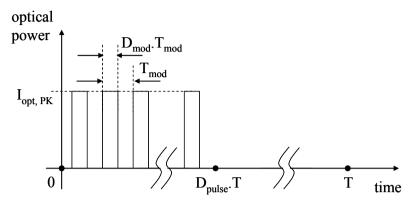

Figure 18: Active illumination waveform

A typical active illumination waveform is shown in Figure 18. The waveform consists of two parts: during the first, a pulse train of active illumination is emitted and during the second, no active light is emitted. During this time, the active light source can cool down and the pixel values can be read out.

The symbols in the graph have the following meaning:

- T is the time between consecutive measurements

- D<sub>pulse</sub> is the ratio between the time that active pulses should be emitted and the total time of the measurement

- *T<sub>mod</sub>* is the duration of each active pulse

- D<sub>mod</sub> is the ratio between the duration of an active pulse and the time between consecutive pulses

- *I*<sub>opt,PK</sub> is the peak optical power or intensity level of the active pulse

- The average optical power or intensity *I*<sub>opt,AVG</sub> can be calculated as

- $I_{opt,AVG} = I_{opt,PK} * D_{mod} * D_{pulse}$

- The average duty cycle  $D_{mod} * D_{pulse}$  should be chosen such that the active illumination can operate reliably i.e. does not exceed its critical temperature, while aiming for maximum peak power  $I_{opt,PK}$  to achieve the best measurement SNR in high ambient light conditions.

Referring to Section 12.1, we note that:

- The integration time T<sub>int</sub> equals D<sub>pulse</sub> \* T

- The cool down time  $T_{cooldown}$  equals  $(1 D_{pulse}) * T$

- The modulation frequency  $f_{MIX}$  equals  $1/T_{mod}$

- The modulation duty cycle  $D_{mod}$  equals 50% in case of square wave or sine modulation

### **13. Package information**

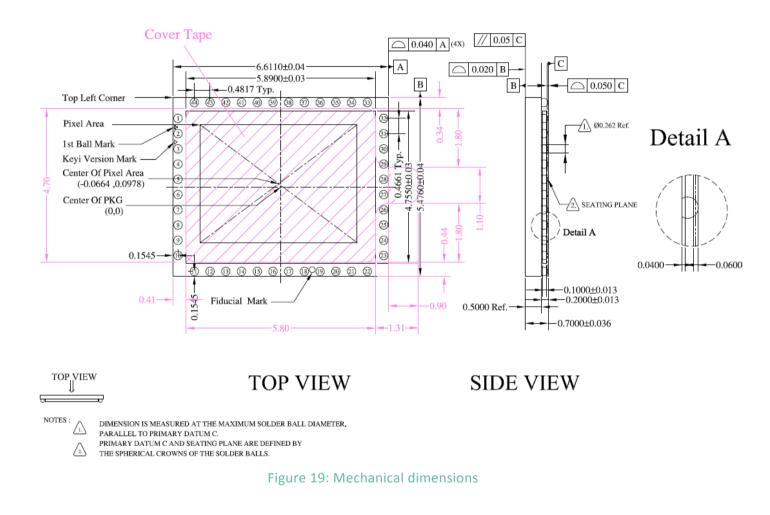

#### 13.1. Mechanical Dimensions

To avoid dust accumulation, scratches or other sources of damage during component storage, logistics or the assembly processes, we offer product variants that include a plastic cover tape to protect the sensitive area of the sensor.

In order to focus the lens over the sensor and capture the light in the most efficient way, it's important to have the sensor's sensitive part at the focal length of the lens. The sensitive area of the pixels is about 550 microns below the glass surface of the sensor. This glass surface is the last surface at the left of the SIDE VIEW on Figure 19 below.

### **13.2.** Moisture sensitivity level

The GBGA44 package is qualified as automotive grade 2 according to AEC-Q100. It is qualified for MSL1 with soldering temperature 260 degrees Celsius.

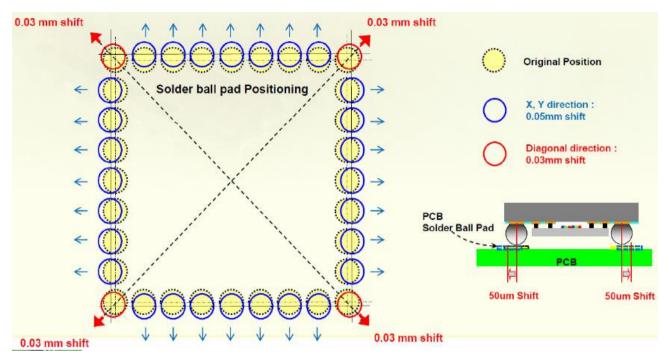

#### **13.3. PCB Footprint Recommendations**

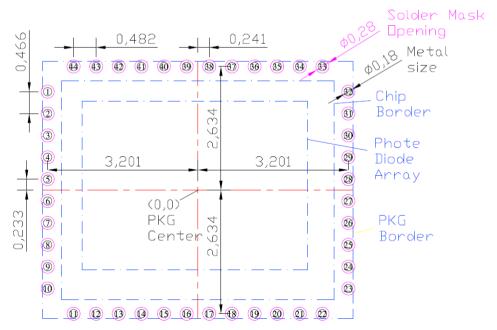

It's recommended to use NSMD (Non Solder Mask Defined) type of pads on the PCB. In order to prevent the solder balls of the sensor to get in contact with each other after reflow, it's also recommended to shift the solder ball pads 50 um outward from the package position, as illustrated in Figure 20 and Figure 21.

Figure 20: Recommended solder pad shift

Figure 21: Recommended PCB land pattern (dimensions in mm), Pixel (0,0) is located on the top right corner of the pixel array here, close to pin 31.

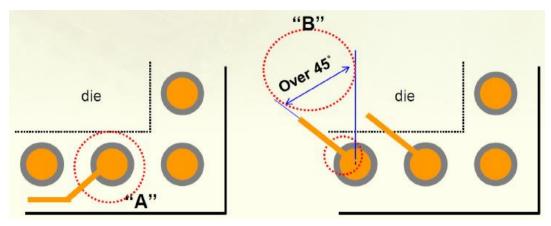

### **13.4. PCB Trace Layout Recommendation**

It is recommended to route the traces connected to the solder balls outside of the solder ball perimeter (see Figure 22, left). In case that traces shall be routed inside of the solder ball perimeter, the trace angle shall be greater than 45 deg (see Figure 22, right).

Figure 22: Recommended trace layout

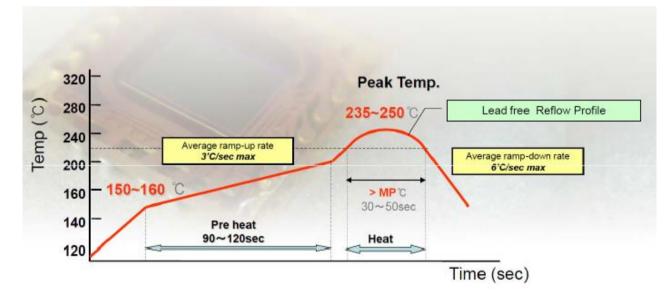

#### **13.5. Sensor Reflow Profile**

Figure 23: Recommended reflow profile

Datasheet

### Disclaimer

The content of this document is believed to be correct and accurate. However, the content of this document is furnished "as is" for informational use only and no representation, nor warranty is provided by Melexis about its accuracy, nor about the results of its implementation. Melexis assumes no responsibility or liability for any errors or inaccuracies that may appear in this document. Customer will follow the practices contained in this document under its sole responsibility. This documentation is in fact provided without warranty, term, or condition of any kind, either implied or expressed, including but not limited to warranties of merchantability, satisfactory quality, non-infringement, and fitness for purpose. Melexis, its employees and agents and its affiliates' and their employees and agents will not be responsible for any loss, however arising, from the use of, or reliance on this document. Notwithstanding the foregoing, contractual obligations expressly undertaken in writing by Melexis prevail over this disclaimer.

This document is subject to change without notice, and should not be construed as a commitment by Melexis. Therefore, before placing orders or prior to designing the product into a system, users or any third party should obtain the latest version of the relevant information.

Users or any third party must determine the suitability of the product described in this document for its application, including the level of reliability required and determine whether it is fit for a particular purpose.

This document as well as the product here described may be subject to export control regulations. Be aware that export might require a prior authorization from competent authorities. The product is not designed, authorized or warranted to be suitable in applications requiring extended temperature range and/or unusual environmental requirements. High reliability applications, such as medical life-support or life-sustaining equipment or avionics application are specifically excluded by Melexis. The product may not be used for the following applications subject to export control regulations: the development, production, processing, operation, maintenance, storage, recognition or proliferation of:

1. chemical, biological or nuclear weapons, or for the development, production, maintenance or storage of missiles for such weapons;

2. civil firearms, including spare parts or ammunition for such arms;

3. defense related products, or other material for military use or for law enforcement;

4. any applications that, alone or in combination with other goods, substances or organisms could cause serious harm to persons or goods and that can be used as a means of violence in an armed conflict or any similar violent situation.

No license nor any other right or interest is granted to any of Melexis' or third party's intellectual property rights.

If this document is marked "restricted" or with similar words, or if in any case the content of this document is to be reasonably understood as being confidential, the recipient of this document shall not communicate, nor disclose to any third party, any part of the document without Melexis' express written consent. The recipient shall take all necessary measures to apply and preserve the confidential character of the document. In particular, the recipient shall (i) hold document in confidence with at least the same degree of care by which it maintains the confidentiality of its own proprietary and confidential information, but no less than reasonable care; (ii) restrict the disclosure of the document solely to its employees for the purpose for which this document was received, on a strictly need to know basis and providing that such persons to whom the document is disclosed are bound by confidentiality terms substantially similar to those in this disclaimer; (iii) use the document only in connection with the purpose for which this document was received, and reproduce document only to the extent necessary for such purposes; (iv) not use the document for commercial purposes or to the detriment of Melexis or its customers. The confidentiality obligations set forth in this disclaimer will have indefinite duration and in any case they will be effective for no less than 10 years from the receipt of this document.

This disclaimer will be governed by and construed in accordance with Belgian law and any disputes relating to this disclaimer will be subject to the exclusive jurisdiction of the courts of Brussels, Belgium.

The invalidity or ineffectiveness of any of the provisions of this disclaimer does not affect the validity or effectiveness of the other provisions. The previous versions of this document are repealed.

Melexis © - No part of this document may be reproduced without the prior written consent of Melexis. (2020)

IATF 16949 and ISO 14001 Certified

DepthSense™ is Trademark of Sony Corporation.

### **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Melexis:

MLX75024RTF-GAA-000-SP MLX75024RTF-GAA-000-TR MLX75024STF-GAA-001-TR