# **General Description**

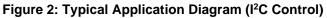

DA9220 is a power management unit (PMU) suitable for supplying CPUs, GPUs, DDR memory rails in single in-line pin package (SIPP) modules, smartphones, tablets, and other handheld applications.

DA9220 integrates two single-phase buck converters, each phase requiring a small external 0.10  $\mu$ H inductor. Each buck is capable of delivering up to 3 A output current at a 0.3 V to 1.9 V output voltage range. The 2.5 V to 5.5 V input voltage range is suitable for a wide variety of low-voltage systems, including, but not limited to, all Li-lon battery supplied applications.

With remote sensing, the DA9220 guarantees the highest accuracy and supports multiple PCB routing scenarios without loss of performance.

The pass devices are fully integrated, so no external FETs or Schottky diodes are needed.

A programmable soft start-up can be enabled, which limits the inrush current from the input node and secures a slope-controlled rail activation.

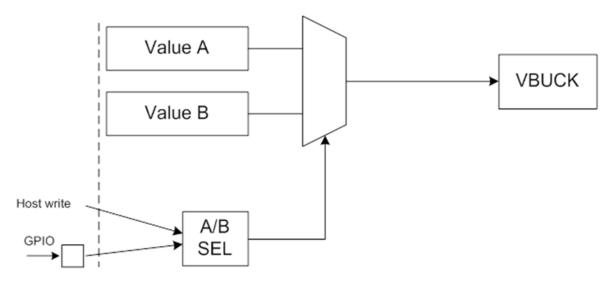

The dynamic voltage control (DVC) supports adaptive adjustment of the supply voltage dependent on the processor load, via either a direct register write using the communication interface (I<sup>2</sup>C-compatible) or with a programmable input pin.

A configurable GPI allows multiple I<sup>2</sup>C address selection for multiple instances of DA9220 in the same application.

DA9220 has integrated over-temperature and over-current protection for increased system reliability, without the need for external sensing components.

## **Key Features**

- 2.5 V to 5.5 V input voltage

- 0.3 V to 1.9 V output voltage

- 4 MHz nominal switching frequency

- ±1 % accuracy (static)

- ±5 % accuracy (dynamic)

- I<sup>2</sup>C-compatible interface (FM+)

- Programmable GPIOs

## **Applications**

- SIPP modules (SoC, DRAM)

- Smartphones

- Tablet PCs

- Infotainment

- Programmable soft-start

- Voltage, current, and temperature supervision

- -40 °C to +85 °C ambient temperature range

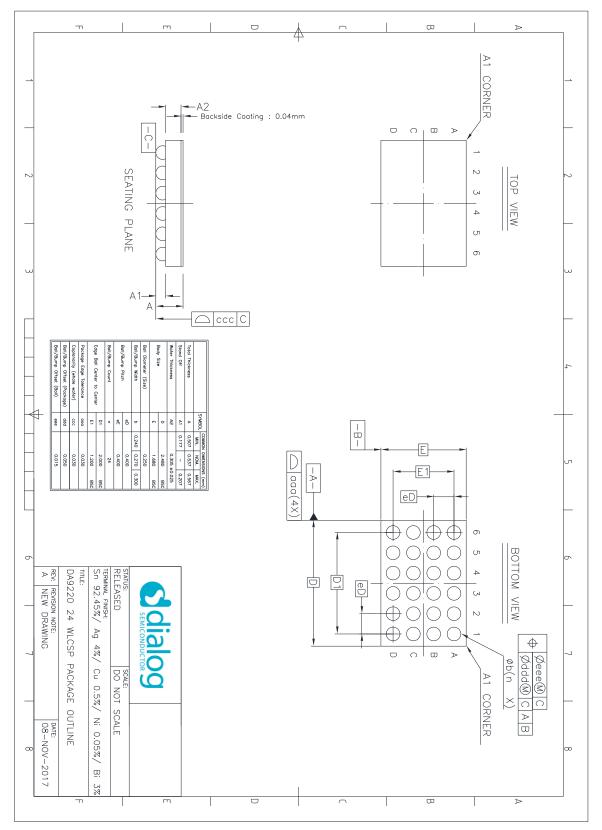

- Package: 24WLCSP 2.5 mm x 1.7 mm (0.4 mm pitch)

- Ultrabooks<sup>™</sup>

- Wi-Fi Modules

- Game Consoles

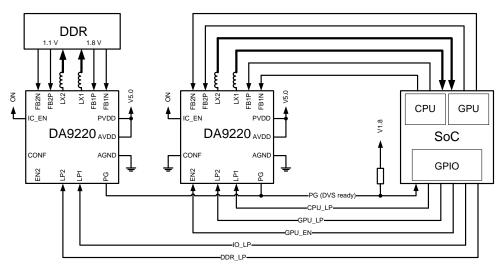

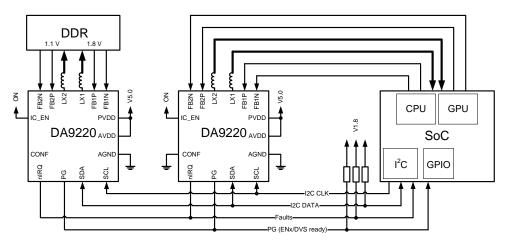

# **System Diagrams**

Figure 1: Typical Application Diagram (Port Control)

| Datasheet Revision 2.1 |

|------------------------|

|------------------------|

# High-Performance Dual-Channel DC-DC Converter

## Contents

| Ge  | neral I    | Descriptio           | on                       |                                       | 1 |  |

|-----|------------|----------------------|--------------------------|---------------------------------------|---|--|

| Ke  | y Feat     | ures                 |                          |                                       | 1 |  |

| Ар  | plicati    | ons                  |                          |                                       | 1 |  |

| Sv  | stem D     | Diagrams             |                          |                                       |   |  |

| •   |            | •                    |                          |                                       |   |  |

|     |            |                      |                          |                                       | - |  |

| 1   |            |                      |                          |                                       |   |  |

| 2   |            |                      |                          |                                       |   |  |

| 3   |            |                      | -                        |                                       | - |  |

|     | 3.1        |                      |                          | Ratings                               |   |  |

|     | 3.2        |                      |                          | ating Conditions                      |   |  |

|     | 3.3        |                      |                          | ics                                   |   |  |

|     |            | 3.3.1                |                          | itings                                |   |  |

|     | ~ 1        | 3.3.2                |                          | ipation                               |   |  |

|     | 3.4        |                      |                          |                                       |   |  |

|     | 3.5        |                      |                          |                                       |   |  |

|     | 3.6        |                      |                          | pervision Characteristics             |   |  |

|     | 3.7<br>3.8 | 0                    |                          | SIICS                                 |   |  |

|     | 3.9        | •                    |                          | 5                                     |   |  |

|     |            |                      |                          |                                       |   |  |

| 4   |            |                      | •                        |                                       |   |  |

|     | 4.1        | 4.1.1                |                          |                                       |   |  |

|     |            | 4.1.1                | -                        | requency<br>Aodes and Phase Selection |   |  |

|     |            | 4.1.2                | •                        | age Selection                         |   |  |

|     |            | 4.1.3                | •                        | lp and Shutdown                       |   |  |

|     |            | 4.1.5                |                          | it                                    |   |  |

|     |            | 4.1.6                |                          | otection                              |   |  |

|     | 4.2        |                      |                          |                                       |   |  |

|     | 1.2        | 4.2.1                |                          | Enable/Disable                        |   |  |

|     |            |                      |                          | upt                                   |   |  |

|     |            | 4.2.3                |                          | ~~                                    |   |  |

|     |            |                      | 4.2.3.1                  | GPIO Pin Assignment                   |   |  |

|     |            |                      | 4.2.3.2                  | GPIO Function                         |   |  |

|     |            |                      | 4.2.3.3                  | Chip Configuration Select (CONF)      |   |  |

|     |            |                      | 4.2.3.4                  | OTP Reload (RELOAD)                   |   |  |

|     | 4.3        | Operating            | g Modes                  | · · · · · · · · · · · · · · · · · · · |   |  |

|     |            | 4.3.1                | ON                       |                                       |   |  |

|     |            | 4.3.2                | OFF                      |                                       |   |  |

|     | 4.4        | I <sup>2</sup> C Com | munication               |                                       |   |  |

|     |            | 4.4.1                | I <sup>2</sup> C Protoco | I                                     |   |  |

| 5   | Regis      | ter Defin            | itions                   |                                       |   |  |

|     | 5.1        | Register             | Мар                      |                                       |   |  |

|     |            | 5.1.1                | System                   |                                       |   |  |

|     |            | 5.1.2                | Buck1                    |                                       |   |  |

| Dat |            |                      |                          |                                       |   |  |

|       | 5.1.3                                                                                                    | Buck2                                                                                                                                      | . 52                                                  |

|-------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

|       | 5.1.4                                                                                                    | Serialization                                                                                                                              | . 57                                                  |

| Pack  | age Infori                                                                                               | nation                                                                                                                                     | . 58                                                  |

| 6.1   | Package                                                                                                  | Outlines                                                                                                                                   | . 58                                                  |

| 6.2   | Moisture                                                                                                 | Sensitivity Level                                                                                                                          | . 59                                                  |

| 6.3   | WLCSP                                                                                                    | Handling                                                                                                                                   | . 59                                                  |

| 6.4   | Soldering                                                                                                | g Information                                                                                                                              | . 59                                                  |

| Orde  | ring Infor                                                                                               | mation                                                                                                                                     | . 60                                                  |

| Appli | ication In                                                                                               | formation                                                                                                                                  | . 60                                                  |

| 8.1   | Capacito                                                                                                 | r Selection                                                                                                                                | . 60                                                  |

| 8.2   | Inductor                                                                                                 | Selection                                                                                                                                  | . 61                                                  |

|       | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>Orde</li> <li>Appli</li> <li>8.1</li> </ul> | 5.1.4<br>Package Inform<br>6.1 Package<br>6.2 Moisture<br>6.3 WLCSP<br>6.4 Soldering<br>Ordering Infor<br>Application Info<br>8.1 Capacito | 5.1.4       Serialization         Package Information |

## **1** Terms and Definitions

| ATE    | Automated test equipment                           |

|--------|----------------------------------------------------|

| CPU    | Central processing unit                            |

| DDR    | Dual data rate                                     |

| DVC    | Dynamic voltage control                            |

| FET    | Field effect transistor                            |

| FM+    | Fast mode plus                                     |

| GBD    | Guaranteed by design                               |

| GBQ    | Guaranteed by qualification                        |

| GBSPC  | Guaranteed by statistical process characterization |

| GPI    | General purpose input                              |

| GPIO   | General purpose input/output                       |

| GPU    | Graphics processing unit                           |

| IC     | Integrated circuit                                 |

| HW     | Hardware                                           |

| Li-Ion | Lithium-ion                                        |

| OTP    | One time programmable                              |

| PCB    | Printed circuit board                              |

| PRS    | Product requirements specification                 |

| SCL    | Serial clock                                       |

| SDA    | Serial data                                        |

| SIPP   | Single in-line pin package                         |

| SW     | Software                                           |

|        |                                                    |

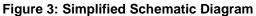

## 2 Pinout

Figure 4: DA9220 Pinout Diagram (Top View)

#### Table 1: Pin Description

| Pin No. | Pin Name   | Type<br>(Table 2) | Drive<br>(mA) | Reset<br>State | Description                                                                                                |

|---------|------------|-------------------|---------------|----------------|------------------------------------------------------------------------------------------------------------|

| A1, B1  | PVDD1      | PWR               | 5000          |                | Supply voltage for Buck1 power stage, decouple with 10 $\mu F$ and connect to same source as AVDD          |

| A2, B2  | LX1        | AIO               | 5000          |                | Switch node of Buck1, connect a 100 nH inductor between LX1 and output capacitor                           |

| A3, B3  | PGND1      | GND               | 5000          |                | Buck1 power stage VSS rail                                                                                 |

| A4, B4  | PGND2      | GND               | 5000          |                | Buck2 power stage VSS rail                                                                                 |

| A5, B5  | LX2        | AIO               | 5000          |                | Switch node of Buck2, connect a 100 nH inductor between LX2 and output capacitor                           |

| A6, B6  | PVDD2      | PWR               | 5000          |                | Supply voltage for Buck2 power stage, decouple with 10 $\mu F$ and connect to same source as AVDD          |

| C1      | SCL/GPIO3  | DIO               | 15            |                | I <sup>2</sup> C clock or general purpose I/O                                                              |

| C2      | SDA/GPIO4  | DIO               | 15            |                | I <sup>2</sup> C data or general purpose I/O                                                               |

| C3      | IC_EN      | AI                | 10            |                | Powers up SW control interface and auxiliary circuitry (for example, bandgap, oscillator, and references). |

| C4      | CONF/GPIO0 | AI/DIO            | 10            |                | Chip configuration or general purpose I/O                                                                  |

| C5      | GPIO1      | DIO               | 10            |                | General purpose I/O                                                                                        |

| C6      | GPIO2      | DIO               | 10            |                | General purpose I/O                                                                                        |

| D1      | FB1N       | AI                | 10            |                | Buck1 negative node of differential voltage feedback, connect to VSS at point of load                      |

| D2      | FB1P       | AI                | 10            |                | Buck1 positive node of differential voltage feedback, connect to VOUT1 at point of load                    |

| D3      | AVDD       | PWR               | 10            |                | Supply rail for analog control circuitry, decouple with 1 $\mu$ F and connect to same source as PVDD       |

## High-Performance Dual-Channel DC-DC Converter

| Pin No. | Pin Name | Type<br>(Table 2) | Drive<br>(mA) | Reset<br>State | Description                                                                             |

|---------|----------|-------------------|---------------|----------------|-----------------------------------------------------------------------------------------|

| D4      | AGND     | GND               | 10            |                | Analog control and auxiliary circuitry VSS                                              |

| D5      | FB2P     | AI                | 10            |                | Buck2 positive node of differential voltage feedback, connect to VOUT2 at point of load |

| D6      | FB2N     | AI                | 10            |                | Buck2 negative node of differential voltage feedback, connect to VSS at point of load   |

### Table 2: Pin Type Definition

| Pin Type | Description          | Pin Type | Description         |

|----------|----------------------|----------|---------------------|

| DI       | Digital input        | AI       | Analog input        |

| DO       | Digital output       | AO       | Analog output       |

| DIO      | Digital input/output | AIO      | Analog input/output |

| PWR      | Power                | GND      | Ground              |

## **3** Characteristics

## 3.1 Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, so functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification are not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

#### Table 3: Absolute Maximum Ratings

| Parameter        | Description           | Conditions | Min  | Max | Unit |

|------------------|-----------------------|------------|------|-----|------|

| T <sub>STG</sub> | Storage temperature   |            | -65  | 150 | °C   |

| TJ               | Junction temperature  |            | -40  | 150 | °C   |

| Vsys             | System supply voltage |            | -0.3 | 6.0 | V    |

| VPIN             | Voltage on pins       |            | -0.3 | 6.0 | V    |

## 3.2 Recommended Operating Conditions

#### **Table 4: Recommended Operating Conditions**

| Parameter      | Description           | Conditions (Note 1) | Min  | Тур | Max                    | Unit |

|----------------|-----------------------|---------------------|------|-----|------------------------|------|

| Vsys           | System supply voltage |                     | 2.5  |     | 5.5                    | V    |

| VPIN           | Voltage on pins       |                     | -0.3 |     | V <sub>SYS</sub> + 0.3 | V    |

| TJ             | Junction temperature  |                     | -40  |     | 125                    | °C   |

| T <sub>A</sub> | Ambient temperature   |                     | -40  |     | 85                     | °C   |

**Note 1** Within the specified limits, a lifetime of 10 years is guaranteed. If operating outside of these recommended conditions, please consult with Dialog Semiconductor.

### High-Performance Dual-Channel DC-DC Converter

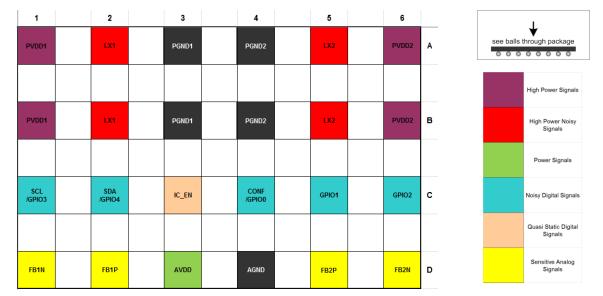

### 3.3 Thermal Characteristics

#### 3.3.1 Thermal Ratings

#### Table 5: Package Ratings

| Parameter | Description                          | Conditions | Min | Тур  | Max | Unit |

|-----------|--------------------------------------|------------|-----|------|-----|------|

| Αμθ       | Package thermal resistance<br>Note 1 |            |     | 32.7 |     | °C/W |

Note 1 Obtained from package thermal simulation, 2S2P4L board (JEDEC), influenced by PCB technology and layout.

#### 3.3.2 **Power Dissipation**

#### Table 6: Power Dissipation

| Parameter | Description       | Conditions                                                                            | Min | Тур  | Max | Unit |

|-----------|-------------------|---------------------------------------------------------------------------------------|-----|------|-----|------|

| PD        | Power dissipation | Derating factor above $T_A = 70^{\circ}C : 30.6 \text{ mW/}^{\circ}C (1/\theta_{JA})$ |     | 2140 |     | mW   |

### 3.4 ESD Characteristics

#### **Table 7: ESD Characteristics**

| Parameter                     | Description                            | Conditions | Min | Тур | Max | Unit |

|-------------------------------|----------------------------------------|------------|-----|-----|-----|------|

| $V_{\text{ESD}_{\text{HBM}}}$ | ESD protection, human body model (HBM) |            |     |     | 2   | kV   |

**Datasheet**

**Revision 2.1**

### 3.5 Buck Characteristics

Unless otherwise noted, the following is valid for  $T_J$  = -40 °C to +125 °C,  $V_{SYS}$  = 2.5 V to 5.5 V

| Parameter                                  | Description Conditions                                                             |                                                                                    | Min   | Тур       | Max   | Unit |

|--------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------|-----------|-------|------|

| External Ele                               | ectrical Conditions                                                                |                                                                                    |       |           |       |      |

| VIN                                        | Input voltage                                                                      | V <sub>IN</sub> = V <sub>SYS</sub> 2.5                                             |       |           | 5.5   | V    |

| Соит                                       | Output capacitance, per<br>phase, including voltage and<br>temperature coefficient |                                                                                    | -40 % | 2 x 10    | +30 % | μF   |

| ESR <sub>COUT</sub>                        | Output capacitor series resistance, per phase                                      | f > 100 kHz                                                                        |       | 2         |       | mΩ   |

| L                                          | Inductor value, per phase,<br>including current and<br>temperature dependence      |                                                                                    | -50 % | 0.1       | +20 % | μH   |

| DCR∟                                       | Inductor DC resistance                                                             |                                                                                    |       | 30        | 50    | mΩ   |

| Electrical P                               | erformance                                                                         |                                                                                    |       |           |       |      |

| Vout                                       | Output voltage,<br>programmable in 10 mV<br>steps                                  | $I_{OUT} = 0$ mA to $I_{MAX}$<br>$V_{IN} = 2.5$ V to 5.5 V                         | 0.3   |           | 1.57  | V    |

| Vout_lim                                   | Output voltage,<br>programmable in 10 mV<br>steps                                  | $I_{OUT} = 0 \text{ mA to } I_{MAX}$<br>$V_{IN} = 3.0 \text{ V to } 5.5 \text{ V}$ | 0.3   |           | 1.9   | V    |

| ILIM                                       | Current limit, programmable<br>per phase<br>Note 1                                 | CHx_ILIM = 1010                                                                    | -20 % | 20 % 8    |       | A    |

| V <sub>OUT_ACC</sub>                       | Output voltage accuracy,<br>including static line and load<br>regulation           | V <sub>OUT</sub> ≥ 1 V                                                             | -1    |           | 1     | %    |

| Vout_acc                                   | Output voltage accuracy,<br>including static line and load<br>regulation           | Vout < 1 V                                                                         | -10   |           | 10    | mV   |

| $V_{\text{THR}_{\text{PG}}_{\text{RISE}}}$ | Power good voltage threshold for rising                                            | Referred to Vout                                                                   | -80   | -50       | -20   | mV   |

| $V_{\text{THR}\_\text{PG}\_\text{DWN}}$    | Power good voltage threshold for falling                                           | Referred to VOUT                                                                   | -160  | -160 -130 |       | mV   |

| VTHR_HV                                    | High Vout voltage threshold                                                        | Referred to VOUT                                                                   | 100   | 150       | 200   | mV   |

| Vout_tr_line                               | Line transient response                                                            | $V_{IN} = 3 V \text{ to } 3.6 V$<br>$I_{OUT} = 0.5 * I_{MAX}$<br>$dt = 10 \ \mu s$ |       | 15        |       | mV   |

| fsw                                        | Switching frequency, post-<br>trim                                                 |                                                                                    |       | 4         |       | MHz  |

| Parameter            | Description                                                                                                                                                                   | Conditions                                                    | Min | Тур | Мах | Unit |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|-----|-----|------|

| t <sub>ON_MIN</sub>  | Minimum turn-on pulse<br>0 % duty is also supported                                                                                                                           |                                                               |     | 20  |     | ns   |

| tbuck_en             | Turn-on time                                                                                                                                                                  | CHx_EN = high                                                 |     |     | 20  | μs   |

| Rpd                  | Output pull-down resistance<br>for each phase at the LX<br>node, see CHx_PD_DIS                                                                                               | V <sub>IN</sub> = 3.7 V<br>V <sub>OUT</sub> = 0.5 V           | 100 |     | 200 | Ω    |

| R <sub>ON_PMOS</sub> | On resistance of switching PMOS, per phase                                                                                                                                    | V <sub>IN</sub> = 3.7 V                                       |     | 36  |     | mΩ   |

| Ron_nmos             | On resistance of switching NMOS, per phase                                                                                                                                    | V <sub>IN</sub> = 3.7 V                                       |     | 17  |     | mΩ   |

| AUTO Mode            |                                                                                                                                                                               |                                                               |     |     |     |      |

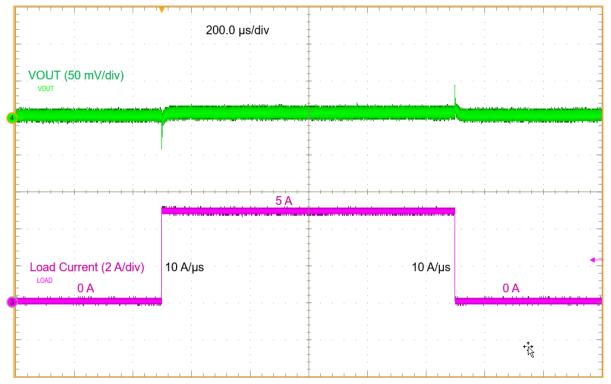

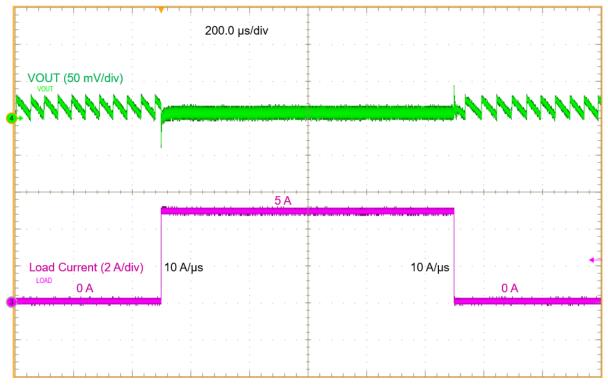

| Vout_tr_ld_1<br>ph   | Load transient response $\begin{cases} 1-\text{phase} \\ V_{\text{OUT}} = 1 \text{ V} \\ I_{\text{OUT}} = 0 \text{ A to 5 A} \\ dI/dt = 10 \text{ A}/\mu\text{s} \end{cases}$ |                                                               |     | ±5  |     | %    |

| PFM Mode             |                                                                                                                                                                               |                                                               |     |     |     |      |

| Iq_pfm_1ph           | Quiescent current in PFM                                                                                                                                                      | 1-phase<br>V <sub>IN</sub> = 3.7 V<br>No load<br>No switching |     |     |     | μΑ   |

**Note 1** ton > 40 ns

## 3.6 **Performance and Supervision Characteristics**

#### **Table 9: Electrical Characteristics**

| Parameter              | Description                            | Conditions                                      | Min | Тур | Мах  | Unit |  |  |

|------------------------|----------------------------------------|-------------------------------------------------|-----|-----|------|------|--|--|

| Electrical Performance |                                        |                                                 |     |     |      |      |  |  |

| VTHR_POR               | Power-on-reset threshold               | Threshold for AVDD falling                      |     | 2.1 | 2.25 | V    |  |  |

| Vthr_por_hy<br>s       | Power-on-reset hysteresis              |                                                 |     | 200 |      | mV   |  |  |

| Twarn                  | Thermal warning temperature threshold  |                                                 | 115 | 125 | 135  | °C   |  |  |

| T <sub>CRIT</sub>      | Thermal shutdown temperature threshold |                                                 | 130 | 140 | 150  | °C   |  |  |

| IIN_OFF                | Supply current                         | OFF state<br>$T_A = 27 \text{ °C}$<br>IC_EN = 0 |     | 0.1 | 1    | μA   |  |  |

**Datasheet**

**Revision 2.1**

| Parameter | Description    | Conditions                                                  | Min | Тур | Max | Unit |

|-----------|----------------|-------------------------------------------------------------|-----|-----|-----|------|

| lin_on    | Supply current | ON state<br>T <sub>A</sub> = 27 °C<br>IC_EN = 1<br>Buck off | 5   | 10  | 20  | μΑ   |

# 3.7 Digital I/O Characteristics

### Table 10: Digital I/O Electrical Characteristics

| Parameter              | Description                          | Conditions                                | Min          | Тур  | Мах          | Unit |  |  |

|------------------------|--------------------------------------|-------------------------------------------|--------------|------|--------------|------|--|--|

| Electrical Performance |                                      |                                           |              |      |              |      |  |  |

| VIH_EN                 | Input high voltage, IC enable        |                                           | 1.2          |      | AVDD         | V    |  |  |

| VIL_EN                 | Input low voltage, IC enable         |                                           |              |      | 0.4          | V    |  |  |

| tic_en                 | IC enable time                       |                                           |              |      | 1000         | μs   |  |  |

| Vih_gpio_scl<br>_sda   | Input high voltage<br>GPIO, SCL, SDA |                                           | 1.2          |      | AVDD         | V    |  |  |

| Vil_gpio_scl_<br>sda   | Input low voltage<br>GPIO, SCL, SDA  |                                           |              |      | 0.4          | V    |  |  |

| Voh_gpio               | Output high voltage<br>GPIO          | Push-pull mode<br>I <sub>OUT</sub> = 1 mA | 0.8*AV<br>DD |      | AVDD         | V    |  |  |

| Vol_gpio               | Output low voltage<br>GPIO           | Push-pull mode<br>lout = 1 mA             |              |      | 0.2*AV<br>DD | V    |  |  |

| Vol_sda                | Output low voltage<br>SDA            | louт = 3 mA                               |              | 0.24 |              | V    |  |  |

| R <sub>PD</sub>        | GPIO pull-down resistor              |                                           | 2            | 10   | 120          | kΩ   |  |  |

| Rpu                    | GPIO pull-up resistor                |                                           | 2            | 10   | 120          | kΩ   |  |  |

## 3.8 Timing Characteristics

### Table 11: I2C Electrical Characteristics

| Parameter              | Description                                      | Conditions            | Min          | Тур | Max  | Unit |  |  |

|------------------------|--------------------------------------------------|-----------------------|--------------|-----|------|------|--|--|

| Electrical Performance |                                                  |                       |              |     |      |      |  |  |

| t <sub>BUS</sub>       | Bus free time between a STOP and START condition |                       | 0.5          |     |      | μs   |  |  |

| CBUS                   | Bus line capacitive load                         |                       |              |     | 150  | pF   |  |  |

| fscL                   | SCL clock frequency                              |                       | 20<br>Note 1 |     | 1000 | kHz  |  |  |

| tLO_SCL                | SCL low time                                     |                       | 0.5          |     |      | μs   |  |  |

| thi_scl                | SCL high time                                    |                       | 0.26         |     |      | μs   |  |  |

| trise                  | SCL and SDA rise time                            | Requirement for input |              |     | 1000 | ns   |  |  |

| tFALL                  | SCL and SDA fall time                            | Requirement for input |              |     | 300  | ns   |  |  |

| tsetup_start           | Start condition setup time                       |                       | 0.26         |     |      | μs   |  |  |

| thold_start            | Start condition hold time                        |                       | 0.26         |     |      | μs   |  |  |

| tsetup_stop            | Stop condition setup time                        |                       | 0.26         |     |      | μs   |  |  |

| <b>t</b> data          | Data valid time                                  |                       |              |     | 0.45 | μs   |  |  |

| tdata_ack              | Data valid acknowledge time                      |                       |              |     | 0.45 | μs   |  |  |

| tsetup_data            | Data setup time                                  |                       | 50           |     |      | ns   |  |  |

| thold_data             | Data hold time                                   |                       | 0            |     |      | ns   |  |  |

**Note 1** Minimum clock frequency is limited to 20 kHz if I2C\_TIMEOUT is enabled

### High-Performance Dual-Channel DC-DC Converter

## 3.9 Typical Performance

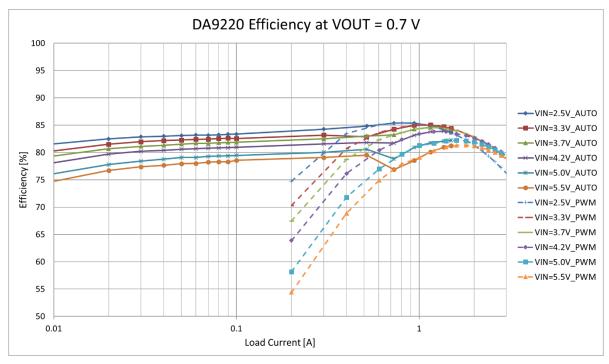

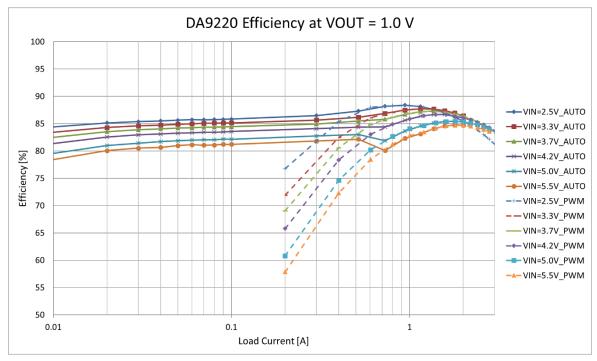

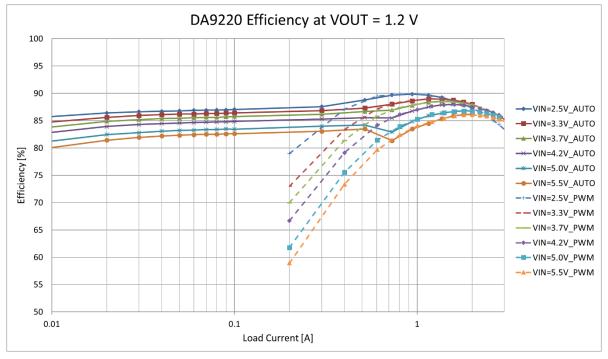

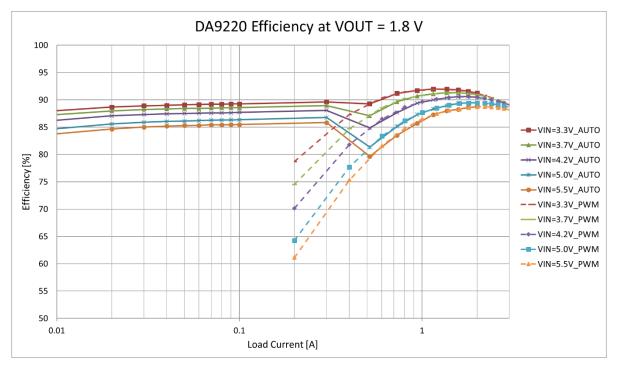

Unless otherwise noted,  $V_{IN} = 3.7 \text{ V}$ ,  $V_{OUT} = 1.0 \text{ V}$ ,  $T_A = 25 \text{ °C}$ , 2.0 mm x 1.6 mm 0.1 µH output inductor (DCR = typ. 11.5 m $\Omega$ ) and 2 x 10 µF output capacitors per-channel.

Figure 6: Efficiency vs Load, V<sub>OUT</sub> = 0.7 V

Figure 7: Efficiency vs Load,  $V_{OUT}$  = 1.0 V

| _ |     | _  |    |   |

|---|-----|----|----|---|

| D | ata | sh | 60 | t |

|   | utu |    |    |   |

Figure 8: Efficiency vs Load, V<sub>OUT</sub> = 1.2 V

Figure 9: Efficiency vs Load, V<sub>OUT</sub> = 1.8 V

| De |    | - 4 |

|----|----|-----|

| Da | ne | ет  |

|    |    |     |

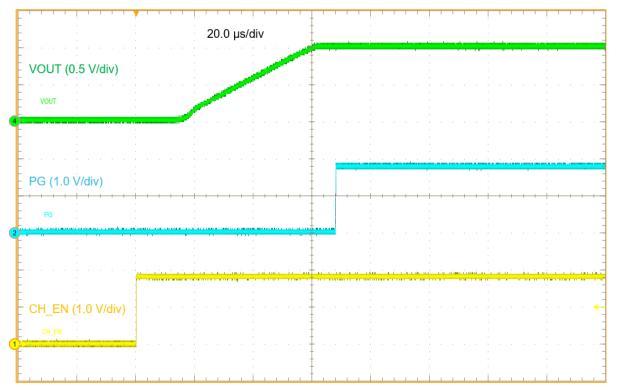

### Figure 10: Buck Soft Start-up at 20 mV/µs Slew Rate

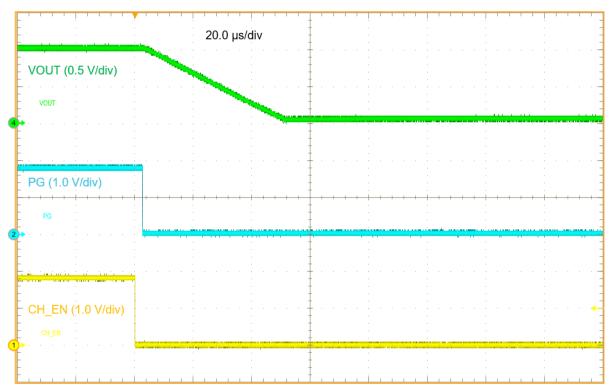

Figure 11: Buck Active Shutdown at 20 mV/µs Slew Rate

**Datasheet**

17-Sep-2020

Figure 12: Buck Load Transient Response in PWM Mode, 0 A to 5 A at 10 A/µs

Figure 13: Buck Load Transient Response in AUTO Mode, 0 A to 5 A at 10 A/ $\mu s$

**Datasheet**

# 4 Functional Description

## 4.1 DC-DC Buck Converter

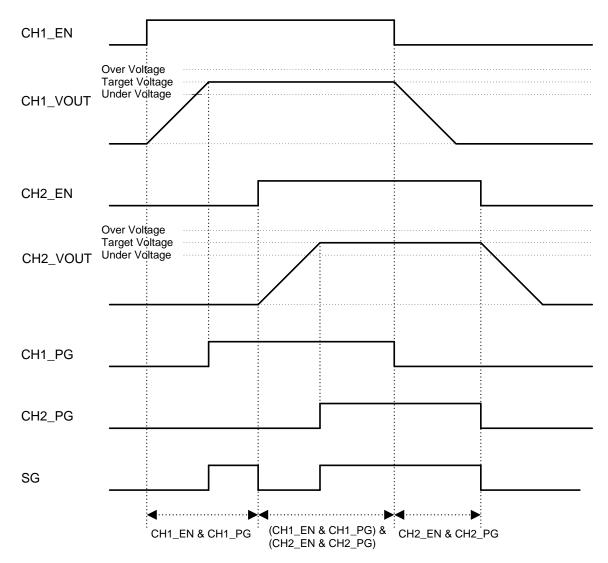

DA9220 contains two buck converters, Buck1 and Buck2, each capable of delivering up to 3 A output current at a 0.3 V to 1.9 V output voltage range.

Buck1 and Buck2 have two voltage registers each. One defines the normal output voltage, while the other offers an alternative retention voltage. In this way, different application power modes can easily be supported. The voltage selection can be operated either via GPI or via control interface to guarantee the maximum flexibility according to the specific host processor status in the application.

When a buck is enabled, its output voltage is monitored and a power good signal indicates that the buck output voltage has reached a level higher than the V<sub>THR\_PG\_RISE</sub> threshold. The power good status is lost when the voltage drops below V<sub>THR\_PG\_DWN</sub> or increases above V<sub>THR\_HV</sub>. For each of the buck converters the status of the power good indicator can be read back via I<sup>2</sup>C from the PG1 and PG2 status bits. It can be also individually assigned to any of the GPIOs by setting the GPIO mode registers to either PG1 or PG2 output.

The buck converters are capable of supporting DVC transitions that occur:

- When the active and selected A- or B-voltage is updated to a new target value.

- When the voltage selection is changed from the A- to B-voltage (or B- to A-voltage) using CH<x>\_VSEL.

The DVC controller operates in pulse width modulation (PWM) mode with synchronous rectification.

The slew rate of the DVC transition is individually programmed for each buck converter at 10 mV per 8  $\mu$ s, 4  $\mu$ s, 2  $\mu$ s, 1  $\mu$ s, or 0.5  $\mu$ s in register bits CH1\_SR\_DVC and CH2\_SR\_DVC.

A pull-down resistor (typically 150  $\Omega$ ) for each phase is always activated unless it is disabled by setting register bits CH<x>\_PD\_DIS to 1.

### 4.1.1 Switching Frequency

The buck switching frequency can be tuned using register bit OSC\_TUNE. The internal 8 MHz oscillator frequency is tuned in  $\pm 160$  kHz steps. This impacts the buck converter frequency in steps of 80 kHz and helps to mitigate possible disturbances to other high frequency systems in the application.

### 4.1.2 Operation Modes and Phase Selection

The buck converters can operate in PWM and PFM modes. The operating mode is selected using register bits CH1\_<A or B>\_MODE and CH2\_<A or B>\_MODE.

If the automatic operation mode is selected on CH1\_<A or B>\_MODE or CH2\_<A or B>\_MODE, the buck converters automatically change between synchronous PWM mode and PFM depending on the load current. This improves the efficiency across the whole range of output load currents.

### 4.1.3 Output Voltage Selection

The switching converter can be configured using the I<sup>2</sup>C interface.

For each buck converter two output voltages can be pre-configured in registers CH<x>\_<A or B>\_VOUT. The output voltage can be selected by either toggling register bit CH<x>\_VSEL or by reprogramming the selected voltage control register. Both changes will result in ramped voltage transitions. After being enabled, the buck converter will, by default, use the register settings in CH<x>\_A\_VOUT unless the output voltage selection is configured via the GPI port.

Registers CH<1 and 2>\_VMAX limit the output voltage that can be set for each of the respective buck converters.

#### 4.1.4 Soft Start-Up and Shutdown

To limit in-rush current from VSYS, the buck converters can perform a soft-start after being enabled. The start-up behavior is a compromise between acceptable inrush current from the battery and turnon time. Individual ramp times can be configured for each buck converter in registers CH<1 and 2>\_SR\_STARTUP respectively. Rates higher than 20 mV/µs may produce overshoot during the start-up phase, so they should be considered carefully.

A ramped power down can be selected in register bits CH<1 and 2>\_SR\_SHDN. When no ramp is selected (immediate power down), the output node will be discharged only by the pull-down resistor, if enabled in registers CH<1 and 2>\_PD\_DIS.

#### 4.1.5 Current Limit

The integrated current limit protects the power stages and external coil from excessive current. The buck current limit should be configured to at least 40 % higher than the required maximum output current.

When the current limit is reached, each buck converter generates an event and an interrupt to the host processor unless the interrupt has been masked using register M\_OC<x> in SYS\_MASK\_1. Register bits OC\_DVC\_MASK is used to mask over-current events during DVC transitions.

| _  |     | _     |  |

|----|-----|-------|--|

| Da | tac | heet  |  |

| υa | ιas | 11661 |  |

## High-Performance Dual-Channel DC-DC Converter

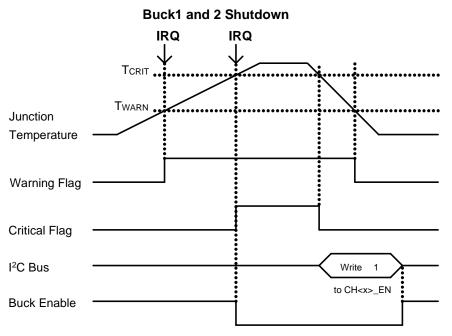

### 4.1.6 Thermal Protection

DA9220 is protected from internal overheating by thermal shutdown.

There are two kinds of flags concerning thermal protection, thermal warning and thermal critical. The warning flag is asserted when  $T_J > T_{WARN}$  and the critical flag is asserted when  $T_J > T_{CRIT}$ . When the critical flag is asserted, Buck1 and 2 are shut down immediately.

| Category  | Register name | Description                                                   |

|-----------|---------------|---------------------------------------------------------------|

| Statua    | TEMP_WARN     | Asserted as long as the thermal warning threshold is reached  |

| Status    | TEMP_CRIT     | Asserted as long as the thermal shutdown threshold is reached |

| IDO event | E_TEMP_WARN   | TEMP_WARN caused event                                        |

| IRQ event | E_TEMP_CRIT   | TEMP_CRIT caused event                                        |

|           | M_TEMP_WARN   | TEMP_WARN event IRQ mask                                      |

| IRQ mask  | M_TEMP_CRIT   | TEMP_CRIT event IRQ mask                                      |

|           | M_VR_HOT      | TEMP_WARN status IRQ mask                                     |

#### **Table 12: Thermal Protection Control Registers**

### 4.2 Internal Circuits

#### 4.2.1 IC\_EN/Chip Enable/Disable

IC\_EN is chip enable/disable control input. When IC\_EN = 0, all blocks except for low  $I_Q$  POR are powered-down and buck output is pulled-down.

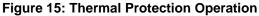

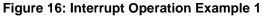

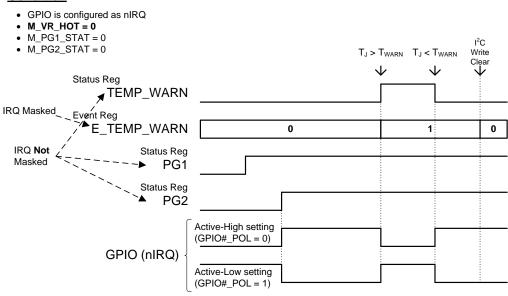

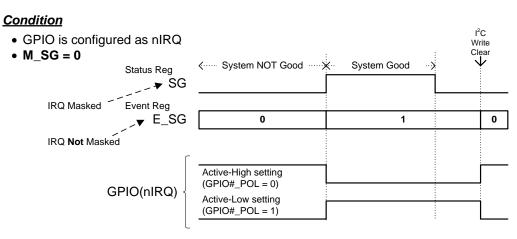

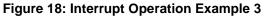

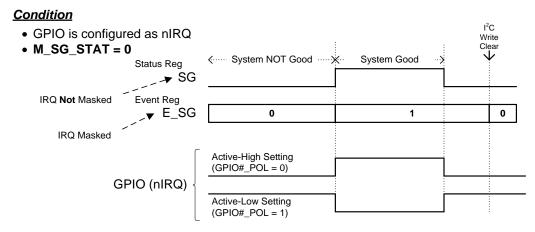

#### 4.2.2 nIRQ/Interrupt

The interrupt triggers events. Trigger conditions and control registers for each interrupt event are listed in Table 13.

Some of these events are categorized as fault events and affect device operation (for example, buck disable), see Section 4.1.6.

| Name                                  | Polarity<br>(Note 1) | Trigger                                                                                                     | IRQ Status<br>Register | IRQ Mask<br>Register | Deglitch<br>Period     |

|---------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------|------------------------|----------------------|------------------------|

| Thermal<br>warning<br>(event)         | N                    | $T_J$ rising above $T_{WARN}$                                                                               | E_TEMP_WARN            | M_TEMP_WARN          | 0 s                    |

| Thermal<br>critical<br>(event)        | N                    | TJ rising above TCRIT                                                                                       | E_TEMP_CRIT            | M_TEMP_CRIT          | 0 s                    |

| System<br>good<br>(event)             | Ρ                    |                                                                                                             | E_SG                   | M_SG                 | 0 s                    |

| Buck1<br>power-good<br>(event)        | Р                    | Buck1 V <sub>OUT</sub> is in power-good<br>voltage range<br>(not under- or over-voltage)                    | E_PG1                  | M_PG1                | 0 s                    |

| Buck2<br>power-good<br>(event)        | Ρ                    | Buck2 V <sub>OUT</sub> is in power-good<br>voltage range<br>(not under- or over-voltage)                    | E_PG2                  | M_PG2                | 0 s                    |

| Buck1<br>over-voltage<br>(event)      | N                    | Buck1 V <sub>OUT</sub> rising above<br>over-voltage<br>threshold (target voltage +<br>150 mV)               | E_OV1                  | M_OV1                | Rise:8 µs<br>Fall:8 µs |

| Buck2<br>over-voltage<br>(event)      | N                    | Buck2 V <sub>OUT</sub> rising above<br>over-voltage<br>threshold (target voltage +<br>150 mV)               | E_OV2                  | M_OV2                | Rise:8 µs<br>Fall:8 µs |

| Buck1<br>under-<br>voltage<br>(event) | N                    | Buck1 V <sub>OUT</sub> falling below<br>under-voltage<br>threshold (target voltage -<br>V <sub>TH_PG)</sub> | E_UV1                  | M_UV1                | 0 s                    |

| Buck2<br>under-<br>voltage<br>(event) | N                    | Buck2 Vout falling below<br>under-voltage threshold<br>(target voltage - Vth_PG)                            | E_UV2                  | M_UV2                | 0 s                    |

| Buck1<br>over-current<br>(event)      | N                    | Buck1 current rising above<br>over-current threshold                                                        | E_OC1                  | M_OC1                | 0 s                    |

#### Table 13: Interrupt List

## High-Performance Dual-Channel DC-DC Converter

| Name                                        | Polarity<br>(Note 1) | Trigger                                                                                  | IRQ Status<br>Register | IRQ Mask<br>Register   | Deglitch<br>Period                  |

|---------------------------------------------|----------------------|------------------------------------------------------------------------------------------|------------------------|------------------------|-------------------------------------|

| Buck2<br>over-current<br>(event)            | N                    | Buck2 current rising above<br>over-current threshold                                     | E_OC2                  | M_OC2                  | 0 s                                 |

| Buck1<br>power-good<br>(status)<br>(Note 2) | Ρ                    | Buck1 V <sub>OUT</sub> is in power-good<br>voltage range<br>(not under- or over-voltage) | PG1                    | M_PG1_STAT<br>(Note 3) | 0 s                                 |

| Buck2<br>power-good<br>(status)<br>(Note 2) | Ρ                    | Buck2 V <sub>OUT</sub> is in power-good<br>voltage range<br>(not under- or over-voltage) | PG2                    | M_PG2_STAT<br>(Note 3) | 0 s                                 |

| System<br>good<br>(status)<br>(Note 2)      | Ρ                    |                                                                                          | SG                     | M_SG_STAT<br>(Note 3)  | 0 s                                 |

| Thermal<br>warning<br>(status)<br>(Note 2)  | N                    | $T_J$ rising above $T_{WARN}$                                                            | TEMP_WARN              | M_VR_HOT<br>(Note 3)   | 0 s                                 |

| GPIO0<br>change<br>(event)                  | N                    | Detect GPIO0 change for<br>active trigger<br>selected GPIO0_TRIG<br>register             | E_GPIO0                | M_GPIO0                | 100 µs/                             |

| GPIO1<br>change<br>(event)                  | N                    | Detect GPIO1 change for<br>active trigger<br>selected GPIO1_TRIG<br>register             | E_GPIO1                | M_GPIO1                | 1 ms/<br>10 ms/<br>10 ms/<br>100 ms |

| GPIO2<br>change<br>(event)                  | Ν                    | Detect GPIO2 change for<br>active trigger<br>selected GPIO2_TRIG<br>register             | E_GPIO2                | M_GPIO2                |                                     |

**Note 1** Polarity at the source of the flag: P = active-high, N = active-low.

General rule is: normal system state is high, and abnormal system state is low (for example, PG = high means power-good, TEMP\_CRIT = low when TEMP critical state).

**Note 2** Interrupt outputs the status as is. I<sup>2</sup>C write is not required for interrupt clear.

**Note 3** OTP load value defined by CONF pin setting if CONF\_EN = 1.

#### Table 14: Interrupt Registers Except for Power Good Status

| Register         | Description                                                                  |

|------------------|------------------------------------------------------------------------------|

| E_ <name></name> | Read-only interrupt event register                                           |

|                  | 0: No interrupt                                                              |

|                  | 1: Interrupt occurred                                                        |

|                  | Cleared after being written to I <sup>2</sup> C. Set until IRQ is removed.   |

| M_ <name></name> | Interrupt mask register                                                      |

|                  | 0: Not masked                                                                |

|                  | 1: Masked. No IRQ signal sent. Event register (E_ <name>) is updated.</name> |

#### Table 15: Interrupt Registers for Power Good, System Good, and Temp Warning Status

| Register          | Description                                                                                                                                                                                                               |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PG <x></x>        | Buck <x> power good status. Asserted as long as the buck<x> output voltage is in range<br/>(under-voltage threshold &lt; buck output voltage &lt; over-voltage threshold)<br/>0: Not power good<br/>1: Power good</x></x> |

| M_PG <x>_STAT</x> | Power good status interrupt mask register<br>0: Not masked<br>1: Masked. No IRQ signal sent. Power good status register (PG <x>) is updated</x>                                                                           |

| SG                | System good status<br>0: Not system good<br>1: System good                                                                                                                                                                |

| M_SG_STAT         | System good status (SG) interrupt mask register<br>0: Not masked<br>1: Masked. No IRQ signal sent. System good status register (SG) is updated                                                                            |

| TEMP_WARN         | Asserted as long as the thermal warning threshold (T <sub>WARN</sub> ) is reached<br>0: Junction temperature is below T <sub>WARN</sub><br>1: Junction temperature is above T <sub>WARN</sub>                             |

| M_VR_HOT          | Temperature warning status (TEMP_WARN) interrupt mask register<br>0: Not masked<br>1: Masked. No IRQ signal sent. Temperature warning status register (TEMP_WARN) is<br>updated                                           |

#### <u>Condition</u>

Figure 17: Interrupt Operation Example 2

Figure 19: Interrupt Operation Example 4

#### 4.2.3 GPIO

#### 4.2.3.1 GPIO Pin Assignment

The DA9220 provides up to five GPIO pins, three if the  $I^2C$  is enabled, see Table 16. These registers are OTP programmable. When CONF\_EN = 1 GPIO0 can be used for chip configuration.

Any register settings for GPIO3 and GPIO4 are ignored and GPIO3 and GPIO4 function as SCL and SDA respectively if I2C\_EN = 1.

#### Table 16: GPIO Pin Assignment

| OTP Option |         | GPIO Pin       |       |       |               | Available     |       |

|------------|---------|----------------|-------|-------|---------------|---------------|-------|

| I2C_EN     | CONF_EN | CONF/<br>GPIO0 | GPI01 | GPIO2 | SCL/<br>GPIO3 | SDA/<br>GPIO4 | GPIOs |

| 1'b0       | 1'b0    | GPIO0          | GPIO1 | GPIO2 | GPIO3         | GPIO4         | 5     |

|            | 1'b1    | CONF           | GPIO1 | GPIO2 | GPIO3         | GPIO4         | 4     |

| 1'b1       | 1'b0    | GPIO0          | GPIO1 | GPIO2 | SCL           | SDA           | 3     |

|            | 1'b1    | CONF           | GPIO1 | GPIO2 | SCL           | SDA           | 2     |

#### 4.2.3.2 GPIO Function

The GPIOs pins are configurable as the following functions in register GPIO<x>\_MODE (x = 0 to 4):

- Buck1 enable input (EN1)

- Buck2 enable input (EN2)

- Buck1 and Buck2 enable input (EN1 & EN2)

- Buck1 DVC control input (DVC1)

- Buck2 DVC control input (DVC2)

- Buck1 and Buck2 DVC control input (DVC1 & DVC2)

- Buck1 and Buck2 OTP setting reload input (RELOAD)

- Buck1 power good output (PG1)

- Buck2 power good output (PG2)

- Buck1 power good and Buck2 power good output (PG1 & PG2)

- System good output (SG)

- Interrupt output (nIRQ)

#### Table 17: GPIO Function Configuration

| GPIO <x>_MODE[3:0]</x> | Function     | IO Condition |

|------------------------|--------------|--------------|

| 4'h0                   | GPIO disable | HiZ          |

| 4'h1                   | EN1          | In           |

| 4'h2                   | EN2          | In           |

| 4'h3                   | EN1 & EN2    | In           |

| 4'h4                   | DVC1         | In           |

| 4'h5                   | DVC2         | In           |

| 4'h6                   | DVC1 & DVC2  | In           |

| 4'h7                   | RELOAD       | In           |

| 4'h8                   | PG1          | Out          |

| 4'h9                   | PG2          | Out          |

**Datasheet**

**Revision 2.1**

| GPIO <x>_MODE[3:0]</x> | Function   | IO Condition |

|------------------------|------------|--------------|

| 4'hA                   | PG1 & PG2  | Out          |

| 4'hB                   | SG         | Out          |

| 4'hC                   | nIRQ       | Out          |

| 4'hD                   | Reserved   | HiZ          |

| 4'hE                   | Low level  | Out          |

| 4'hF                   | High level | Out          |

| _  |        | _ |    |

|----|--------|---|----|

|    | 400    |   | -  |

| Da | tas    |   | ет |

|    | - COLO |   | ~  |

#### 4.2.3.3 Chip Configuration Select (CONF)

GPIO0 functions as chip configuration select (CONF) input when CONF\_EN = 1.

Three different chip configurations can be selected according to the CONF pin level, whether it is HIGH, LOW, or Hi-Z.

#### Table 18: GPIO0-Configurable Registers when CONF\_EN = 1

| Register Name      | Description                                |

|--------------------|--------------------------------------------|

| IF_SLAVE_ADDR[6:0] | I2C slave address                          |

| CH1_A_MODE[1:0]    | CH1_A Operation mode select                |

| CH1_B_MODE[1:0]    | CH1_B Operation mode select                |

| CH1_VSEL           | CH1 output voltage and operation selection |

| CH1_EN             | CH1 enable                                 |

| CH1_A_VOUT[7:0]    | CH1 output voltage setting A               |

| CH1_B_VOUT[7:0]    | CH1 output voltage setting B               |

| CH2_A_MODE[1:0]    | CH2_A Operation mode select                |

| CH2_B_MODE[1:0]    | CH2_B Operation mode select                |

| CH2_VSEL           | CH2 output voltage and operation selection |

| CH2_EN             | CH2 enable                                 |

| CH2_A_VOUT[7:0]    | CH2 output voltage setting A               |

| CH2_B_VOUT[7:0]    | CH2 output voltage setting B               |

| M_PG1_STAT         | IRQ mask setting for CH1 power good status |

| M_PG2_STAT         | IRQ mask setting for CH2 power good status |

| M_SG_STAT          | IRQ mask setting for system good status    |

| M_VR_HOT           | IRQ mask setting for temp warning status   |

| CH1_EN_DLY[3:0]    | Delay setting for CH1 enable               |

| CH1_DIS_DLY[3:0]   | Delay setting for CH1 disable              |

| CH2_EN_DLY[3:0]    | Delay setting for CH2 enable               |

| CH2_DIS_DLY[3:0]   | Delay setting for CH2 disable              |

| GPIO1_MODE[3:0]    | GPIO1 mode setting                         |

| GPIO2_MODE[3:0]    | GPIO2 mode setting                         |

| GPIO1_OBUF         | GPIO1 output buffer select                 |

| GPIO2_OBUF         | GPIO2 output buffer select                 |

| GPIO1_TRIG[1:0]    | GPIO1 input trigger select                 |

| GPIO1_POL          | GPIO1 polarity select                      |

| GPIO1_PUPD         | GPIO1 pull-up/pull-down enable             |

| GPIO1_DEB[1:0]     | GPIO1 input debounce time setting          |

| GPIO1_DEB_RISE     | GPIO1 input debounce rising edge enable    |

| GPIO1_DEB_FALL     | GPIO1 input debounce falling edge enable   |

| GPIO2_TRIG[1:0]    | GPIO2 input trigger select                 |

| GPIO2_POL          | GPIO2 polarity select                      |

|                    |                                            |

#### Datasheet

#### **Revision 2.1**

## High-Performance Dual-Channel DC-DC Converter

| Register Name  | Description                              |

|----------------|------------------------------------------|

| GPIO2_DEB[1:0] | GPIO2 input debounce time setting        |

| GPIO2_DEB_RISE | GPIO2 input debounce rising edge enable  |

| GPIO2_DEB_FALL | GPIO2 input debounce falling edge enable |

#### 4.2.3.4 OTP Reload (RELOAD)

Buck settings listed in Table 19 are reloaded from CONF registers by triggering GPIO configured as RELOAD input.

The OTP reload happens at the same time for Buck1 and Buck2 settings. During reloading, Buck1/2 keep operating as configured without shut-down.

| Register Name   | Description                                                                           |

|-----------------|---------------------------------------------------------------------------------------|

| CH#_VSEL        | CH# output voltage and operation selection.                                           |

|                 | 0: A, 1: B                                                                            |

| CH#_A_VOUT[7:0] | CH# output voltage setting A : CH#_A_VOUT * 10 mV                                     |

|                 | Setting under 0.3V is clamped to 0.3V, and setting over 1.9V is clamped to 1.9 V $$   |

| CH#_B_VOUT[7:0] | CH# output voltage setting B : CH#_A_VOUT * 10 mV                                     |

|                 | Setting under 0.3 V is clamped to 0.3 V, and setting over 1.9V is clamped to 1.9 V $$ |

| CH#_A_MODE[1:0] | Operation mode selection                                                              |

|                 | 0: Force PFM                                                                          |

|                 | 1: Force PWM. full phase                                                              |

|                 | 2: Force PWM with phase shedding                                                      |

|                 | 3: Auto mode                                                                          |

| CH#_B_MODE[1:0] | Operation mode selection                                                              |

|                 | 0: Force PFM                                                                          |

|                 | 1: Force PWM. full phase                                                              |

|                 | 2: Force PWM with phase shedding                                                      |

|                 | 3: Auto mode                                                                          |

#### Table 19: OTP Reload Registers

## 4.3 **Operating Modes**

#### 4.3.1 ON

DA9220 is ON when the IC\_EN port is higher than  $V_{IH_{EN}}$  and the supply voltage is higher than  $V_{THR_{POR}}$ . Once enabled, the host processor can start communicating with DA9220 using the control interface, after the t<sub>IC\_EN</sub> delay.

#### 4.3.2 OFF

DA9220 is OFF when the IC\_EN port is lower than V<sub>IL\_EN</sub>. In OFF, the bucks are always disabled and LX nodes are pulled down by (typically 150  $\Omega$ ) internal pull-down resistors.

### 4.4 I<sup>2</sup>C Communication

All features of DA9220 can be controlled with the I<sup>2</sup>C interface which is enabled or disabled in register I2C\_EN.

## High-Performance Dual-Channel DC-DC Converter

| I2C_EN | Description                                                                                                                            |

|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| 0      | I <sup>2</sup> C disable: SCL/GPIO3 and SDA/GPIO4 pins can be used as GPIO                                                             |

| 1      | I <sup>2</sup> C enable: SCL/GPIO3 and SDA/GPIO4 pins are used as I <sup>2</sup> C clock input and I <sup>2</sup> C data input/output. |

GPIO3 functions as the I<sup>2</sup>C clock and GPIO4 carries all the power manager bidirectional I<sup>2</sup>C data. The I<sup>2</sup>C interface is open-drain supporting multiple devices on a single line. The bus lines have to be pulled high by external pull-up resistors (2 k $\Omega$  to 20 k $\Omega$ ). The standard frequency of the I<sup>2</sup>C bus is 1 MHz in fast-mode plus (FM+), 400 kHz in fast-mode, or 100 kHz in standard mode.

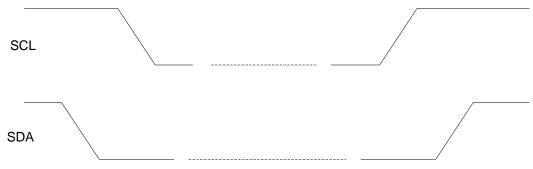

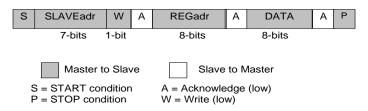

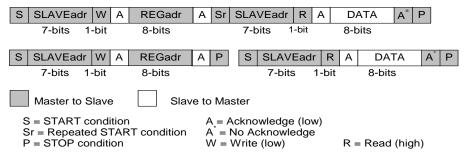

### 4.4.1 I<sup>2</sup>C Protocol

All data is transmitted across the I<sup>2</sup>C bus in eight-bit groups. To send a bit, the SDA line is driven towards the intended state while the SCL is low (a low SDA indicates a zero bit). Once the SDA has settled, the SCL line is brought high and then low. This pulse on SCL clocks the SDA bit into the receiver's shift register.

A two-byte serial protocol is used containing one byte for address and one byte data. Data and address transfer are transmitted MSB first for both read and write operations. All transmissions begin with the START condition from the master while the bus is in idle state (the bus is free). It is initiated by a high to low transition on the SDA line while the SCL is in the high state (a STOP condition is indicated by a low to high transition on the SDA line while the SCL is in the high state).

Figure 21: I<sup>2</sup>C START and STOP Condition Timing

The I<sup>2</sup>C bus is monitored for a valid slave address whenever the interface is enabled. It responds immediately when it receives its own slave address. The acknowledge is done by pulling the SDA line low during the following clock cycle (white blocks marked with A in Figure 22 and Figure 23).

The protocol for a register write from master to slave consists of a START condition, a slave address with read/write bit, and the eight-bit register address followed by eight bits of data, terminated by a STOP condition. DA9220 responds to all bytes with acknowledge (A), see Figure 22.

When the host reads data from a register it first has to write to DA9220 with the target register address and then read from DA9220 with a repeated START, or alternatively a second START, condition. After receiving the data, the host sends no acknowledge (A\*) and terminates the transmission with a STOP condition, see Figure 23.

| Datas | shoot |  |

|-------|-------|--|

| Dalas | sneet |  |

Figure 23: I<sup>2</sup>C Byte Read (SDA Line) Examples

# High-Performance Dual-Channel DC-DC Converter

# **5 Register Definitions**

## 5.1 Register Map

### Table 20: Register Map

| Addr     | Register     | 7                  | 6                  | 5         | 4               | 3              | 2             | 1               | 0               |

|----------|--------------|--------------------|--------------------|-----------|-----------------|----------------|---------------|-----------------|-----------------|

| System I | Module       |                    |                    |           |                 |                |               |                 |                 |

| System   |              |                    |                    |           |                 |                |               |                 |                 |

| 0x0001   | SYS_STATUS_0 | Reserved           | Reserved           | Reserved  | Reserved        | Reserved       | SG            | TEMP_CRIT       | TEMP_W<br>ARN   |

| 0x0002   | SYS_STATUS_1 | PG2                | OV2                | UV2       | OC2             | PG1            | OV1           | UV1             | OC1             |

| 0x0003   | SYS_STATUS_2 | Reserved           | Reserved           | Reserved  | Reserved        | Reserved       | GPIO2         | GPIO1           | GPIO0           |

| 0x0004   | SYS_EVENT_0  | Reserved           | Reserved           | Reserved  | Reserved        | Reserved       | E_SG          | E_TEMP_C<br>RIT | E_TEMP_<br>WARN |

| 0x0005   | SYS_EVENT_1  | E_PG2              | E_OV2              | E_UV2     | E_OC2           | E_PG1          | E_OV1         | E_UV1           | E_OC1           |

| 0x0006   | SYS_EVENT_2  | Reserved           | Reserved           | Reserved  | Reserved        | Reserved       | E_GPIO2       | E_GPIO1         | E_GPIO0         |

| 0x0007   | SYS_MASK_0   | Reserved           | Reserved           | Reserved  | Reserved        | Reserved       | M_SG          | M_TEMP_C<br>RIT | M_TEMP_<br>WARN |

| 0x0008   | SYS_MASK_1   | M_PG2              | M_OV2              | M_UV2     | M_OC2           | M_PG1          | M_OV1         | M_UV1           | M_OC1           |

| 0x0009   | SYS_MASK_2   | Reserved           | Reserved           | Reserved  | Reserved        | Reserved       | M_GPIO2       | M_GPIO1         | M_GPIO0         |

| 0x000A   | SYS_MASK_3   | Reserved           | Reserved           | Reserved  | Reserved        | M_VR_HO<br>T   | M_SG_STA<br>T | M_PG2_ST<br>AT  | M_PG1_S<br>TAT  |

| 0x000B   | SYS_CONFIG_0 | CH1_DIS_D          | LY<3:0>            |           |                 | CH1_EN_DL      | .Y<3:0>       |                 |                 |

| 0x000C   | SYS_CONFIG_1 | CH2_DIS_D          | LY<3:0>            |           |                 | CH2_EN_DL      | .Y<3:0>       |                 |                 |

| 0x000D   | SYS_CONFIG_2 | Reserved           | OC_LATCHO          | OFF<1:0>  | OC_DVC_<br>MASK | PG_DVC_M       | ASK<1:0>      | Reserved        | Reserved        |

| 0x000E   | SYS_CONFIG_3 | Reserved           | OSC_TUNE           | <2:0>     |                 | Reserved       | Reserved      | I2C_TIMEO<br>UT | Reserved        |

| 0x0010   | SYS_GPIO0_0  | Reserved           | Reserved           | Reserved  | GPIO0_MOE       | DE<3:0>        |               |                 | GPIO0_O<br>BUF  |

| 0x0011   | SYS_GPIO0_1  | GPIO0_D<br>EB_FALL | GPIO0_D<br>EB_RISE | GPIO0_DEB | <1:0>           | GPIO0_P<br>UPD | GPIO0_POL     | GPIO0_TRIG<     | :1:0>           |

| 0x0012   | SYS_GPIO1_0  | Reserved           | Reserved           | Reserved  | GPIO1_MOE       | DE<3:0>        |               |                 | GPIO1_O<br>BUF  |

| 0x0013   | SYS_GPIO1_1  | GPIO1_D<br>EB_FALL | GPIO1_D<br>EB_RISE | GPIO1_DEB | <1:0>           | GPIO1_P<br>UPD | GPIO1_POL     | GPIO1_TRIG      | :1:0>           |

| 0x0014   | SYS_GPIO2_0  | Reserved           | Reserved           | Reserved  | GPIO2_MOE       | DE<3:0>        |               |                 | GPIO2_O<br>BUF  |

| 0x0015   | SYS_GPIO2_1  | GPIO2_D<br>EB_FALL | GPIO2_D<br>EB_RISE | GPIO2_DEB | <1:0>           | GPIO2_P<br>UPD | GPIO2_POL     | GPIO2_TRIG<     | :1:0>           |

## High-Performance Dual-Channel DC-DC Converter

| Addr       | Register        | 7                 | 6               | 5          | 4            | 3           | 2                  | 1                  | 0              |

|------------|-----------------|-------------------|-----------------|------------|--------------|-------------|--------------------|--------------------|----------------|

| Buck Cor   | Buck Control    |                   |                 |            |              |             |                    |                    |                |

| Buck1      | Buck1           |                   |                 |            |              |             |                    |                    |                |

| 0x0020     | BUCK_BUCK1_0    | Reserved          | CH1_SR_DV       | C_DWN<2:0> |              | CH1_SR_DV   | C_UP<2:0>          |                    | CH1_EN         |

| 0x0021     | BUCK_BUCK1_1    | Reserved          | CH1_SR_SH       | DN<2:0>    |              | CH1_SR_ST   | ARTUP<2:0>         |                    | CH1_PD_<br>DIS |

| 0x0022     | BUCK_BUCK1_2    | Reserved          | Reserved        | Reserved   | Reserved     | CH1_ILIM<3: | 0>                 |                    |                |

| 0x0023     | BUCK_BUCK1_3    | CH1_VMAX<         | :7:0>           |            |              |             |                    |                    |                |

| 0x0024     | BUCK_BUCK1_4    | Reserved          | Reserved        | Reserved   | CH1_VSE<br>L | CH1_B_MOD   | 0E<1:0>            | CH1_A_MODE         | =<1:0>         |

| 0x0025     | BUCK_BUCK1_5    | CH1_A_VOL         | IT<7:0>         |            |              |             |                    |                    |                |

| 0x0026     | BUCK_BUCK1_6    | CH1_B_VOL         | IT<7:0>         |            |              |             |                    | -                  |                |

| 0x0027     | BUCK_BUCK1_7    | Reserved          | Reserved        | Reserved   | Reserved     | Reserved    | Reserved           | CH1_RIPPLE_<br>:0> | CANCEL_<1      |

| Buck2      |                 |                   |                 |            |              |             |                    |                    |                |

| 0x0028     | BUCK_BUCK2_0    | Reserved          | CH2_SR_DV       | C_DWN<2:0> |              | CH2_SR_DV   | CH2_SR_DVC_UP<2:0> |                    |                |

| 0x0029     | BUCK_BUCK2_1    | Reserved          | CH2_SR_SH       | DN<2:0>    |              | CH2_SR_ST   | ARTUP<2:0>         |                    | CH2_PD_<br>DIS |

| 0x002A     | BUCK_BUCK2_2    | Reserved          | Reserved        | Reserved   | Reserved     | CH2_ILIM<3: | 0>                 |                    |                |

| 0x002B     | BUCK_BUCK2_3    | CH2_VMAX<         | :7:0>           |            |              |             |                    |                    |                |

| 0x002C     | BUCK_BUCK2_4    | Reserved          | Reserved        | Reserved   | CH2_VSE<br>L | CH2_B_MOD   | 0E<1:0>            | CH2_A_MODE         | =<1:0>         |

| 0x002D     | BUCK_BUCK2_5    | CH2_A_VOL         | IT<7:0>         |            |              |             |                    |                    |                |

| 0x002E     | BUCK_BUCK2_6    | CH2_B_VOL         | CH2_B_VOUT<7:0> |            |              |             |                    |                    |                |

| 0x002F     | BUCK_BUCK2_7    | Reserved          | Reserved        | Reserved   | Reserved     | Reserved    | Reserved           | CH2_RIPPL<br>1:0>  | E_CANCEL<      |

| Serializat | ion             |                   |                 |            |              |             |                    |                    |                |

| 0x0048     | OTP_DEVICE_ID   | DEV_ID<7:0>       |                 |            |              |             |                    |                    |                |

| 0x0049     | OTP_VARIANT_ID  | MRC<3:0> VRC<3:0> |                 |            |              |             |                    |                    |                |

| 0x004A     | OTP_CUSTOMER_ID | CUST_ID<7:0>      |                 |            |              |             |                    |                    |                |

| 0x004B     | OTP_CONFIG_ID   | CONFIG_REV<7:0>   |                 |            |              |             |                    |                    |                |

## 5.1.1 System

#### Table 21: SYS\_STATUS\_0 (0x0001)

| Bit | Symbol    | Description                                                     |

|-----|-----------|-----------------------------------------------------------------|

| [2] | SG        | Asserted as long as the enabled buck output voltage is in range |

| [1] | TEMP_CRIT | Asserted as long as the thermal shutdown threshold is reached   |

| [0] | TEMP_WARN | Asserted as long as the thermal warning threshold is reached    |

| Bit | Symbol | Description                                              |

|-----|--------|----------------------------------------------------------|

| [7] | PG2    | Asserted as long as the Buck2 output voltage is in range |

| [6] | OV2    | Asserted as long as Buck2 hitting over-voltage           |

| [5] | UV2    | Asserted as long as Buck2 hitting under-voltage          |

| [4] | OC2    | Asserted as long as Buck2 hitting over-current           |

| [3] | PG1    | Asserted as long as the Buck1 output voltage is in range |

| [2] | OV1    | Asserted as long as Buck1 hitting over-voltage           |

| [1] | UV1    | Asserted as long as Buck1 hitting under-voltage          |

| [0] | OC1    | Asserted as long as Buck1 hitting over-current           |

#### Table 22: SYS\_STATUS\_1 (0x0002)

#### Table 23: SYS\_STATUS\_2 (0x0003)

| Bit | Symbol | Description  |

|-----|--------|--------------|

| [2] | GPIO2  | GPIO2 status |

| [1] | GPIO1  | GPIO1 status |

| [0] | GPIO0  | GPIO0 status |

#### Table 24: SYS\_EVENT\_0 (0x0004)

| Bit | Symbol      | Description                                                                                       |

|-----|-------------|---------------------------------------------------------------------------------------------------|

| [2] | E_SG        | SG caused event. Writing 1 action clear this bit into 0 if event source has been released.        |

| [1] | E_TEMP_CRIT | TEMP_CRIT caused event. Writing 1 action clear this bit into 0 if event source has been released. |

| [0] | E_TEMP_WARN | TEMP_WARN caused event. Writing 1 action clear this bit into 0 if event source has been released. |

| Bit | Symbol | Description                                                                                 |

|-----|--------|---------------------------------------------------------------------------------------------|

| [7] | E_PG2  | PG2 caused event. Writing 1 action clear this bit into 0 if event source has been released. |

| [6] | E_OV2  | OV2 caused event. Writing 1 action clear this bit into 0 if event source has been released. |

| [5] | E_UV2  | UV2 caused event. Writing 1 action clear this bit into 0 if event source has been released. |

| [4] | E_OC2  | OC2 caused event. Writing 1 action clear this bit into 0 if event source has been released. |

| [3] | E_PG1  | PG1 caused event. Writing 1 action clear this bit into 0 if event source has been released. |