## **General description**

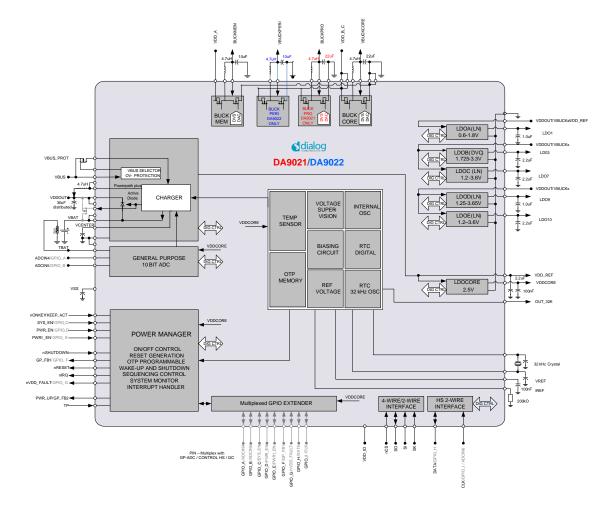

The DA9021/22 family is a highly integrated PMIC subsystem with supply domains to support a wide range of application processors, associated peripherals, and user interface functions. Combining a switched-mode USB compatible charger, full power-path management, three bucks, five linear regulators and support for multiple sleep modes, the DA9021 offers an energy-optimised solution suitable for portable handheld, wireless and, infotainment applications.

DA9021/22 comes in a 4 x 4 mm, 64-bump, WLCSP package making it ideal for space constrained applications.

The high-efficiency Li-Ion/Polymer switching charger supports precise current/voltage charging as well as pre-charge and USB modes without processor interaction. During charging, the die temperature is thermally regulated enabling high-capacity batteries to be rapidly charged at currents up to 1.26 A with minimum thermal impact to space-constrained PCBs.

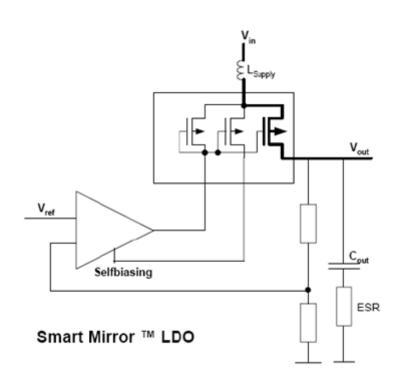

DA9021 offers a merged buck configuration for a combined 1.6 A or DA9022 offers a higher voltage capability on one DC-DC buck converter which is ideal for peripherals and memory running up to 3.6 V. USB suspend mode operation is supported and, for robustness, the power input is protected against over-voltage conditions.

The internally generated system power rail supports power scenarios such as instant-on with a fully discharged battery.

The power efficiency and flexibility of the switching DC-DC bucks is maintained to generate the various supply domains.

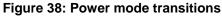

Controlled by a programmable digital power manager, the eight user-programmable switched/linear regulators may be configured to meet the start-up sequence, voltage, and timing requirements for most applications. The power manager includes supply-rail qualification and system reset management. For optimal processor energy-per-task performance, Dynamic Voltage Scaling (DVS) is available on up to four supply domains. Dialog's patented SmartMirror™ dynamic biasing is implemented on all linear regulators.

## **Key features**

- Switched USB charger with power path management

- Three buck converters with DVC, 0.5 V to 3.6 V, up to 800 mA

- Five programmable LDOs, high PSRR, 1 % accuracy

- 32 kHz RTC oscillator

- An integrated 7-channel general purpose ADC

## **Applications**

- Personal media players

- Smartphone handsets

- 9-bit GPIO bus for enhanced wakeup and peripheral control

- HS2-wire and 4-wire control interfaces

- Unique USB supply detection and charge current selection

- 64 WLCSP 4x4 mm, 0.5 mm pitch package

- Personal navigation devices

- Consumer infotainment devices

- IoT

## System PMIC with high efficiency USB power manager

## Contents

| Ge  | neral o | descriptio | on                                                | 1           |

|-----|---------|------------|---------------------------------------------------|-------------|

| Ke  | y featu | ıres       |                                                   | 1           |

| Ap  | plicati | ons        |                                                   | 1           |

| Со  | ntents  |            |                                                   | 2           |

| Fia | ures    |            |                                                   |             |

| -   |         |            |                                                   |             |

|     |         |            | initions                                          |             |

| 1   |         |            |                                                   |             |

| 2   |         | -          | 1                                                 |             |

| 3   | Gene    | rated sup  | oply domains                                      | 11          |

| 4   | Pad d   | lescriptio | on                                                | 12          |

| 5   | Abso    | lute maxi  | imum ratings                                      | 20          |

| 6   | Reco    | mmende     | d operating conditions                            | 21          |

| 7   |         |            | imption                                           |             |

| 8   |         |            | acteristics                                       |             |

| 0   | 8.1     |            | D characteristics                                 |             |

|     | 8.2     | 0          | aracteristics                                     |             |

|     | 8.3     |            | n reset characteristics                           |             |

|     | 8.4     |            | ontrol bus                                        |             |

|     | 8.5     |            | r characteristics                                 |             |

|     | 8.6     |            | e voltage generation and temperature supervision  |             |

|     | 8.7     |            | age regulators                                    |             |

|     |         | 8.7.1      | LDO1                                              | 25          |

|     |         | 8.7.2      | LDO3                                              |             |

|     |         | 8.7.3      | LDO7                                              | 27          |

|     |         | 8.7.4      | LDO9                                              | 28          |

|     |         | 8.7.5      | LDO10                                             | 29          |

|     |         | 8.7.6      | LDOCORE                                           | 30          |

|     | 8.8     | DC/DC b    | buck converters                                   | 31          |

|     |         | 8.8.1      | BUCKCORE                                          | 31          |

|     |         | 8.8.2      | BUCKPRO                                           |             |

|     |         | 8.8.3      | BUCKPERI                                          |             |

|     |         | 8.8.4      | BUCKMEM                                           |             |

|     | 8.9     | -          | harger                                            |             |

|     |         | 8.9.1      | Charger buck                                      |             |

|     |         | 8.9.2      | Voltage levels on VBAT                            |             |

|     |         | 8.9.3      | Charging modes                                    |             |

|     |         | 8.9.4      | Charger detection circuit                         |             |

|     |         | 8.9.5      | VBUS charge control                               |             |

|     |         | 8.9.6      | Charge timer                                      |             |

|     | 0.40    | 8.9.7      | DCCC and active-diode                             |             |

|     |         | Oscillato  |                                                   | 40          |

| -   |         |            | ce voltage generation and temperature supervision |             |

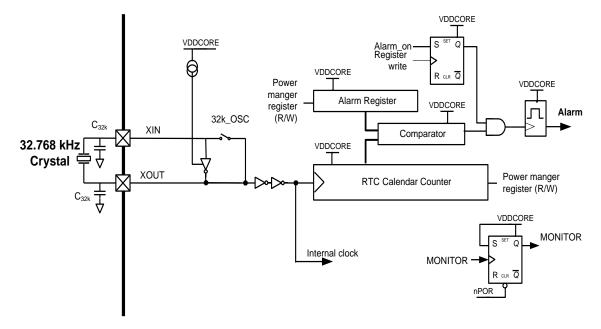

| 9   | Real    | time cloc  | k and 32 kHz oscillator                           | 41          |

| Dat | ashee   | et         | Revision 2.5                                      | 17-Feb-2017 |

|     | 9.1    | 32 kHz oscillator                                            | 41          |  |  |  |

|-----|--------|--------------------------------------------------------------|-------------|--|--|--|

|     | 9.2    | RTC counter and alarm                                        | 41          |  |  |  |

| 10  | Typic  | cal characteristics                                          | 43          |  |  |  |

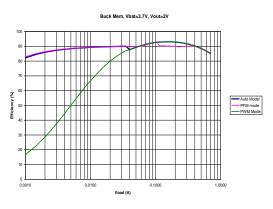

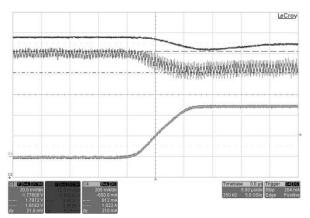

|     | 10.1   | Buck regulator performance                                   | 43          |  |  |  |

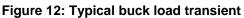

|     | 10.2   | Linear regulator performance                                 | 44          |  |  |  |

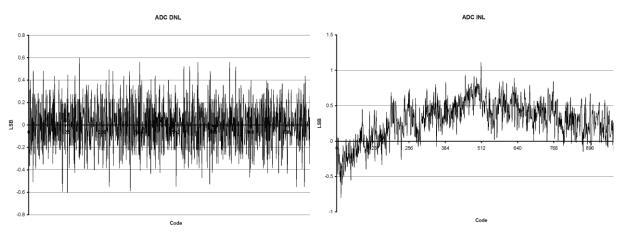

|     | 10.3   | ADC performance                                              | 45          |  |  |  |

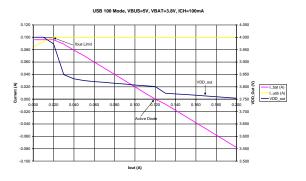

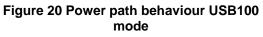

|     | 10.4   | Power path performance                                       | 45          |  |  |  |

| 11  | Func   | tional description                                           | 46          |  |  |  |

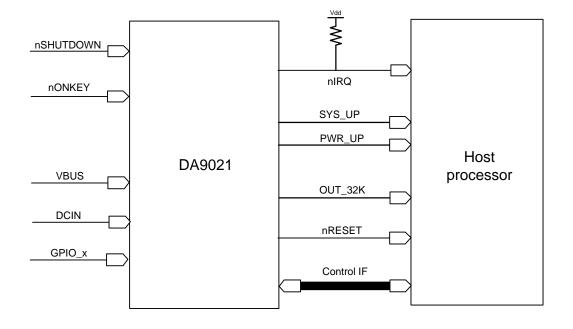

|     | 11.1   | Power manager IO ports                                       |             |  |  |  |

|     | 11.2   | On/off (nONKEY)                                              | 46          |  |  |  |

|     | 11.3   | Hardware reset (nSHUTDOWN, nONKEY, GPIO14 & GPIO15)          |             |  |  |  |

|     | 11.4   | Reset output (nRESET)                                        | 47          |  |  |  |

|     | 11.5   | System enable (SYS_EN)                                       | 47          |  |  |  |

|     | 11.6   | Power enable (PWR_EN)                                        | 47          |  |  |  |

|     | 11.7   | Power1 enable (PWR1_EN)                                      | 47          |  |  |  |

|     | 11.8   | General purpose feedback signal 1 (GP_FB1: EXT_WAKEUP/READY) | 47          |  |  |  |

|     | 11.9   | Power domain status (PWR_UP/GP_FB2)                          | 48          |  |  |  |

|     | 11.10  | ) Supply rail fault (nVDD_FAULT)                             | 48          |  |  |  |

|     | 11.11  | Interrupt request (nIRQ)                                     | 48          |  |  |  |

|     |        | 2 Real time clock output (OUT_32K)                           |             |  |  |  |

|     | 11.13  | 3 IO_supply voltage (VDD_IO)                                 | 48          |  |  |  |

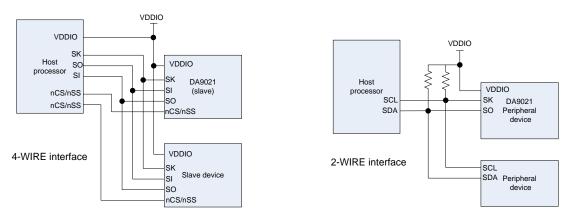

| 12  | Cont   | rol interfaces                                               | 49          |  |  |  |

|     | 12.1   | Power manager interface (4-wire and 2-wire control bus)      | 49          |  |  |  |

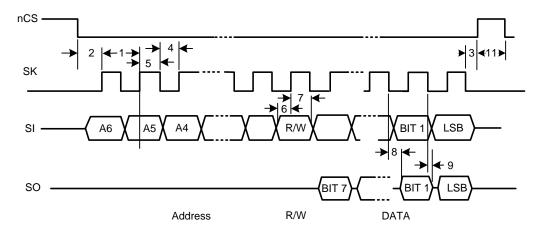

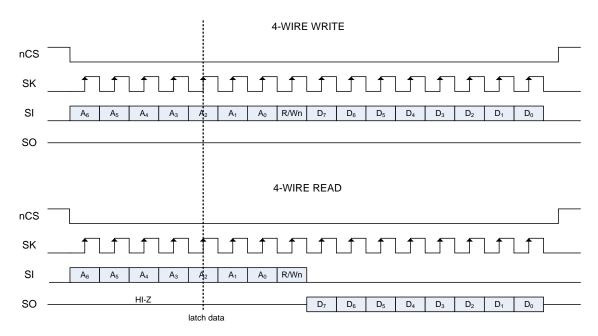

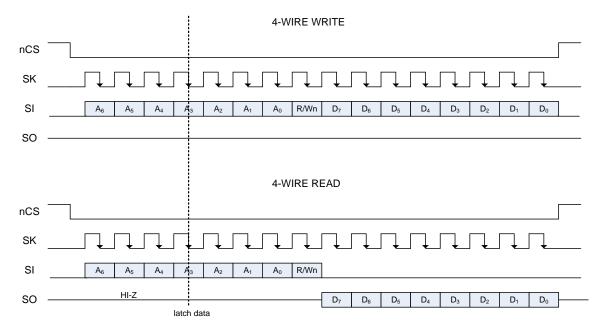

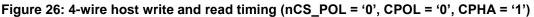

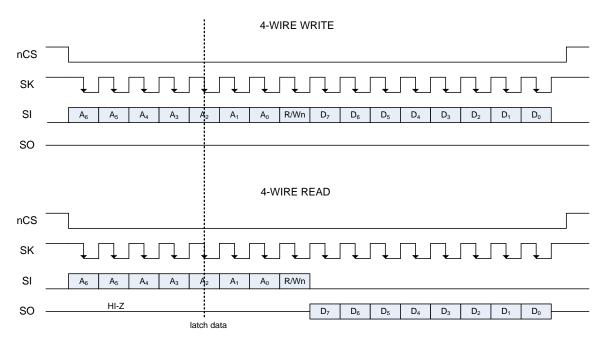

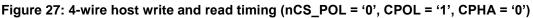

|     | 12.2   | 4-wire communication                                         | 49          |  |  |  |

|     | 12.3   | 2-wire communication                                         | 53          |  |  |  |

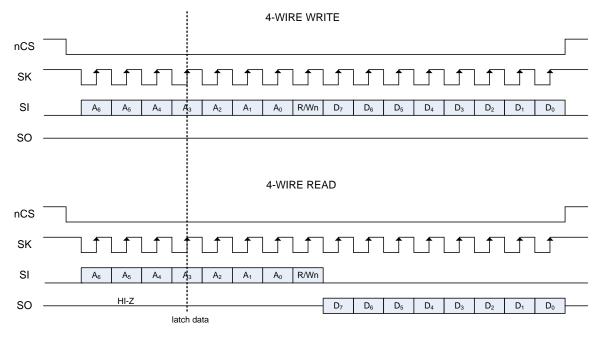

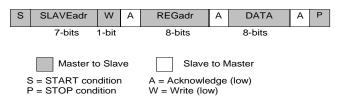

|     |        | 12.3.1 2-wire control bus protocol                           | 53          |  |  |  |

|     |        | 12.3.2 Alternative high speed 2-wire interface               | 55          |  |  |  |

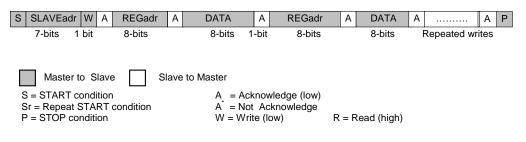

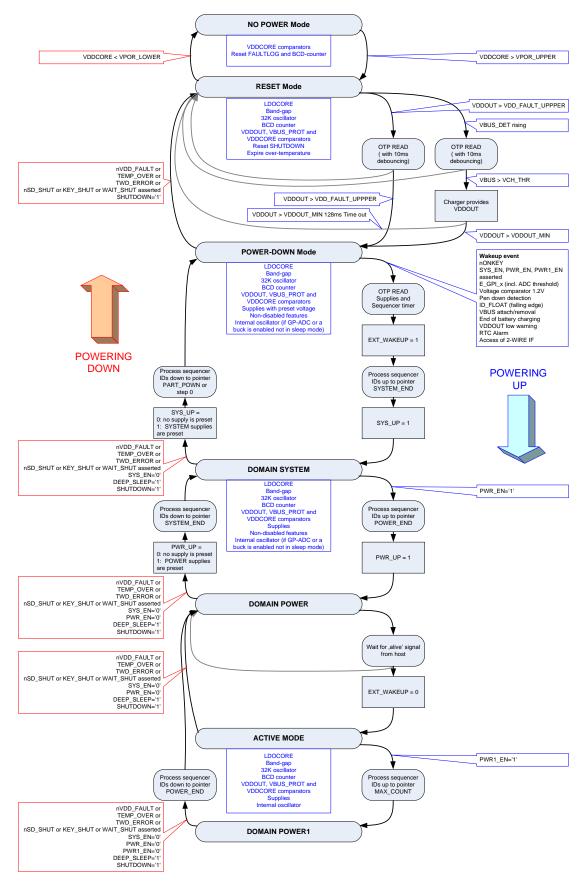

| 13  | DA90   | 021 operating modes                                          | 56          |  |  |  |

|     | 13.1   | ACTIVE mode                                                  | 56          |  |  |  |

|     | 13.2   | POWERDOWN mode                                               | 56          |  |  |  |

|     | 13.3   | RESET mode                                                   | 56          |  |  |  |

|     | 13.4   | NO-POWER mode                                                | 57          |  |  |  |

|     | 13.5   | POWER COMMANDER mode                                         | 57          |  |  |  |

|     | 13.6   | Start up from NO POWER mode                                  | 58          |  |  |  |

|     |        | 13.6.1 Power-On-Reset (nPOR)                                 | 58          |  |  |  |

|     |        | 13.6.2 Application wakeup                                    | 59          |  |  |  |

|     |        | 13.6.3 Power supply sequencer                                | 60          |  |  |  |

| 14  | Regis  | ster page control                                            | 65          |  |  |  |

|     | 14.1   | Register page 0                                              | 65          |  |  |  |

|     |        | 14.1.1 Power manager control and monitoring                  | 65          |  |  |  |

| 15  | GPIO   | ) Extender                                                   | 75          |  |  |  |

|     |        | GPIO control                                                 |             |  |  |  |

| 16  | Powe   | er supply sequencer                                          |             |  |  |  |

|     |        | 1 Power sequencer                                            |             |  |  |  |

| 17  |        | ge regulators                                                |             |  |  |  |

| .,  |        | DA9021/22 core regulator LDOCORE                             |             |  |  |  |

| Det |        | -                                                            |             |  |  |  |

| Dal | tashee | et Revision 2.5                                              | 17-Feb-2017 |  |  |  |

## System PMIC with high efficiency USB power manager

| 18 | DC/D   | C buck converters                                                                     | 88    |

|----|--------|---------------------------------------------------------------------------------------|-------|

|    | 18.1   | Converters BUCKCORE, BUCKPRO (DA9021 only) and BUCKMEM with DVC                       | 88    |

|    | 18.2   | Converter BUCKPERI with OTP programmable output voltage and bypass mode (DA9022 only) | 90    |

|    | 18.3   | Power supplies                                                                        | 91    |

| 19 | Prog   | rammable battery charger                                                              | . 103 |

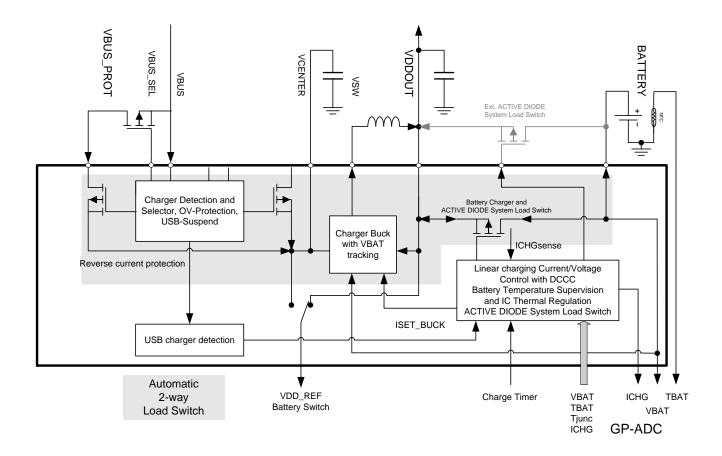

|    | 19.1   | High efficiency charger DC-DC buck converter                                          |       |

|    | 19.2   | Charger supply detection/VBUS monitoring                                              |       |

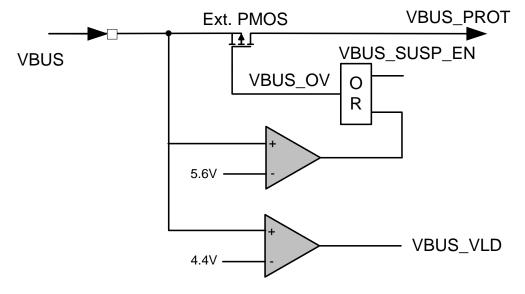

|    | 19.3   | VBUS overvoltage protection and USB suspend                                           |       |

|    | 19.4   | Battery pre-charge mode                                                               | 106   |

|    | 19.5   | Fast linear-charge mode                                                               | 107   |

|    | 19.6   | Thermal charge current control                                                        | 107   |

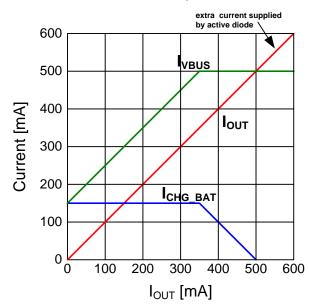

|    | 19.7   | Dynamic charging current control (DCCC) and active-diode                              | 108   |

|    | 19.8   | Programmable charge termination by time                                               | 108   |

|    |        | 19.8.1 Battery charger                                                                | 109   |

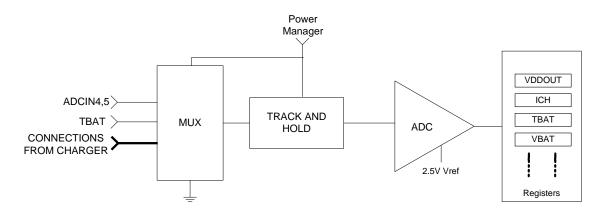

| 20 | Moni   | toring ADC and touch screen interface                                                 | . 114 |

|    | 20.1   | ADC overview                                                                          | 114   |

|    |        | 20.1.1 Input MUX                                                                      | 114   |

|    |        | 20.1.2 ADC                                                                            | .114  |

|    | 20.2   | MANUAL CONVERSION mode                                                                | . 114 |

|    | 20.3   | Automatic measurements scheduler                                                      | 115   |

|    |        | 20.3.1 A0: VDDOUT low voltage nIRQ measurement mode                                   | . 115 |

|    |        | 20.3.2 A1: ICH (and ICH_BAT average) measurement mode                                 | 115   |

|    |        | 20.3.3 A2: TBAT and battery temperature warning nIRQ measurement mode                 |       |

|    |        | 20.3.4 A4, A5: automatic measurement and high/low threshold warning nIRQ mode.        |       |

|    |        | 20.3.5 A8: automatic measurement of internal temperature                              |       |

|    |        | 20.3.6 A3, A9: manual measurement VBAT and VBBAT                                      |       |

|    | 20.4   | Fixed threshold comparator                                                            |       |

|    |        | 20.4.1 LED driver                                                                     |       |

|    |        | 20.4.2 GP-ADC                                                                         |       |

|    |        | 20.4.3 RTC calendar and alarm                                                         |       |

|    | 20.5   | Register page 1                                                                       |       |

|    |        | 20.5.1 Customer OTP                                                                   |       |

| 21 | Regis  | ster Map                                                                              | 127   |

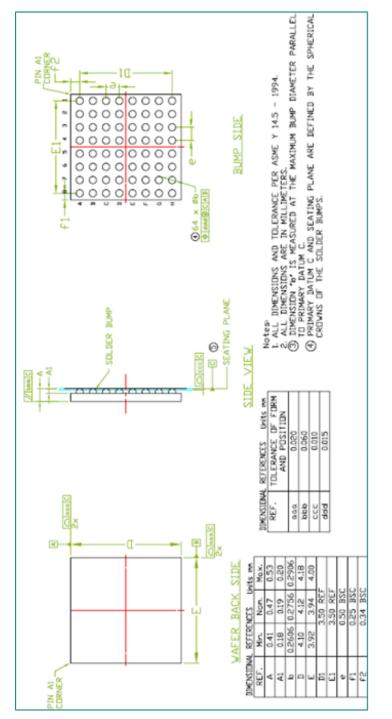

| 22 | Pack   | age information                                                                       | 133   |

|    | 22.1   | Package outlines                                                                      | 133   |

| 23 | Exter  | nal component selection                                                               | 134   |

|    | 23.1   | Capacitor selection                                                                   | 134   |

|    | 23.2   | Inductor selection                                                                    | 135   |

|    | 23.3   | Resistors 135                                                                         |       |

|    | 23.4   | External pass transistors and Schottky diodes                                         | 135   |

|    | 23.5   | Battery pack temperature sensor (NTC)                                                 | 135   |

|    | 23.6   | Crystal 136                                                                           |       |

| 24 | Layo   | ut guidelines                                                                         | . 137 |

|    | 24.1   |                                                                                       |       |

|    | 24.2   | System supply and charger                                                             | 137   |

|    |        |                                                                                       |       |

| Da | tashee | et Revision 2.5 17-Feb-2                                                              | 2017  |

|    | 24.3   | LDOs and switched mode supplies |                                                 |     |  |

|----|--------|---------------------------------|-------------------------------------------------|-----|--|

|    | 24.4   | Crystal of                      | oscillator                                      | 137 |  |

|    | 24.5   | DA9021                          | thermal connection, land pad and stencil design | 138 |  |

| 25 | Defin  | itions                          |                                                 |     |  |

|    | 25.1   | Power d                         | issipation and thermal design                   | 139 |  |

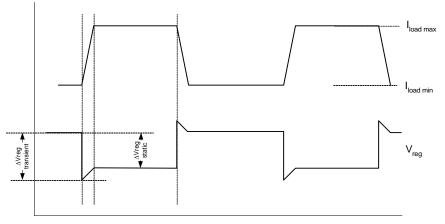

|    | 25.2   | Regulate                        | or parameters                                   | 139 |  |

|    |        | 25.2.1                          | Dropout voltage                                 | 139 |  |

|    |        | 25.2.2                          | Power supply rejection                          |     |  |

|    |        | 25.2.3                          | Line regulation                                 |     |  |

|    |        | 25.2.4                          | Load regulation                                 |     |  |

| 26 | Orde   | ring info                       | rmation                                         |     |  |

|    | 26.1   | Addition                        | al applications information                     |     |  |

| Re | vision | history.                        |                                                 |     |  |

## **Figures**

| Figure 1: Block diagram                                                              | 10 |

|--------------------------------------------------------------------------------------|----|

| Figure 2: PCB board DA9021 pad arrangement (view from the top)                       |    |

| Figure 3: PCB board DA9022 pad arrangement (view from the top)                       |    |

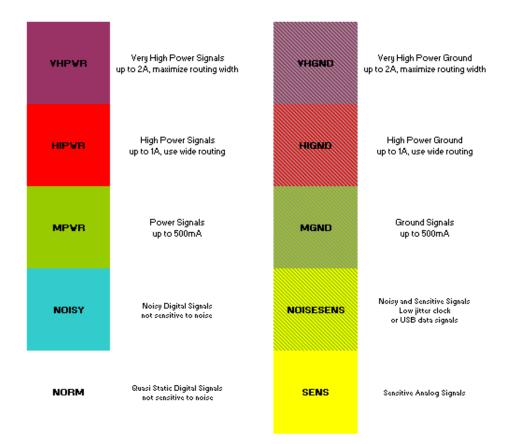

| Figure 4: Pad arrangement colour key                                                 |    |

| Figure 5: 4-wire control bus timing diagram                                          |    |

| Figure 6: Schematics of the RTC oscillator and counter functionality                 |    |

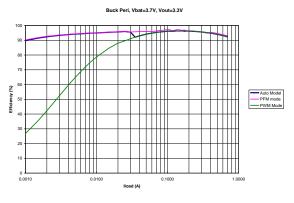

| Figure 7: BUCKPERI efficiency curves                                                 |    |

| Figure 8: BUCKCORE efficiency curves                                                 |    |

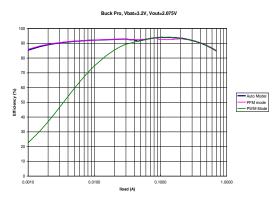

| Figure 9: BUCKPRO efficiency curves                                                  |    |

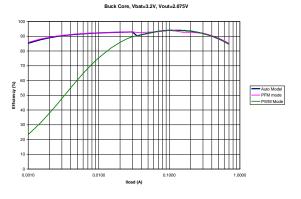

| Figure 10: BUCKMEM efficiency curves                                                 |    |

| Figure 11: Typical buck line transient                                               |    |

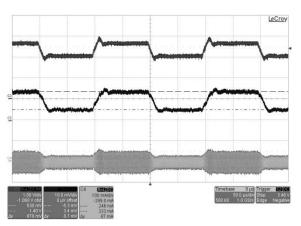

| Figure 12: Typical buck load transient                                               |    |

| Figure 13: Typical LDO load regulation                                               |    |

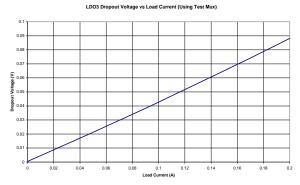

| Figure 14: Typical LDO drop-out voltage                                              |    |

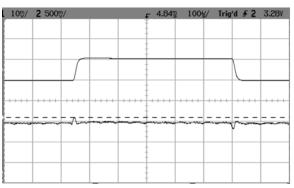

| Figure 15: Typical LDO line transient                                                | 44 |

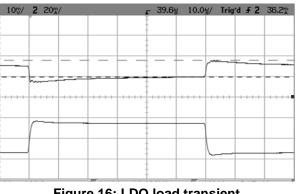

| Figure 16: LDO load transient                                                        | 44 |

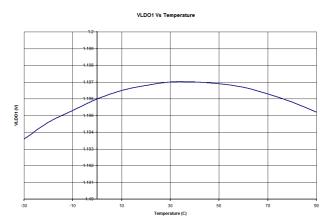

| Figure 17: Typical LDO voltage vs temperature                                        | 44 |

| Figure 18: ADC DNL performance                                                       |    |

| Figure 19: ADC INL performance                                                       | 45 |

| Figure 20 Power path behaviour USB100 mode                                           | 45 |

| Figure 21 Power path behaviour USB500 mode                                           | 45 |

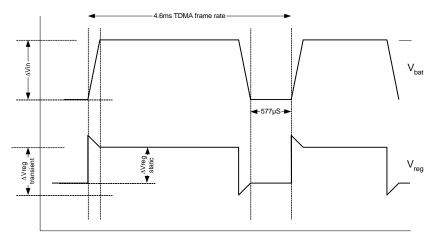

| Figure 22: Transitioning supply from USB 5 V (via VBUS) to VBAT                      | 45 |

| Figure 23: Control ports and interface                                               | 46 |

| Figure 24: Schematic of 4-wire and 2-wire power manager bus                          | 49 |

| Figure 25: 4-wire host write and read timing (nCS POL = '0', CPOL = '0', CPHA = '0') | 50 |

| Figure 26: 4-wire host write and read timing (nCS_POL = '0', CPOL = '0', CPHA = '1') | 51 |

| Figure 27: 4-wire host write and read timing (nCS_POL = '0', CPOL = '1', CPHA = '0') |    |

| Figure 28: 4-wire host write and read timing (nCS_POL = '0', CPOL = '1', CPHA = '1') |    |

| Figure 29: Timing of 2-wire START and STOP condition                                 |    |

| Figure 30: 2-wire byte write (SO/DATA line)                                          | 54 |

| Figure 31: Examples of 2-wire byte read (SO/DATA line)                               |    |

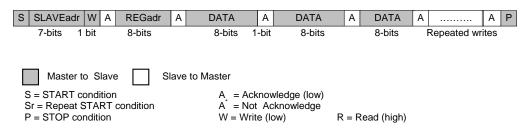

| Figure 32: 2-wire page write (SO/DATA line)                                          |    |

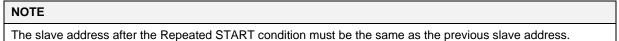

| Figure 33: 2-wire repeated write (SO/DATA line)                                      |    |

| Figure 34: Start-up from NO-POWER to POWERDOWN mode                                  |    |

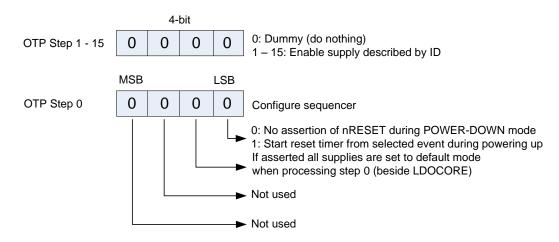

| Figure 35: Content of OTP power sequencer register cell                              |    |

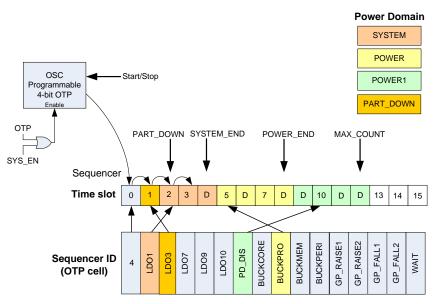

| Figure 36: Allocation of supplies (IDs) into to the sequencer time slots             |    |

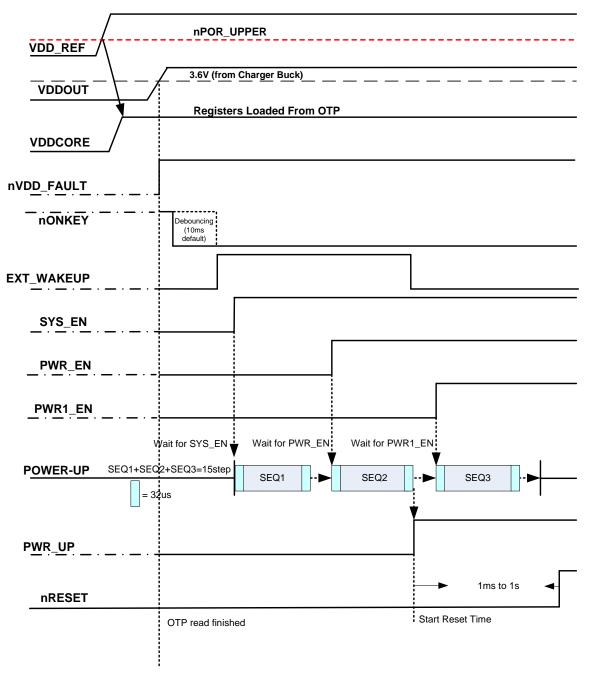

| Figure 37: Typical power-up timing                                                   |    |

| Figure 38: Power mode transitions                                                    | 82 |

|                                                                                      |    |

## System PMIC with high efficiency USB power manager

| Figure 39: Smart Mirror™ voltage regulator   | 86  |

|----------------------------------------------|-----|

| Figure 40: DC-DC buck converter              |     |

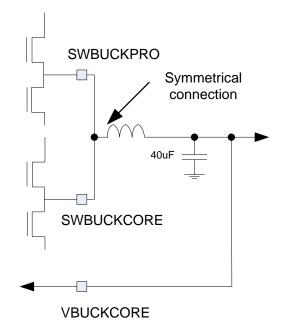

| Figure 41: BUCKCORE merged with BUCKPRO      |     |

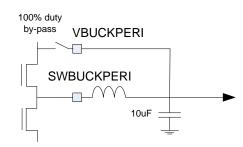

| Figure 42: BUCKPERI BYPASS mode              |     |

| Figure 43: Charger block diagram             | 104 |

| Figure 44: Charger detection                 |     |

| Figure 45: DCCC & active diode operation     | 108 |

| Figure 46: ADC block diagram                 | 114 |

| Figure 47: ADC sequence                      |     |

| Figure 48: DA9021/22 package outline drawing | 133 |

| Figure 49: Line regulation                   |     |

| Figure 50: Load regulation                   | 140 |

## **Tables**

| Table 1: Regulator overview                                                                            | . 11 |

|--------------------------------------------------------------------------------------------------------|------|

| Table 2: Pin description for DA9021                                                                    |      |

| Table 3: Pin description for DA9022                                                                    | . 17 |

| Table 4: Pin type definition                                                                           |      |

| Table 5: Absolute maximum ratings                                                                      |      |

| Table 6: Recommended operating conditions                                                              | . 21 |

| Table 7: Current consumption                                                                           | . 21 |

| Table 8: Digital I/O (VDD_REF > 2.8 V)                                                                 |      |

| Table 9: GPIOs                                                                                         |      |

| Table 10: Power on reset                                                                               |      |

| Table 11: 4-wire timing                                                                                |      |

| Table 12: Oscillator                                                                                   |      |

| Table 13: Reference voltage generation and temperature supervision                                     |      |

| Table 14: LDO1                                                                                         |      |

| Table 15: LDO3                                                                                         |      |

| Table 16: LDO7                                                                                         |      |

| Table 17: LDO9                                                                                         |      |

| Table 18: LDO10                                                                                        | . 29 |

| Table 19: LDOCORE (T <sub>a</sub> = -25 °C to +85 °C)                                                  | . 30 |

| Table 20: BUCKCORE                                                                                     |      |

| Table 21: BUCKPRO (DA9021 only)                                                                        |      |

| Table 22: BUCKPERI (DA9022 only)                                                                       |      |

| Table 23: BUCKMEM                                                                                      |      |

| Table 24: Battery charger                                                                              |      |

| Table 25: Charger buck                                                                                 |      |

| Table 26: Voltage levels on VBAT                                                                       |      |

| Table 27: Charging modes                                                                               | . 38 |

| Table 28: Charger detection circuit                                                                    | . 39 |

| Table 29: VBUS charge control                                                                          |      |

| Table 30: Charge timer                                                                                 |      |

| Table 31: DCCC and active-diode                                                                        |      |

| Table 32: Oscillator ( $T_A = -25 \text{ °C to } +85 \text{ °C}$ )                                     | . 40 |

| Table 33: Reference voltage generation and temperature supervision (T <sub>A</sub> = -25 °C to +85 °C) | . 40 |

| Table 34: 4-wire clock configurations                                                                  |      |

| Table 35: 4-wire interface summary                                                                     | . 52 |

| Table 36: Wakeup events                                                                                | . 60 |

| Table 37: Power sequencer controlled actions                                                           | . 61 |

| Table 38: Register page control                                                                        | . 65 |

| Table 39: STATUS_A                                                                                     |      |

| Table 40: STATUS_B                                                                                     |      |

| Table 41: STATUS_C                                                                                     |      |

| Table 42: STATUS_D                                                                                     | . 66 |

| Table 43: EVENT_A                                                                                      | . 66 |

| Table 44: EVENT_B                                                                                      | . 67 |

|                                                                                                        |      |

Datasheet

**Revision 2.5**

## System PMIC with high efficiency USB power manager

| Table 45: EVENT_C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 46: EVENT_D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                       |

| Table 47: FAULT_LOG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                       |

| Table 48: IRQ_MASK_A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                       |

| Table 49: IRQ_MASK_B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                       |

| Table 50: IRQ_MASK_C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                       |

| Table 51: IRQ_MASK_D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                       |

| Table 52: CONTROL_A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                       |

| Table 53: CONTROL_B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                       |

| Table 54: CONTROL_C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                       |

| Table 55: CONTROL_D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                       |

| Table 56: PD_DIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                       |

| Table 57: INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73                                                                                                                                                    |

| Table 58: RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74                                                                                                                                                    |

| Table 59: GPIO0 to 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 76                                                                                                                                                    |

| Table 60: RESERVED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 77                                                                                                                                                    |

| Table 61: GPIO8 to 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 77                                                                                                                                                    |

| Table 62: GPIO10 to 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                       |

| Table 63: GPIO12 to 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                       |

| Table 64: GPIO14 to 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                       |

| Table 65: ID 0 to 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                                                                                                                                     |

| Table 66: ID 2 to 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                       |

| Table 67: RESERVED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                       |

| Table 68: ID 6 to 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                       |

| Table 68: ID 6 to 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                       |

| Table 70: ID 10 to 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                       |

| Table 71: ID 12 to 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                       |

| Table 72: ID 14 to 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                       |

| Table 73: ID 16 to 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                       |

| Table 74: ID 18 to 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                       |

| Table 75: ID 20 to 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                       |

| Table 76: SEQ status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 84                                                                                                                                                    |

| Table 76: SEQ status<br>Table 77: SEQ_A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 84<br>84                                                                                                                                              |

| Table 76: SEQ status<br>Table 77: SEQ_A<br>Table 78: SEQ_B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 84<br>84<br>85                                                                                                                                        |

| Table 76: SEQ status<br>Table 77: SEQ_A<br>Table 78: SEQ_B<br>Table 79: SEQ timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 84<br>84<br>85<br>85                                                                                                                                  |

| Table 76: SEQ status         Table 77: SEQ_A         Table 78: SEQ_B         Table 79: SEQ timer         Table 80: Selection of buck current limit from coil parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 84<br>84<br>85<br>85<br>91                                                                                                                            |

| Table 76: SEQ status<br>Table 77: SEQ_A<br>Table 78: SEQ_B<br>Table 79: SEQ timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 84<br>84<br>85<br>85<br>91                                                                                                                            |

| Table 76: SEQ status         Table 77: SEQ_A         Table 78: SEQ_B         Table 79: SEQ timer         Table 80: Selection of buck current limit from coil parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 84<br>84<br>85<br>85<br>91<br>91                                                                                                                      |

| Table 76: SEQ status         Table 77: SEQ_A.         Table 78: SEQ_B.         Table 79: SEQ timer         Table 80: Selection of buck current limit from coil parameters         Table 81: Buck A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 84<br>84<br>85<br>85<br>91<br>91<br>92                                                                                                                |

| Table 76: SEQ status         Table 77: SEQ_A.         Table 78: SEQ_B.         Table 79: SEQ timer         Table 80: Selection of buck current limit from coil parameters         Table 81: Buck A.         Table 82: Buck B.         Table 83: BUCKCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 84<br>84<br>85<br>85<br>91<br>91<br>92<br>92                                                                                                          |

| Table 76: SEQ status<br>Table 77: SEQ_A<br>Table 78: SEQ_B<br>Table 79: SEQ timer<br>Table 80: Selection of buck current limit from coil parameters<br>Table 81: Buck A<br>Table 82: Buck B<br>Table 83: BUCKCORE<br>Table 84: BUCKPRO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 84<br>84<br>85<br>85<br>91<br>91<br>92<br>92<br>93                                                                                                    |

| Table 76: SEQ status         Table 77: SEQ_A.         Table 78: SEQ_B.         Table 79: SEQ timer         Table 80: Selection of buck current limit from coil parameters         Table 81: Buck A.         Table 82: Buck B.         Table 83: BUCKCORE         Table 84: BUCKPRO         Table 85: BUCKMEM                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 84<br>85<br>85<br>91<br>91<br>92<br>92<br>93<br>94                                                                                                    |

| Table 76: SEQ status         Table 77: SEQ_A.         Table 78: SEQ_B.         Table 79: SEQ timer         Table 80: Selection of buck current limit from coil parameters         Table 81: Buck A.         Table 82: Buck B.         Table 83: BUCKCORE         Table 84: BUCKPRO.         Table 85: BUCKMEM         Table 86: BUCKPERI                                                                                                                                                                                                                                                                                                                                                                                                                      | 84<br>84<br>85<br>91<br>91<br>92<br>92<br>92<br>93<br>94<br>95                                                                                        |

| Table 76: SEQ status<br>Table 77: SEQ_A<br>Table 78: SEQ_B<br>Table 79: SEQ timer<br>Table 80: Selection of buck current limit from coil parameters<br>Table 81: Buck A<br>Table 82: Buck B<br>Table 82: BUCKCORE<br>Table 83: BUCKCORE<br>Table 84: BUCKPRO<br>Table 85: BUCKMEM<br>Table 85: BUCKMEM<br>Table 86: BUCKPERI<br>Table 87: LDO1                                                                                                                                                                                                                                                                                                                                                                                                                | 84<br>84<br>85<br>91<br>91<br>92<br>92<br>92<br>93<br>94<br>95<br>96                                                                                  |

| Table 76: SEQ status         Table 77: SEQ_A.         Table 78: SEQ_B.         Table 79: SEQ timer.         Table 80: Selection of buck current limit from coil parameters         Table 81: Buck A.         Table 82: Buck B.         Table 83: BUCKCORE         Table 84: BUCKPRO.         Table 85: BUCKMEM         Table 86: BUCKPERI         Table 87: LDO1         Table 88: RESERVED.                                                                                                                                                                                                                                                                                                                                                                  | 84<br>84<br>85<br>91<br>91<br>92<br>92<br>92<br>93<br>94<br>95<br>96<br>97                                                                            |

| Table 76: SEQ status         Table 77: SEQ_A.         Table 78: SEQ_B.         Table 79: SEQ timer         Table 80: Selection of buck current limit from coil parameters         Table 81: Buck A         Table 82: Buck B         Table 83: BUCKCORE         Table 84: BUCKPRO         Table 85: BUCKMEM         Table 86: BUCKPERI         Table 87: LDO1         Table 88: RESERVED         Table 89: LDO3                                                                                                                                                                                                                                                                                                                                                | 84<br>85<br>85<br>91<br>91<br>92<br>92<br>92<br>93<br>94<br>95<br>97<br>97                                                                            |

| Table 76: SEQ status         Table 77: SEQ_A         Table 78: SEQ_B         Table 79: SEQ timer         Table 80: Selection of buck current limit from coil parameters         Table 81: Buck A         Table 82: Buck B         Table 83: BUCKCORE         Table 84: BUCKPRO         Table 85: BUCKMEM         Table 86: BUCKPERI         Table 87: LDO1         Table 88: RESERVED         Table 89: LDO3         Table 90: RESERVED                                                                                                                                                                                                                                                                                                                       | 84<br>85<br>85<br>91<br>91<br>92<br>92<br>92<br>93<br>94<br>95<br>96<br>97<br>98                                                                      |

| Table 76: SEQ statusTable 77: SEQ_ATable 78: SEQ_BTable 79: SEQ timerTable 80: Selection of buck current limit from coil parametersTable 81: Buck ATable 82: Buck BTable 83: BUCKCORETable 84: BUCKPROTable 85: BUCKMEMTable 86: BUCKPERITable 87: LDO1Table 88: RESERVEDTable 89: LDO3Table 90: RESERVEDTable 91: LDO7                                                                                                                                                                                                                                                                                                                                                                                                                                       | 84<br>85<br>85<br>91<br>91<br>92<br>92<br>92<br>93<br>94<br>95<br>96<br>97<br>98<br>98                                                                |

| Table 76: SEQ statusTable 77: SEQ_A.Table 78: SEQ_B.Table 79: SEQ timerTable 80: Selection of buck current limit from coil parametersTable 81: Buck A.Table 82: Buck B.Table 83: BUCKCORETable 84: BUCKPRO.Table 85: BUCKMEMTable 86: BUCKPERITable 87: LDO1Table 88: RESERVED.Table 89: LDO3Table 90: RESERVED.Table 91: LDO7Table 92: RESERVED.                                                                                                                                                                                                                                                                                                                                                                                                             | 84<br>84<br>85<br>91<br>91<br>92<br>92<br>93<br>94<br>95<br>96<br>97<br>98<br>98<br>100                                                               |

| Table 76: SEQ statusTable 77: SEQ_A.Table 78: SEQ_B.Table 79: SEQ timerTable 80: Selection of buck current limit from coil parametersTable 81: Buck A.Table 82: Buck B.Table 83: BUCKCORETable 84: BUCKPROTable 85: BUCKMEMTable 86: BUCKPERITable 87: LDO1Table 88: RESERVEDTable 89: LDO3Table 90: RESERVEDTable 91: LDO7Table 93: LDO9                                                                                                                                                                                                                                                                                                                                                                                                                     | 84<br>84<br>85<br>91<br>91<br>92<br>92<br>93<br>94<br>95<br>96<br>97<br>98<br>100<br>100                                                              |

| Table 76: SEQ status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 84<br>84<br>85<br>91<br>91<br>92<br>92<br>93<br>94<br>95<br>96<br>97<br>98<br>100<br>100                                                              |

| Table 76: SEQ statusTable 77: SEQ_A.Table 78: SEQ_B.Table 79: SEQ timerTable 80: Selection of buck current limit from coil parametersTable 81: Buck ATable 82: Buck BTable 83: BUCKCORETable 84: BUCKPRO.Table 85: BUCKMEMTable 86: BUCKPERITable 87: LDO1Table 88: RESERVED.Table 89: LDO3Table 90: RESERVEDTable 91: LDO7Table 92: RESERVEDTable 93: LDO9Table 94: LDO10Table 95: SUPPLY                                                                                                                                                                                                                                                                                                                                                                    | 84<br>84<br>85<br>91<br>91<br>92<br>93<br>94<br>95<br>96<br>97<br>98<br>100<br>100<br>101                                                             |