#### September 2012

User manual for the set-up and operation of the DA7210/11 evaluation board and control software

### Contents

| С | ontents |                                              | 1  |  |  |  |  |  |  |

|---|---------|----------------------------------------------|----|--|--|--|--|--|--|

| 1 | Intro   | duction                                      | 2  |  |  |  |  |  |  |

| 2 | Hard    | lware                                        | 2  |  |  |  |  |  |  |

|   | 2.1     | Power Supplies                               | 5  |  |  |  |  |  |  |

|   | 2.2     | Jumpers and Link Positions                   | 6  |  |  |  |  |  |  |

| 3 | Eval    | uation Board Features                        | 13 |  |  |  |  |  |  |

|   | 3.1     | USB Interface                                | 13 |  |  |  |  |  |  |

| 4 | Con     | trol Software                                | 13 |  |  |  |  |  |  |

|   | 4.1     | Installation                                 | 13 |  |  |  |  |  |  |

|   | 4.2     | Set-up Files                                 | 16 |  |  |  |  |  |  |

|   | 4.2.1   | I Text File                                  | 16 |  |  |  |  |  |  |

|   | 4.2.2   | 2 Spreadsheet File                           | 17 |  |  |  |  |  |  |

|   | 4.3     | Control Panels                               | 19 |  |  |  |  |  |  |

|   | 4.3.1   | Front Panel                                  | 19 |  |  |  |  |  |  |

|   | 4.3.2   | 2 Register Map Page 0                        | 20 |  |  |  |  |  |  |

|   | 4.3.3   | B Register Map Page 1                        | 21 |  |  |  |  |  |  |

|   | 4.3.4   | GP Filters Register Map                      | 22 |  |  |  |  |  |  |

|   | 4.3.5   | 5 Volume Control Panel                       | 23 |  |  |  |  |  |  |

| 5 | RT F    | Filters GUI                                  | 24 |  |  |  |  |  |  |

|   | 5.1     | Software Installation                        |    |  |  |  |  |  |  |

|   | 5.2     | Control Panels                               | 26 |  |  |  |  |  |  |

|   | 5.2.2   | Running the Interface and USB Initialisation | 26 |  |  |  |  |  |  |

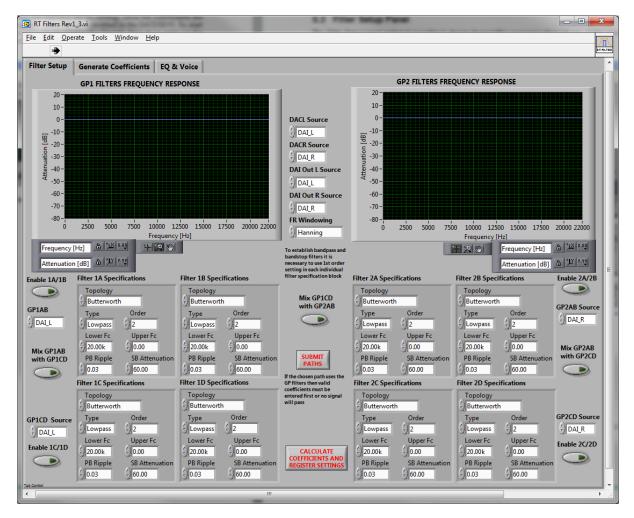

|   | 5.3     | Filter Setup Panel                           | 28 |  |  |  |  |  |  |

|   | 5.4     | Coefficients Tab                             | 29 |  |  |  |  |  |  |

|   | 5.5     | Five-band Equaliser and Voice Filter Panel   |    |  |  |  |  |  |  |

#### 1 Introduction

The DA7210/11 evaluation board has been produced to allow measurement, evaluation and programming of the DA7210/11 ultra-low power audio codec evaluation board and control software. The evaluation PCB is supplied together with a DVD ROM containing documentation and driver files.

The driver software uses a simple graphical user interface (GUI), allowing the DA7210/11 device to be controlled via a USB port of a PC. An additional GUI is available to control the highly configurable filter paths within the DA7210/11; including general purpose, five-band equaliser and high pass filters

The board has a number of jumper links to allow configuration of the board and to provide measurement test points.

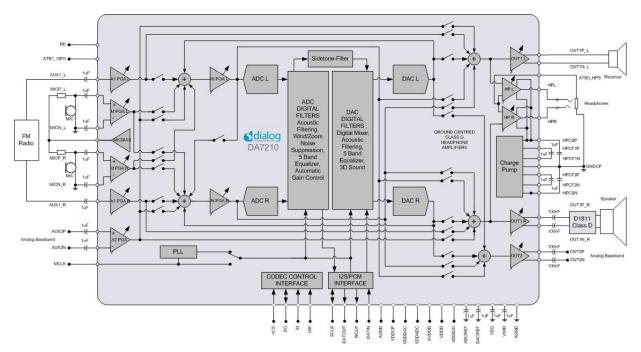

Figure 1 DA7210/11 Block Diagram

The accompanying software requires a PC operating Windows 2000/XP with a USB1.1 or USB2 interface. The software will run under Vista if the default installation location is changed to 'C:\Dialog Semiconductor\'

The DA7210/11 device plus the USB Interface consume approximately 5mA in the standby state. The evaluation board and software are not guaranteed to operate in a USB hub. See the section on Power Supplies below.

The control software permits configuration of the device using either pre-prepared templates or individual write and read operations to all control registers

#### 2 Hardware

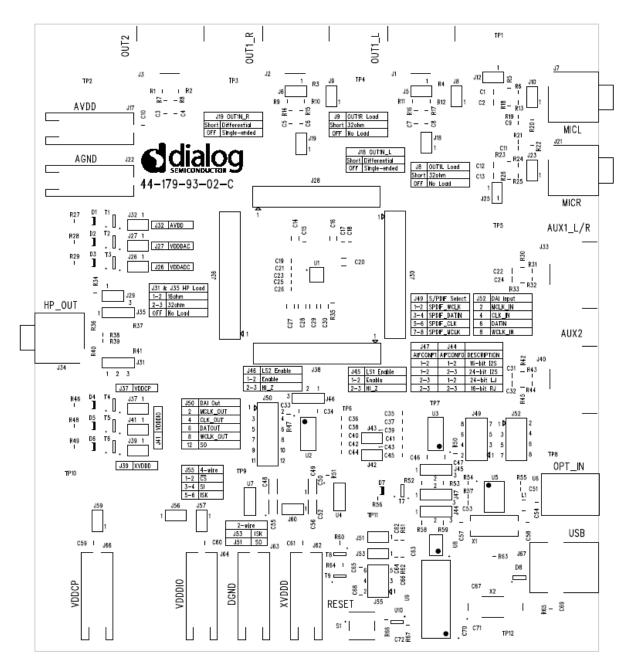

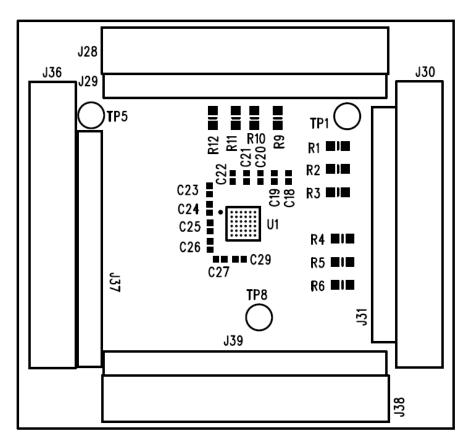

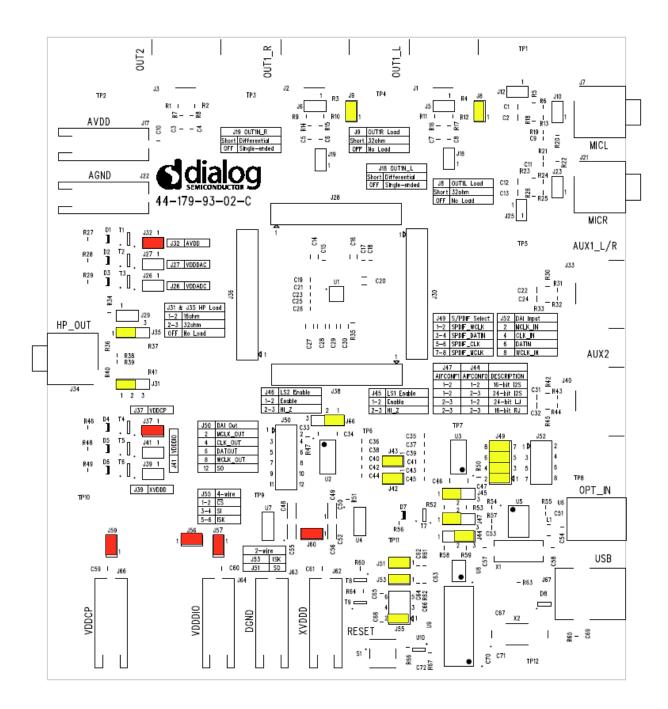

There are three options available when using the DA7210/11 evaluation mainboard, Figure 2:

1. A miniboard containing the DA7210 in a CSP 49-pin package connected to evaluation board 44-179-93-02-C via jumpers J28, J30, J36 and J38, Figure 3. This board can also be used standalone or in conjunction with a customer development system.

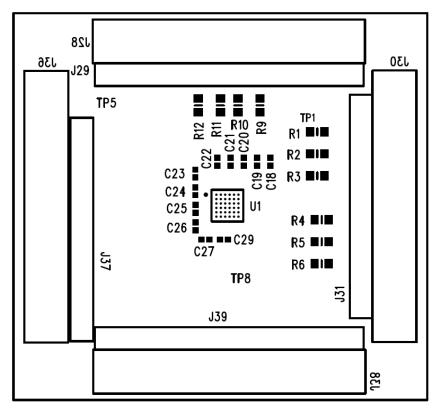

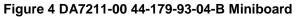

- 2. A miniboard containing the DA7211-00 in a 36-pin CSP package connected to evaluation board 44-179-93-02-B via jumpers J28, J30, J36 and J38, Figure 4. This board can also be used standalone or in conjunction with a customer development system.

- 3. A miniboard containing the DA7211-01 in a 36-pin CSP package connected to evaluation board 44-179-93-02-E via jumpers J28, J30, J36 and J38,. This board can also be used standalone or in conjunction with a customer development system.

A USB-I2C bridge is used for communication with the device, and there are number of external active components to reduce the requirement for external equipment.

Figure 2 Evaluation Board 44-179-93-02-C Mainboard

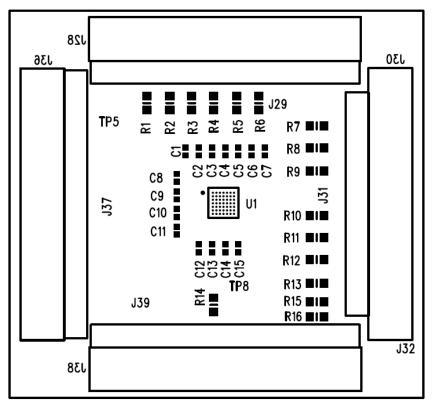

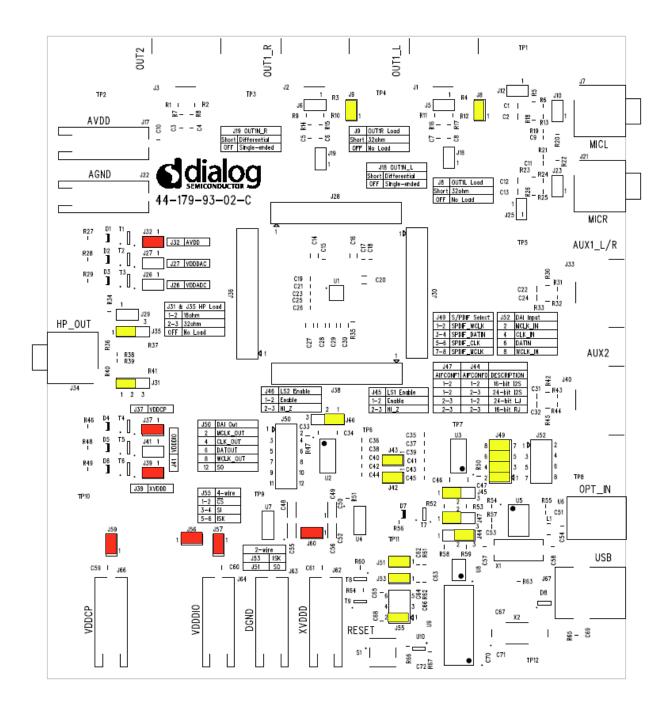

#### Figure 3 DA7210 44-179-93-04-C Miniboard

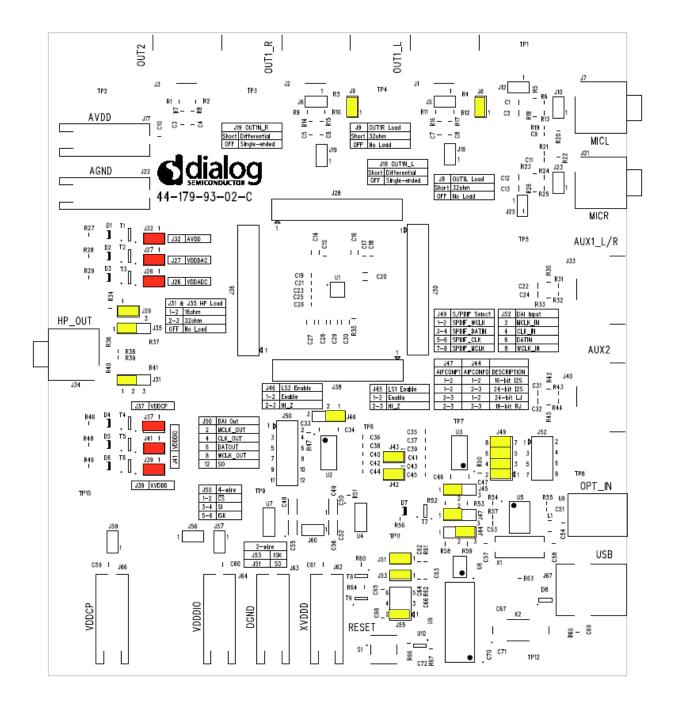

Figure 5 DA7211-01 44-179-93-04-E Miniboard

The passive components needed for noise decoupling or charge pump operation have been placed as close as possible to the DUT pins to ensure optimum operational performance.

Gerber data for the board is available on request.

#### 2.1 **Power Supplies**

The board is intended to be supplied by power supplies in the range  $+1.8V_{dc}$  to  $+2.5V_{dc}$  (nominal). The power supplies are connected via 4mm sockets: AVDD, VDDCP, VDDDAC, VDDADC, VDDDIO, DGND and AGND. LEDs D1 to D6 will illuminate when the power supplies are correctly connected.

Some devices on the board will be powered from the  $+5V_{dc}$  or  $+3.3V_{dc}$  supply produced by the USB interface module.

For demonstration purposes the  $+5V_{dc}$  USB supply can be connected to regulator, U9, to produce  $+1.8V_{dc}$  capable of supplying all of the DUT the power supply pins. This configuration allows complete DUT operation using just USB and TOSLINK connections only, but maximum headphone power output will be limited when using +1.8V VDDDCP power supply.

#### 2.2 Jumpers and Link Positions

| Header | Link<br>Position | Function                               | Notes                  |

|--------|------------------|----------------------------------------|------------------------|

| J5     |                  | OUT1_L speaker connection              | External connection    |

| J6     |                  | OUT1_R speaker connection              | External connection    |

| 10     | On               | OUT1_L 32Ω load selected               |                        |

| J8     | Off              | OUT1_L no load                         | _                      |

| 10     | On               | OUT1_R 32Ω load selected               | -                      |

| J9     | Off              | OUT1_R no load                         | -                      |

| J10    |                  | MIC_L differential connection          | External connection    |

| 14.0   | On               | MICN_L single-ended input              |                        |

| J12    | Off              | MICN_L differential input              | -                      |

| 14.0   | On               | OUT1N_L differential output            | -                      |

| J18    | Off              | OUT1N_L single-ended output            | -                      |

| 14.0   | On               | OUT1N_R differential output            | -                      |

| J19    | Off              | OUT1N_R single-ended output            | -                      |

| J23    |                  | MIC_R differential connection          | External connection    |

| 105    | On               | MIC_R single-ended input               |                        |

| J25    | Off              | MIC_R differential input               |                        |

| 100    | Short link       | Short VDDADC current measurement point |                        |

| J26    | DMM link         | VDDADC current measurement point       | - N/A for DA7211       |

| 107    | Short link       | Short VDDDAC current measurement point |                        |

| J27    | DMM link         | VDDDAC current measurement point       | – N/A for DA7211       |

| 100    | On               | Headphone sense ground connected       | Should be disconnected |

| J29    | Off              | Headphone sense ground disconnected    | for DA7211             |

| 104    | 1-2              | HPL 16Ω load selected                  |                        |

| J31    | 2-3              | HPL 32Ω load selected                  |                        |

| J32    | Short link       | Short AVDD current measurement point   |                        |

|       | DMM link   | AVDD current measurement point         |                                            |

|-------|------------|----------------------------------------|--------------------------------------------|

|       | 1-2        | HPR 16Ω load selected                  |                                            |

| J35   | 2-3        | HPR 32Ω load selected                  |                                            |

|       | Short link | Short VDDCP current measurement point  |                                            |

| J37   | DMM link   | VDDCP current measurement point        |                                            |

|       | Short link | Short XVDDD current measurement point  |                                            |

| J39   | DMM link   | XVDDD current measurement point        | N/A for DA7211                             |

| 144   | Short link | Short VDDDIO current measurement point |                                            |

| J41   | DMM        | VDDDIO current measurement point       | N/A for DA7211                             |

| 140   | On         | WCLK slave mode                        |                                            |

| J42   | Off        | WCLK master mode                       |                                            |

| 140   | On         | CLK slave mode                         |                                            |

| J43   | Off        | CLK master mode                        |                                            |

|       | 1-2 / 1-2  | 16-bit I2S mode                        |                                            |

| J44 / | 1-2/2-3    | 24-bit I2S mode                        | J44 and J47 must both be set for correct   |

| J47   | 2-3 / 1-2  | 24-bit left justified mode             | S/PDIF receiver DAI format and word length |

|       | 2-3 / 2-3  | 16-bit right justified mode            |                                            |

| 145   | 1-2        | DAI input level shift enable           |                                            |

| J45   | 2-3        | DAI input level shift high impedance   |                                            |

| 140   | 1-2        | DAI output level shift enable          |                                            |

| J46   | 2-3        | DAI output level shift high impedance  |                                            |

| 140   | On         | S/PDIF receiver +5V supply enabled     |                                            |

| J48   | Off        | S/PDIF receiver +5V supply disabled    |                                            |

|       | 1-2        | SPDIF word clock                       |                                            |

| 140   | 3-4        | SPDIF bit clock                        | Short links only if no                     |

| J49   | 5-6        | SPDIF data                             | sources are connected to J52               |

|       | 7-8        | SPDIF master clock                     |                                            |

|     | 1-2   | MCLK output                              |                                         |

|-----|-------|------------------------------------------|-----------------------------------------|

|     | 3-4   | CLK output                               |                                         |

| J50 | 5-6   | DATOUT output                            | External connections                    |

|     | 7-8   | WCLK output                              |                                         |

|     | 11-12 | SO output                                |                                         |

| 154 | On    | Control interface 2-wire ISK selected    | Short only if J55 links                 |

| J51 | Off   | Control interface 2-wire ISK de-selected | are removed                             |

|     | 1-2   | DAI MCLK input                           |                                         |

| 150 | 3-4   | DAI CLK input                            | Short only if J49 links                 |

| J52 | 5-6   | DAI DATIN input                          | are removed                             |

|     | 7-8   | DAI WCLK input                           |                                         |

| 150 | On    | Control interface 2-wire SO selected     | Short only if J55 links                 |

| J53 | Off   | Control interface 2-wire SO de-selected  | removed                                 |

|     | 1-2   | Control interface 4-wire nCS selected    |                                         |

| J55 | 3-4   | Control interface 4-wire SI de-selected  | Short only if J51 and J53 links removed |

| 000 | 5-6   | Control interface 4-wire ISK selected    |                                         |

| J56 | On    | XVDDD connected to VDDCP                 |                                         |

| J20 | Off   | XVDDD disconnected from VDDCP            |                                         |

| 157 | On    | XVDDD connected to VDDDIO                |                                         |

| J57 | Off   | XVDDD disconnected from VDDDIO           |                                         |

| 150 | On    | VDDCP connected to AVDD                  |                                         |

| J59 | Off   | VDDCP disconnected from AVDD             |                                         |

| 160 | On    | REG_+1.8V supply connected               |                                         |

| J60 | Off   | REG_+1.8V disconnected                   |                                         |

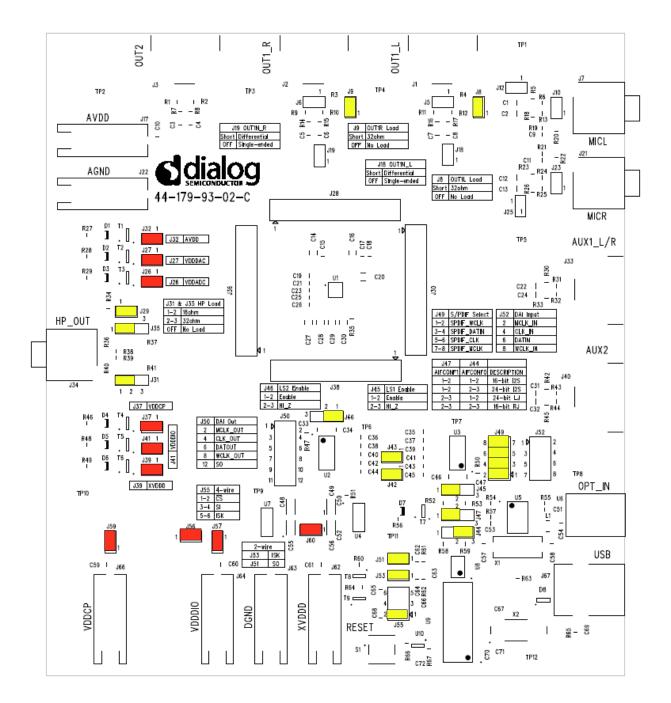

#### **Table 1 Jumpers and Link Positions**

The evaluation board can be set up to run solely from the +5V USB supply as the source for all board supplies. It is necessary to remove all external power supplies and to add jumpers J56, J57, J59 and J60 for this operation, which is the default configuration for the board.

The digital audio interface jumpers are set to receive a TOSLINK input and should be removed to accept other external clocks at J52. Figure 9 shows the extra links required to enable the onboard supplies.

Figure 7 DA7211-00 Default Link Locations

Figure 8 DA7211-01 Default Link Locations

Figure 9 shows the locations of the jumper links when using the DA7210 with external power supplies to AVDD J66, VDDCP J17, XVDDD J62 and VDDDIO J64. The digital audio interface jumpers are set to receive a TOSLINK input and should be removed to accept other external I2S clocks at J52.

Figure 9 External Power Supply Jumper Configuration

© Dialog Semiconductor 2011

#### 3 Evaluation Board Features

#### 3.1 USB Interface

The USB Interface is used here for the following purposes:

- As a source of I2C and SPI control signals.

- To provide a discrete signal to the power down pin *PD* (DA7210 only).

- To provide level shifting voltages.

- To allow standalone operation of the evaluation board using the  $+5V_{dc}$  USB power supply only.

The USB control signal device is powered by the USB bus cable via a fixed  $+3.3V_{dc}$  regulator.

The USB interface control signals can be isolated from rest of the evaluation board by removing J51, J53 and J55 described in Table 1. Removing these jumpers will allow external signal access to the DA7210 control interface. The USB interface can also be used to supply the power supplies to the DUT on the evaluation board.

The USB Interface implements multi-mastering on its I2C interface, permitting concurrent operation with any other multi-mastering controller. This allows the software to control a DA7210/11 device which is already part of the users system, and under control of the system processor.

#### 4 Control Software

#### 4.1 Installation

Insert the DVD-ROM containing the software into the controlling PC. If the installation does not start automatically, run the program 'setup.exe' from the DVD-ROM containing the software. An automated script will install the program to your PC. By default, the directory 'C:\ProgramFiles\Dialog Semiconductor\Audio\DA7210 Rev x.x' will be used.

As Windows Vista imposes limitiations on the 'C: \Program Files' directory, change this default to 'C: \Dialog Semiconductor\Audio\DA7210 Rev x.x' when prompted.

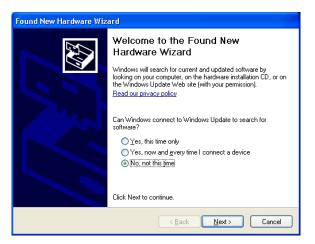

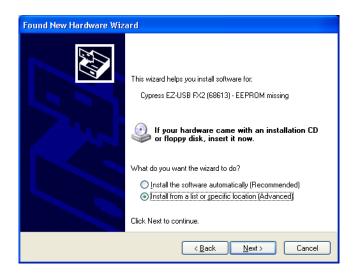

Plug in the USB cable, and Windows will detect the USB device. It will prompt for the drivers, which should be automatically located on the root directory of the DVD-ROM. The setup file is *''dlgezusb.inf'* and the following description explains how to install the driver.

Select No, not this time and press Next >

Select Install from a list or specific location (Advanced) and press Next >

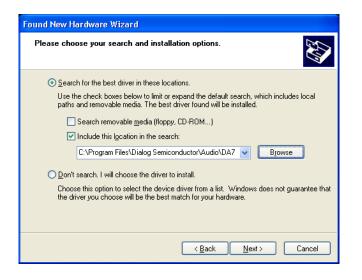

Select Browse and locate the folder

C:\Program Files\Dialog Semiconductor\Audio\DA7210\_11 Rev x.x

| Found | New H   | lardware Wizard                                                            |              |                  |

|-------|---------|----------------------------------------------------------------------------|--------------|------------------|

| Plea  | ase sel | ect the best match for your hardware                                       | from the lis | t below.         |

|       | ÷       | Cypress EZ-USB FX2 (68613) - EEPROM                                        | nissing      |                  |

|       | Descr   | iption                                                                     | Version      | Manufacturer     |

|       | Сур     | oress EZ-USB FX2 (68613) - EEPROM missi                                    | ng Unknown   | Dialog Semicondu |

|       | Сур     | oress EZ-USB FX2 (68613) - EEPROM missi                                    | ng Unknown   | Dialog Semicondu |

|       | <       |                                                                            |              | >                |

|       |         | is driver is not digitally signed!<br>I me why driver signing is important |              |                  |

|       |         | < <u> 8</u>                                                                | ack <u>N</u> | ext > Cancel     |

Select dlgezusb.inf and press Next >

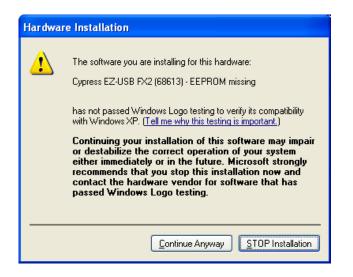

#### Press Continue Anyway

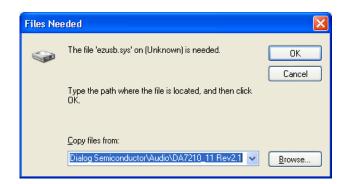

Select Browse and locate C:\Program Files\Dialog Semiconductor\Audio\DA7210\_11 Rev x.x then press OK

#### Select Finish

If you are using Windows XP, you may get a message saying that a USB2 device is attached to a USB1.1 port. This can safely be ignored.

To uninstall the software please use the Windows '*Add/Remove Programs*' function that can be found under '*Start->Settings->Control Panel*'.

#### 4.2 Set-up Files

#### 4.2.1 Text File

The DUT registers can written to by submitting a text file containing the register values; Figure 10 shows an example file. Only the data in the first three columns is required: register, data, R/W; other comments, such as those shown in the example, will be ignored. Lines of text that do not follow register write entries should be preceded by // in order that the line is ignored when reading the text file.

The text file can be created by saving the first three columns of the template spreadsheet file above as a text file or can be created from scratch; it is only necessary for the text file to contain the registers required for set up all others can be omitted.

To add a delay in the file the register value is entered as *Delay* followed by the delay time require in milliseconds. The example in Figure 10 shows a 100ms delay added as the third entry.

| D DA           | IC_H           | IPLR CI         | ass G.       | bat - Not                   | epad                                                                                                                                                                               | <b>→</b>                                      |        |

|----------------|----------------|-----------------|--------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------|

| <u>F</u> ile ļ | <u>E</u> dit   | F <u>o</u> rmat | <u>V</u> iew | Help                        |                                                                                                                                                                                    |                                               |        |

|                | _<br>CL/I<br>g | -               |              | <u>⊓</u> eip<br>⊂lass<br>/₩ | G Mode<br>Funct<br>PAGEC<br>CONTR<br>STATL<br>START<br>RESERV<br>MIC_L<br>MIC_R<br>AUX1_<br>AUX1_<br>AUX1_<br>AUX2 <br>IN_GA<br>INMI><br>ADC_E<br>ADC_E<br>ADC_E<br>ADC_E<br>DAC_F | :ion<br>)<br>(OL<br>JS<br>:UP2<br>:UP3<br>/ED |        |

| 17<br><        |                | DC              | 0            |                             | DAC_S                                                                                                                                                                              | SEL                                           | ×<br>> |

#### Figure 10 Text Set-up File

A selection of text files can be found on the DVD containing the register control software setup files.

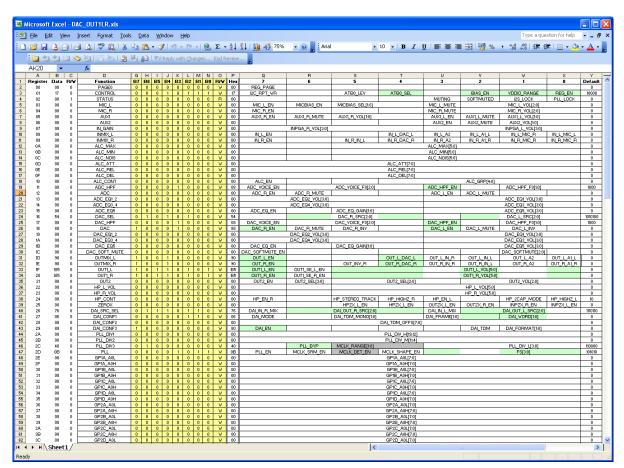

#### 4.2.2 Spreadsheet File

The register settings can be prepared using a spreadsheet file template provided, Figure 11, and saved as a tab delimited text file like Figure 10. The only bits that can be altered on the spreadsheet are the individual register bits in columns G to N and the R/W bit in column O. If any of these bits are set to 1 the bit will be highlighted in green on the register map. If the bit default setting is 1 and the bit value is changed to 0 then the register map bit will be highlighted in grey. This highlighting allows easy visual reference to the register changes from the default settings.

Figure 11 Spreadsheet Set-up File

#### 4.3 Control Panels

Run the DA7210/11 program by clicking the shortcut on the appropriate item in the Start menu. The best setting for the PC display size is 1024x768 pixels or above. Font size on the PC display should be Normal (95dpi). It is important to note that a display size other than the recommended setting may affect the way in which the panels appear.

#### 4.3.1 Front Panel

The front panel allows selection of a number of methods for programming the registers of the DUT.

- Submit a text file template, which allows register sequencing and time delays to be added.

- Select register map page 0 for individual register read/write access.

- Select register map page 1 for individual register write access.

- Select general purpose filters register map for individual register write access.

- Open a panel to access the volume control registers for real time volume control.

- Direct read/write access to a single register.

| DA7210/11 Rev 2.3 - Control Panel Selection                                    | → .□⊠               |

|--------------------------------------------------------------------------------|---------------------|

| Register Map Page 0 Set device page 0 registers                                | Register            |

| Register Map Page 1 Set device page 1 registers                                | Setting             |

| Filter Coefficients Set filter coefficient registers                           | R/W Select<br>Write |

| Volume Controls Volume Controls                                                | Submit              |

| Submit register settings from text file                                        |                     |

| File Submit .txt                                                               |                     |

| Save present register settings to spreadsheet           File Save         .xls |                     |

| Reset Reset all registers to default values                                    |                     |

| 2-wire Control Interface Mode                                                  |                     |

| Enabled Powerdown                                                              |                     |

#### Figure 12 Front Panel

Any file path required can be opened using the '...' button to the right of the corresponding text box, but it must then be submitted or saved using the submit button to the left of the corresponding text box.

It is possible to save the present register settings by selecting a spreadsheet file by locating the filename path using the '*Save present register setting to spreadsheet*' box. This function will not read back the device registers, but will only output the values shown on Page 0 and Page 1 of the GUI.

The front panel also contains a reset button, a device power down button and 2-wire/4-wire control selection.

#### 4.3.2 Register Map Page 0

The page 0 register map panel allows read/write access to single bits or to the hex value of a single register; both can be submitted individually.

| Register | R/W | B7 | 86 B | 5 B | 4 B3 | B2 | B1 B0 | Hex | Submit                                | FUNCTION    | 7            | 6                         | 5               | 4            | 3            | 2             | 1              | 0          | DEFAUL |

|----------|-----|----|------|-----|------|----|-------|-----|---------------------------------------|-------------|--------------|---------------------------|-----------------|--------------|--------------|---------------|----------------|------------|--------|

| 0x00     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | · ·                                   | PAGE0       | REG_PAGE     |                           |                 |              | •            | •             | •              | •          | 0      |

| 0x01     | W   | 0  | 0 0  | 1 1 | 0    | 0  | 0 0   | 10  | · · ·                                 | CONTROL     | WRITE_MODE   |                           | ATB1_LEV        | ATB1_SEL     | NOISE_SUP    | BIAS_EN       | VDDIO_RANGE    | REG_EN     | 10000  |

| 0x02     | B   | 0  | 0 0  | 1 0 | 0 1  | 0  | 0 0   | 0   |                                       | STATUS      |              |                           |                 |              | MUTING       | SOFTMUTED     | 128 LOCK       | PLL LOCK   | 0      |

| 0x03     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   |                                       | STARTUP1    | SC CLK DIS   |                           |                 | SC OVERRIDE  |              |               |                | SC MST EN  | 0      |

| 0x04     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | · · ·                                 | STARTUP2    |              |                           |                 | ST           | ARTUP2[6:0]  |               |                |            | 0      |

| 0x05     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | · · ·                                 | STARTUPS    |              |                           |                 | ST           | ARTUPS[6:0]  |               |                |            | 0      |

| 0x06     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | · · ·                                 | RESERVED    |              |                           |                 | RESERVED     |              |               |                |            | 0      |

| 0x07     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | · ·                                   | MIC_L       | MIC_L_EN     | MICBIAS_EN                | MICBIAS         | _SEL[1:0]    | MIC_L_MUTE   |               | MIC_L_VOL[2:0] |            | 0      |

| 0x08     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | · ·                                   | MIC_R       | MIC_R_EN     | MIC_R_MUTE MIC_R_VOL(2:0) |                 |              |              |               |                |            | 0      |

| 0x09     | W   | 0  | 0 0  | 1 1 | 0    | 0  | 0 0   | 10  | · · ·                                 | AUX1_L      | AUX1_L_EN    | AUX1_L_VOL[6:0]           |                 |              |              |               |                |            | 10000  |

| 0x0A     | W   | 0  | 0 0  | 1 1 | 0    | 0  | 0 0   | 10  | · ·                                   | AUX1_R      | AUX1_R_EN    |                           | AUX1_R_VOL[5:0] |              |              |               |                |            |        |

| 0x0B     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | · ·                                   | AUX2        |              |                           |                 |              | AUX2_EN      | AUX2_MUTE     | AUX2_VC        | DL[1:0]    | 0      |

| 0x0C     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | · ·                                   | IN_GAIN     |              | INPGA_                    | R_VOL[3:0]      |              |              | INPGA_L       | _VOL[3:0]      |            | 0      |

| 0x0D     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | _ · _ ]                               | INMIX_L     | IN_L_EN      |                           |                 |              |              | IN_L_SEL[4:0] |                |            | 0      |

| 0x0E     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | · · )                                 | INMIX_R     | IN_R_EN      |                           |                 |              | IN_R_SEL     | _[5:0]        |                |            | 0      |

| 0x0F     | W   | 0  | 0 0  | 1 0 | 1    | 0  | 0 0   | 8   | ]                                     | ADC_HPF     | ADC_VOICE_EN |                           | ADC_VOICE_F0[2  | :0]          | ADC_HPF_EN   |               | ADC_HPF_       | F0[1:0]    | 1000   |

| 0x10     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   |                                       | ADC         | ADC_R_EN     | ADC_R_MUTE                |                 |              | ADC_L_EN     | ADC_L_MUTE    |                | ALC_EN     | 0      |

| 0x11     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   |                                       | ADC_EQ1_2   |              | ADC_EC                    | 2_VOL[8:0]      |              |              | ADC_EQ1       | 1_VOL[3:0]     |            | 0      |

| 0x12     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   |                                       | ADC_EQ3_4   |              | ADC_EC                    | 4_VOL[8:0]      |              |              | ADC_EQ        | 3_VOL[3:0]     |            | 0      |

| 0x13     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | - I                                   | ADC_EQ5     | ADC_EQ_EN    |                           | ADC_EQ_         | _GAIN[1:0]   |              | ADC_EQ        | 5_VOL[3:0]     |            | 0      |

| 0x14     | W   | 0  | 0 0  | 1 0 | 1    | 0  | 0 0   | 8   | - I                                   | DAC_HPF     | DAC_VOICE_EN |                           | DAC_VOICE_FO[2  | :0]          | DAC_HPF_EN   | DAC_MUTE      | DAC_HPF        | _F0[1:0]   | 1000   |

| 0x15     | W   | 0  | 0 0  | 1 1 | 0    | 0  | 0 0   | 10  | · · ·                                 | DAC_L       | DAC_L_INV    | AC_L_INV DAC_L_GAIN[6:0]  |                 |              |              |               |                |            | 10000  |

| 0x16     | W   | 0  | 0 0  | 1 1 | 0    | 0  | 0 0   | 10  | · · ·                                 | DAC_R       | DAC_R_INV    | INV DAC_R_GAIN[6:0]       |                 |              |              |               |                | 10000      |        |

| 0x17     | W   | 0  | 1 (  | 1 1 | 0    | 1  | 0 0   | 54  | · · ·                                 | DAC_SEL     | DAC_R_EN     |                           | DAC_R_SRC[2:0   | 1            | DAC_L_EN     |               | DAC_L_SRC[2:0] |            | 101010 |

| 0x18     | W   | 0  | 1 (  | 1 0 | 1 0  | 0  | 0 0   | 40  | · ·                                   | SOFT_MUTE   | SOFT_MUTE    | RAMP_EN                   |                 |              |              |               | MUTE_RATE[2:0] |            | 100000 |

| 0x19     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | _ · _ ]                               | DAC_EQ1_2   |              | DAC_EC                    | 2_VOL[8:0]      |              |              | DAC_EQ        | 1_VOL[3:0]     |            | 0      |

| 0x1A     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | · · ·                                 | DAC_EQ3_4   |              | DAC_EC                    | 4_VOL[3:0]      |              |              | DAC_EQ        | 3_VOL[3:0]     |            | 0      |

| 0x1B     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | · ·                                   | DAC_EQ5     | DAC_EQ_EN    |                           |                 |              |              | DAC_EQ        | 5_VOL[3:0]     |            | 0      |

| 0x1C     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | · ·                                   | OUTMIX_L    | OUT_L_EN     | OUT_L_INV                 |                 |              |              | UT_L_SEL[4:0] |                |            | 0      |

| 0x1D     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   | · ·                                   | OUTMIX_R    | OUT_R_EN     | OUT_R_INV                 |                 |              | C            | UT_R_SEL[4:0] |                |            | 0      |

| 0x1E     | W   | 0  | 0 1  | 1   | 0    | 1  | 0 1   | 35  | · ·                                   | OUT1_L      | OUT1_L_EN    | OUT1_L_SE                 |                 |              | OUT1_L_V     | OL[5:0]       |                |            | 110101 |

| 0x1F     | W   | 0  | 0 1  | 1   | 0    | 1  | 0 1   | 35  | . I                                   | OUT1_R      | OUT1_R_EN    | OUT1_R_SE                 |                 |              | OUT1_R_V     | OL[5:0]       |                |            | 110101 |

| 0x20     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 1 1   | 3   |                                       | OUT2        | OUT2_EN      |                           | OUT2_S          | EL[8:0]      |              |               | OUT2_VOL[2:0]  |            | 11     |

| 0x21     | W   | 0  | 0 0  | 1   | 0    | 0  | 0 0   | 10  |                                       | HP_L_VOL    |              | HP_L_INV                  |                 |              | HP_L_VO      | L[5:0]        |                |            | 10000  |

| 0x22     | W   | 0  | 0 0  | 1   | 0    | 0  | 0 0   | 10  | _ · _ ]                               | HP_R_VOL    |              | HP_R_INV                  |                 |              | HP_R_VO      |               |                |            | 10000  |

| 0x23     | W   | 0  | 0 0  | 1 0 | 0    | 0  | 1 0   | 2   |                                       | HP_CFG      | HP_R_EN      | HP_MODE                   | STEREO_TRACK    | HP HIGHZ R   | HP L EN      | HP_SENSE_EN   | HP_2CAP_MODE   | HP_HIGHZ_L | 10     |

| 0x24     | W   | 0  | 0 0  | 1 0 | 0    | 0  | 0 0   | 0   |                                       | ZEROX       | HFZX R EN    | HPZX_L_EN                 | OUTZX R EN      | OUTZX_L_EN   | INZX_R_EN    | INZX L_EN     | A1ZX R EN      | A1ZX L EN  | 0      |

| 0x25     | W   | 0  | 1 1  | 1   | 0    | 1  | 1 0   | 76  | · · · · · · · · · · · · · · · · · · · | DAI_SRC_SEL | DALIN_R_MIX  |                           | DALOUT R SRC[2  | 2:0]         | DAI_IN_L_MIX | D/            | U OUT L SRC[2: | 0]         | 111011 |

| 0x26     | W   | 0  | 0 0  | 1 0 | 0    | 0  | 0 0   | 0   | · · ]                                 | DAI_CFG1    | DAI_MODE     |                           |                 | DAI_TDM_MONO | DAI_FR       | AME[1:0]      | DAI_WOR        | RD[1:0]    | 0      |

| 0x27     | W   | 0  | 0 0  | 1 0 | 0    | 0  | 0 0   | 0   |                                       | DAI_CFG2    |              | -                         |                 | DAI_TDM_OFF  | S[7:0]       |               |                |            | 0      |

| 0x28     | W   | 0  | 0 0  | 1 0 | 1    | 0  | 0 0   | 8   |                                       | DAI_CFG3    | DAI_EN       | 1                         |                 |              | DAI_OE       | DAI_TDM       | DALFORM        | AT[1:0]    | 1000   |

| 0x29     | W   | 0  | 0 0  | 1 0 | 0    | 0  | 0 0   | 0   | _ · _ ]                               | PLL_DIV1    |              | -                         |                 | PLL_DIV_H[1  | 9:12]        |               |                |            | 0      |

| 0x2A     | W   | 0  | 0 0  | 1 0 | 1 0  | 0  | 0 0   | 0   |                                       | PLL_DIV2    |              |                           |                 | PLL_DIV_M    |              |               |                |            | 0      |

| 0x2B     | W   | 0  | 0 0  | 1 1 | 0    | 0  | 0 0   | 10  | · · ·                                 | PLL_DIV3    |              | PLL_BYP                   | MCLK_R          | AN GE[1:0]   |              | PLL_D         | V_L[3:0]       |            | 10000  |

|          |     |    |      | _   | 1 1  | -  | 1 0   | A   |                                       | PLL         | PLL EN       |                           | MOLK_DET_EN     |              | -            |               | [3:0]          |            | 1010   |

Figure 13 Register Map Page 0

To select readback of an individual register click on the R/W bit of the required register and select R. To read the value press the submit button of the same row.

| Register | R/W                   | B7 | B6 | B5 | B4 | BЗ | B2 | B1 | BO | Hex | Submit   | FUNCTION | 7       |

|----------|-----------------------|----|----|----|----|----|----|----|----|-----|----------|----------|---------|

| 0x00     | W                     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | · )      | PAGE0    | REG_P/  |

| 0x01     | W                     | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 10  |          | CONTROL  | WRITE_N |

| 0x02     | R                     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |          | STATUS   |         |

| 0x03     | W                     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | _ · _ ]  | STARTUP1 | SC_CLK  |

| 0x04     | W                     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |          | STARTUP2 |         |

| 0x05     | W                     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |          | STARTUP3 |         |

| 0x06     |                       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | _ · _ ]  | RESERVED |         |

| 0x07     | <ul><li>✓ W</li></ul> |    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |          | MIC_L    | MIC_L   |

| 0x08     | R                     |    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |          | MIC_R    | MIC_R   |

| 0x09     | W                     | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 10  | <u> </u> | AUX1_L   | AUX1_L  |

| 0x0A     | W                     | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 10  |          | AUX1_R   | AUX1_F  |

| 0x0B     | W                     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |          | AUX2     |         |

| 0x0C     | W                     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |          | IN_GAIN  |         |

| 0x0D     | W                     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | <u> </u> | INMIX_L  | IN_L_   |

| 0x0E     | W                     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | <u> </u> | INMIX_R  | IN_R_   |

Figure 14 Selecting Individual Register Readback

A pop up window will then appear displaying the readback value of the register, Figure 15.

| Register Readback Value (Hex) | × |

|-------------------------------|---|

| Reg 0x6 = 0                   |   |

| QK                            |   |

Figure 15 Readback Pop-up Window

To select readback of all Page 0 register simultaneously press the read all button at the base of the R/W column. This will write the register readback values to a spreadheet file at the following location: *C:\Program Files\Dialog Semiconductor\Audio\DA7210\_11 Rev x.x \Page0\_Readback\_Values.xls*

| 🐱 Regi | ster Map | Pag | ye C | ) |   |   |   |   |   |    | →               |        |

|--------|----------|-----|------|---|---|---|---|---|---|----|-----------------|--------|

| 0420   | **       | •   | 0    |   |   |   |   | • | 0 |    |                 |        |

| 0x21   | W        | 0   | 0    | 1 | 1 | 0 | 1 | 0 | 1 | 35 | <u> </u>        | HP_L   |

| 0x22   | W        | 0   | 0    | 1 | 1 | 0 | 1 | 0 | 1 | 35 | <u> </u>        | HP_R   |

| 0x23   | W        | 1   | 0    | 1 | 0 | 1 | 1 | 1 | 0 | AE |                 | HP     |

| 0x24   | W        | 1   | 1    | 0 | 0 | 0 | 0 | 0 | 0 | CO | $\Box$ · $\Box$ | ZEF    |

| 0x25   | W        | 0   | 1    | 1 | 1 | 0 | 1 | 1 | 0 | 76 |                 | DAI_SF |

| 0x26   | W        | 0   | 0    | 0 | 0 | 0 | 1 | 1 | 0 | 6  |                 | DAI_   |

| 0x27   | W        | 0   | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0  | _ · _ ]         | DAI_   |

| 0x28   | W        | 1   | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 80 |                 | DAI_   |

| 0x29   | W        | 0   | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0  |                 | PLL_   |

| 0x2A   | W        | 0   | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0  |                 | PLL_   |

| 0x2B   | W        | 0   | 1    | 0 | 1 | 0 | 0 | 0 | 0 | 50 |                 | PLL_   |

| 0x2C   | W        | 0   | 0    | 0 | 0 | 1 | 0 | 1 | 1 | В  | _ · _ ]         | PI     |

|        | Read All |     |      |   |   |   |   |   |   |    | Submit All      | Reset  |

Figure 16 Readback All Registers

#### 4.3.3 Register Map Page 1

The page 1 register map panel allows access to single bits or to the hex value of a single register; both can be submitted individually. Readback from Page 1 registers is limited, but individual register readback can be selected in the same way as Page 1 where available.

| Disab | bled | Pa | iae 1 | l En | able | (4-w | ireп | ode | only | Re | set Table |              |          |                    |              |              |          |               |               |               |          |

|-------|------|----|-------|------|------|------|------|-----|------|----|-----------|--------------|----------|--------------------|--------------|--------------|----------|---------------|---------------|---------------|----------|

|       |      |    | _     |      |      |      |      |     |      |    |           | FUNCTION     | 7        | 6                  | 5            | 4            | 3        | 2             | 1             | 0             | DEFAULT  |

| 0x80  | W    | 0  | ) (   | ) (  | 0    | 0    | 0    | 0   | 0    | 0  | · ·       | PAGE1        | REG_PAGE |                    |              |              |          |               |               |               | 0        |

| 0x81  | R    | 0  | ) (   | ) (  | 1    | 0    | 0    | 0   | 1    | 11 | · ·       | CHIP_ID      |          | MRC[8:0] MMRC[2:0] |              |              |          |               |               |               | 10001    |

| 0x82  | R    | 0  | ) (   | ) '  | 0    | 1    | 1    | 0   | 0    | 2C |           | INTERFACE    |          | IF_BASE_ADDR[2:0]  |              | NCS_FOL      | RW_POL   | CPHA          | CPOL          | OTP_FUSED     | 101100   |

| 0x83  | W    | 0  | ) ·   | 1 (  | 0    | 0    | 0    | 0   | 0    | 40 |           | ALC_MAX      |          | ALC_MERGE          |              |              |          | ALC_MAX[5:0]  |               |               | 100000   |

| 0x84  | W    | 0  | ) (   | ) (  | 0    | 0    | 0    | 0   | 0    | 0  |           | ALC_MIN      |          |                    |              |              |          | ALC_MIN[5:0]  |               |               | 0        |

| 0x85  | W    | 0  | ) (   | ) (  | 0    | 0    | 0    | 0   | 0    | 0  |           | ALC_NOIS     |          |                    |              |              |          | ALC_NOI8[5:0] |               |               | 0        |

| 0x86  | W    | 0  | ) (   | ) (  | 0    | 0    | 0    | 0   | 0    | 0  | · · ·     | ALC_ATT      |          |                    |              | ALC_ATT[7:0] |          |               |               |               | 0        |

| 0x87  | W    | 0  | 0 1   | ) (  | 0    | 0    | 0    | 0   | 0    | 0  | · ·       | ALC_REL      |          |                    |              | ALC_REL(7:0) |          |               |               |               | 0        |

| 0x88  | W    | 0  | 1 0   | ) (  | 0    | 0    | 0    | 0   | 0    | 0  | · · ·     | ALC_DEL      |          |                    |              | ALC_DEL[7:0] |          |               |               |               | 0        |

| 0x8A  | W    | 1  | 1 1   | ) (  | 0    | 1    | 0    | 1   | 1    | 8B | _ ·       | A_HD_JNLOCK  |          |                    |              | HDDBN[7:0]   |          |               |               |               | 10001011 |

| 0x8B  | W    | 1  | 1   1 | ) 1  | 1    | 0    | 1    | 0   | 0    | B4 | · · ·     | A_TST_UNLOCK |          |                    |              | TEST[7:0]    |          |               | -             |               | 10110100 |

| 0x90  | W    | 0  | ) (   | ) (  | 0    | 0    | 0    | 0   | 0    | 0  | -         | A_PLL1       |          |                    |              |              |          |               |               | VCORST_EN     | 0        |

| 0x95  | W    | 0  | ) (   | ) (  | 0    | 0    | 0    | 0   | 0    | 0  | · ·       | A_ACCO       |          |                    |              |              | ADC_T2   |               |               |               | 0        |

| 0x96  | W    | 0  | ) (   | ) (  | 0    | 0    | 1    | 1   | 1    | 7  |           | A_DAC0       |          |                    |              |              |          | VMD_BUFF_EN2  | VVID_BLFF_EN' | VMID_BUFF_EN2 | 111      |

| 0xA7  | W    | 0  | ) ·   | 1    | 1    | 1    | 1    | 1   | 0    | 7E | · ·       | A_CP_MODE    |          | VDC_EN             | VDD/2_EN     | VDD/8_EN     | VDD/4_EN | HP_LML_DET    | DAC_LVL_DET   | YOL_LYL_DET   | 1111110  |

| 0xB7  | W    | 0  | 0 1   | ) (  | 1 0  | 0    | 0    | 0   | 0    | 0  | -         | A_BGAP       |          |                    | DIGREG_CNTL1 | DIGREG_CNTL0 |          |               |               |               | 0        |

Figure 17 Register Map Page 1

#### 4.3.4 GP Filters Register Map

The general purpose filters register map panel allows access to the hex value of a single register; all registers are submitted after changes. All registers may also be reset using the *Reset Filters* button.

| Filter Coefficients                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2F         GP1A_A0H         39         GP1D_A0H           30         GP1B_A0L         3A         GP2C_A0L           31         GP1B_A0H         3B         GP2C_A0H           32         GP2A_A0L         3C         GP2D_A0L           33         GP2A_A0H         3D         GP2D_A0H           34         GP2B_A0H         3D         GP2D_A0H           34         GP2B_A0L         3E         GP1A_A1L           35         GP2B_A0H         3F         GP1A_A1H           36         GP1C_A0L         40         GP1B_A1L | 43         GP2A         A1H         4D         GP2D         A1H           44         GP2B         A1L         4E         GP1A         A2L           45         GP2B         A1H         4F         GP1A         A2L           45         GP2B         A1H         4F         GP1A         A2L           46         GP1C         A1L         50         GP1B         A2L           47         GP1C         A1H         51         GP1B         A2L           48         GP1D         A1L         52         GP2A         A2L           49         GP1D         A1H         53         GP2A         A2L           4A         GP2C         A1L         54         GP2B         A2L | 1 59 GP1D_A2H 63 GP2A_B1H<br>5A GP2C_A2L 64 GP2B_B1L<br>1 5B GP2C_A2H 65 GP2B_B1H<br>5C GP2D_A2L 66 GP1C_B1L | 6B         GP2C_B1H         75         GP2B_B2H           6C         GP2D_B1L         76         GP1C_B2L           6D         GP2D_B1H         77         GP1C_B2H           6E         GP1A_B2L         78         GP1D_B2L           6F         GP1A_B2H         79         GP1D_B2H           70         GP1B_B2L         7A         GP2C_B2L           71         GP1B_B2H         7B         GP2C_B2H           72         GP2A_B2L         7C         GP2D_B2L |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x2D \$ 0 0x37 \$ 0<br>0x2E \$ 0 0x38 \$ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x41 ♀ 0     0x4B ♀ 0       0x42 ♀ 0     0x4C ♀ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x55 \$ 0 0x5F \$ 0<br>0x56 \$ 0 0x60 \$ 0                                                                   | 0x69 ‡ 0 0x73 ‡ 0<br>0x6A ‡ 0 0x74 ‡ 0                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x2F 🗘 0 0x39 🗘 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x43 ♀ 0 0x4D ♀ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x57 🗘 0 0x61 🗘 0                                                                                            | <b>0x6B ↓</b> 0 <b>0x75 ↓</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x30 🗘 0 0x3A 🗘 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>0x44 0 0x4E 0</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x58 ♀ 0 0x62 ♀ 0                                                                                            | <b>0x6C</b> 0 <b>0x76</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x31 ‡ 0 0x3B ‡ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>0x45</b> 🗘 0 <b>0x4F</b> 🗘 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>0x59 ⊕ 0 0x63 ⊕ 0</b>                                                                                     | <b>0x6D ↓</b> 0 <b>0x77 ↓</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x32 🗘 0 0x3C 🗘 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>0x46</b> 0 <b>0x50</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x5A ♀ 0 0x64 ♀ 0                                                                                            | <b>0x6E</b> 0 <b>0x78</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x33 ‡ 0 0x3D ‡ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>0x47 ↓</b> 0 <b>0x51 ↓</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>0x5B ↓</b> 0 <b>0x65 ↓</b> 0                                                                              | <b>0x6F</b> 0 <b>0x79</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x34 🗘 0 0x3E 🗘 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>0x48</b> 0 <b>0x52</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x5C ♀ 0 0x66 ♀ 0                                                                                            | <b>0x70</b> 0 <b>0x7A</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x35 🗘 0 0x3F 🗘 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>0x49 ‡ 0 0x53 ‡ 0</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x5D ♀ 0 0x67 ♀ 0                                                                                            | 0x71 🗘 0 0x7B 🗘 0                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x36 🗘 0 0x40 🗘 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>0x4A</b> 🗘 0 <b>0x54</b> 🗘 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x5E ‡ 0 0x68 ‡ 0                                                                                            | 0x72 ÷ 0 0x7C ÷ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Submit Filters Reset Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GP1AB/2AB - 0x7D 🗘 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GP1CD/2CD - 0x7E = 75                                                                                        | GP Enable - 0x7F 🗘                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Figure 18 Filter Coefficients Set-up Panel

An alternative 'RT Filters' GUI is available that allows easy submission of any of the DAC or ADC filters paths present within the DA7210/11. This is contained on the installation DVD within the distribution kit.

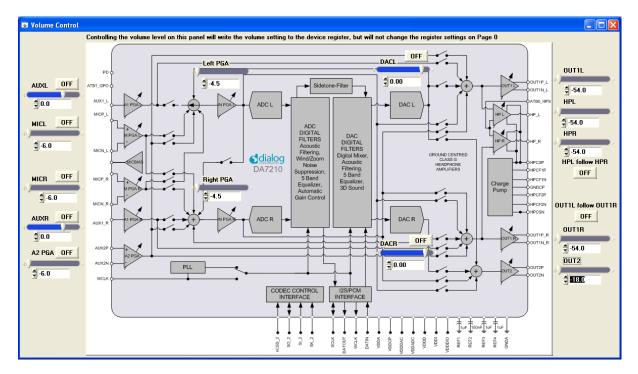

#### 4.3.5 Volume Control Panel

The *Volume Control* panel allows real time changes to any of the analogue input or output PGAs within the DUT. Muting is also possible where this function exists.

Gain controls are available to the following PGAs:

- AUX\_L and AUX\_R

- MIC\_L and MIC\_R

- A2 PGA

- Left and Right Input PGAs

- OUT1\_L and OUT1\_R

- HPL and HPR

- OUT2

It is possible to change the headphone and OUT1 gain control registers as stereo pairs by simultaneously selecting the *HPL follow HPR* and *OUT1L follow OUT1R* buttons.

**Figure 19 Volume Control Panel**

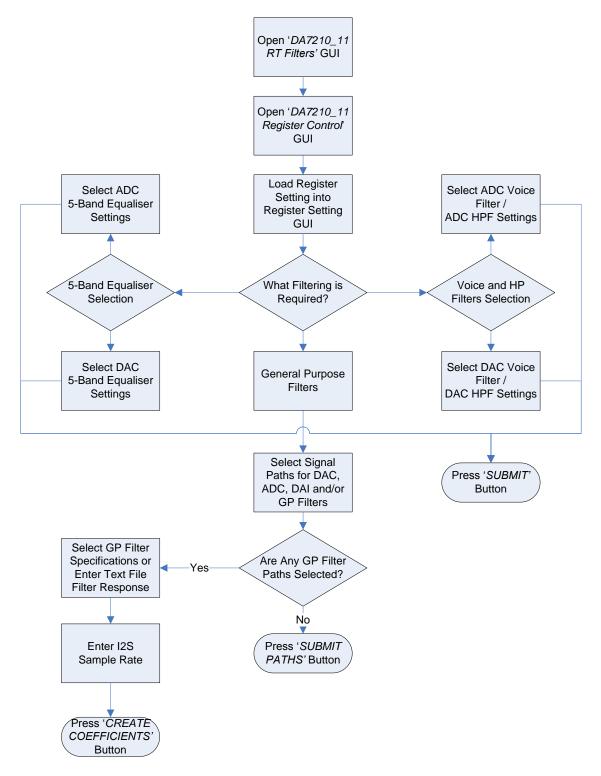

### 5 RT Filters GUI

The RT filters GUI allows easy control of all the filter options within the DA7210/11 device through USB control. This includes general purpose filters, five-band equalisers and voice filters for ADC and DAC.

The *Filter Setup* page makes it possible to design the required filter response for all of the general purpose filter bi-quad IIR paths available in the DA7210/11.

#### 5.1 Software Installation

The set-up file for the RT Filters control software can be found on the accompanying DVD in the folder *DA7210 RT Filters Rev x.x*

Double click setup.exe file and the install will begin.

| 🐙 DA7210 Realtime Filters Rev1_0                                                                                                                                                                                                         |        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| It is strongly recommended that you exit all programs before running this<br>installer. Applications that run in the background, such as virus-scanning<br>utilities, might cause the installer to take longer than average to complete. |        |

| Please wait while the installer initializes.                                                                                                                                                                                             |        |

|                                                                                                                                                                                                                                          |        |

|                                                                                                                                                                                                                                          |        |

|                                                                                                                                                                                                                                          | Cancel |

Do not change the installation directory or necessary license files will not be accessible.

| 1 DA7210 Realtime Filters Rev1_0                                                                                                                                        |                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Destination Directory<br>Select the primary installation directory.                                                                                                     |                |

| All software will be installed in the following location(s). To install software into a<br>different location(s), click the Browse button and select another directory. |                |

| Directory for DA7210 Realtime Filters Rev1_0<br>C:\Program Files\DA7210 Realtime Filters Rev1_0\<br>Browse                                                              |                |

| Directory for National Instruments products<br>C:\Program Files\National Instruments\<br>Browse                                                                         |                |

| << Back Next >>                                                                                                                                                         | <u>C</u> ancel |

Select I accept the License Agreement and press Next>>

| I DA 7210 Realtime Filters Rev1_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|