# **General Description**

The DA14585 is an ultra-low power SoC integrating a 2.4 GHz transceiver and an *ARM Cortex-M0*™ microcontroller with 96kB of RAM and 64kB of One-Time Programmable (OTP) memory. It offers a very fast boot time (<50ms) and supports up to 8 BLE connections. It can be used as a standalone application processor or as a data pump in hosted systems.

The radio transceiver, the baseband processor and the qualified *Bluetooth® LE* stack is fully compliant with the *Bluetooth® Low Energy 5.0* standard.

The DA14585 has dedicated hardware for the Link Layer implementation of *Bluetooth® Low Energy* and interface controllers for enhanced connectivity capabilities.

The *Bluetooth*® *Low Energy* firmware includes the L2CAP service layer protocols, Security Manager (SM), Attribute Protocol (ATT), the Generic Attribute Profile (GATT) and the Generic Access Profile (GAP). All profiles published by the *Bluetooth* SIG as well as custom profiles are supported.

The device is suitable for remote control units (RCU) requiring support for voice commands, wireless sensor nodes, Bluetooth Mesh applications, fitness trackers, toys and HID devices (keyboards, mice, etc.).

# **Key Features**

|                                           | mplies with <i>Bluetooth V5.0</i> , ETSI EN 300 328 and EN            | ■ Fle     | exible Reset Circuitry                                  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------|-----------|---------------------------------------------------------|--|--|

|                                           | 0 440 Class 2 (Europe), FCC CFR47 Part 15 (US) and IB STD-T66 (Japan) |           | System & Power On Reset in a single pin                 |  |  |

| Supports up to 8 Bluetooth LE connections |                                                                       |           | eneral purpose, Capture and Sleep timers                |  |  |

| Fas                                       | st cold boot in less than 50 ms                                       | ■ Dig     | Digital interfaces                                      |  |  |

| Pro                                       | cessing power                                                         |           | Gen. purpose I/Os: 14 (WLCSP34), 25 (QFN40), 32 (QFN48) |  |  |

|                                           | 16 MHz 32 bit ARM Cortex-M0 with SWD interface                        |           | 2 x UARTs with hardware flow control up to 1 Mbps       |  |  |

|                                           | Dedicated Link Layer Processor                                        |           | SPI+™ interface                                         |  |  |

|                                           | AES-128 bit encryption Processor                                      |           | I2C bus at 100 kHz, 400 kHz                             |  |  |

| Mei                                       | mories                                                                |           | 3-axes capable Quadrature Decoder                       |  |  |

|                                           | 64 kB One-Time-Programmable (OTP) memory                              | –<br>■ An | alog interfaces                                         |  |  |

|                                           | 96 kB Data/Retention SRAM                                             | _ /       | 4-channel 10-bit ADC                                    |  |  |

|                                           | 128 kB ROM                                                            | _         | dio transceiver                                         |  |  |

| Pov                                       | ver management                                                        |           | Fully integrated 2.4 GHz CMOS transceiver               |  |  |

|                                           | Integrated Buck/Boost DCDC converter                                  |           | Single wire antenna: no RF matching or RX/TX            |  |  |

|                                           | P0, P1 and P2 ports with 3.3 V tolerance                              | Ш         | switching required                                      |  |  |

|                                           | Easy decoupling of only 4 supply pins                                 |           | Supply current at VBAT3V:                               |  |  |

|                                           | Supports coin (typ. 3.0 V) and alkaline (typ. 1.5 V)                  |           | TX: 3.4 mA, RX: 3.7 mA (with ideal DC-DC)               |  |  |

|                                           | battery cells                                                         |           | 0 dBm transmit output power                             |  |  |

|                                           | 1.8 V cold boot support                                               |           | -20 dBm output power in "Near Field Mode"               |  |  |

|                                           | 10-bit ADC for battery voltage measurement                            |           | -93 dBm receiver sensitivity                            |  |  |

| Dig                                       | ital controlled oscillators                                           | ■ Pa      | ckages:                                                 |  |  |

|                                           | 16 MHz crystal (±20 ppm max) and RC oscillator                        |           | WLCSP 34 pins, 2.40 mm x 2.66 mm                        |  |  |

|                                           | 32 kHz crystal (±50 ppm, ±500 ppm max) and RCX                        |           | QFN 40 pins, 5 mm x 5 mm                                |  |  |

|                                           | oscillator                                                            | П         | QFN 48 pins, 6 mm x 6 mm                                |  |  |

# **Applications**

- Voice-controlled remote controls

- Beacons

- (Multi-sensor) Wearable devices

- □ Fitness trackers

- □ Consumer health

- Smartwatches

- Human interface devices

- □ Keyboard

- □ Mouse

- Toys

- Consumer appliances

# **Key Benefits**

- Lowest power consumption

- Smallest system size

- Lowest system cost

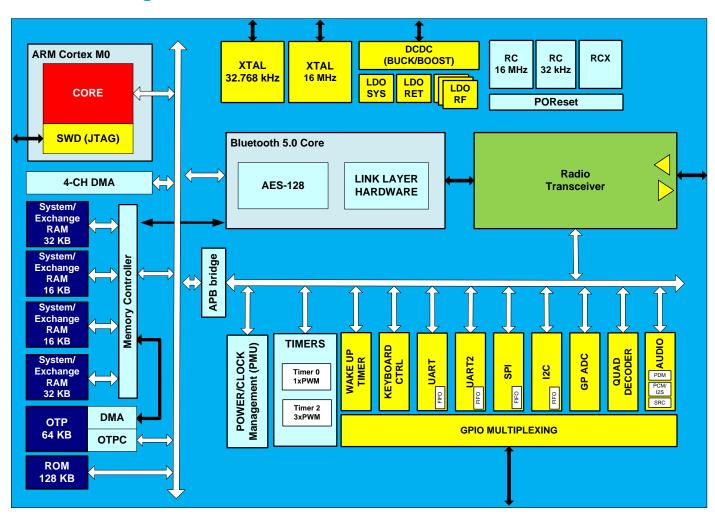

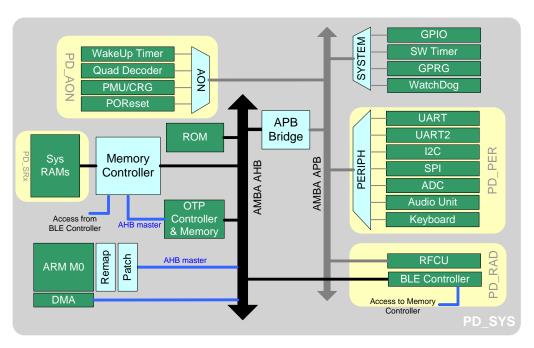

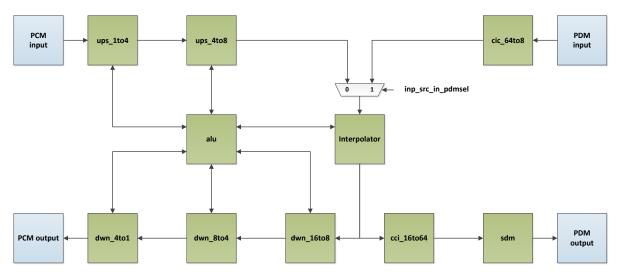

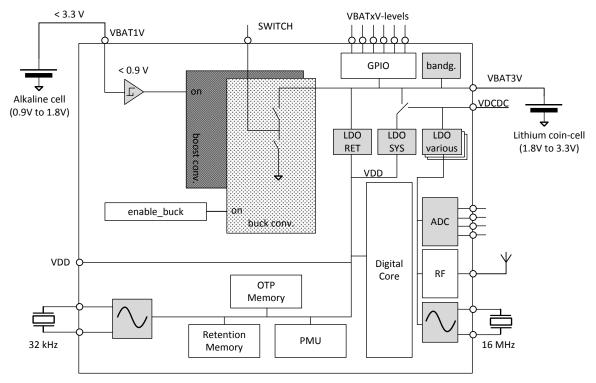

# **System Diagram**

Figure 1: System Diagram

2 of 340

# **Contents**

| Ge | General Description 1 |           |              |                                                        |    |

|----|-----------------------|-----------|--------------|--------------------------------------------------------|----|

| Ke | y Feat                | ures      |              |                                                        | 1  |

| Αp | plicati               | ons       |              |                                                        | 1  |

| Ke | y Bene                | efits     |              |                                                        | 2  |

| Sv | stem [                | Diagram . |              |                                                        | 2  |

| •  |                       | _         |              |                                                        |    |

|    |                       |           |              |                                                        |    |

|    | •                     |           |              |                                                        |    |

|    |                       |           |              |                                                        |    |

| 1  |                       |           | •            | ram                                                    |    |

| 2  |                       |           |              |                                                        |    |

| 3  | •                     |           |              |                                                        |    |

|    | 3.1                   |           |              | Ratings                                                |    |

|    | 3.2                   |           | -            | rating Conditions                                      |    |

|    | 3.3                   |           |              |                                                        |    |

|    | 3.4                   | •         |              | Ustra Ohara taristica                                  |    |

|    | 3.5                   |           | -            | llator Characteristics                                 |    |

|    | 3.6<br>3.7            |           | •            | lator Characteristicscy RCX Oscillator Characteristics |    |

|    | 3.8                   |           | •            | Characteristics                                        |    |

|    | 3.9                   | •         |              | C Characteristics                                      |    |

|    | 3.10                  |           | -            | naracteristics                                         |    |

|    | 3.11                  |           |              | S                                                      |    |

| 4  |                       |           |              |                                                        |    |

| _  | 4.1                   |           |              |                                                        |    |

|    | 4.2                   |           |              |                                                        |    |

|    | 4.3                   |           |              |                                                        |    |

|    |                       | 4.3.1     |              | er                                                     |    |

|    | 4.4                   |           |              | ure                                                    |    |

|    |                       | 4.4.1     |              | ke-Up Sequence                                         |    |

|    |                       | 4.4.2     |              | ing                                                    |    |

|    |                       | 4.4.3     | BootROM S    | Sequence                                               | 45 |

|    | 4.5                   | Power S   | upply Config | guration                                               | 48 |

|    |                       | 4.5.1     | Power Dom    | nains                                                  | 48 |

|    |                       | 4.5.2     | Power Mod    | les                                                    | 48 |

|    |                       | 4.5.3     | Retention F  | Registers                                              | 49 |

|    |                       | 4.5.4     | Sleep LDO    | Voltage Trimming                                       | 50 |

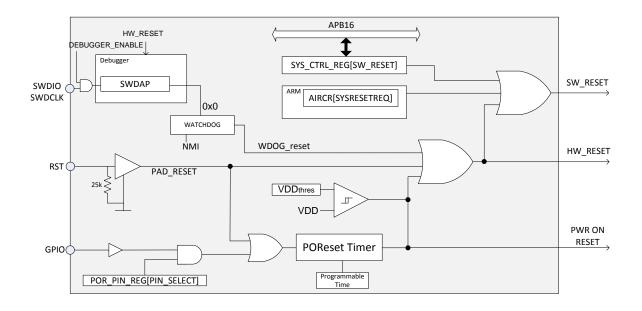

| 5  | Rese                  | t         |              |                                                        | 51 |

|    | 5.1                   | POR, HV   | V and SW R   | eset                                                   | 51 |

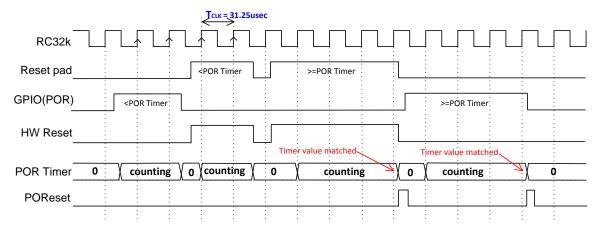

|    |                       | 5.1.1     | Power-On I   | Reset Functionality                                    | 52 |

|    |                       |           | 5.1.1.1      | POR Timer Clock                                        | 53 |

|    |                       |           | 5.1.1.2      | Reset Pad                                              |    |

|    |                       |           | 5.1.1.3      | POR from GPIO                                          |    |

|    |                       | 5.1.2     | Power-On I   | Reset Timing Diagram                                   | 53 |

|    |                       |           |              |                                                        |    |

|    |              | 5.1.3 Power-On Reset Considerations                | 54 |

|----|--------------|----------------------------------------------------|----|

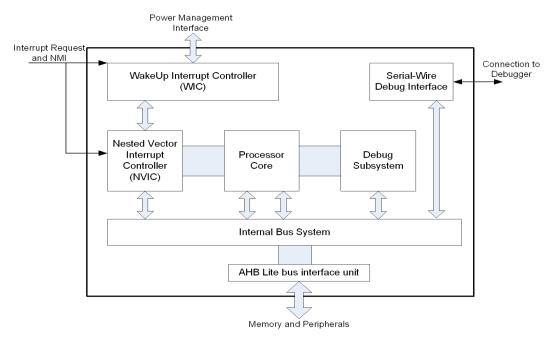

| 6  | ARM          | Cortex-M0                                          | 55 |

|    | 6.1          | Interrupts                                         | 56 |

|    | 6.2          | System Timer (systick)                             | 58 |

|    | 6.3          | Wake-Up Interrupt Controller                       | 58 |

|    | 6.4          | Reference                                          | 58 |

| 7  | AMB          | A Bus Overview                                     | 59 |

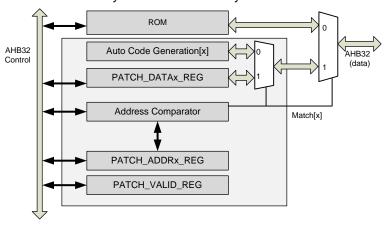

| 8  | Patch        | 1 Block                                            | 60 |

| 9  | Mem          | ory Map                                            | 62 |

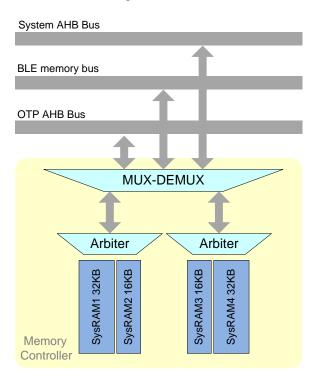

| 10 | Mem          | ory Controller                                     | 64 |

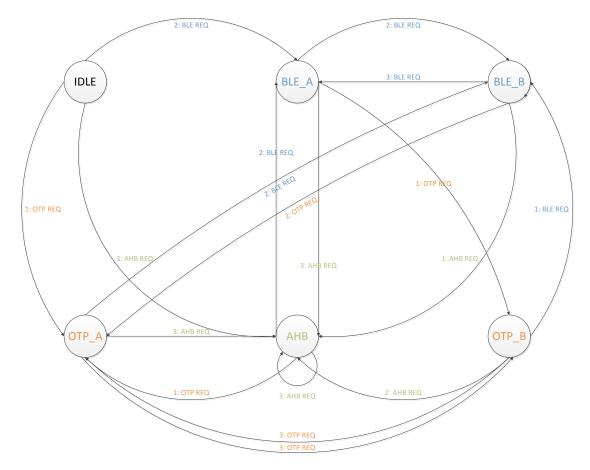

|    | 10.1         | Arbitration                                        | 65 |

| 11 | Clock        | k Generation                                       | 66 |

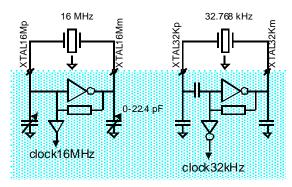

|    | 11.1         | Crystal Oscillators                                | 66 |

|    |              | 11.1.1 Frequency Control (16 MHz Crystal)          | 66 |

|    |              | 11.1.2 Automated Trimming Mechanism                | 67 |

|    | 11.2         | RC Oscillators                                     | 67 |

|    |              | 11.2.1 Frequency Calibration                       | 68 |

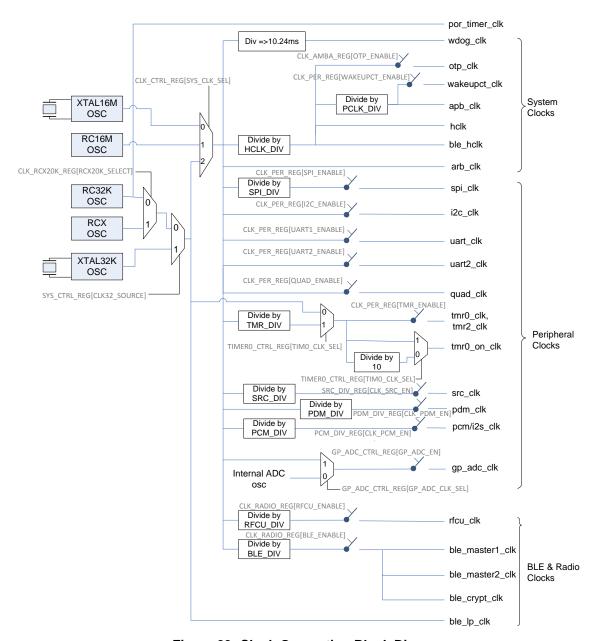

|    | 11.3         | System Clock Generation                            | 68 |

|    | 11.4         | General Clock Constraints                          | 70 |

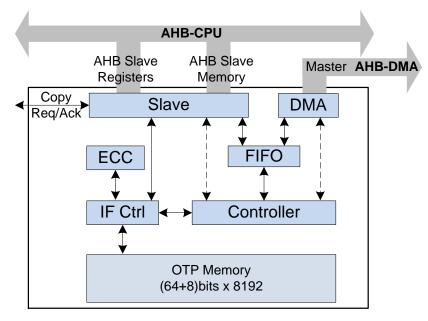

| 12 | OTP          | Controller                                         | 71 |

|    | 12.1         | Introduction                                       | 71 |

|    | 12.2         | Operating Modes                                    | 71 |

|    | 12.3         | AHB Master Interface                               |    |

|    | 12.4         | AHB Slave Interface                                |    |

|    | 12.5         | Error Correcting Code (ECC)                        |    |

|    | 12.6         | BUILD-IN Self Repair (BISR)                        | 73 |

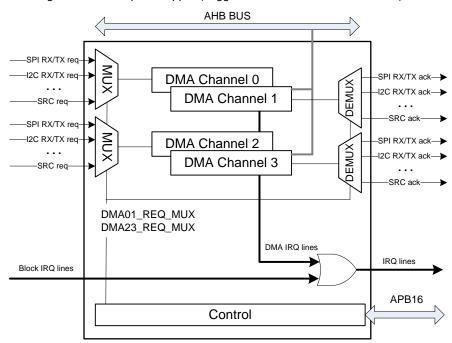

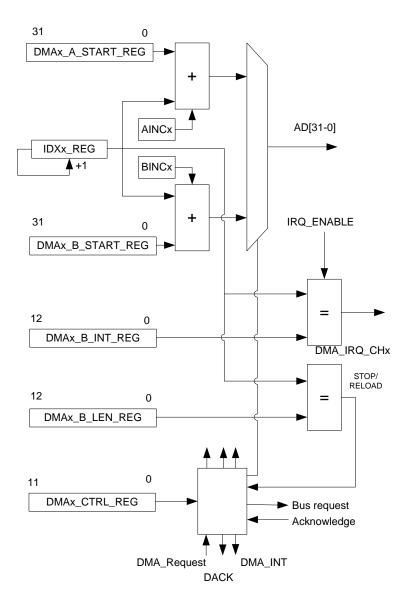

| 13 | DMA          | controller                                         | 74 |

|    | 13.1         | DMA Peripherals                                    | 74 |

|    | 13.2         | Input/Output Multiplexer                           |    |

|    | 13.3         | DMA Channel Operation                              |    |

|    | 13.4         | DMA Arbitration                                    |    |

|    | 13.5         | Freezing DMA channels                              | 77 |

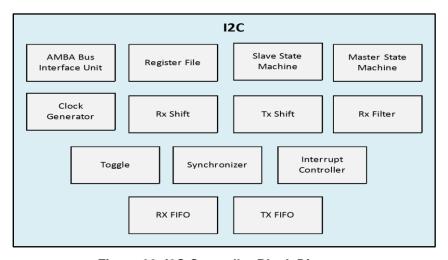

| 14 | I2C Ir       | nterface                                           |    |

|    | 14.1         | I2C Bus Terms                                      |    |

|    |              | 14.1.1 Bus Transfer Terms                          |    |

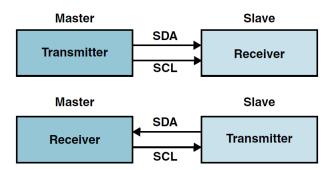

|    | 14.2         | I2C Behavior                                       |    |

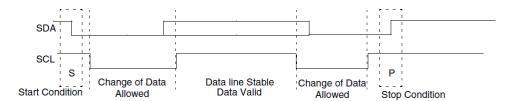

|    |              | 14.2.1 START and STOP Generation                   |    |

|    |              | 14.2.2 Combined Formats                            |    |

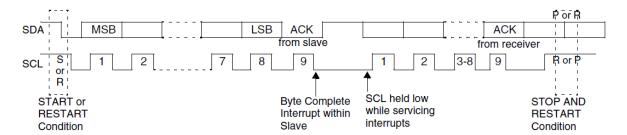

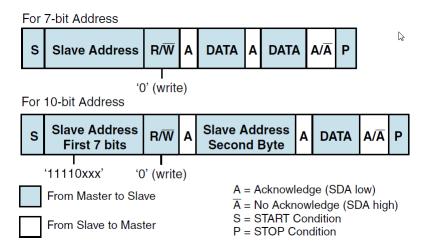

|    | 14.3         | I2C Protocols                                      |    |

|    |              | 14.3.1 START and STOP Conditions                   |    |

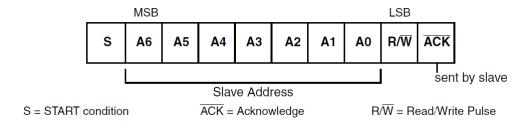

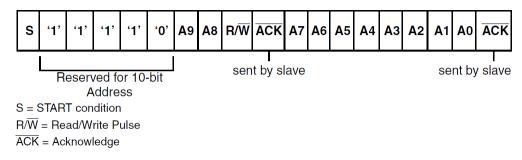

|    |              | 14.3.2 Addressing Slave Protocol.                  |    |

|    | 111          | 14.3.3 Transmitting and Receiving Protocols        |    |

|    | 14.4<br>14.5 | Multiple Master Arbitration  Clock Synchronization |    |

|    | 14.5         | Operation Modes                                    |    |

|    | 14.0         | Ορειαιιοι ινιουες                                  | ပ၁ |

|    |       |            | Slave Mode Operation                   |     |

|----|-------|------------|----------------------------------------|-----|

|    |       | 14.6.2     | Master Mode Operation                  | 88  |

|    | 14.7  | Disabling  | the I2C Controller                     | 89  |

| 15 | UART  | -<br>      |                                        | 90  |

|    | 15.1  | UART (R    | RS232) Serial Protocol                 | 91  |

|    | 15.2  | IrDA 1.0   | SIR Protocol                           | 92  |

|    | 15.3  | Clock Su   | ıpport                                 | 93  |

|    | 15.4  | Interrupts | S                                      | 93  |

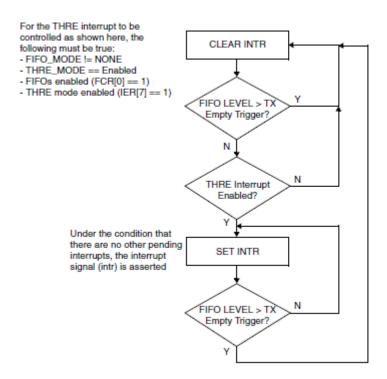

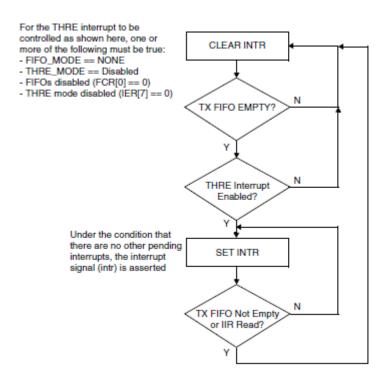

|    | 15.5  | Programi   | mable THRE Interrupt                   | 94  |

|    | 15.6  | Shadow     | Registers                              | 96  |

|    | 15.7  | Direct Te  | est Mode                               | 96  |

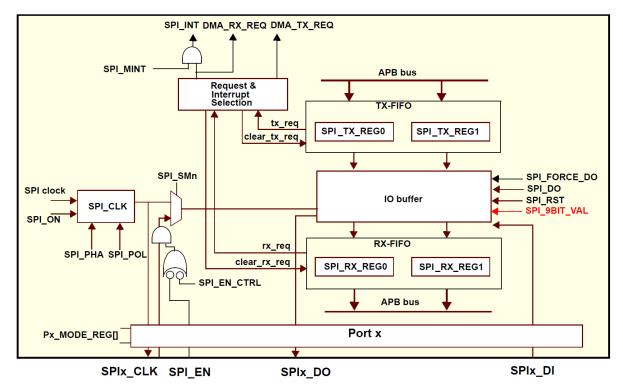

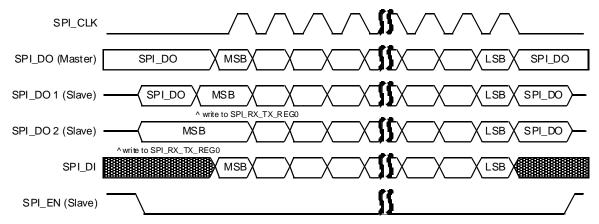

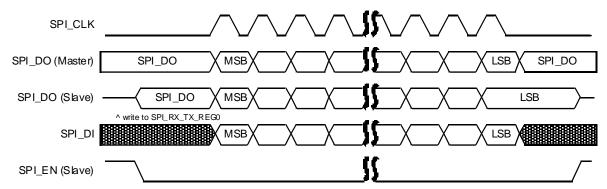

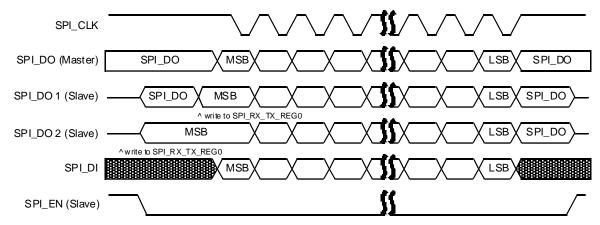

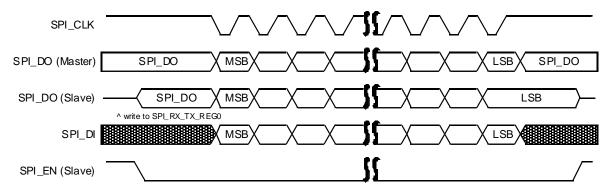

| 16 | SPI+  | Interface. |                                        | 97  |

|    | 16.1  | Operation  | n without FIFOs                        | 98  |

|    | 16.2  | 9 Bits Mo  | ode                                    | 99  |

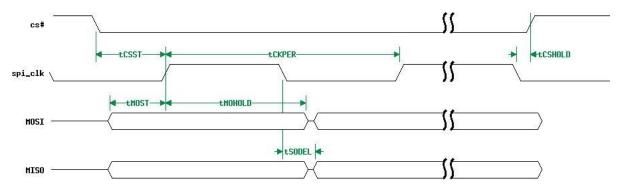

|    | 16.3  | SPI Timir  | ng                                     | 100 |

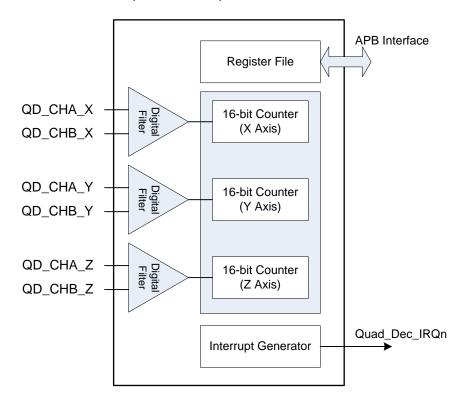

| 17 | Quad  | rature De  | ecoder                                 | 102 |

|    |       |            | PT                                     |     |

|    |       | -          | ose Timers                             |     |

| 19 |       | •          | ose Timers                             |     |

|    |       |            |                                        |     |

|    |       |            |                                        |     |

|    |       | _          | ner                                    |     |

| 21 | -     |            | troller                                |     |

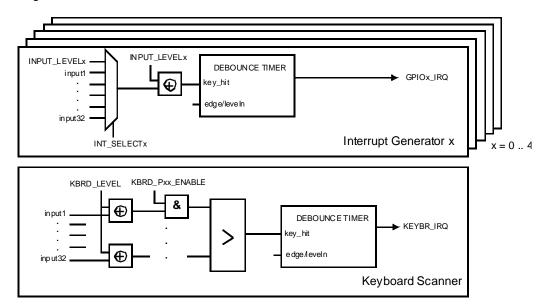

|    | 21.1  | •          | d Scanner                              |     |

|    |       |            | errupt Generator                       |     |

| 22 | •     | •          | Ports                                  |     |

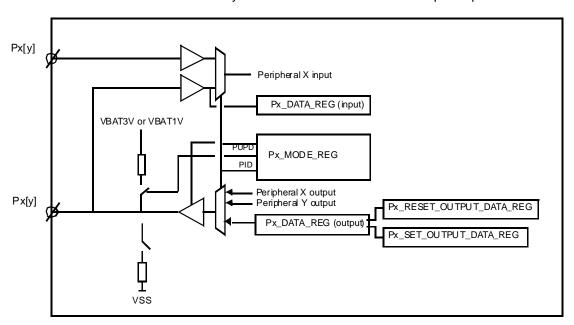

|    | 22.1  | -          | mable Pin Assignment                   |     |

|    | 22.2  |            | Purpose Port Registers                 |     |

|    |       | 22.2.1     | Port Data Register                     |     |

|    |       | 22.2.2     | Port Set Data Output Register          |     |

|    |       |            | Port Reset Data Output Register        |     |

|    | 22.3  | Fixed As   | signment Functionality                 | 116 |

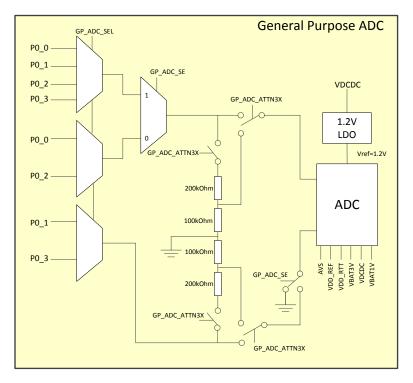

| 23 | Gene  | ral Purpo  | ose ADC                                | 118 |

|    | 23.1  | Input Cha  | annels and Input Scale                 | 118 |

|    | 23.2  | _          | the ADC and Sampling Rate              |     |

|    | 23.3  |            | al Effects                             |     |

|    | 23.4  |            | g                                      |     |

|    | 23.5  |            | alibration                             |     |

|    |       |            | ale Adjustment                         |     |

|    |       |            | n Mode Adjustment                      |     |

|    | 23.8  |            | pedance, Inductance and Input Settling |     |

|    |       | •          | ounter                                 |     |

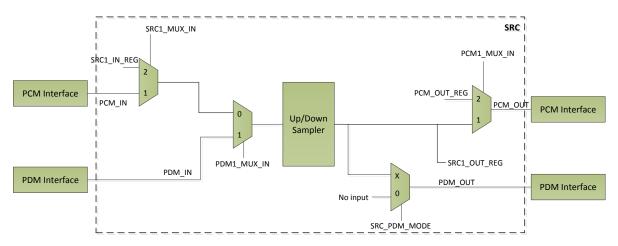

| 24 | Audio | •          | J)                                     |     |

|    | 24.1  | Introducti | ion                                    | 123 |

|    | 24.2  | Architect  | ure                                    |     |

|    |       | 24.2.1     | Data Paths                             | 124 |

|    |       |            |                                        |     |

**Datasheet**

© 2018 Dialog Semiconductor

|    |       | 24.2.2    | Up/Down     | Sampler                                  | 124 |

|----|-------|-----------|-------------|------------------------------------------|-----|

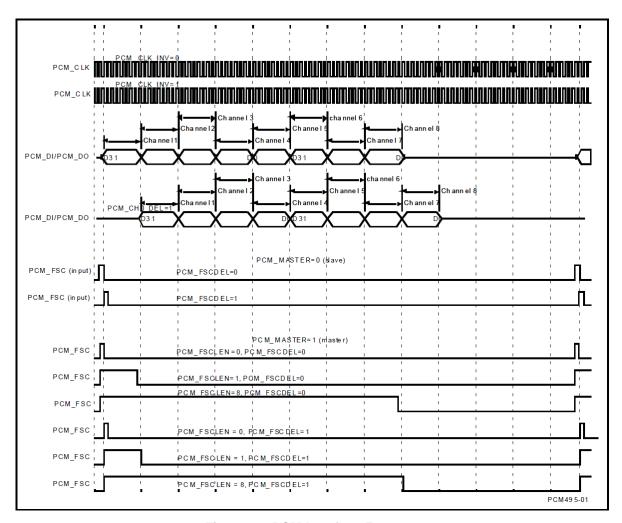

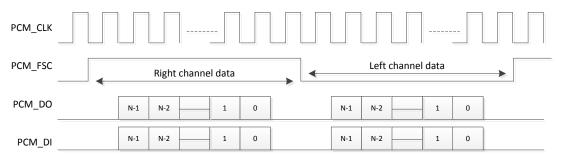

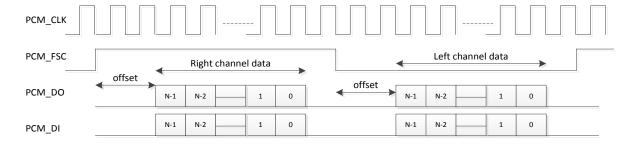

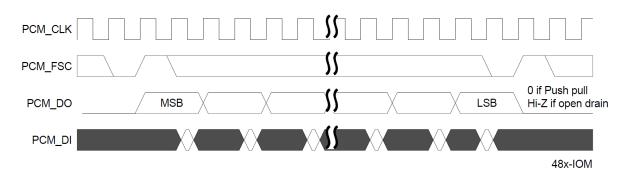

|    |       | 24.2.3    | PCM Inter   | face                                     | 125 |

|    |       |           | 24.2.3.1    | Channel Access and Delay                 | 125 |

|    |       |           | 24.2.3.2    | Clock Generation                         | 125 |

|    |       |           | 24.2.3.3    | External Synchronization                 | 127 |

|    |       |           | 24.2.3.4    | Data Formats                             |     |

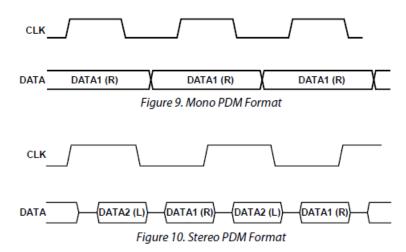

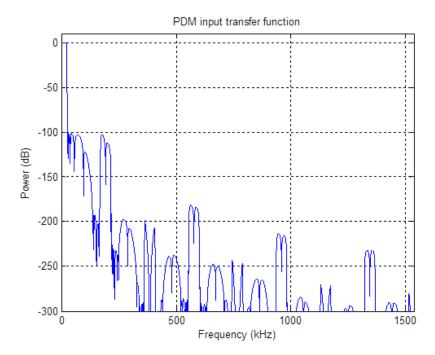

|    |       | 24.2.4    | PDM Inter   | face                                     | 130 |

|    |       | 24.2.5    | DMA Supp    | port                                     | 131 |

|    |       | 24.2.6    | Interrupts. |                                          | 131 |

| 25 | Powe  | r Manag   | ement       |                                          | 132 |

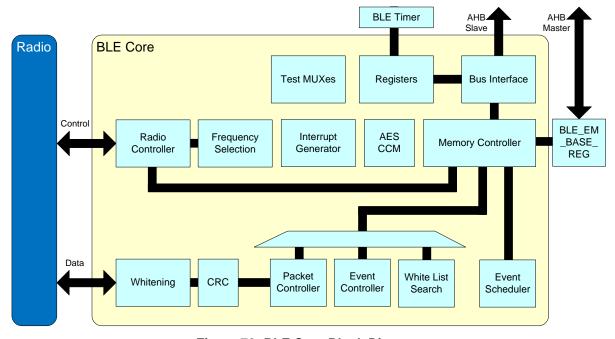

| 26 | BLE ( | Core      |             |                                          | 135 |

|    | 26.1  | Architect | ture        |                                          | 136 |

|    |       | 26.1.1    | Exchange    | Memory                                   | 136 |

|    | 26.2  | Program   | ū           | ······································   |     |

|    |       | 26.2.1    | _           | IRQ                                      |     |

|    |       | 26.2.2    | •           | m BLE Active Mode to BLE Deep Sleep Mode |     |

|    |       | 26.2.3    |             | m BLE Deep Sleep Mode to BLE Active Mode |     |

|    |       | 26.2.4    |             | at Anchor Points                         |     |

|    |       | 26.2.5    | _           | Due to an External Event                 |     |

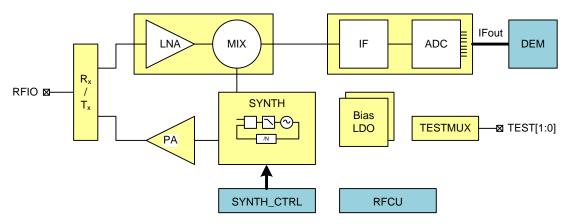

| 27 | Dadia |           | •           |                                          |     |

| 21 | 27.1  |           |             |                                          |     |

|    | 27.1  |           |             |                                          |     |

|    |       | •         |             |                                          |     |

|    | 27.4  |           |             |                                          |     |

|    | 27.5  |           |             |                                          |     |

|    | _     | •         |             |                                          |     |

| 28 |       |           |             |                                          |     |

| 20 | _     |           |             | us Registers                             |     |

|    |       | _         |             | S                                        |     |

|    |       |           | Ū           | 3                                        |     |

|    |       |           | Ü           | nd Reset Registers                       |     |

|    | 28.5  |           |             | egisters                                 |     |

|    | 28.6  |           |             | gisters                                  |     |

|    | 28.7  |           | _           | DC Registers                             |     |

|    | 28.8  |           | -           | D Registers                              |     |

|    |       |           | •           | egisters                                 |     |

|    |       |           | -           | ters                                     |     |

|    |       |           | _           |                                          |     |

|    |       | -         | _           | isters                                   |     |

|    |       |           | _           | r Registers                              |     |

|    |       |           |             | ters                                     |     |

|    |       |           | _           | VM Registers                             |     |

|    |       |           | •           | gisters                                  |     |

|    |       |           |             | ters                                     |     |

|    |       | •         | _           |                                          |     |

|    |       | ,         |             | S                                        |     |

|    | •     |           | 9.5.51      | -                                        |     |

6 of 340

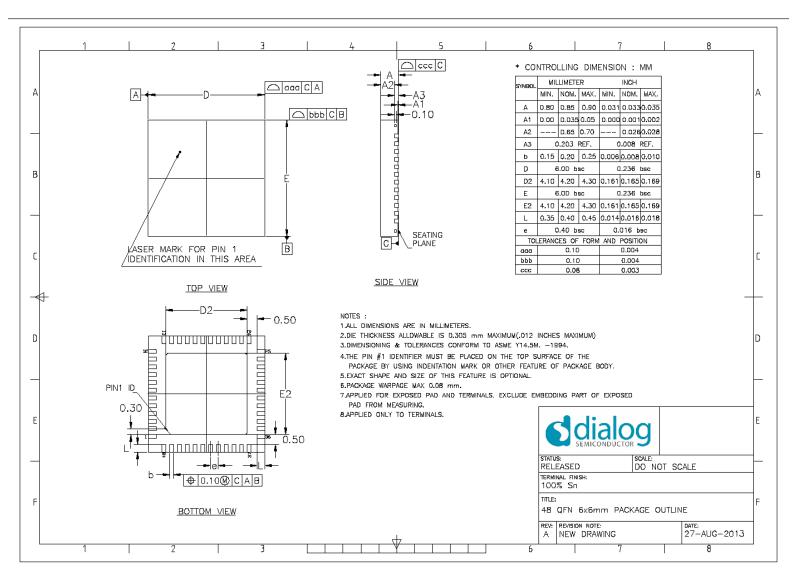

| 29  | Orde   | ring Information                                                            | 335            |

|-----|--------|-----------------------------------------------------------------------------|----------------|

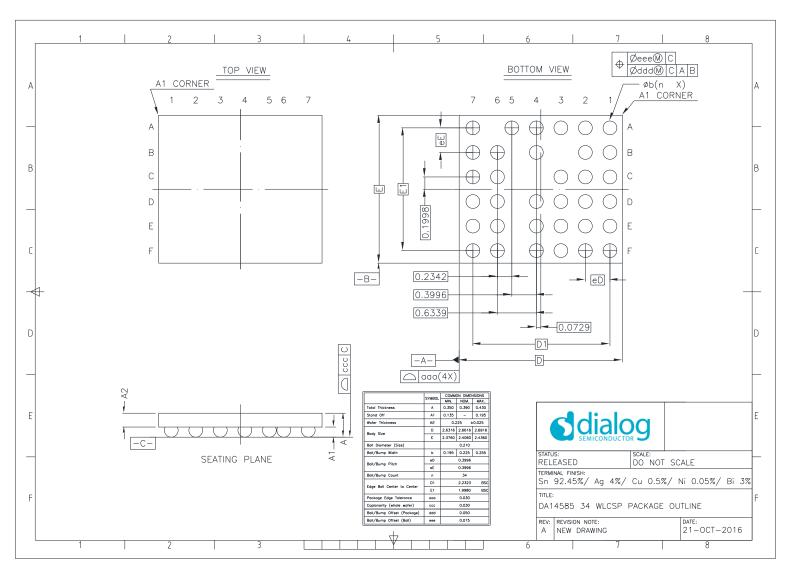

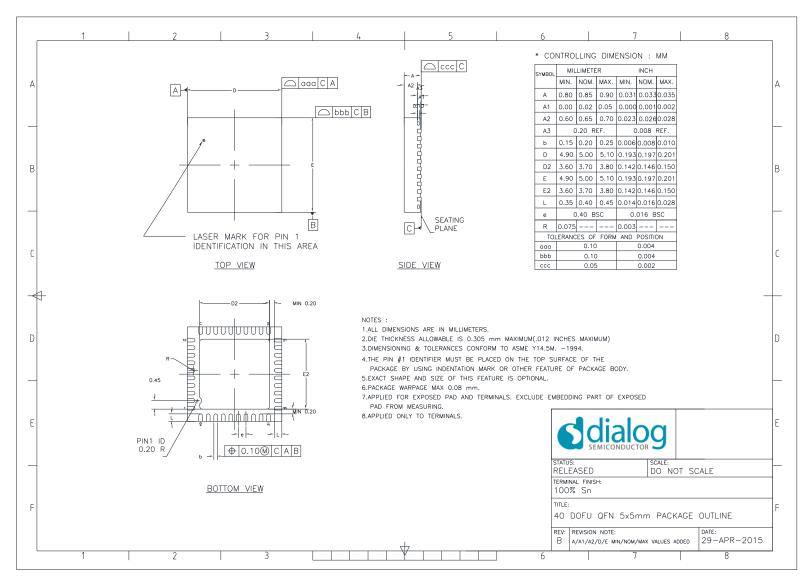

| 30  | Pack   | age information                                                             | 336            |

|     | 30.1   | Moisture sensitivity level (MSL)                                            |                |

|     |        | WLCSP handling                                                              |                |

|     | 30.3   | -                                                                           |                |

|     |        | Package outlines                                                            |                |

|     |        |                                                                             |                |

| Re  | vision | History Error! Bookmarl                                                     | k not defined. |

|     |        |                                                                             |                |

| Fi  | gure   |                                                                             |                |

|     |        |                                                                             | _              |

|     |        | System Diagram                                                              |                |

|     |        | DA14585 Block Diagram                                                       |                |

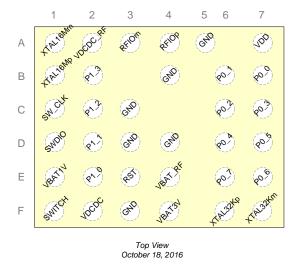

|     |        | WLCSP34 Ball Assignment (Top View)                                          |                |

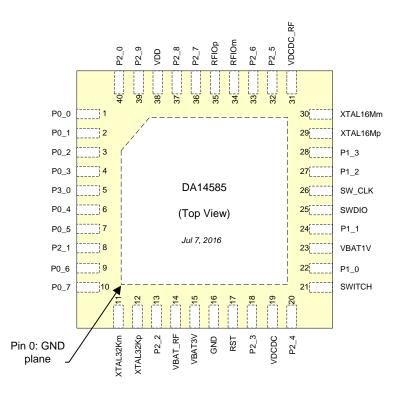

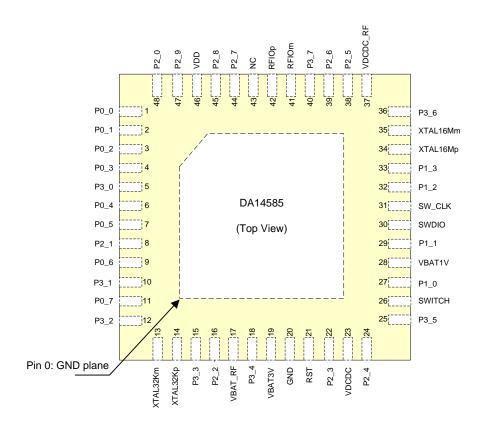

|     |        | QFN40 Pin AssignmentQFN48 Pin Assignment                                    |                |

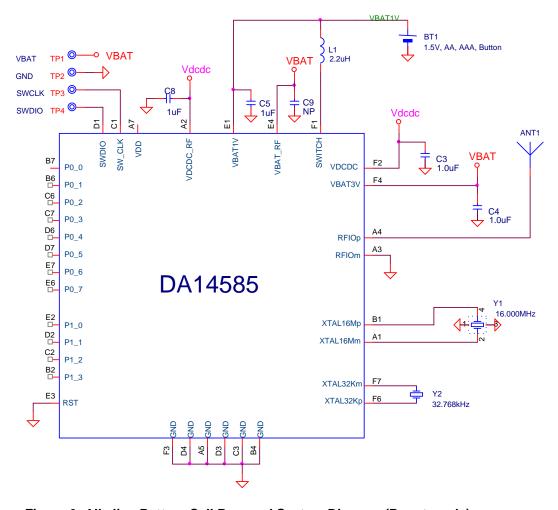

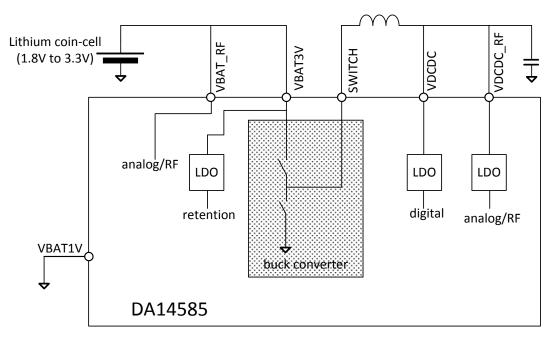

|     |        | Alkaline Battery Cell Powered System Diagram (Boost mode)                   |                |

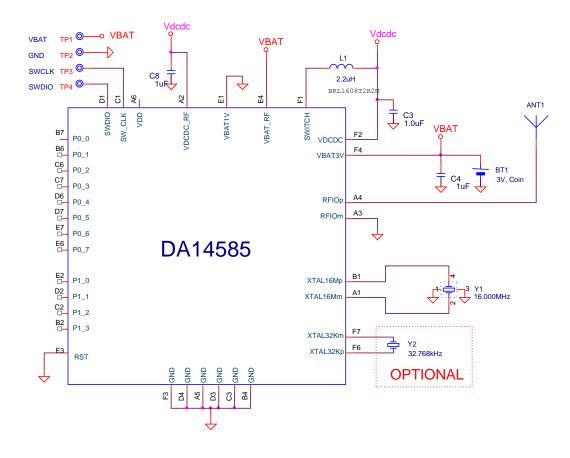

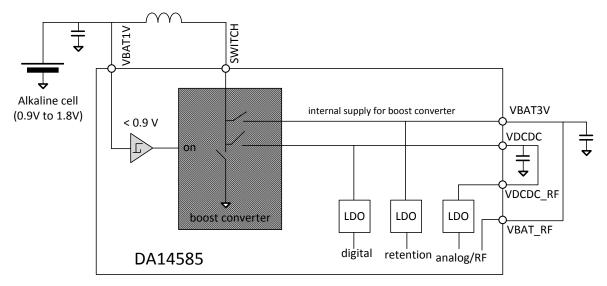

|     |        | Lithium Coin Cell Powered System Diagram (Buck mode)                        |                |

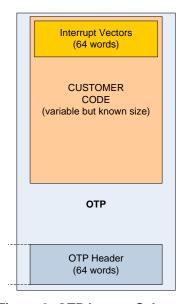

|     |        | OTP Layout Scheme                                                           |                |

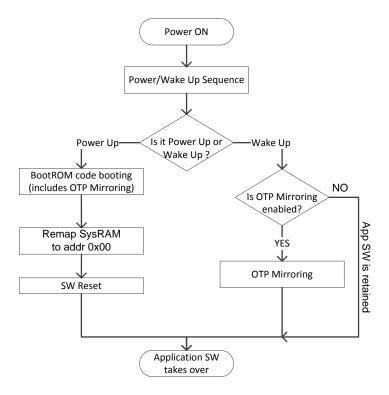

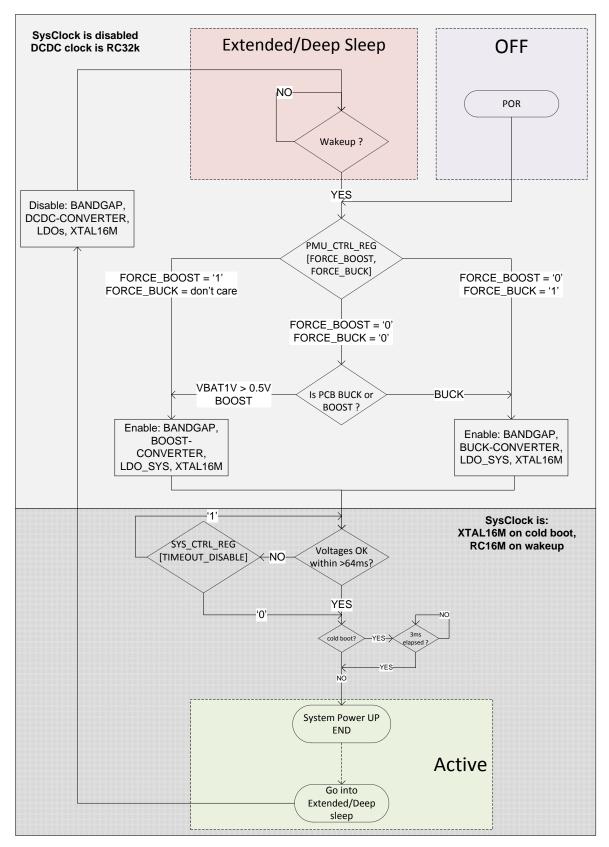

|     |        | General Start-up Flow                                                       |                |

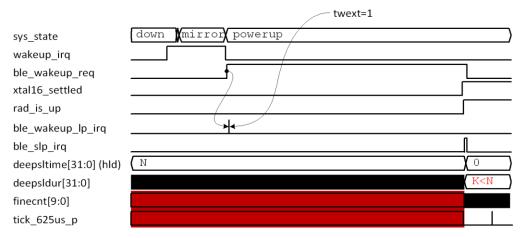

|     |        | : Power/Wake-Up Sequence                                                    |                |

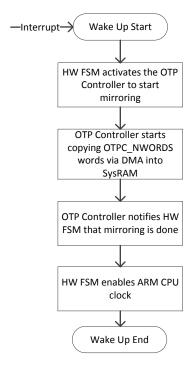

|     |        | : Wake-Up OTP Mirroring                                                     |                |

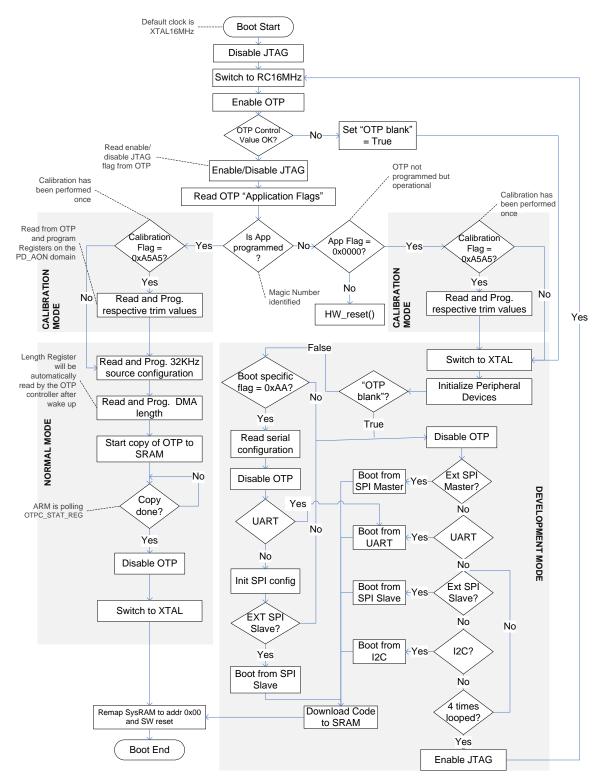

|     |        | : BootROM Sequence                                                          |                |

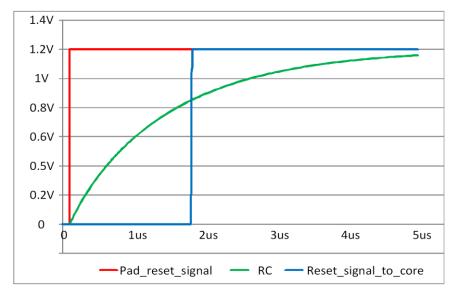

|     |        | : RST Pad Latency                                                           |                |

|     |        | Reset Block Diagram                                                         |                |

| _   |        | : Power-On Reset Timing Diagram                                             |                |

|     |        | : ARM Cortex-M0 Block Diagram                                               |                |

| Fia | ure 17 | : AMBA Bus Architecture and Power Domains                                   | 59             |

|     |        | : Patch Block                                                               |                |

| _   |        | : Memory Controller Block Diagram                                           |                |

|     |        | : Arbitration Scheme                                                        |                |

|     |        | : Crystal Oscillator Circuits                                               |                |

|     |        | : 16 MHz Crystal Oscillator Frequency Trimming                              |                |

|     |        | : Clock Generation Block Diagram                                            |                |

|     |        | : OTP Controller Block Diagram                                              |                |

| _   |        | : OTP Word Layout                                                           |                |

|     |        | : DMA Controller Block Diagram                                              |                |

| Fig | ure 27 | : DMA Channel Diagram                                                       | 76             |

| Fig | ure 28 | : I2C Controller Block Diagram                                              | 78             |

|     |        | : Master/Slave and Transmitter/Receiver Relationships                       |                |

|     |        | : Data Transfer on the I2C Bus                                              |                |

|     |        | : START and STOP Conditions                                                 |                |

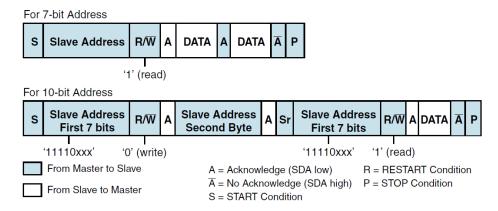

|     |        | : 7-bit Address Format                                                      |                |

| Fig | ure 33 | : 10-bit Address Format                                                     | 82             |

| Fig | ure 34 | : Master-Transmitter Protocol                                               | 83             |

| Fig | ure 35 | : Master-Receiver Protocol                                                  | 83             |

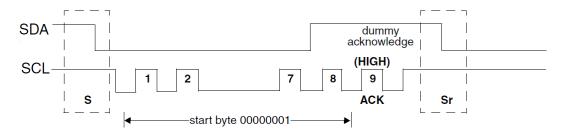

| Fig | ure 36 | : START BYTE Transfer                                                       | 84             |

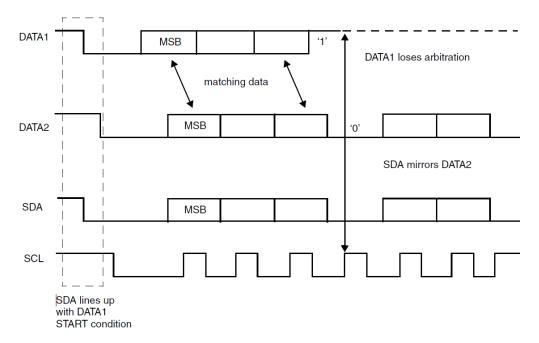

| Fig | ure 37 | : Multiple Master Arbitration                                               | 85             |

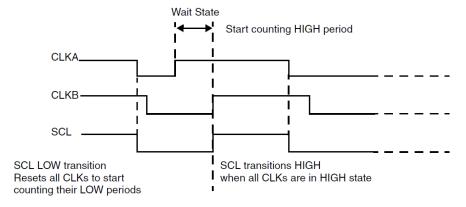

| Fig | ure 38 | : Multiple Master Clock Synchronization                                     | 85             |

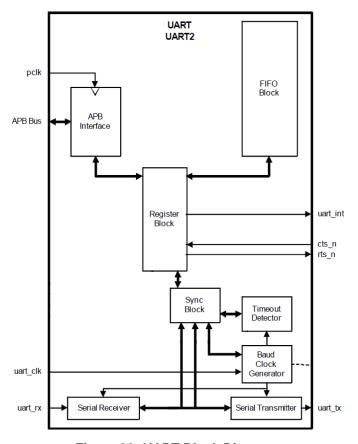

| Fig | ure 39 | : UART Block Diagram                                                        | 90             |

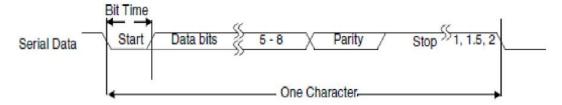

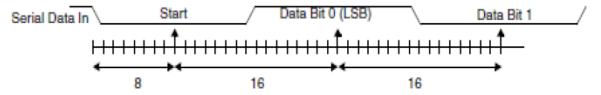

|     |        | : Serial Data Format                                                        |                |

| Fig | ure 41 | : Receiver Serial Data Sampling Points                                      | 91             |

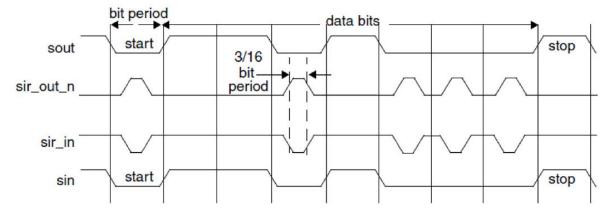

|     |        | : IrDA SIR Data Format                                                      |                |

|     |        | : Flowchart of Interrupt Generation for Programmable THRE Interrupt Mode    |                |

|     |        | : Flowchart of Interrupt Generation When Not in Programmable THRE Interrupt |                |

|     |        | : SPI Block Diagram                                                         |                |

| Fig | ure 46 | : SPI Master/Slave, Mode 0: SPI_POL=0 and SPI_PHA=0                         | 99             |

|     |        |                                                                             |                |

| Da  | tashee | et Revision 3.3                                                             | 15-Oct-2018    |

| Figure 47: | : SPI Master/Slave, Mode 1: SPI_POL=0 and SPI_PHA=1                   | 100  |

|------------|-----------------------------------------------------------------------|------|

| Figure 48: | : SPI Master/Slave, Mode 2: SPI_POL=1 and SPI_PHA=0                   | 100  |

| Figure 49: | : SPI Master/slave, Mode 3: SPI_POL=1 and SPI_PHA=1                   | 100  |

| Figure 50: | SPI Slave Mode Timing (CPOL = 0, CPHA = 0)                            | 101  |

| Figure 51: | : Quadrature Decoder Block Diagram                                    | 102  |

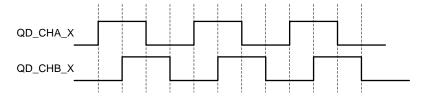

| Figure 52: | : Moving Forward on Axis X                                            | 102  |

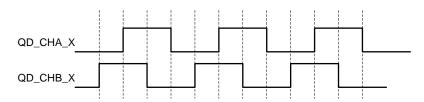

| Figure 53: | : Moving Backwards on Axis X                                          | 103  |

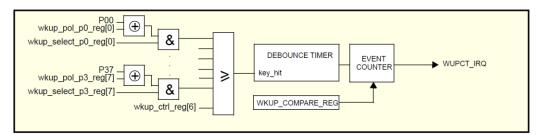

| Figure 54: | : Wake-Up Timer Block Diagram                                         | 104  |

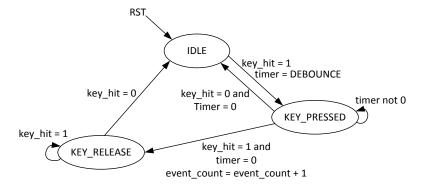

| Figure 55: | Event Counter State Machine for the Wake-Up Interrupt Generator       | 104  |

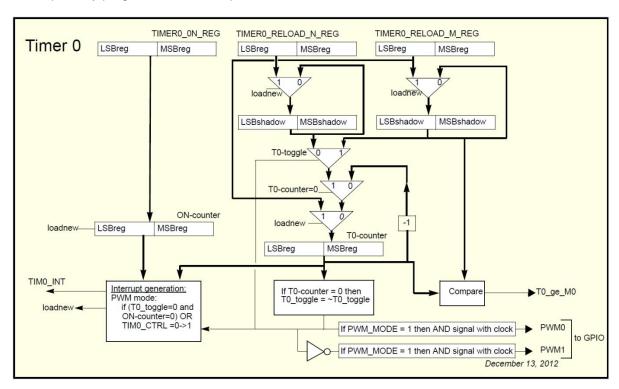

| Figure 56: | : Timer 0 Block Diagram                                               | 105  |

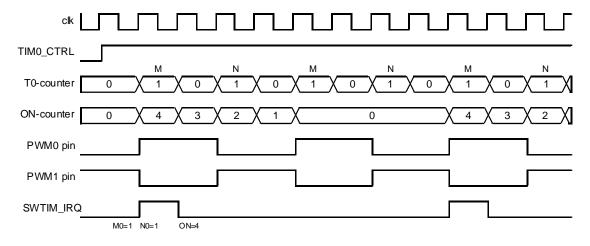

| Figure 57: | : Timer 0 PWM Mode                                                    | 106  |

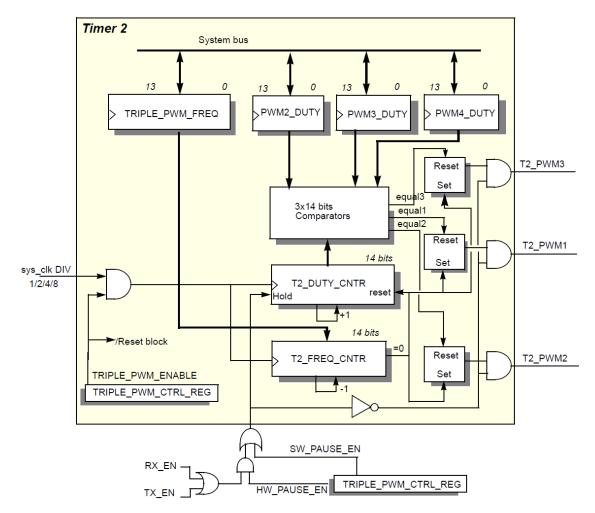

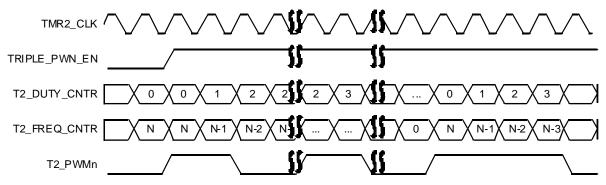

| Figure 58: | : Timer 2 PWM Block Diagram                                           | 108  |

|            | : Timer 2 PWM Timing Diagram                                          |      |

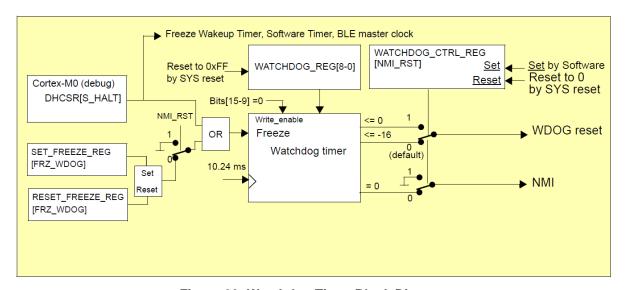

|            | : Watchdog Timer Block Diagram                                        |      |

|            | : Keyboard Controller Block Diagram                                   |      |

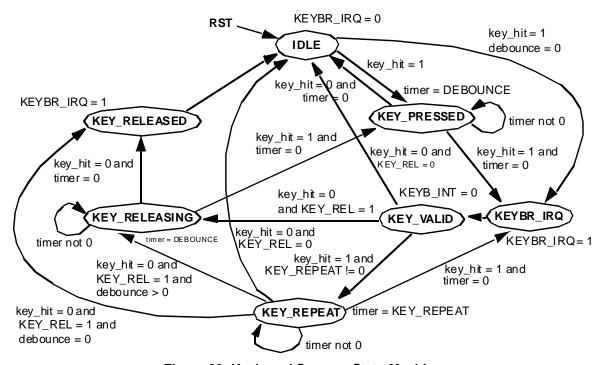

|            | : Keyboard Scanner State Machine                                      |      |

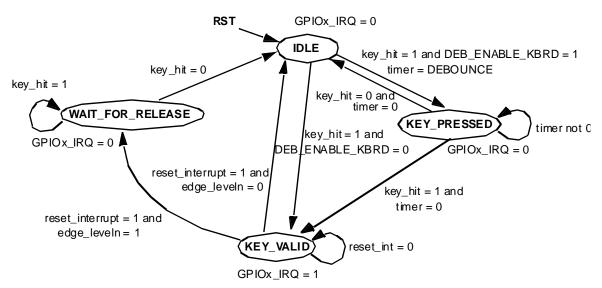

|            | GPIO Interrupt Generator State Machine                                |      |

|            | : Port P0, P1, P2 and P3 with Programmable Pin Assignment             |      |

|            | : Block Diagram of the General Purpose ADC                            |      |

|            | : Audio Unit Block Diagram                                            |      |

|            | : Audio Unit Up/Down Sampler Block Diagram                            |      |

|            | PCM Interface Formats                                                 |      |

|            | : I2S Mode                                                            |      |

|            | : I2S TDM mode (left justified mode)                                  |      |

|            | : IOM format                                                          |      |

|            | PDM Mono/Stereo formats                                               |      |

|            | SRC PDM Input Transfer Function                                       |      |

|            | Block Diagram of the Analog Power Block and Internal Interconnections |      |

|            | Supply Overview, Coin-Cell Application                                |      |

|            | Supply Overview, Alkaline-Cell Application                            |      |

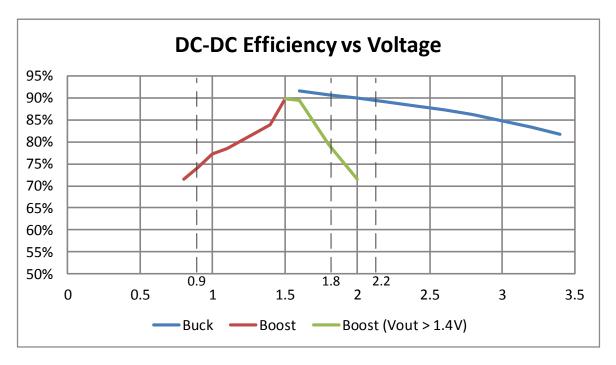

|            | DC-DC Efficiency in Buck/Boost Mode at Various Voltage Levels         |      |

|            | BLE Core Block Diagram                                                |      |

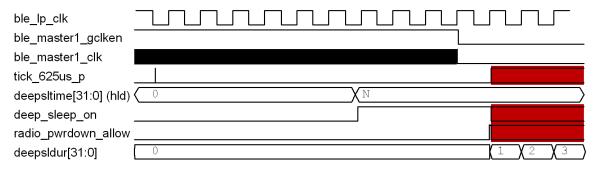

|            | Entering into BLE Deep Sleep mode                                     |      |

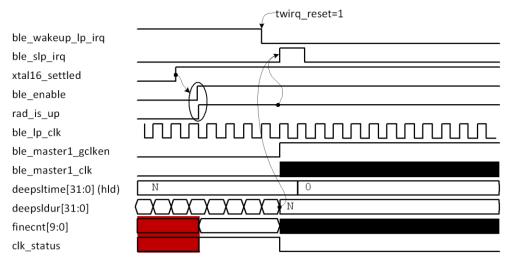

|            | Exit BLE Deep Sleep Mode at Predetermined Time (Zoom In)              |      |

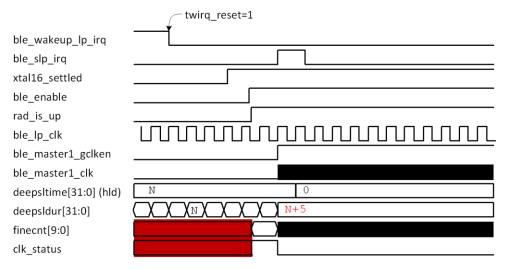

|            | Exit BLE Deep Sleep Mode after Predetermined Time (Zoom In)           |      |

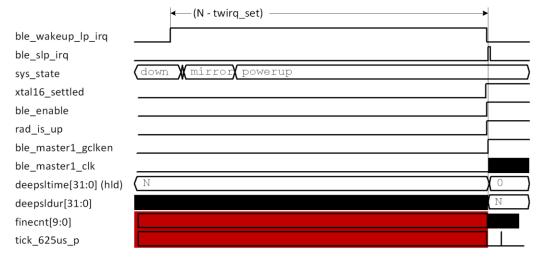

|            | Exit BLE Deep Sleep Mode at Predetermined Time (Zoom Out)             |      |

|            | Exit BLE Deep Sleep Mode Due to External Event                        |      |

|            | Bluetooth Radio block diagram                                         |      |

|            | WLCSP34 Package Outline Drawing                                       |      |

|            | : QFN40 Package Outline Drawing                                       |      |

| r iguio or | e at 1410 Factoring Contact Dialog calco for availability)            |      |

| Tables     |                                                                       |      |

|            | Pin Description                                                       |      |

|            | Absolute Maximum Ratings                                              |      |

|            | Recommended Operating Conditions                                      |      |

|            | OC Characteristics                                                    |      |

|            | iming Characteristics                                                 |      |

|            | 6 MHz Crystal Oscillator - Recommended Operating Conditions           |      |

|            | 6 MHz Crystal Oscillator - Timing Characteristics                     |      |

|            | 2 kHz Crystal Oscillator - Recommended Operating Conditions           |      |

|            | 2 kHz Crystal Oscillator - Timing Characteristics                     |      |

|            | Stable Low Frequency RCX Oscillator - Timing Characteristics          |      |

| Table 11:  | Digital Input/Output - DC Characteristics                             | . 30 |

| Table 12:  | General Purpose ADC - Recommended Operating Conditions                | . 31 |

| 1 able 13: | General Purpose ADC - DC Characteristics                              | . ა1 |

| Datashee   | Revision 3.3 15-Oct-20                                                | 018  |

© 2018 Dialog Semiconductor

| Table 14:                                                                                                                                                                                                                                                                                         | General Purpose ADC - Timing Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 31                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                   | DC-DC Converter - Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | DC-DC Converter - DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Radio - DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Radio - AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | OTP Header                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Development Mode Peripheral Pin Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Development Mode Peripheral Search Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Power Domains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                          |

| Table 23:                                                                                                                                                                                                                                                                                         | Activating Power Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 49                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                   | Power Domain Manipulation When Activating Extended Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Retention Registers and Power Domains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Sleep LDO Recommended Settings across Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Reset Signals and Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Interrupt list                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | ARM Documents List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                          |

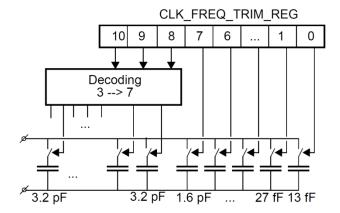

|                                                                                                                                                                                                                                                                                                   | CLK_FREQ_TRIM_REG Decoding 3> 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Generated Clocks Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | DMA Served Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | I2C Definition of Bits in First Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | UART Baud Rate Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Low Power Divisor Latch Register Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | UART Interrupt Priorities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | SPI Timing Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Fixed Assignment of Specific Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                          |

| Table 40:                                                                                                                                                                                                                                                                                         | GPADC Input Channels and Voltage Scale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 119                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                   | GPADC Calibration Procedure for Single-Ended and Differential Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   | Common Mode Adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1・ル                                                                                                                                      |

| T able 43.                                                                                                                                                                                                                                                                                        | PCM_FDIV_REG programming example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 120                                                                                                                                      |