### 1 Description

The AS3824 is a 16 channel high precision LED controller for use in LCD-backlight panels. Dynamic power feedback controls the external power supply to guarantee best efficiency. One high accurate global 10 bit DAC can be used to set the LED current as well as each channel has its own additional 8 bit DAC to boost the dynamic range of LED Backlight systems.

Each channel is equipped with an independent PWM generator which can also be synchronized to an external synchronization signal (VSYNC).

A fast mode supports minimum PWM duty cycle operation which helps to further reduce the energy consumption of modern LED Backlight systems.

The PWM generator clock can be generated internally (DPLL) or an external clock source can be connected to the HSYNC input.

Built-in safety features include thermal shutdown as well as open and short LED detection. The device is programmable via serial interface (SPI).

### 2 Features

- Supports all LED backlight topologies

- » No limit of VLED or ILED, device is not exposed to high voltage/high current

- Optimum power savings through local dimming

- » 16 fully flexible 12 bit PWM generators (period, high time, delay, reverse)

- One global highly accurate 10 bit DAC which sets the LED current (±0.5% accuracy)

- High dynamic range boost function

- » 16 independent 8 bit DACs can be used to boost/ decrease LED current within certain frames

- Global dimming mode option

- » AS3824E/E1 are pre-programmed as external PWM mode (DPWM mode), V<sub>SYNC</sub> pin is used as PWM input. AS3824A/A1 are pre-programmed as SPI mode

- VSYNC and HSYNC inputs, as well as integrated digital PLL for synchronization with TV frame

- Lowest BOM

- » Due to 2 pin concept of the output channel: no HV protection, no cascade FETs

- Feedback function is compatible to every DC-DC architecture and configurable via SPI

- Short/OPEN LED detection, temperature shutdown, register lock/unlock, SPI transfer checksum

### 3 Applications

- HD TVs

- UHD TVs

- LCD Monitors

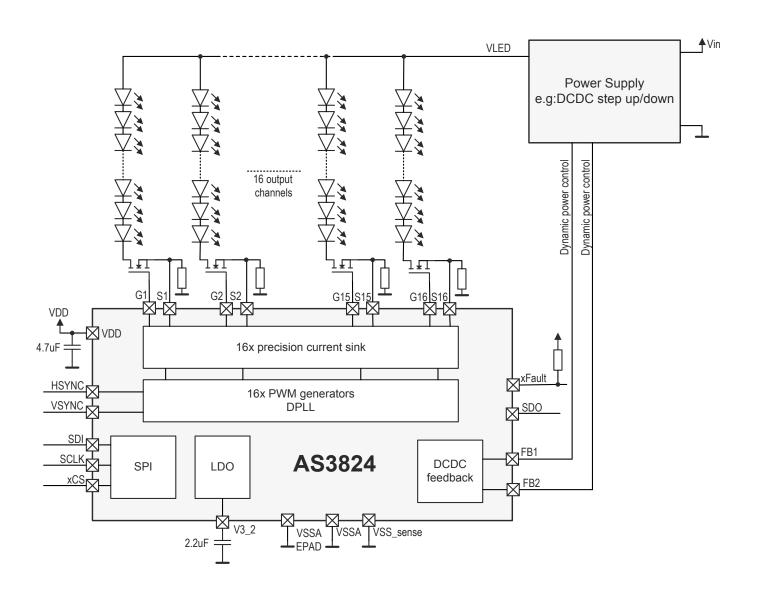

Figure 3.1 : AS3824 Typical Application

## **4 Pinout Description**

### AS3824

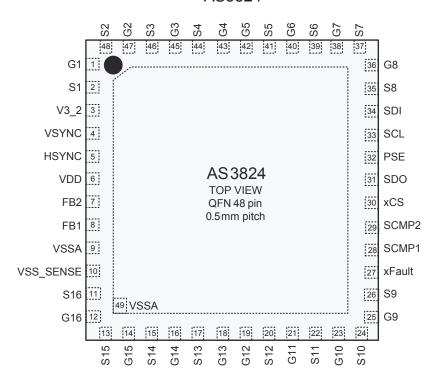

Figure 4.1 : Pin Diagram of AS3824 (Top View)

| Pin Number | Pin Name  | Туре  | Pin Description                                               | If Not Used    |

|------------|-----------|-------|---------------------------------------------------------------|----------------|

| 1          | G1        | A_I/O | Connect to gate of external transistor                        | Connect to S1  |

| 2          | S1        | A_I/O | Connect to source of external transistor                      | Connect to G1  |

| 3          | V3_2      | Р     | Digital supply output. Connect 2.2uF capacitor to GND         |                |

| 4          | VSYNC     | DI_PD | Vertical sync frequency. PWM generator reset                  | Leave open     |

| 5          | HSYNC     | DI_PD | Clock input for PWM generators                                | Leave open     |

| 6          | VDD       | Р     | Supply Voltage input<br>Connect 4.7uF bypass capacitor to GND |                |

| 7          | FB2       | A_I/O | Power supply feedback output 2                                | Leave open     |

| 8          | FB1       | A_I/O | Power supply feedback output 1                                | Leave open     |

| 9          | VSSA      | Р     | GND                                                           |                |

| 10         | VSS_SENSE | Р     | GND                                                           |                |

| 11         | S16       | A_I/O | Connect to source of external transistor                      | Connect to G16 |

Product Summary Rev. 1.0 06-Mar-2020

## 4 Pinout Description (cont'd)

| Pin Number | Pin Name | Туре  | Pin Description                                  | If Not Used    |

|------------|----------|-------|--------------------------------------------------|----------------|

| 12         | G16      | A_I/O | Connect to gate of external transistor           | Connect to S16 |

| 13         | S15      | A_I/O | Connect to source of external transistor         | Connect to G15 |

| 14         | G15      | A_I/O | Connect to gate of external transistor           | Connect to S15 |

| 15         | S14      | A_I/O | Connect to source of external transistor         | Connect to G14 |

| 16         | G14      | A I/O | Connect to gate of external transistor           | Connect to S14 |

| 17         | S13      | A I/O | Connect to source of external transistor         | Connect to G13 |

| 18         | G13      | A I/O | Connect to gate of external transistor           | Connect to S13 |

| 19         | G12      | A I/O | Connect to gate of external transistor           | Connect to S12 |

| 20         | S12      | A I/O | Connect to source of external transistor         | Connect to G12 |

| 21         | G11      | A I/O | Connect to gate of external transistor           | Connect to S11 |

| 22         | S11      | A I/O | Connect to source of external transistor         | Connect to G11 |

| 23         | G10      | A I/O | Connect to gate of external transistor           | Connect to S10 |

| 24         | S10      | A I/O | Connect to source of external transistor         | Connect to G10 |

| 25         | G9       | A I/O | Connect to gate of external transistor           | Connect to S9  |

| 26         | S9       | A I/O | Connect to source of external transistor         | Connect to G9  |

| 27         | xFAULT   | DO_OD | Open drain fault output, connect pull-up to V3_2 | Leave open     |

| 28         | SCMP1    | Al    | Input of short comparator 1                      | Connect to VSS |

| 29         | SCMP2    | Al    | Input of short comparators 2                     | Connect to VSS |

| 30         | xCS      | DI_PU | SPI interface chip select                        | Leave open     |

| 31         | SDO      | DO    | SPI interface data output. Tristate output       | Leave open     |

| 32         | PSE      | DI    | Phase Shift enable                               | Connect to VSS |

| 33         | SCL      | DI_PD | SPI interface clock                              | Leave open     |

| 34         | SDI      | DI_PD | SPI interface data input                         | Leave open     |

| 35         | S8       | A I/O | Connect to source of external transistor         | Connect to G8  |

| 36         | G8       | A I/O | Connect to gate of external transistor           | Connect to S8  |

| 37         | S7       | A I/O | Connect to source of external transistor         | Connect to G7  |

| 38         | G7       | A I/O | Connect to gate of external transistor           | Connect to S7  |

| 39         | S6       | A I/O | Connect to source of external transistor         | Connect to G6  |

| 40         | G6       | A I/O | Connect to gate of external transistor           | Connect to S6  |

## 4 Pinout Description (cont'd)

| Pin Number | Pin Name | Туре  | Pin Description                          | If Not Used   |

|------------|----------|-------|------------------------------------------|---------------|

| 41         | S5       | A I/O | Connect to source of external transistor | Connect to G5 |

| 42         | G5       | A I/O | Connect to gate of external transistor   | Connect to S5 |

| 43         | G4       | A I/O | Connect to gate of external transistor   | Connect to S4 |

| 44         | S4       | A I/O | Connect to source of external transistor | Connect to G4 |

| 45         | G3       | A I/O | Connect to gate of external transistor   | Connect to S3 |

| 46         | S3       | A I/O | Connect to source of external transistor | Connect to G3 |

| 47         | G2       | A I/O | Connect to gate of external transistor   | Connect to S2 |

| 48         | S2       | A I/O | Connect to source of external transistor | Connect to G2 |

| EP         | VSSA     | Р     | Exposed PAD. Connect to VSSP             |               |

**Note 1.** If an output channel "X" is not used, connect unused pins Gx and Sx together.

A\_I/O: Analog pinP: Power pinDO: Digital Output

DO\_OD: Digital Output Open Drain

**DI:** Digital Input

**DI\_PU:** Digital Input with Pull Up resistor **DI\_PD:** Digital Input with Pull Down resistor

### **5 Absolute Maximum Ratings**

Absolute maximum ratings are the parameter values or ranges which can cause permanent damage if exceeded. For maximum safe operating conditions, refer to the Electrical Characteristics section.

| Parameter                                 | Symbol                                | Conditions                                                                                                                                                                                                                                                                                       | Min  | Max | Unit |  |

|-------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|--|

| Electrical Parameters                     |                                       |                                                                                                                                                                                                                                                                                                  |      |     |      |  |

| Supply Voltage to Ground                  | V <sub>DDMAX</sub> / V <sub>GND</sub> | Applicable for pin VDD                                                                                                                                                                                                                                                                           | -0.3 | 7   | V    |  |

| Maximum Voltage Analog pins               | V <sub>ANAMAX</sub>                   | Applicable for pins: FB1, FB2, G1-<br>G16, S1-S16, VSYNC, HSYNC                                                                                                                                                                                                                                  | -0.3 | 7   | V    |  |

| Maximum Voltage Digital pins              | $V_{DIGMAX}$                          | Applicable for pins: V3_2, SDI, SDO, SCL, xCS, SCMP1, SCMP2, xFAULT, PSE                                                                                                                                                                                                                         | -0.3 | 5   | V    |  |

| Input Current (latch-up immunity)         | I <sub>SCR</sub>                      | JEDEC JESD78D Nov 2011                                                                                                                                                                                                                                                                           | ±1   | 00  | mA   |  |

| Electrostatic Discharge                   |                                       |                                                                                                                                                                                                                                                                                                  |      |     |      |  |

| Electrostatic Discharge HBM               | ESD <sub>HBM</sub>                    | JS-001-2012                                                                                                                                                                                                                                                                                      | ±20  | 000 | V    |  |

| Electrostatic Discharge CDM               | ESD <sub>CDM</sub>                    | JEDEC JESD22-C101F Oct 2013                                                                                                                                                                                                                                                                      | ±500 |     | V    |  |

| Electrostatic Discharge MM                | ESD <sub>MM</sub>                     | JESD22-A115C                                                                                                                                                                                                                                                                                     | ±200 |     | V    |  |

| Temperature Ranges and Storage Conditions |                                       |                                                                                                                                                                                                                                                                                                  |      |     |      |  |

| Junction to Ambient Thermal Resistance    | R <sub>THJA</sub>                     | R <sub>THJA</sub> typical 35°C/W                                                                                                                                                                                                                                                                 |      |     | °C/W |  |

| Operating Junction Temperature            | T <sub>J</sub>                        |                                                                                                                                                                                                                                                                                                  | -20  | 115 | °C   |  |

| Storage Temperature Range                 | T <sub>STRG</sub>                     |                                                                                                                                                                                                                                                                                                  | -55  | 150 | °C   |  |

| Package Body Temperature                  | T <sub>BODY</sub>                     | IPC/JEDEC J-STD-020 The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices." The lead finish for Pb-free leaded packages is "Matte Tin" (100% Sn) |      | 260 | °C   |  |

| Relative Humidity (non-condensing)        | RH <sub>NC</sub>                      |                                                                                                                                                                                                                                                                                                  | 5    | 85  | %    |  |

| Moisture Sensitivity Level                | MSL                                   | Maximum floor life time of 168h                                                                                                                                                                                                                                                                  | 3    |     |      |  |

**Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, so functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

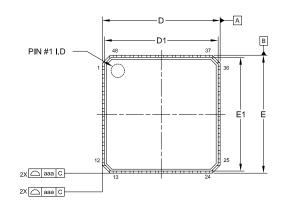

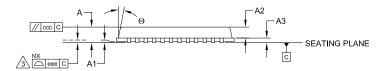

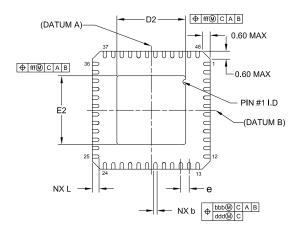

## **6 Physical Dimensions**

| REF. | MIN      | NOM      | MAX  |  |  |

|------|----------|----------|------|--|--|

| A    | 0.80     | 0.90     | 1.00 |  |  |

| A1   | 0        | 0.02     | 0.05 |  |  |

| A2   | -        | 0.65     | 1.00 |  |  |

| A3   |          | 0.20 REF |      |  |  |

| L    | 0.35     | 0.40     | 0.45 |  |  |

| Θ    | 0°       | -        | 14°  |  |  |

| b    | 0.18     | 0.25     | 0.30 |  |  |

| D    |          | 7.00 BSC |      |  |  |

| E    | 7.00 BSC |          |      |  |  |

| е    | 0.50 BSC |          |      |  |  |

| D2   | 4.00     | 4.10     | 4.20 |  |  |

| E2   | 4.00     | 4.10     | 4.20 |  |  |

| D1   | -        | 6.75 BSC | -    |  |  |

| E1   |          | 6.75 BSC | -    |  |  |

| aaa  | -        | 0.15     | -    |  |  |

| bbb  | -        | 0.10     | -    |  |  |

| ccc  | -        | 0.10     | -    |  |  |

| ddd  | -        | 0.05     | -    |  |  |

| eee  | -        | 0.08     | -    |  |  |

| fff  | -        | 0.10     | -    |  |  |

| N    | 48       |          |      |  |  |

#### NOTE:

- 1. DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES)

- OPLANARITY APPLIES TO THE EXPOSED HEAT SLUG AS WELL AS THE TERMINAL.

- 4. RADIUS ON TERMINAL IS OPTIONAL.

- 5. N IS THE TOTAL NUMBER OF TERMINALS.

Figure 6.1 : QFN-48 package outline drawing

## 7 Ordering Information

| Part Number | Ordering Code | Package    | Description              |

|-------------|---------------|------------|--------------------------|

| AS3824A1    | AS3824A1-ZQFT | 48-Pin QFN | Tape & Reel <sup>1</sup> |

| AS3824E1    | AS3824E1-ZQFT | 48-Pin QFN | Tape & Reel <sup>1</sup> |

**Note 1.** Tape & Reel packing quantity is 4,000/reel. Minimum packing quantity is 4,000.

#### **Disclaimer**

Unless otherwise agreed in writing, the Dialog Semiconductor products (and any associated software) referred to in this document are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of a Dialog Semiconductor product (or associated software) can reasonably be expected to result in personal injury, death or severe property or environmental damage. Dialog Semiconductor and its suppliers accept no liability for inclusion and/or use of Dialog Semiconductor products (and any associated software) in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, express or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including, without limitation, the specification and the design of the related semiconductor products, software and applications. Notwithstanding the foregoing, for any automotive grade version of the device, Dialog Semiconductor reserves the right to change the information published in this document, including, without limitation, the specification and the design of the related semiconductor products, software and applications, in accordance with its standard automotive change notification process.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document is subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, available on the company website (www.dialog-semiconductor.com) unless otherwise stated.

Dialog, Dialog Semiconductor and the Dialog logo are trademarks of Dialog Semiconductor Plc or its subsidiaries. All other product or service names and marks are the property of their respective owners.

© 2020 Dialog Semiconductor. All rights reserved.

### **RoHS Compliance**

Dialog Semiconductor's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

### **Contacting Dialog Semiconductor**

### United Kingdom (Headquarters)

Dialog Semiconductor (UK) LTD Phone: +44 1793 757700

#### Germany

Dialog Semiconductor GmbH Phone: +49 7021 805-0

### The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 8822

#### Email

info\_pcbg@diasemi.com

### North America

Dialog Semiconductor Inc. Phone: +1 408 845 8500

#### Japar

Dialog Semiconductor K. K. Phone: +81 3 5769 5100

#### Taiwar

Dialog Semiconductor Taiwan Phone: +886 281 786 222

### Web site:

www.dialog-semiconductor.com

### Hong Kong

Dialog Semiconductor Hong Kong Phone: +852 2607 4271

#### Korea

Dialog Semiconductor Korea Phone: +82 2 3469 8200

### China (Shenzhen)

Dialog Semiconductor China Phone: +86 755 2981 3669

#### China (Shanghai)

Dialog Semiconductor China Phone: +86 21 5424 9058

Product Summary Rev. 1.0 06-Mar-2020

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Dialog Semiconductor:

AS3824A1-ZQFT AS3824E1-ZQFT