## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# 16

# M16C/64 Group

Hardware Manual RENESAS MCU M16C FAMILY / M16C/60 SERIES

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Renesas Electronics www.renesas.com

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

You should not use the products or the technology described in this document for the purpose of military

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below: (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

## General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

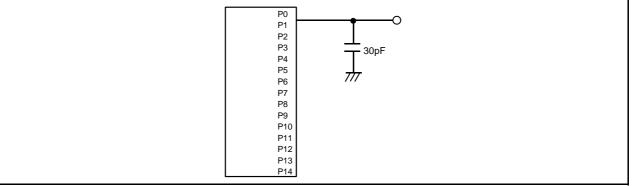

1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

- In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do

not access these addresses; the correct operation of LSI is not guaranteed if they are

accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

## HOW TO USE THIS MANUAL

## 1. Purpose and Target Readers

This manual is designed to provide the user with an understanding of the hardware functions and electrical characteristics of the MCU. It is intended for users designing application systems incorporating the MCU. A basic knowledge of electric circuits, logical circuits, and MCUs is necessary in order to use this manual. The manual comprises an overview of the product; descriptions of the CPU, system control functions, peripheral functions, and electrical characteristics; and usage notes.

Particular attention should be paid to the precautionary notes when using the manual. These notes occur within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. Refer to the text of the manual for details.

The following documents apply to the M16C/64 Group. Make sure to refer to the latest versions of these documents. The newest versions of the documents listed may be obtained from the Renesas Technology Web site.

| Document Type    | Description                                         | Document Title     | Document No.  |

|------------------|-----------------------------------------------------|--------------------|---------------|

| Datasheet        | Hardware overview and electrical characteristics    | M16C/64 Group      | REJ03B0216    |

|                  |                                                     | Datasheet          |               |

| Hardware manual  | Hardware specifications (pin assignments,           | M16C/64 Group      | This hardware |

|                  | memory maps, peripheral function                    | Hardware Manual    | manual        |

|                  | specifications, electrical characteristics, timing  |                    |               |

|                  | charts) and operation description                   |                    |               |

|                  | Note: Refer to the application notes for details on |                    |               |

|                  | using peripheral functions.                         |                    |               |

| Software Manual  | Descriptions of Instruction set                     | M16C/60, M16C/     | REJ09B0137    |

|                  |                                                     | 20, M16C/Tiny      |               |

|                  |                                                     | Series Software    |               |

|                  |                                                     | Manual             |               |

| Application note | Information on using peripheral functions and       | Available from Ren | esas          |

|                  | application examples                                | Technology Web si  | te.           |

|                  | Sample programs                                     |                    |               |

|                  | Information on writing programs in assembly         |                    |               |

|                  | language and C                                      |                    |               |

| Renesas          | Product specifications, updates on documents,       |                    |               |

| technical update | etc.                                                |                    |               |

## 2. Notation of Numbers and Symbols

The notation conventions for register names, bit names, numbers, and symbols used in this manual are described below.

(1) Register Names, Bit Names, and Pin Names

Registers, bits, and pins are referred to in the text by symbols. The symbol is accompanied by the word "register," "bit," or "pin" to distinguish the three categories.

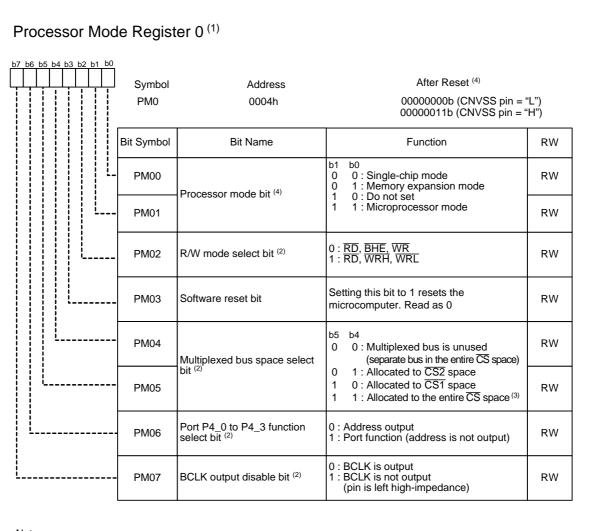

Examples the PM03 bit in the PM0 register

P3\_5 pin, VCC pin

(2) Notation of Numbers

The indication "b" is appended to numeric values given in binary format. However, nothing is appended to the values of single bits. The indication "h" is appended to numeric values given in hexadecimal format. Nothing is appended to numeric values given in decimal format.

Examples Binary: 11b Hexadecimal: EFA0h Decimal: 1234

## 3. Register Notation

The symbols and terms used in register diagrams are described below.

| XXX Register |            | *1                                             |                                                  |    |             |

|--------------|------------|------------------------------------------------|--------------------------------------------------|----|-------------|

|              |            | Symbol<br>XXX                                  | Address After Reset<br>XXX 00h                   |    |             |

|              | Bit Symbol | Bit Name                                       | Function                                         | RW | <u>,</u> *2 |

|              | XXX0       | XXX bits                                       | b1 b0<br>1 0: XXX<br>0 1: XXX                    | RW |             |

|              | XXX1       |                                                | 1 0: Do not set.<br>1 1: XXX                     | RW |             |

|              | (b2)       | Nothing is assigned. I<br>When read, the conte | f necessary, set to 0.<br>nt is undefined.       | _  | — *3        |

|              | (b3)       | Reserved bits                                  | Set to 0.                                        | RW | *4          |

|              | XXX4       | XXX bits                                       | Function varies according to the operating mode. | RW |             |

|              | XXX5       |                                                |                                                  | wo |             |

|              | XXX6       |                                                |                                                  | RW |             |

| i            | XXX7       | XXX bit                                        | 0: XXX<br>1: XXX                                 | RO |             |

\*1

Blank: Set to 0 or 1 according to the application.

0: Set to 0.

1: Set to 1.

X: Nothing is assigned.

\*2

RW: Read and write. RO: Read only. WO: Write only.

-: Nothing is assigned.

\*3

Reserved bit

Reserved bit. Set to specified value.

\*4

Nothing is assigned

Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.

• Do not set to a value

Operation is not guaranteed when a value is set.

• Function varies according to the operating mode.

The function of the bit varies with the peripheral function mode. Refer to the register diagram for information on the individual modes.

## 4. List of Abbreviations and Acronyms

| Abbreviation | Full Form                                    |

|--------------|----------------------------------------------|

| ACIA         | Asynchronous Communication Interface Adapter |

| bps          | bits per second                              |

| CRC          | Cyclic Redundancy Check                      |

| DMA          | Direct Memory Access                         |

| DMAC         | Direct Memory Access Controller              |

| GSM          | Global System for Mobile Communications      |

| Hi-Z         | High Impedance                               |

| IEBus        | Inter Equipment bus                          |

| I/O          | Input/Output                                 |

| IrDA         | Infrared Data Association                    |

| LSB          | Least Significant Bit                        |

| MSB          | Most Significant Bit                         |

| NC           | Non-Connection                               |

| PLL          | Phase Locked Loop                            |

| PWM          | Pulse Width Modulation                       |

| SIM          | Subscriber Identity Module                   |

| UART         | Universal Asynchronous Receiver/Transmitter  |

| VCO          | Voltage Controlled Oscillator                |

All trademarks and registered trademarks are the property of their respective owners.

IEBus is a registered trademark of NEC Electronics Corporation.

## **Table of Contents**

| SF | R Page | Reference                                                  | B-1 |

|----|--------|------------------------------------------------------------|-----|

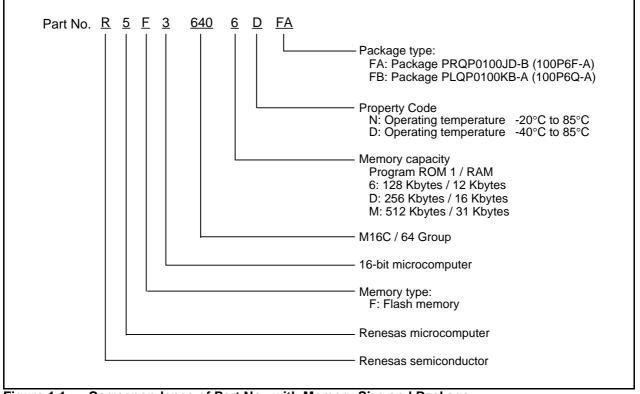

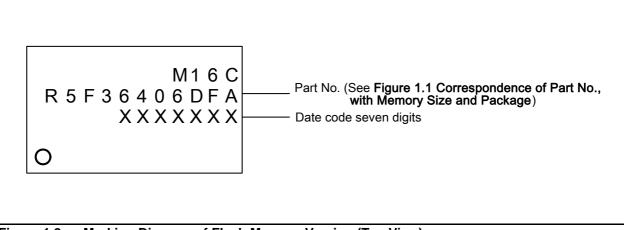

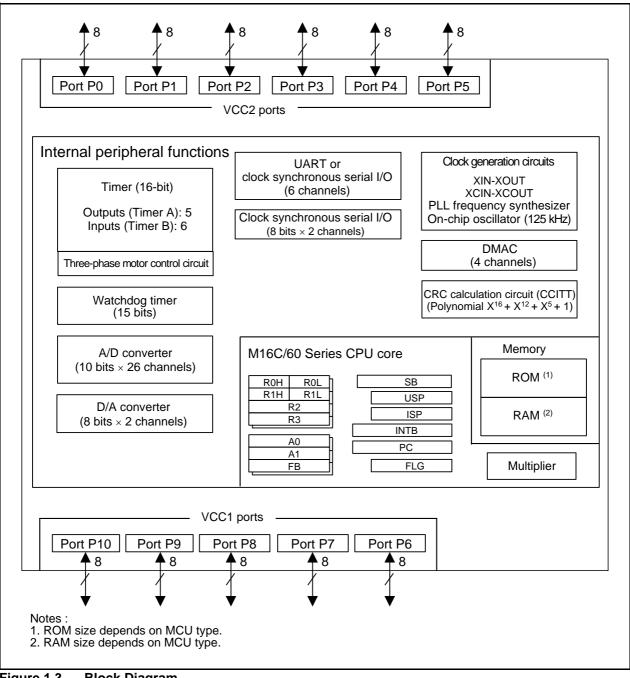

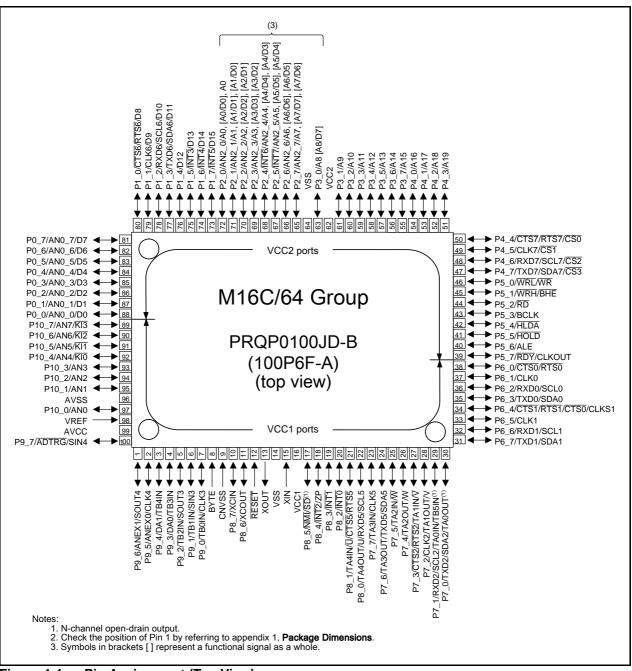

| 1. | Ove    | view                                                       | 1   |

|    | 1.1    | Features                                                   | 1   |

|    | 1.1.1  | Applications                                               | 1   |

|    | 1.2    | Specifications                                             | 2   |

|    | 1.3    | Product List                                               | 4   |

|    | 1.4    | Block Diagram                                              | 6   |

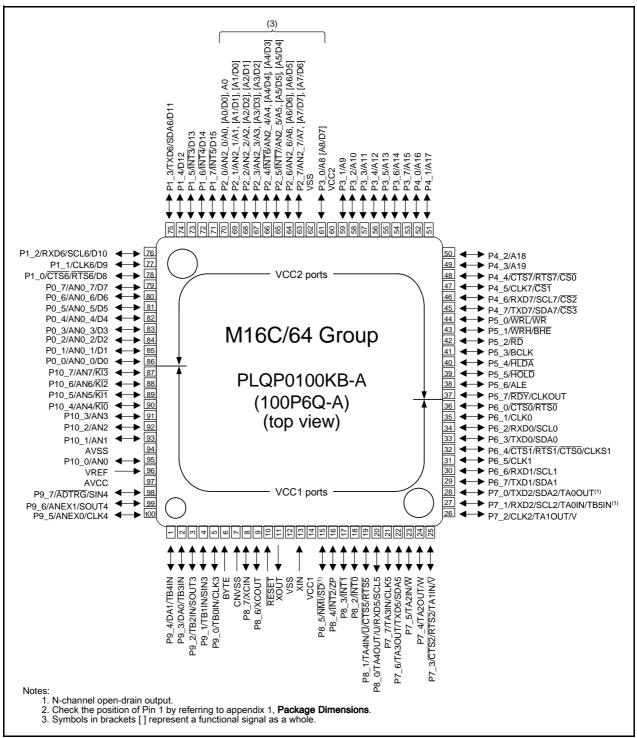

|    | 1.5    | Pin Assignments                                            | 7   |

|    | 1.6    | Pin Functions                                              | 11  |

| 2. | Cen    | ral Processing Unit (CPU)                                  | 14  |

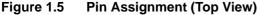

|    | 2.1    | Data Registers (R0, R1, R2 and R3)                         |     |

|    | 2.2    | Address Registers (A0 and A1)                              | 15  |

|    | 2.3    | Frame Base Registers (FB)                                  |     |

|    | 2.4    | Interrupt Table Register (INTB)                            |     |

|    | 2.5    | Program Counter (PC)                                       |     |

|    | 2.6    | User Stack Pointer (USP) and Interrupt Stack Pointer (ISP) | 15  |

|    | 2.7    | Static Base Register (SB)                                  | 15  |

|    | 2.8    | Flag Register (FLG)                                        | 15  |

|    | 2.8.   | Carry Flag (C Flag)                                        | 15  |

|    | 2.8.2  | Debug Flag (D Flag)                                        | 15  |

|    | 2.8.3  | Zero Flag (Z Flag)                                         | 15  |

|    | 2.8.4  | Sign Flag (S Flag)                                         | 15  |

|    | 2.8.   | Register Bank Select Flag (B Flag)                         | 15  |

|    | 2.8.6  | Overflow Flag (O Flag)                                     | 15  |

|    | 2.8.7  | Interrupt Enable Flag (I Flag)                             | 15  |

|    | 2.8.8  | Stack Pointer Select Flag (U Flag)                         |     |

|    | 2.8.9  | Processor Interrupt Priority Level (IPL)                   |     |

|    | 2.8.   | 0 Reserved Space                                           |     |

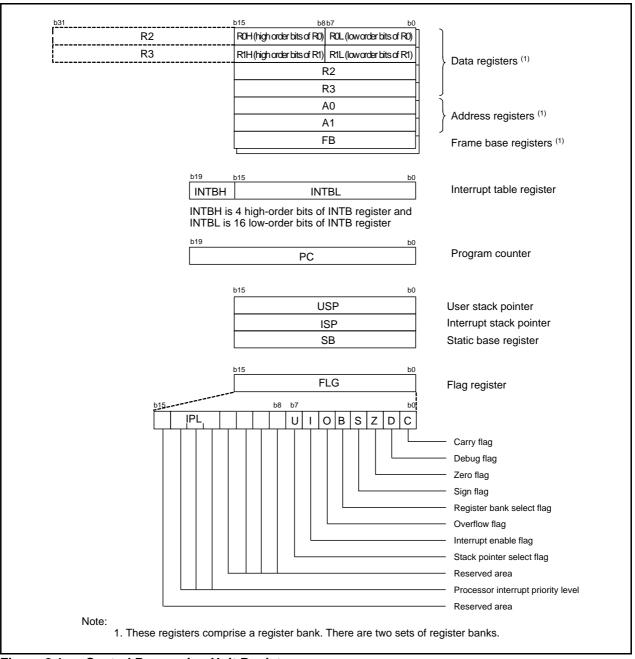

| 3. | Men   | nory | /                                         |    |

|----|-------|------|-------------------------------------------|----|

| 4. | Spe   | cial | Function Registers (SFRs)                 |    |

| 5. | Res   | et   |                                           |    |

|    | 5.1   | Har  | dware Reset 1                             | 32 |

|    | 5.1.  | 1    | Reset on a Stable Supply Voltage          |    |

|    | 5.1.2 | 2    | Power-on Reset                            |    |

|    | 5.2   | Bro  | wn-out Reset                              |    |

|    | 5.3   | Sof  | tware Reset                               |    |

|    | 5.4   | Wat  | chdog Timer Reset                         | 35 |

|    | 5.5   | Osc  | illation Stop Detection Reset             |    |

|    | 5.6   | Inte | rnal Space                                |    |

| 6. | Volta | age  | Detection Circuit                         |    |

|    | 6.1   | Bro  | wn-out Reset                              | 41 |

|    | 6.2   | Low  | Voltage Detection Interrupt               |    |

|    | 6.3   | Lim  | itations on Exiting Stop Mode             |    |

|    | 6.4   | Lim  | itations on Exiting Wait Mode             |    |

|    | 6.5   | Col  | d Start-up / Warm Start-up Discrimination | 45 |

| 7. | Proc  | cess | sor Mode                                  | 47 |

|    | 7.1   | Тур  | es of Processor Mode                      |    |

|    | 7.2   | Set  | ting Processor Modes                      |    |

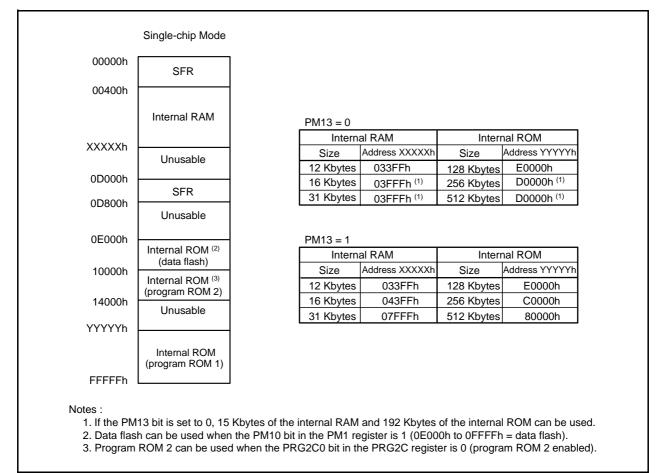

|    | 7.3   | Inte | rnal Memory                               | 51 |

| 8. | Bus   |      |                                           | 53 |

|    | 8.1   | Bus  | Mode                                      | 53 |

|    | 8.1.  | 1    | Separate Bus                              |    |

|    | 8.1.2 | 2    | Multiplexed Bus                           |    |

|    | 8.2   | Bus  | Control                                   | 54 |

|    | 8.2.  | 1    | Address Bus                               | 54 |

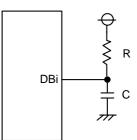

|    | 8.2.2 | 2    | Data Bus                                  | 54 |

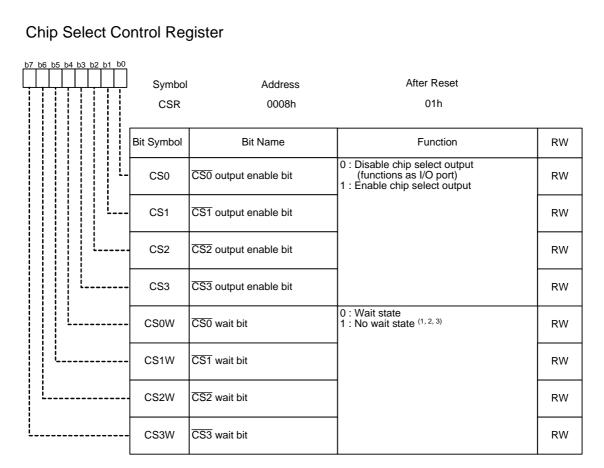

|    | 8.2.3 | 3    | Chip Select Signal                        | 54 |

|    | 8.2.4 | 4    | Read and Write Signals                    | 57 |

|    | 8.2.  | 5    | ALE Signal                                | 57 |

|    | 8.2.6 | 6    | RDY Signal                                |    |

| 8.2     | 2.7    | HOLD Signal                                                                        | 59  |

|---------|--------|------------------------------------------------------------------------------------|-----|

| 8.2     | 2.8    | BCLK Output                                                                        | 59  |

| 8.2     | 2.9    | External Bus Status When Internal Area IS Accessed                                 | 61  |

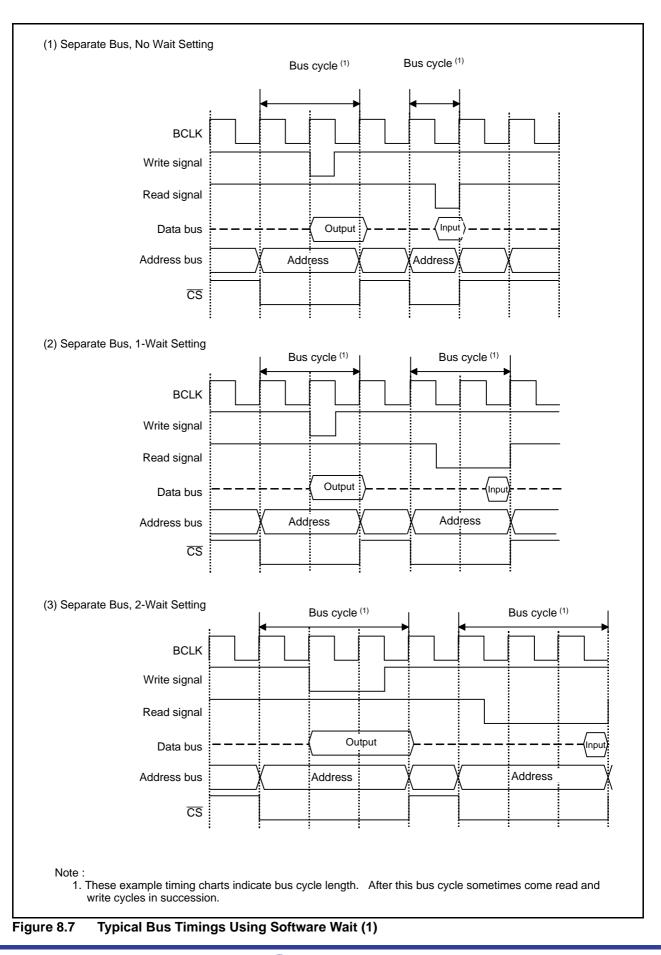

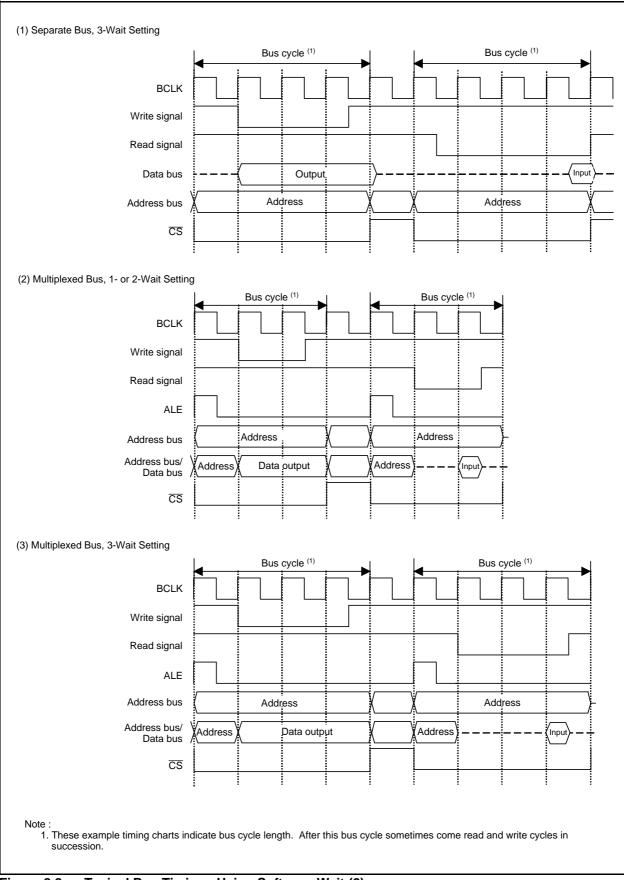

| 8.2     | 2.10   | Software Wait                                                                      | 61  |

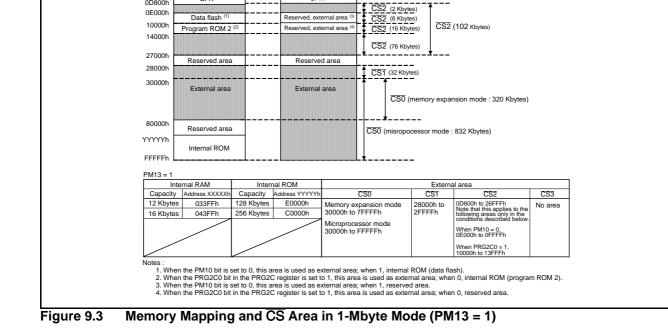

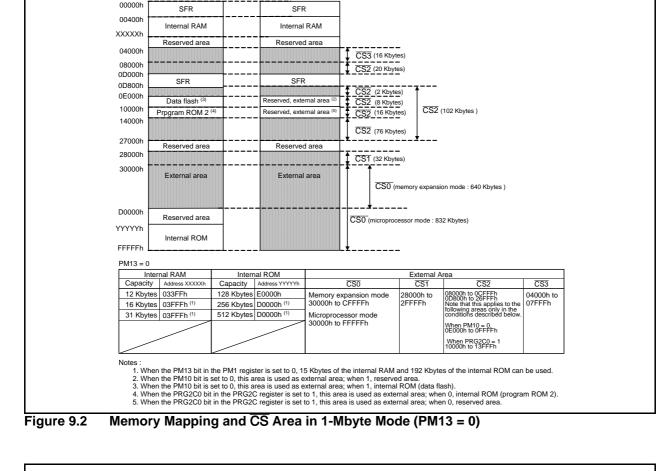

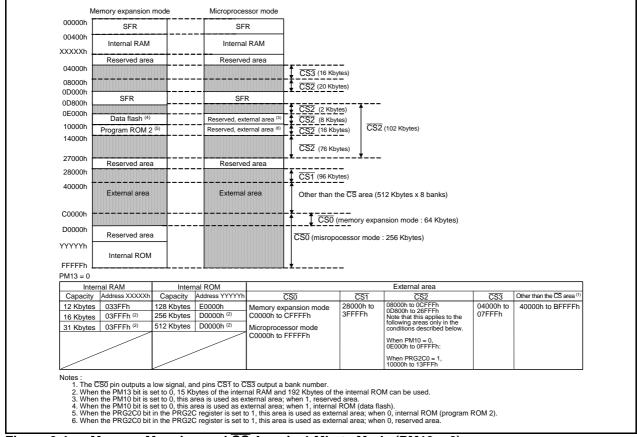

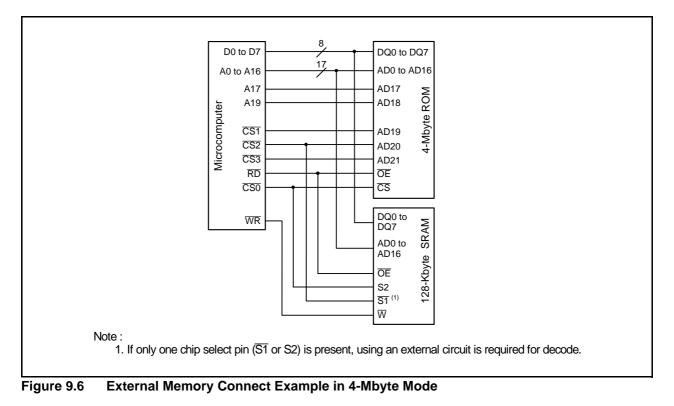

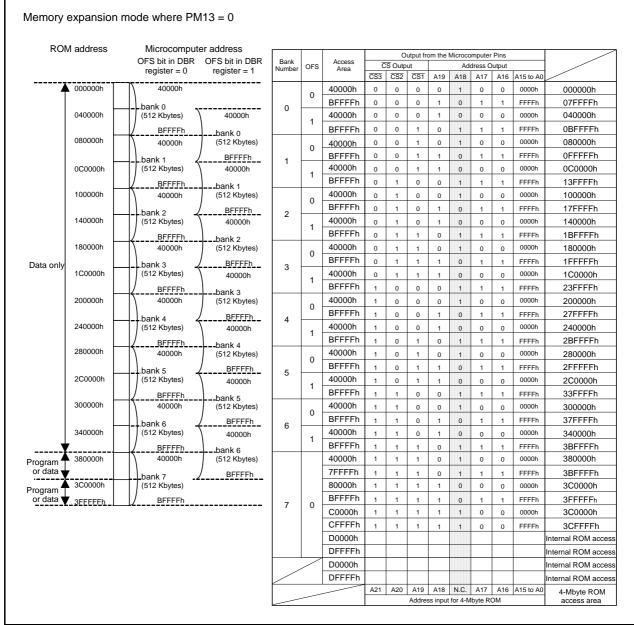

| 9. Me   | emory  | / Space Expansion Function                                                         | 66  |

| 9.2     | 4-N    | Ibyte Mode                                                                         | 66  |

| 9.2     | 2.1    | Addresses 04000h to 3FFFFh, C0000h to FFFFFh                                       | 66  |

| 9.2     | 2.2    | Addresses 40000h to BFFFFh                                                         | 66  |

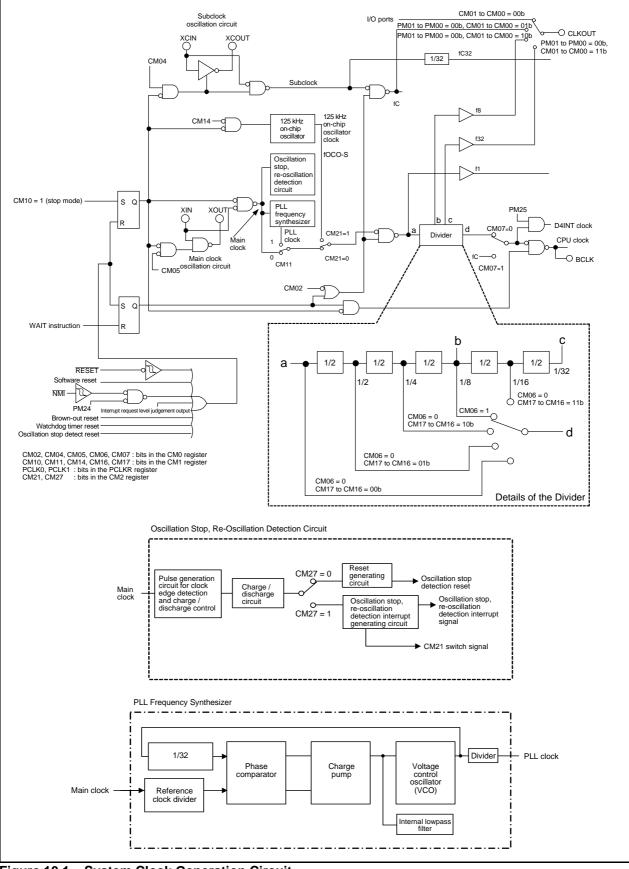

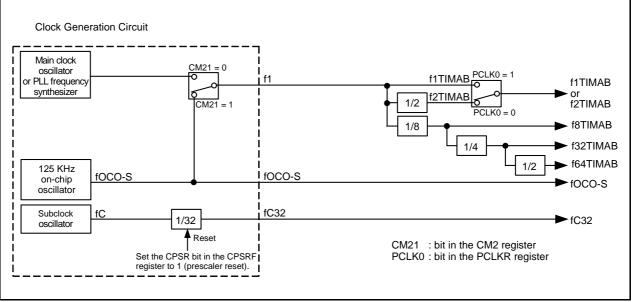

| 10. Cl  | ock G  | Generation Circuit                                                                 | 74  |

| 10.1    | Тур    | e of the Clock Generation Circuit                                                  | 74  |

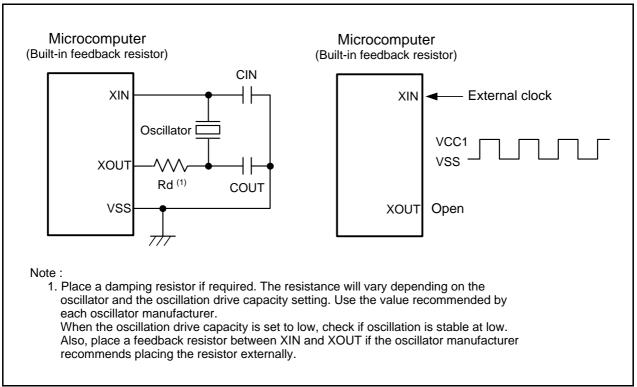

| 10      | ).1.1  | Main Clock                                                                         | 81  |

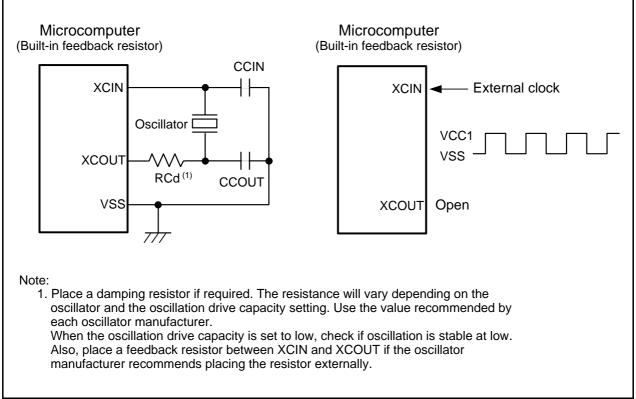

| 10      | .1.2   | Sub Clock                                                                          | 82  |

| 10      | .1.3   | 125 kHz On-Chip Oscillator Clock (fOCO-S)                                          | 83  |

| 10      | 0.1.4  | PLL Clock                                                                          | 83  |

| 10.2    | CP     | U Clock and Peripheral Function Clock                                              | 86  |

| 10      | .2.1   | CPU Clock and BCLK                                                                 | 86  |

| 10      | .2.2   | Peripheral Function Clock (f1, fC32)                                               | 87  |

| 10.3    | Clo    | ck Output Function                                                                 | 87  |

| 10.4    | Ρον    | ver Control                                                                        | 88  |

| 10      | .4.1   | Normal Operating Mode                                                              | 88  |

| 10      | .4.2   | Wait Mode                                                                          | 90  |

| 10      | .4.3   | Stop Mode                                                                          | 92  |

| 10.5    | Sys    | stem Clock Protection Function                                                     | 95  |

| 10.6    | Oso    | cillation Stop and Re-Oscillation Detect Function                                  | 96  |

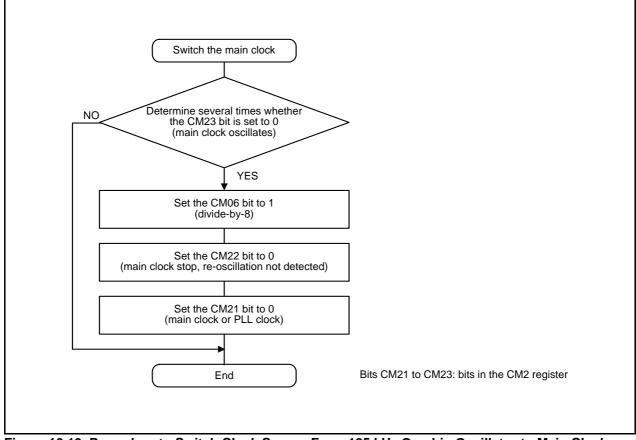

| 10      | .6.1   | Operation When CM27 bit = 0 (Oscillation Stop Detection Reset)                     | 96  |

| 10      | .6.2   | Operation When CM27 bit = 1 (Oscillation Stop and Re-oscillation Det<br>Interrupt) |     |

| 10      | .6.3   | How to Use Oscillation Stop and Re-Oscillation Detect Function                     | 97  |

| 11. Pr  | otecti | on                                                                                 | 98  |

| 12. Int | errup  | vt                                                                                 | 99  |

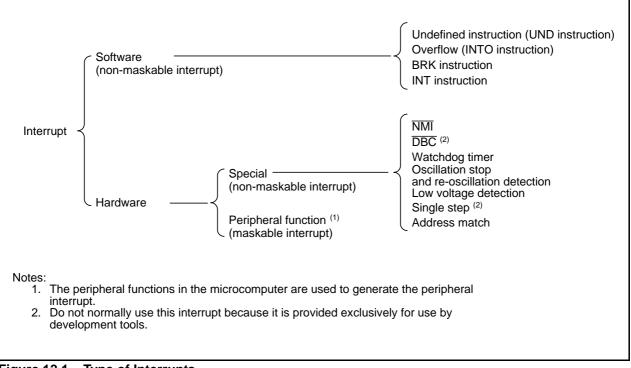

| 12.1    | Тур    | e of Interrupts                                                                    | 99  |

| 12.2    | Sof    | tware Interrupts                                                                   | 100 |

| 12      | 2.2.1  | Undefined Instruction Interrupt                                                    | 100 |

| 12.2    | 2.2  | Overflow Interrupt                                  | 100 |

|---------|------|-----------------------------------------------------|-----|

| 12.2    | 2.4  | INT Instruction Interrupt                           |     |

| 12.3    | Har  | dware Interrupts                                    | 101 |

| 12.3    | 3.1  | Special Interrupts                                  | 101 |

| 12.3    | 3.2  | Peripheral Function Interrupts                      | 101 |

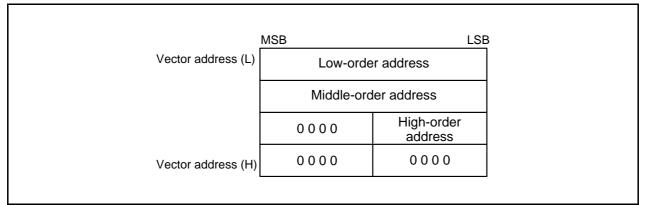

| 12.4    | Inte | errupts and Interrupt Vector                        |     |

| 12.4    | 4.1  | Fixed Vector Tables                                 | 102 |

| 12.4    | 4.2  | Relocatable Vector Tables                           |     |

| 12.5    | Inte | errupt Control                                      | 105 |

| 12.5    | 5.1  | I Flag                                              |     |

| 12.5    | 5.2  | IR Bit                                              | 107 |

| 12.5    | 5.3  | Bits ILVL2 to ILVL0 and IPL                         | 107 |

| 12.5    | 5.4  | Interrupt Sequence                                  | 108 |

| 12.5    | 5.5  | Interrupt Response Time                             |     |

| 12.5    | 5.6  | Variation of IPL when Interrupt Request IS Accepted |     |

| 12.5    | 5.7  | Saving Registers                                    | 110 |

| 12.5    | 5.8  | Returning from an Interrupt Routine                 |     |

| 12.5    | 5.9  | Interrupt Priority                                  |     |

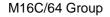

| 12.5    | 5.10 | Interrupt Priority Level Select Circuit             | 111 |

| 12.6    | INT  | Interrupt                                           | 113 |

| 12.7    | NM   | Ī Interrupt                                         | 115 |

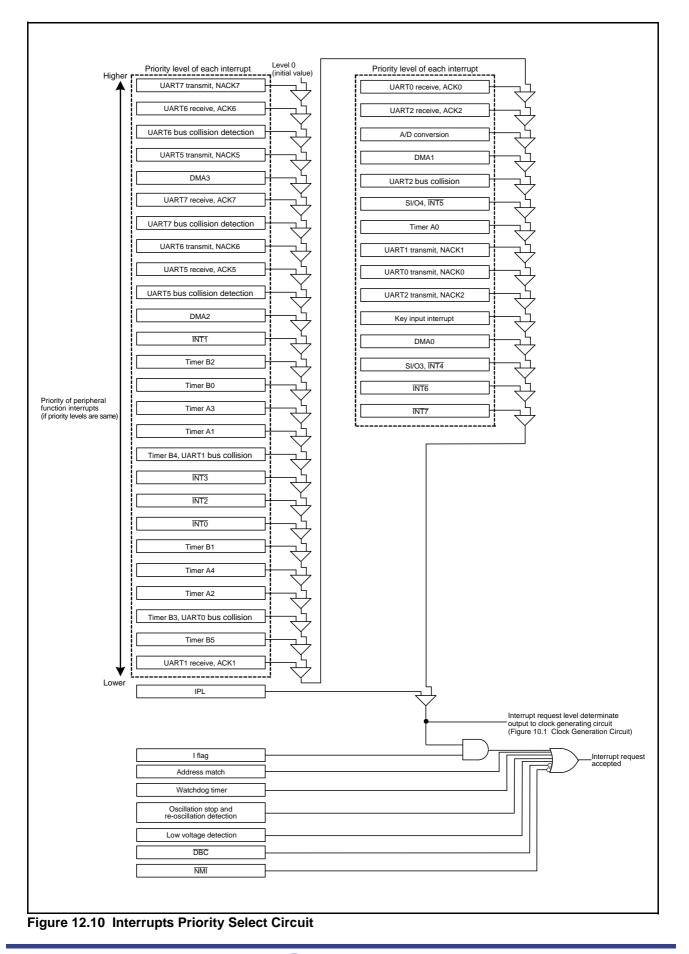

| 12.8    | Key  | / Input Interrupt                                   | 115 |

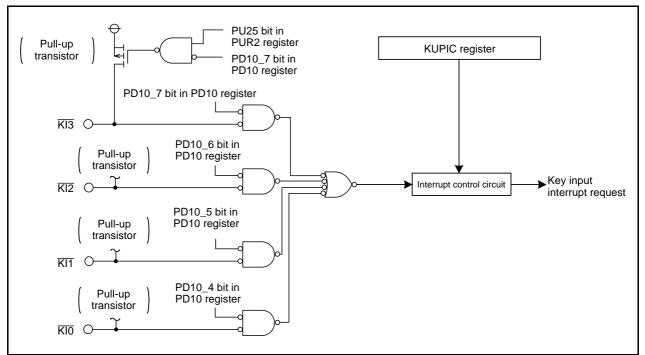

| 12.9    | Add  | dress Match Interrupt                               | 116 |

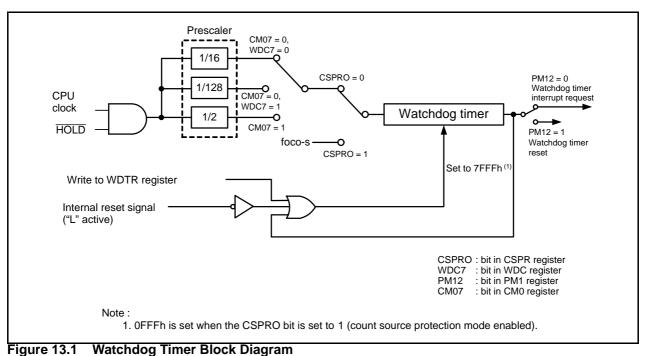

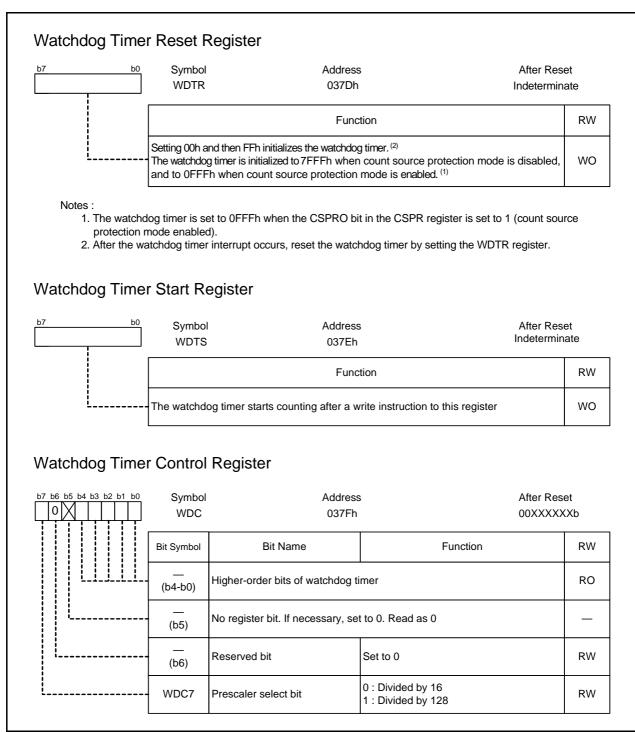

| 13. Wat | tchd | og Timer                                            | 118 |

| 13.1    |      | unt Source Protection Mode Disabled                 |     |

| 13.2    |      | unt Source Protection Mode Enabled                  |     |

|         |      |                                                     |     |

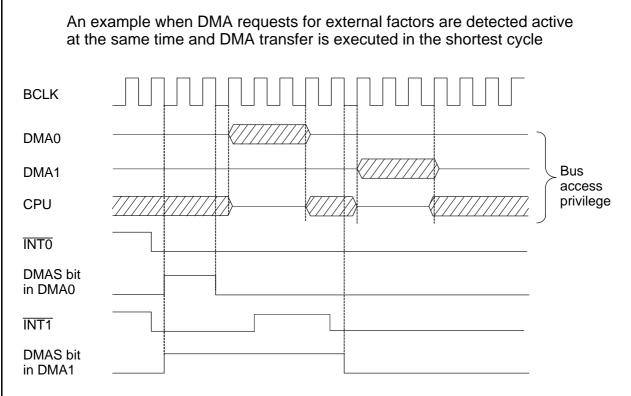

| 14. DM  |      |                                                     |     |

| 14.1    | Tra  | nsfer Cycles                                        |     |

| 14.1    |      | Effect of Source and Destination Addresses          |     |

| 14.1    | 1.2  | Effect of BYTE Pin Level                            |     |

| 14.1    | 1.3  | Effect of Software Wait                             |     |

| 14.1    | 1.4  | Effect of RDY Signal                                | 130 |

| 14.2    | DM   | A Transfer Cycles                                   | 132 |

| 14.3    | DM   | A Enabled                                           |     |

| 1   | 4.4  | DM.   | A Request                                              | 133 |

|-----|------|-------|--------------------------------------------------------|-----|

| 1   | 4.5  | Cha   | annel Priority and DMA Transfer Timing                 | 134 |

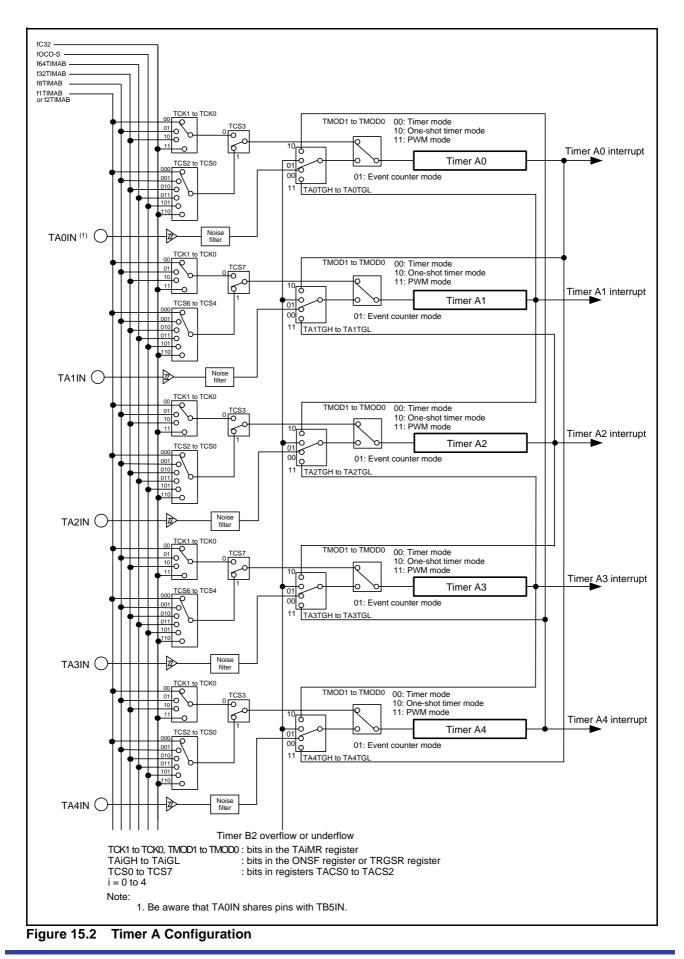

| 15. | Tim  | ers.  |                                                        | 135 |

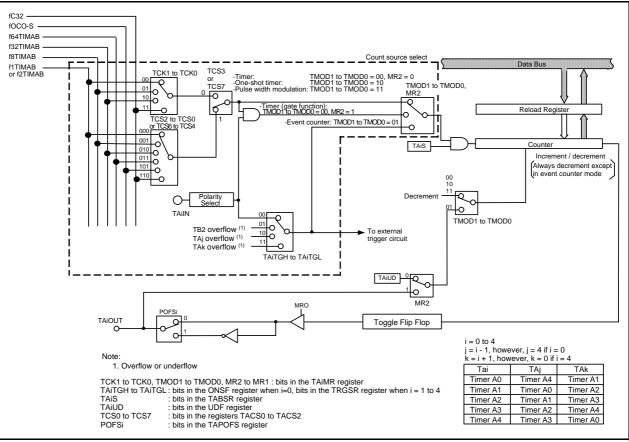

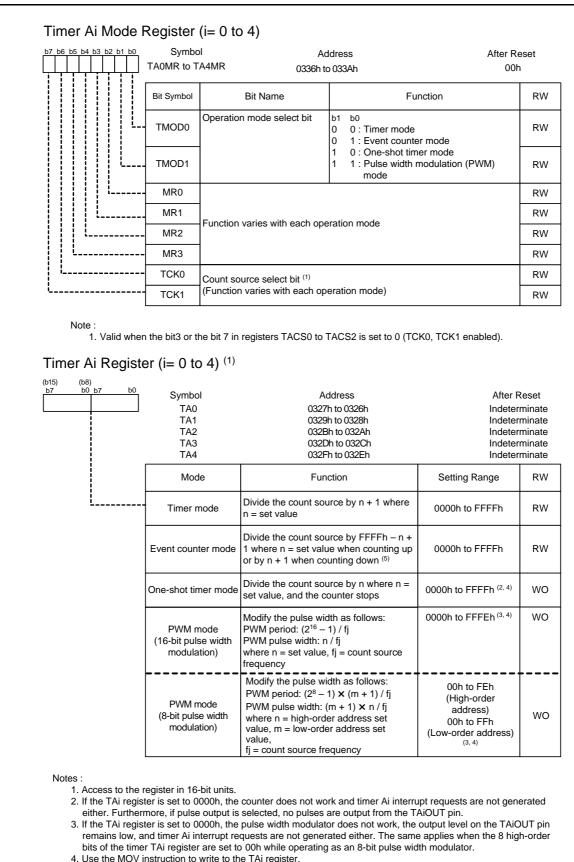

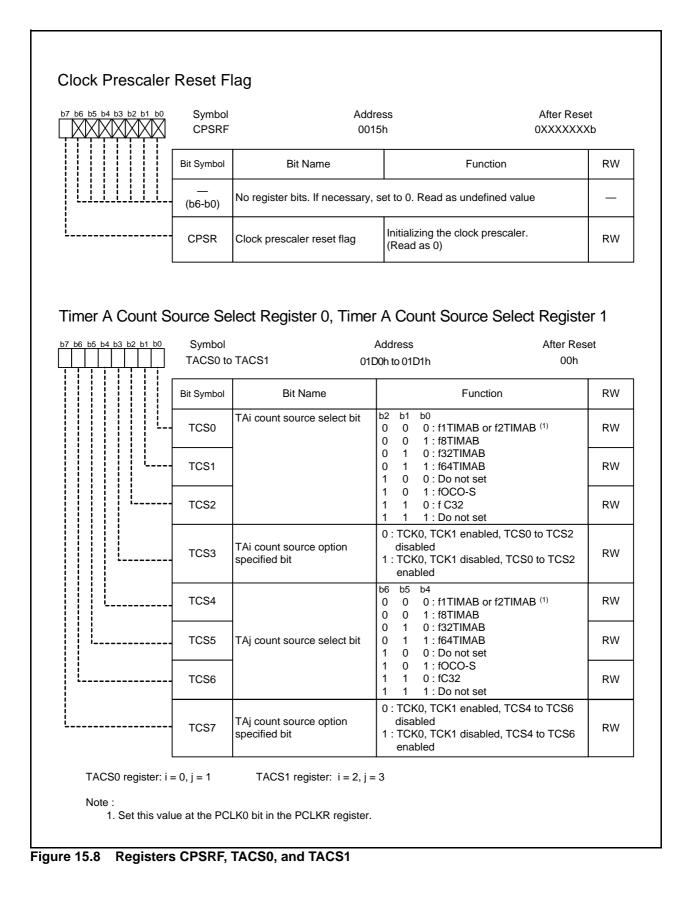

| 1   | 5.1  | Tim   | er A                                                   | 138 |

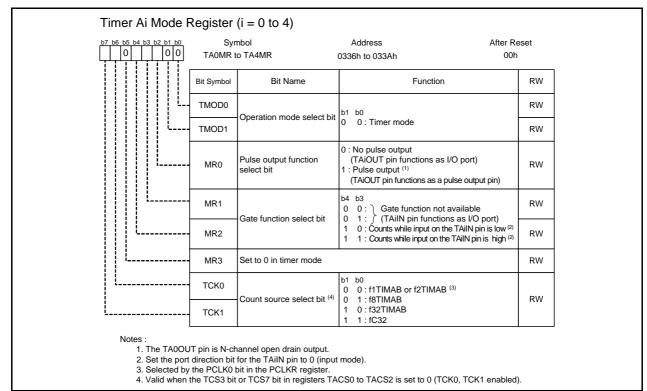

|     | 15.1 | .1    | Timer Mode                                             | 144 |

|     | 15.1 | .2    | Event Counter Mode                                     | 145 |

|     | 15.1 | .3    | One-Shot Timer Mode                                    | 150 |

|     | 15.1 | .4    | PWM Mode (Pulse Width Modulation Mode)                 | 152 |

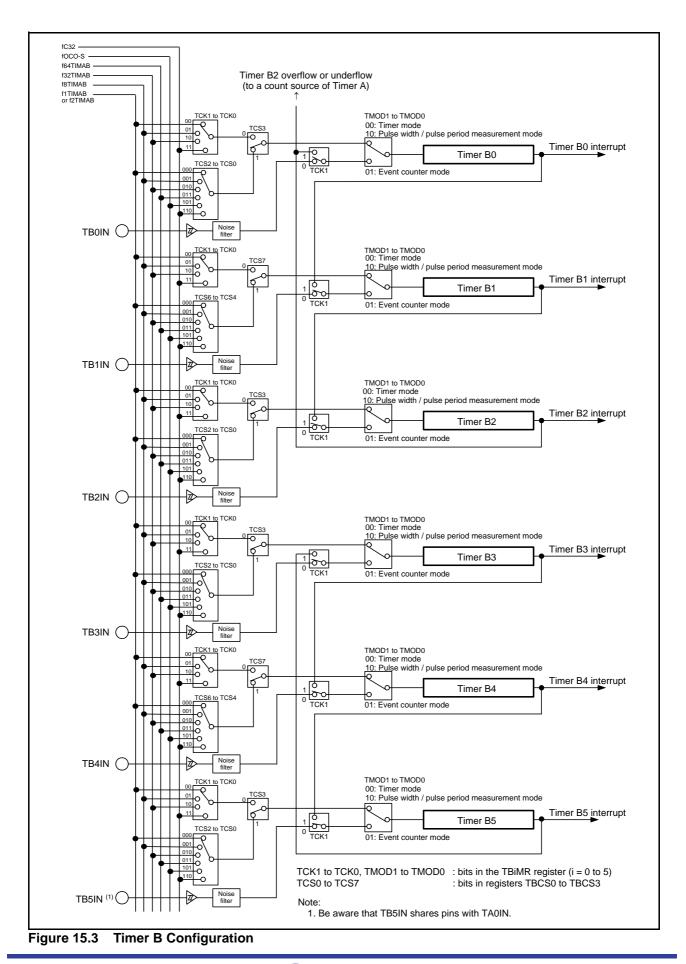

| 1   | 5.2  | Tim   | er B                                                   | 155 |

|     | 15.2 | 2.1   | Timer Mode                                             | 159 |

|     | 15.2 | 2.2   | Event Counter Mode                                     | 161 |

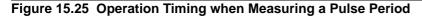

|     | 15.2 | 2.3   | Pulse Period and Pulse Width Measurement Modes         | 163 |

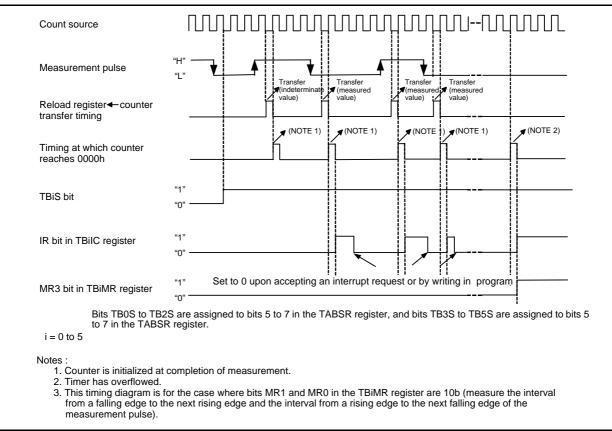

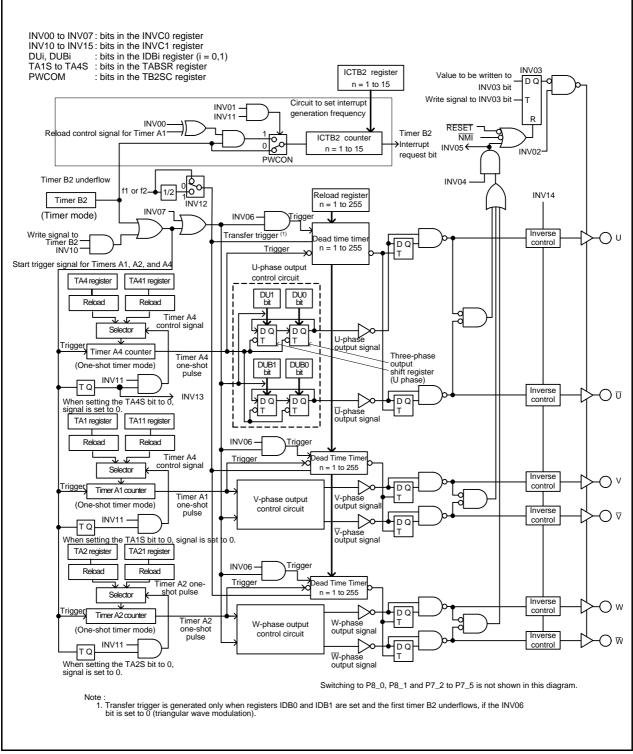

| 16. | Thre | ee-F  | Phase Motor Control Timer Function                     | 166 |

| 17. | Seri | al Ir | nterface                                               | 176 |

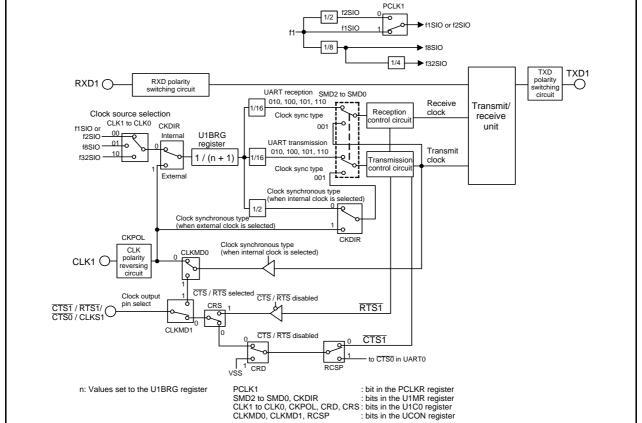

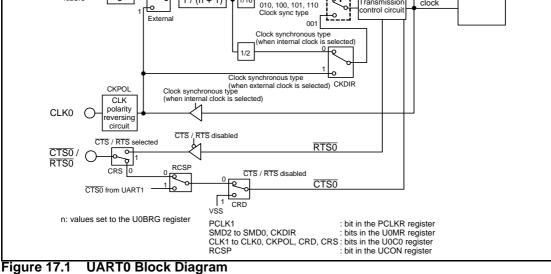

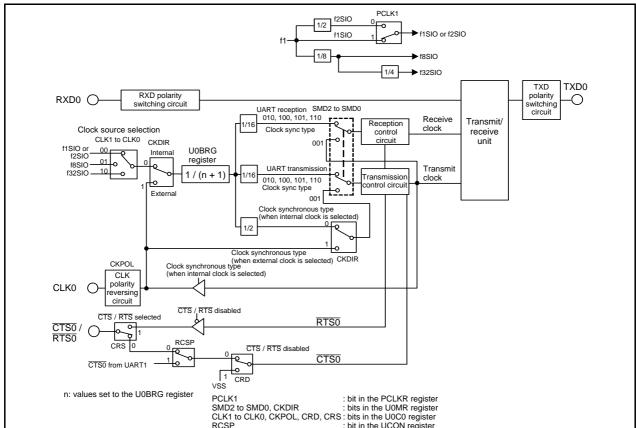

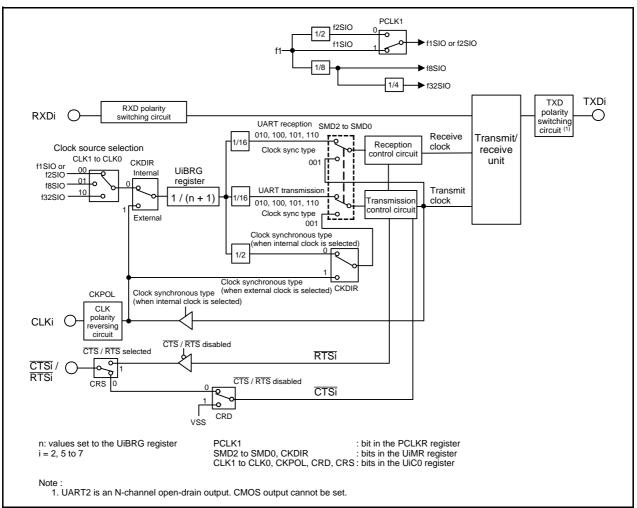

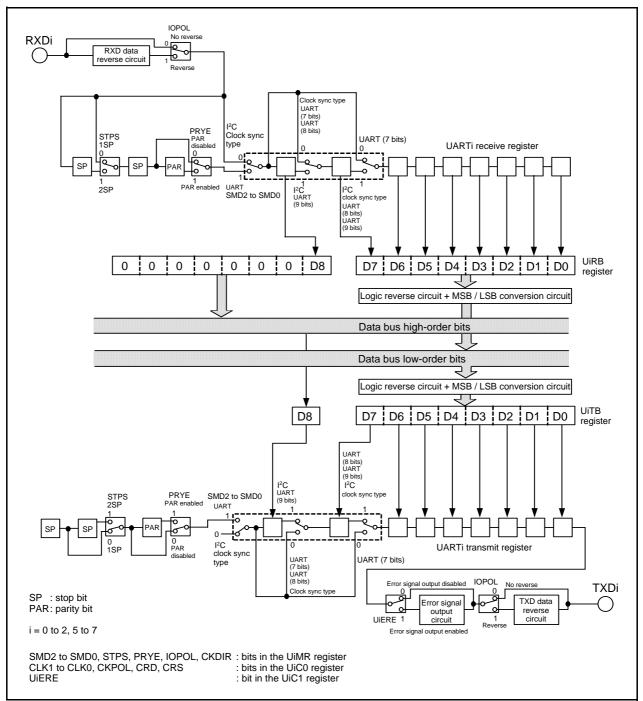

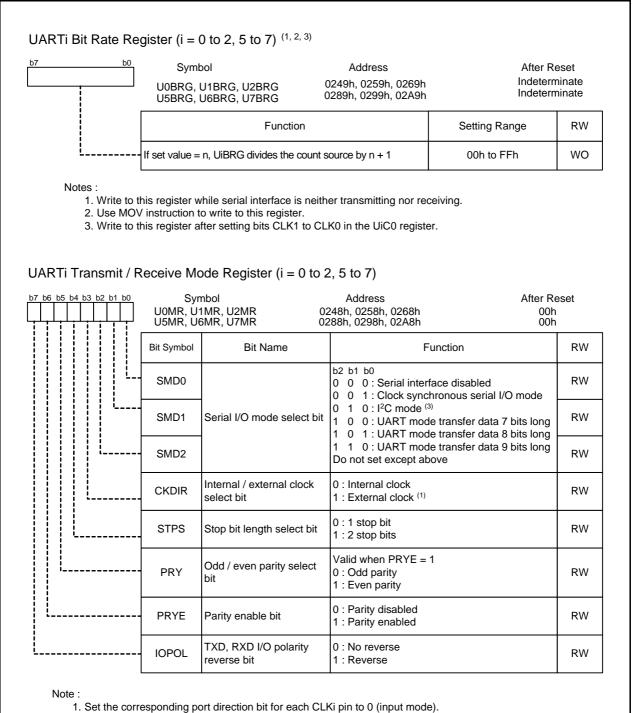

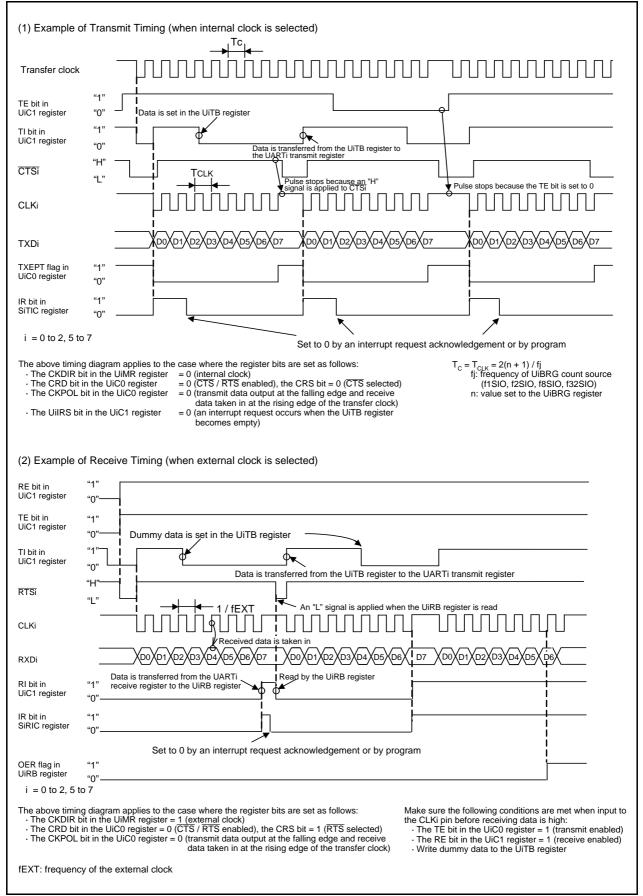

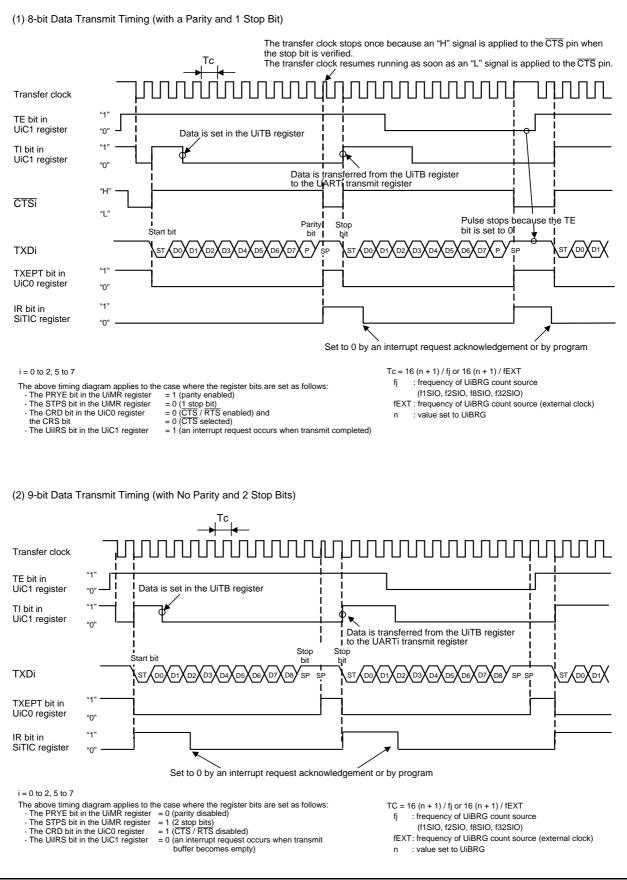

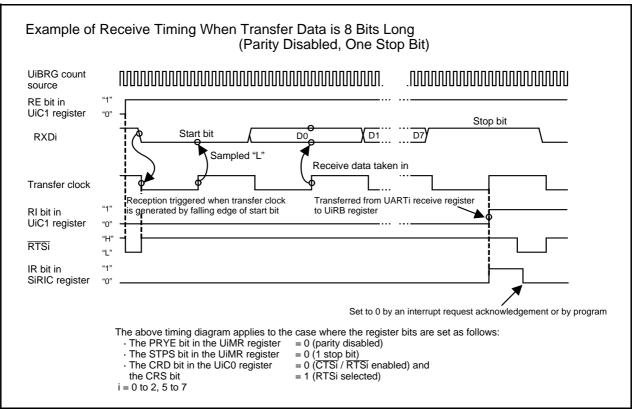

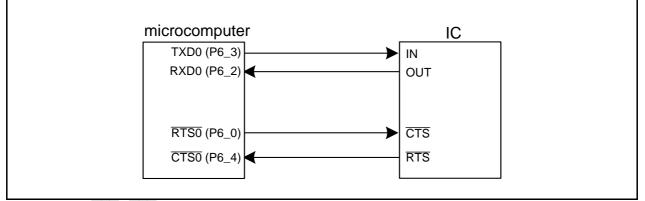

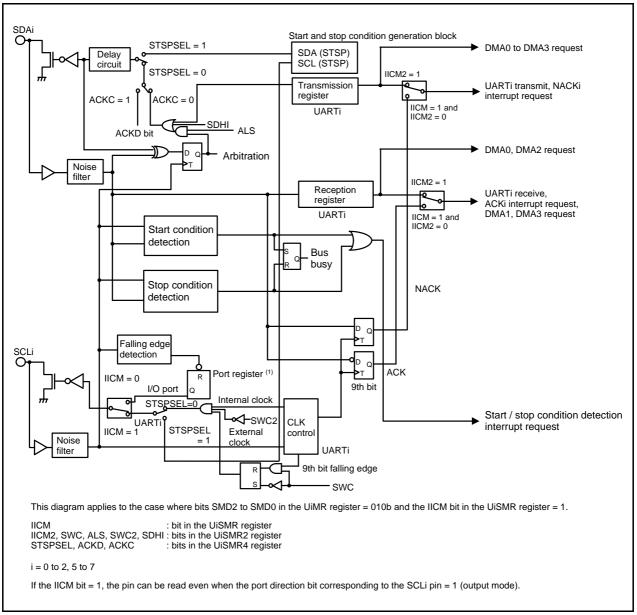

| 1   | 7.1  | UAF   | RTi (i = 0 to 2, 5 to 7)                               | 176 |

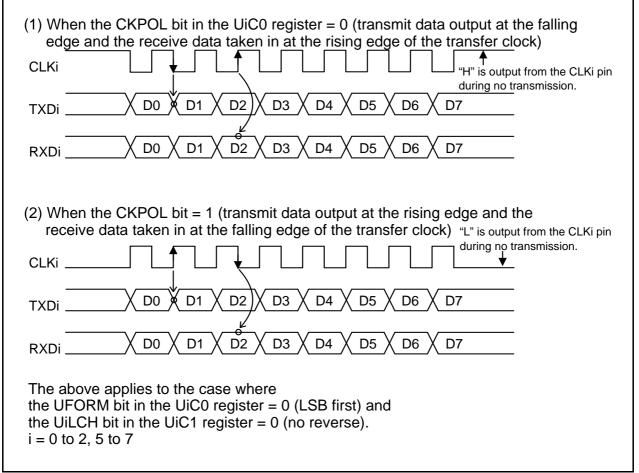

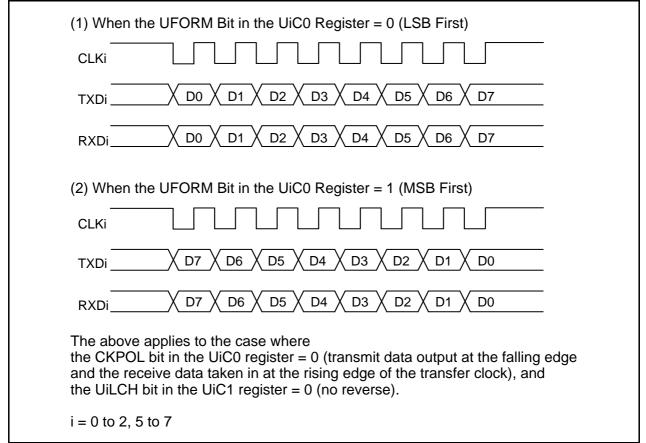

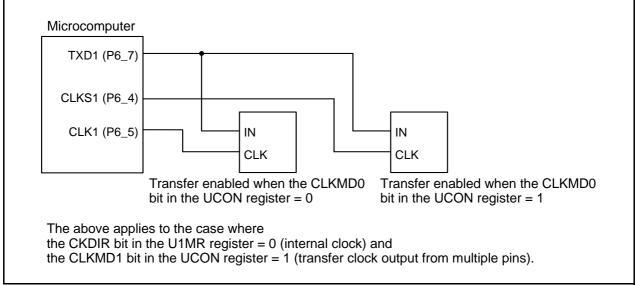

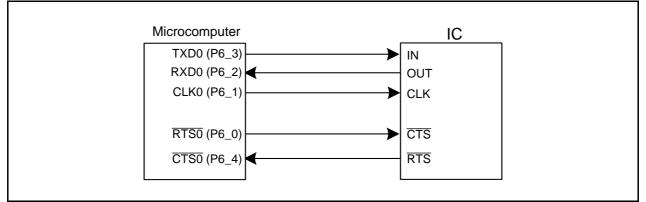

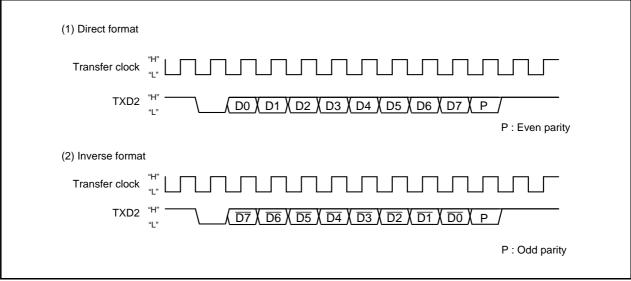

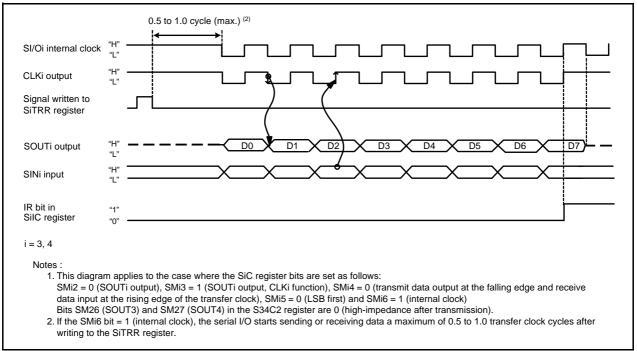

|     | 17.1 | .1    | Clock Synchronous Serial I/O Mode                      | 187 |

|     | 17.1 | .2    | Clock Asynchronous Serial I/O (UART) Mode              | 195 |

|     | 17.1 | .3    | Special Mode 1 (I <sup>2</sup> C mode)                 |     |

|     | 17.1 | .4    | Special Mode 2                                         | 213 |

|     | 17.1 | .5    | Special Mode 3 (IE mode)                               |     |

|     | 17.1 | .6    | Special Mode 4 (SIM Mode) (UART2)                      | 220 |

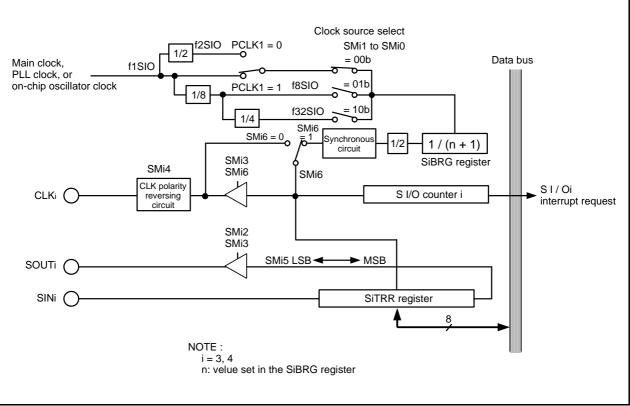

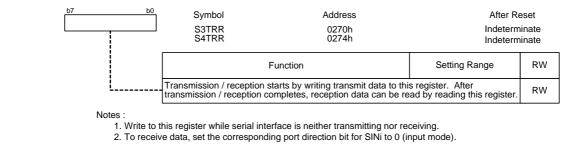

| 1   | 7.2  | SI/C  | 03 and SI/O4                                           | 225 |

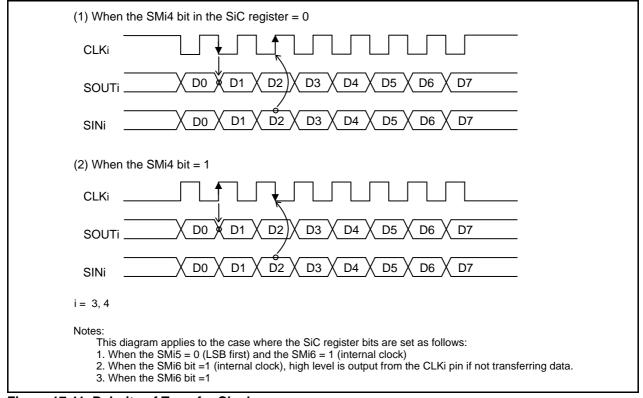

|     | 17.2 | 2.1   | SI/Oi Operation Timing                                 | 229 |

|     | 17.2 | 2.2   | CLK Polarity Selection                                 | 229 |

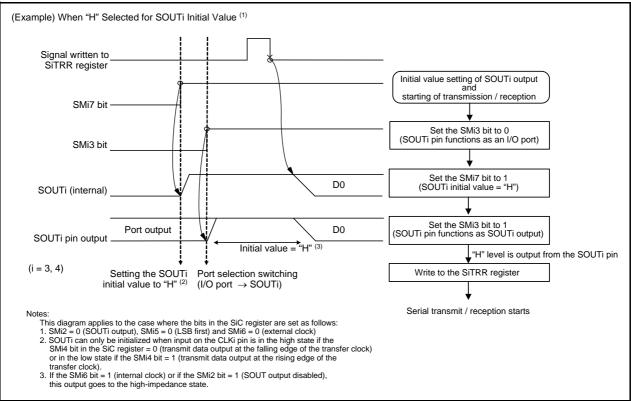

|     | 17.2 | 2.3   | Functions for Setting an SOUTi Initial Value           | 230 |

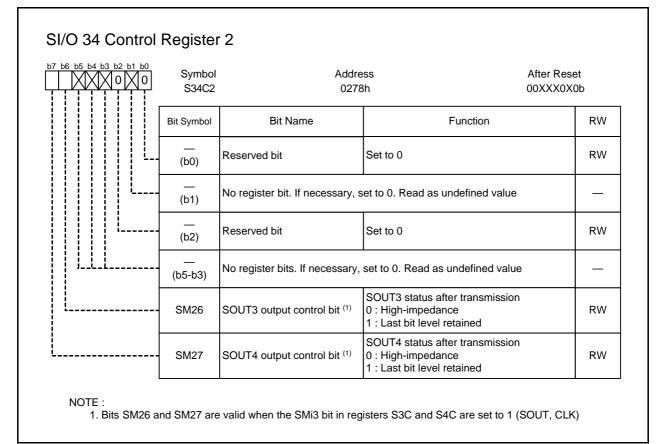

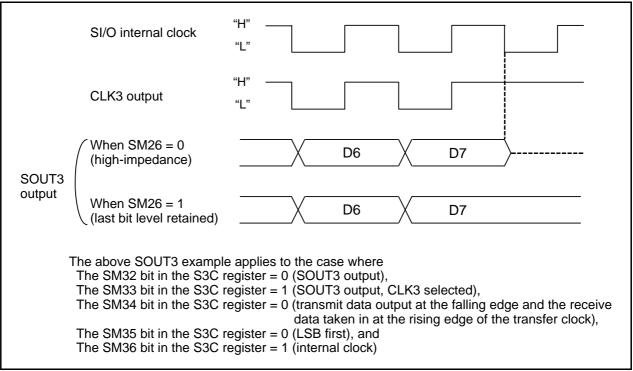

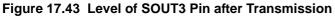

|     | 17.2 | 2.4   | Functions for Selecting SOUTi State after Transmission | 231 |

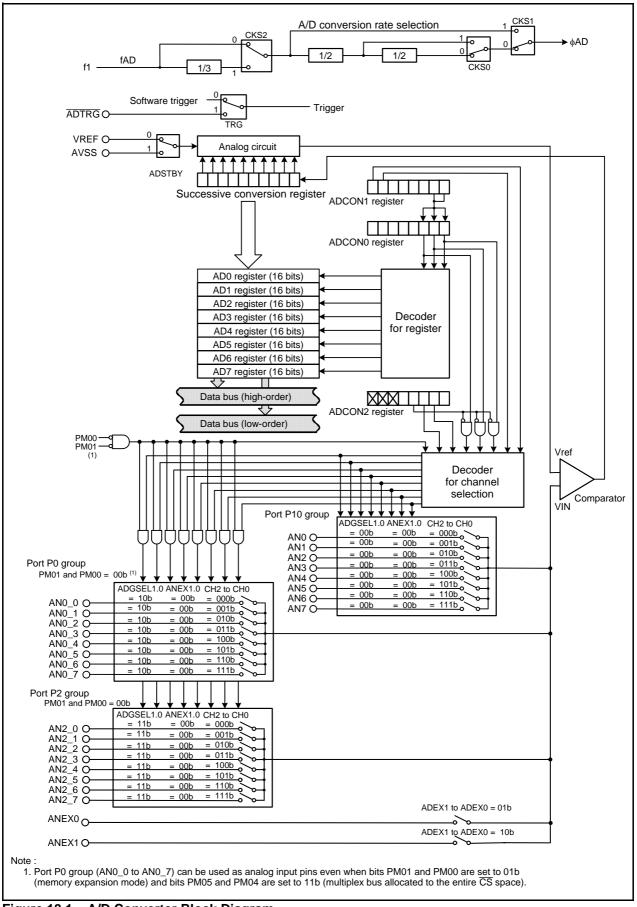

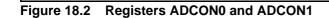

| 18. | A/D  | Cor   | nverter                                                |     |

| 1   | 8.1  | Мос   | de Description                                         |     |

|     | 18.1 | .1    | One-Shot Mode                                          |     |

|     | 18.1 | .2    | Repeat Mode                                            | 238 |

|     | 18.1 | .3    | Single Sweep Mode                                      |     |

|     | 18.1 | .4    | Repeat Sweep Mode 0                                    |     |

|     | 18.1 | .5    | Repeat Sweep Mode 1                                    |     |

| 18.2    | Cor   | nversion Rate                                                       |     |

|---------|-------|---------------------------------------------------------------------|-----|

| 18.3    | Ext   | ended Analog Input Pins                                             |     |

| 18.4    | Cur   | rrent Consumption Reducing Function                                 |     |

| 18.5    | Ext   | ernal Sensor                                                        |     |

| 19. D/A |       | nverter                                                             |     |

| 19.1    | Sur   | nmary                                                               |     |

| 20. CR  | CO    | peration                                                            | 251 |

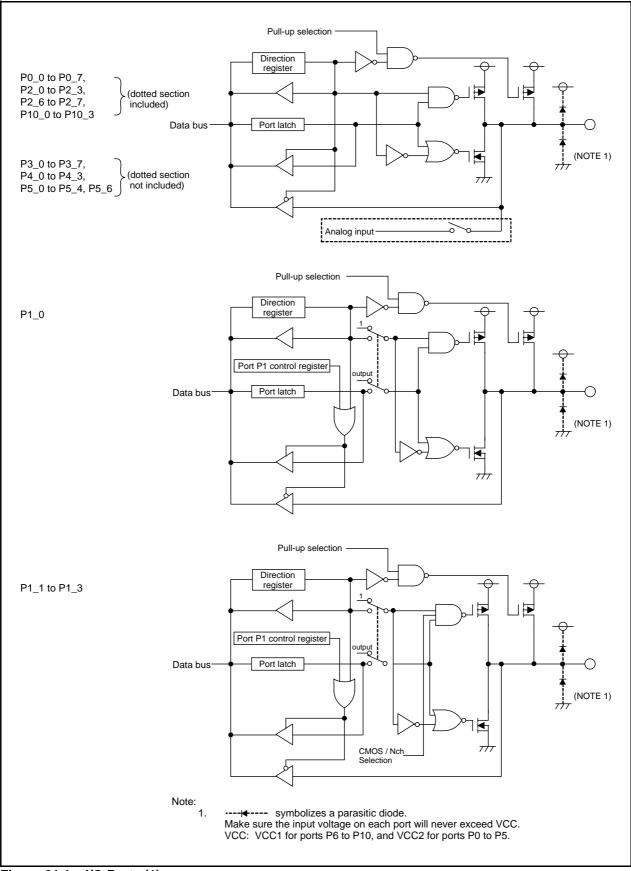

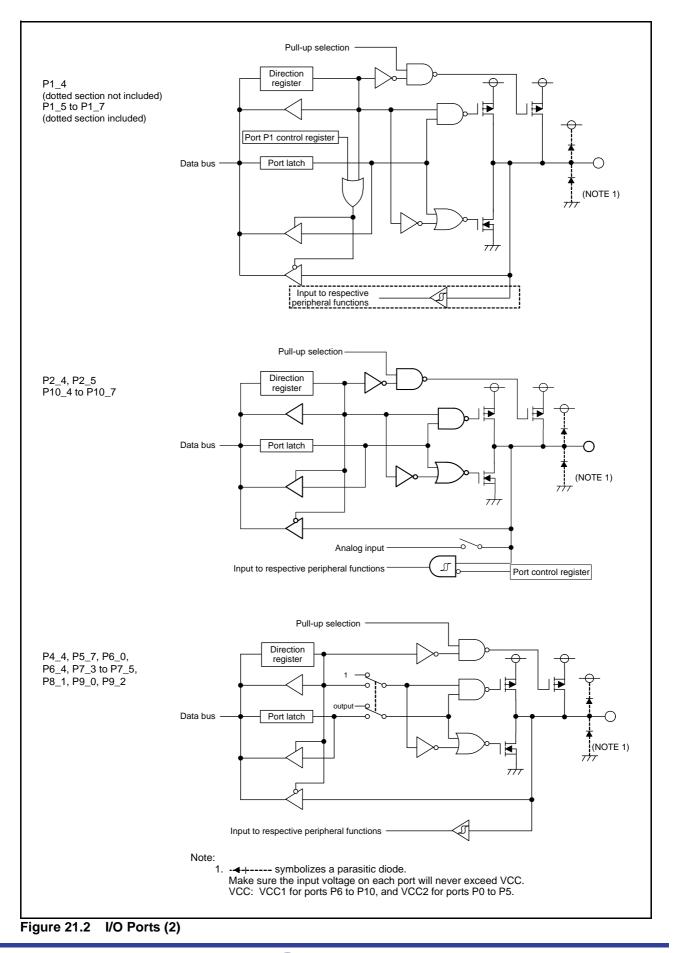

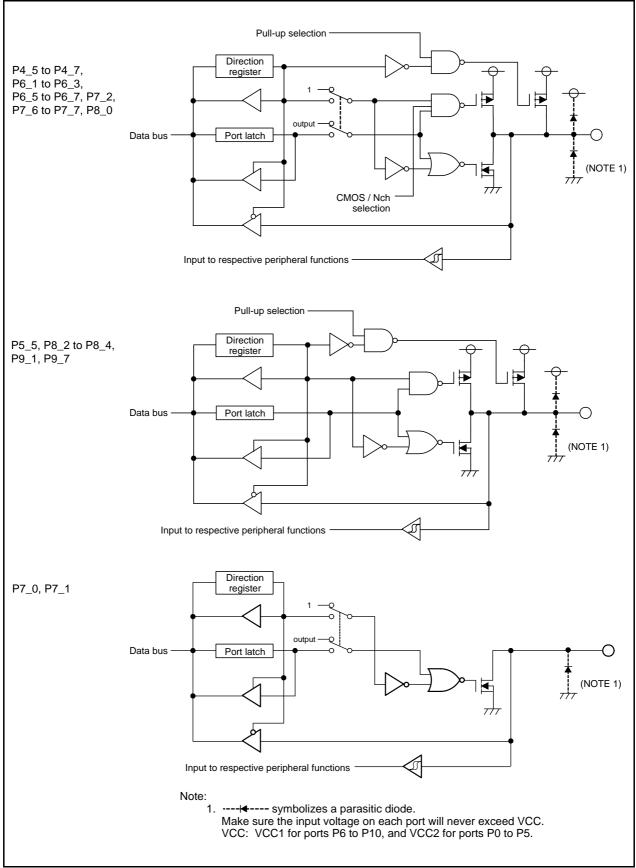

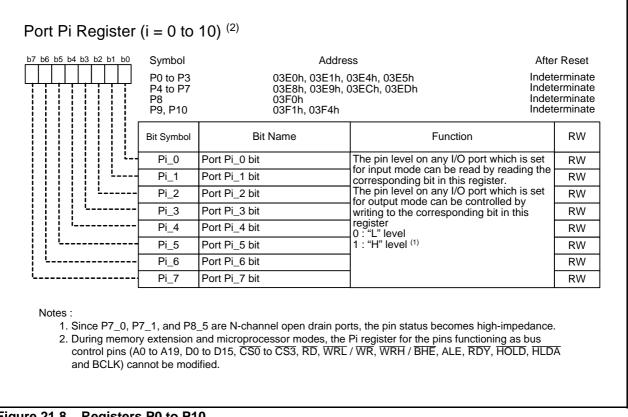

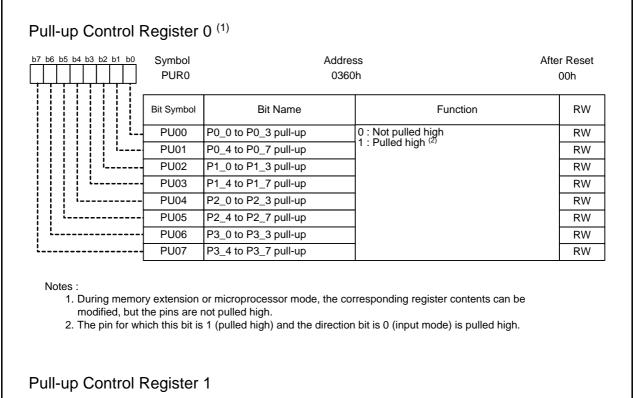

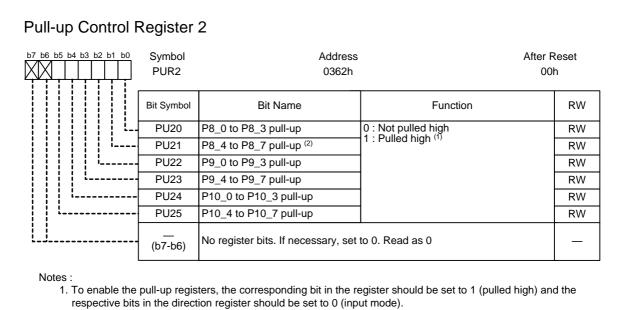

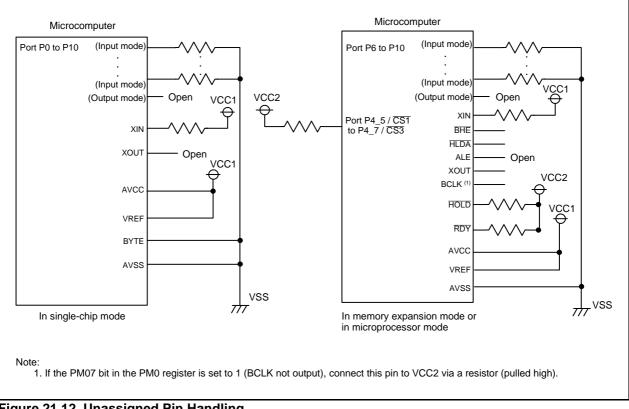

| 21. Pro | ograr | mmable I/O Ports                                                    | 253 |

| 21.1    | Por   | t Pi Direction Register (PDi Register, i = 0 to 10)                 |     |

| 21.2    | Por   | t Pi Register (Pi Register, i = 0 to 10)                            |     |

| 21.3    |       | I-up Control Register 0 to Pull-up Control Register 2 (Registers PL |     |

| 21.4    |       | t Control Register (PCR Register)                                   |     |

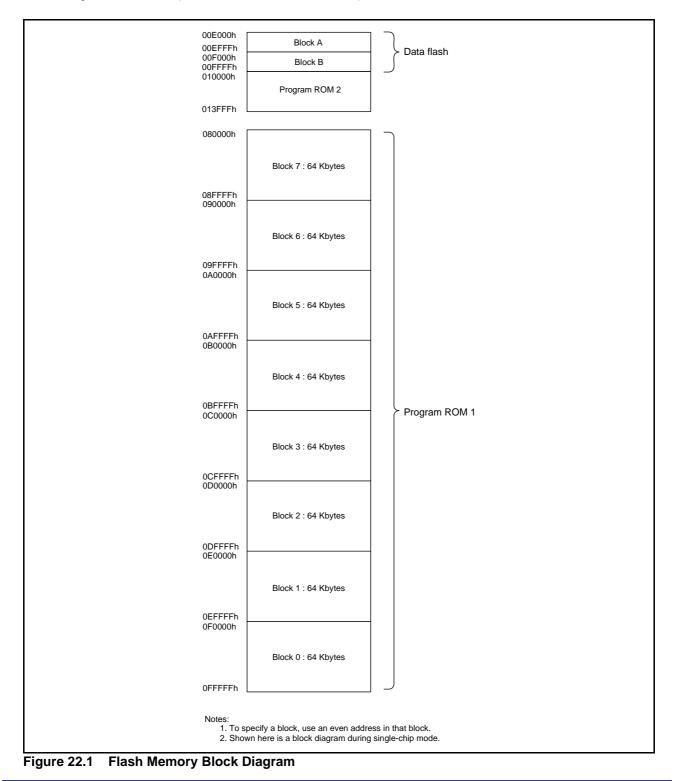

| 22. Fla | sh M  | 1emory Version                                                      |     |

| 22.1    |       | mory Map                                                            |     |

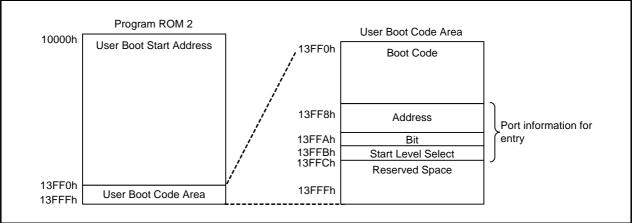

| 22.     |       | Boot Mode                                                           |     |

|         | 1.2   | User Boot Function                                                  |     |

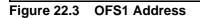

| 22.2    |       | nctions to Prevent Flash Memory from Rewriting                      |     |

| 22.     |       | ROM Code Protect Function                                           |     |

|         | 2.2   | ID Code Check Function                                              |     |

|         |       | Forced Frase Function                                               |     |

| 22.     | 2.4   | Standard Serial I/O Mode Disable Function                           |     |

| 22.3    |       | U Rewrite Mode                                                      |     |

| 22.     | 3.1   | EW0 Mode                                                            |     |

| 22.     | 3.2   | EW1 Mode                                                            |     |

| 22.     | 3.3   | Flash Memory Control Register (Registers FMR0, FMR1, FMR2           | ,   |

| 22.     | 3.4   | Precautions on CPU Rewrite Mode                                     |     |

| 22.     | 3.5   | Software Commands                                                   |     |

| 22.     | 3.6   | Data Protect Function                                               |     |

| 22.     | 3.7   | Status Register                                                     |     |

| 22.     | 3.8   | Full Status Check                                                   |     |

| 22.4    | Sta   | ndard Serial I/O Mode                                               |     |

|     | 22.4 | 1.1         | ID Code Check Function                                         |     |

|-----|------|-------------|----------------------------------------------------------------|-----|

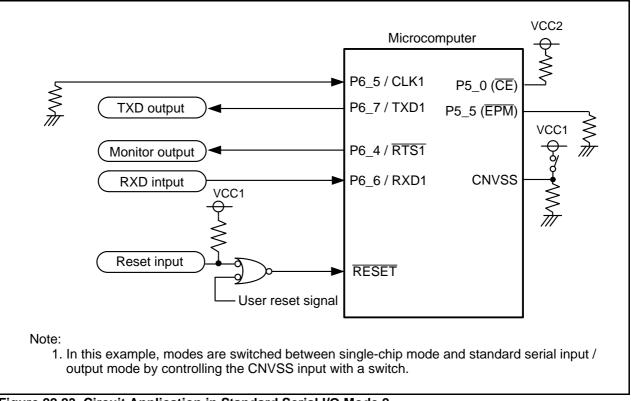

|     | 22.4 | .2          | Example of Circuit Application in the Standard Serial I/O Mode | 302 |

| 2   | 2.5  | Par         | allel I/O Mode                                                 | 304 |

|     | 22.5 | 5.1         | ROM Code Protect Function                                      | 304 |

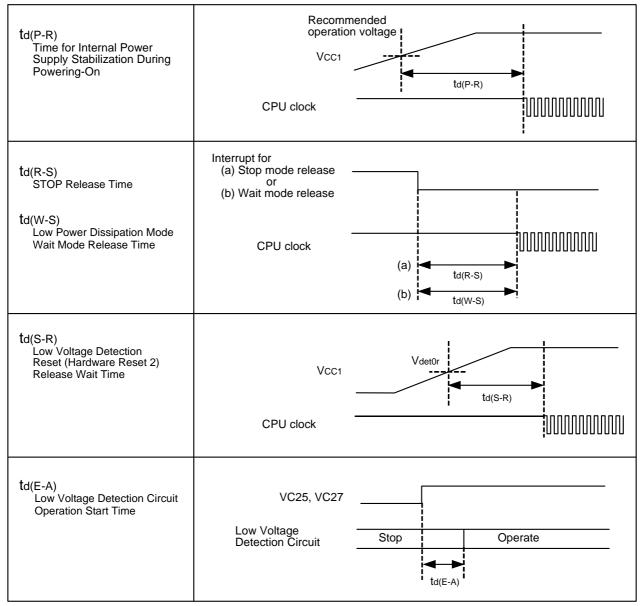

| 23. | Elec | ctrica      | al Characteristics                                             | 305 |

| 2   | 3.1  | Eleo        | ctrical Characteristics                                        | 305 |

| 24. | Pred | caut        | ions                                                           | 345 |

| 2   | 4.1  | SFF         | ۶                                                              | 345 |

|     | 24.1 | .1          | Register Settings                                              | 345 |

| 2   | 4.2  | Res         | set                                                            | 346 |

|     | 24.2 | 2.1         | VCC1                                                           | 346 |

|     | 24.2 | 2.2         | CNVSS                                                          | 346 |

| 2   | 4.3  | Bus         | 5                                                              | 347 |

| 2   | 4.4  | PLL         | - Frequency Synthesizer                                        | 348 |

| 2   | 4.5  | Pov         | ver Control                                                    | 349 |

| 2   | 4.6  | Pro         | tect                                                           | 351 |

| 2   | 4.7  | Inte        | rrupt                                                          | 352 |

|     | 24.7 | <b>'</b> .1 | Reading address 00000h                                         | 352 |

|     | 24.7 | <b>.</b> 2  | SP Setting                                                     | 352 |

|     | 24.7 | <b>'</b> .3 | NMI Interrupt                                                  | 352 |

|     | 24.7 | <b>'</b> .4 | Changing an Interrupt Generate Factor                          | 353 |

|     | 24.7 | <b>'</b> .5 | INT Interrupt                                                  | 353 |

|     | 24.7 | <b>'</b> .6 | Rewriting the Interrupt Control Register                       | 354 |

|     | 24.7 | <b>'</b> .7 | Watchdog Timer Interrupt                                       | 355 |

| 2   | 4.8  | DM          | AC                                                             | 356 |

|     | 24.8 | 3.1         | Write to the DMAE Bit in the DMiCON Register (i = 0 to 3)      | 356 |

|     | 24.8 | 3.2         | DMAC Channel Priority                                          | 356 |

| 2   | 4.9  | Tim         | ers                                                            | 357 |

|     | 24.9 | 9.1         | Timer A                                                        | 357 |

|     | 24.9 | ).2         | Timer B                                                        |     |

| 2   | 4.10 | Ser         | ial Interface                                                  |     |

|     | 24.1 | 0.1         | Clock Synchronous Serial I/O                                   |     |

|     | 24.1 | 0.2         | UART (Clock Asynchronous Serial I/O) Mode                      |     |

|     | 24.1 | 0.3         | Special Mode 1 (I2C Mode)                                      |     |

| 24.10.4 Special Mode 4 (SIM Mode)                                                    |

|--------------------------------------------------------------------------------------|

| 24.10.5 SI/O3, SI/O4                                                                 |

| 24.11 A/D Converter                                                                  |

| 24.11.1 Repeat Mode, Repeat Sweep Mode 0, and Repeat Sweep Mode 1 370                |

| 24.12 Programmable I/O Ports                                                         |

| 24.13 Flash Memory Version                                                           |

| 24.13.1 Functions to Inhibit Rewriting Flash Memory                                  |

| 24.13.2 Stop Mode                                                                    |

| 24.13.3 Wait Mode                                                                    |

| 24.13.4 Low Power Consumption Mode,<br>On-Chip Oscillator Low Power Consumption Mode |

| 24.13.5 Writing Command and Data                                                     |

| 24.13.6 Program Command                                                              |

| 24.13.7 Lock Bit Program Command                                                     |

| 24.13.8 Operation Speed                                                              |

| 24.13.9 Instructions Inhibited against Use                                           |

| 24.13.10 Interrupts                                                                  |

| 24.13.11 How to Access                                                               |

| 24.13.12 Writing                                                                     |

| 24.13.13 DMA transfer                                                                |

| 24.13.14 Programming / Erasing Endurance and Execution Time                          |

| 24.13.15 When Entering to Boot Mode                                                  |

| 24.14 Noise                                                                          |

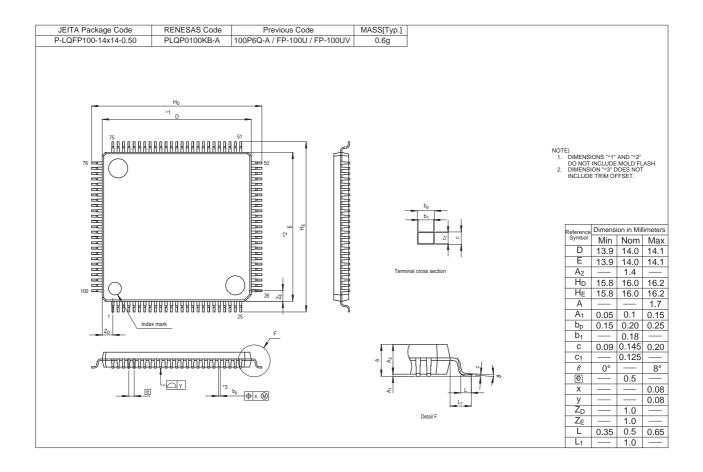

| Appendix 1.Package Dimensions                                                        |

| Appendix 2.Difference Between M16C/64 and M16C/62P                                   |

| REGISTER INDEX 382                                                                   |

## SFR Page Reference

| 0005h         Proc           0006h         Syst           0007h         Syst           0008h         Chip           0009h         Doogh           0000h         Prot           0000h         Data           0000h         Data           0000h         Data           0000h         Osci           0000h         Osci           0000h         Prog           0000h         Prog           0000h         Prog           0010h         Prog           0011h         Oo12h           0013h         Oo14h                                                                                                                                                                             | eessor Mode Register 0<br>eessor Mode Register 1<br>tem Clock Control Register 0<br>tem Clock Control Register 1<br>o Select Control Register<br>ect Register<br>a Bank Register<br>illation Stop Detection Register | PM0<br>PM1<br>CM0<br>CM1<br>CSR<br>PRCR<br>DBR<br>CM2 | 48<br>49<br>76<br>77<br>55<br>98<br>67<br>78 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------|

| 0002h         0003h           0003h         Proc           0004h         Proc           0005h         Proc           0006h         Syst           0007h         Syst           0008h         Chip           0009h         Prot           0009h         Prot           0000h         Data           0000h         Osci           0000h         Prot           0001h         Prot           0011h         Port           0013h         Port           0014h         Port | essor Mode Register 1<br>tem Clock Control Register 0<br>tem Clock Control Register 1<br>o Select Control Register<br>ect Register<br>a Bank Register<br>illation Stop Detection Register                            | PM1<br>CM0<br>CM1<br>CSR<br>PRCR<br>DBR               | 49<br>76<br>77<br>55<br>98<br>67             |

| 0003h         0004h           0004h         Proc           0005h         Proc           0006h         Syst           0007h         Syst           0008h         Chip           0009h         Prot           0009h         Prot           0000h         Data           0000h         Data           0000h         Osci           0000h         Prot           0000h         Prot           0000h         Prot           0000h         Prot           0000h         Prot           0001h         Prot           0011h         Port           0013h         Peri           0014h         Peri                                                                                        | essor Mode Register 1<br>tem Clock Control Register 0<br>tem Clock Control Register 1<br>o Select Control Register<br>ect Register<br>a Bank Register<br>illation Stop Detection Register                            | PM1<br>CM0<br>CM1<br>CSR<br>PRCR<br>DBR               | 49<br>76<br>77<br>55<br>98<br>67             |

| 0004h         Proc           0005h         Proc           0006h         Syst           0007h         Syst           0008h         Chip           0009h         Prot           0009h         Prot           0009h         Data           0000h         Data           0000h         Osci           0000h         Prot           0000h         Prot           0000h         Prot           0000h         Prot           0000h         Prot           0001h         Prot           0011h         Port           0013h         Peri           0014h         Peri                                                                                                                      | essor Mode Register 1<br>tem Clock Control Register 0<br>tem Clock Control Register 1<br>o Select Control Register<br>ect Register<br>a Bank Register<br>illation Stop Detection Register                            | PM1<br>CM0<br>CM1<br>CSR<br>PRCR<br>DBR               | 49<br>76<br>77<br>55<br>98<br>67             |

| 0005h         Proc           0006h         Syst           0007h         Syst           0008h         Chip           0009h         Prot           0000h         Prot           0000h         Data           0000h         Data           0000h         Osci           0000h         Osci           0000h         Prog           0000h         Prog           0000h         Prog           0010h         Prog           0011h         Pori           0013h         Outah                                                                                                                                                                                                            | essor Mode Register 1<br>tem Clock Control Register 0<br>tem Clock Control Register 1<br>o Select Control Register<br>ect Register<br>a Bank Register<br>illation Stop Detection Register                            | PM1<br>CM0<br>CM1<br>CSR<br>PRCR<br>DBR               | 49<br>76<br>77<br>55<br>98<br>67             |

| 0006h         Syst           0007h         Syst           0008h         Chip           0009h         0           0008h         Prot           0008h         Data           0008h         Post           0008h         Prog           0010h         Prog           0011h         Port           0012h         Perin           0013h         Out4h                                                                                          | tem Clock Control Register 0<br>tem Clock Control Register 1<br>o Select Control Register<br>ect Register<br>a Bank Register<br>illation Stop Detection Register                                                     | CM0<br>CM1<br>CSR<br>PRCR<br>DBR                      | 76<br>77<br>55<br>98<br>67                   |

| 0007h         Syst           0008h         Chip           0009h         0           000Ah         Prot           000Bh         Data           000Ch         Osci           000Dh         0           000Dh         0           000Dh         0           000Fh         0           0010h         Prog           0011h         0           0012h         Perij           0013h         0                                                                                                                                                                                                                                                                                           | tem Clock Control Register 1<br>o Select Control Register<br>ect Register<br>a Bank Register<br>illation Stop Detection Register                                                                                     | CM1<br>CSR<br>PRCR<br>DBR                             | 77<br>55<br>98<br>67                         |

| O008h         Chip           0008h         Chip           0009h         Prot           0008h         Data           0008h         Data           0000h         Osci           0000h         Osci           0000h         Osci           0000h         Prog           0000h         Prog           0010h         Prog           0011h         Poriji           0012h         Periji           0013h         Out4h                                                                                                                                                                                                                                                                  | o Select Control Register<br>ect Register<br>a Bank Register<br>illation Stop Detection Register                                                                                                                     | CSR<br>PRCR<br>DBR                                    | 55<br>98<br>67                               |

| 0009h           000Ah         Prot           000Bh         Data           000Ch         Osci           000Dh         0           000Eh         0           000Fh         0           0010h         Prog           0011h         0           0012h         Perij           0013h         0                                                                                                                                                                                                                                                                                                                                                                                         | ect Register<br>a Bank Register<br>illation Stop Detection Register                                                                                                                                                  | PRCR<br>DBR                                           | 98<br>67                                     |

| 000Ah         Prot           000Bh         Data           000Ch         Osci           000Dh         -           000Eh         -           000Fh         -           0010h         Prog           0011h         -           0012h         Perin           0013h         -                                                                                                                                                                                                                                                                                                                                                                                                         | a Bank Register                                                                                                                                                                                                      | DBR                                                   | 67                                           |

| 000Bh         Data           000Ch         Osc           000Dh         0           000Eh         0           000Fh         0           0010h         Prog           0011h         0           0012h         Perij           0013h         0                                                                                                                                                                                                                                                                                                                                                                                                                                       | a Bank Register                                                                                                                                                                                                      | DBR                                                   | 67                                           |

| 000Ch         Osci           000Dh         000Eh           000Fh         000Fh           0010h         Prog           0011h         0012h           0012h         Perij           0013h         0014h                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | illation Stop Detection Register                                                                                                                                                                                     |                                                       | -                                            |

| 000Dh         000Eh           000Fh         000Fh           0010h         Prog           0011h         0012h           0013h         0014h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                      | CM2                                                   | 78                                           |

| 000Eh         000Fh           000Fh         Prog           0010h         Prog           0011h         0012h           0013h         0014h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | rum 0 Arco Control Docistor                                                                                                                                                                                          |                                                       |                                              |

| 000Fh         Prog           0010h         Prog           0011h         0012h           0013h         0014h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nom 2 Area Castral Deviator                                                                                                                                                                                          |                                                       |                                              |

| 0010h         Prog           0011h            0012h         Perij           0013h            0014h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | num 2 Augo Control Deviator                                                                                                                                                                                          |                                                       |                                              |

| 0011h Perij<br>0012h Perij<br>0013h 0014h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ware 2 Area Cantral Decister                                                                                                                                                                                         |                                                       |                                              |

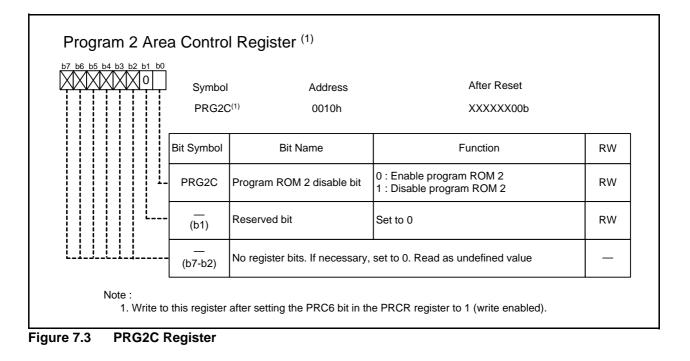

| 0012h Peri<br>0013h<br>0014h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | gram 2 Area Control Register                                                                                                                                                                                         | PRG2C                                                 | 50                                           |

| 0013h<br>0014h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |                                                       |                                              |

| 0014h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | pheral Clock Select Register                                                                                                                                                                                         | PCLKR                                                 | 79                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                      |                                                       |                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                      |                                                       |                                              |

| 0015h Cloc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | k Prescaler Reset Flag                                                                                                                                                                                               | CPSRF                                                 | 142                                          |

| 0016h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                      |                                                       |                                              |

| 0017h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                      |                                                       |                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | et Source Determine Flag                                                                                                                                                                                             | RSTFR                                                 | 46                                           |

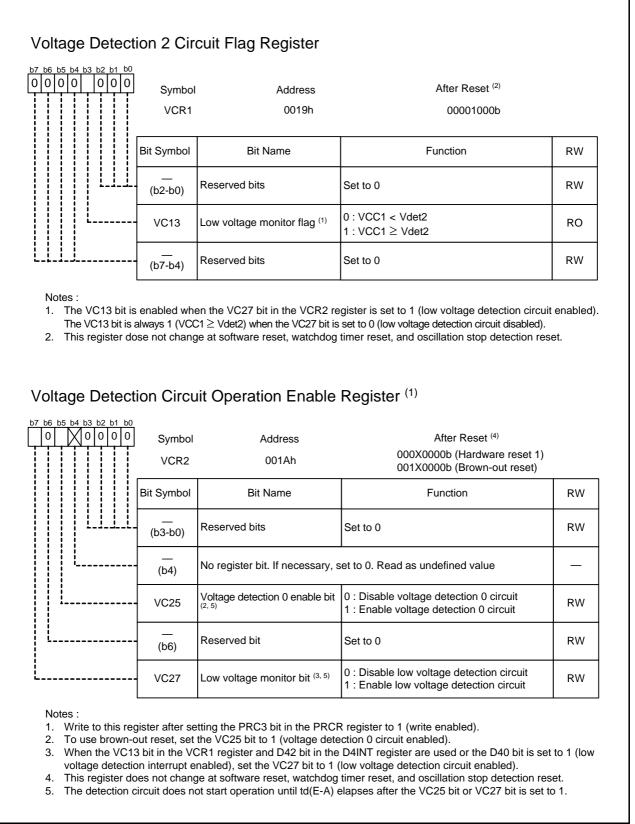

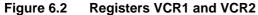

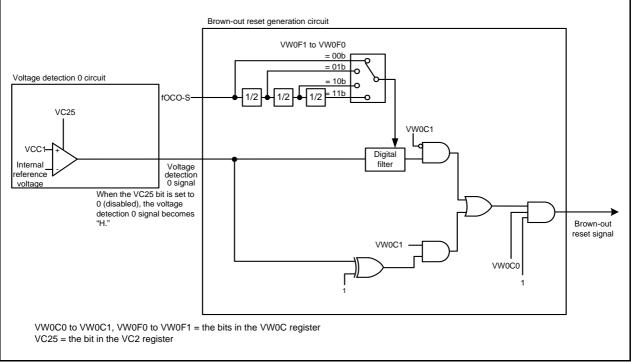

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | age Detection 2 Circuit Flag Register                                                                                                                                                                                | VCR1                                                  | 38                                           |

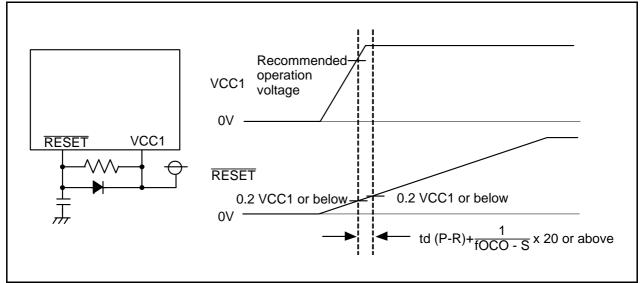

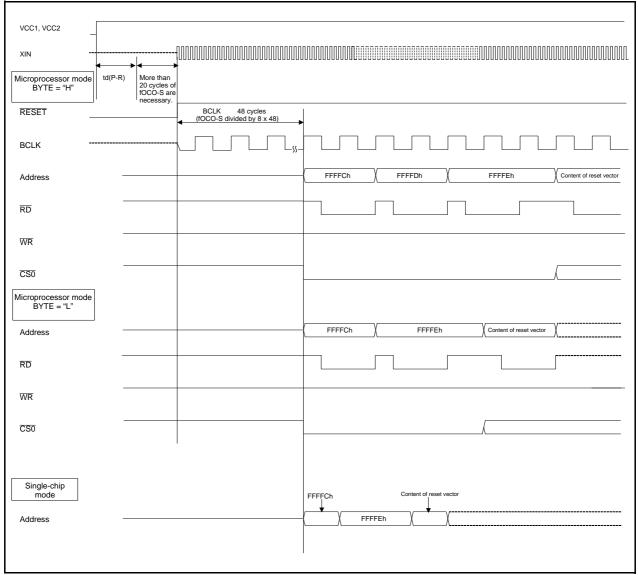

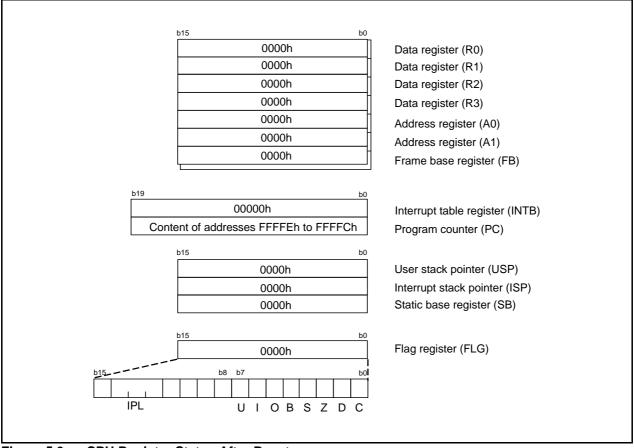

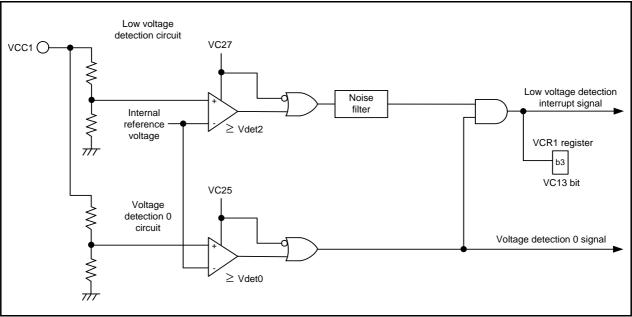

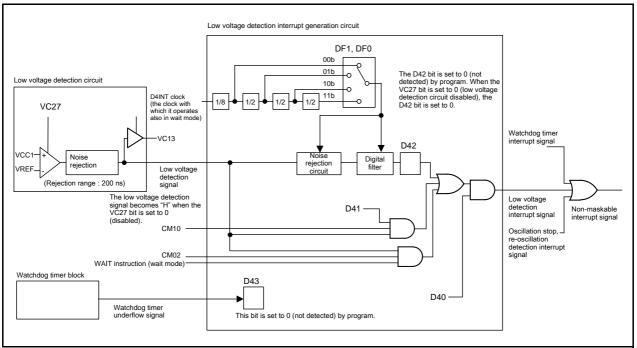

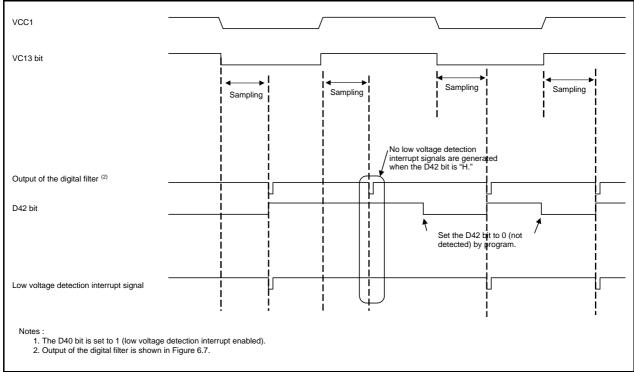

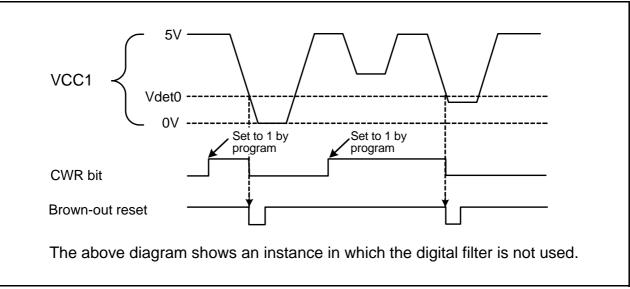

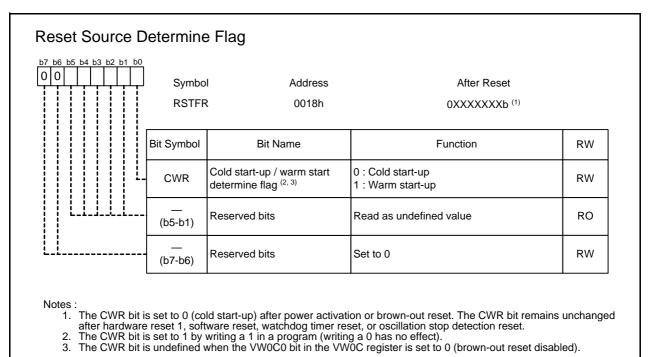

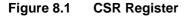

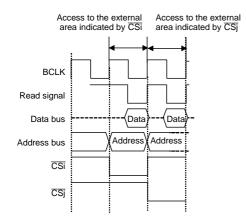

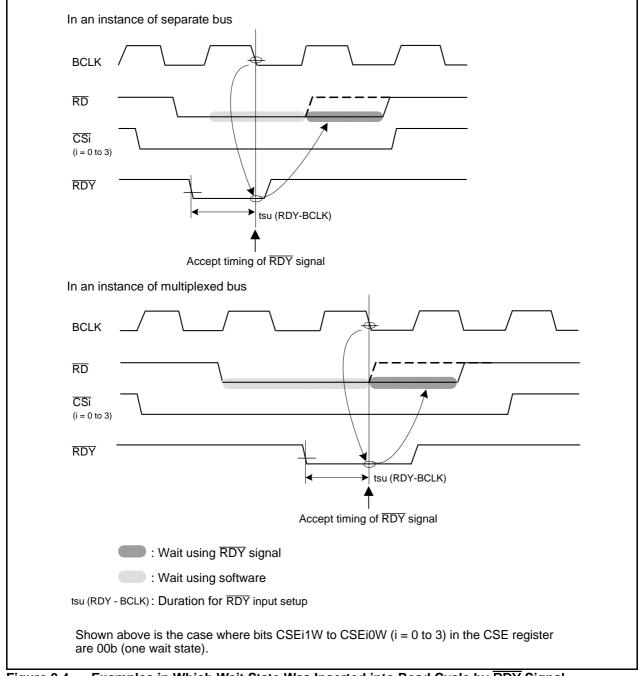

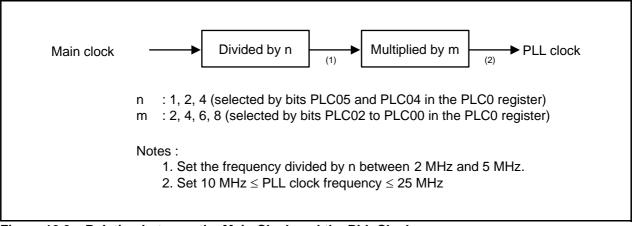

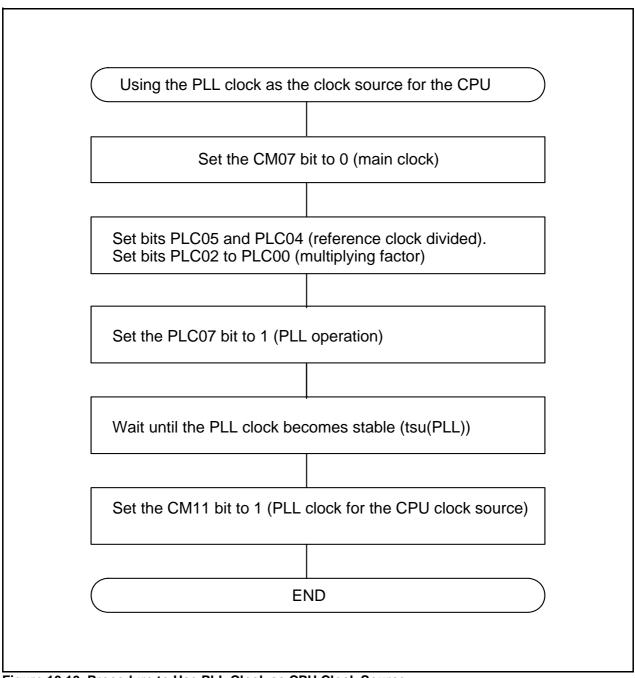

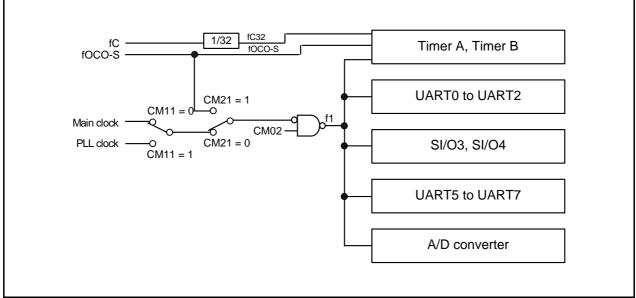

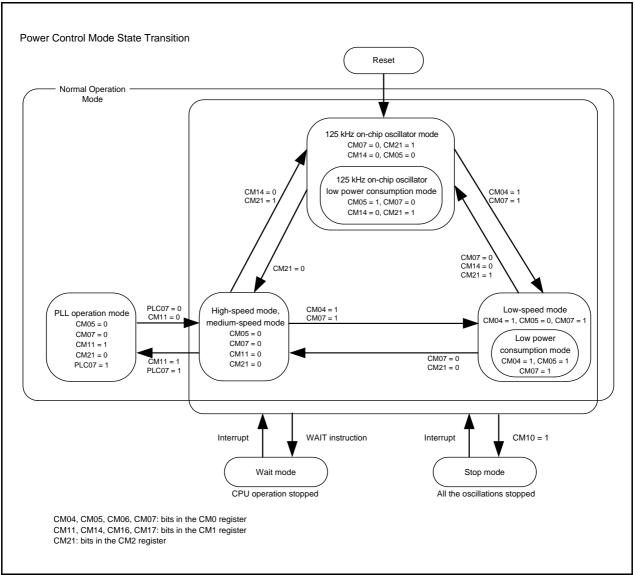

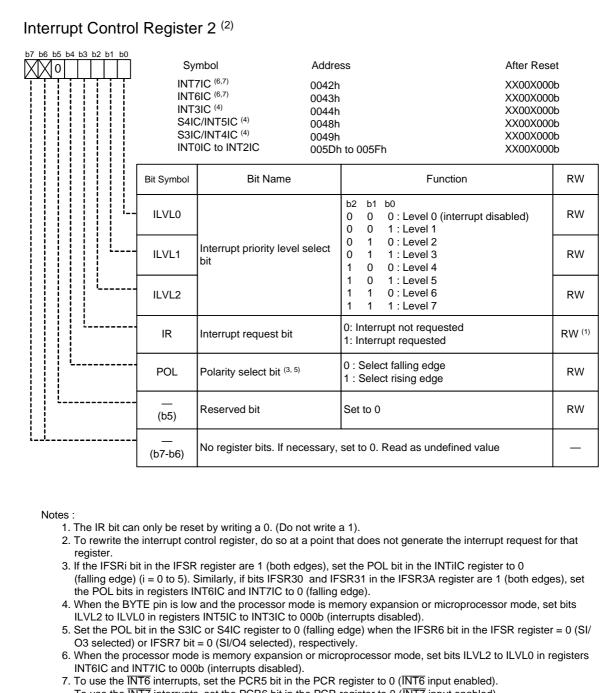

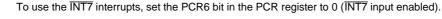

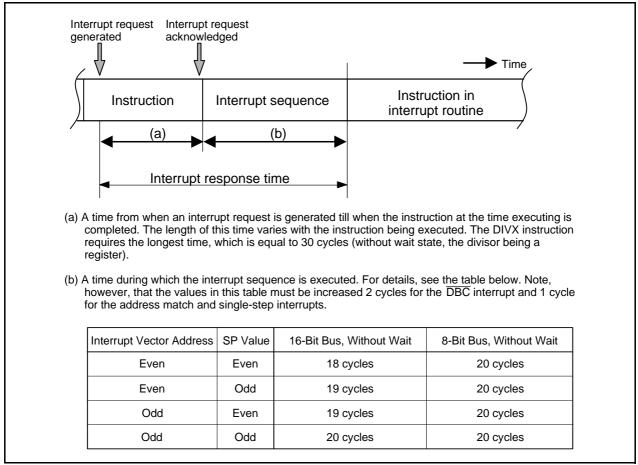

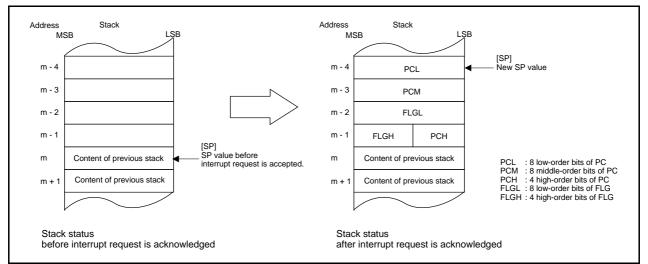

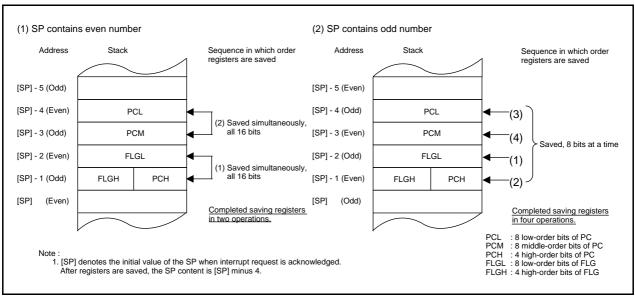

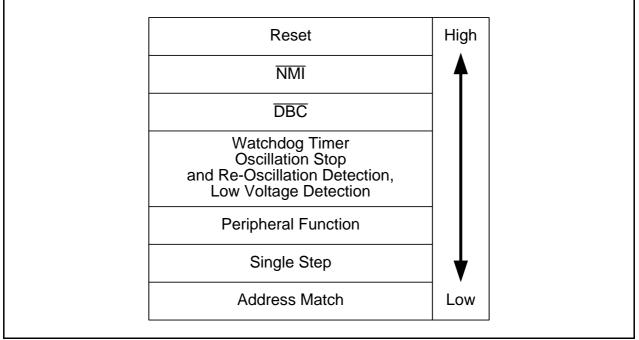

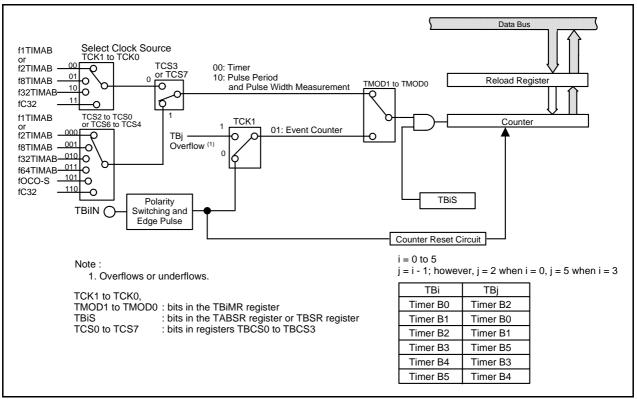

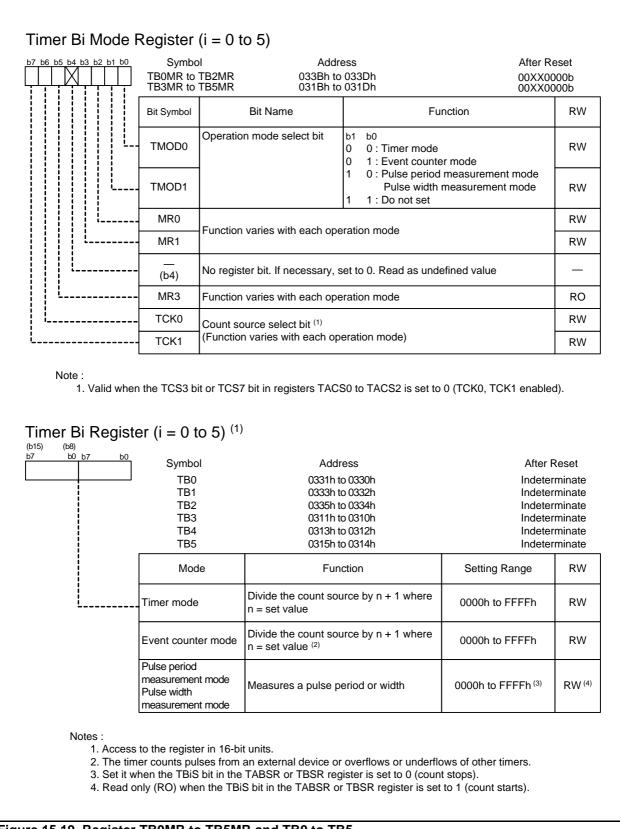

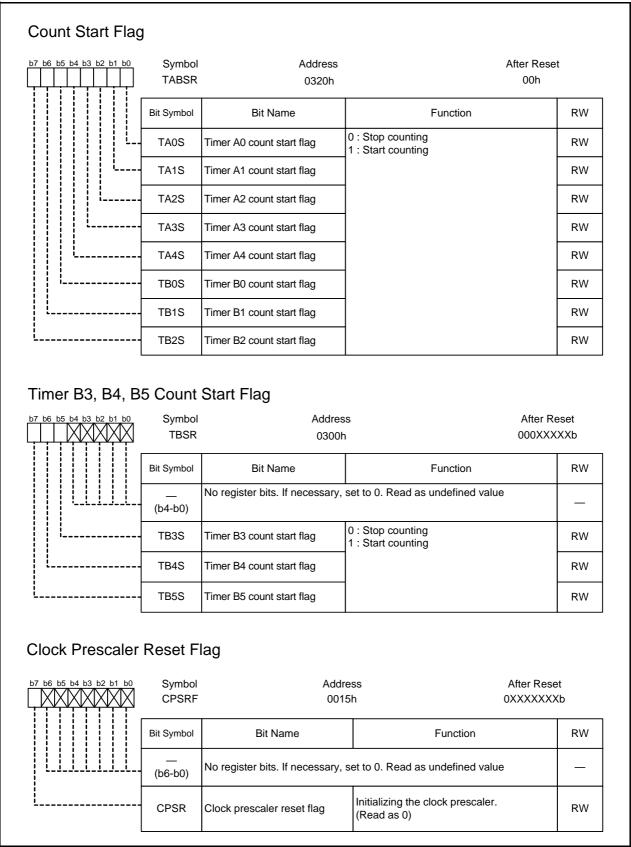

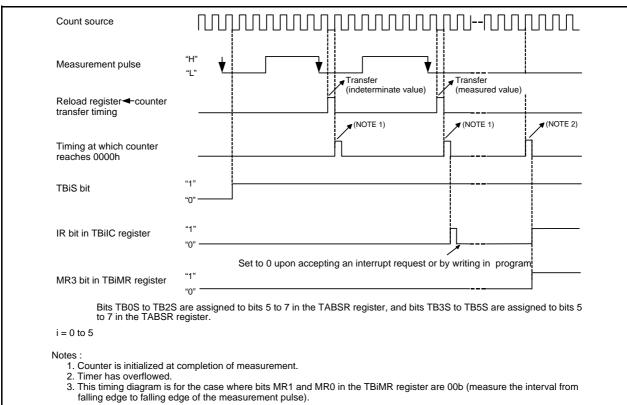

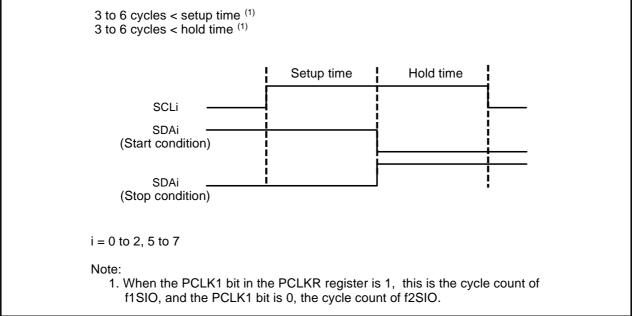

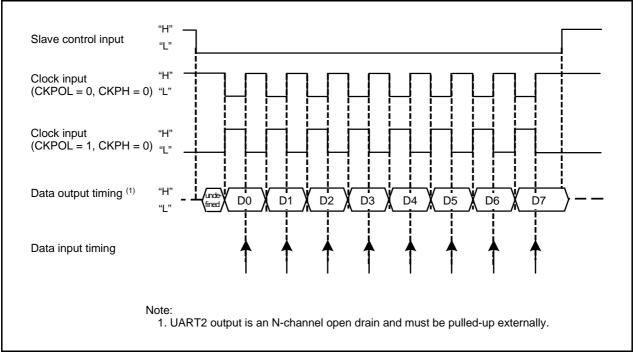

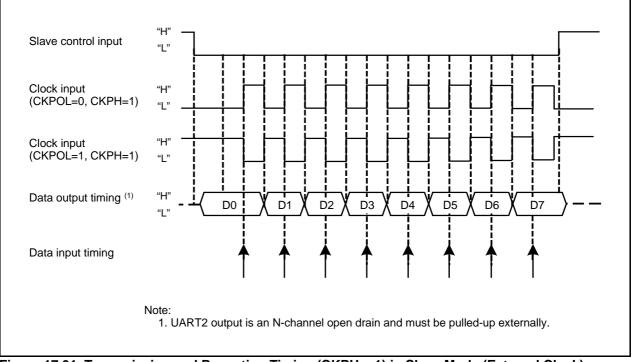

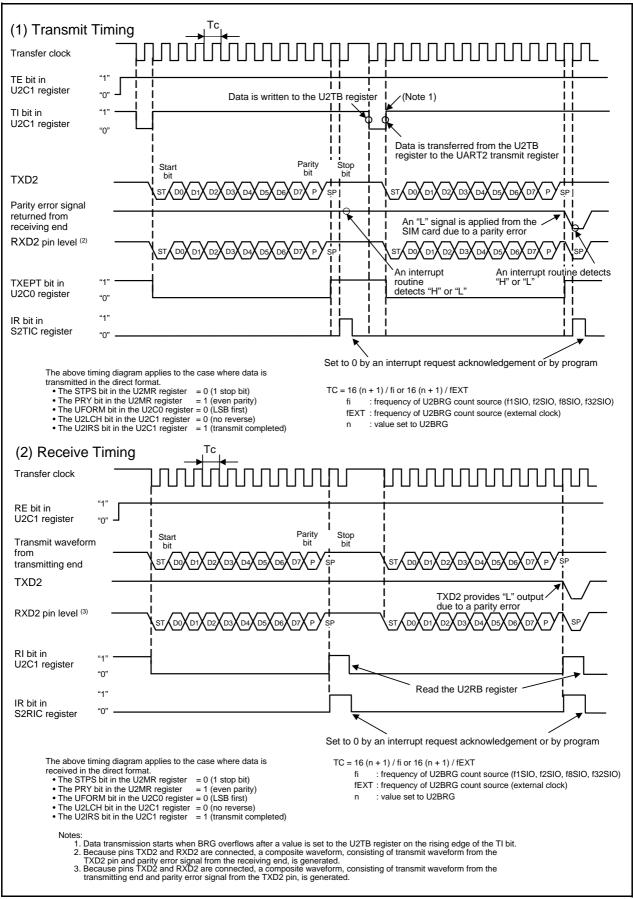

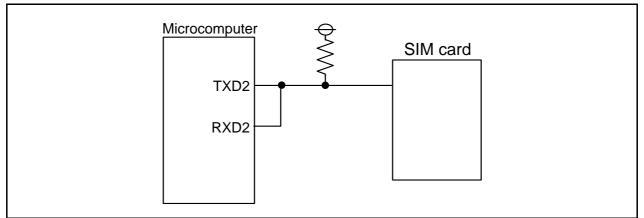

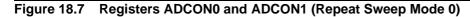

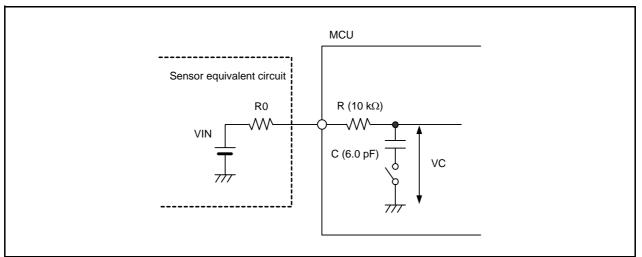

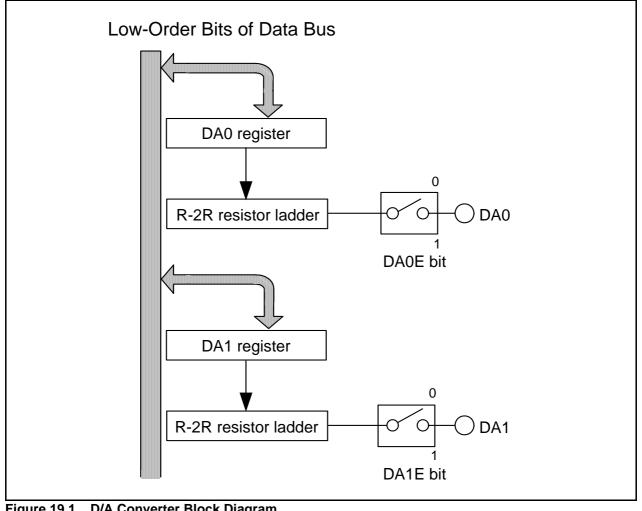

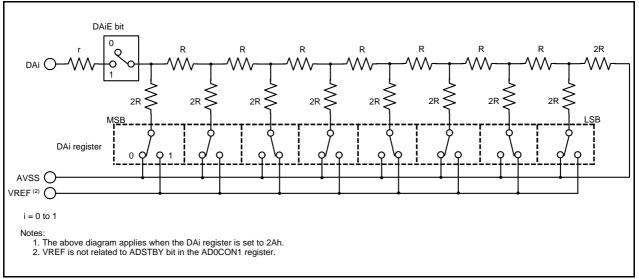

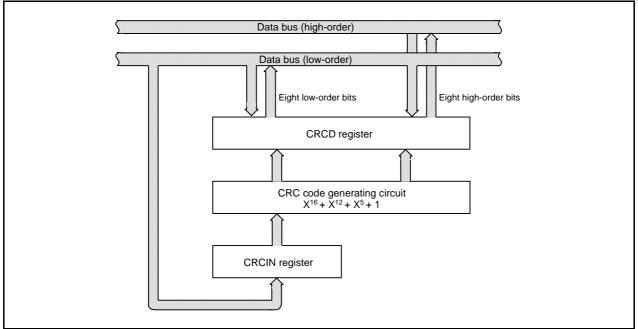

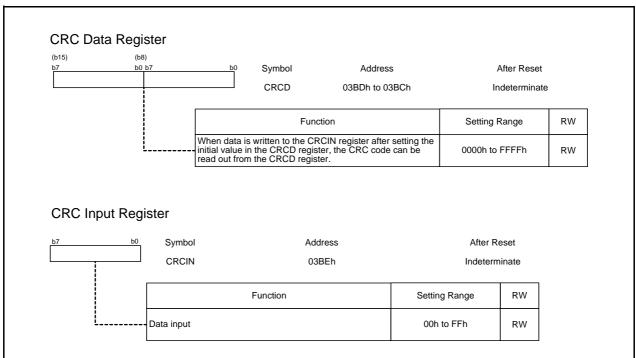

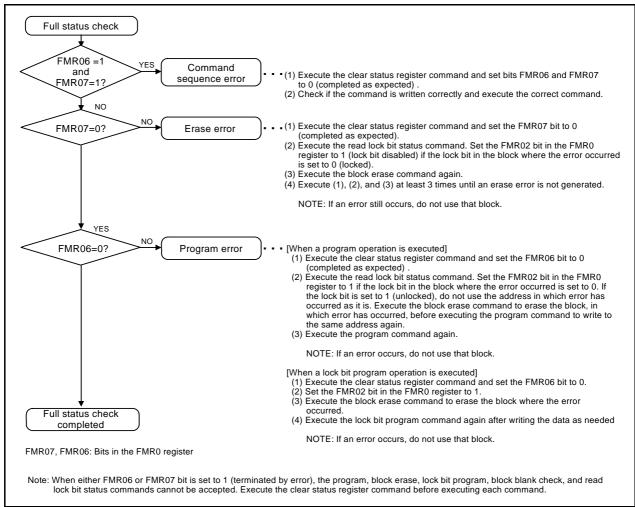

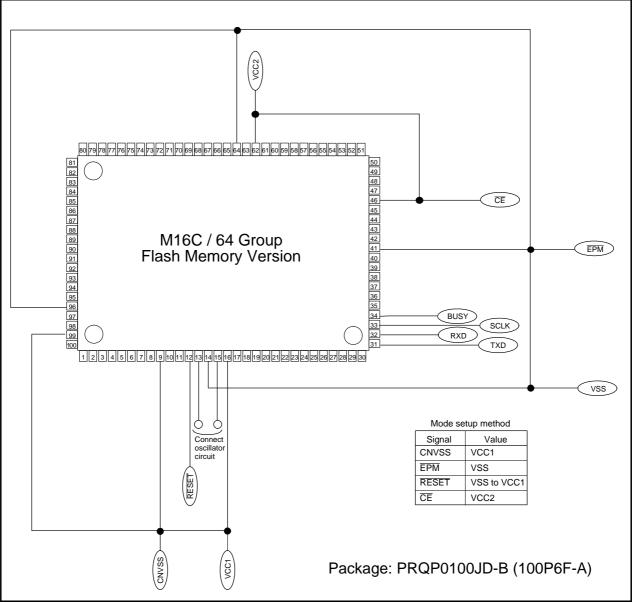

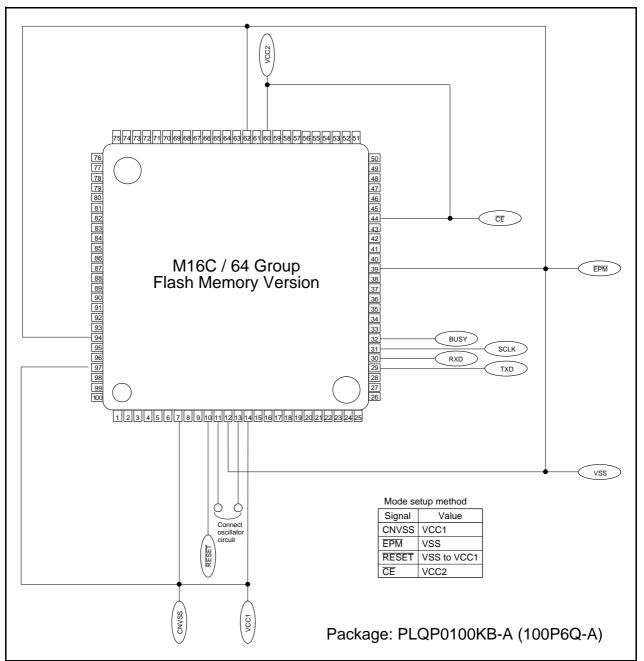

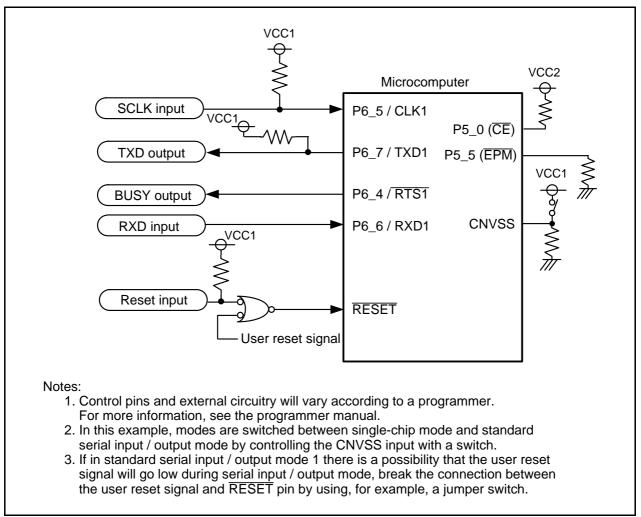

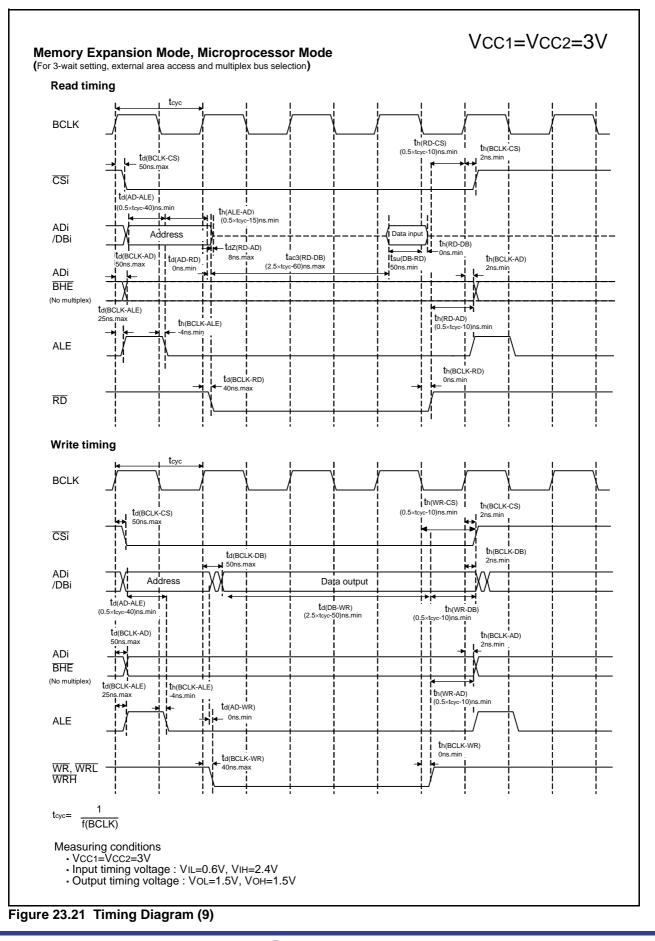

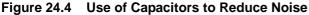

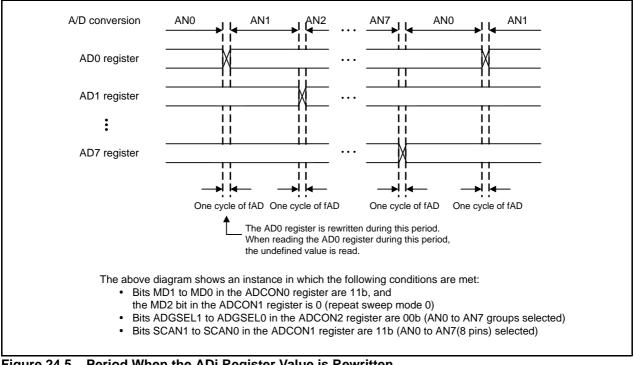

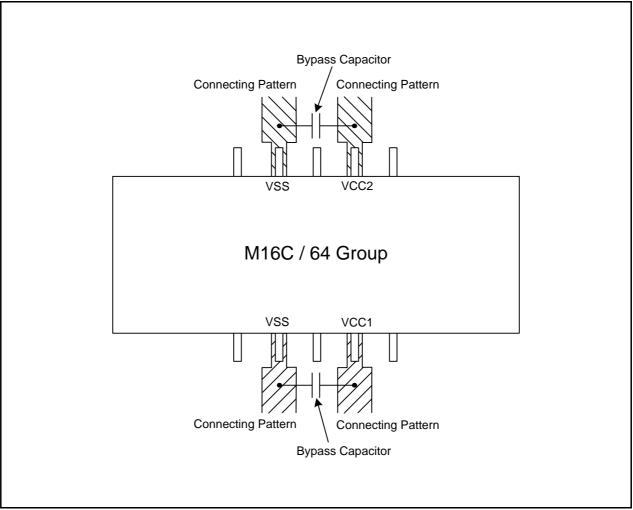

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | age Detection Circuit Operation Enable                                                                                                                                                                               | VCR2                                                  | 38                                           |