# RENESAS

# RE01 Group Products with 1.5-Mbyte Flash Memory

# **Renesas Microcomputers**

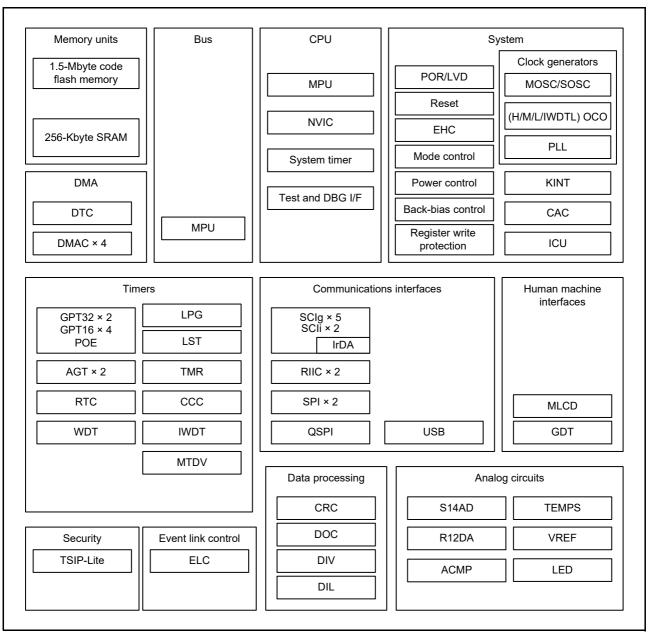

64 MHz, 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M0+, 1.5-Mbyte flash memory supporting background operation, 256-Kbyte SRAM, energy harvesting control circuit, MIP LCD controller, 2D graphic engine,

14-bit ultra-low power A/D converter, reference voltage generation circuit, RTC, sub-clock correction circuit (theoretical regulation), security function (optional), USB 2.0 full-speed module, SPI, quad SPI

# Features

### ■ Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ core incorporated

- Maximum operating frequency: 64 MHz (boost mode)

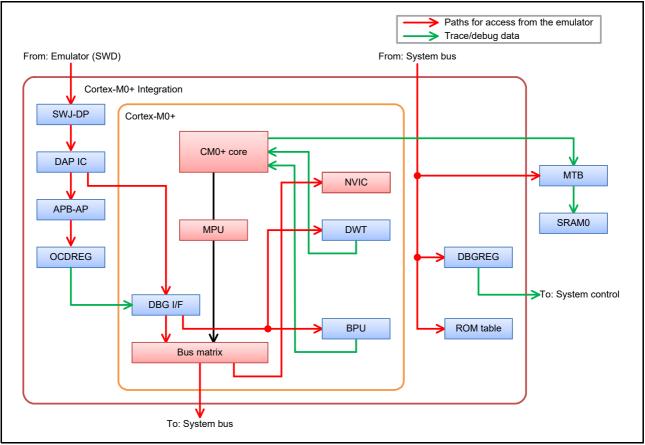

- ARM<sup>®</sup> Memory Protection Unit (MPU)

CoreSight<sup>™</sup> debug port: SW-DP

### Power-saving functions

- Back-bias control function based on silicon-on-thin-buried-oxide (SOTB<sup>TM</sup>) process technology

Operation at ultra-low power-supply voltages (from 1.62 V to 3.6 V)

- Four power control modes based on the operating frequency Four low power consumption modes

- Three power supply mode.

### On-chip code flash memory

- 1.5-Mbyte code flash memory

- No cycles of waiting for access in operation at or below 32 MHz;

- one cycle of waiting at frequencies above 32 MHz · Function for area protection prevents erroneous overwriting or tampering

# On-chip SRAM

· 256-Kbyte SRAM with no access wait cycles

### Data transfer

- Four DMA controllers

- Single data transfer controller (DTC)

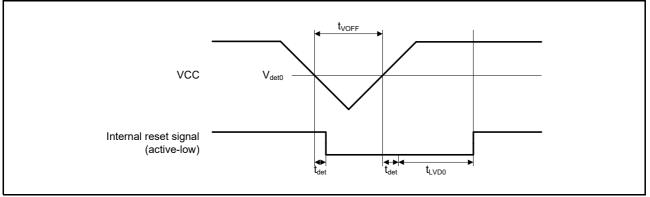

### Reset and supply management

- Power-on reset circuit (POR)

- Low voltage detection (LVD) can be set.

### Multiple clock sources

- External crystal oscillator (main clock): 8 to 32 MHz

- External crystal oscillator (sub-clock): 32.768 kHz High-speed on-chip oscillator (HOCO): 24, 32, 48, or 64 MHz Middle-speed on-chip oscillator (MOCO): 2 MHz

- Low-speed on-chip oscillator (LOCO): 32 kHz Independent watchdog timer on-chip oscillator: 16 kHz

- PLL frequency synthesizer

## Energy harvesting control

- A power generation element is directly connectable.

- · High-speed startup is possible without having to wait for the charging of a secondary battery.

- · Function to prevent a secondary battery from overcharging

### Independent watchdog timer

• 14-bit counter, 16-kHz (1/2 LOCO clock frequency) operation

### Sub-clock correction circuit (CCC)

- · The CCC corrects the accuracy of oscillation every 16 seconds

- (theoretical regulation). · Events can be generated per second in deep software standby mode.

### Communication functions

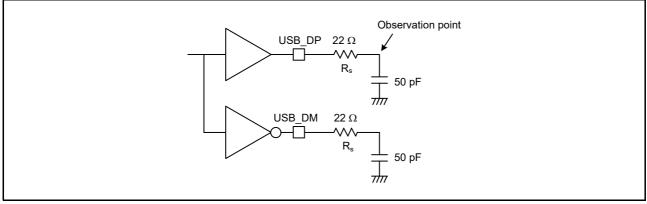

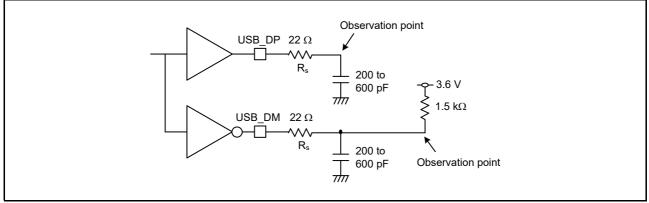

- · Single USB 2.0 full-speed host/function module with PHY layer

- Two serial peripheral interfaces Single 128-bit buffer for which up to eight commands can be specified Single 32-bit buffer for which one command can be specified

- Single quad serial peripheral interface connectable to an external flash memory Two I<sup>2</sup>C bus interfaces

- Five serial communications interfaces (SCIg) Asynchronous, clock-synchronous, simple I<sup>2</sup>C, simple SPI, and smart card interfaces, and IrDA interface version 1.0 (the latter is only

- applicable to SCI0) Two serial communication interfaces (SCIi) each having a 16-byte FIFO

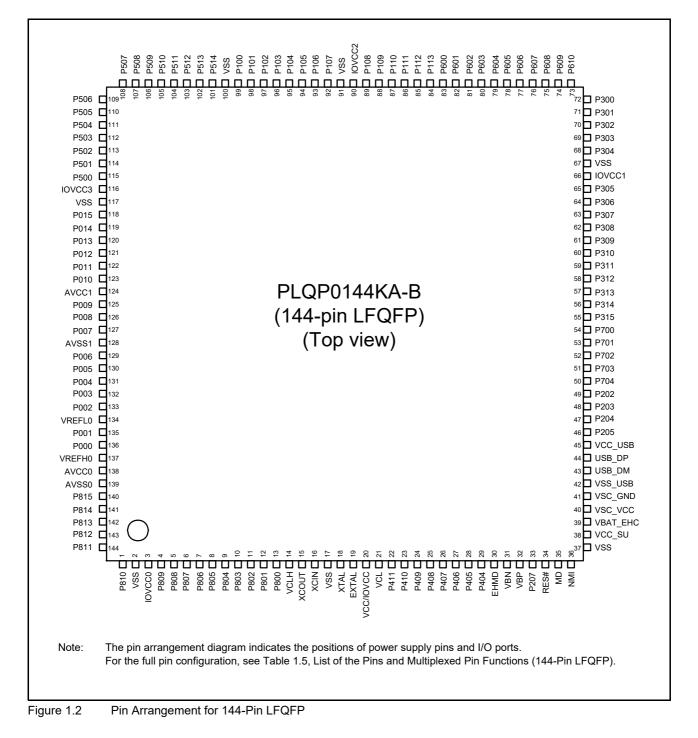

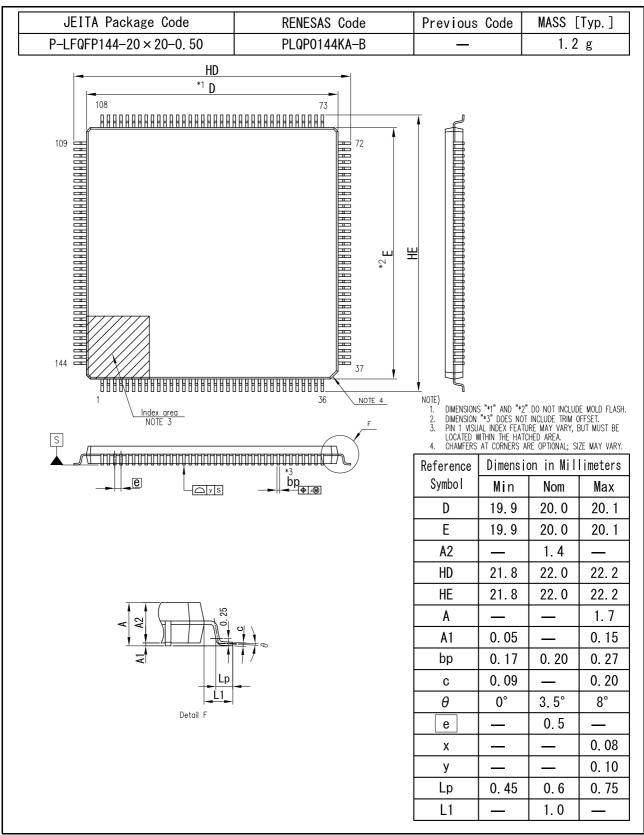

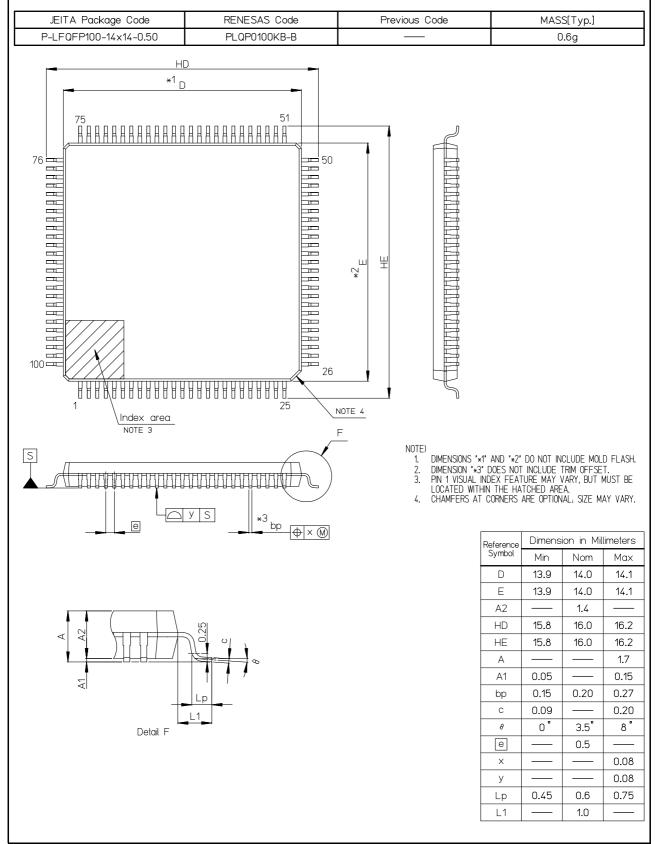

PLQP0144KA-B 20 × 20 mm, 0.5-mm pitch PLQP0100KB-B

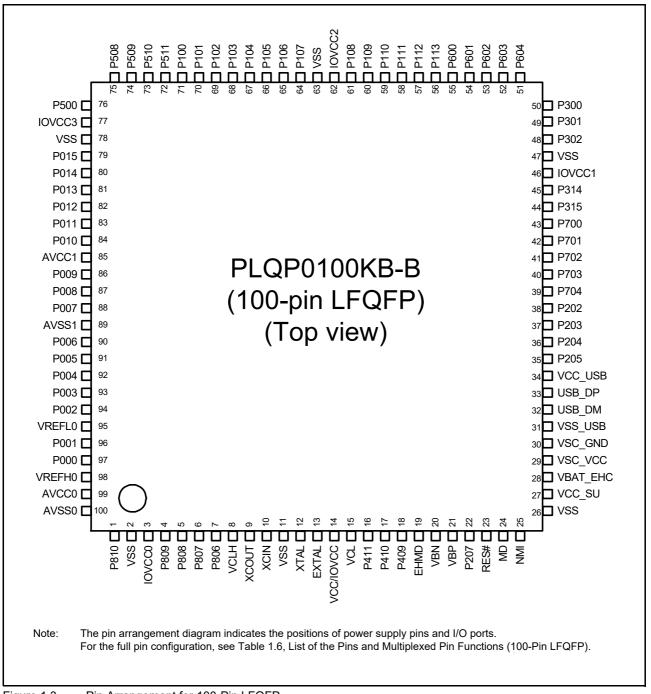

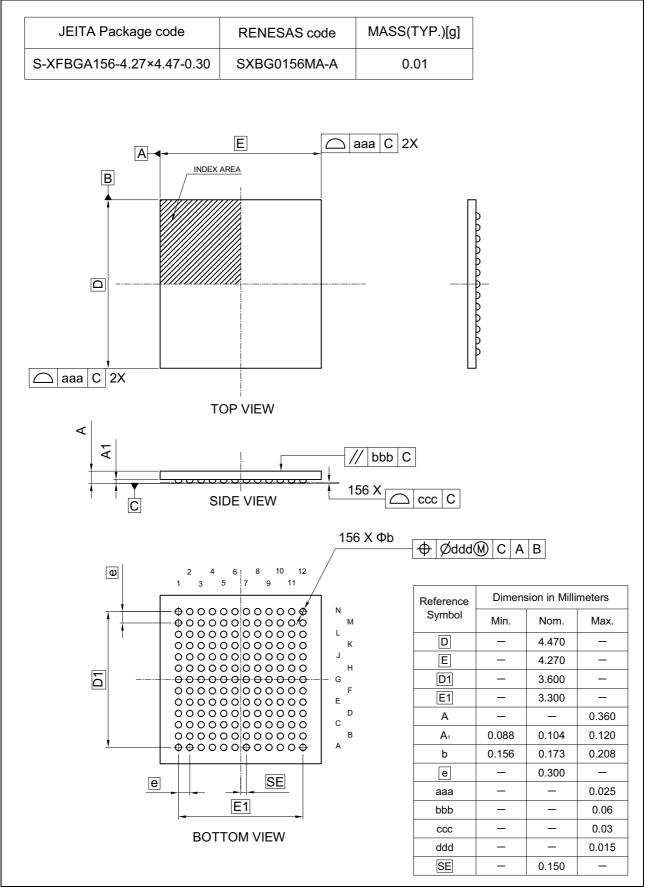

4.5 × 4.3 mm, 0.3-mm pitch

### Various analog circuits

- Single 14-bit successive approximation A/D converter

- High precision: 7 channels, standard precision: 11 channels Single 12-bit D/A converter with a buffer amplifier

- Single analog comparator (ACMP)

- · Single temperature sensor for measuring the internal temperature of the chip

- Reference voltage generation circuit for the 14-bit A/D converter

- Single motor driver control circuit (MTDV) The MTDV can drive up to three motors.

Single constant current (1 mA or 0.5 mA) source circuit with three channels that can drive three external LEDs

- Two asynchronous general-purpose timers (AGT) that can be used in standby mode

- Two 8-bit timers (TMR)

- Single realtime clock (RTC)

- Single watchdog timer (WDT) Single low-speed timer (LST) that operates at 1 kHz A circuit for converting hexadecimal numbers to decimal numbers for

- Single low-speed pulse generator (LPG) Pulse output at two frequencies (2.048 or 4.096 kHz) is possible.

### Human machine interfaces

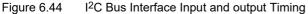

- Single memory-in-pixel (MIP) LCD controller (MLCD)

- Parallel interface is supported.Single 2D graphics data conversion circuit (GDT)

### Security functions (optional)

- Single Trusted Secure IP Lite (TSIP-Lite)

- AES (128- or 256-bit key length, supporting ECB, CBC, CMAC, GCM, and others)

- Key wrapping protects against the leakage of the encryption keys of users.

- An access management circuit disables illicit access to the encryption engine.

- Using the other security functions together with area protection enables secure booting and secure over-the-air (OTA) software updates

### Operating voltage and temperature range

- VCC = IOVCC = 1.62 V to 3.6 V IOVCCn and AVCCn can each be independently set to a voltage within the range between 1.62 V and 3.6 V.  $T_a$ : -40 to +85°C

Datasheet

R01DS0363EJ0110

Rev.1.10

May 29, 2020

use as a stopwatch

### Various timer circuits • Six general PWM timers (GPT) Two 32-bit counters Four 16-bit counters

# 1. Overview

# 1.1 Outline of Specifications

Table 1.1 shows the specifications in outline.

The specifications in the table are the maximum specifications, and the number of peripheral modules and channels in some cases depends on the number of pins of the package. For details, see Table 1.3, Function Comparison.

Table 1.1Outline of Specifications (1/10)

| Classification | Feature                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|----------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CPU            | Central processing unit | <ul> <li>Maximum operating frequency: 64 MHz</li> <li>Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ <ul> <li>Revision: r0p1-00rel0</li> <li>Arm<sup>®</sup>v6-M architecture profile</li> <li>Single-cycle integer multiplier</li> </ul> </li> <li>Arm<sup>®</sup> Memory Protection Units (MPUs) <ul> <li>Arm<sup>®</sup>v6 Protected Memory System Architecture</li> <li>Eight protected memory areas</li> </ul> </li> <li>SysTick timer <ul> <li>Driven by SYSTICCLK (LOCO clock) or ICLK</li> </ul> </li> </ul>                                              |  |  |  |  |

| Memory         | Code flash memory       | <ul> <li>Maximum 1.5 Mbytes</li> <li>No cycles of waiting for access in operation at or below 32 MHz;<br/>one cycle of waiting at frequencies above 32 MHz</li> <li>Prefetch function</li> <li>On-board programming (four types): <ul> <li>Programming in serial programming mode (SCI boot mode)</li> <li>Programming in serial programming mode (USB boot mode)</li> <li>Programming in on-chip debug mode</li> <li>Programming by a routine for code flash memory programming within a user program</li> </ul> </li> </ul>                             |  |  |  |  |

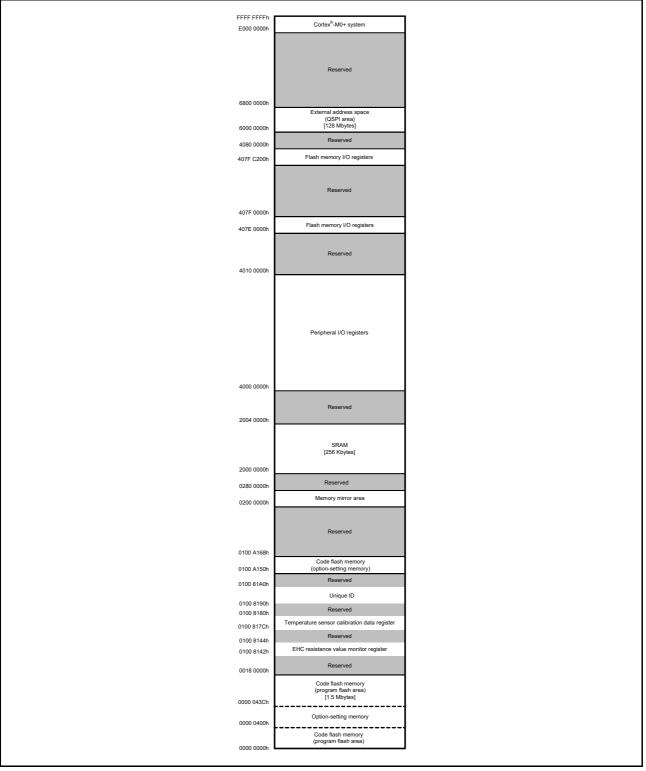

|                | SRAM                    | <ul> <li>Maximum 256 Kbytes<br/>SRAM0: 2000 0000h to 2000 7FFFh<br/>SRAM1: 2000 8000h to 2003 FFFFh<br/>Both areas are available during low leakage current mode.</li> <li>64 MHz, No cycles of waiting for access</li> </ul>                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

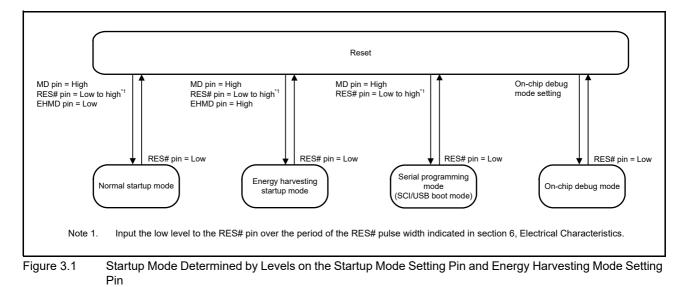

| Startup modes  |                         | Three startup modes:<br>• Normal startup mode<br>• Energy harvesting startup mode<br>• SCI/USB boot mode                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

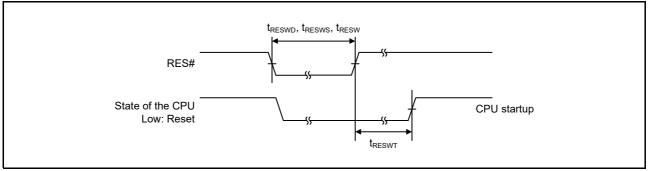

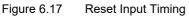

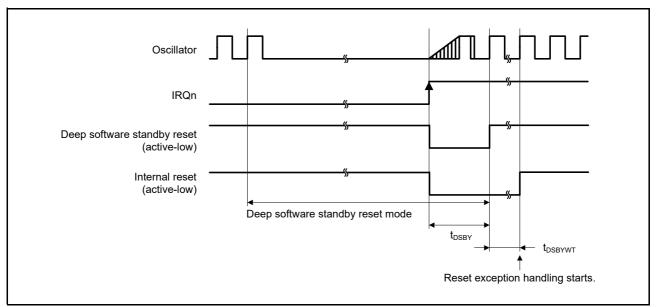

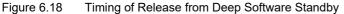

| Reset          |                         | The LSI chip supports 12 system resets and one power shutdown reset.<br>[System resets]<br>• RES# pin reset<br>• Power-on reset<br>• Independent watchdog timer reset<br>• Watchdog timer reset<br>• Voltage monitor 0 reset<br>• Voltage monitor 1 reset<br>• Voltage monitor 1 reset<br>• Voltage monitor BAT reset<br>• Bus master MPU error reset<br>• Bus slave MPU error reset<br>• Stack pointer error reset<br>• Stack pointer error reset<br>• Software reset<br>• Deep software standby reset<br>[Power shutdown reset]<br>• MINPWON mode reset |  |  |  |  |

| Classification      | Feature | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|---------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

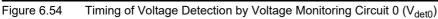

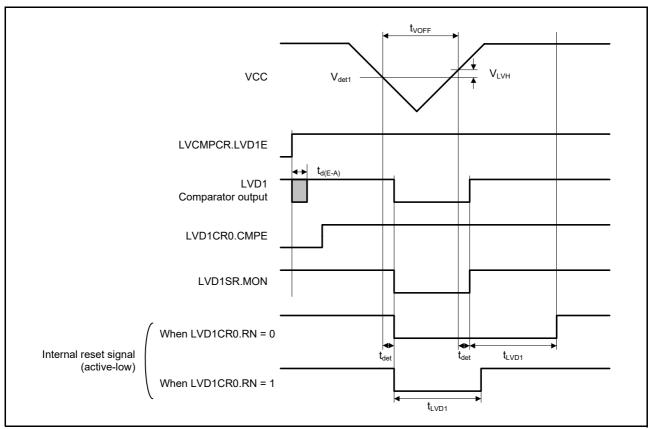

| Low-voltage detecti |         | <ul> <li>The low-voltage detection circuits (LVD) monitors the voltage level input to the VCC pin or VBAT_EHC pin. The detection level can be selected using a program.</li> <li>Voltage detection circuit 0 <ul> <li>Target for monitoring: VCC pin</li> <li>Capable of generating an internal reset</li> <li>The option-setting memory can be used to enable or disable the low-voltage detection circuit.</li> <li>Selectable from four different voltage detection levels (1.67 V, 1.92 V, 2.17 V, and 2.42 V)</li> </ul> </li> <li>Voltage detection circuit 1 <ul> <li>Target for monitoring: VCC pin</li> <li>The register setting can be used to enable or disable the low-voltage detection circuit.</li> </ul> </li> <li>Selectable from eight different voltage detection levels (1.67 V, 1.92 V, 2.17 V, and 2.42 V)</li> <li>Voltage detection circuit 1 <ul> <li>Target for monitoring: VCC pin</li> <li>The register setting can be used to enable or disable the low-voltage detection circuit.</li> </ul> </li> <li>Selectable from eight different voltage detection levels (1.67 V, 1.84 V, 2.00 V, 2.17 V, 2.33 V, 2.50 V, 2.66 V, and 2.83 V)</li> <li>Digital filtering is available (1/2, 1/4, 1/8, and 1/16 LOCO frequency).</li> <li>Detection of voltage rising above and falling below thresholds is selectable.</li> <li>Capable of generating an internal reset</li> <li>Two types of timing are selectable for release from reset.</li> <li>An internal interrupt can be requested.</li> <li>Voltage detection circuit BAT</li> <li>Target for monitoring: VBAT_EHC pin</li> <li>The register setting can be used to enable or disable the low-voltage detection circuit.</li> <li>Selectable from five different voltage detection levels (1.67 V, 1.84 V, 2.00 V, 2.17 V, and 2.33 V)</li> <li>Digital filtering is available.</li> </ul> <li>Voltage detection circuit BAT</li> <li>Target for monitoring: VBAT_EHC pin</li> <li>The register setting can be used to enable or disable the low-voltage detection circuit.</li> <li>Selectable from five different voltage detection lev</li> |  |  |  |

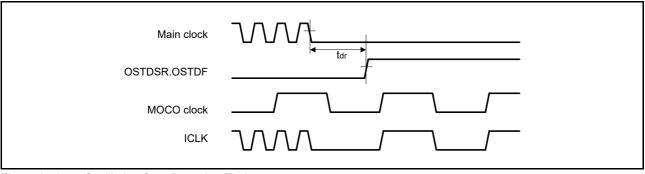

| Clock               |         | <ul> <li>The LSI chip has the following clock generation circuits.</li> <li>Main clock oscillator (MOSC)</li> <li>Sub-clock oscillator (SOSC)</li> <li>High-speed on-chip oscillator (HOCO)</li> <li>Middle-speed on-chip oscillator (MOCO)</li> <li>Low-speed on-chip oscillator (LOCO)</li> <li>PLL frequency synthesizer</li> <li>IWDT-dedicated on-chip oscillator (IWDTLOCO)</li> <li>Clock output support</li> <li>CLKOUT pin (capable of the output of all types of clock signals)</li> <li>CLKOUT32K pin (capable of the output of the SOSC clock signal)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

Table 1.1Outline of Specifications (2/10)

| Classification                                            | Feature                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-----------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Clock frequency a<br>circuit (CAC)                        | accuracy measurement                                    | The CAC checks the system clock frequency with a reference clock signal by counting<br>the number of pulses of the system clock to be measured. Event signals can be<br>generated when the frequency does not match or measurement ends. This function is<br>particularly useful in implementing a fail-safe mechanism for home and industrial<br>automation applications.<br>• Target clocks for measurement<br>- Main clock<br>- Sub-clock<br>- HOCO clock<br>- HOCO clock<br>- LOCO clock<br>- LOCO clock<br>- LOCO clock<br>- Peripheral module clock B (PCLKB)<br>• Reference clocks for measurement<br>- External clock input to the CACREF pin<br>- Main clock<br>- Sub-clock<br>- HOCO clock<br>- HOCO clock<br>- LOCO clock<br>- Sub-clock<br>- BOCO clock<br>- LOCO clock<br>- HOCO clock<br>- LOCO clock<br>- LOCO clock<br>- LOCO clock<br>- LOCO clock<br>- IWDT-dedicated clock<br>- Peripheral module clock B (PCLKB)<br>• Digital filtering is selectable. |  |  |

| Low power<br>consumption                                  | Power-saving functions                                  | <ul> <li>The LSI chip has several functions for power saving, such as setting clock dividers, stopping modules, selecting power control mode in operating mode, transitioning to low power consumption mode, and power supply mode per domain.</li> <li>Three power control modes based on the operating frequency         <ul> <li>Boost mode (up to 64 MHz)</li> <li>Normal mode</li> <li>High-speed mode (up to 32 MHz)</li> <li>Low-speed mode (up to 2 MHz)</li> <li>Subosc-speed mode (this LSI chip can be placed in the low leakage current mode at 32.768 kHz.)</li> <li>Low leakage current mode (32.768 kHz)</li> </ul> </li> <li>Five low-power consumption modes     <ul> <li>Operating mode</li> <li>Sleep mode</li> <li>Software standby mode</li> <li>Three power supply mode (ALLPWON)</li> <li>Flash-excluded power supply mode (MINPWON)</li> </ul> </li> </ul>                                                                                                                                                                                         |  |  |

|                                                           | Back-bias voltage control <sup>*1</sup> (VBBC) function | Program control of the back bias voltage enables low leakage current operation in the low leakage current mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

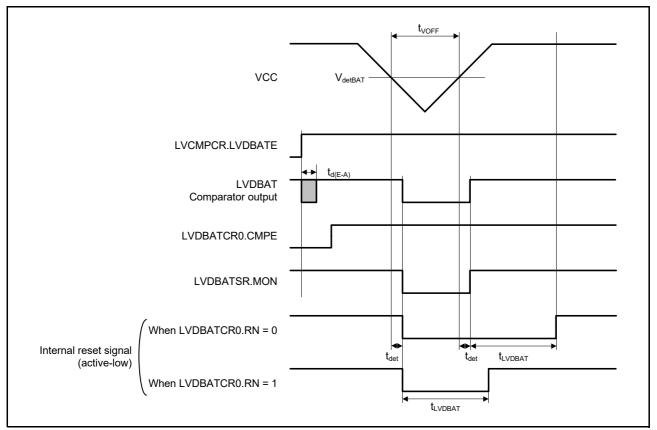

| Energy harvesting                                         | g control circuit (EHC)                                 | Starting up of this LSI chip in the power-saving mode is possible by controlling the power generating element, storage capacitor, and secondary battery.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Register write protection (RWP)                           |                                                         | The register write protection function protects important registers from rewrites caused by software errors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Memory protection units (MPUs) and stack pointer monitors |                                                         | <ul> <li>Illicit memory access <ul> <li>CPU (attempt at access to an undefined address space)</li> <li>CPU stack pointer monitors: Two regions</li> </ul> </li> <li>Memory protection <ul> <li>Arm<sup>®</sup> MPU: Eight areas</li> <li>Bus master MPU: Four areas</li> <li>Bus slave MPU</li> </ul> </li> <li>Security <ul> <li>Security</li> <li>Security MPU: Two secure program areas</li> <li>Three secure data areas (code flash memory, SRAM, and TSIP-Lite</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

Table 1.1Outline of Specifications (3/10)

RENESAS

| Classification                    | Feature                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|-----------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Interrupt                         | Interrupt controller unit<br>(ICU) | <ul> <li>Peripheral function interrupts: 168 sources</li> <li>External interrupts: 10 sources (pins IRQ0 to IRQ9)</li> <li>Non-maskable interrupts: Nine sources</li> <li>DMAC and DTC control: The DMAC and DTC can be activated by interrupt sources.</li> <li>Interrupts for NVIC: 32 sources</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Key interrupt fund                | tion (KINT)                        | An interrupt can be generated by inputting a rising or falling edge to the key interrupt input pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

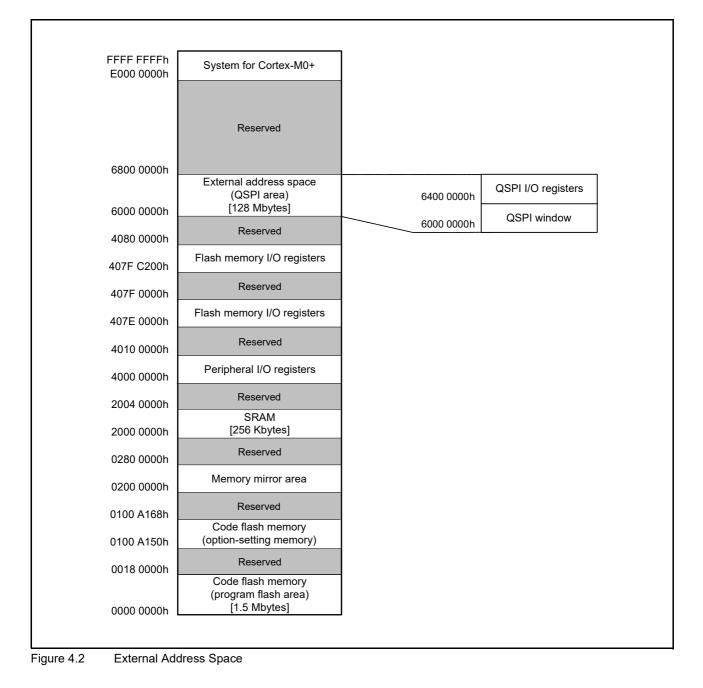

| External bus                      |                                    | QSPI area: Connectable to the QSPI (external device interface)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| DMA                               | Data transfer controller<br>(DTC)  | <ul> <li>Transfer modes: Normal transfer, repeat transfer, and block transfer</li> <li>Activation sources: External interrupts and interrupt requests from peripheral functions</li> <li>Transfer channels: Multiple data units can be transferred on a single activation source (chain transfer).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                                   | DMA controller (DMAC)              | <ul> <li>A 4-channel DMA controller (DMAC) module is incorporated for transferring data without CPU intervention. When a DMA transfer request is generated, the DMAC transfers data stored at the transfer source address to the transfer destination address.</li> <li>Transfer modes: Normal transfer, repeat transfer, and block transfer</li> <li>Activation sources: Software trigger, external interrupts, and interrupt requests from peripheral functions</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Event link control                | ler (ELC)                          | The ELC uses the interrupt requests generated by various peripheral modules as event signals and connects them to different modules. This enables modules to function in combination with each other without CPU intervention.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Timers General PWM timer<br>(GPT) |                                    | <ul> <li>Two 32-bit counters (GPT32), and four 16-bit counters (GPT16)</li> <li>Up-counting or down-counting (saw waves) or up-counting or down-counting (triangle waves) is selectable for each counter.</li> <li>Two input/output pins per channel</li> <li>Two output compare/input capture registers per channel</li> <li>For the two output compare/input capture registers of each channel, four buffer registers are provided and are capable of operating as comparison registers when buffering is not in use.</li> <li>In output compare operation, buffer switching can be at crests or troughs, enabling the generation of laterally asymmetric PWM waveforms.</li> <li>Registers for setting up frame cycles in each channel (with capability for generating interrupts at overflow or underflow)</li> <li>Generation of dead times in PWM operation</li> <li>Synchronous starting, stopping and clearing counters for arbitrary channels</li> <li>Based on the ELC settings, up to four ELC events can start or stop counting, clear the counter, drive counting up or down, or trigger input capture.</li> <li>Up to two external triggers can start or stop counting, clear the counter, drive counting up or down, or trigger input capture.</li> <li>Output pin disable function in response to detecting short-circuits between output pins</li> <li>PWM waveforms for controlling brushless DC motors can be generated.</li> <li>Compare match A to D events, overflow or underflow events and input UVW edge events can be output to the ELC.</li> <li>A noise filter can be used for input capture input and hall sensor input.</li> </ul> |  |  |  |  |  |

|                                   | Port output enable for GPT (POE)   | <ul> <li>Output disabling in response to detection of the input level on the GTETRGn pin</li> <li>Output disabling in response to a request from the GPT.</li> <li>Output disabling in response to detection of stopped oscillation.</li> <li>Output disabling in response to an ACMP interrupt request.</li> <li>Output disabling in response to software register settings.</li> <li>The GTETRGn signals can be output to the GPT as external trigger signals after polarity and filter selection.</li> <li>An input filter can be used for the GTETRGn pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

Table 1.1Outline of Specifications (4/10)

| Classification | Feature Description                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|----------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

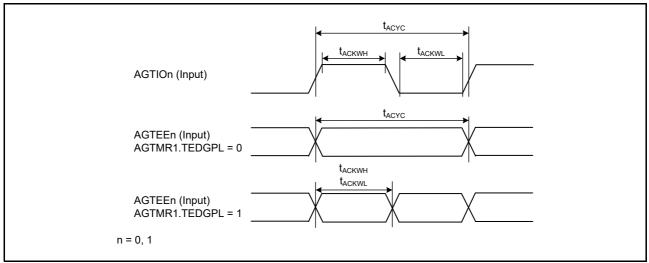

| Timers         | Asynchronous general-<br>purpose timer (AGT) | <ul> <li>The asynchronous general-purpose timer (AGT) is a 16-bit timer that can be used for pulse output, external pulse width or period measurement, and counting external events.</li> <li>Two channels</li> <li>Support for five operating modes <ul> <li>Timer mode</li> <li>Pulse output mode</li> <li>Event counter mode</li> <li>Pulse width measurement mode</li> <li>Pulse period measurement mode</li> </ul> </li> <li>The AGT supports the interrupt and event link functions for three sources, and the chip can return from software standby mode.</li> <li>Underflow event signal/measurement complete event signal</li> <li>Compare match A event signal</li> </ul>                                                                                                                                                                                         |  |  |  |  |  |

|                | 8-bit timers (TMR)                           | <ul> <li>(8 bits × 2 channels) × 1 unit</li> <li>Select from among seven internal clock signals (PCLKB/1, PCLKB/2, PCLKB/8, PCLKB/32, PCLKB/64, PCLKB/1024, PCLKB/8192) and one external clock signal.</li> <li>Capable of output of pulse with desired duty cycles or of PWM signals</li> <li>The two channels can be cascaded to create a 16-bit timer.</li> <li>Conversion start trigger for the 14-bit A/D converter can be generated.</li> <li>Support of function for event linking by the ELC</li> </ul>                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                | Realtime clock (RTC)                         | <ul> <li>The RTC has two counting modes: a calendar count mode and a binary count mode.<br/>These modes are controlled by the register settings.</li> <li>For calendar count mode, the RTC has a 100-year calendar from 2000 to 2099 and automatically adjusts dates for leap years.</li> <li>For binary count mode, the RTC counts seconds and retains the information as a serial value.</li> <li>Binary count mode can be used for calendars other than the Gregorian (western) calendar.</li> <li>Clock source: Sub-clock oscillator</li> <li>Counting by either clock counters or 32-bit binary counters in second units is selectable.</li> <li>Clock and calendar functions</li> <li>Interrupt sources: Alarm interrupt, periodic interrupt, and carry interrupt</li> <li>Time capture function</li> <li>Support of function for event linking by the ELC</li> </ul> |  |  |  |  |  |

|                | Clock correction circuit<br>(CCC)            | <ul> <li>The CCC corrects the oscillation accuracy every 16 seconds for the sub-clock (32.768 kHz).</li> <li>Clock output after correction: 2.048 kHz or 512 Hz</li> <li>Signal output (CCCOUT): Selectable from 512 Hz, 1 Hz, and RTC output (1 Hz or 64 Hz)</li> <li>Support of function for event linking by the ELC</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

Table 1.1Outline of Specifications (5/10)

| Classification | Feature                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|----------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Timers         | Watchdog timer (WDT)                   | <ul> <li>The WDT can be used to reset the LSI chip when the system runs out of control. A non-maskable interrupt or interrupt can be generated by an underflow of the counter.</li> <li>14 bits × 1 channel</li> <li>Count clock (WDTCLK): Selectable from PCLKB and CCC_2K</li> <li>Selectable counter clock signal: 6 types (WDTCLK/4, WDTCLK/64, WDTCLK/128, WDTCLK/512, WDTCLK/2048, WDTCLK/8192).</li> </ul>                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                | Independent watchdog<br>timer (IWDT)   | <ul> <li>The IWDT is a 14-bit down-counter and operates with the clock (IWDTCLK) that is independent of the clock used by the system. It can reset the LSI chip if the system runs out of control. The IWDT provides functionality to reset the LSI chip or to generate a non-maskable interrupt or interrupt on a counter underflow.</li> <li>14 bits × 1 channel</li> <li>Counter-input clock: IWDTLOCO</li> <li>IWDTLOCO/1, IWDTLOCO/16, IWDTLOCO/32, IWDTLOCO/64, IWDTLOCO/128, IWDTLOCO/256</li> <li>Window function: The positions where the window starts and ends are specifiable (the window defines the timing with which refreshing is enabled and disabled).</li> <li>Support of function for event linking by the ELC</li> </ul> |  |  |  |  |

|                | Low-speed clock timer<br>(LST)         | <ul> <li>The low-speed clock timer (LST) is a 13-bit timer that consists of a 1-kHz timer-counter and a circuit for converting hexadecimal numbers to decimal numbers. The LST can be used to indicate a count that needs to be displayed in decimal.</li> <li>Capable of counting from 0.000 to 1.999 seconds (in units of 0.001 seconds)</li> <li>The counted value can be directly stored in a register in decimal notation.</li> </ul>                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                | Low-speed pulse<br>generator (LPG)     | <ul> <li>The LPG is a simple 4-bit timer that operates with a 32-kHz clock (SOSC clock, LOCO clock).</li> <li>Two types of pulse output are possible (4.096 kHz and 2.048 kHz).</li> <li>Two duty cycles are selectable (1/4, 1/2).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                | Motor driver control circuit<br>(MTDV) | The MTDV can drive up to three motors.<br>• Two-signal waveform output (three modes: PM1/PM2/PM3)<br>• Three-signal waveform output (two modes: PM5/PM6)<br>• Rotation detection function (PM1 mode only)<br>• Polarity reversal function<br>• Forward-/reverse-rotation control function<br>• Support of function for event linking by the ELC                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

Table 1.1Outline of Specifications (6/10)

| Classification               | Feature                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Communications<br>interfaces | Serial communications<br>interfaces (SCIg, SCIi) | <ul> <li>Without FIFO (SCIg) × 5 channels, with FIFO (SCIi) × 2 channels</li> <li>The SCI is configurable for five asynchronous and synchronous serial interfaces.</li> <li>Asynchronous interfaces (UART and asynchronous communications interface adapter (ACIA))</li> <li>8-bit clock-synchronous interface</li> <li>Simple I<sup>2</sup>C (master-only)</li> <li>Simple SPI</li> <li>Smart card interface complies with the ISO/IEC 7816-3 standard for electronic signals and transmission protocol.</li> <li>SCI0 and SCI1 have 16-byte FIFO buffers to enable continuous and full-duplex communications.</li> <li>The data transfer speed can be configured independently using an on-chip baud rate generator.</li> <li>Selectable as LSB-first or MSB-first transfer</li> <li>Support of function for event linking by the ELC (SCI2 only)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                              | IrDA interface (IrDA)                            | The IrDA interface sends and receives IrDA data communications waveforms in cooperation with the SCI1 based on the IrDA (Infrared Data Association) standard 1.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

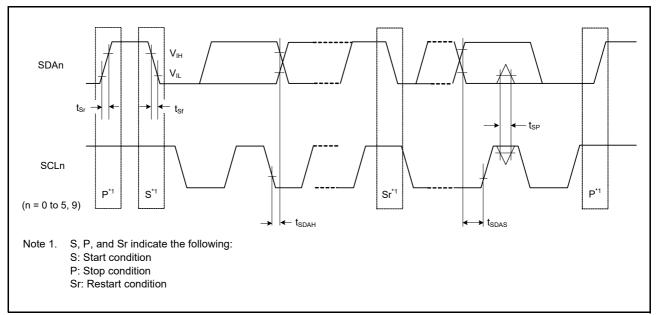

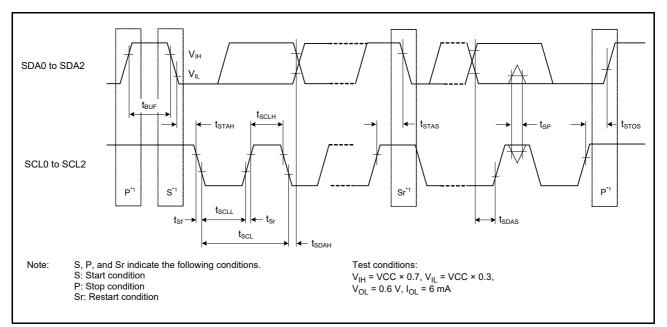

|                              | I <sup>2</sup> C bus interface (RIIC)            | <ul> <li>The RIIC conforms with and provides a subset of the NXP I<sup>2</sup>C bus (Inter-Integrated Circuit bus) interface functions.</li> <li>I<sup>2</sup>C bus format or SMBus format</li> <li>Two channels</li> <li>Master or slave selectable</li> <li>Automatic securing of the setup times, hold times, and bus-free times for the multimaster transfer rate</li> <li>Support of function for event linking by the ELC</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

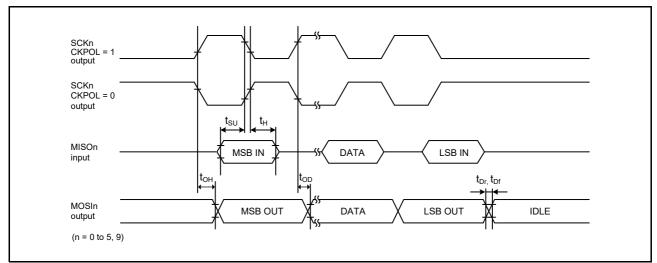

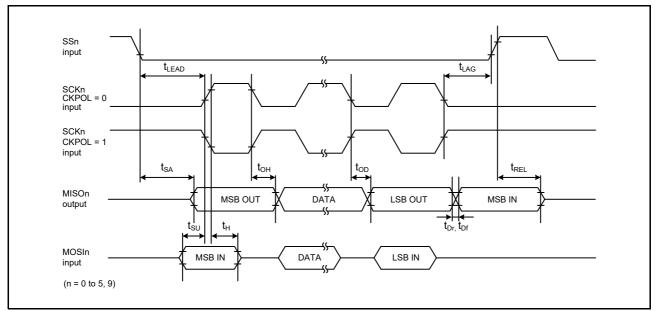

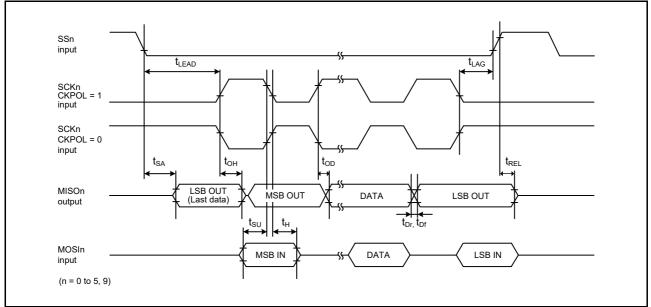

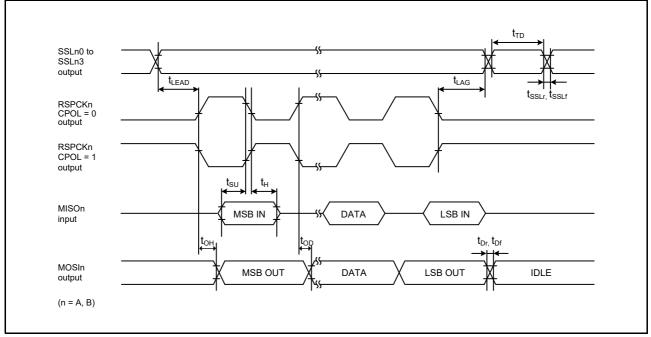

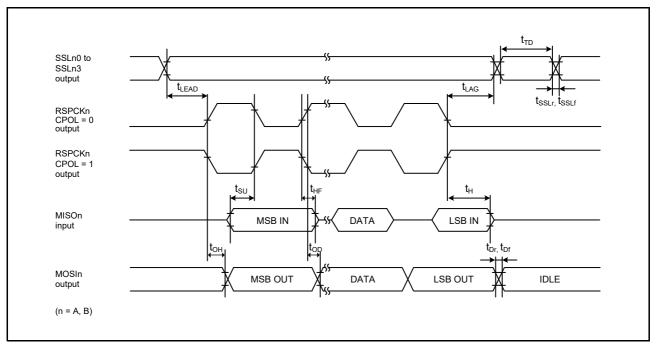

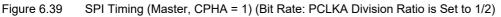

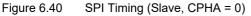

|                              | Serial peripheral interface<br>(SPI)             | <ul> <li>The SPI can handle high-speed and full-duplex synchronous serial communications with multiple processors and peripheral devices.</li> <li>Up to eight commands/128-bit buffer × 1 channel (SPI0)</li> <li>One command/32-bit buffer × 1 channel (SPI1)</li> <li>Use of MOSI (master out/slave in), MISO (master in/slave out), SSL (slave select), and RSPCK (SPI clock) signals allows serial communications through SPI operation (four-wire method) or clock synchronous operation (three-wire method).</li> <li>Transmit-only operation is available.</li> <li>Switching of RSPCK polarity</li> <li>Switching of RSPCK phase</li> <li>MSB-first or LSB-first selectable</li> <li>Transfer bit length selectable as 8, 9, 10, 11, 12, 13, 14, 15, 16, 20, 24, or 32 bits</li> <li>128-bit (SPI0) or 32-bit (SPI1) transmit and receive buffers</li> <li>Up to four frames can be transferred in one round of transmission or reception (each frame consisting of up to 32 bits).</li> <li>Double buffer configuration for the transmission and reception buffers</li> <li>Support of function for event linking by the ELC</li> <li>Communications with the MIP LCD controller of the three-wire serial type are possible (SPI0 only).</li> </ul> |  |  |  |  |

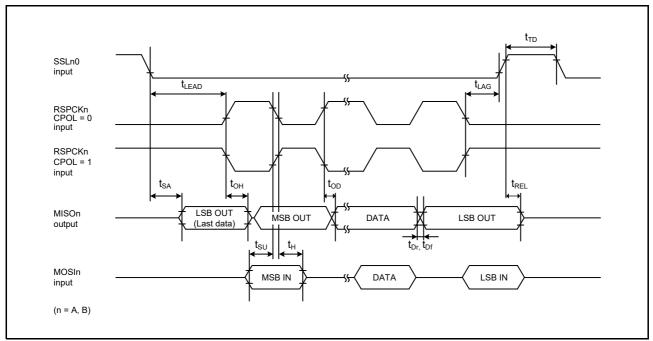

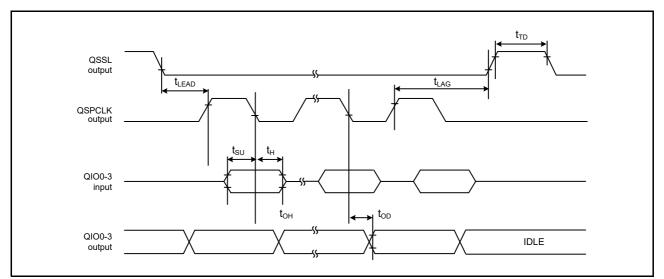

|                              | Quad serial peripheral<br>interface (QSPI)       | <ul> <li>The QSPI is connectable to a serial ROM that has an SPI-compatible interface.</li> <li>1 channel</li> <li>Support for extended SPI, dual SPI, and quad SPI protocols</li> <li>Configurable to SPI mode 0 and SPI mode 3</li> <li>Address width selectable from 8, 16, 24, or 32 bits.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

Table 1.1Outline of Specifications (7/10)

| Classification               | Feature                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Communications<br>interfaces | USB 2.0 FS host/function<br>module (USB)       | <ul> <li>Full-speed USB controller that can operate as a host controller or device controller. The module supports full-speed and low-speed (host controller only) transfer as defined in the Universal Serial Bus Specification 2.0. The module has an internal USB transceiver and supports all of the transfer types defined in the Universal Serial Bus Specification 2.0. The USB has buffer memory for data transfer, providing a maximum of 10 pipes. Pipes 1 to 9 can be assigned any endpoint number based on the peripheral devices used for communications or based on your system.</li> <li>USB device controller (UDC) and USB 2.0 transceiver supporting host controller, device controller, and On-The-Go (OTG) functions (one channel)</li> <li>Host and device controllers can be switched by the software.</li> <li>Self-power mode or bus power mode can be selected.</li> <li>When the host controller function is selected: Full-speed transfer (12 Mbps) and low-speed transfer (1.5 Mbps)</li> <li>When the device controller function is selected: Full-speed transfer (12 Mbps)</li> </ul>                                                                                                                                                                                                                                           |  |  |  |

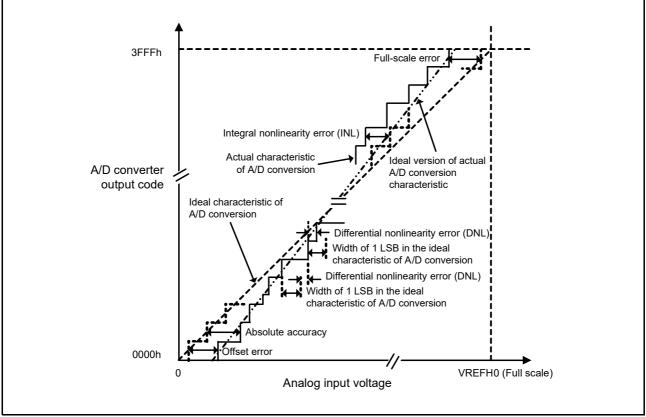

| Analog                       | 14-bit A/D converter<br>(S14AD)                | <ul> <li>A 14-bit successive approximation A/D converter incorporated</li> <li>Up to 18 analog input channels are selectable. The analog input channels and the temperature sensor output are selectable for conversion. The A/D conversion accuracy is selectable between 12-bit and 14-bit conversion making it possible to optimize the tradeoff between speed and resolution in generating a digital value.</li> <li>14 bits × 18 channels (maximum value) (high accuracy: 7 channels, standard accuracy: 11 channels)</li> <li>Resolution: 14 bits (14-bit or 12-bit conversion selectable)</li> <li>Operating mode:</li> <li>Scan mode (single-scan mode, continuous-scan mode, or group-scan mode)</li> <li>Group A priority control (only for group-scan mode)</li> <li>Variable sampling state count</li> <li>A/D-converted value addition mode or average mode selectable</li> <li>Disconnection detection assist function</li> <li>Double-trigger mode (duplication of A/D conversion data)</li> <li>Support of function for event linking by the ELC</li> <li>Automatic clear function of A/D data registers</li> <li>Compare function for window A and window B</li> <li>Digital compare function</li> <li>Comparison of values in the comparison register and the data register, and comparison between values in the data registers</li> </ul> |  |  |  |

|                              | 12-bit D/A converter<br>(R12DA)                | <ul> <li>A 12-bit D/A converter with an output amplifier incorporated</li> <li>12 bits × 1 channel</li> <li>Resolution: 12 bits</li> <li>Support of function for event linking by the ELC</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                              | Temperature sensor<br>(TEMPS)                  | The temperature sensor outputs the voltage that is directly proportional to the die temperature.<br>The output voltage is converted to a digital value by the S14AD for conversion and can be further used by the end application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                              | Analog comparator<br>(ACMP)                    | <ul> <li>The ACMP can be used to compare a reference input voltage and analog input voltage.</li> <li>1 channel × 1 unit</li> <li>Analog input: Input from the CMPIN pin</li> <li>Reference voltage: Input from the CMPREF pin</li> <li>Whether to use a noise filter and a sampling clock frequency can be selected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                              | LED driver (LED)                               | <ul> <li>The LSI chip has a constant current source circuit that can drive three external LED channels.</li> <li>3 channels × 1 unit</li> <li>Output constant current: 1.0 mA (LED load: 1.4 kΩ), 0.5 mA (LED load: 2.8 kΩ)</li> <li>Constant current temperature characteristics: 2000 ppm/°C (T<sub>a</sub> = -20°C to 60°C)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                              | Reference voltage<br>generation circuit (VREF) | The circuit generates two types (1.25 V/2.5 V) of reference voltage.<br>The generated voltage can be used as the reference voltage for the ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

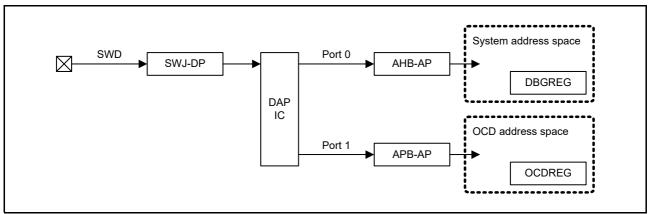

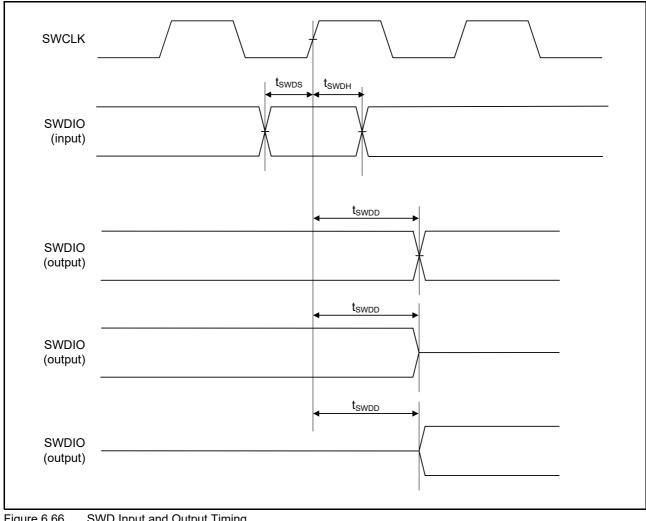

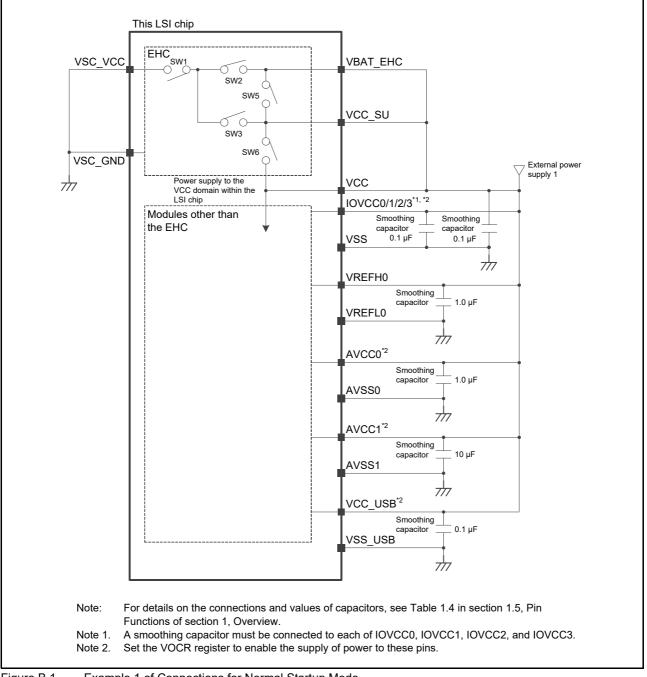

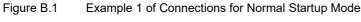

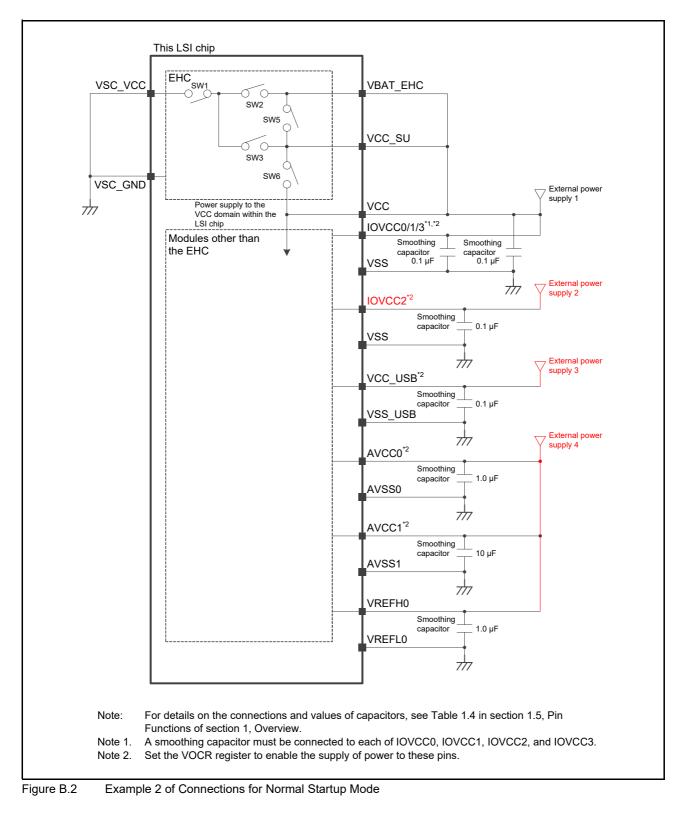

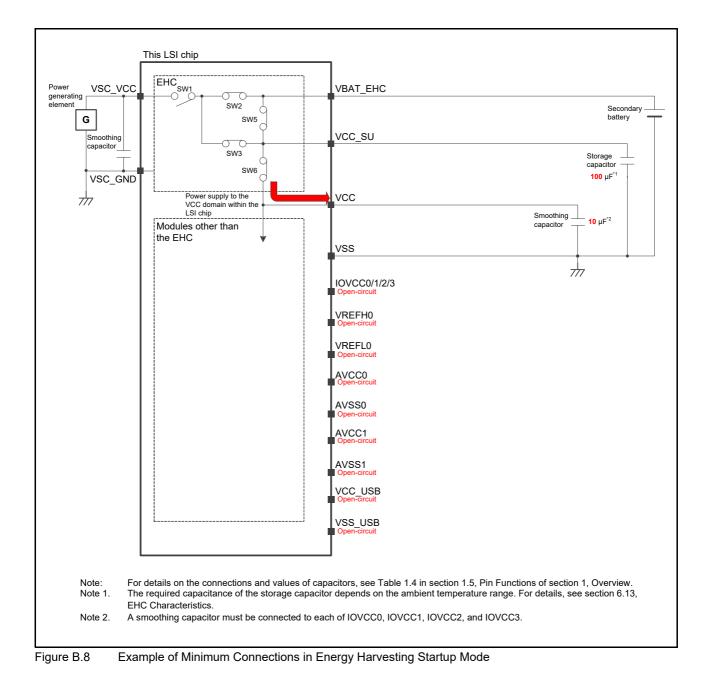

Table 1.1Outline of Specifications (8/10)