### RL78/G1G RENESAS MCU

## Datasheet

### R01DS0241EJ0140 Rev. 1.40 Apr 26, 2024

## 1. OUTLINE

### 1.1 Features

#### Ultra-low power consumption technology

- + VDD = single power supply voltage of 2.7 to 5.5 V

- HALT mode

- STOP mode

- SNOOZE mode

#### RL78 CPU core

- CISC architecture with 3-stage pipeline

- Minimum instruction execution time: Can be changed from high-speed (0.04167  $\mu$ s: @ 24 MHz operation with high-speed on-chip oscillator) to low-speed (1.0  $\mu$ s: @1 MHz operation with high-speed on-chip oscillator)

- Multiply/divide/multiply & accumulate instructions are supported.

- Address space: 1 MB

- General-purpose registers: (8-bit register × 8) × 4 banks

- On-chip RAM: 1.5 KB

#### Code flash memory

- Code flash memory: 8 to 16 KB

- Block size: 1 KB

- Prohibition of block erase and rewriting (security function)

- On-chip debug function

- · Self-programming (flash shield window function)

#### High-speed on-chip oscillator

- Select from 48 MHz, 24 MHz, 16 MHz, 12 MHz, 8 MHz, 4 MHz, and 1 MHz

- High accuracy: ±2.0%

#### Operating ambient temperature

• TA = -40 to +85°C

#### Power management and reset function

- On-chip power-on-reset (POR) circuit

- On-chip voltage detector (LVD) (Select interrupt and reset from 6 levels)

#### Event link controller (ELC)

• Event signals of 18 to 19 types can be linked to the specified peripheral function.

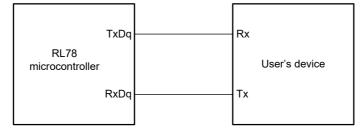

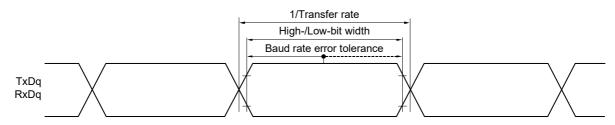

#### Serial interfaces

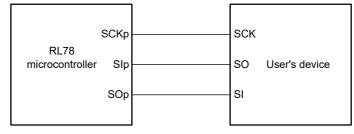

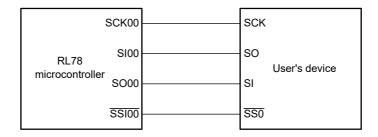

- Simplified SPI (CSINote 1): 1 channel

- UART: 2 channels

- Simplified I<sup>2</sup>C: 1 channel

#### Timer

- 16-bit timer: 7 channels

- (Timer Array Unit (TAU): 4 channels, Timer RJ: 1 channel, Timer RD: 2 channels)

- 12-bit interval timer: 1 channel

- Watchdog timer: 1 channel (operable with the dedicated low-speed on-chip oscillator)

#### A/D converter

- 8/10-bit resolution A/D converter (VDD = 2.7 to 5.5 V)

- Analog input: 8 to 12 channels

- Internal reference voltage (1.45 V) and temperature sensor<sup>Note 2</sup>

#### Comparator

- 2 channels

- The voltage from a dedicated 8-bit DAC (resolution of 256 with VDD/AVREFP or VSS/AVREFM as the internally generated reference voltage) can be selected as the reference voltage.

#### Programmable gain amplifier

#### I/O port

- I/O port: 26 to 40

- Can be set to N-ch open drain, TTL input buffer, and onchip pull-up resistor

- Different potential interface: Can connect to a 2.5/3 V device

- On-chip key interrupt function

- · On-chip clock output/buzzer output controller

#### Others

- · On-chip BCD (binary-coded decimal) correction circuit

- **Note 1.** Although the CSI function is generally called SPI, it is also called CSI in this product, so it is referred to as such in this manual.

- Note 2. Selectable only in HS (high-speed main) mode.

- Remark The functions mounted depend on the product. See 1.6 Outline of Functions.

### ○ ROM, RAM capacities

| Flash ROM | RAM                    | 30 pins     | 32 pins     | 44 pins     |

|-----------|------------------------|-------------|-------------|-------------|

| 16 KB     | 1.5 KB <sup>Note</sup> | R5F11EAAASP | R5F11EBAAFP | R5F11EFAAFP |

| 8 KB      |                        | R5F11EA8ASP | R5F11EB8AFP | R5F11EF8AFP |

Note

This is 630 bytes when the self-programming function is used. (For details, see CHAPTER 3 CPU ARCHITECTURE in the RL78/G1G User's Manual).

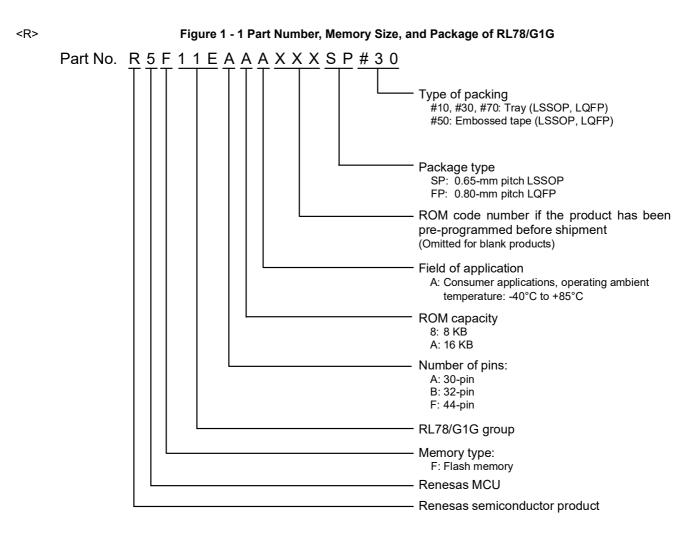

### 1.2 List of Part Numbers

### Table 1 - 1 Orderable Part Numbers

|         | Pin Count | Package                              | Part Number                     |

|---------|-----------|--------------------------------------|---------------------------------|

|         | 44 pins   | 44-pin plastic LQFP (10 × 10 mm)     | R5F11EFAAFP#10, R5F11EFAAFP#30, |

| <r></r> |           |                                      | R5F11EFAAFP#50, R5F11EFAAFP#70  |

|         |           |                                      | R5F11EF8AFP#10, R5F11EF8AFP#30, |

| <r></r> |           |                                      | R5F11EF8AFP#50, R5F11EF8AFP#70  |

|         | 32 pins   | 32-pin plastic LQFP (7 × 7 mm)       | R5F11EBAAFP#10, R5F11EBAAFP#30, |

| <r></r> |           |                                      | R5F11EBAAFP#50, R5F11EBAAFP#70  |

|         |           |                                      | R5F11EB8AFP#10, R5F11EB8AFP#30, |

| <r></r> |           |                                      | R5F11EB8AFP#50, R5F11EB8AFP#70  |

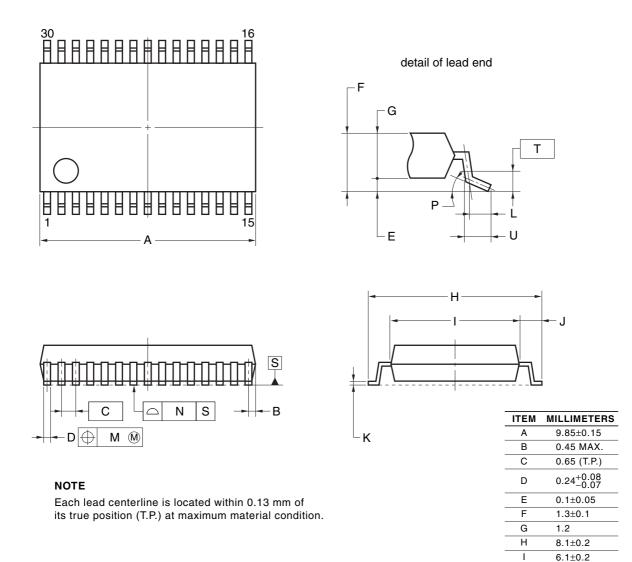

|         | 30 pins   | 30-pin plastic LSSOP (7.62 mm (300)) | R5F11EAAASP#10, R5F11EAAASP#30, |

| <r></r> |           |                                      | R5F11EAAASP#50, R5F11EAAASP#70  |

|         |           |                                      | R5F11EA8ASP#10, R5F11EA8ASP#30, |

| <r></r> |           |                                      | R5F11EA8ASP#50, R5F11EA8ASP#70  |

### 1.3 Pin Configuration (Top View)

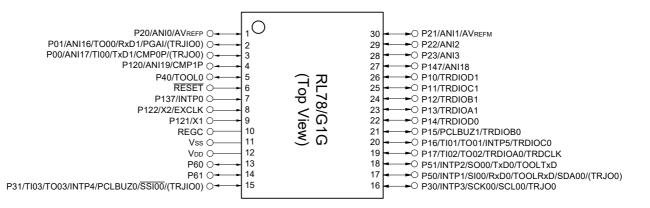

### 1.3.1 30-pin products

• 30-pin plastic LSSOP (7.62 mm (300), 0.65 mm pitch)

Caution Connect the REGC pin to Vss pin via a capacitor (0.47 to 1  $\mu$ F).

Remark 1. For pin identification, see 1.4 Pin Identification.

**Remark 2.** The functions in parentheses shown in the above figure can be assigned by setting peripheral I/O redirection register 1 (PIOR1).

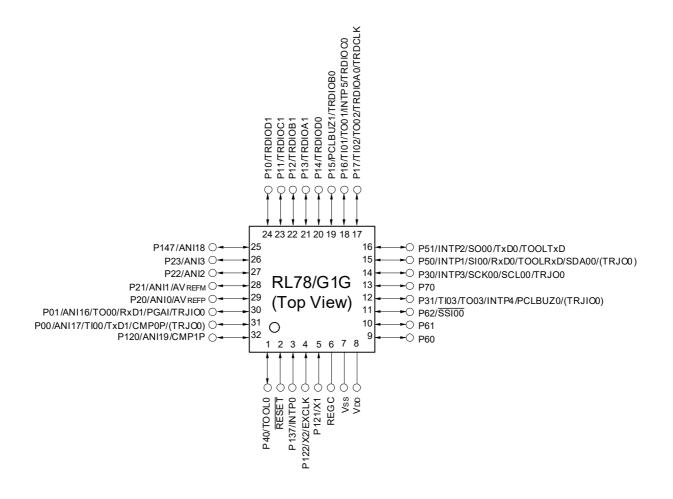

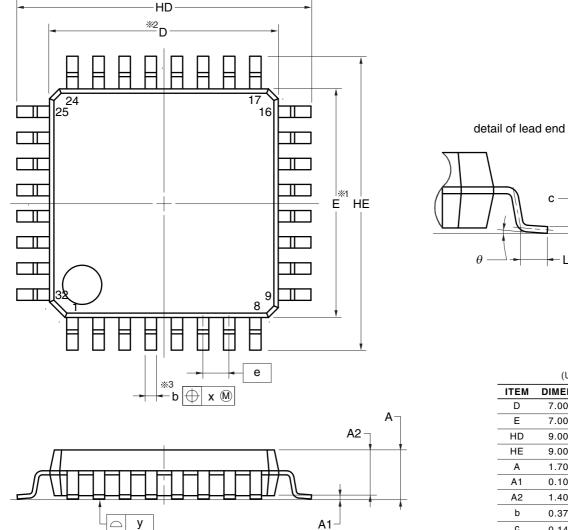

### 1.3.2 32-pin products

• 32-pin plastic LQFP (7 x 7 mm, 0.8 mm pitch)

- Caution Connect the REGC pin to Vss pin via a capacitor (0.47 to 1  $\mu$ F).

- Remark 1. For pin identification, see 1.4 Pin Identification.

- **Remark 2.** The functions in parentheses shown in the above figure can be assigned by setting peripheral I/O redirection register 1 (PIOR1).

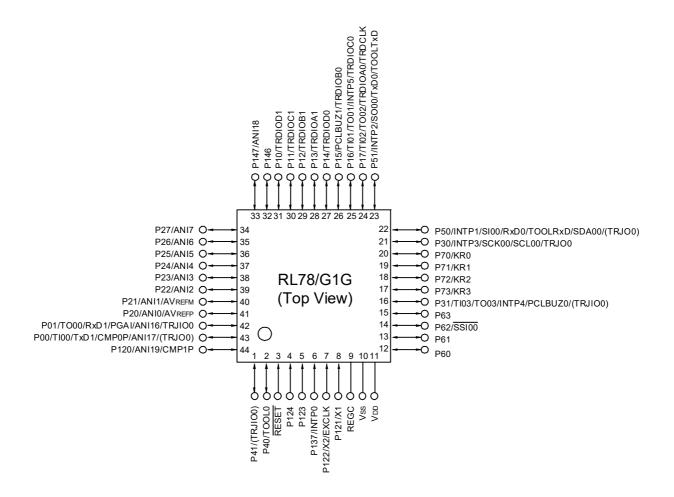

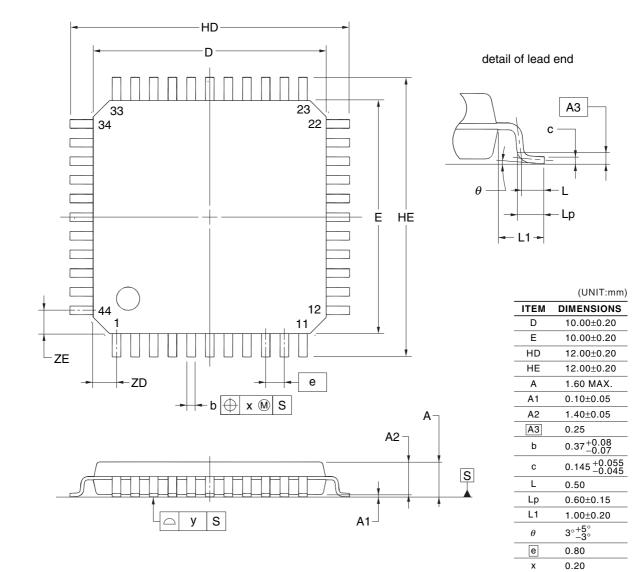

### 1.3.3 44-pin products

• 44-pin plastic LQFP (10 x 10 mm, 0.8 mm pitch)

- Caution Connect the REGC pin to Vss pin via a capacitor (0.47 to 1  $\mu$ F).

- Remark 1. For pin identification, see 1.4 Pin Identification.

- **Remark 2.** The functions in parentheses shown in the above figure can be assigned by setting peripheral I/O redirection register 1 (PIOR1).

### 1.4 Pin Identification

ANI0 to ANI7, ANI16 to ANI19: Analog input

| ANIU to ANI7, ANI16 to A | NI19:Analog input                                |

|--------------------------|--------------------------------------------------|

| AVREFM:                  | A/D converter reference potential (- side) input |

| AVREFP:                  | A/D converter reference potential (+ side) input |

| EXCLK:                   | External clock input (main system clock)         |

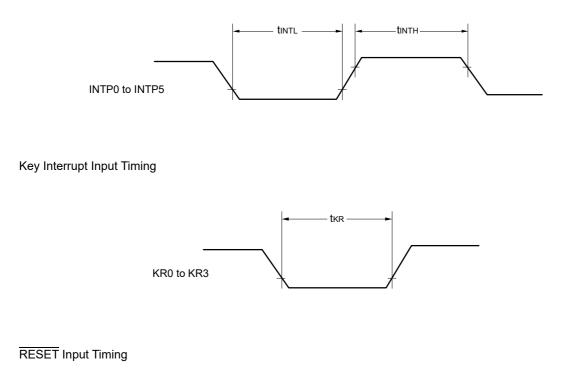

| INTP0 to INTP5:          | External interrupt input                         |

| KR0 to KR3:              | Key Return                                       |

| P00, P01:                | Port 0                                           |

| P10 to P17:              | Port 1                                           |

| P20 to P27:              | Port 2                                           |

| P30, P31:                | Port 3                                           |

| P40, P41:                | Port 4                                           |

| P50, P51:                | Port 5                                           |

| P60 to P63:              | Port 6                                           |

| P70 to P73:              | Port 7                                           |

| P120 to P124:            | Port 12                                          |

| P137:                    | Port 13                                          |

| P146, P147:              | Port 14                                          |

| PCLBUZ0, PCLBUZ1:        | Programmable clock output/buzzer output          |

| REGC:                    | Regulator capacitance                            |

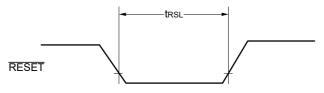

| RESET:                   | Reset                                            |

| RxD0, RxD1:              | Receive data                                     |

| SCK00:                   | Serial clock input/output                        |

| SCL00:                   | Serial clock output                              |

| SDA00:                   | Serial data input/output                         |

| SI00:                    | Serial data input                                |

| SO00:                    | Serial data output                               |

| SSI00:                   | Serial interface chip select input               |

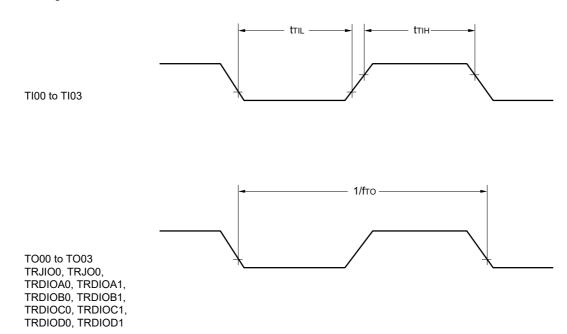

| TI00 to TI03:            | Timer input                                      |

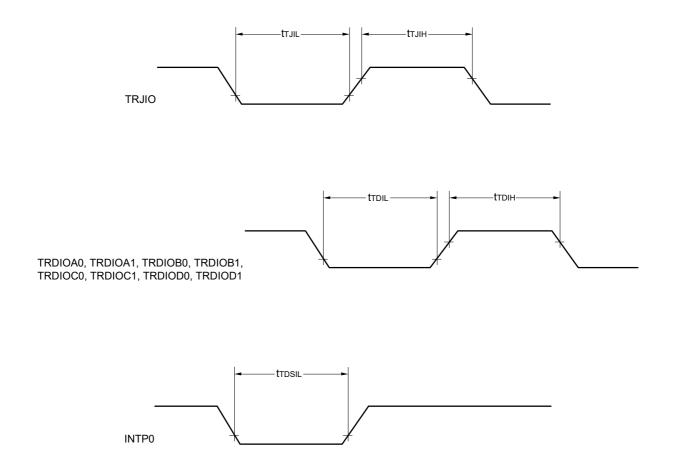

| TO00 to TO03, TRJO0:     | Timer output                                     |

| TOOL0:                   | Data input/output for tool                       |

| TOOLRxD, TOOLTxD:        | Data input/output for external device            |

| TRDCLK:                  | Timer external input clock                       |

| TRDIOA0, TRDIOB0, TR     | DIOC0, TRDIOD0,:Timer input/output               |

| TRDIOA1, TRDIOB1, TR     | DIOC1, TRDIOD1,                                  |

| TRJIO0                   |                                                  |

| TxD0, TxD1:              | Transmit data                                    |

| CMP0P, CMP1P:            | Comparator input                                 |

| PGAI:                    | PGA input                                        |

| VDD:                     | Power supply                                     |

| Vss:                     | Ground                                           |

| X1, X2:                  | Crystal oscillator (main system clock)           |

|                          |                                                  |

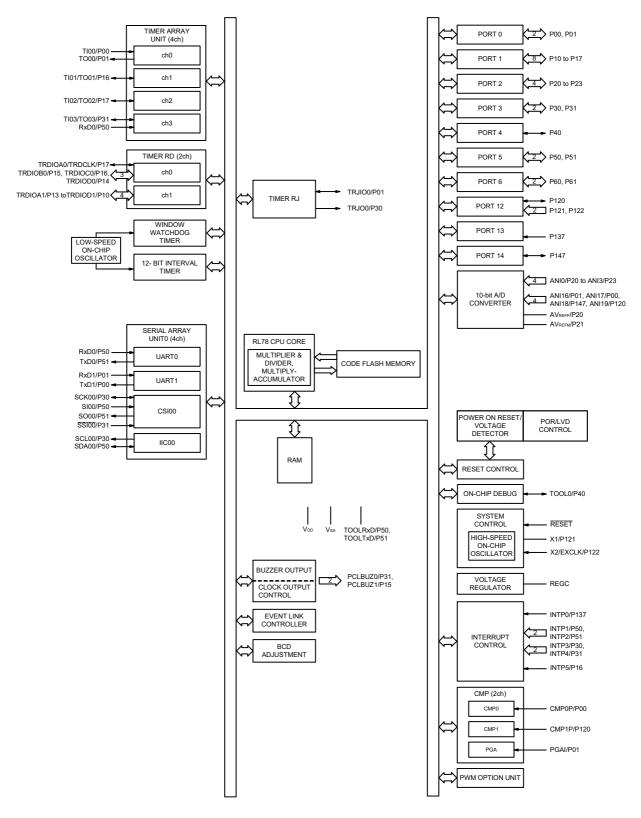

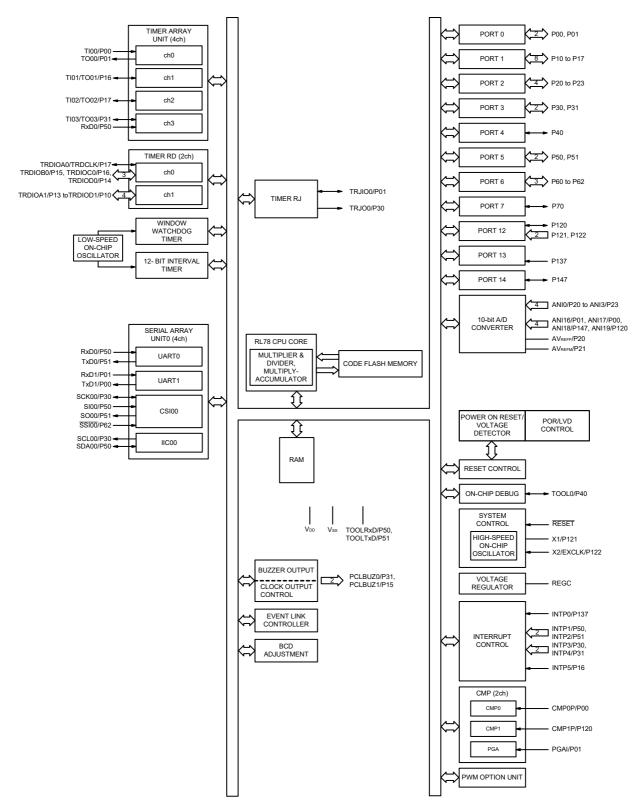

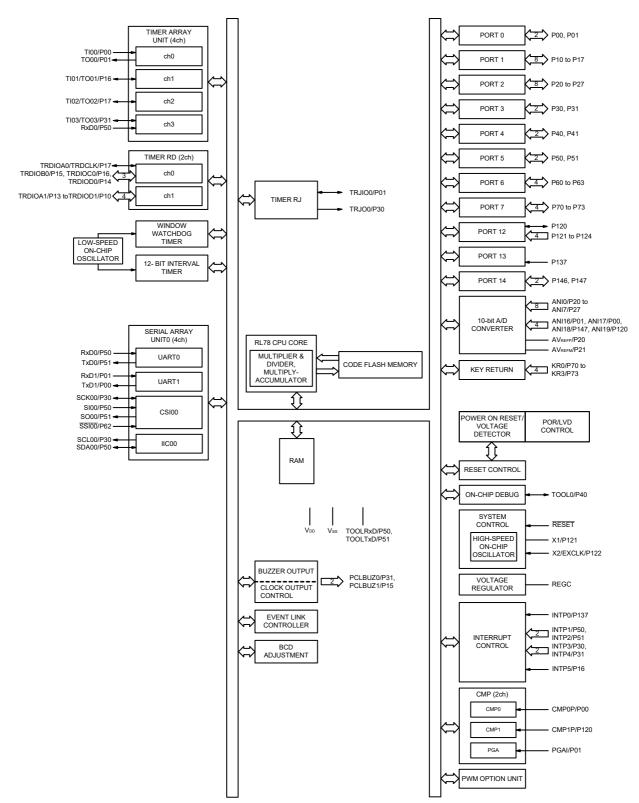

### 1.5 Block Diagram

### 1.5.1 30-pin products

### 1.5.2 32-pin products

### 1.5.3 44-pin products

### **1.6** Outline of Functions

[30-pin, 32-pin, 44-pin products (code flash memory 8 KB to 16 KB)]

## Caution The above outline of the functions applies when peripheral I/O redirection register 1 (PIOR1) is set to 00H.

|                      |                                              |                                                                                                                                                                                                                                                                                                                                                                                                    |                             | (1/2)                       |  |  |

|----------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|--|--|

|                      |                                              | 30-pin                                                                                                                                                                                                                                                                                                                                                                                             | 32-pin                      | 44-pin                      |  |  |

|                      | Item                                         | R5F11EA8ASP,<br>R5F11EAAASP                                                                                                                                                                                                                                                                                                                                                                        | R5F11EB8AFP,<br>R5F11EBAAFP | R5F11EF8AFP,<br>R5F11EFAAFP |  |  |

| Code flash m         | emory (KB)                                   |                                                                                                                                                                                                                                                                                                                                                                                                    | 8 to 16                     |                             |  |  |

| RAM (KB)             |                                              |                                                                                                                                                                                                                                                                                                                                                                                                    | 1.5                         |                             |  |  |

| Address space        | ce                                           | 1 MB                                                                                                                                                                                                                                                                                                                                                                                               |                             |                             |  |  |

| Main system<br>clock | High-speed system clock                      | X1 (crystal/ceramic) oscillation, d<br>LS (low-speed main) mode: 1 to<br>HS (high-speed main) mode: 1 t                                                                                                                                                                                                                                                                                            | 8 MHz (VDD = 2.7 to 5.5 V), | (EXCLK)                     |  |  |

|                      | High-speed on-chip<br>oscillator clock (fiH) | LS (low-speed main) mode: 1 to<br>HS (high-speed main) mode: 1                                                                                                                                                                                                                                                                                                                                     |                             |                             |  |  |

| Low-speed o          | n-chip oscillator clock                      | 15 kHz (TYP.): VDD = 2.7 to 5.5                                                                                                                                                                                                                                                                                                                                                                    | V                           |                             |  |  |

| General-purp         | oose register                                | 8 bits × 32 registers (8 bits × 8 registers × 4 banks)                                                                                                                                                                                                                                                                                                                                             |                             |                             |  |  |

| Minimum inst         | truction execution                           | 0.04167 μs (High-speed on-chip oscillator clock: fiн = 24 MHz operation)                                                                                                                                                                                                                                                                                                                           |                             |                             |  |  |

| time                 |                                              | 0.05 μs (High-speed system clock: fмx = 20 MHz operation)                                                                                                                                                                                                                                                                                                                                          |                             |                             |  |  |

| Instruction se       | 21                                           | <ul> <li>Data transfer (8/16 bits)</li> <li>Adder and subtractor/logical operation (8/16 bits)</li> <li>Multiplication (8 bits × 8 bits, 16 bits × 16 bits), Division (16 bits ÷ 16 bits, 32 bits ÷ 32 bits)</li> <li>Multiplication and Accumulation (16 bits × 16 bits + 32 bits)</li> <li>Rotate, barrel shift, and bit manipulation (Set, reset, test, and Boolean operation), etc.</li> </ul> |                             |                             |  |  |

| I/O port             | Total                                        | 26                                                                                                                                                                                                                                                                                                                                                                                                 | 28                          | 40                          |  |  |

|                      | CMOS I/O                                     | 23                                                                                                                                                                                                                                                                                                                                                                                                 | 25                          | 35                          |  |  |

|                      | CMOS input                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                  | 3                           | 5                           |  |  |

|                      | CMOS output                                  |                                                                                                                                                                                                                                                                                                                                                                                                    |                             |                             |  |  |

|                      | N-ch open-drain I/O<br>(6 V tolerance)       | _                                                                                                                                                                                                                                                                                                                                                                                                  |                             |                             |  |  |

| Timer                | 16-bit timer                                 | 7 channels<br>(TAU: 4 channels, Timer RJ: 1 channel, Timer RD: 2 channels)                                                                                                                                                                                                                                                                                                                         |                             |                             |  |  |

|                      | Watchdog timer                               | 1 channel                                                                                                                                                                                                                                                                                                                                                                                          |                             |                             |  |  |

|                      | 12-bit interval timer                        | 1 channel                                                                                                                                                                                                                                                                                                                                                                                          |                             |                             |  |  |

|                      | Timer output                                 | Timer outputs: 14 channels<br>PWM outputs: 9 channels                                                                                                                                                                                                                                                                                                                                              |                             |                             |  |  |

Caution Since a library is used when rewriting the flash memory using the user program, flash ROM and RAM areas are used. Refer to the RL78 Family Flash Self-Programming Library Type01 User's Manual before using these products.

|                      |                     |                                                                                                                                                                                                                                                                                                   |                                                   | (2/2)                         |  |  |

|----------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------|--|--|

|                      |                     | 30-pin                                                                                                                                                                                                                                                                                            | 32-pin                                            | 44-pin                        |  |  |

|                      | Item                | R5F11EA8ASP,                                                                                                                                                                                                                                                                                      | R5F11EB8AFP,                                      | R5F11EF8AFP,                  |  |  |

|                      |                     | R5F11EAAASP                                                                                                                                                                                                                                                                                       | R5F11EBAAFP                                       | R5F11EFAAFP                   |  |  |

| Clock output/        | /buzzer output      |                                                                                                                                                                                                                                                                                                   | 2                                                 |                               |  |  |

|                      |                     | • 2.44 kHz, 4.88 kHz, 9.77 kHz,<br>(Main system clock: fMAIN = 20                                                                                                                                                                                                                                 |                                                   | 10 MHz                        |  |  |

| 8/10-bit resol       | ution A/D converter | 8 channels                                                                                                                                                                                                                                                                                        | 12 channels                                       |                               |  |  |

| Comparator           |                     | 2 channels                                                                                                                                                                                                                                                                                        |                                                   |                               |  |  |

| PGA                  |                     | 1 channel                                                                                                                                                                                                                                                                                         |                                                   |                               |  |  |

| Serial interfac      | ce                  | Simplified SPI (CSI): 1 channel     UART1: 1 channel                                                                                                                                                                                                                                              | I/UART0: 1 channel/simplified                     | d I <sup>2</sup> C: 1 channel |  |  |

| Event link co        | ntroller (ELC)      | Event input: 18                                                                                                                                                                                                                                                                                   |                                                   | Event input: 19               |  |  |

|                      |                     | Event trigger output: 6                                                                                                                                                                                                                                                                           | Event trigger output: 6                           |                               |  |  |

| Vectored             | Internal            | 20                                                                                                                                                                                                                                                                                                |                                                   |                               |  |  |

| interrupt<br>sources | External            | 6                                                                                                                                                                                                                                                                                                 |                                                   | 7                             |  |  |

| Key interrupt        |                     | _                                                                                                                                                                                                                                                                                                 |                                                   | 4                             |  |  |

| Reset                |                     | <ul> <li>Reset by RESET pin</li> <li>Internal reset by watchdog time</li> <li>Internal reset by power-on-rese</li> <li>Internal reset by voltage detect</li> <li>Internal reset by illegal instruct</li> <li>Internal reset by RAM parity er</li> <li>Internal reset by illegal-memory</li> </ul> | et<br>tor<br>ion execution <sup>Note</sup><br>ror |                               |  |  |

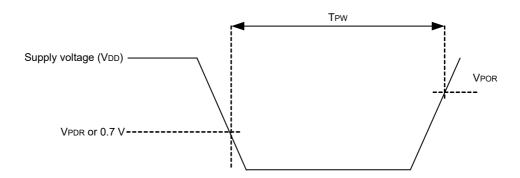

| Power-on-res         | set circuit         | <ul> <li>Power-on-reset: 1.51 ±0.03 V</li> <li>Power-down-reset: 1.50 ±0.03 V</li> </ul>                                                                                                                                                                                                          |                                                   |                               |  |  |

| Voltage detec        | ctor                | 2.75 V to 4.06 V (6 stages)                                                                                                                                                                                                                                                                       |                                                   |                               |  |  |

| On-chip debu         | ug function         | Provided                                                                                                                                                                                                                                                                                          |                                                   |                               |  |  |

| Power supply         | / voltage           | VDD = 2.7 to 5.5 V                                                                                                                                                                                                                                                                                |                                                   |                               |  |  |

| Operating an         | nbient temperature  | TA = -40 to +85°C                                                                                                                                                                                                                                                                                 |                                                   |                               |  |  |

**Note** The illegal instruction is generated when instruction code FFH is executed.

Reset by the illegal instruction execution is not issued by emulation with the in-circuit emulator or on-chip debug emulator.

## 2. ELECTRICAL SPECIFICATIONS

Caution 1. The RL78 microcontroller has an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

Caution 2. The pins mounted are as follows according to product.

### 2.1 Pins Mounted According to Product

### 2.1.1 Port functions

Refer to **2.1.1 30-pin products**, **2.1.2 32-pin products**, and **2.1.3 44-pin products** in the RL78/G1G User's Manual.

### 2.1.2 Non-port functions

Refer to 2.2.1 With functions for each product in the RL78/G1G User's Manual.

(1/2)

### 2.2 Absolute Maximum Ratings

### **Absolute Maximum Ratings**

| Parameter              | Symbols | Conditions                                                                                                                                          | Ratings                                                               | Unit |

|------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|

| Supply voltage         | Vdd     |                                                                                                                                                     | -0.5 to +6.5                                                          | V    |

| REGC pin input voltage | VIREGC  | REGC                                                                                                                                                | -0.3 to +2.8<br>and -0.3 to V <sub>DD</sub> +0.3 <sup>Note 1</sup>    | V    |

| Input voltage          | VI1     | P00, P01, P10 to P17, P20 to P27, P30,<br>P31, P40, P41, P50, P51, P60 to P63, P70<br>to P73, P120, P121 to P124, P137, P146,<br>P147, EXCLK, RESET | -0.3 to V <sub>DD</sub> +0.3 Note 2                                   | V    |

| Output voltage         | Vo1     | P00, P01, P10 to P17, P20 to P27, P30,<br>P31, P40, P41, P50, P51, P60 to P63, P70<br>to P73, P120, P146, P147                                      | -0.3 to V <sub>DD</sub> +0.3 Note 2                                   | V    |

| Analog input voltage   | VAI1    | ANI0 to ANI7, ANI16 to ANI19                                                                                                                        | -0.3 to V <sub>DD</sub> +0.3 Notes 2, 3<br>and -0.3 to AVREF (+) +0.3 | V    |

**Note 1.** Connect the REGC pin to Vss via a capacitor (0.47 to 1 μF). This value regulates the absolute maximum rating of the REGC pin. Do not use this pin with voltage applied to it.

Note 2. Must be 6.5 V or lower.

**Note 3.** Do not exceed AVREF (+) + 0.3 V in case of A/D conversion target pin.

- Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

- Remark 1. Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

**Remark 2.** AVREF (+): + side reference voltage of the A/D converter.

Remark 3. Vss: Reference voltage

### **Absolute Maximum Ratings**

(2/2)

|                      | langs   |                      |                                                                                                 |             | (2/2) |

|----------------------|---------|----------------------|-------------------------------------------------------------------------------------------------|-------------|-------|

| Parameter            | Symbols |                      | Conditions                                                                                      | Ratings     | Unit  |

| Output current, high | Іон1    | Per pin              | P00, P01, P10 to P17, P30, P31, P40, P41, P50,<br>P51, P60 to P63, P70 to P73, P120, P146, P147 | -40         | mA    |

|                      |         | Total of all         | P00, P01, P40, P41, P120                                                                        | -70         | mA    |

|                      |         | pins<br>-170 mA      | P10 to P17, P30, P31, P50, P51, P60 to P63, P70 to P73, P146, P147                              | -100        | mA    |

|                      | Іон2    | Per pin              | P20 to P27                                                                                      | -0.5        | mA    |

|                      |         | Total of all<br>pins |                                                                                                 | -2          | mA    |

| Output current, low  | IOL1    | Per pin              | P00, P01, P10 to P17, P30, P31, P40, P41, P50,<br>P51, P60 to P63, P70 to P73, P120, P146, P147 | 40          | mA    |

|                      |         | Total of all         | P00, P01, P40, P41, P120                                                                        | 70          | mA    |

|                      |         | pins<br>170 mA       | P10 to P17, P30, P31, P50, P51, P60 to P63, P70<br>to P73, P146, P147                           | 100         | mA    |

|                      | IOL2    | Per pin              | P20 to P27                                                                                      | 1           | mA    |

|                      |         | Total of all<br>pins |                                                                                                 | 5           | mA    |

| Operating ambient    | TA      | In normal c          | peration mode                                                                                   | -40 to +85  | °C    |

| temperature          |         | In flash me          | mory programming mode                                                                           |             |       |

| Storage temperature  | Tstg    |                      |                                                                                                 | -65 to +150 | °C    |

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

### 2.3 Oscillator Characteristics

### 2.3.1 X1 oscillator characteristics

#### $(TA = -40 \text{ to } +85^{\circ}C, 2.7 \text{ V} \le \text{VDD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                                | Resonator          | Conditions                                              | MIN. | TYP. | MAX. | Unit |

|------------------------------------------|--------------------|---------------------------------------------------------|------|------|------|------|

| X1 clock oscillation frequency (fx) Note | Ceramic resonator/ | $2.7~\text{V} \leq \text{V}\text{DD} \leq 5.5~\text{V}$ | 1.0  |      | 20.0 | MHz  |

|                                          | crystal resonator  |                                                         |      |      |      |      |

Note Indicates only permissible oscillator frequency ranges. Refer to AC Characteristics for instruction execution time. Request evaluation by the manufacturer of the oscillator circuit mounted on a board to check the oscillator characteristics.

### 2.3.2 On-chip oscillator characteristics

#### $(TA = -40 \text{ to } +85^{\circ}C, 2.7 \text{ V} \le \text{VDD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Oscillators                                              | Parameters | Conditions | MIN. | TYP. | MAX. | Unit |

|----------------------------------------------------------|------------|------------|------|------|------|------|

| High-speed on-chip oscillator                            | fін        |            | 1    |      | 24   | MHz  |

| clock frequency Notes 1, 2                               | fносо      |            | 1    |      | 48   |      |

| High-speed on-chip oscillator                            |            |            | -2   |      | +2   | %    |

| clock frequency accuracy                                 |            |            |      |      |      |      |

| Low-speed on-chip oscillator<br>clock frequency          | fı∟        |            |      | 15   |      | kHz  |

|                                                          |            |            |      |      |      |      |

| Low-speed on-chip oscillator<br>clock frequency accuracy |            |            | -15  |      | +15  | %    |

Note 1. High-speed on-chip oscillator frequency is selected with bits 0 to 4 of the option byte (000C2H) and bits 0 to 2 of the HOCODIV register.

Note 2. This only indicates the oscillator characteristics. Refer to AC Characteristics for instruction execution time.

Caution Since the CPU is started by the high-speed on-chip oscillator clock after a reset release, check the X1 clock oscillation stabilization time using the oscillation stabilization time counter status register (OSTC) by the user. Determine the oscillation stabilization time of the OSTC register and the oscillation stabilization time select register (OSTS) after sufficiently evaluating the oscillation stabilization time with the resonator to be used.

Remark When using the X1 oscillator, refer to 5.4 System Clock Oscillator in the RL78/G1G User's Manual.

### 2.4 DC Characteristics

### 2.4.1 Pin characteristics

| (TA = -40 to +85°C, 2.7 | $V \leq VDD \leq 5.5 V$ , $Vss = 0 V$ ) |

|-------------------------|-----------------------------------------|

|-------------------------|-----------------------------------------|

| Items                                  | Symbol | Conditions                                                                                                        |                                                          | MIN. | TYP. | MAX.            | Unit |

|----------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|------|-----------------|------|

| Output current, high <sup>Note 1</sup> | Іон1   | Per pin for P00, P01, P10 to P17,<br>P30, P31, P40, P41, P50, P51,<br>P60 to P63, P70 to P73, P120,<br>P146, P147 | $2.7 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V}$       |      |      | -10.0<br>Note 2 | mA   |

|                                        |        | Total of P00, P01, P40, P41, P120                                                                                 | $4.0~V \leq V \text{DD} \leq 5.5~V$                      |      |      | -55.0           | mA   |

|                                        |        | (When duty $\leq$ 70% <sup>Note 3</sup> )                                                                         | $2.7~V \leq V_{DD} < 4.0~V$                              |      |      | -10.0           | mA   |

|                                        |        | Total of P10 to P17, P30, P31,                                                                                    | $4.0~V \leq V \text{DD} \leq 5.5~V$                      |      |      | -80.0           | mA   |

|                                        |        | P50, P51, P60 to P63, P70 to<br>P73, P146, P147<br>(When duty ≤ 70% <sup>Note 3</sup> )                           | $2.7 \text{ V} \le \text{V}_{\text{DD}} < 4.0 \text{ V}$ |      |      | -19.0           | mA   |

|                                        |        | Total of all pins<br>(When duty ≤ 70% <sup>Note 3</sup> )                                                         | $2.7~V \leq V_{DD} \leq 5.5~V$                           |      |      | -135.0          | mA   |

| lo                                     | Іон2   | Per pin for P20 to P27                                                                                            | $2.7~V \leq V \text{DD} \leq 5.5~V$                      |      |      | -0.1<br>Note 2  | mA   |

|                                        |        | Total of all pins<br>(When duty ≤ 70% <sup>Note 3</sup> )                                                         | $2.7~V \leq V\text{DD} \leq 5.5~V$                       |      |      | -1.5            | mA   |

Note 1. Value of current at which the device operation is guaranteed even if the current flows from the VDD pin to an output pin.

**Note 2.** Do not exceed the total current value.

Note 3. Specification under conditions where the duty factor ≤ 70%. The output current value that has changed to the duty factor > 70% the duty ratio can be calculated with the following expression (when changing the duty factor from 70% to n%).

• Total output current of pins = (IOH × 0.7)/(n × 0.01)

<Example> Where n = 80% and IOH = -10.0 mA

Total output current of pins =  $(-10.0 \times 0.7)/(80 \times 0.01) \approx -8.7$  mA

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

Caution P00, P10, P15, P17, P30, P50, P51 do not output high level in N-ch open-drain mode.

| Items                                    | Symbol  | Conditions                                                                                                                |                                                          | MIN. | TYP. | MAX.           | Unit |

|------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|------|----------------|------|

| Output current, low <sup>Note 1</sup> Id | IOL1    | Per pin for P00, P01, P10 to P17,<br>P30, P31, P40, P41, P50, P51,<br>P60 to P63, P70 to P73, P120,<br>P146, P147         |                                                          |      |      | 20.0<br>Note 2 | mA   |

|                                          |         | Total of P00, P01, P40, P41, P120                                                                                         | $4.0~\text{V} \leq \text{V}\text{DD} \leq 5.5~\text{V}$  |      |      | 70.0           | mA   |

|                                          |         | (When duty $\leq$ 70% <sup>Note 3</sup> )                                                                                 | $2.7~V \leq V_{DD} < 4.0~V$                              |      |      | 15.0           | mA   |

|                                          |         | Total of P10 to P17, P30, P31,<br>P50, P51, P60 to P63, P70 to<br>P73, P146, P147<br>(When duty ≤ 70% <sup>Note 3</sup> ) | $4.0~\text{V} \leq \text{Vdd} \leq 5.5~\text{V}$         |      |      | 80.0           | mA   |

|                                          |         |                                                                                                                           | $2.7 \text{ V} \le \text{V}_{\text{DD}} < 4.0 \text{ V}$ |      |      | 35.0           | mA   |

| lc                                       |         | Total of all pins<br>(When duty ≤ 70% <sup>Note 3</sup> )                                                                 |                                                          |      |      | 150.0          | mA   |

|                                          | Iol2 Pe | Per pin for P20 to P27                                                                                                    |                                                          |      |      | 0.4<br>Note 2  | mA   |

|                                          |         | Total of all pins (When duty $\leq$ 70% <sup>Note 3</sup> )                                                               | $2.7~V \leq V \text{DD} \leq 5.5~V$                      |      |      | 5.0            | mA   |

#### (TA = -40 to +85°C, 2.7 V $\leq$ VDD $\leq$ 5.5 V, Vss = 0 V)

Note 1. Value of current at which the device operation is guaranteed even if the current flows from an output pin to the Vss pin.

Note 2. However, do not exceed the total current value.

Note 3. Specification under conditions where the duty factor ≤ 70%. The output current value that has changed to the duty factor > 70% the duty ratio can be calculated with the following expression (when changing the duty factor from 70% to n%).

- Total output current of pins =  $(I_{OL} \times 0.7)/(n \times 0.01)$

- <Example> Where n = 80% and IoL = 10.0 mA

Total output current of pins =  $(10.0 \times 0.7)/(80 \times 0.01) \approx 8.7 \text{ mA}$

However, the current that is allowed to flow into one pin does not vary depending on the duty factor.

A current higher than the absolute maximum rating must not flow into one pin.

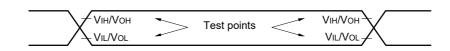

| Items               | Symbol | Conditions                                                                                                    | MIN.                                                                | TYP.    | MAX. | Unit    |   |

|---------------------|--------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------|------|---------|---|

| Input voltage, high | VIH1   | P00, P01, P10 to P17, P30, P31,<br>P40, P41, P50, P51, P60 to P63,<br>P70 to P73, P120 to P124,<br>P146, P147 | Normal input buffer                                                 | 0.8 Vdd |      | Vdd     | V |

|                     | VIH2   | P01, P10, P15 to P17, P30, P31,<br>P50                                                                        | TTL input buffer<br>4.0 V $\leq$ VDD $\leq$ 5.5 V                   | 2.2     |      | Vdd     | V |

|                     |        |                                                                                                               | TTL input buffer $3.3 \text{ V} \leq \text{V}_{DD} < 4.0 \text{ V}$ | 2.0     |      | Vdd     | V |

|                     |        |                                                                                                               | TTL input buffer<br>2.7 V ≤ Vpp < 3.3 V                             | 1.50    |      | Vdd     | V |

|                     | Vінз   | P20 to P27                                                                                                    | l                                                                   | 0.7 Vdd |      | Vdd     | V |

|                     | VIH4   | EXCLK, RESET                                                                                                  |                                                                     | 0.8 Vdd |      | Vdd     | V |

| Input voltage, low  | VIL1   | P00, P01, P10 to P17, P30, P31,<br>P40, P41, P50, P51, P60 to P63,<br>P70 to P73, P120 to P124,<br>P146, P147 | Normal input buffer                                                 | 0       |      | 0.2 VDD | V |

|                     | VIL2   | P01, P10, P15 to P17, P30, P31,<br>P50                                                                        | TTL input buffer<br>4.0 V $\leq$ VDD $\leq$ 5.5 V                   | 0       |      | 0.8     | V |

|                     |        |                                                                                                               | TTL input buffer $3.3 \text{ V} \le \text{V}_{DD} < 4.0 \text{ V}$  | 0       |      | 0.5     | V |

|                     |        |                                                                                                               | TTL input buffer<br>2.7 V ≤ Vpp < 3.3 V                             | 0       |      | 0.32    | V |

|                     | VIL3   | P20 to P27                                                                                                    | •                                                                   | 0       |      | 0.3 Vdd | V |

|                     | VIL4   | EXCLK, RESET                                                                                                  |                                                                     | 0       |      | 0.2 Vdd | V |

### (TA = -40 to +85°C, 2.7 V $\leq$ VDD $\leq$ 5.5 V, Vss = 0 V)

Caution The maximum value of V<sub>IH</sub> of pins P00, P10, P15, P17, P30, P50, and P51 is V<sub>DD</sub>, even in the N-ch open-drain mode.

| Items                | Symbol                       | Condition                                                          | IS                                                                            | MIN.      | TYP. | MAX. | Unit |

|----------------------|------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------|------|------|------|

| Output voltage, high | Voh1                         | P00, P01, P10 to P17, P30, P31,<br>P40, P41, P50, P51, P60 to P63, | 4.0 V ≤ VDD ≤ 5.5 V,<br>IOH1 = -10.0 mA                                       | Vdd - 1.5 |      |      | V    |

|                      |                              | P70 to P73, P120, P146, P147                                       | 4.0 V ≤ VDD ≤ 5.5 V,<br>Іон1 = -3.0 mA                                        | Vdd - 0.7 |      |      | V    |

|                      |                              |                                                                    | 2.7 V ≤ VDD ≤ 5.5 V,<br>Іон1 = -2.0 mA                                        | Vdd - 0.6 |      |      | V    |

|                      |                              |                                                                    | 2.7 V ≤ Vdd ≤ 5.5 V,<br>Іон1 = -1.0 mA                                        | Vdd - 0.5 |      |      | V    |

|                      | Voh2                         | P20 to P27                                                         | 2.7 V ≤ Vdd ≤ 5.5 V,<br>Іон2 = -100 µА                                        | Vdd - 0.5 |      |      | V    |

| Output voltage, low  | VOL1                         | P00, P01, P10 to P17, P30, P31,<br>P40, P41, P50, P51, P60 to P63, | $4.0 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V},$<br>IOL1 = 20.0 mA |           |      | 1.3  | V    |

|                      | P70 to P73, P120, P146, P147 | $4.0 \text{ V} \le \text{Vdd} \le 5.5 \text{ V},$<br>Iol1 = 8.5 mA |                                                                               |           | 0.7  | V    |      |

|                      |                              |                                                                    | $2.7 \text{ V} \leq \text{Vdd} \leq 5.5 \text{ V},$<br>Iol1 = 3.0 mA          |           |      | 0.6  | V    |

|                      |                              |                                                                    | $2.7 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V},$<br>IOL1 = 1.5 mA          |           |      | 0.4  | V    |

|                      |                              |                                                                    | $2.7 \text{ V} \le \text{Vdd} \le 5.5 \text{ V},$<br>Iol1 = 0.3 mA            |           |      | 0.4  | V    |

|                      | Vol2                         | P20 to P27                                                         | $2.7 \text{ V} \leq \text{Vdd} \leq 5.5 \text{ V},$<br>Iol2 = 400 µA          |           |      | 0.4  | V    |

### (Ta = -40 to +85°C, 2.7 V $\leq$ VDD $\leq$ 5.5 V, Vss = 0 V)

Caution P00, P10, P15, P17, P30, P50, and P51 do not output high level in N-ch open-drain mode.

| Items                          | Symbol | Conditi                                                                                                                                       | ons          |                                             | MIN. | TYP. | MAX. | Unit |

|--------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------|------|------|------|------|

| Input leakage<br>current, high | Ilih1  | P00, P01, P10 to P17, P20 to<br>P27, P30, P31, P40, P41, P50,<br>P51, P60 to P63, P70 to P73,<br>P120, P123, P124, P137, P146,<br>P147, RESET | VI = VDD     |                                             |      |      | 1    | μA   |

|                                | Ilih2  | P121, P122 (X1, X2, EXCLK)                                                                                                                    | VI = VDD     | In input port or<br>external clock<br>input |      |      | 1    | μA   |

|                                |        |                                                                                                                                               |              | In resonator connection                     |      |      | 10   | μA   |

| Input leakage<br>current, low  | ILIL1  | P00, P01, P10 to P17, P20 to<br>P27, P30, P31, P40, P41, P50,<br>P51, P60 to P63, P70 to P73,<br>P120, P123, P124, P137, P146,<br>P147, RESET | VI = Vss     |                                             |      |      | -1   | μA   |

|                                | Ilil2  | P121, P122 (X1, X2, EXCLK)                                                                                                                    | VI = VSS     | In input port or<br>external clock<br>input |      |      | -1   | μA   |

|                                |        |                                                                                                                                               |              | In resonator connection                     |      |      | -10  | μA   |

| On-chip pull-up<br>resistance  | Ru     | P00, P01, P10 to P17, P30, P31,<br>P40, P41, P50, P51, P60 to P63,<br>P70 to P73, P120, P146, P147                                            | Vı = Vss, ir | n input port                                | 10   | 20   | 100  | kΩ   |

### (TA = -40 to +85°C, 2.7 V $\leq$ VDD $\leq$ 5.5 V, Vss = 0 V)

(1/2)

### 2.4.2 Supply current characteristics

(1) Flash ROM: 16 KB of 30- pin to 44-pin products

(TA = -40 to +85°C, 2.7 V  $\leq$  VDD  $\leq$  5.5 V, Vss = 0 V)

| (1A 40    | 10 .05 | $\mathbf{O}, \mathbf{Z}.\mathbf{I} \mathbf{V} \geq \mathbf{V}$ | $v_{DD} \ge 5.5 v, v_{SS} = 0$ | •)              |           |                      |      |      |      | (1/2) |

|-----------|--------|----------------------------------------------------------------|--------------------------------|-----------------|-----------|----------------------|------|------|------|-------|

| Parameter | Symbol |                                                                |                                | Conditions      |           |                      | MIN. | TYP. | MAX. | Unit  |

| Supply    | IDD1   | Operating                                                      | HS (high-speed                 | fносо = 48 MHz, | Basic     | VDD = 5.0 V          |      | 1.8  |      | mA    |

| current   |        | mode                                                           | main) mode Notes 3, 4          | fін = 24 MHz    | operation | VDD = 3.0 V          |      | 1.8  |      |       |

| Note 1    |        |                                                                | HS (high-speed                 | fносо = 48 MHz, | Normal    | VDD = 5.0 V          |      | 3.9  | 6.9  | mA    |

|           |        |                                                                | main) mode Notes 3, 4          | fін = 24 MHz    | operation | VDD = 3.0 V          |      | 3.9  | 6.9  |       |

|           |        |                                                                |                                | fносо = 24 MHz, | Normal    | VDD = 5.0 V          |      | 3.7  | 6.3  |       |

|           |        |                                                                |                                | fін = 24 MHz    | operation | VDD = 3.0 V          |      | 3.7  | 6.3  |       |

|           |        |                                                                |                                | fносо = 16 MHz, | Normal    | VDD = 5.0 V          |      | 2.8  | 4.6  |       |

|           |        |                                                                |                                | fін = 16 MHz    | operation | VDD = 3.0 V          |      | 2.8  | 4.6  |       |

|           |        |                                                                | LS (low-speed main)            | fiн = 8 MHz     | Normal    | VDD = 3.0 V          |      | 1.2  | 2.0  | mA    |

|           |        |                                                                | mode Notes 3, 4                |                 | operation |                      |      |      |      |       |

|           |        |                                                                | HS (high-speed                 | fмх = 20 MHz,   | Normal    | Square wave input    |      | 3.1  | 5.3  | mA    |

|           |        |                                                                | main) mode Notes 2, 4          | Vdd = 5.0 V     | operation | Resonator connection |      | 3.3  | 5.5  |       |

|           |        |                                                                |                                | fмх = 20 MHz,   | Normal    | Square wave input    |      | 3.1  | 5.3  |       |

|           |        |                                                                |                                | VDD = 3.0 V     | operation | Resonator connection |      | 3.3  | 5.5  |       |

|           |        |                                                                |                                | fмх = 10 MHz,   | Normal    | Square wave input    |      | 2.0  | 3.1  |       |

|           |        |                                                                |                                | Vdd = 5.0 V     | operation | Resonator connection |      | 2.0  | 3.2  |       |

|           |        |                                                                |                                | fмх = 10 MHz,   | Normal    | Square wave input    |      | 2.0  | 3.1  |       |

|           |        |                                                                |                                | VDD = 3.0 V     | operation | Resonator connection |      | 2.0  | 3.2  | 1     |

|           |        |                                                                | LS (low-speed main)            | fmx = 8 MHz,    | Normal    | Square wave input    |      | 1.2  | 1.9  | mA    |

|           |        |                                                                | mode Notes 2, 4                | VDD = 3.0 V     | operation | Resonator connection |      | 1.2  | 2.0  | 1     |

Note 1. Total current flowing into VDD, including the input leakage current flowing when the level of the input pin is fixed to VDD or Vss. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, comparator, programmable gain amplifier, watchdog timer, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors.

Note 2. When high-speed on-chip oscillator is stopped.

**Note 3.** When high-speed system clock is stopped.

Note 4.Relationship between operation voltage width, operation frequency of CPU and operation mode is as below.HS (high speed main) mode: VDD = 2.7 V to 5.5 V@1 MHz to 24 MHzLS (low speed main) mode: VDD = 2.7 V to 5.5 V@1 MHz to 8 MHz

Remark 1. fmx: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

Remark 2. fHOCO: High-speed on-chip oscillator clock frequency (48 MHz max.)

Remark 3. fill: High-speed on-chip oscillator clock frequency (24 MHz max.)

Remark 4. Temperature condition of the TYP. value is TA = 25°C

### (1) Flash ROM: 16 KB of 30-pin to 44-pin products

| Parameter | Symbol      |                       | Co                    | nditions                     |                      | MIN.     | TYP. | MAX. | Unit |

|-----------|-------------|-----------------------|-----------------------|------------------------------|----------------------|----------|------|------|------|

| Supply    |             | HALT mode             | -                     | fносо = 48 MHz. VDD = 5.0 V  |                      | iviir v. | 0.60 | 2.40 | mA   |

| current   | Note 2      | TIALT MODE            | main) mode Notes 4, 6 | fiн = 24 MHz                 | VDD = 3.0 V          |          | 0.60 | 2.40 |      |

| Note 1    |             |                       | ,                     | fносо = 24 MHz,              | VDD = 5.0 V          |          | 0.40 | 1.83 | 1    |

|           |             |                       |                       | fін = 24 MHz                 | VDD = 3.0 V          |          | 0.40 | 1.83 |      |

|           |             |                       |                       | fносо = 16 MHz,              | VDD = 5.0 V          |          | 0.38 | 1.38 | 1    |

|           |             |                       |                       | fін = 16 MHz                 | VDD = 3.0 V          |          | 0.38 | 1.38 | 1    |

|           |             |                       | LS (low-speed main)   | fiн = 8 MHz                  | VDD = 3.0 V          |          | 260  | 710  | μA   |

|           |             |                       | mode Notes 4, 6       |                              |                      |          |      |      |      |

|           |             | HS (high-speed        | fмх = 20 MHz,         | Square wave input            |                      | 0.28     | 1.55 | mA   |      |

|           |             | main) mode Notes 3, 6 | VDD = 5.0 V           | Resonator connection         |                      | 0.42     | 1.74 |      |      |

|           |             | fмх = 20 MHz,         | Square wave input     |                              | 0.28                 | 1.55     |      |      |      |

|           |             |                       |                       | VDD = 3.0 V                  | Resonator connection |          | 0.42 | 1.74 |      |

|           |             |                       |                       | fмх = 10 MHz,                | Square wave input    |          | 0.19 | 0.86 |      |

|           |             |                       |                       | VDD = 5.0 V<br>fmx = 10 MHz, | Resonator connection |          | 0.27 | 0.93 |      |

|           |             |                       |                       |                              | Square wave input    |          | 0.19 | 0.86 |      |

|           |             |                       |                       | VDD = 3.0 V                  | Resonator connection |          | 0.27 | 0.93 |      |

|           |             |                       | LS (low-speed main)   | fмх = 8 MHz,                 | Square wave input    |          | 95   | 550  | μA   |

|           |             |                       | mode Notes 3, 6       | VDD = 3.0 V                  | Resonator connection |          | 145  | 590  |      |

|           | IDD3        | STOP                  | TA = -40°C            |                              |                      |          | 0.18 | 0.51 | μA   |

| mode Note | mode Note 5 | TA = +25°C            |                       |                              | 0.24                 | 0.51     |      |      |      |

|           |             | TA = +50°C            | TA = +50°C            |                              |                      |          | 0.29 | 1.10 |      |

|           |             |                       | TA = +70°C            |                              |                      |          | 0.41 | 1.90 |      |

|           |             |                       | TA = +85°C            |                              |                      |          | 0.90 | 3.30 |      |

#### 40.4+ +0.5°0 0.7 \/ +\/-. . . . . . . . ....

Note 1. Total current flowing into VDD, including the input leakage current flowing when the level of the input pin is fixed to VDD or Vss. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, comparator, programmable gain amplifier, watchdog timer, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors.

- Note 2. During HALT instruction execution by flash memory.

- Note 3. When high-speed on-chip oscillator is stopped.

- Note 4. When high-speed system clock is stopped.

- Note 5. When high-speed on-chip oscillator and high-speed system clock are stopped. When watchdog timer is stopped. The values below the MAX. column include the leakage current.

- Note 6. Relationship between operation voltage width, operation frequency of CPU and operation mode is as below. HS (high speed main) mode: V\_DD = 2.7 V to 5.5 V@1 MHz to 24 MHz LS (low speed main) mode: VDD = 2.7 V to 5.5 V@1 MHz to 8 MHz

- Remark 1. fmx: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- Remark 2. fHOCO: High-speed on-chip oscillator clock frequency (48 MHz max.)

- Remark 3. fill: High-speed on-chip oscillator clock frequency (24 MHz max.)

- Remark 4. Temperature condition of the TYP. value is TA = 25°C

### (2) Peripheral Functions (Common to all products)

| Parameter                                     | Symbol                     | Conditions          |                                             |                                          |  | TYP.  | MAX.  | Unit |

|-----------------------------------------------|----------------------------|---------------------|---------------------------------------------|------------------------------------------|--|-------|-------|------|

| 12-bit interval timer operating current       | I <sub>IT</sub> Notes 1, 8 |                     |                                             |                                          |  |       |       | μA   |

| Watchdog timer<br>operating current           | IWDT<br>Notes 1, 2         | fı∟ = 15 kHz        | fiL = 15 kHz                                |                                          |  |       |       | μA   |

| A/D converter                                 | IADC Note 3                | When conversion     | Normal mode, AVRER                          | P = VDD = 5.0 V                          |  | 1.3   | 1.7   | mA   |

| operating current                             |                            | at maximum<br>speed | Low voltage mode, A                         | WREFP = VDD = 3.0 V                      |  | 0.5   | 0.7   | mA   |

| A/D converter<br>reference voltage<br>current | IADREF                     |                     |                                             |                                          |  | 75    |       | μA   |

| Temperature sensor operating current          | ITMPS                      |                     |                                             |                                          |  | 75    |       | μA   |

| Comparator operating                          | ICMP Note 4                | Per channel of      | When the comparate                          | or is operating                          |  | 45.0  | 65.0  | μA   |

| current                                       |                            | comparator 1        | When the comparate                          | or is stopped                            |  | 0.0   | 0.1   |      |

| Programmable gain                             | IPGA Note 5                | When the program    | nmable gain amplifier                       | is operating                             |  | 240.0 | 340.0 | μA   |

| amplifier operating<br>current                |                            | When the program    | nmable gain amplifier                       | is stopped                               |  | 0.0   | 0.1   |      |

| LVD operating current                         | ILVI Note 6                |                     |                                             |                                          |  | 0.08  |       | μA   |

| SNOOZE operating                              | Isnoz                      | ADC operation       | The mode is perform                         | ned Note 7                               |  | 0.50  | 0.60  | mA   |

| current                                       |                            |                     | The A/D conversion operations are performed | Low voltage mode<br>AVREFP = VDD = 3.0 V |  | 1.20  | 1.44  | mA   |

|                                               |                            | Simplified SPI (CS  | SI)/UART operation                          |                                          |  | 0.70  | 0.84  | mA   |

#### $(T_A = -40 \text{ to } +85^{\circ}C, 2.7 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

Note 1. When high speed on-chip oscillator and high-speed system clock are stopped.

Note 2. Current flowing only to the watchdog timer (including the operating current of the low-speed on-chip oscillator). The current value of the RL78 microcontroller is the sum of IDD1, IDD2 or IDD3 and IwDT when the watchdog timer operates in STOP mode.

- **Note 3.** Current flowing only to the A/D converter. The current value of the RL78 microcontroller is the sum of IDD1 or IDD2 and IADC when the A/D converter operates in an operation mode or the HALT mode.

- **Note 4.** Current flowing only to the comparator. The current value of the RL78 microcontroller is the sum of IDD1 or IDD2 and ICMP when the comparator operates in operating mode or HALT mode.

**Note 5.** Current flowing only to the programmable gain amplifier. The current value of the RL78 microcontroller is the sum of IDD1 or IDD2 and IPGA when the programmable gain amplifier operates in operating mode or HALT mode.

Note 6. Current flowing only to the LVD circuit. The current value of the RL78 microcontroller is the sum of IDD1, IDD2 or IDD3 and ILVI when the LVD circuit operates in the Operating, HALT or STOP mode.

Note 7. For details on the transition time to SNOOZE mode, refer to 18.3.3 SNOOZE mode in the RL78/G1G User's Manual.

Note 8. Current flowing only to the 12-bit interval timer (excluding the operating current of the low-speed on-chip oscillator). The supply current of the RL78 microcontroller is the sum of the values of either IDD1 or IDD2, and IIT, when the 12-bit interval timer operates in operation mode or HALT mode. When the low-speed on-chip oscillator is selected, IFIL should be added.

- Remark 1. fil: Low-speed on-chip oscillator clock frequency

- Remark 2. fcLk: CPU/peripheral hardware clock frequency

- **Remark 3.** Temperature condition of the TYP. value is  $TA = 25^{\circ}C$

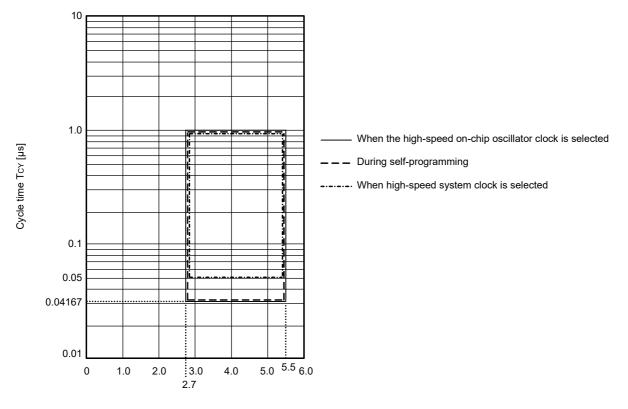

### 2.5 AC Characteristics

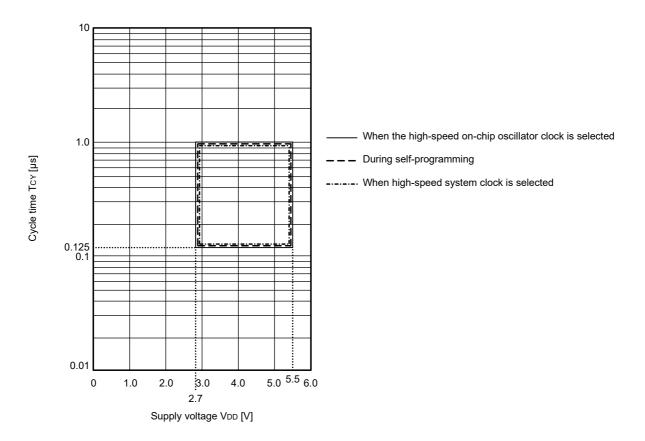

### 2.5.1 Basic operation

| Items                                                                    | Symbol          |                                      | Conditior                 | IS                                                        | MIN.           | TYP. | MAX. | Unit |

|--------------------------------------------------------------------------|-----------------|--------------------------------------|---------------------------|-----------------------------------------------------------|----------------|------|------|------|

| Instruction cycle (minimum instruction execution time)                   | Тсү             | Main system<br>clock (fMAIN)         | HS (high-speed main) mode | $2.7 \text{ V} \leq \text{Vdd} \leq 5.5 \text{ V}$        | 0.04167        |      | 1    | μs   |

|                                                                          |                 | operation                            | LS (low-speed main) mode  | $2.7 \text{ V} \leq \text{Vdd} \leq 5.5 \text{ V}$        | 0.125          |      | 1    | μs   |

|                                                                          |                 | In the self programming              | HS (high-speed main) mode | $2.7 \text{ V} \leq \text{Vdd} \leq 5.5 \text{ V}$        | 0.04167        |      | 1    | μs   |

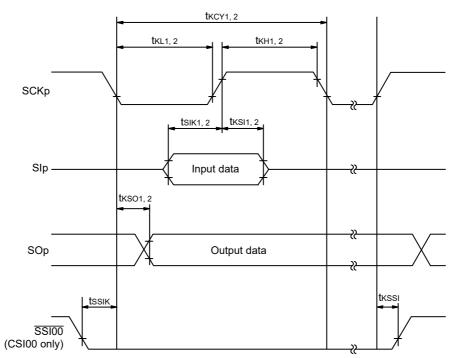

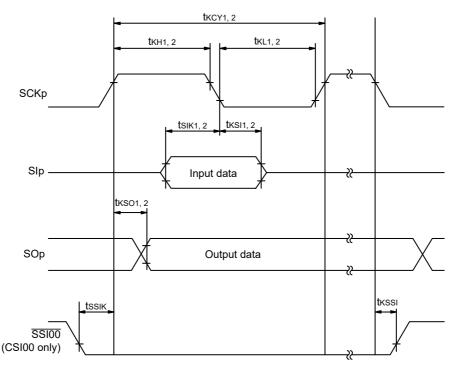

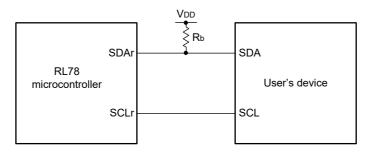

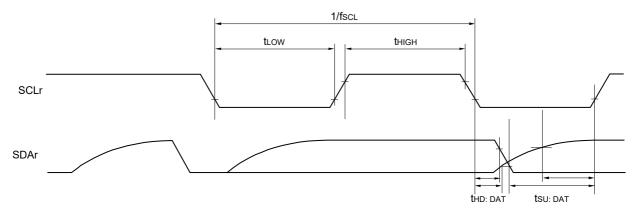

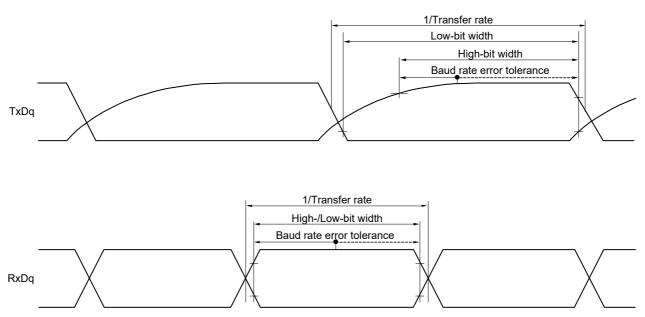

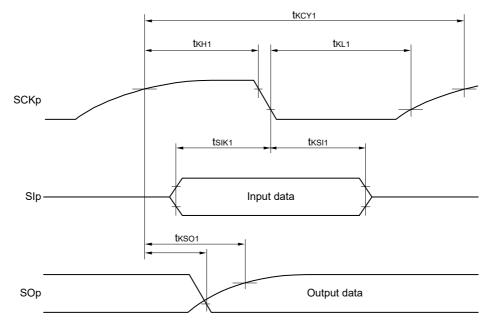

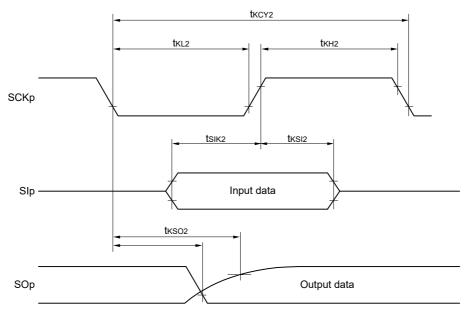

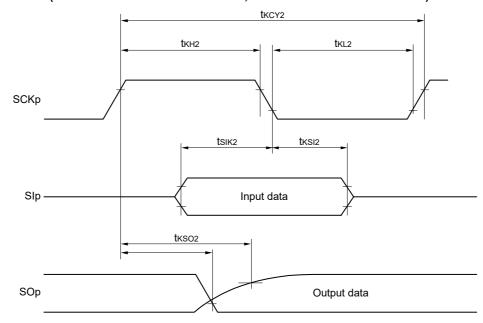

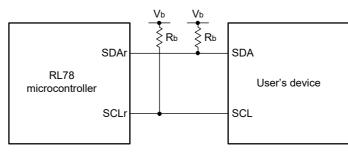

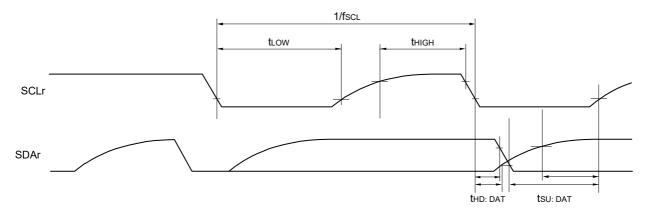

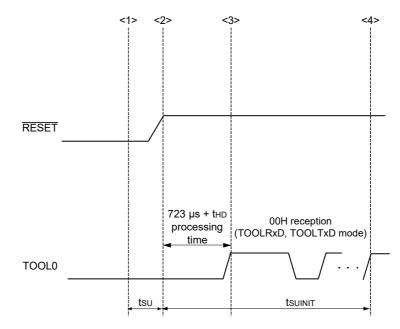

|                                                                          |                 | mode                                 | LS (low-speed main) mode  | $2.7 \text{ V} \leq \text{Vdd} \leq 5.5 \text{ V}$        | 0.125          |      | 1    | μs   |