## RENESAS

## RL78/I1A

## **RENESAS MCU**

## Datasheet

R01DS0171EJ0320 Rev.3.20 Sep 29, 2017

True Low Power Platform, High Resolution PWM and Rich Analog, 2.7 V to 5.5 V operation, 32 to 64 Kbyte Flash, for Inverter Control, Digital Power Control and Lighting Control Applications

## 1. OUTLINE

#### 1.1 Features

#### **Ultra-Low Power Technology**

- 2.7 V to 5.5 V operation from a single supply

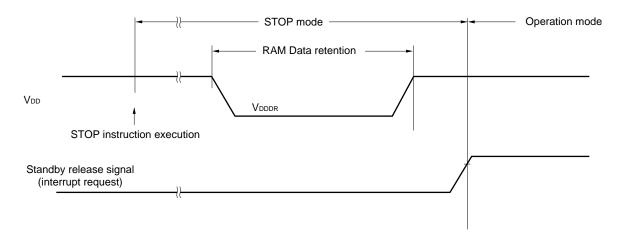

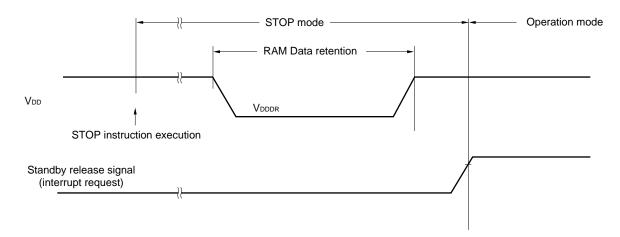

- Stop (RAM retained): 0.23 μA, (LVD enabled): 0.31 μA

- Halt (RTC + LVD): 0.60 μA

- Operating: 156.25 µA/MHz

#### 16-bit RL78 CPU Core

- Delivers 41 DMIPS at maximum operating frequency of 32 MHz

- Instruction execution: 86% of instructions can be executed in 1 to 2 clock cycles

- CISC architecture (Harvard) with 3-stage pipeline

- Multiply signed & unsigned: 16 x 16 to 32-bit result in 1 clock cycle

- MAC: 16 x 16 to 32-bit result in 2 clock cycles

- 16-bit barrel shifter for shift & rotate in 1 clock cycle

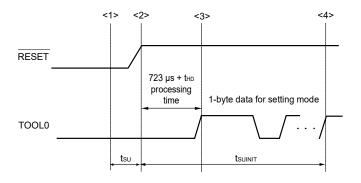

- 1-wire on-chip debug function

#### Main Flash Memory

- Density: 32 KB to 64 KB

- Block size: 1 KB

<R>

<R>

- On-chip single voltage flash memory with protection from block erase/writing

- Self-programming with secure boot swap function and flash shield window function

#### **Data Flash Memory**

- Data flash with background operation

- Data flash size: 4 KB

- Erase cycles: 1 million (typ.)

- Erase/programming voltage: 2.7 V to 5.5 V

#### RAM

- 2 KB to 4 KB size options

- Supports operands or instructions

- Back-up retention in all modes

#### **High-speed On-chip Oscillator**

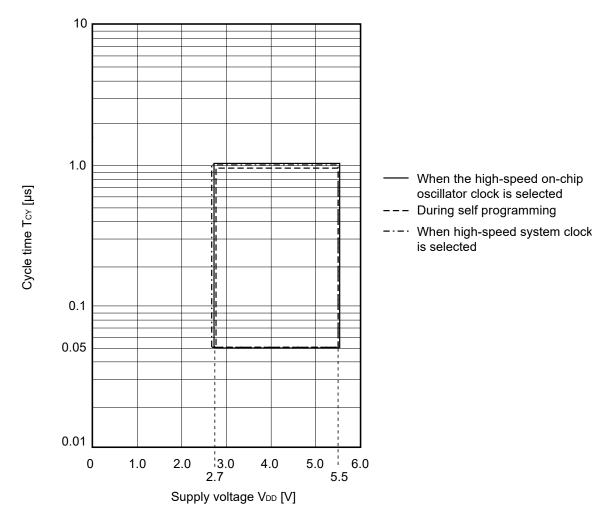

- 32 MHz with +/- 1% accuracy over voltage (2.7 V to 5.5 V) and temperature (-20°C to 85°C)

- Pre-configured settings: 32 MHz, 24 MHz, 16 MHz, 12 MHz, 8 MHz, 6 MHz, 4 MHz, 3 MHz, 2 MHz & 1 MHz

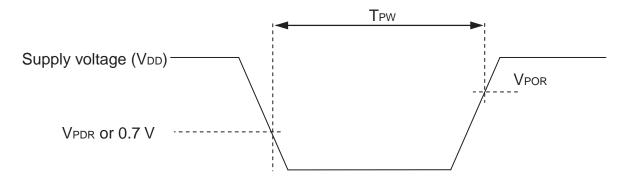

#### **Reset and Supply Management**

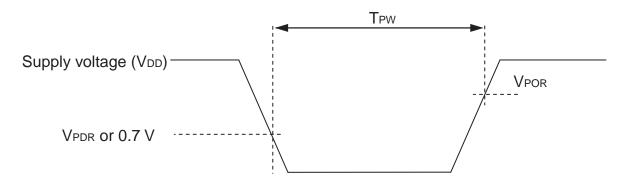

- Power-on reset (POR) monitor/generator

- Low voltage detection (LVD) with 6 setting options (Interrupt and/or reset function)

#### Data Memory Access (DMA) Controller

- Up to 2 fully programmable channels

- Transfer unit: 8- or 16-bit

#### 16-bit timers KB0 to KB2, and KC0 for PWM output

16-bit timers KB0 to KB2: maximum 6 outputs (3 channels × 2)

- Smooth start function, dithering function, forced output stop function (unsynchronized with comparator or external interrupt) enables over-voltage protection, over-current protection and peak current control, and single/interleave PFC function

- Average resolution < 0.98 nsec output, 64 MHz (when using PLL) + dithering option

- 16-bit timer KC0 (1 channel × 6 (output))

- PWM output gating function by interlocking with 16-bit timers KB0, KB1, and KB2

#### **Extended-Function Timers**

- Multi-function 16-bit timers: Up to 8 channels

- Real-time clock (RTC): 1 channel (full calendar and alarm function with watch correction function)

- Interval timer: 12-bit, 1 channel

- 15 kHz watchdog timer: 1 channel (window function)

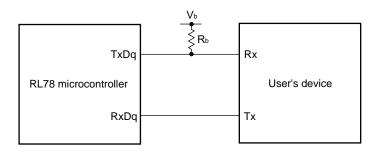

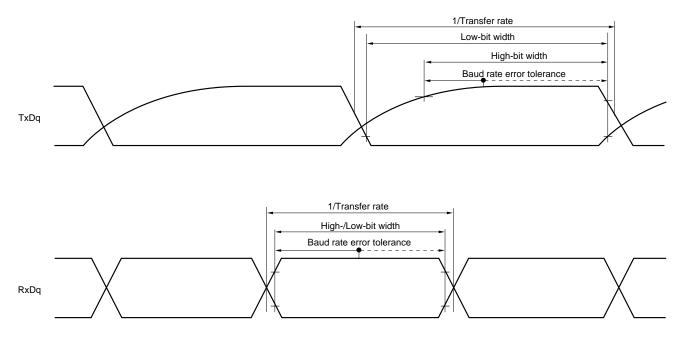

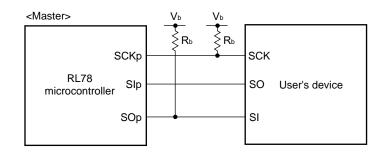

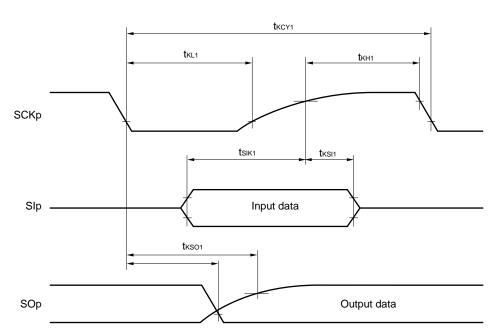

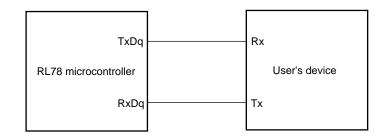

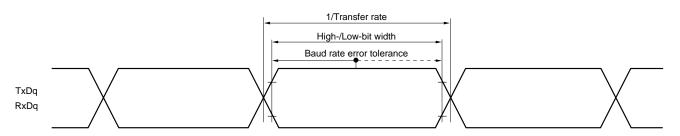

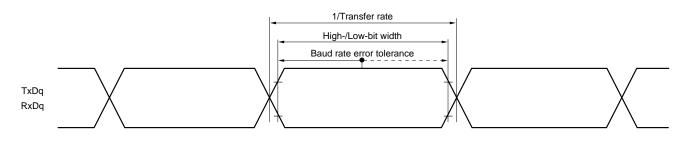

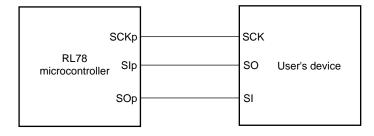

#### Multiple Communication Interfaces

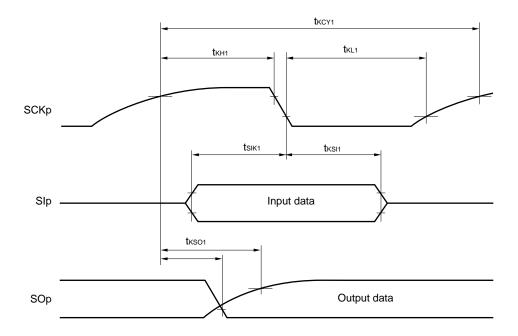

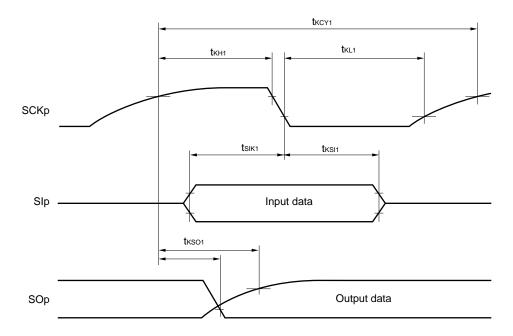

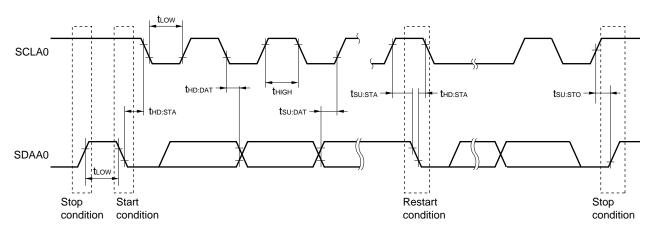

- Up to 1 channel x I<sup>2</sup>C multi-master (SMBus/PMBus support)

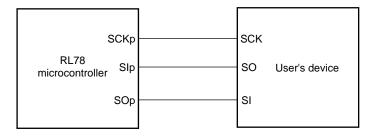

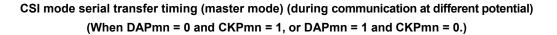

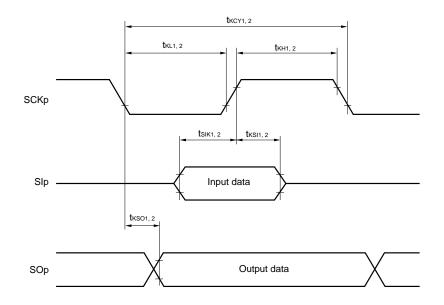

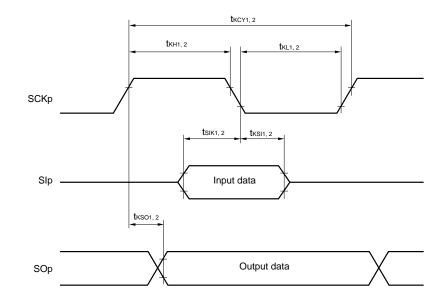

- Up to 1 channel x CSI/SPI (7-, 8-bit)

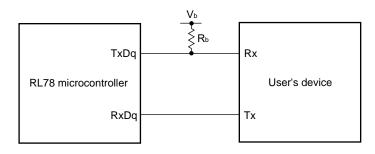

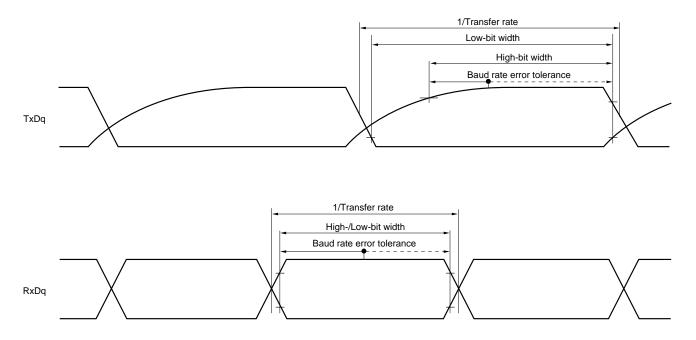

- Up to 3 channels x UART (7-, 8-, 9-bit), DALI support 1 channel (8-, 16-, 17-, 24-bit, master and slave)

- Up to 1 channel x LIN

#### **Rich Analog**

- $\bullet$  ADC: Up to 11 channels, 8/10-bit resolution, 2.125  $\mu s$  conversion time

- Supports 2.7 V

- Internal voltage reference (1.45 V)

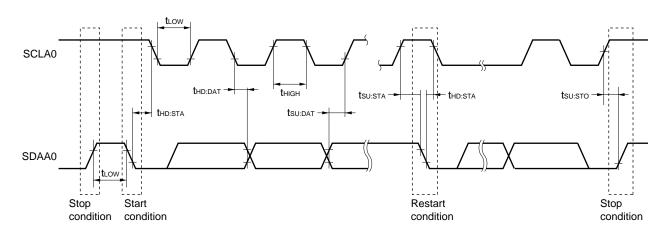

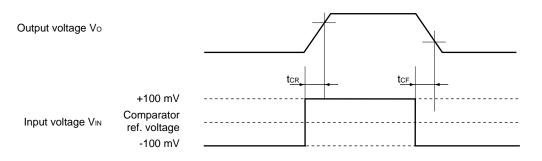

- Comparator: High response time 70 ns (typ.), up to 6 channels, internal DAC 3 channels 8-bit resolution, window comparator mode

- PGA (x4 to x32): 6 input channels

- On-chip temperature sensor

#### Safety Features (IEC or UL 60730 compliance)

- Flash memory CRC calculation

- RAM parity error check

- RAM/SFR write protection

- Illegal memory access detection

- Clock stop/frequency detection

- ADC self-test

- General Purpose I/O

- 5-V tolerant, high-current (up to 8.5 mA per pin)

Open-drain, internal pull-up support

#### Operating Ambient Temperature

- Standard: –40°C to +105°C

- Extend: -40°C to +125°C

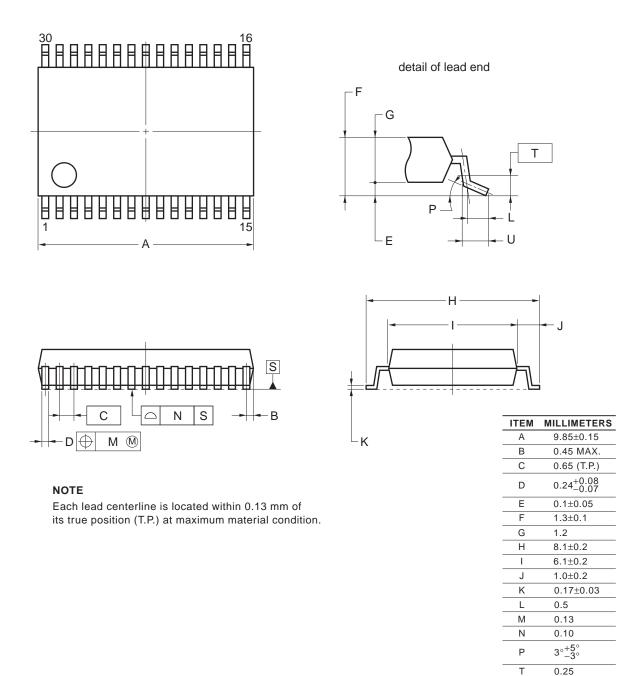

## Package Type and Pin Count SSOP: 20, 30, 38

• ROM, RAM capacities

| Flash ROM | Data flash | RAM                  | RL78/I1A |          |          |  |  |

|-----------|------------|----------------------|----------|----------|----------|--|--|

|           |            |                      | 20 pins  | 30 pins  | 38 pins  |  |  |

| 64 KB     | 4 KB       | 4 KB <sup>Note</sup> | _        | R5F107AE | R5F107DE |  |  |

| 32 KB     | 4 KB       | 2 KB                 | R5F1076C | R5F107AC | -        |  |  |

**Note** This is about 3 KB when the self-programming function and data flash function are used.

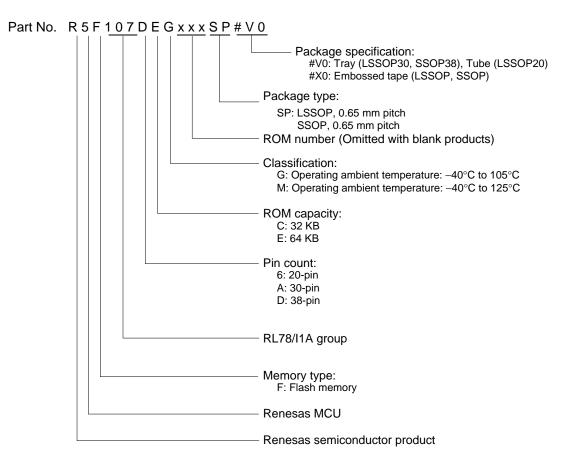

## 1.2 List of Part Numbers

Figure 1-1. Part Number, Memory Size, and Package of RL78/I1A

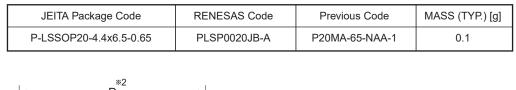

| Pin count                                       | Package              | Operating Ambient<br>Temperature | Part Number                                                       |

|-------------------------------------------------|----------------------|----------------------------------|-------------------------------------------------------------------|

| 20 pins                                         | 20-pin plastic LSSOP | TA = -40 to +105°C               | R5F1076CGSP#V0, R5F1076CGSP#X0                                    |

|                                                 | (4.4 × 6.5)          | TA = -40 to +125°C               | R5F1076CMSP#V0, R5F1076CMSP#X0                                    |

| 30 pins 30-pin plastic LSSOP<br>(7.62 mm (300)) |                      | TA = -40 to +105°C               | R5F107ACGSP#V0, R5F107AEGSP#V0,<br>R5F107ACGSP#X0, R5F107AEGSP#X0 |

|                                                 |                      | TA = -40 to +125°C               | R5F107ACMSP#V0, R5F107AEMSP#V0,<br>R5F107ACMSP#X0, R5F107AEMSP#X0 |

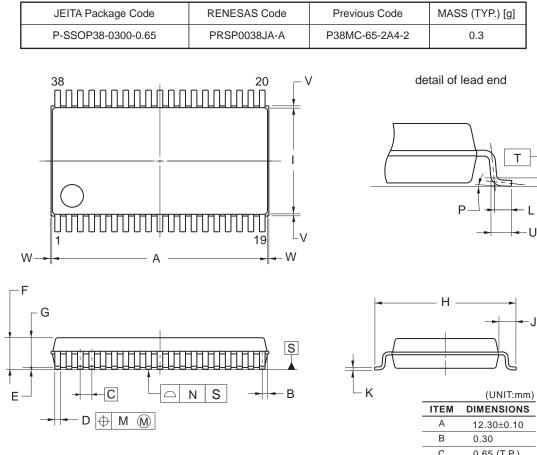

| 38 pins                                         | 38-pin plastic SSOP  | T <sub>A</sub> = -40 to +105°C   | R5F107DEGSP#V0, R5F107DEGSP#X0                                    |

|                                                 | (7.62 mm (300))      | TA = -40 to +125°C               | R5F107DEMSP#V0, R5F107DEMSP#X0                                    |

Caution The ordering part numbers represent the numbers at the time of publication. For the latest ordering part numbers, refer to the target product page of the Renesas Electronics website.

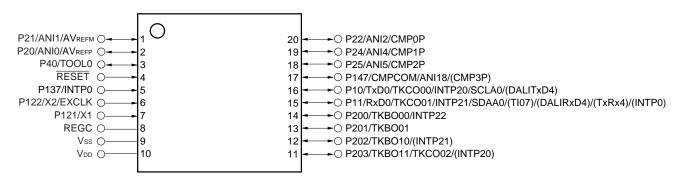

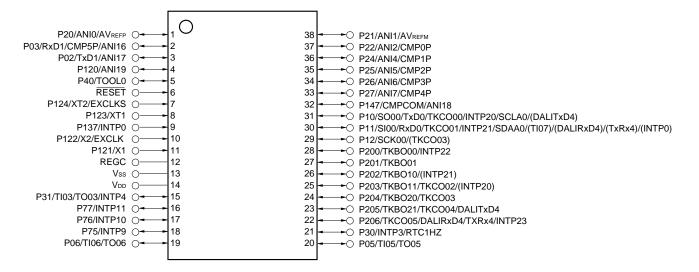

## 1.3 Pin Configuration (Top View)

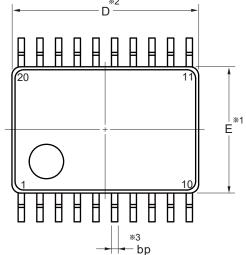

### 1.3.1 20-pin products

• 20-pin plastic LSSOP (4.4 x 6.5)

Remarks 1. For pin identification, see 1.4 Pin Identification.

- Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR1) or the input switch control register (ISC). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR1) and Figure 15-20 Format of Input Switch Control Register (ISC) in the RL78/I1A User's Manual.

- **3.** The shared function CMP3P can be assigned to P147 by setting the CMPSEL0 bit in the comparator input switch control register (CMPSEL).

## 1.3.2 30-pin products

• 30-pin plastic LSSOP (7.62 mm (300))

Caution Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

- Remarks 1. For pin identification, see 1.4 Pin Identification.

- Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR1) or the input switch control register (ISC). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR1) and Figure 15-20 Format of Input Switch Control Register (ISC) in the RL78/I1A User's Manual.

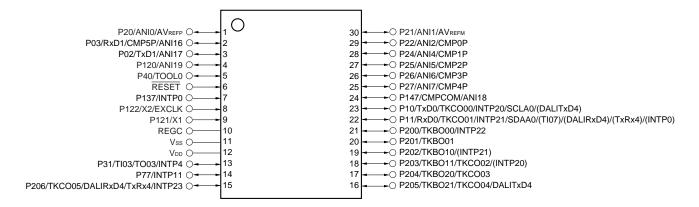

## 1.3.3 38-pin products

• 38-pin plastic SSOP (7.62 mm (300))

#### Caution Connect the REGC pin to Vss via a capacitor (0.47 to 1 $\mu$ F).

Remarks 1. For pin identification, see 1.4 Pin Identification.

Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR1) or the input switch control register (ISC). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR1) and Figure 15-20 Format of Input Switch Control Register (ISC) in the RL78/I1A User's Manual.

## 1.4 Pin Identification

| ANI0 to ANI2,     |                                   | REGC:             | Regulator Capacitance                  |

|-------------------|-----------------------------------|-------------------|----------------------------------------|

| ANI4 to ANI7,     |                                   | RESET:            | Reset                                  |

| ANI16 to ANI19:   | Analog Input                      | RTC1HZ:           | Real-time Clock Correction Clock       |

| AVREFM:           | Analog Reference Voltage Minus    |                   | (1 Hz) Output                          |

| AVREFP:           | Analog Reference Voltage Plus     | RxD0, RxD1,       |                                        |

| CMP0P to CMP5P:   | Comparator Analog Input           | DALIRxD4:         | Receive Data                           |

| CMPCOM:           | Comparator External Reference     | SCK00:            | Serial Clock Input/Output              |

|                   | Voltage                           | SCLA0:            | Serial Clock Input/Output              |

| EXCLK:            | External Clock Input (Main System | SDAA0:            | Serial Data Input/Output               |

|                   | Clock)                            | SI00:             | Serial Data Input                      |

| EXCLKS:           | External Clock Input (Subsystem   | SO00:             | Serial Data Output                     |

|                   | Clock)                            | TI03, TI05, TI06, |                                        |

| INTP0, INTP3,     |                                   | TI07:             | Timer Input                            |

| INTP4, INTP9,     |                                   | TO03, TO05, TO06, |                                        |

| INTP10, INTP11,   |                                   | TKBO00, TKBO01 to | 0                                      |

| INTP20 to INTP23: | Interrupt Request from Peripheral | TKBO20, TKBO21,   |                                        |

| P02, P03,         |                                   | TKCO00 to TKCO05  | : Timer Output                         |

| P05, P06:         | Port 0                            | TOOL0:            | Data Input/Output for Tool             |

| P10 to P12:       | Port 1                            | TxRx4:            | Serial Data Input/Output for Single    |

| P20 to P22,       |                                   |                   | Wired UART                             |

| P24 to P27:       | Port 2                            | TxD0, TxD1        |                                        |

| P30, P31:         | Port 3                            | DALITxD4:         | Transmit Data                          |

| P40:              | Port 4                            | Vdd:              | Power Supply                           |

| P75 to P77:       | Port 7                            | Vss:              | Ground                                 |

| P120 to P124:     | Port 12                           | X1, X2:           | Crystal Oscillator (Main System Clock) |

| P137:             | Port 13                           | XT1, XT2:         | Crystal Oscillator (Subsystem Clock)   |

| P147:             | Port 14                           |                   |                                        |

| P200 to P206:     | Port 20                           |                   |                                        |

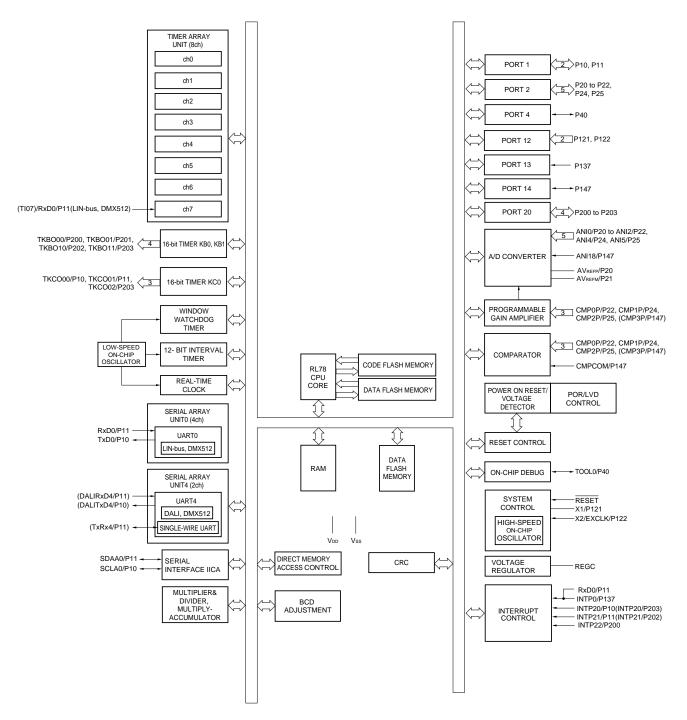

## 1.5 Block Diagram

## 1.5.1 20-pin products

- Remarks 1. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR1) or the input switch control register (ISC). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR1) and Figure 15-20 Format of Input Switch Control Register (ISC) in the RL78/I1A User's Manual.

- **2.** The shared function CMP3P can be assigned to P147 by setting the CMPSEL0 bit in the comparator input switch control register (CMPSEL).

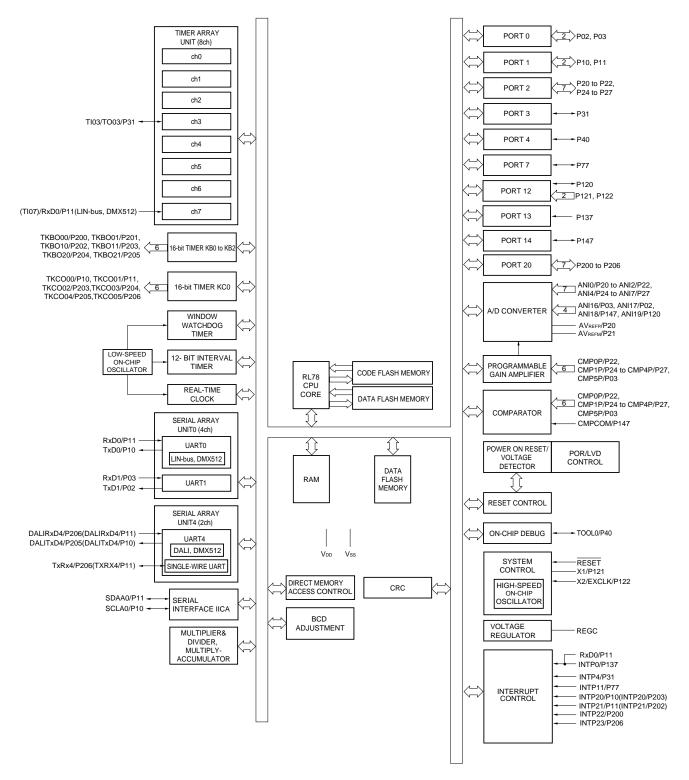

## 1.5.2 30-pin products

Remark Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR1) or the input switch control register (ISC). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR1) and Figure 15-20 Format of Input Switch Control Register (ISC) in the RL78/I1A User's Manual.

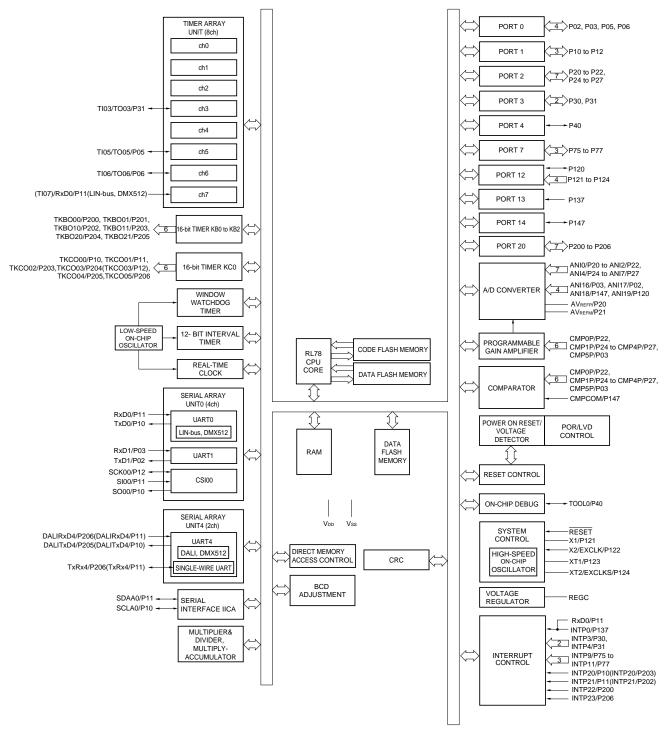

## 1.5.3 38-pin products

Remark Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR1) or the input switch control register (ISC). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR1) and Figure 15-20 Format of Input Switch Control Register (ISC) in the RL78/I1A User's Manual.

## 1.6 Outline of Functions

# Caution This outline describes the functions at the time when Peripheral I/O redirection register (PIOR1) is set to 00H.

|                                                                                                                                      |                            |                                                                                                                  |                                                                                       |                                         | (1/3)                                                                  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------|--|--|--|

|                                                                                                                                      | Item                       | 20-pin                                                                                                           | 30                                                                                    | -pin                                    | 38-pin                                                                 |  |  |  |

|                                                                                                                                      |                            | R5F1076C                                                                                                         | R5F107AC                                                                              | R5F107AE                                | R5F107DE                                                               |  |  |  |

| Code flash m                                                                                                                         | emory (KB)                 | 32                                                                                                               | 32                                                                                    | 64                                      | 64                                                                     |  |  |  |

| Data flash me                                                                                                                        | emory (KB)                 | 4                                                                                                                | 4                                                                                     | 4                                       | 4                                                                      |  |  |  |

| RAM (KB)                                                                                                                             |                            | 2                                                                                                                | 2                                                                                     | 4 <sup>Note 1</sup> 4 <sup>Note 1</sup> |                                                                        |  |  |  |

| Address spac                                                                                                                         | e                          | 1 MB                                                                                                             |                                                                                       |                                         |                                                                        |  |  |  |

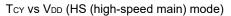

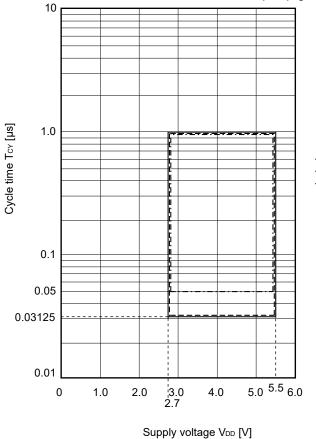

| Main system<br>clock                                                                                                                 | High-speed system<br>clock | HS (High-speed main)                                                                                             | cillation, external main symbols<br>mode: 1 to 20 MHz (Vpp<br>node: 1 to 8 MHz (Vpp = | ,                                       |                                                                        |  |  |  |

| High-speed on-chip<br>oscillatorHS (High-speed main) mode:1 to 32 MHz (V_{DD} = 2.7 to 5.5 V),<br>1 to 8 MHz (V_{DD} = 2.7 to 5.5 V) |                            |                                                                                                                  |                                                                                       |                                         |                                                                        |  |  |  |

| Clock for 16-b<br>and KC0                                                                                                            | bit timers KB0 to KB2,     | 64 MHz (TYP.)                                                                                                    |                                                                                       |                                         |                                                                        |  |  |  |

| Subsystem cl<br>only)                                                                                                                | ock (38-pin products       | XT1 (crystal) oscillation 32.768 kHz                                                                             | , external subsystem clo                                                              | ck input (EXCLKS)                       |                                                                        |  |  |  |

| Low-speed or                                                                                                                         | n-chip oscillator          | 15 kHz (TYP.)                                                                                                    |                                                                                       |                                         |                                                                        |  |  |  |

| General-purp                                                                                                                         | ose register               | (8-bit register $\times$ 8) $\times$ 4 banks                                                                     |                                                                                       |                                         |                                                                        |  |  |  |

| Minimum inst                                                                                                                         | ruction execution time     | 0.03125 µs (High-speed on-chip oscillator: fiн = 32 MHz operation)                                               |                                                                                       |                                         |                                                                        |  |  |  |

|                                                                                                                                      |                            | 0.05 $\mu$ s (High-speed system clock: f <sub>MX</sub> = 20 MHz operation)                                       |                                                                                       |                                         |                                                                        |  |  |  |

|                                                                                                                                      |                            | 30.5 µs (Subsystem clo                                                                                           | ck: fsuв = 32.768 kHz ор                                                              | eration) (38-pin products o             | nly)                                                                   |  |  |  |

| Instruction se                                                                                                                       | t                          | <ul> <li>8-bit operation, 16-bit</li> <li>Multiplication (8 bits &gt;</li> <li>Bit manipulation (Set,</li> </ul> |                                                                                       | n operation), etc.                      |                                                                        |  |  |  |

| I/O port                                                                                                                             | Total                      | 16                                                                                                               |                                                                                       | 26                                      | 34                                                                     |  |  |  |

|                                                                                                                                      | CMOS I/O                   | 13                                                                                                               |                                                                                       | 23                                      | 29                                                                     |  |  |  |

|                                                                                                                                      | CMOS input                 | 3                                                                                                                |                                                                                       | 3                                       | 5                                                                      |  |  |  |

|                                                                                                                                      | CMOS output                | -                                                                                                                |                                                                                       | -                                       | -                                                                      |  |  |  |

| Timer                                                                                                                                | 16-bit timer TAU           | 8 channels (no timer<br>output)                                                                                  | 8 channels (timer outpu                                                               | t: 1, PWM output: 1 <sup>Note 2</sup> ) | 8 channels (timer<br>outputs: 3, PWM<br>outputs: 3 <sup>Note 2</sup> ) |  |  |  |

|                                                                                                                                      | 16-bit timer KB            | 2 channels (PWM outputs: 4)                                                                                      | 3                                                                                     | channels (PWM outputs: 6                | )                                                                      |  |  |  |

|                                                                                                                                      | 16-bit timer KC            | 1 channel (PWM<br>outputs: 3)                                                                                    | 1 channel (PWM outputs: 6)                                                            |                                         |                                                                        |  |  |  |

Notes 1. This is about 3 KB when the self-programming function and data flash function are used. (For details, see CHAPTER 3 in the RL78/I1A User's Manual.)

The number of PWM outputs varies depending on the setting of channels in use (the number of masters and slaves) (see 6.9.3 Operation as multiple PWM output function in the RL78/I1A User's Manual).

|                              |                    |                         |                                                                                                                                                                                                                     |                                                                | (2/3)                                                        |  |  |

|------------------------------|--------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------|--|--|

|                              | Item               |                         | 20-pin                                                                                                                                                                                                              | 30-pin                                                         | 38-pin                                                       |  |  |

|                              |                    |                         | R5F1076C                                                                                                                                                                                                            | R5F107AC, R5F107AE                                             | R5F107DE                                                     |  |  |

| Timer                        | Natchdog           | g timer                 |                                                                                                                                                                                                                     | 1 channel                                                      |                                                              |  |  |

|                              | Real-time<br>RTC)  | clock                   |                                                                                                                                                                                                                     | 1 channel <sup>Notes 1, 2</sup>                                |                                                              |  |  |

|                              | 12-bit inte<br>IT) | erval timer             |                                                                                                                                                                                                                     | 1 channel                                                      |                                                              |  |  |

|                              | RTC outp           | out                     |                                                                                                                                                                                                                     | -                                                              | 1<br>1 Hz (subsystem clock<br>f <sub>SUB</sub> = 32.768 kHz) |  |  |

| 8/10-bit resoluti            | on A/D co          | onverter                | 6 channels                                                                                                                                                                                                          | 11 channels                                                    | 11 channels                                                  |  |  |

| Comparator                   |                    |                         | 4 channels                                                                                                                                                                                                          | 6 channels                                                     | 6 channels                                                   |  |  |

| Programmable                 | gain amp           | lifier                  |                                                                                                                                                                                                                     | 1 channel                                                      | ·                                                            |  |  |

|                              |                    | Input <sup>Note 3</sup> | 4 channels                                                                                                                                                                                                          | 6 channels                                                     | 6 channels                                                   |  |  |

| Serial interface             |                    |                         | [20-pin] Note 5                                                                                                                                                                                                     |                                                                | ·                                                            |  |  |

|                              |                    |                         | UART (Supporting LIN-bus and DMX512): 1 channel                                                                                                                                                                     |                                                                |                                                              |  |  |

|                              |                    |                         | UART (Supporting DALI                                                                                                                                                                                               | communication): 1 channel                                      |                                                              |  |  |

|                              |                    |                         | [30-pin products]                                                                                                                                                                                                   |                                                                |                                                              |  |  |

|                              |                    |                         | UART (Supporting LIN-bus and DMX512): 1 channel                                                                                                                                                                     |                                                                |                                                              |  |  |

|                              |                    |                         | UART: 1 channel                                                                                                                                                                                                     |                                                                |                                                              |  |  |

|                              |                    |                         | UART (Supporting DALI                                                                                                                                                                                               | communication): 1 channel                                      |                                                              |  |  |

|                              |                    |                         | [38-pin products]                                                                                                                                                                                                   |                                                                |                                                              |  |  |

|                              |                    |                         | <ul><li>CSI: 1 channel/UART (S</li><li>UART: 1 channel</li></ul>                                                                                                                                                    | Supporting LIN-bus and DMX512): 1 chan                         | nel                                                          |  |  |

|                              |                    |                         | UART (Supporting DALI                                                                                                                                                                                               | communication): 1 channel                                      |                                                              |  |  |

|                              | l <sup>2</sup> C b | us                      | 1 channel                                                                                                                                                                                                           | 1 channel                                                      | 1 channel                                                    |  |  |

| Multiplier and d accumulator | vider/mul          | ltiply-                 | <ul> <li>16 bits × 16 bits = 32 bits (Unsigned or signed)</li> <li>32 bits ÷ 32 bits = 32 bits (Unsigned)</li> <li>16 bits × 16 bits + 32 bits = 32 bits (Unsigned or signed)</li> </ul>                            |                                                                |                                                              |  |  |

| DMA controller               |                    |                         |                                                                                                                                                                                                                     | 2 channels                                                     |                                                              |  |  |

| Vectored interru             | pt Interr          | nal                     | 27                                                                                                                                                                                                                  | 30                                                             | 30                                                           |  |  |

| sources                      | Exter              |                         | 7                                                                                                                                                                                                                   | 10                                                             | 11                                                           |  |  |

| Reset                        |                    |                         | <ul> <li>Reset by RESET pin</li> <li>Internal reset by watchd</li> <li>Internal reset by power-orego internal reset by voltage</li> <li>Internal reset by illegal in</li> <li>Internal reset by RAM page</li> </ul> | on-reset<br>detector<br>nstruction execution <sup>Note 4</sup> |                                                              |  |  |

|                              |                    |                         | <ul> <li>Internal reset by illegal-r</li> </ul>                                                                                                                                                                     | -                                                              |                                                              |  |  |

Notes 1. The subsystem clock (fsub) can be selected as the operating clock only for 38-pin products.

2. The 20- and 30-pin products can only be used as the constant-period interrupt function.

- 3. The comparator input is alternatively used with analog input pin (ANI pin).

- The illegal instruction is generated when instruction code FFH is executed. Reset by the illegal instruction execution not issued by emulation with the in-circuit emulator or onchip debug emulator.

- 5. The 20 pin products can only be used 1 UART simultaneously due to sharing of the same I/O pins.

|                               |                                    |                                                                                                        | (3/3)    |  |  |  |

|-------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------|----------|--|--|--|

| Item                          | 20-pin                             | 30-pin                                                                                                 | 38-pin   |  |  |  |

|                               | R5F1076C                           | R5F107AC, R5F107AE                                                                                     | R5F107DE |  |  |  |

| Power-on-reset circuit        |                                    | Power-on-reset: 1.51 V (TYP.)<br>Power-down-reset: 1.50 V (TYP.)                                       |          |  |  |  |

| Voltage detector              | 0 0                                | V to 4.06 V (6 stages)<br>5 V to 3.98 V (6 stages)                                                     |          |  |  |  |

| On-chip debug function        | Provided                           |                                                                                                        |          |  |  |  |

| Power supply voltage          | V <sub>DD</sub> = 2.7 to 5.5 V     |                                                                                                        |          |  |  |  |

| Operating ambient temperature | T <sub>A</sub> = -40 to +105°C (G: | $T_A = -40$ to +105°C (G: Industrial applications), $T_A = -40$ to +125°C (M: Industrial applications) |          |  |  |  |

## 2. ELECTRICAL SPECIFICATIONS (G: Industrial applications, $T_A = -40$ to +105°C)

In this chapter, shows the electrical specifications of the target products. Target products (G: Industrial applications):  $T_A = -40$  to  $+105^{\circ}C$ R5F107xxGxx

- Cautions 1. The RL78/I1A has an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

- 2. The pins mounted depend on the product. See 2.1 Port Function to 2.2.1 Functions for each product in the RL78/I1A User's Manual.

#### 2.1 Absolute Maximum Ratings

| Parameter              | Symbols | Conditions                                                                                                                                               | Ratings                                                                                        | Unit |

|------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|

| Supply voltage         | Vdd     |                                                                                                                                                          | –0.5 to +6.5                                                                                   | V    |

| REGC pin input voltage | Viregc  | REGC                                                                                                                                                     | $-0.3$ to +2.8 and $-0.3$ to $V_{\text{DD}}$ +0.3 $^{\text{Note 1}}$                           | V    |

| Input voltage          | Vi1     | P02, P03, P05, P06, P10 to P12, P20 to P22,<br>P24 to P27, P30, P31, P40, P75 to P77,<br>P120 to P124, P137, P147, P200 to P206,<br>EXCLK, EXCLKS, RESET | -0.3 to V <sub>DD</sub> +0.3 <sup>Note 2</sup>                                                 | V    |

| Output voltage         | Vo1     | P02, P03, P05, P06, P10 to P12, P20 to P22,<br>P24 to P27, P30, P31, P40, P75 to P77, P120,<br>P147, P200 to P206                                        | -0.3 to V <sub>DD</sub> +0.3 <sup>Note 2</sup>                                                 | V    |

| Analog input voltage   | Vaii    | ANI0 to ANI2, ANI4 to ANI7, ANI16 to ANI19                                                                                                               | -0.3 to V <sub>DD</sub> +0.3<br>and -0.3 to AV <sub>REF(+)</sub><br>+0.3 <sup>Notes 2, 3</sup> | V    |

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C) (1/2)

- **Notes 1.** Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F). This value regulates the absolute maximum rating of the REGC pin. Do not use this pin with voltage applied to it.

- 2. Must be 6.5 V or lower.

- 3. Do not exceed  $AV_{REF(+)}$  + 0.3 V in case of A/D conversion target pin.

- Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

- **Remarks 1.** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

- 2. AV<sub>REF (+)</sub>: + side reference voltage of the A/D converter.

- **3.** Vss: Reference voltage

| Parameter            | Symbols |                             | Conditions                                                                                | Ratings     | Unit |

|----------------------|---------|-----------------------------|-------------------------------------------------------------------------------------------|-------------|------|

| Output current, high | Іон1    | Per pin                     | P02, P03, P05, P06, P10 to P12,<br>P30, P31, P40, P75 to P77, P120,<br>P147, P200 to P206 | -40         | mA   |

|                      |         | Total of all pins           | P02, P03, P40, P120                                                                       | -70         | mA   |

|                      |         | –170 mA                     | P05, P06, P10 to P12, P30, P31,<br>P75 to P77, P147, P200 to P206                         | -100        | mA   |

|                      | Іон2    | Per pin                     | P20 to P22, P24 to P27                                                                    | -0.5        | mA   |

|                      |         | Total of all pins           |                                                                                           | -2          | mA   |

| Output current, low  | lol1    | Per pin                     | P02, P03, P05, P06, P10 to P12,<br>P30, P31, P40, P75 to P77, P120,<br>P147, P200 to P206 | 40          | mA   |

|                      |         | Total of all pins<br>170 mA | P02, P03, P40, P120                                                                       | 70          | mA   |

|                      |         |                             | P05, P06, P10 to P12, P30, P31,<br>P75 to P77, P147, P200 to P206                         | 100         | mA   |

|                      | IOL2    | Per pin                     | P20 to P22, P24 to P27                                                                    | 1           | mA   |

|                      |         | Total of all pins           |                                                                                           | 5           | mA   |

| Operating ambient    | TA      | In normal operation         | on mode                                                                                   | -40 to +105 | °C   |

| temperature          |         | In flash memory p           | In flash memory programming mode                                                          |             |      |

| Storage temperature  | Tstg    |                             |                                                                                           | -65 to +150 | °C   |

## Absolute Maximum Ratings (T<sub>A</sub> = 25°C) (2/2)

- Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

- **Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

### 2.2 Oscillator Characteristics

### 2.2.1 X1, XT1 oscillator characteristics

#### $(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}, \text{V}_{\text{SS}} = 0 \text{ V})$

| Parameter                                           | Resonator                           | Conditions | MIN. | TYP.   | MAX. | Unit |

|-----------------------------------------------------|-------------------------------------|------------|------|--------|------|------|

| X1 clock oscillation frequency (fx) <sup>Note</sup> | Ceramic resonator/crystal resonator |            | 1.0  |        | 20.0 | MHz  |

| XT1 clock oscillation frequency $(f_{XT})^{Note}$   | Crystal resonator                   |            | 32   | 32.768 | 35   | kHz  |

- **Note** Indicates only permissible oscillator frequency ranges. See **AC Characteristics** for instruction execution time. Request evaluation by the manufacturer of the oscillator circuit mounted on a board to check the oscillator characteristics.

- Caution Since the CPU is started by the high-speed on-chip oscillator clock after a reset release, check the X1 clock oscillation stabilization time using the oscillation stabilization time counter status register (OSTC) by the user. Determine the oscillation stabilization time of the OSTC register and the oscillation stabilization time select register (OSTS) after sufficiently evaluating the oscillation stabilization time with the resonator to be used.

- Remark When using the X1 oscillator and XT1 oscillator, see 5.4 System Clock Oscillator in the RL78/I1A User's Manual.

#### 2.2.2 On-chip oscillator characteristics

#### $(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}, \text{V}_{\text{SS}} = 0 \text{ V})$

| Oscillators                                                        | Parameters | Conditions                    | MIN. | TYP. | MAX. | Unit |

|--------------------------------------------------------------------|------------|-------------------------------|------|------|------|------|

| High-speed on-chip oscillator<br>clock frequency <sup>Note 1</sup> | fін        |                               | 1    |      | 32   | MHz  |

| High-speed on-chip oscillator                                      |            | T <sub>A</sub> = -20 to 85°C  | -1   |      | +1   | %    |

| clock frequency accuracy <sup>Note 2</sup>                         |            | T <sub>A</sub> = -40 to 105°C | -1.5 |      | +1.5 | %    |

| Low-speed on-chip oscillator<br>clock frequency                    | fı∟        |                               |      | 15   |      | kHz  |

| Low-speed on-chip oscillator<br>clock frequency accuracy           |            |                               | -15  |      | +15  | %    |

- **Notes 1.** Frequency can be selected in a high-speed on-chip oscillator. Selected by bits 0 to 3 of option byte (000C2H/010C2H).

- 2. This indicates the oscillator characteristics only. See AC Characteristics for instruction execution time.

#### 2.2.3 PLL characteristics

#### (T\_A = -40 to +105°C, 2.7 V $\leq$ V\_DD $\leq$ 5.5 V, Vss = 0 V)

| Parameter                                     | Symbol | Conditions                                                    | MIN. | TYP.                        | MAX. | Unit |

|-----------------------------------------------|--------|---------------------------------------------------------------|------|-----------------------------|------|------|

| PLL input clock                               | fpllin | High-speed system clock is selected ( $f_{MX}$ = 4 MHz)       | 3.94 | 4.00                        | 4.06 | MHz  |

| frequency <sup>Note</sup>                     |        | High-speed on-chip oscillator clock is selected (fiн = 4 MHz) | 3.94 | 4.00                        | 4.06 | MHz  |

| PLL output clock<br>frequency <sup>Note</sup> | fpll   |                                                               |      | $f_{\text{PLLIN}} 	imes 16$ |      | MHz  |

Note This only indicates the oscillator characteristics. See AC Characteristics for instruction execution time.

## 2.3 DC Characteristics

## 2.3.1 Pin characteristics

#### $(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.7 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{ Vss} = 0 \text{ V})$

| Items                  | Symbol | Conditions                                                                                                             |                                       | MIN. | TYP. | MAX.                   | Unit |

|------------------------|--------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------|------------------------|------|

| Output current,        | Іон1   | Per pin for P02, P03, P05, P06, P10 to P12,                                                                            | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -3.0 <sup>Note 2</sup> | mA   |

| high <sup>Note 1</sup> |        | P30, P31, P40, P75 to P77, P120, P147,<br>P200 to P206                                                                 | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -1.0                   | mA   |

|                        |        | Total of P02, P03, P40, P120                                                                                           | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -12.0                  | mA   |

|                        |        | (When duty $\leq 70\%^{\text{Note 3}}$ )                                                                               | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -4.0                   | mA   |

|                        |        | Total of P05, P06, P10 to P12, P30, P31,<br>P75 to P77, P147, P200 to P206<br>(When duty $\leq 70\%^{\text{Note 3}}$ ) | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -30.0                  | mA   |

|                        |        |                                                                                                                        | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -10.0                  | mA   |

|                        |        | Total of all pins                                                                                                      | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -30.0                  | mA   |

|                        |        | (When duty $\leq 70\%^{\text{Note 3}}$ )                                                                               | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -14.0                  | mA   |

| Іон2                   | Іон2   | Per pin for P20 to P22, P24 to P27                                                                                     | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -0.1 <sup>Note 2</sup> | mA   |

|                        |        | Total of all pins (When duty $\leq 70\%^{Note 3}$ )                                                                    | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -0.7                   | mA   |

- **Notes 1.** Value of current at which the device operation is guaranteed even if the current flows from the V<sub>DD</sub> pin to an output pin.

- 2. However, do not exceed the total current value.

- 3. Specification under conditions where the duty factor  $\leq$  70%. The output current value that has changed to the duty factor > 70% the duty ratio can be calculated

with the following expression (when changing the duty factor from 70% to n%).

• Total output current of pins = (Iон × 0.7)/(n × 0.01)

<Example> Where n = 80% and  $I_{OH}$  = -10.0 mA

Total output current of pins =  $(-10.0 \times 0.7)/(80 \times 0.01) \cong -8.7$  mA

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

#### Caution P02, P10 to P12 do not output high level in N-ch open-drain mode.

| Items                 | Symbol | Conditions                                                                                                             |                                       | MIN. | TYP. | MAX.                  | Unit |

|-----------------------|--------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------|-----------------------|------|

| Output current,       | IOL1   | Per pin for P02, P03, P05, P06,                                                                                        | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 8.5 <sup>Note 2</sup> | mA   |

| IOW <sup>Note 1</sup> |        | P10 to P12, P30, P31, P40,<br>P75 to P77, P120, P147, P200 to P206                                                     | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 1.5 <sup>Note 2</sup> | mA   |

|                       |        | Total of P02, P03, P40, P120                                                                                           | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 40.0                  | mA   |

|                       |        | (When duty $\leq 70\%^{\text{Note 3}}$ )                                                                               | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 7.5                   | mA   |

|                       |        | Total of P05, P06, P10 to P12, P30,<br>P31, P75 to P77, P147, P200 to P206<br>(When duty $\leq 70\%^{\text{Note 3}}$ ) | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 40.0                  | mA   |

|                       |        |                                                                                                                        | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 17.5                  | mA   |

|                       |        | Total of all pins                                                                                                      | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 80.0                  | mA   |

|                       |        | (When duty $\leq 70\%^{\text{Note 3}}$ )                                                                               | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 25.0                  | mA   |

|                       | IOL2   | Per pin for P20 to P22, P24 to P27                                                                                     | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 0.4 <sup>Note 2</sup> | mA   |

|                       |        | Total of all pins (When duty $\leq 70\%^{\text{Note 3}}$ )                                                             | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 2.8                   | mA   |

#### (T\_A = -40 to +105°C, 2.7 V $\leq$ V\_DD $\leq$ 5.5 V, V\_SS = 0 V)

**Notes 1**. Value of current at which the device operation is guaranteed even if the current flows from an output pin to the Vss pin.

- 2. However, do not exceed the total current value.

- **3.** Specification under conditions where the duty factor  $\leq$  70%.

The output current value that has changed to the duty factor > 70% the duty ratio can be calculated with the following expression (when changing the duty factor from 70% to n%).

- Total output current of pins =  $(I_{OL} \times 0.7)/(n \times 0.01)$

- <Example> Where n = 80% and IoL = -10.0 mA

Total output current of pins =  $(-10.0 \times 0.7)/(80 \times 0.01) \approx -8.7$  mA

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

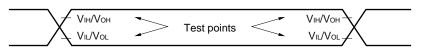

| Items                  | Symbol | Conditions                                                                                                                                                  |                                                                               | MIN.   | TYP. | MAX.               | Unit |

|------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------|------|--------------------|------|

| Input voltage,<br>high | VIH1   | P02, P03, P05, P06, P10 to P12,<br>P20 to P22, P24 to P27, P30, P31,<br>P40, P75 to P77, P120 to P124, P137,<br>P147, P200 to P206, EXCLK,<br>EXCLKS, RESET | Normal input buffer                                                           | 0.8Vdd |      | Vdd                | V    |

|                        | VIH2   | P03, P10, P11                                                                                                                                               | TTL input buffer $4.0 \text{ V} \leq V_{\text{DD}} \leq 5.5 \text{ V}$        | 2.1    |      | Vdd                | V    |

|                        |        |                                                                                                                                                             | TTL input buffer $3.3~V \leq V_{\text{DD}} < 4.0~V$                           | 2.0    |      | Vdd                | V    |

|                        |        |                                                                                                                                                             | TTL input buffer $2.7 \ V \leq V_{\text{DD}} < 3.3 \ V$                       | 1.5    |      | Vdd                | V    |

| Input voltage, low     | VIL1   | P02, P03, P05, P06, P10 to P12,<br>P20 to P22, P24 to P27, P30, P31,<br>P40, P75 to P77, P120 to P124, P137,<br>P147, P200 to P206, EXCLK,<br>EXCLKS, RESET | Normal input buffer                                                           | 0      |      | 0.2V <sub>DD</sub> | V    |

|                        | VIL2   | P03, P10, P11                                                                                                                                               | TTL input buffer $4.0 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$ | 0      |      | 0.8                | V    |

|                        |        |                                                                                                                                                             | TTL input buffer $3.3 \text{ V} \leq V_{\text{DD}} < 4.0 \text{ V}$           | 0      |      | 0.5                | V    |

|                        |        |                                                                                                                                                             | TTL input buffer $2.7 \ V \leq V_{\text{DD}} < 3.3 \ V$                       | 0      |      | 0.32               | V    |

#### (T\_A = -40 to +105°C, 2.7 V $\leq$ V\_DD $\leq$ 5.5 V, V\_SS = 0 V)

#### Caution The maximum value of VIH of pins P02, P10 to P12 is VDD, even in the N-ch open-drain mode.

| Items                   | Symbol                       | Conditions                                                                |                                                                                                                                         | MIN.                | TYP. | MAX. | Unit |

|-------------------------|------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|------|

| Output voltage,<br>high | Vон1                         | P02, P03, P05, P06, P10 to P12, P30,<br>P31, P40, P75 to P77, P120, P147, | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OH1}} = -3.0 \ mA \end{array} \end{array} \label{eq:eq:entropy}$ | $V_{\text{DD}}-0.7$ |      |      | V    |

|                         |                              |                                                                           | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V},$<br>Ioh1 = -1.0 mA                                                           | $V_{\text{DD}}-0.5$ |      |      | V    |

|                         | Vон2                         | P20 to P22, P24 to P27                                                    | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V},$<br>Ioh2 = -100 $\mu$ A                                                      | $V_{\text{DD}}-0.5$ |      |      | V    |

| Output voltage,<br>low  |                              |                                                                           | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 8.5 \ mA \end{array} \end{array} \label{eq:DD}$          |                     |      | 0.7  | V    |

|                         |                              | P200 to P206                                                              | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 4.0 \ mA \end{array} \end{array} \label{eq:DD}$          |                     |      | 0.4  | V    |

|                         |                              |                                                                           | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V},$<br>lol1 = 1.5 mA                                                            |                     |      | 0.4  | V    |

|                         | Vol.2 P20 to P22, P24 to P27 |                                                                           | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V},$<br>Iol2 = 400 $\mu$ A                                                       |                     |      | 0.4  | V    |

#### (T\_A = -40 to +105°C, 2.7 V $\leq$ V\_DD $\leq$ 5.5 V, V\_SS = 0 V)

#### Caution P02, P10 to P12 do not output high level in N-ch open-drain mode.

| Items                          | Symbol | Condition                                                                                                                            | ns           |                                             | MIN. | TYP. | MAX. | Unit |

|--------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------|------|------|------|------|

| Input leakage<br>current, high | ILIH1  | P02, P03, P05, P06, P10 to P12,<br>P20 to P22, P24 to P27, P30,<br>P31, P40, P75 to P77, P120,<br>P137, P147, P200 to P206,<br>RESET | VI = VDD     |                                             |      |      | 1    | μA   |

|                                | Ilih2  | P121 to P124<br>(X1, X2, XT1, XT2, EXCLK,<br>EXCLKS)                                                                                 | VI = VDD     | In input port or<br>external clock<br>input |      |      | 1    | μA   |

|                                |        |                                                                                                                                      |              | In resonator connection                     |      |      | 10   | μA   |

| Input leakage<br>current, low  | ILIL1  | P02, P03, P05, P06, P10 to P12,<br>P20 to P22, P24 to P27, P30,<br>P31, P40, P75 to P77, P120,<br>P137, P147, P200 to P206,<br>RESET | VI = Vss     |                                             |      |      | -1   | μA   |

|                                | Ilil2  | P121 to P124<br>(X1, X2, XT1, XT2, EXCLK,<br>EXCLKS)                                                                                 | VI = Vss     | In input port or<br>external clock<br>input |      |      | -1   | μA   |

|                                |        |                                                                                                                                      |              | In resonator connection                     |      |      | -10  | μA   |

| On-chip pull-up<br>resistance  | Ru     | P02, P03, P05, P06, P10 to P12,<br>P30, P31, P40, P75 to P77,<br>P120, P147, P200 to P206                                            | Vı = Vss, In | input port                                  | 10   | 20   | 100  | kΩ   |

## (T\_A = -40 to +105°C, 2.7 V $\leq$ V\_DD $\leq$ 5.5 V, Vss = 0 V)

### 2.3.2 Supply current characteristics

| 1 | T <sub>A</sub> = -40 to | +105°C  | 27V   | < Vnn < | 55V      | $V_{SS} = 0$ | N N  | (1/2) |

|---|-------------------------|---------|-------|---------|----------|--------------|------|-------|

|   | 1 = -40 10              | T105 C, | Z./ V |         | ≤ 0.0 v, | v 55 - C     | ' ¥) | (1/2) |

| Parameter         | Symbol |                                     |                                                   | Conditions                                                     |                         | MIN. | TYP. | MAX. | Unit |

|-------------------|--------|-------------------------------------|---------------------------------------------------|----------------------------------------------------------------|-------------------------|------|------|------|------|

| Supply            | IDD1   | Operating                           | HS (high-                                         | f⊮ = 32 MHz <sup>Note 3</sup>                                  | V <sub>DD</sub> = 5.0 V |      | 5.0  | 7.5  | mA   |

| Current<br>Note 1 |        | mode                                | speed main)<br>mode <sup>Note 5</sup>             |                                                                | V <sub>DD</sub> = 3.0 V |      | 5.0  | 7.5  | mA   |

|                   |        |                                     | mode                                              | f⊩ = 24 MHz <sup>Note 3</sup>                                  | V <sub>DD</sub> = 5.0 V |      | 3.9  | 5.8  | mA   |

|                   |        |                                     |                                                   |                                                                | V <sub>DD</sub> = 3.0 V |      | 3.9  | 5.8  | mA   |

|                   |        |                                     |                                                   | f⊩ = 16 MHz <sup>Note 3</sup>                                  | V <sub>DD</sub> = 5.0 V |      | 2.9  | 4.2  | mA   |

|                   |        |                                     |                                                   |                                                                | V <sub>DD</sub> = 3.0 V |      | 2.9  | 4.2  | mA   |

|                   |        |                                     | LS (low-<br>speed main)<br>mode <sup>Note 5</sup> | $f_{H} = 8 \text{ MHz}^{\text{Note 3}},$<br>TA = -40 to + 85°C | V <sub>DD</sub> = 3.0 V |      | 1.3  | 2.0  | mA   |

|                   |        |                                     | HS (high-                                         | f <sub>MX</sub> = 20 MHz <sup>Note 2</sup> ,                   | Square wave input       |      | 3.2  | 4.9  | mA   |

|                   |        |                                     | speed main)<br>mode <sup>Note 5</sup>             | V <sub>DD</sub> = 5.0 V                                        | Resonator connection    |      | 3.3  | 5.0  | mA   |

|                   |        |                                     | modense                                           | f <sub>MX</sub> = 20 MHz <sup>Note 2</sup> ,                   | Square wave input       |      | 3.2  | 4.9  | mA   |

|                   |        |                                     |                                                   | V <sub>DD</sub> = 3.0 V                                        | Resonator connection    |      | 3.3  | 5.0  | mA   |

|                   |        |                                     | f <sub>MX</sub> = 10 MHz <sup>Note 2</sup> ,      | Square wave input                                              |                         | 2.0  | 2.9  | mA   |      |

|                   |        |                                     |                                                   | V <sub>DD</sub> = 5.0 V                                        | Resonator connection    |      | 2.0  | 2.9  | mA   |

|                   |        |                                     | f <sub>MX</sub> = 10 MHz <sup>Note 2</sup> ,      | Square wave input                                              |                         | 2.0  | 2.9  | mA   |      |

|                   |        |                                     | V <sub>DD</sub> = 3.0 V                           | Resonator connection                                           |                         | 2.0  | 2.9  | mA   |      |

|                   |        | LS (low-                            | f <sub>MX</sub> = 8 MHz <sup>Note 2</sup> ,       | Square wave input                                              |                         | 1.2  | 1.8  | mA   |      |

|                   |        |                                     | speed main)<br>mode <sup>Note 5</sup>             | V <sub>DD</sub> = 3.0 V,<br>TA = -40 to + 85°C                 | Resonator connection    |      | 1.2  | 1.8  | mA   |

|                   |        |                                     | HS (high-                                         | fi⊢ = 4 MHz <sup>Note 3</sup>                                  | V <sub>DD</sub> = 5.0 V |      | 5.4  | 8.5  | mA   |

|                   |        |                                     | speed main)<br>mode <sup>Note 5</sup>             | fpll = 64 MHz, fclk = 32 MHz                                   | V <sub>DD</sub> = 3.0 V |      | 5.4  | 8.5  | mA   |

|                   |        |                                     | mode                                              | fi⊢ = 4 MHz <sup>Note 3</sup>                                  | V <sub>DD</sub> = 5.0 V |      | 3.3  | 5.7  | mA   |

|                   |        |                                     |                                                   | fpll = 64 MHz, fclк = 16 MHz                                   | V <sub>DD</sub> = 3.0 V |      | 3.3  | 5.7  | mA   |

|                   |        |                                     | Subsystem                                         | fsue = 32.768 kHz <sup>Note 4</sup>                            | Square wave input       |      | 4.2  | 6.0  | μA   |

|                   |        |                                     | clock<br>operation                                | $T_A = -40^{\circ}C$                                           | Resonator connection    |      | 4.4  | 6.2  | μA   |

|                   |        |                                     | operation                                         | fsue = 32.768 kHz <sup>Note 4</sup>                            | Square wave input       |      | 4.2  | 6.0  | μA   |

|                   |        |                                     |                                                   | T <sub>A</sub> = +25°C                                         | Resonator connection    |      | 4.4  | 6.2  | μA   |

|                   |        |                                     |                                                   | fsue = 32.768 kHz <sup>Note 4</sup>                            | Square wave input       |      | 4.3  | 7.2  | μA   |

|                   |        |                                     |                                                   | T <sub>A</sub> = +50°C                                         | Resonator connection    |      | 4.5  | 7.4  | μA   |

|                   |        |                                     |                                                   | fsue = 32.768 kHz <sup>Note 4</sup>                            | Square wave input       |      | 4.4  | 8.1  | μA   |

|                   |        |                                     | T <sub>A</sub> = +70°C                            | Resonator connection                                           |                         | 4.6  | 8.3  | μA   |      |

|                   |        |                                     | fsue = 32.768 kHz <sup>Note 4</sup>               | Square wave input                                              |                         | 5.2  | 11.4 | μA   |      |

|                   |        |                                     |                                                   | T <sub>A</sub> = +85°C                                         | Resonator connection    |      | 5.4  | 11.6 | μA   |

|                   |        | fsue = 32.768 kHz <sup>Note 4</sup> | Square wave input                                 |                                                                | 6.9                     | 20.8 | μA   |      |      |

|                   |        | T <sub>A</sub> = +105°C             | Resonator connection                              |                                                                | 7.1                     | 21.0 | μA   |      |      |

(Notes and Remarks are listed on the next page.)

- **Notes 1.** Total current flowing into V<sub>DD</sub>, including the input leakage current flowing when the level of the input pin is fixed to V<sub>DD</sub> or V<sub>SS</sub>. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, comparator, programmable gain amplifier, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

- 2. When high-speed on-chip oscillator and subsystem clock are stopped.

- 3. When high-speed system clock and subsystem clock are stopped.