## NOT RECOMMENDED FOR NEW DESIGNS RECOMMENDED REPLACEMENT PART ISL8014A

ISL8014

4A Low Quiescent Current 1MHz High Efficiency Synchronous Buck Regulator

FN6576 Rev 4.00 November 23, 2009

The ISL8014 is a high efficiency, monolithic, synchronous step-down DC/DC converter that can deliver up to 4A continuous output current from a 2.7V to 5.5V input supply. It uses a current control architecture to deliver very low duty cycle operation at high frequency with fast transient response and excellent loop stability.

The ISL8014 integrates a pair of low ON-resistance P-Channel and N-Channel internal MOSFETs to maximize efficiency and minimize external component count. The 100% duty-cycle operation allows less than 400mV dropout voltage at 4A output current. High 1MHz pulse-width modulation (PWM) switching frequency allows the use of small external components and SYNC input enables multiple ICs to synchronize out of phase to reduce ripple and eliminate beat frequencies.

The ISL8014 can be configured for discontinuous or forced continuous operation at light load. Forced continuous operation reduces noise and RF interference while discontinuous mode provides high efficiency by reducing switching losses at light loads.

Fault protection is provided by internal hiccup mode current limiting during short circuit and overcurrent conditions, an output over voltage comparator and over-temperature monitor circuit. A power good output voltage monitor indicates when the output is in regulation.

The ISL8014 is offered in a space saving 4x4 QFN lead free package with exposed pad lead frames for low thermal.

The ISL8014 offers a 1ms Power-Good (PG) timer at power-up. When shutdown, ISL8014 discharges the output capacitor. Other features include internal soft-start, internal compensation, overcurrent protection, and thermal shutdown.

The ISL8014 is offered in a 16 Ld 4mmx4mm QFN package with 1mm maximum height. The complete converter occupies less than 0.4in<sup>2</sup> area.

## **Features**

- High Efficiency Synchronous Buck Regulator with up to 97% Efficiency

- · Power-Good (PG) Output with a 1ms Delay

- 2.7V to 5.5V Supply Voltage

- 3% Output Accuracy Over-Temperature/Load/Line

- 4A Output Current

- Pin Compatible to ISL8013

- · Start-up with Pre-Biased Output

- Internal Soft-Start 1ms

- Soft-Stop Output Discharge During Disabled

- 35µA Quiescent Supply Current in PFM Mode

- Selectable Forced PWM Mode and PFM Mode

- External Synchronization up to 4MHz

- Less than 1µA Logic Controlled Shutdown Current

- 100% Maximum Duty Cycle

- Internal Current Mode Compensation

- Peak Current Limiting and Hiccup Mode Short Circuit Protection

- Over-Temperature Protection

- Small 16 Ld 4mmx4mm QFN

- · Pb-Free (RoHS Compliant)

## **Applications**

- DC/DC POL Modules

- μC/μP, FPGA and DSP Power

- Plug-in DC/DC Modules for Routers and Switchers

- · Portable Instruments

- Test and Measurement Systems

- · Li-ion Battery Powered Devices

- · Small Form Factor (SFP) Modules

- · Bar Code Readers

## **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | TEMP.<br>RANGE<br>(°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|--------------------------------|-----------------|------------------------|----------------------|----------------|

| ISL8014IRZ                     | 80 14IRZ        | -40 to +85             | 16 Ld 4x4 QFN        | L16.4x4        |

#### NOTES:

- 1. Add "-T" suffix for tape and reel. Please refer to <a href="IB347">IB347</a> for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL8014</u>. For more information on MSL please see techbrief <u>TB363</u>.

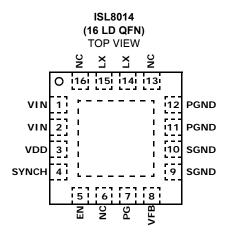

## **Pin Configuration**

## **Pin Descriptions**

| PIN NUMBER | PIN NAME    | DESCRIPTION                                                                                                                                                                                                                                                                 |

|------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2       | VIN         | Input supply voltage. Connect a 10µF ceramic capacitor to power ground.                                                                                                                                                                                                     |

| 3          | VDD         | Input supply voltage for the analog circuitry. Connect to VIN pin.                                                                                                                                                                                                          |

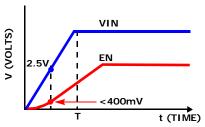

| 5          | EN          | Regulator enable pin. Keep the EN voltage low in disabled state until VIN settles or is above 2.5V. Enable the output when driven to high. Shut down the chip and discharge output capacitor when driven to low. Do not connect directly to VIN or leave this pin floating. |

| 7          | PG          | 1ms timer output. At power-up or EN HI, this output is a 1ms delayed Power-Good signal for the output voltage.                                                                                                                                                              |

| 4          | SYNCH       | Mode Selection pin. Connect to logic high or input voltage VDD for PWM mode. Connect to logic low or ground for PFM mode. Connect to an external function generator for synchronization with the negative edge trigger. Do not leave this pin floating.                     |

| 14, 15     | LX          | Switching node connection. Connect to one terminal of the inductor.                                                                                                                                                                                                         |

| 11, 12     | PGND        | Power ground                                                                                                                                                                                                                                                                |

| 9, 10      | SGND        | Signal ground.                                                                                                                                                                                                                                                              |

| 8          | VFB         | Buck regulator output feedback. Connect to the output through a resistor divider for adjustable output voltage. For 0.8V output voltage, connect this pin to the output.                                                                                                    |

| 6, 13, 16  | NC          | No connect.                                                                                                                                                                                                                                                                 |

| -          | Exposed Pad | The exposed pad must be connected to the SGND pin for proper electrical performance. Place as much vias as possible under the pad connecting to SGND plane for optimal thermal performance.                                                                                 |

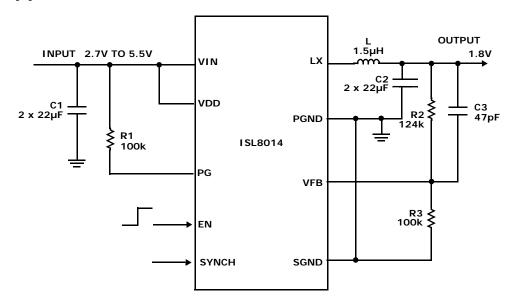

# **Typical Application**

FIGURE 1. TYPICAL APPLICATION DIAGRAM

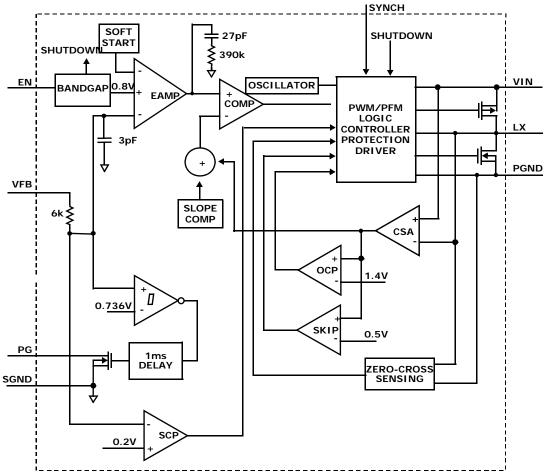

## **Block Diagram**

FIGURE 2. FUNCTIONAL BLOCK DIAGRAM

### Absolute Maximum Ratings (Reference to GND)

| VIN, VDD0.3V to                | o 6V (DC) or 7V (20ms) |

|--------------------------------|------------------------|

| EN, SYNCH, PG                  | 0.3V to VIN + 0.3V     |

| LX1.5V (100ns)/-0.3V (DC) to 6 | 6.5V (DC) or 7V (20ms) |

| VFB                            | 0.3V to 2.7V           |

## **Recommended Operating Conditions**

| VIN Supply Voltage Range  | . 2.7V to 5.5V |

|---------------------------|----------------|

| Load Current Range        | 0A to 4A       |

| Ambient Temperature Range | 40°C to +85°C  |

#### Thermal Information

$\label{eq:continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous$

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTE

- θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 5. θ<sub>JC</sub>, "case temperature" location is at the center of the exposed metal pad on the package underside. See Tech Brief TB379.

### **Electrical Specifications**

Unless otherwise noted, all parameter limits are established over the recommended operating conditions and the typical specification are measured at the following conditions:  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $V_{IN} = 3.6\text{V}$ , EN = VDD, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ . Boldface limits apply over the operating temperature range,  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ .

| PARAMETER                              | SYMBOL             | TEST CONDITIONS                                                | MIN<br>(Note 7) | ТҮР  | MAX<br>(Note 7) | UNITS        |

|----------------------------------------|--------------------|----------------------------------------------------------------|-----------------|------|-----------------|--------------|

| INPUT SUPPLY                           |                    |                                                                |                 |      |                 |              |

| V <sub>DD</sub> Undervoltage Lockout   | V <sub>UVLO</sub>  | Rising, no load                                                | -               | 2.5  | 2.7             | V            |

| Threshold                              |                    | Falling, no load                                               | 2.2             | 2.4  | -               | V            |

| Quiescent Supply Current               | I <sub>VIN</sub>   | SYNCH = GND, no load at the output                             | -               | 35   | -               | μΑ           |

|                                        |                    | SYNCH = GND, no load at the output and no switches switching   | -               | 30   | 45              | μА           |

|                                        |                    | SYNCH = VDD, $F_S$ = 1MHz, no load at the output               | -               | 6.5  | 10              | mA           |

| Shut Down Supply Current               | I <sub>SD</sub>    | $V_{IN} = 5.5V$ , $EN = low$                                   | -               | 0.1  | 2               | μΑ           |

| OUTPUT REGULATION                      |                    |                                                                | ll.             | l    | I.              |              |

| Reference Voltage                      | V <sub>REF</sub>   |                                                                | 0.790           | 0.8  | 0.810           | V            |

| VFB Bias Current                       | I <sub>VFB</sub>   | VFB = 0.75V                                                    | -               | 0.1  | -               | μΑ           |

| Line Regulation                        |                    | $V_{IN} = V_O + 0.5V \text{ to } 5.5V \text{ (minimal } 2.7V)$ | -               | 0.2  | -               | %/V          |

| Soft-Start Ramp Time Cycle             |                    |                                                                | -               | 1    | -               | ms           |

| OVERCURRENT PROTECTION                 |                    |                                                                |                 |      |                 |              |

| Current Limit Blanking Time            | t <sub>OCON</sub>  |                                                                | -               | 17   | -               | Clock pulses |

| Overcurrent and Auto Restart<br>Period | tocoff             |                                                                | -               | 4    | -               | SS cycle     |

| Switch Current Limit                   | I <sub>LIMIT</sub> | (Note 6)                                                       | 4.9             | 6.0  | 7.1             | А            |

| Peak Skip Limit                        | I <sub>SKIP</sub>  | (Note 6)                                                       | -               | 1.3  | -               | А            |

| COMPENSATION                           |                    |                                                                |                 | •    |                 |              |

| Error Amplifier<br>Trans-Conductance   |                    |                                                                | -               | 20   | -               | μΑ/V         |

| Trans-Resistance                       | RT                 |                                                                | 0.17            | 0.20 | 0.23            | Ω            |

## **Electrical Specifications**

Unless otherwise noted, all parameter limits are established over the recommended operating conditions and the typical specification are measured at the following conditions:  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $V_{IN} = 3.6\text{V}$ , EN = VDD, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ . Boldface limits apply over the operating temperature range, -40°C to +85°C. (Continued)

| PARAMETER                             | SYMBOL          | TEST CONDITIONS                              | MIN<br>(Note 7) | ТҮР  | MAX<br>(Note 7) | UNITS |

|---------------------------------------|-----------------|----------------------------------------------|-----------------|------|-----------------|-------|

| LX                                    |                 |                                              |                 |      |                 |       |

| P-Channel MOSFET                      |                 | $V_{IN} = 5V, I_O = 200mA$                   | -               | 50   | 75              | mΩ    |

| ON-Resistance                         |                 | $V_{1N} = 2.7V$ , $I_{O} = 200mA$            | -               | 70   | 100             | mΩ    |

| N-Channel MOSFET                      |                 | V <sub>IN</sub> = 5V, I <sub>O</sub> = 200mA | -               | 50   | 75              | mΩ    |

| ON-Resistance                         |                 | $V_{1N} = 2.7V$ , $I_{O} = 200mA$            | -               | 70   | 100             | mΩ    |

| LX Maximum Duty Cycle                 |                 |                                              | -               | 100  | -               | %     |

| PWM Switching Frequency               | f <sub>S</sub>  |                                              | 0.80            | 1.0  | 1.20            | MHz   |

| LX Minimum On-Time                    |                 | SYNCH = High                                 | -               | -    | 140             | ns    |

| PG                                    | 1               |                                              |                 |      | 1               |       |

| Output Low Voltage                    |                 | Sinking 1mA                                  | -               | -    | 0.3             | V     |

| Delay Time (Rising Edge)              |                 |                                              | 0.65            | 1    | 1.35            | ms    |

| PG Pin Leakage Current                |                 | $PG = V_{IN} = 3.6V$                         | -               | 0.01 | 0.1             | μΑ    |

| PGOOD Rising Threshold                |                 | Percentage of regulation voltage             | 89              | 92   | 95              | %     |

| PGOOD Falling Threshold               |                 | Percentage of regulation voltage             | 85              | 88   | 91              | %     |

| PGOOD Delay Time (Falling Edge)       |                 |                                              | -               | 15   | -               | μs    |

| EN, SYNCH                             | 1               |                                              |                 |      | 1               |       |

| Logic Input Low                       |                 |                                              | -               | -    | 0.4             | V     |

| Logic Input High                      |                 |                                              | 1.4             | -    | -               | V     |

| Synch Logic Input Leakage<br>Current  | ISYNCH          | Pulled up to 5.5V                            | -               | 0.1  | 1               | μΑ    |

| Enable Logic Input Leakage<br>Current | I <sub>EN</sub> |                                              | -               | 0.1  | 1               | μΑ    |

| Thermal Shutdown                      |                 |                                              | -               | 140  | -               | °C    |

| Thermal Shutdown Hysteresis           |                 |                                              | -               | 25   | -               | °C    |

### NOTES:

- 6. Limits established by characterization and are not production tested.

- 7. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

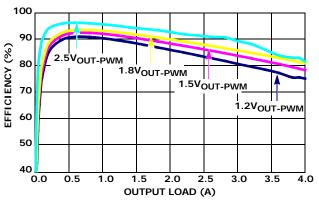

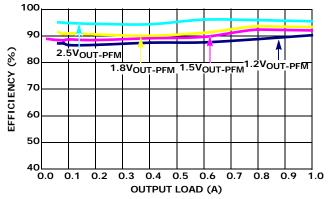

FIGURE 3. EFFICIENCY vs LOAD (1MHz 3.3 V<sub>IN</sub> PWM)

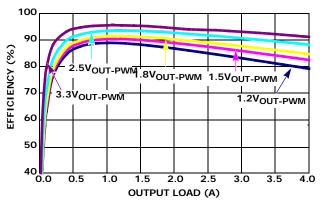

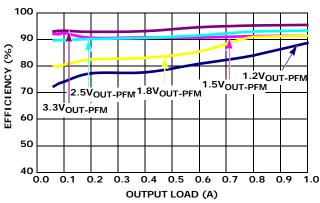

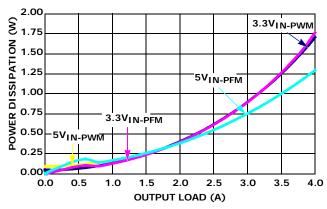

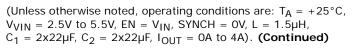

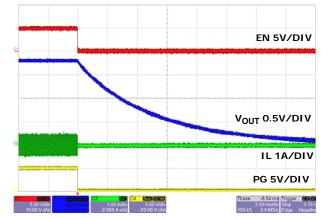

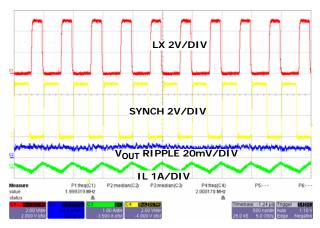

(Unless otherwise noted, operating conditions are:  $T_A=+25\,^{\circ}\text{C},$   $V_{VIN}=2.5V$  to 5.5V, EN =  $V_{IN},$  SYNCH = 0V, L = 1.5 $\mu\text{H},$  C1 = 2x22 $\mu\text{F},$  C2 = 2x22 $\mu\text{F},$  I\_OUT = 0A to 4A).

FIGURE 4. EFFICIENCY vs LOAD (1MHz 3.3 VIN PFM)

FIGURE 5. EFFICIENCY vs LOAD (1MHz 5VIN PWM)

FIGURE 6. EFFICIENCY vs LOAD (1MHz 5VIN PFM)

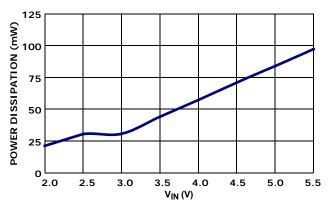

FIGURE 7. POWER DISSIPATION vs LOAD (1MHz,  $V_{OUT} = 1.8V$ )

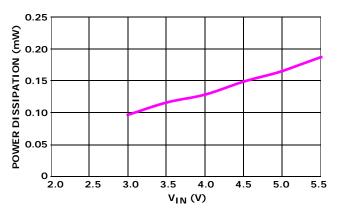

FIGURE 8. POWER DISSIPATION WITH NO LOAD vs  $V_{IN}$  (PWM  $V_{OUT} = 1.8V$ )

FIGURE 9. POWER DISSIPATION WITH NO LOAD vs  $V_{IN}$  (PFM  $V_{OUT} = 1.8V$ )

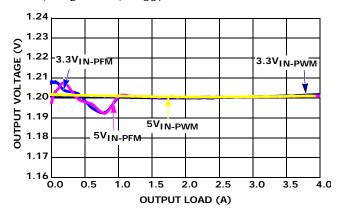

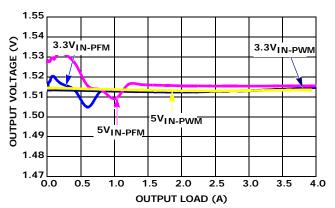

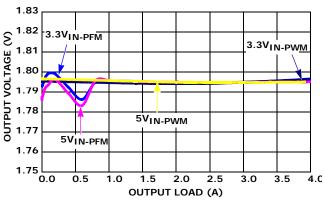

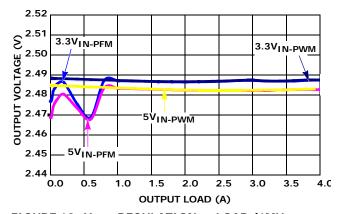

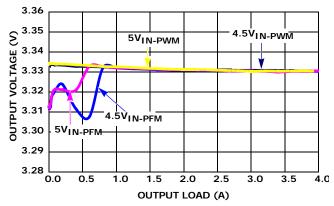

(Unless otherwise noted, operating conditions are:  $T_A=+25\,^{\circ}C$ ,  $V_{VIN}=2.5V$  to 5.5V, EN =  $V_{IN}$ , SYNCH = 0V, L = 1.5µH,  $C_1=2x22\mu F$ ,  $C_2=2x22\mu F$ ,  $I_{OUT}=0A$  to 4A). (Continued)

FIGURE 10.  $V_{OUT}$  REGULATION vs LOAD (1MHz,  $V_{OUT} = 1.2V$ )

FIGURE 11.  $V_{OUT}$  REGULATION vs LOAD (1MHz,  $V_{OUT} = 1.5V$ )

FIGURE 12.  $V_{OUT}$  REGULATION vs LOAD (1MHz,  $V_{OUT} = 1.8V$ )

FIGURE 13.  $V_{OUT}$  REGULATION vs LOAD (1MHz,  $V_{OUT} = 2.5V$ )

FIGURE 14.  $V_{OUT}$  REGULATION vs LOAD (1MHz,  $V_{OUT} = 3.3V$ )

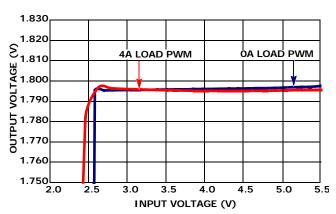

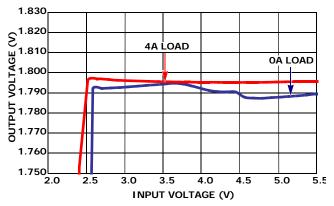

FIGURE 15. OUTPUT VOLTAGE REGULATION vs VIN (PWM  $V_{OUT} = 1.8$ )

(Unless otherwise noted, operating conditions are:  $T_A=+25\,^{\circ}\text{C},$   $V_{VIN}=2.5V$  to 5.5V, EN =  $V_{IN},$  SYNCH = 0V, L = 1.5 $\mu\text{H},$  C  $_1=2x22\mu\text{F},$  C  $_2=2x22\mu\text{F},$  I  $_{OUT}=0\text{A}$  to 4A). (Continued)

FIGURE 16. OUTPUT VOLTAGE REGULATION vs VIN (PFM V<sub>OUT</sub> = 1.8V)

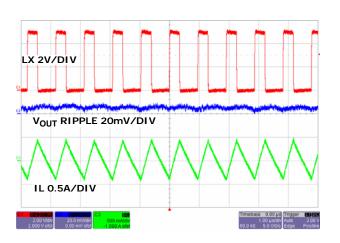

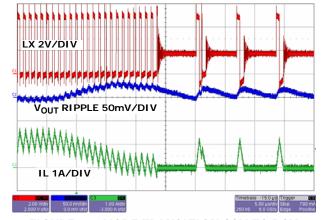

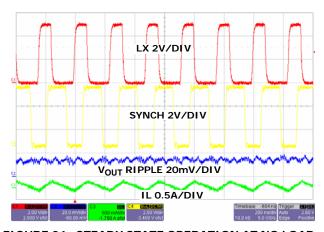

FIGURE 17. STEADY STATE OPERATION AT NO LOAD (PWM)

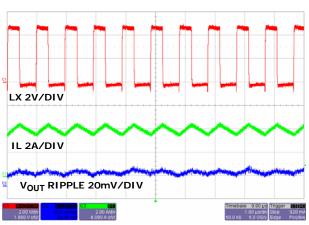

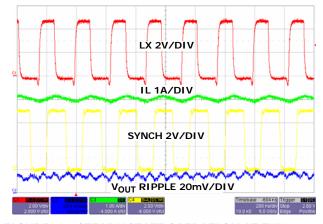

FIGURE 19. STEADY STATE OPERATION WITH FULL LOAD

FIGURE 18. STEADY STATE OPERATION AT NO LOAD (PFM)

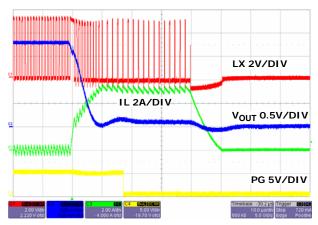

FIGURE 20. MODE TRANSITION CCM TO DCM

FIGURE 21. MODE TRANSITION DCM TO CCM

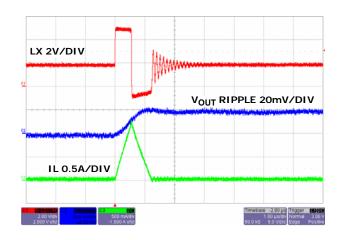

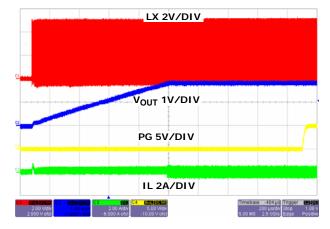

(Unless otherwise noted, operating conditions are:  $T_A=+25\,^{\circ}\text{C},$   $V_{VIN}=2.5V$  to 5.5V, EN =  $V_{IN},$  SYNCH = 0V, L = 1.5 $\mu\text{H},$  C  $_1=2x22\mu\text{F},$  C  $_2=2x22\mu\text{F},$  I  $_{OUT}=0\text{A}$  to 4A). (Continued)

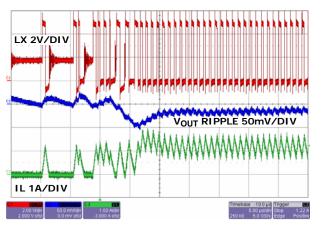

FIGURE 22. LOAD TRANSIENT (PWM)

FIGURE 23. LOAD TRANSIENT (PFM)

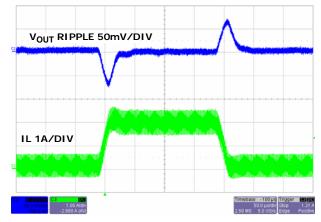

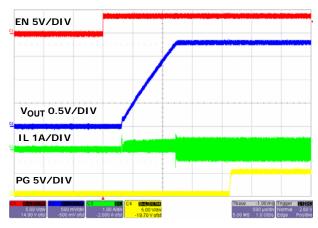

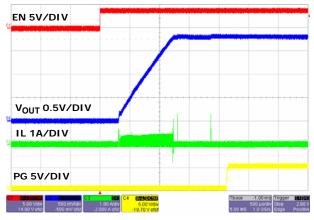

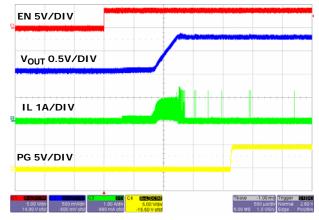

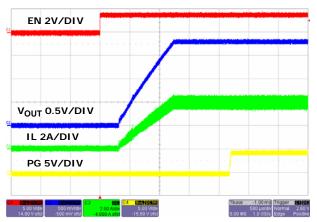

FIGURE 24. SOFT-START WITH NO LOAD (PWM)

FIGURE 25. SOFT-START AT NO LOAD (PFM)

FIGURE 26. SOFT-START WITH PRE-BIASED 1V

FIGURE 27. SOFT-START AT FULL LOAD

FIGURE 28. SOFT-DISCHARGE SHUTDOWN

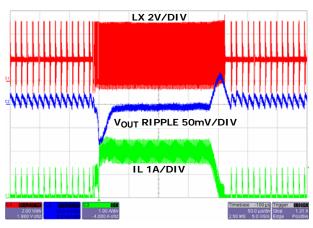

FIGURE 29. STEADY STATE OPERATION AT NO LOAD WITH FREQUENCY = 2MHz

FIGURE 30. STEADY STATE OPERATION AT FULL LOAD WITH FREQUENCY = 2MHz

FIGURE 31. STEADY STATE OPERATION AT NO LOAD WITH FREQUENCY = 4MHz

FIGURE 32. STEADY STATE OPERATION AT FULL LOAD (PWM) WITH FREQUENCY = 4MHz

FIGURE 33. OUTPUT SHORT CIRCUIT

(Unless otherwise noted, operating conditions are:  $T_A=+25\,^{\circ}\text{C},$   $V_{VIN}=2.5V$  to 5.5V, EN =  $V_{IN},$  SYNCH = 0V, L = 1.5 $\mu\text{H},$  C  $_1=2x22\mu\text{F},$  C  $_2=2x22\mu\text{F},$  I  $_{OUT}=0A$  to 4A). (Continued)

FIGURE 34. OUTPUT SHORT CIRCUIT RECOVERY

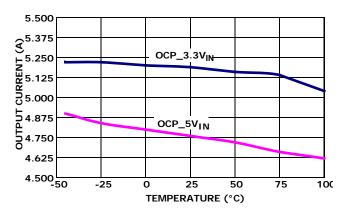

FIGURE 35. OUTPUT CURRENT LIMIT vs TEMPERATURE

## **Theory of Operation**

The ISL8014 is a step-down switching regulator optimized for battery-powered handheld applications. The regulator operates at 1MHz fixed switching frequency under heavy load conditions to allow smaller external inductors and capacitors to be used for minimal printed-circuit board (PCB) area. At light load, the regulator reduces the switching frequency, unless forced to the fixed frequency, to minimize the switching loss and to maximize the battery life. The quiescent current when the output is not loaded is typically only  $35\mu\text{A}$ . The supply current is typically only  $0.1\mu\text{A}$  when the regulator is shut down.

## **PWM Control Scheme**

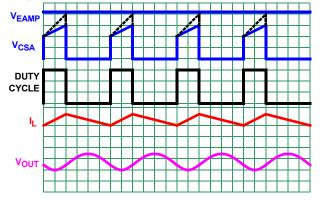

Pulling the SYNCH pin HI (>2.5V) forces the converter into PWM mode, regardless of output current. The ISL8014 employs the current-mode pulse-width modulation (PWM) control scheme for fast transient response and pulse-by-pulse current limiting. Figure 2 shows the block diagram. The current loop consists of the oscillator, the PWM comparator, current sensing circuit

and the slope compensation for the current loop stability. The gain for the current sensing circuit is typically 200mV/A. The control reference for the current loops comes from the error amplifier's (EAMP) output.

The PWM operation is initialized by the clock from the oscillator. The P-Channel MOSFET is turned on at the beginning of a PWM cycle and the current in the MOSFET starts to ramp up. When the sum of the current amplifier CSA and the slope compensation (237mV/µs) reaches the control reference of the current loop, the PWM comparator COMP sends a signal to the PWM logic to turn off the P-MOSFET and turn on the N-Channel MOSFET. The N-MOSFET stays on until the end of the PWM cycle. Figure 36 shows the typical operating waveforms during the PWM operation. The dotted lines illustrate the sum of the slope compensation ramp and the current-sense amplifier's CSA output.

The output voltage is regulated by controlling the  $V_{EAMP}$  voltage to the current loop. The bandgap circuit outputs a 0.8V reference voltage to the voltage loop. The feedback signal comes from the VFB pin. The soft-start block only affects the operation during the start-up and

will be discussed separately. The error amplifier is a transconductance amplifier that converts the voltage error signal to a current output. The voltage loop is internally compensated with the 27pF and 390k $\Omega$  RC network. The maximum EAMP voltage output is precisely clamped to 1.6V.

FIGURE 36. PWM OPERATION WAVEFORMS

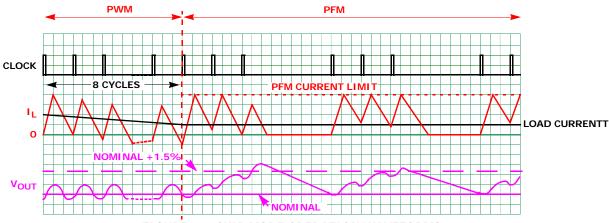

#### **SKIP Mode**

Pulling the SYNCH pin LO (<0.4V) forces the converter into PFM mode. The ISL8014 enters a pulse-skipping mode at light load to minimize the switching loss by reducing the switching frequency. Figure 37 illustrates the skip-mode operation. A zero-cross sensing circuit shown in Figure 2 monitors the N-MOSFET current for zero crossing. When 8 consecutive cycles of the inductor current crossing zero are detected, the regulator enters the skip mode. During the eight detecting cycles, the current in the inductor is allowed to become negative. The counter is reset to zero when the current in any cycle does not cross zero.

Once the skip mode is entered, the pulse modulation starts being controlled by the SKIP comparator shown in Figure 2. Each pulse cycle is still synchronized by the PWM clock. The P-MOSFET is turned on at the clock's rising edge and turned off when the output is higher than 1.5% of the nominal regulation or when its current reaches the peak Skip current limit value. Then the inductor current is discharging to 0A and stays at zero. The internal clock is disabled. The output voltage reduces gradually due to the load current discharging the output

capacitor. When the output voltage drops to the nominal voltage, the P-MOSFET will be turned on again at the rising edge of the internal clock as it repeats the previous operations.

The regulator resumes normal PWM mode operation when the output voltage drops 1.5% below the nominal voltage.

### **Synchronization Control**

The frequency of operation can be synchronized up to 4MHz by an external signal applied to the SYNCH pin. The falling edge on the SYNCH triggers the rising edge of the LX pulse. Make sure that the minimum on time of the LX node is greater than 140ns.

### **Overcurrent Protection**

The overcurrent protection is realized by monitoring the CSA output with the OCP comparator, as shown in Figure 2. The current sensing circuit has a gain of 200mV/A, from the P-MOSFET current to the CSA output. When the CSA output reaches 1.4V, which is equivalent to 5.7A for the switch current, the OCP comparator is tripped to turn off the P-MOSFET immediately. The overcurrent function protects the switching converter from a shorted output by monitoring the current flowing through the upper MOSFET.

Upon detection of overcurrent condition, the upper MOSFET will be immediately turned off and will not be turned on again until the next switching cycle. Upon detection of the initial overcurrent condition, the overcurrent fault counter is set to 1. If, on the subsequent cycle, another overcurrent condition is detected, the OC fault counter will be incremented. If there are 17 sequential OC fault detections, the regulator will be shut down under an overcurrent fault condition. An overcurrent fault condition will result in the regulator attempting to restart in a hiccup mode within the delay of four soft-start periods. At the end of the fourth soft-start wait period, the fault counters are reset and soft-start is attempted again. If the overcurrent condition goes away during the delay of four soft-start periods, the output will resume back into regulation point after hiccup mode expires.

FIGURE 37. SKIP MODE OPERATION WAVEFORMS

#### **Short-Circuit Protection**

The short-circuit protection SCP comparator monitors the VFB pin voltage for output short-circuit protection. When the VFB is lower than 0.2V, the SCP comparator forces the PWM oscillator frequency to drop to 1/3 of the normal operation value. This comparator is effective during start-up or an output short-circuit event.

#### PG

During power-up, the open-drain power good output holds low for about 1ms after  $V_{OUT}$  reaches the regulation voltage. The PG output also serves as a 1ms delayed the Power Good signal when the pull-up resistor  $R_1$  is installed.

### Soft Start-Up

The soft-start-up reduces the inrush current during the start-up. The soft-start block outputs a ramp reference to the input of the error amplifier. This voltage ramp limits the inductor current as well as the output voltage speed so that the output voltage rises in a controlled fashion. When VFB is less than 0.2V at the beginning of the soft-start, the switching frequency is reduced to 1/3 of the nominal value so that the output can start up smoothly at light load condition. During soft-start, the IC operates in the SKIP mode to support pre-biased output condition.

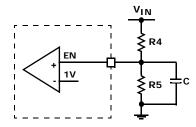

### **UVLO**

When the input voltage is below the undervoltage lockout (UVLO) threshold, the regulator is disabled. To adjust the voltage level of power on and UVLO, use a resistive divider across EN. The input voltage programming resistor  $R_4$  will depend on on the bottom resistor  $R_5$ , as referred to in Figure 38. The value of  $R_5$  is typically between  $10k\Omega$  and  $100k\Omega$

FIGURE 38. EXTERNAL RESISTOR DIVIDER

#### **Enable**

The enable (EN) input allows the user to control the turning on or off the regulator for purposes such as power-up sequencing. When the regulator is enabled, there is typically a 600 $\mu$ s delay for waking up the bandgap reference and then the soft-start-up begins. It is recommended that the EN voltage should be kept logic low (less than 400mV), until V<sub>IN</sub> reaches 2.5V. Refer to Figures 38 and 39 for suggested circuit implementation with V<sub>IN</sub> slew rate.

FIGURE 39. CIRCUIT IMPLEMENTATION WITH  $V_{\mbox{\scriptsize IN}}$  SLEW RATE

Let T equal the rise time of  $V_{IN}$ . Select the ratio of  $R_5$  and  $R_4$  such that the voltage is 1.4V (minimum enable logic high threshold) when  $V_{IN}$  is equal to or greater than 2.5V. Set  $R_5$  between  $10k\Omega$  to  $100k\Omega$ , and use Equation 1 to determine  $R_4$ :

$$R_4 = \frac{R_5 \cdot (V_{IN} - 1.4V)}{1.4V}$$

(EQ. 1)

Where V<sub>IN</sub> is greater than or equal to 2.5V.

Then select C such that the equivalent time constant is at least 2x the rise time, T. This will delay the EN voltage enough so that the overall EN voltage is less than 400mV by the time  $V_{\mbox{\footnotesize IN}}$  reaches 2.5V. Use Equation 2 to get C:

$$C \ge \frac{2 \bullet T}{R_4 \parallel R_5} \tag{EQ. 2}$$

Where T is the rise time of  $V_{IN}$

As an example, let  $V_{IN}=5V$  with rise time, T=10ms. Then  $R_4=56.2k\Omega$ ,  $R_5=71.5k\Omega$ , and  $C=0.68\mu F$  are used to insure that  $V_{IN}$  was >2.5V and the EN voltage was <400mV.

### Discharge Mode (Soft-Stop)

When a transition to shutdown mode occurs or the VIN UVLO is set, the outputs discharge to GND through an internal  $100\Omega$  switch.

## **Power MOSFETs**

The power MOSFETs are optimized for best efficiency. The ON-resistance for the P-MOSFET is typically  $50m\Omega$  and the ON-resistance for the N-MOSFET is typically  $50m\Omega$ .

### 100% Duty Cycle

The ISL8014 features 100% duty cycle operation to maximize the battery life. When the battery voltage drops to a level that the ISL8014 can no longer maintain the regulation at the output, the regulator completely turns on the P-MOSFET. The maximum dropout voltage under the 100% duty-cycle operation is the product of the load current and the ON-resistance of the P-MOSFET.

#### **Thermal Shut-Down**

The ISL8014 has built-in thermal protection. When the internal temperature reaches  $+140^{\circ}$ C, the regulator is completely shut down. As the temperature drops to  $+115^{\circ}$ C, the ISL8014 resumes operation by stepping through the soft-start.

## **Applications Information**

## **Output Inductor and Capacitor Selection**

To consider steady state and transient operations, ISL8014 typically uses a  $1.5\mu H$  output inductor. The higher or lower inductor value can be used to optimize the total converter system performance. For example, for higher output voltage 3.3V application, in order to decrease the inductor current ripple and output voltage ripple, the output inductor value can be increased. It is recommended to set the ripple inductor current approximately 30% of the maximum output current for optimized performance. The inductor ripple current can be expressed as shown in Equation 3:

$$\Delta I = \frac{V_O \cdot \left(1 - \frac{V_O}{V_{IN}}\right)}{L \cdot f_S}$$

(EQ. 3)

The inductor's saturation current rating needs to be at least larger than the peak current. The ISL8014 protects the typical peak current 6A. The saturation current needs be over 7A for maximum output current application.

ISL8014 uses internal compensation network and the output capacitor value is dependent on the output voltage. The ceramic capacitor is recommended to be X5R or X7R. The recommended X5R or X7R minimum output capacitor values are shown in Table 1.

TABLE 1. OUTPUT CAPACITOR VALUE vs V<sub>OUT</sub>

| V <sub>OUT</sub><br>(V) | C <sub>OUT</sub><br>(µF) | L<br>(µH) |

|-------------------------|--------------------------|-----------|

| 0.8                     | 2 x 22                   | 1.0~2.2   |

| 1.2                     | 2 x 22                   | 1.0~2.2   |

| 1.5                     | 2 x 22                   | 1.5~3.3   |

| 1.8                     | 2 x 22                   | 1.5~3.3   |

| 2.5                     | 2 x 22                   | 1.5~3.3   |

| 3.3                     | 2 x 22                   | 2.2~4.7   |

| 3.6                     | 2 x 22                   | 2.2~4.7   |

In Table 1, the minimum output capacitor value is given for the different output voltage to make sure that the whole converter system is stable. Additional output capacitance should be added for better performances in applications where high load transient or low output ripple is required. It is recommended to check the system level performance along with the simulation model.

### **Output Voltage Selection**

The output voltage of the regulator can be programmed via an external resistor divider that is used to scale the output voltage relative to the internal reference voltage and feed it back to the inverting input of the error amplifier. Refer to Figure 1.

The output voltage programming resistor,  $R_3$ , will depend on the value chosen for the feedback resistor and the desired output voltage of the regulator. The value for the feedback resistor is typically between  $10k\Omega$  and  $100k\Omega$ , as shown in Equation 4.

$$R_3 = \frac{R_2 \cdot 0.8V}{V_{OUT} - 0.8V}$$

(EQ. 4)

If the output voltage desired is 0.8V, then  $R_3$  is left unpopulated and  $R_2$  is shorted. There is a leakage current from VIN to LX. It is recommended to preload the output with 10µA minimum. For better performance, add 47pF in parallel with  $R_2$  (100k $\Omega$ ).

### **Input Capacitor Selection**

The main functions for the input capacitor are to provide decoupling of the parasitic inductance and to provide filtering function to prevent the switching current flowing back to the battery rail. Two  $22\mu F$  X5R or X7R ceramic capacitors are a good starting point for the input capacitor selection.

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

| DATE REVISION |          | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 11/23/09      | FN6576.4 | Updated on page 13 in UVLO section, last sentence from "programming resistor R5, The value of R4" to "programming resistor R4, The value of R5". Replaced Figure 38, Removed Equation after Figure 38. Reworded last sentence in Enable section from "It is necessary to keep the voltage on the EN low until Vin is greater than 2.5V" to "It is recommended that the EN voltage should be kept logic low (less than 400mV), until VIN reaches 2.5V. Refer to Figure 39 for suggested circuit implementation with VIN slew rate. Added Figure 39. Added Equations 1 and 2 and referencing text. Added Revision History and Products information.  Moved Soft-Start section to read after PG section on page 13, changed "R4" to "R5" in last sentence of UVLO section, added reference of both Figures 38 and 39 in Enable section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 09/10/09      | FN6576.3 | 9/10/09: Page 6; Revised last sentence of EN section from: "Do not leave this pin floating." TO: "Do not connect directly to VIN or leave this pin floating." 9/2/09: Page 2: Order Info: Added MSL link to Order Info per new standard Page 2: Revised Typical Application Diagram Pages 4-5: Per new Intersil standard: Added "Boldface limits apply over the operating temperature range, -40°C to +85°C." to common conditions of Electrical Specs table. Bolded MIN MAX columns where applicable. Moved "Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested." from common conditions of Electrical Specs table to note in Min Max columns. Page 6: Added following sentence to EN pin description: "Keep the EN voltage low in disabled state until Vin settle or above 2.5V." Revised "FIGURE 37. SKIP MODE OPERATION WAVEFORMS Page 14: Added FIGURE 38. EXTERNAL RESISTOR DIVIDER graphic and following sentence to UVLO section: "To adjust the voltage level of power on and UVLO, use a resistive divider across EN. The input voltage programming resistor R5 will depend on on the bottom resistor R4, as referred to in Figure 38. The value of R4 is typically between 10kohm and 100kohm." Added equation 1 to UVLO section: Added following sentence to Enable section: "It is necessary to keep the voltage of the EN low until Vin is greater than 2.5V." |  |  |  |  |

| 08/04/08      | FN6576.2 | Added to VIN, VDD and LX in Abs Max Rating (DC) or 7V (20ms). Added Intersil Standards as follows: Added to Electrical Specs conditions at top over-temp note. Updated POD L16.4x4 to latest version.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 12/20/07      | FN6576.1 | Removed the MIN and MAX value of "Peak Skip Limit" in the EC table at page 4. Replaced the Trans-Resistance (RT) value "0.18" into "0.17" for MIN and "0.22" into "0.23" for MAX in the EC table on page 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 11/28/07      | FN6576.0 | Initial Release to web                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

### **Products**

device information page on intersil.com: ISL8014

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks. Intersil's product families address power management and analog signal processing functions. Go to <a href="https://www.intersil.com/products">www.intersil.com/products</a> for a complete list of Intersil product families. \*For a complete listing of Applications, Related Documentation and Related Parts, please see the respective

To report errors or suggestions for this datasheet, please go to <a href="www.intersil.com/askourstaff">www.intersil.com/askourstaff</a> FITs are available from our website at <a href="http://rel.intersil.com/reports/search.php">http://rel.intersil.com/reports/search.php</a>

© Copyright Intersil Americas LLC 2007-2009. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

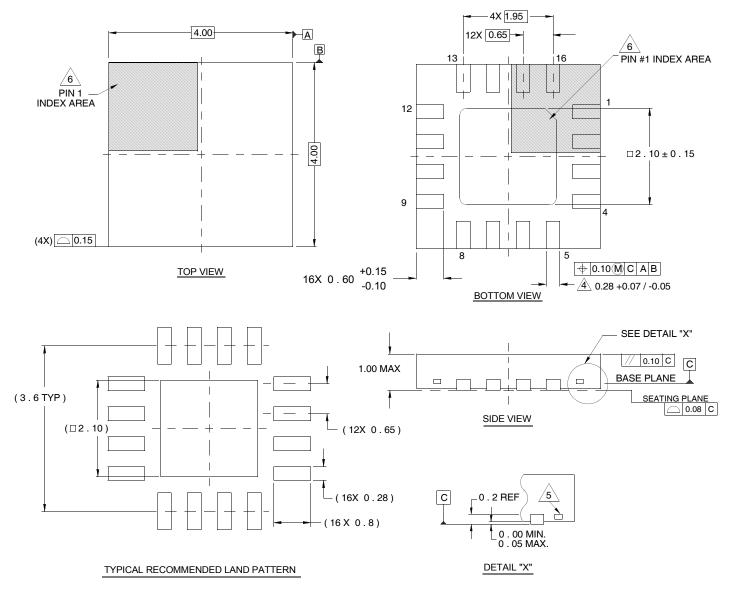

# **Package Outline Drawing**

L16.4x4

16 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE

Rev 6, 02/08

## NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance: Decimal ± 0.05

- Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Renesas Electronics: ISL8014IRZ ISL8014IRZ-T