# RENESAS

### SmartBond Bluetooth® LE 5.2 Module

**Final**

## **General Description**

Based on the SmartBond DA14695 Bluetooth® low energy 5.2 system on chip (SoC), the DA14695 Module brings out all the DA14695 hardware features and capabilities. The module integrates all passives, antenna, a 32Mbit QSPI FLASH and is supported by software that is easy to work with. The DA14695 Module targets broad market use and will be certified across regions providing significant reductions in development cost and risks, and time-to-market.

The DA14695 is a multi-core wireless microcontroller, combining the latest Arm® Cortex®-M33 application processor with floating-point unit, advanced power management functionality, a cryptographic security engine, analog and digital peripherals, a dedicated sensor node controller, and a software configurable protocol engine with a radio that is compliant to the Bluetooth® 5.2 low energy standard.

The DA14695 is based on an Arm® Cortex®-M33 CPU with an 8-region MPU and a single-precision FPU offering up to 144 dMIPS. The dedicated application processor executes code from embedded memory (RAM) or external QSPI FLASH via a 16 kB 4-way associative cache controller, which is equipped with an on-the-fly decrypting capability without extra wait states.

Bluetooth® 5.2 connectivity is guaranteed by a new software-configurable Bluetooth® low energy protocol engine (MAC) with an ultra-low-power radio transceiver, capable of +6 dBm output power and -96 dBm sensitivity offering a total link budget of 102 dB.

An optimized programmable sensor node controller allows sensor node operations and data acquisition without CPU intervention, achieving best-in-class power consumption. The advanced power management unit of the DA14695 enables it to run on primary and secondary batteries, as well as provide power to external devices through the integrated SIMO DCDC and integrated LDOs. The on-chip JEITA-compliant hardware charger makes it possible to natively charge rechargeable batteries over USB. A variety of standard and advanced peripherals enable interaction with other system components and the development of advanced user interfaces and feature-rich applications.

## **Key Features**

- □ Compatible with Bluetooth® 5.2, ETSI EN 300 328 and EN 300 440 Class 2 (Europe), FCC CFR47 Part 15 (US) and ARIB STD-T66 (Japan)

- Supports up to eight connections

- □ Supports up to 2 Mbps throughput

- Renesas registered BD address preprogrammed in OTP

- Processing and memories

- 32 kHz up to 96 MHz 32-bit Arm Cortex-M33 with 16 kB, 4-way associative cache and FPU

- A flexible and configurable Bluetooth® LE MAC engine implementing the controller stack up to HCI

- A sensor node controller running uCode for sensors manipulation

- □ 4 MB onboard FLASH

- □ 512 kB RAM

- □ 128 kB ROM

- □ 4 kB OTP

## Current Consumption

- $\Box$  1.8 mA RX at V<sub>BAT</sub> = 3 V

- □ 3 mA TX at VBAT = 3 V and 0 dBm

- □ 18.4 µA at sleep with all RAM retained

#### Radio

- Programmable RF transmit power from

-18 to +6 dBm

- □ -96 dBm receiver sensitivity

### Interfaces

- □ Up to 40 General Purpose IOs

- Decrypt-on-the-fly QSPI FLASH interface and Separate QSPI PSRAM interface

- □ SPI LCD Controller with own DMA

- 4-channels 10-bit SAR ADC,3.4 Msamples/sec

- $\Box$  4-channels 14-bit ΣΔ ADC, 1000 samples/sec

- □ 2 x general purpose timers with PWM

- □ 3 x UARTs up to 1 Mbps, one UART extended to support ISO7816

- □ 2 x SPI+™ controllers

**Final**

- □ 2 x I2C controllers at 100 kHz, 400 kHz, or 3.4 MHz

- 1 x PDM interface with HW sample rate converter

- □ 1 x I2S/PCM master/slave interface up to eight channels

- □ USB 1.1 Full Speed device interface

- Power Management

- □ Operating range: from 2.4 V to 4.75 V

- □ Hardware charger (up to 5.0 V) with programmable curves and JEITA support

- Programmable thresholds for brownout detection

- Other

- □ Real Time Clock

- □ Trimmed 32 MHz Crystal

- Packaging

- □ 15.85 mm x 20 mm x 2.5 mm package

- Module software Development Kit

- □ SDK10 support

- □ MicroPython/Zephyr support

#### Module software tools

- Flash/OTP programmer

- □ SUOTA support

- □ Battery Life Estimation

- Data Rate Monitoring

- □ Real-Time Power Profiling

- Production Line Testing

- Standards conformance

- □ BT SIG QDID 149229

- □ Europe (CE/RED)

- □ US (FCC)

- □ Canada

- □ Japan

- □ South Korea

- Taiwan

- □ South Africa

- □ Brazil

- □ China

- □ Thailand

- □ India

## **Applications**

- Beacons

- Positioning

- Proximity tags

- Low Power Sensors

- Commissioning/Provisioning

- RF pipe

- Industrial applications

- Data acquisition

- Wellness

- Infotainment

- IoT

- Robotics

- Gaming

**Final**

## **Contents**

| Ge  | nerai i | Description                                                |              |

|-----|---------|------------------------------------------------------------|--------------|

| Ke  | / Feat  | Jres                                                       | 1            |

| Ap  | plicati | ons                                                        | 2            |

| Co  | ntents  |                                                            | 3            |

| Fig | ures    |                                                            | 4            |

| Tak | oles    |                                                            | 4            |

| 1   | Terms   | s and Definitions                                          | 5            |

| 2   | Refer   | ences                                                      | 5            |

| 3   |         | Diagram                                                    | _            |

| 4   |         | t                                                          |              |

| 5   |         | cteristics                                                 |              |

| 5   | 5.1     | Absolute Maximum Ratings                                   |              |

|     | 5.2     | Recommended Operating Conditions                           |              |

|     | 5.3     | Electrical Characteristics                                 |              |

| 6   |         | anical Specifications                                      |              |

| •   | 6.1     | Mechanical Dimensions and Land Pattern                     |              |

|     | 6.2     | Marking                                                    |              |

| 7   | вом     | <u> </u>                                                   |              |

| 8   |         | n Guidelines                                               |              |

| Ū   | 8.1     | Installation Location                                      |              |

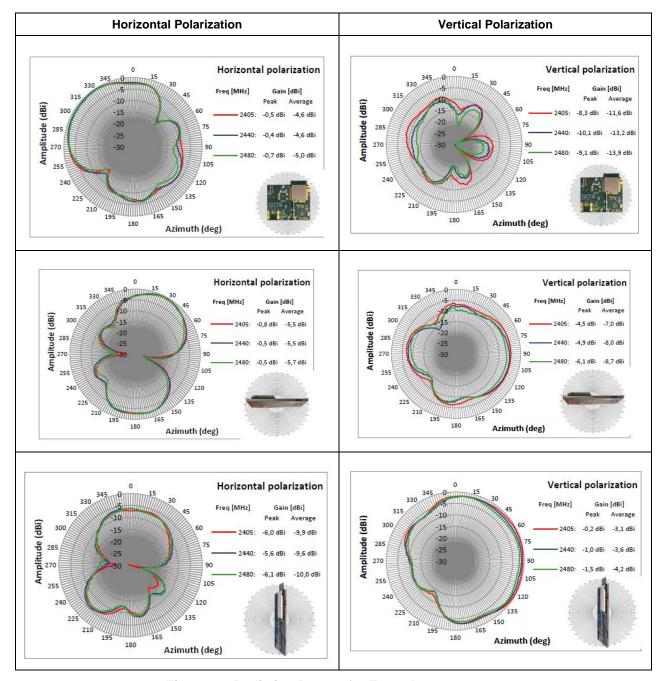

|     | 8.2     | Antenna Graphs                                             |              |

|     | 8.3     | Radiation Pattern                                          |              |

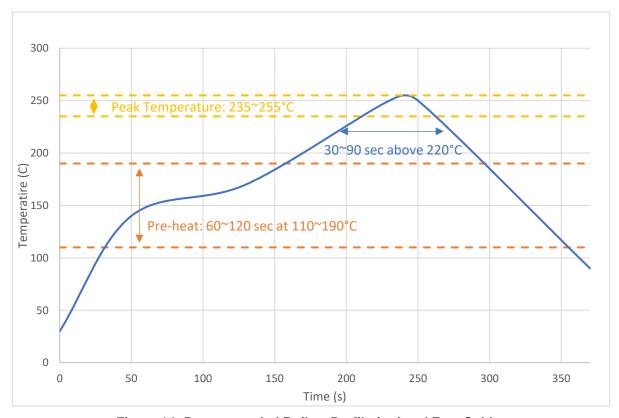

| 9   | Solde   | ring                                                       | 31           |

|     |         | iging Information                                          |              |

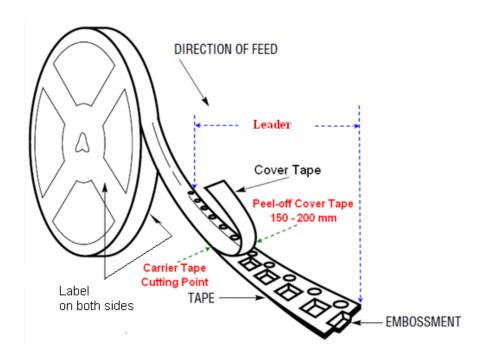

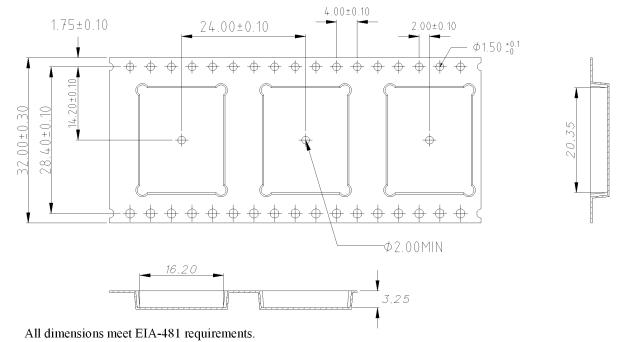

|     | 10.1    | Tape and Reel                                              |              |

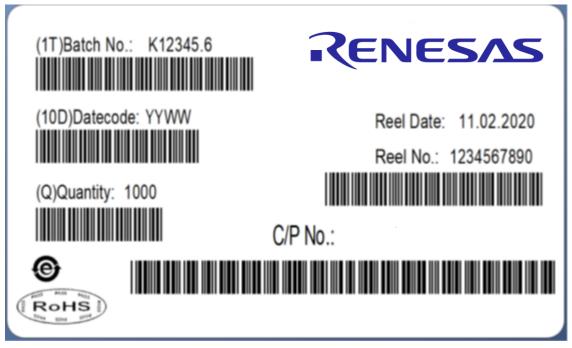

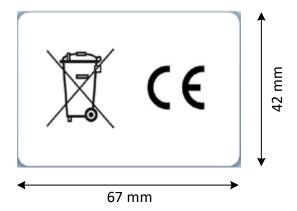

|     | 10.2    | Labeling                                                   |              |

| 11  | Order   | ing Information                                            | 36           |

| 12  |         | atory Information                                          |              |

|     | _       | CE (Radio Equipment Directive 2014/53/EU (RED)) – (Europe) |              |

|     |         | FCC – (U.S.A.)                                             |              |

|     | 12.3    | IC (Canada)                                                | 39           |

|     | 12.4    | NCC (Taiwan)                                               | 39           |

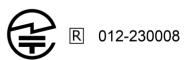

|     | 12.5    | MSIP (South Korea)                                         |              |

|     |         | RCM (Australia/New Zealand)                                |              |

|     |         | ICASA (South Africa)                                       |              |

|     | 12.8    | ANATEL (Brazil)                                            |              |

|     |         | SRRC (China)                                               |              |

|     |         | MIC (Japan) NBTC (Thailand)                                |              |

|     |         | WPC (India)                                                |              |

| 12  |         | both SIG Qualification                                     |              |

|     |         | History                                                    |              |

| ĸe\ | vision  | пізіогу                                                    | 44           |

| Dat | ashee   | t Revision 3.0                                             | 18-July-2023 |

**Final**

## **Figures**

| Figure 1: DA14695 SmartBond™ Module Block Diagram                                                | 6      |

|--------------------------------------------------------------------------------------------------|--------|

| Figure 2: Pinout Diagram – Top View                                                              |        |

| Figure 3: Pinout Diagram – Bottom Pads (Top View)                                                | . 11   |

| Figure 4: Module Shield Marking                                                                  |        |

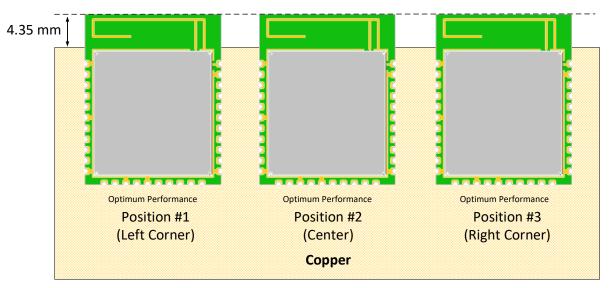

| Figure 5: Installation Locations for Optimum Antenna Performance                                 |        |

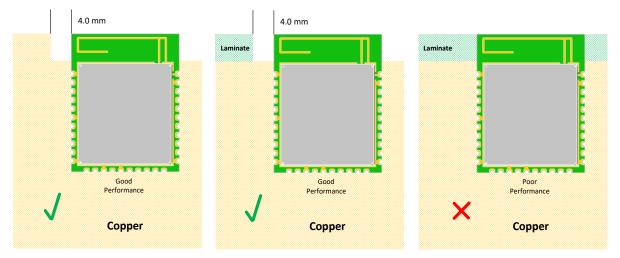

| Figure 6: Antenna Performance in Proximity of Copper (Left), Laminate (Middle), and Laminate und |        |

| Antenna (Right)                                                                                  |        |

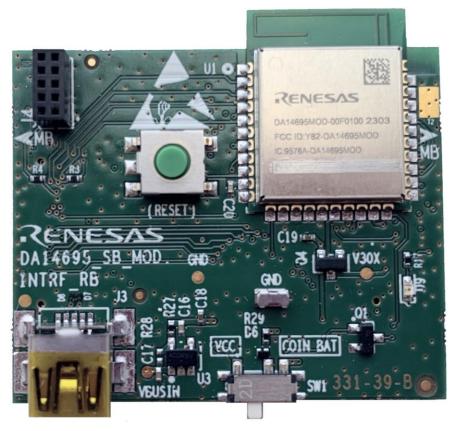

| Figure 7: DA14695MOD Module Evaluation Board                                                     |        |

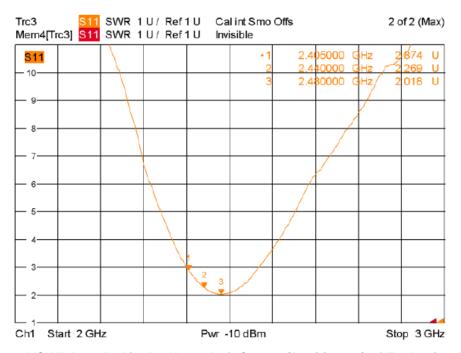

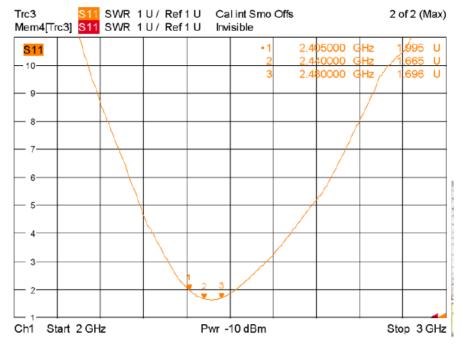

| Figure 8: VSWR Installed in the Upper Left Corner (Position #1) of Evaluation Board              |        |

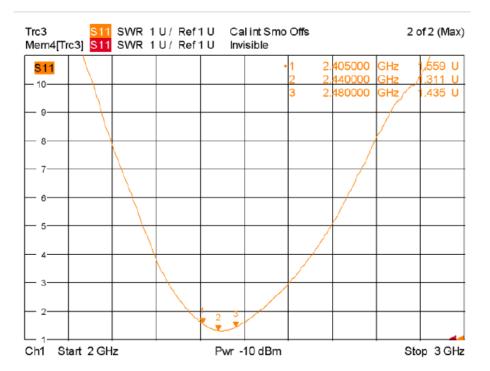

| Figure 9: VSWR with Module Installed in Center (Position #2) of the Evaluation Board             | . 27   |

| Figure 10: VSWR with Module Installed in the Upper Right Corner (Position #3) of the Evaluation  |        |

| Board                                                                                            |        |

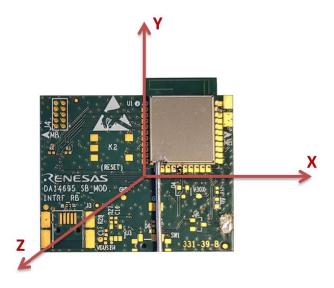

| Figure 11: Measurement Plane Definition                                                          |        |

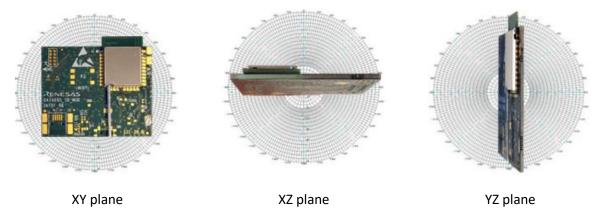

| Figure 12: Board Orientation at Different Planes                                                 |        |

| Figure 13: Radiation Pattern for Trace Antenna                                                   |        |

| Figure 14: Recommended Reflow Profile for Lead Free Solder                                       |        |

| Figure 15: Tape and Reel                                                                         |        |

| Figure 16: Reel Part Information Label                                                           |        |

| Figure 17: Reel Directives Conformity Label                                                      | . 35   |

| Tables                                                                                           |        |

| Table 1: Edge Pins Description                                                                   |        |

| Table 2: Bottom Layer Pins Description                                                           |        |

| Table 3: Absolute Maximum Ratings                                                                |        |

| Table 4: Recommended Operating Conditions                                                        |        |

| Table 5: DC Characteristics                                                                      |        |

| Table 6: GPIO - DC Characteristics                                                               |        |

| Table 7: GPIO - RDS - DC Characteristics                                                         |        |

| Table 9: XTAL32K - Recommended Operating Conditions                                              |        |

| Table 10: XTAL32M - Recommended Operating Conditions                                             |        |

| Table 11: RADIO 1M - AC Characteristics                                                          |        |

| Table 12: RADIO 2M - AC Characteristics                                                          |        |

| Table 13: Bill of Materials                                                                      |        |

| Table 14: Antenna Efficiency vs DA14695MOD Module Positions                                      |        |

| Table 15: Antenna Peak Gain for 2.4 GHz Frequency Band                                           |        |

| Table 16: Reflow Profile Specification                                                           |        |

| Table 17: MSL Level vs Floor Lifetime                                                            |        |

| Table 18: Reel Specifications                                                                    |        |

| Table 19: Ordering Information (Samples)                                                         | . 36   |

| Table 00. Ondering Information (Declination)                                                     | $\sim$ |

**Final**

## 1 Terms and Definitions

ADC Analog-to-digital converter

DIO Digital input-output

MSL Moisture sensitivity level

NTC Negative temperature coefficient

PCB Printed circuit board

RDS Reduced driving strength

VSWR Voltage standing wave ratio

## 2 References

[1] DA1469x, Datasheet, Renesas Electronics.

[2] UM-B-092, DA1469x Software Platform Reference Manual, Renesas Electronics.

Note 1 References are for the latest published version, unless otherwise indicated.

**Final**

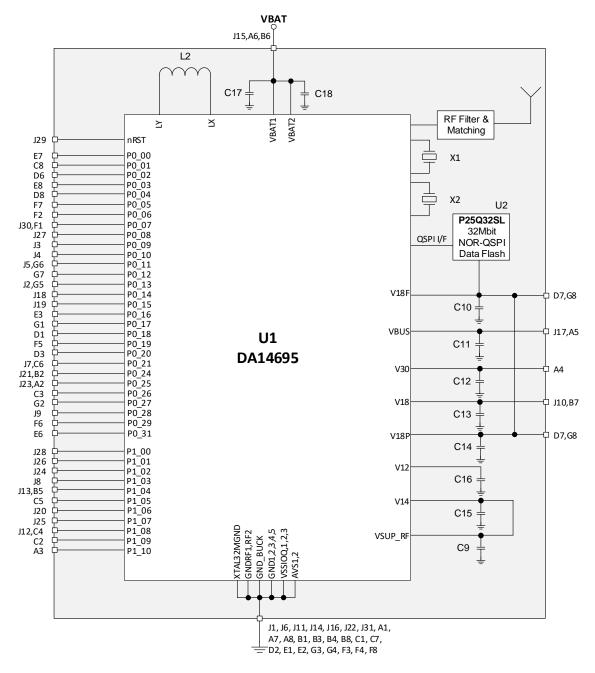

## 3 Block Diagram

The DA14695 SmartBond™ Module is based on the Renesas Electronics DA14695 SoC. With an integrated 32 Mbit QSPI Flash, 32 MHz XTAL and a printed antenna, the module enables a faster time to market at reduced development costs.

The module, as seen in Figure 1, is comprised of:

- A 32 Mbit QSPI FLASH (U2)

- A 32 MHz XTAL (X1)

- A 32 kHz XTAL (X2)

- Ten decoupling capacitors (Cx)

- A power inductor (L2)

- A CLC filter and matching components for the printed antenna

Figure 1: DA14695 SmartBond™ Module Block Diagram

**Final**

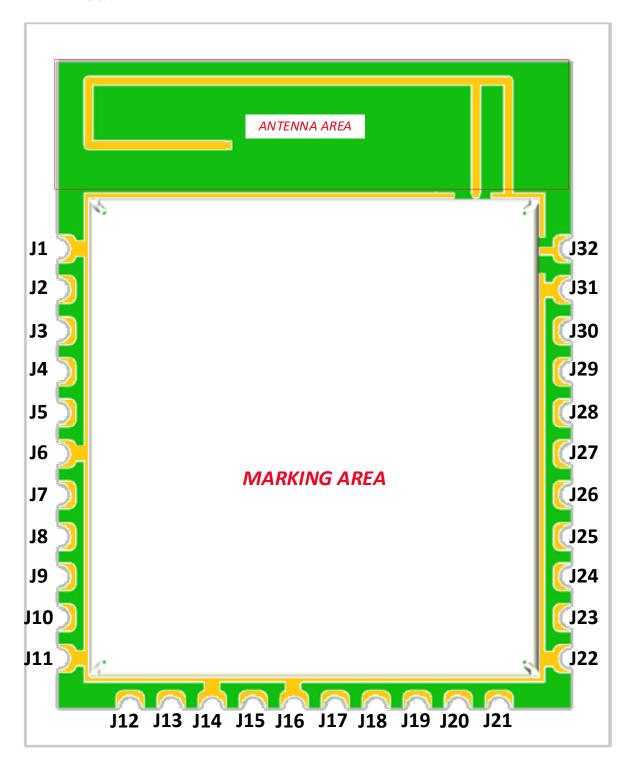

## 4 Pinout

Figure 2: Pinout Diagram - Top View

**Table 1: Edge Pins Description**

| Pin<br>No | Pin Name | Туре | Drive<br>(mA) | Reset<br>State | Description |

|-----------|----------|------|---------------|----------------|-------------|

| J1        | GND      | -    |               |                | Ground      |

**Final**

| Pin<br>No | Pin Name     | Туре | Drive<br>(mA) | Reset<br>State | Description                                                                                                                                                                                                                                |

|-----------|--------------|------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J2        | P0_13        | DIO  | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

|           | CMAC_SWCLK   | DI   |               |                | INPUT. Arm Cortex-M0+ JTAG clock signal.                                                                                                                                                                                                   |

| J3        | P0_09        | DIO  | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                             |

|           | GPADC3       | Al   |               |                | INPUT. Analog to Digital Converter input 3.                                                                                                                                                                                                |

|           | SDADC3       | Al   |               |                | INPUT. Analog input for the $\Sigma\Delta$ ADC, channel 3.                                                                                                                                                                                 |

|           | UART Boot TX | DO   |               |                | OUTPUT. UART Transmit data output during boot.                                                                                                                                                                                             |

| J4        | P0_10        | DIO  | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                             |

|           | M33_SWDIO    | DIO  |               |                | INPUT/OUTPUT. Arm Cortex-M33 JTAG data I/O signal.                                                                                                                                                                                         |

| J5        | P0_11        | DIO  | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                             |

|           | M33_SWCLK    | DI   |               |                | INPUT. Arm Cortex-M33 JTAG clock signal.                                                                                                                                                                                                   |

| J6        | GND          | -    |               |                | Ground                                                                                                                                                                                                                                     |

| J7        | P0_21        | DIO  | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

| J8        | P1_03        | DIO  | 4.8           | 4.8 I-PD       | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                             |

|           | SWDIO        | DIO  |               |                | INPUT/OUTPUT. JTAG Data input/output. Bidirectional data and control communication (by default).                                                                                                                                           |

| J9        | P0_28        | DIO  | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                             |

| J10       | V18          | AIO  |               |                | OUTPUT. 1.8 V power rail. Maximum current 50 mA.                                                                                                                                                                                           |

| J11       | GND          | -    |               |                | Ground                                                                                                                                                                                                                                     |

| J12       | P1_08        | DIO  | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate                                                                                                   |

**Final**

| Pin<br>No | Pin Name   | Туре        | Drive<br>(mA) | Reset<br>State | Description                                                                                                                                                                                                                                |

|-----------|------------|-------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |            |             |               |                | function nodes. Contains state retention mechanism during power down.                                                                                                                                                                      |

| J13       | P1_04      | DIO         | 4.8           | I-PU           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

| J14       | GND        | -           |               |                | Ground                                                                                                                                                                                                                                     |

| J15       | VBAT       | AIO         |               |                | INPUT. Battery connection.                                                                                                                                                                                                                 |

| J16       | GND        | -           |               |                | Ground                                                                                                                                                                                                                                     |

| J17       | VBUS       | AI          |               |                | INPUT. USB bus voltage. INPUT. Battery charge voltage.                                                                                                                                                                                     |

| J18       | P0_14      | DIO         |               | I-PD           | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                             |

|           | USBp       | AIO         |               |                | INPUT/OUTPUT. Analog USB Full Speed D+ signal.                                                                                                                                                                                             |

|           | XTAL32k    | DO          |               |                | OUTPUT. XTAL32k clock signal output (square wave).                                                                                                                                                                                         |

| J19       | P0_15      | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                             |

|           | USBm       | AIO         |               |                | INPUT/OUTPUT. Analog USB Full Speed D-signal.                                                                                                                                                                                              |

|           | DIVN       | DO          |               |                | OUTPUT. DIVN clock signal output (square wave).                                                                                                                                                                                            |

| J20       | P1_06      | DIO/<br>RDS | 4.8/<br>0.15  | I-PD           | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                             |

|           | Timer2.PWM | DO          |               |                | OUTPUT. Timer2/PWM output (PWM2) in Sleep mode.                                                                                                                                                                                            |

| J21       | P0_24      | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                             |

| J22       | GND        | -           |               |                | Ground                                                                                                                                                                                                                                     |

| J23       | P0_25      | DIO/<br>RDS | 4.8/<br>0.15  | I-PD           | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                             |

|           | GPADC_1    | AI          |               |                | INPUT. Analog input for the general-purpose ADC, channel 1.                                                                                                                                                                                |

|           | SDADC_1    | Al          |               |                | INPUT. Analog input for the $\Sigma\Delta$ ADC, channel 1.                                                                                                                                                                                 |

Final

| Pin<br>No | Pin Name      | Туре        | Drive<br>(mA) | Reset<br>State | Description                                                                                                                                                                                                                                |

|-----------|---------------|-------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J24       | P1_02         | DIO/<br>RDS | 4.8/<br>0.15  | I-PD           | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                             |

| J25       | P1_07         | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                             |

| J26       | P1_01         | DIO         |               | I-PD           | INPUT/OUTPUT with selectable pull up/down resistors. Pull-down enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                             |

|           | Timer.PWM     | DO          |               |                | OUTPUT. Timer/PWM output (PWM) in Sleep mode.                                                                                                                                                                                              |

| J27       | P0_08         | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

|           | GPADC_2       | AI          |               |                | INPUT. Analog input for the general-purpose ADC, channel 2.                                                                                                                                                                                |

|           | SDADC_2       | Al          |               |                | INPUT. Analog input for the ΣΔ ADC, channel 2.                                                                                                                                                                                             |

|           | UART Boot RX  | DI          |               |                | INPUT. UART Receive data input during boot.                                                                                                                                                                                                |

| J28       | P1_00         | DIO/<br>RDS | 4.8/<br>0.15  | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

| J29       | RSTn          | Al          |               |                | INPUT. Reset signal (active LOW).                                                                                                                                                                                                          |

| J30       | P0_07         | DIO/<br>RDS | 4.8/<br>0.15  | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

|           | NTC Input     | Al          |               |                | INPUT. Analog input for battery NTC (feedback).                                                                                                                                                                                            |

| J31       | GND           | -           |               |                | Ground                                                                                                                                                                                                                                     |

| J32       | Not connected | -           |               |                | Keep Floating                                                                                                                                                                                                                              |

**Final**

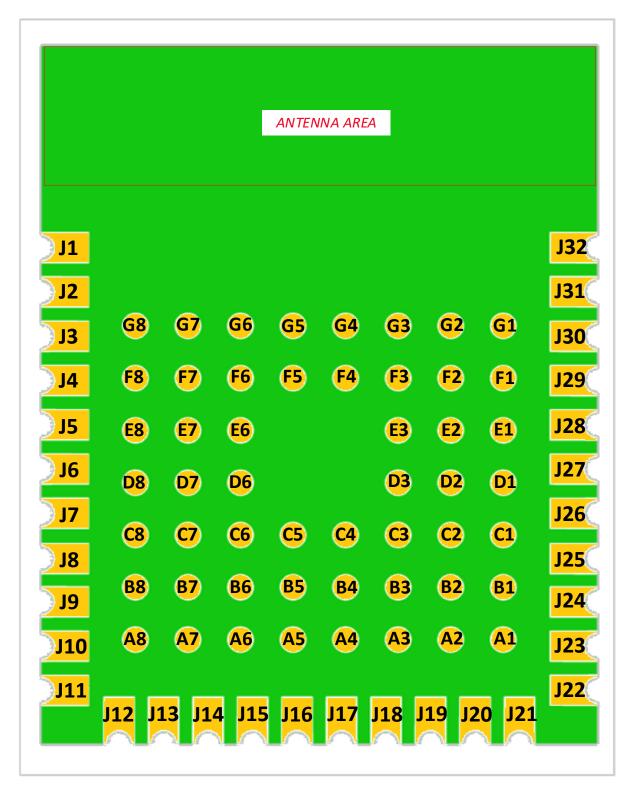

Figure 3: Pinout Diagram – Bottom Pads (Top View)

**Table 2: Bottom Layer Pins Description**

| Ball<br>No | Pin Name | Туре | Drive<br>(mA) | Reset<br>State | Description |

|------------|----------|------|---------------|----------------|-------------|

| A1         | GND      | -    |               |                | Ground      |

| A7         | GND      | -    |               |                | Ground      |

Final

| Ball<br>No | Pin Name | Туре        | Drive<br>(mA) | Reset<br>State | Description                                                                                                                                                                                                                                |

|------------|----------|-------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A8         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| B1         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| В3         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| B4         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| B8         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| C1         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| C7         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| D2         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| E1         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| E2         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| F3         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| F4         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| F8         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| G3         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| G4         | GND      | -           |               |                | Ground                                                                                                                                                                                                                                     |

| A2         | P0_25    | DIO/<br>RDS | 4.8/<br>0.15  | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

|            | GPADC_1  | AI          |               |                | INPUT. Analog input for the general-purpose ADC, channel 1.                                                                                                                                                                                |

|            | SDADC_1  | Al          |               |                | INPUT. Analog input for the $\Sigma\Delta$ ADC, channel 1.                                                                                                                                                                                 |

| A3         | P1_10    | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

| A4         | V30      | AIO         |               |                | OUTPUT. 3.0 V power rail. Maximum current 150 mA.                                                                                                                                                                                          |

| A5         | VBUS     | AI<br>AI    |               |                | INPUT. USB bus voltage. INPUT. Battery charge voltage.                                                                                                                                                                                     |

| A6         | VBAT     | AIO         |               |                | INPUT. Battery connection                                                                                                                                                                                                                  |

| B2         | P0_24    | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

| B5         | P1_04    | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor nd open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.  |

| B6         | VBAT     | AIO         |               |                | INPUT. Battery connection                                                                                                                                                                                                                  |

| B7         | V18      | AIO         |               |                | OUTPUT. 1.8 V power rail. Maximum current 50 mA.                                                                                                                                                                                           |

© 2023 Renesas Electronics

**Final**

| Ball<br>No | Pin Name  | Туре        | Drive<br>(mA) | Reset<br>State | Description                                                                                                                                                                                                                                |

|------------|-----------|-------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C2         | P1_09     | DIO/<br>RDS | 4.8/<br>0.15  | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

|            | GPADC_0   | Al          |               |                | INPUT. Analog input for the general-purpose ADC, channel 0.                                                                                                                                                                                |

|            | SDADC_0   | Al          |               |                | INPUT. Analog input for the $\Sigma\Delta$ ADC, channel 0.                                                                                                                                                                                 |

| C3         | P0_26     | DIO/<br>RDS | 4.8/<br>0.15  | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

| C4         | P1_08     | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

| C5         | P1_05     | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

| C6         | P0_21     | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

| C8         | P0_01     | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

|            | QSPIR_D1  | DIO         |               |                | INPUT/OUTPUT. QSPI RAM data I/O 1.                                                                                                                                                                                                         |

| D1         | P0_18     | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

| D3         | P0_20     | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

| D6         | P0_02     | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

|            | QSPIR_D2  | DIO         |               |                | INPUT/OUTPUT. QSPI RAM data I/O 2.                                                                                                                                                                                                         |

| D7         | V18P/V18F | AO          |               |                | OUTPUT. 1.8 V power rail. Maximum current 50 mA.                                                                                                                                                                                           |

| D8         | P0_04     | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down                                                                                                                                                 |

Final

| Ball<br>No | Pin Name  | Туре        | Drive<br>(mA) | Reset<br>State | Description                                                                                                                                                                                                                                  |

|------------|-----------|-------------|---------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |           |             |               |                | enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.                                                                                              |

|            | QSPIR_CS  | DIO         |               |                | INPUT/OUTPUT. QSPI RAM data I/O 3.                                                                                                                                                                                                           |

| E3         | P0_16     | DIO/<br>RDS | 4.8/<br>0.15  | I-PD           | INPUT / OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

|            | SDADC_REF | AI          |               |                | INPUT. Analog input for the $\Sigma\Delta$ ADC reference voltage.                                                                                                                                                                            |

|            | RCX       | DO          |               |                | OUTPUT. RC32k clock signal output (square wave).                                                                                                                                                                                             |

| E6         | P0_31     | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.   |

| E7         | P0_00     | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.   |

|            | QSPIR_D0  | DIO         |               |                | INPUT/OUTPUT. QSPI RAM data I/O 0.                                                                                                                                                                                                           |

| E8         | P0_03     | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.   |

|            | QSPIR_D3  | DIO         |               |                | INPUT/OUTPUT. QSPI RAM data I/O 3.                                                                                                                                                                                                           |

| F1         | P0_07     | DIO/<br>RDS | 4.8/<br>0.15  | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.   |

|            | NTC Input | Al          |               |                | INPUT. Analog input for battery NTC (feedback).                                                                                                                                                                                              |

| F2         | P0_06     | DIO/<br>RDS | 4.8/<br>0.15  | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.   |

|            | SDADC_GND | AI          |               |                | INPUT. Analog input for the $\Sigma\Delta$ ADC reference ground                                                                                                                                                                              |

| F5         | P0_19     | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.   |

| F6         | P0_29     | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down.   |

**Final**

| Ball<br>No | Pin Name   | Туре        | Drive<br>(mA) | Reset<br>State | Description                                                                                                                                                                                                                                |

|------------|------------|-------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F7         | P0_05      | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

|            | QSPIR_CLK  | DO          |               |                | OUTPUT. QSPI RAM clock.                                                                                                                                                                                                                    |

| G1         | P0_17      | DIO/<br>RDS | 4.8/<br>0.15  | 0.15           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

|            | RC32k      | DO          |               |                | OUTPUT. RC32k clock signal output (square wave).                                                                                                                                                                                           |

| G2         | P0_27      | DIO/<br>RDS | 4.8/<br>0.15  | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

| G5         | P0_13      | DIO         | 4.8           | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

|            | CMAC_SWCLK | DI          |               |                | INPUT. Arm Cortex-M0+ JTAG clock signal.                                                                                                                                                                                                   |

|            | RC32M      | DO          |               |                | OUTPUT. RC32M clock signal output (square wave).                                                                                                                                                                                           |

| G6         | P0_11      | DIO         | 4.8           | 4.8 I-PD       | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

|            | M33_SWCLK  | DI          |               |                | INPUT. Arm Cortex-M33 JTAG clock signal.                                                                                                                                                                                                   |

| G7         | P0_12 DIO  | DIO         | DIO 4.8       | I-PD           | INPUT/OUTPUT with selectable pull up/down resistor and open drain functionality. Pull-down enabled during and after reset. General-purpose I/O port bit or alternate function nodes. Contains state retention mechanism during power down. |

|            | CMAC_SWDIO | DIO         |               |                | INPUT/OUTPUT. Arm Cortex-M0+ JTAG data I/O signal.                                                                                                                                                                                         |

|            | XTAL32M    | DO          |               |                | OUTPUT. XTAL32M clock signal output (square wave).                                                                                                                                                                                         |

| G8         | V18F/V18P  | AO          |               |                | OUTPUT. 1.8 V power rail. Maximum current 50 mA.                                                                                                                                                                                           |

**Note 1** RDS = Reduced Driving Strength functionality (PAD\_WEAK\_CTRL\_REG).

Note 2 I-PD is Input-Pulled Down.

Note 3 I-PU is Input-Pulled Up.

Note 4 DIO is Digital Input-Output.

Note 5 PWR is Power.

Note 6 GND is Ground.

**Final**

## 5 Characteristics

All MIN/MAX specification limits are guaranteed by design, production testing and/or statistical characterization. Typical values are based on characterization results at default measurement conditions and are informative only.

Default measurement conditions (unless otherwise specified): V<sub>BAT</sub>= 3.0 V, T<sub>A</sub> = 25 °C. All radio measurements are done with standard RF measurement equipment.

## 5.1 Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, so the functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

**Table 3: Absolute Maximum Ratings**

| Parameter            | Description                     | Conditions                          | Min  | Max  | Unit |

|----------------------|---------------------------------|-------------------------------------|------|------|------|

| VPIN_LIM_DEF         | Limiting voltage on a pin       | Default, unless otherwise specified | -0.1 | 3.6  | V    |

| V <sub>BAT_LIM</sub> | Limiting battery supply voltage | Pin V <sub>BAT</sub>                | 0    | 6    | V    |

| V <sub>BUS_LIM</sub> | Limiting bus supply voltage     | Pin V <sub>BUS</sub>                | 0    | 6.5  | V    |

| VPIN_LIM_3V0         | Limiting voltage on a pin       | 3.0 V I/O pins                      | 0    | 3.45 | V    |

| VPIN_LIM_1V8         | Limiting voltage on a pin       | 1.8 V I/O pins                      | 0    | 1.98 | V    |

| T <sub>STG</sub>     | Storage temperature             |                                     | -50  | 150  | °C   |

## 5.2 Recommended Operating Conditions

**Table 4: Recommended Operating Conditions**

| Parameter            | Description            | Conditions                                  | Min | Тур | Max  | Unit |

|----------------------|------------------------|---------------------------------------------|-----|-----|------|------|

| V <sub>BAT</sub>     | Battery supply voltage | Pin V <sub>BAT1</sub> and V <sub>BAT2</sub> | 2.4 |     | 4.75 | V    |

| V <sub>BUS</sub>     | Bus supply voltage     | Pin V <sub>BUS</sub>                        | 4.2 |     | 5.75 | V    |

| VPIN_3V0             | Voltage on a pin       | 3.0 V I/O pins                              | 0   |     | 3    | V    |

| V <sub>PIN_1V8</sub> | Voltage on a pin       | 1.8 V I/O pins                              | 0   |     | 1.8  | V    |

| TA                   | Ambient temperature    |                                             | -40 |     | 85   | °C   |

### **Table 5: DC Characteristics**

| Parameter | Description            | Conditions                                                                                                               | Min | Тур | Max | Unit |

|-----------|------------------------|--------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| IBAT_IDLE | Battery supply current | CPU is idle (Wait for Interrupt - WFI); sys_clk = 32 MHz; pclk = 4 MHz; DC-DC on; FLASH off; peripherals on; VBAT = 3 V. |     | 0.8 |     | mA   |

**Final**

| Parameter                 | Description            | Conditions                                                                                                                                                                                                | Min | Тур  | Max | Unit |

|---------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| IBAT_ACTIVE_3<br>2MHz     | Battery supply current | CPU running CoreMark from RAM; sys_clk = 32 MHz; pclk = 4 MHz; DC-DC on; Peripherals off; V <sub>BAT</sub> = 3 V.                                                                                         |     | 1.8  |     | mA   |

| IBAT_ACTIVE_4<br>8MHz     | Battery supply current | CPU running CoreMark from RAM; hclk = 48 MHz; PLL on; pclk = 6 MHz; DC-DC on; Peripherals off; V <sub>BAT</sub> = 3 V.                                                                                    |     | 5    |     | mA   |

| IBAT_ACTIVE_9<br>6MHz     | Battery supply current | CPU running CoreMark from RAM; hclk = 96 MHz; PLL on; pclk = 12 MHz; DC-DC on; Peripherals off; V <sub>BAT</sub> = 3 V.                                                                                   |     | 7.8  |     | mA   |

| IBAT_HIBERN               | Battery supply current | Hibernation mode; no RAM retained; all clocks off; DC-DC off; VDD_clamp setting 0xD (0.83 V), FLASH off; VBAT = 3 V. TA 25 °C  Note 1                                                                     |     | 6.8  |     | μА   |

| I <sub>BAT_DP_</sub> SLP  | Battery supply current | Deep Sleep mode; No RAM retained; XTAL32K on; RTC off; DC-DC off; VDD_RET = 0.75 V; FLASH off; VBAT = 3 V. Bandgap Refresh rate = 0x80                                                                    |     | 10   |     | μА   |

| IBAT_EX_SLP_1<br>6K_64K   | Battery supply current | Extended Sleep mode; 16 kB (Cache) and 64 kB (data) RAM retained; XTAL32K on; DC-DC off; VDD_RET = 0.75 V; FLASH in Power Down mode; VBAT = 3 V. Bandgap Refresh rate = 0x80; RTC off Note 2              |     | 12.3 |     | μА   |

| BAT_EX_SLP_1<br>  6K_128K | Battery supply current | Extended Sleep mode; 16 kB (cache) and 128 kB (data) RAM retained; XTAL32K on; DC-DC off; VDD_RET = 0.75 V; FLASH in Power Down mode; V <sub>BAT</sub> = 3 V. Bandgap Refresh rate = 0x80; RTC off Note 2 |     | 13.1 |     | μА   |

| BAT_EX_SLP_1<br>6K_256K   | Battery supply current | Extended Sleep mode; 16 kB (cache) and 256 kB (data) RAM retained; XTAL32K on; DC-DC off; VDD_RET = 0.75 V; FLASH in Power Down mode; VBAT = 3 V. Bandgap Refresh rate = 0x80; RTC off Note 2             |     | 14.9 |     | μА   |

| IBAT_EX_SLP_1<br>6K_384K  | Battery supply current | Extended Sleep mode; 16 kB (cache) and 384 kB (data) RAM retained; XTAL32K on; DC-DC off; VDD_RET = 0.75                                                                                                  |     | 16.7 |     | μΑ   |

**Final**

| Parameter                 | Description                 | Conditions                                                                                                                                                                                   | Min | Тур  | Max | Unit |

|---------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

|                           |                             | V; FLASH in Power Down<br>mode; V <sub>BAT</sub> = 3 V. Bandgap<br>Refresh rate = 0x80; RTC off<br>Note 2                                                                                    |     |      |     |      |

| BAT_EX_SLP_1<br>6K_512K   | Battery supply current      | Extended Sleep mode; 16 kB (cache) and 512 kB (data) RAM retained; XTAL32K on; DC-DC off; VDD_RET = 0.75 V; FLASH in Power Down mode; VBAT = 3 V. Bandgap Refresh rate = 0x80;RTC off Note 2 |     | 18.4 |     | μА   |

| BAT_BLE_RX_3              | Peak battery supply current | Bluetooth® LE receive mode; fcLK = 32 MHz; CPU idle; DC-DC on; FLASH off; VBAT = 3 V.                                                                                                        |     | 4.9  |     | mA   |

| I <sub>BAT_BLE_TX_3</sub> | Peak battery supply current | Bluetooth® LE transmit mode<br>@ 0dbm; f <sub>CLK</sub> = 32 MHz;<br>CPU idle; DC-DC on; FLASH<br>off; V <sub>BAT</sub> = 3 V.                                                               |     | 5.8  |     | mA   |

| IBAT_BLE_RX_9<br>6M       | Peak battery supply current | Bluetooth® LE receive mode; $f_{CLK} = 96$ MHz; CPU idle; DC-DC on; FLASH off; $V_{BAT} = 3$ V.                                                                                              |     | 7    |     | mA   |

| BAT_BLE_TX_9              | Peak battery supply current | Bluetooth® LE transmit mode<br>@ 0dbm; f <sub>CLK</sub> = 96 MHz;<br>CPU idle; DC-DC on; FLASH<br>off; V <sub>BAT</sub> = 3 V.                                                               |     | 7.8  |     | mA   |

**Note 1** At temperatures higher than 55 °C, a higher voltage setting (0xC) should be applied at the clamp to ensure proper hibernation operation.

## **5.3 Electrical Characteristics**

## Table 6: GPIO - DC Characteristics

| Parameter              | Description              | Conditions                              | Min         | Тур | Max         | Unit |

|------------------------|--------------------------|-----------------------------------------|-------------|-----|-------------|------|

| Іін                    | HIGH level input current | V <sub>I</sub> =V30 = 3.0 V             | -10         |     | 10          | μΑ   |

| IIL                    | LOW level input current  | V <sub>I</sub> =VSS = 0 V               | -10         |     | 10          | μΑ   |

| I <sub>IH_PD_3V0</sub> | HIGH level input current | V <sub>I</sub> =V30 = 3.0 V             | 60          |     | 180         | μΑ   |

| IIL_PU_3V0             | LOW level input current  | V <sub>I</sub> =VSS = 0 V, V30 = 3.0 V  | -180        |     | -60         | μΑ   |

| IIL_PU_1V8             | LOW level input current  | V <sub>I</sub> =VSS = 0 V, V18P = 1.8 V | -110        |     | -35         | μΑ   |

| VIH                    | HIGH level input voltage | V12 = 1.2 V                             | 0.7*V1<br>2 |     |             | ٧    |

| V <sub>IL</sub>        | LOW level input voltage  | V12 = 1.2 V                             |             |     | 0.3*V1<br>2 | V    |

Note 2 If RTC is on then 150 nA should be added.

**Final**

| Parameter           | Description               | Conditions                            | Min          | Тур | Max          | Unit |

|---------------------|---------------------------|---------------------------------------|--------------|-----|--------------|------|

| V <sub>OH_1V8</sub> | HIGH level output voltage | I <sub>O</sub> = 4.8 mA, V18P = 1.8 V | 0.8*V1<br>8p |     |              | V    |

| V <sub>OL_1V8</sub> | LOW level output voltage  | I <sub>O</sub> = 4.8 mA, V18P = 1.8 V |              |     | 0.2*V1<br>8P | V    |

| V <sub>OH_3V0</sub> | HIGH level output voltage | Io = 4.8 mA, V30 = 3 V                | 0.8*V3<br>0  |     |              | V    |

| V <sub>OL_3V0</sub> | LOW level output voltage  | I <sub>O</sub> = 4.8 mA, V30 = 3 V    |              |     | 0.2*V3<br>0  | V    |

### Table 7: GPIO - RDS - DC Characteristics

| Parameter               | Description                              | Conditions                                                            | Min          | Тур | Max          | Unit |

|-------------------------|------------------------------------------|-----------------------------------------------------------------------|--------------|-----|--------------|------|

| V <sub>OH_1V8_LOW</sub> | HIGH level output voltage, limited drive | I <sub>O</sub> = 150 μA, V18P = 1.8 V,<br>low drive enabled<br>Note 1 | 0.8*V1<br>8P |     |              | ٧    |

| VOL_1V8_LOW<br>DRV      | LOW level output voltage, limited drive  | l <sub>O</sub> = 150 μA, V18P = 1.8 V,<br>low drive enabled           |              |     | 0.2*V1<br>8P | V    |

Note 1 Digital pad characteristics are equal to the standard GPIO pads unless overruled or added in this table.

## **Table 8: RCX - Timing Characteristics**

| Parameter            | Description             | Conditions                                   | Min  | Тур | Max | Unit        |

|----------------------|-------------------------|----------------------------------------------|------|-----|-----|-------------|

| Δf <sub>RC</sub> /ΔT |                         | For temperature ranging from -40 °C to 85 °C | -100 |     | 100 | ppm/d<br>eg |

| f <sub>RCX</sub>     | RC oscillator frequency | At target fixed trim setting                 | 13   | 15  | 18  | kHz         |

## **Table 9: XTAL32K - Recommended Operating Conditions**

| Parameter             | Description                                   | Conditions                                                                           | Min  | Тур    | Max | Unit |

|-----------------------|-----------------------------------------------|--------------------------------------------------------------------------------------|------|--------|-----|------|

| f <sub>XTAL_32K</sub> | Crystal oscillator frequency                  |                                                                                      |      | 32.768 |     | kHz  |

| Δfxtal_32k            | Crystal frequency tolerance (including aging) | Timing accuracy is dominated by crystal accuracy. A much smaller value is preferred. | -250 |        | 250 | ppm  |

## Table 10: XTAL32M - Recommended Operating Conditions

| Parameter  | Description                  | Conditions | Min | Тур | Max | Unit |

|------------|------------------------------|------------|-----|-----|-----|------|

| fxtal(32M) | Crystal oscillator frequency |            |     | 32  |     | MHz  |

**Final**

| Parameter              | Description                 | Conditions                                                             | Min | Тур | Max | Unit |

|------------------------|-----------------------------|------------------------------------------------------------------------|-----|-----|-----|------|

| $\Delta f_{XTAL}(32M)$ | Crystal frequency tolerance | After optional trimming; including aging and temperature drift  Note 1 | -20 |     | 20  | ppm  |

**Note 1** Using the internal varicaps a wide range of crystals can be trimmed to the required tolerance.

Table 11: RADIO 1M - AC Characteristics

| Parameter              | Description        | Conditions                                                                                                 | Min | Тур   | Max | Unit |

|------------------------|--------------------|------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Psens_clean            | Sensitivity level  | Dirty Transmitter disabled;<br>DC-DC converter disabled;<br>PER = 30.8 %<br>Note 1                         |     | -96   |     | dBm  |

| Psens                  | Sensitivity level  | Dirty Transmitter enabled;<br>DC-DC converter disabled;<br>PER = 30.8 %<br>Note 1                          |     | -95.5 |     | dBm  |

| PSENS_EPKT_<br>CLEAN   | Sensitivity level  | Dirty Transmitter disabled;<br>DC-DC converter disabled;<br>Extended packet size (255<br>octets)<br>Note 1 |     | -95   |     | dBm  |

| P <sub>SENS_EPKT</sub> | Sensitivity level  | Dirty Transmitter enabled;<br>DC-DC converter disabled;<br>Extended packet size (255<br>octets)            |     | -93   |     | dBm  |

| Po                     | Output power level | Power set to 6 dBm                                                                                         |     | 6     |     | dBm  |

Note 1 Measured according to Bluetooth® Low Energy Test Specification RF-PHY.TS.

Table 12: RADIO 2M - AC Characteristics

| Parameter   | Description       | Conditions                                                                                                 | Min | Тур   | Max | Unit |

|-------------|-------------------|------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Psens_clean | Sensitivity level | Dirty Transmitter disabled;<br>DC-DC converter disabled;<br>PER = 30.8 %<br>Note 1                         |     | -93.5 |     | dBm  |

| Psens       | Sensitivity level | Dirty Transmitter enabled;<br>DC-DC converter disabled;<br>PER = 30.8 %<br>Note 1                          |     | -93   |     | dBm  |

| Psens_epkt_ | Sensitivity level | Dirty Transmitter disabled;<br>DC-DC converter disabled;<br>Extended packet size (255<br>octets)<br>Note 1 |     | -92   |     | dBm  |

**Final**

| Parameter  | Description        | Conditions                                                                                      | Min | Тур   | Max | Unit |

|------------|--------------------|-------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Psens_epkt | Sensitivity level  | Dirty Transmitter enabled;<br>DC-DC converter disabled;<br>Extended packet size (255<br>octets) |     | -91.5 |     | dBm  |

| Po         | Output power level | Power set to 6 dBm                                                                              |     | 6     |     | dBm  |

Note 1 Measured according to Bluetooth® Low Energy Test Specification RF-PHY.TS

**Final**

## **6 Mechanical Specifications**

## 6.1 Mechanical Dimensions and Land Pattern

The module's dimensions are accessible from the Renesas website – 84-Module.

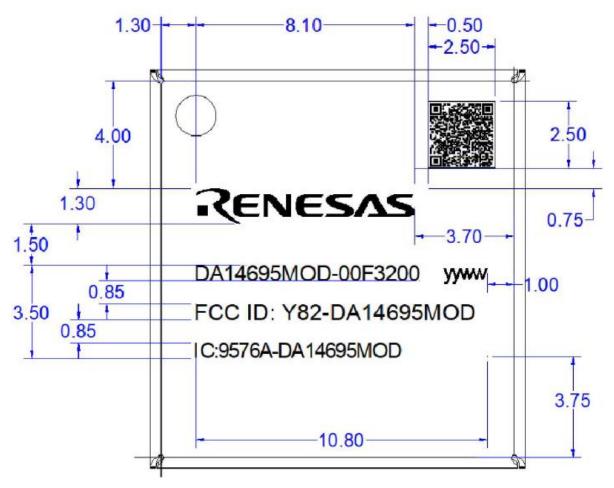

## 6.2 Marking

The module's shield marking is shown in Figure 4.

Figure 4: Module Shield Marking

## Marking Legend:

DA14695MOD-00F3200 yyww

yy: production yearww: production week

All dimension in mm. Tolerance: 0.4 mm

**Final**

## 7 BOM

### **Table 13: Bill of Materials**

| #  | Designator            | Туре                  | Value                | Description                                                         | Manufacturer        | MPN                |

|----|-----------------------|-----------------------|----------------------|---------------------------------------------------------------------|---------------------|--------------------|

| 1  | C9, C15,<br>C16       | Capacitor             | 10uF                 | CAP CER 10UF 6.3 V X5R 0402                                         | Murata              | GRM155R60J106ME05D |

| 2  | C10                   | Capacitor             | 100nF                | CAP CER 100n 25 V 10 % X7R 0402                                     | Murata              | GRM155R71E104KE14D |

| 3  | C11, C12,<br>C17, C18 | Capacitor             | 4.7uF                | CAP CER 4.7UF 10 V X5R 0402                                         | Murata              | GRM155R61A475MEAAD |

| 4  | C13, C14              | Capacitor             | 22uF                 | CAP CER 22UF 6.3 V X5R 0603                                         | Murata              | GRM188R60J226MEA0D |

| 5  | C22, C23              | Capacitor             | 0.7pF                | CAP CER 0.7±0.05pF 50V C0G/NP0 0201                                 | Murata              | GJM0335C1HR70WB01  |

| 6  | C25                   | Capacitor             | 10pF                 | CAP CER 10PF 50 V 5 % NP0 0201                                      | Murata              | GRM0335C1H100JA01D |

| 7  | L2                    | Inductor              | 0.47uH               | Shielded Wirewound Inductor 0.47uH 20 % 3600 mA 0.032 Ω 0806 (2016) | Murata Electronics  | LQM21PNR47MG0D     |