# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

The revision list can be viewed directly by clicking the title page. The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# SH7760 Group

Hardware Manual Renesas 32-Bit RISC Microcomputer SuperH™ RISC engine Family/SH7750 Series

SH7760

HD6417760BL200A HD6417760BL200AV HD6417760BL200AD HD6417760BL200ADV HD6417760BP200ADV

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesa's shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

# General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

#### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions may occur due to the false recognition of the pin state as an input signal. Unused pins should be handled as described under Handling of Unused Pins in the manual.

#### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

#### 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

#### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

— When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

#### Differences between Products

Before changing from one product to another, i.e. to one with a different type number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different type numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different type numbers, implement a system-evaluation test for each of the products.

# **Preface**

The SH7760 RISC (Reduced Instruction Set Computer) microcomputer includes a Renesas Technology-original RISC CPU as its core, and the peripheral functions required to configure a system.

Target Users: This manual was written for users who will be using this LSI in the design of application systems. Users of this manual are expected to understand the

fundamentals of electrical circuits, logical circuits, and microcomputers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of this LSI to the above users.

Notes on reading this manual:

• In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts

on the CPU, system control functions, and peripheral functions.

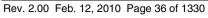

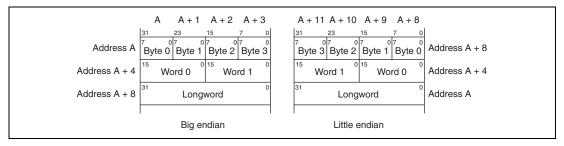

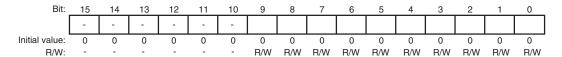

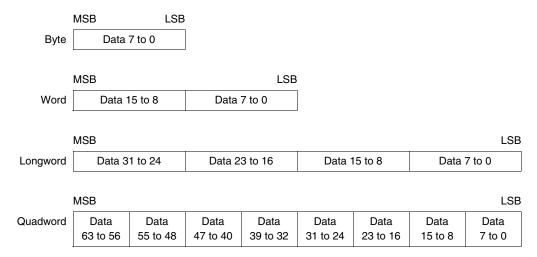

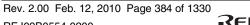

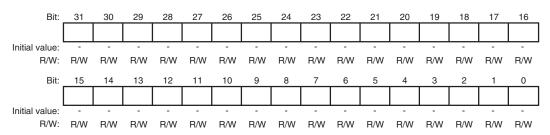

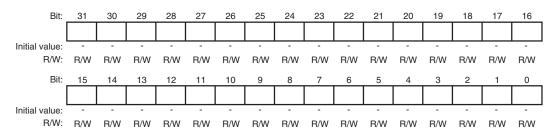

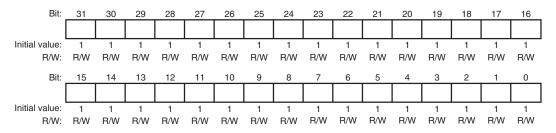

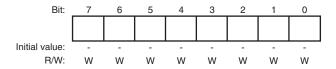

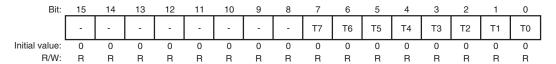

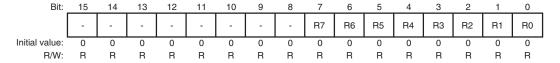

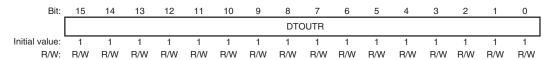

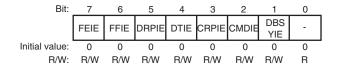

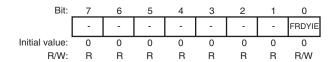

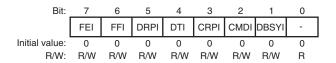

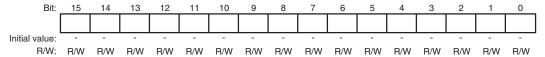

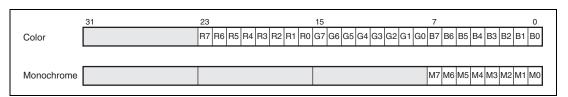

Rules: Bit order: The MSB is on the left and the LSB is on the right.

Related Manuals: The latest versions of all related manuals are available from our web site.

Please ensure you have the latest versions of all documents you require.

http://www.renesas.com

Refer to the SH-4 Software Manual for details on the instruction set.

# Main Revisions for This Edition

| Item                                                        | Page     | Revision (See Manual for Details)                                                                                                                                                                         |

|-------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| All                                                         | _        | Company name and brand names amended                                                                                                                                                                      |

|                                                             |          | (Before) Hitachi, Ltd. $\rightarrow$ (After) Renesas Technology Corp.                                                                                                                                     |

| 1.1 SH7760 Features                                         | 2        | Table amended                                                                                                                                                                                             |

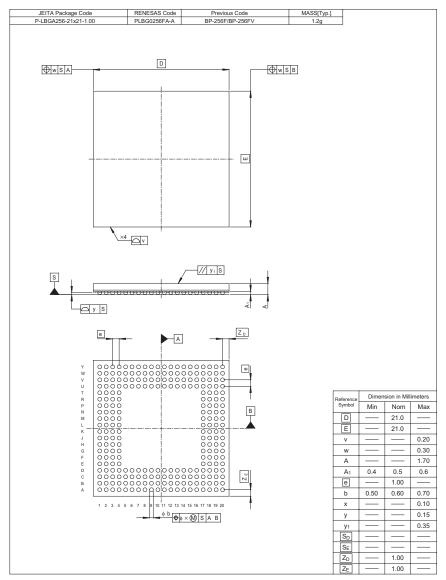

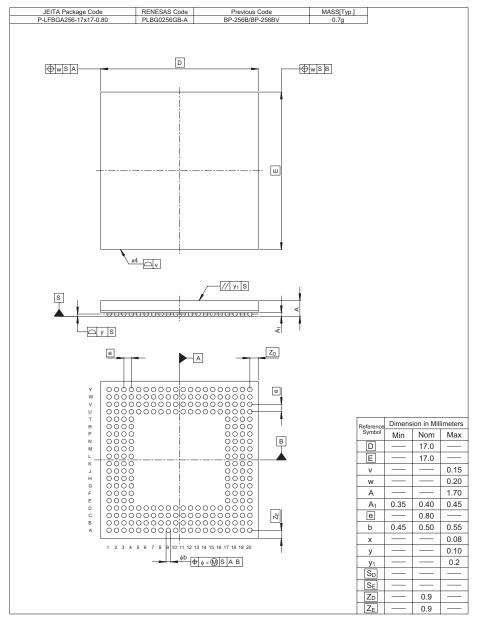

| Table 1.1 Features                                          |          | Item         Features           LSI         • Packages: 256-pin BGA (Size: 17 × 17 mm, pin pitch: 0.8 mm)           CPU         • RISC-type instruction set (upward-compatible with SH-1, SH-2, and SH-3) |

|                                                             | 3        | Table amended                                                                                                                                                                                             |

|                                                             |          | FPU   Features                                                                                                                                                                                            |

|                                                             | 9        | "Product lineup" added                                                                                                                                                                                    |

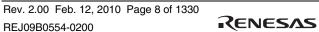

| 1.2 Block Diagram Figure 1.1 SH7760 Block Diagram           | 10       | External bus interface  26-bit address bus  32-bit data bus                                                                                                                                               |

| 1.3 Pin Arrangement                                         | 11       | Figure added                                                                                                                                                                                              |

| Figure 1.2 SH7760 Pin<br>Arrangement (BP-<br>256F/BP-256FV) |          |                                                                                                                                                                                                           |

| Figure 1.3 SH7760 Pin<br>Arrangement (BP-<br>256B/BP-256BV) | 12       | Figure title amended                                                                                                                                                                                      |

| 1.4 Pin Description                                         | 13       | Description amended                                                                                                                                                                                       |

|                                                             |          | Table 1.2 lists the pin configuration of the BP-256F (21 mm* <sup>1</sup> ), and table 1.3 lists the pin configuration of the BP-256B (17 mm* <sup>2</sup> ).                                             |

|                                                             |          | Notes added                                                                                                                                                                                               |

|                                                             |          | Notes: 1. HD6417760BP200AD, HD6417760BP200ADV                                                                                                                                                             |

|                                                             |          | <ol> <li>HD6417760BL200A, HD6417760BL200AV,<br/>HD6417760BL200AD, HD6417760BL200ADV</li> </ol>                                                                                                            |

| Table 1.2 Pin<br>Configuration (BP-<br>256F: 21 mm)         | 13 to 21 | Table added                                                                                                                                                                                               |

| Table 1.3 Pin   Configuration (BP-256B: 17 mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Item                 | Page     | Revision (See Manual for Details)                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------|-------------------------------------------------------------------------------------------------------------|

| Table 1.4   Pin   Pin  | Configuration (BP-   | 22       | Table title amended                                                                                         |

| Notes added   Notes: 1. HD6417760BL200A, HD6417760BL200ADV   Logical Control of Particles   | 1.5 Pin Function     | 31       | Table amended                                                                                               |

| Notes: 1. HD6417760BL200AD, HD6417760BL200AV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |          |                                                                                                             |

| ### HD6417760BL200AD, HD6417760BL200ADV  2. HD6417760BP200AD, HD6417760BP200ADV  Table 1.5 Pin Functions  32 to 34 Table amended    Pin No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |          | Notes added                                                                                                 |

| Table 1.5 Pin Functions  32 to 34 Table amended Functions  34 Notes added  Notes: 1. HD6417760BL200A, HD6417760BL200AV, HD6417760BL200ADV  2. HD6417760BP200AD, HD6417760BP200ADV  Table 1.6 Pin Functions  35 to 38 Table amended Functions  38 Notes added  Notes: 1. HD6417760BL200A, HD6417760BP200ADV  Table 1.6 Pin Functions  38 Notes added  Notes: 1. HD6417760BL200A, HD6417760BP200ADV  2. HD6417760BP200AD, HD6417760BP200ADV  Table 1.6 Pin Name 1/0 SRAM SDRAM PCMCIA MPX Remarks  38 Notes added  Notes: 1. HD6417760BL200A, HD6417760BL200AV, HD6417760BL200ADV  2. HD6417760BL200AD, HD6417760BL200ADV  2. HD6417760BP200AD, HD6417760BP200ADV  2.2.1 Privileged Mode and Banks  Table 2.1 Initial Register SR MD bit = 1, BL bit = 1, BL bit = 1, FD bit = 0, others = undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |          |                                                                                                             |

| Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |          | 2. HD6417760BP200AD, HD6417760BP200ADV                                                                      |

| Notes added   Notes: 1. HD6417760BL200A, HD6417760BL200ADV   HD6 |                      | 32 to 34 | Table amended                                                                                               |

| Notes: 1. HD6417760BL200A, HD6417760BL200AV, HD6417760BL200ADV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Functions            |          |                                                                                                             |

| ### HD6417760BL200AD, HD6417760BL200ADV  2. HD6417760BP200AD, HD6417760BP200ADV  Table 1.6 Pin Functions    St to 38   Table amended   Pin No.   Memory Interface   Pin Name   I/O   SRAM SDRAM PCMCIA MPX   Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | 34       | Notes added                                                                                                 |

| Table 1.6 Pin Functions         Table amended           Pin No.         Pin No.         Memory Interface         Remarks           38         Notes added         Notes: 1. HD6417760BL200A, HD6417760BL200AV, HD6417760BL200ADV         HD6417760BL200AD, HD6417760BL200ADV           2. HD6417760BP200AD, HD6417760BP200ADV         2. HD6417760BP200AD, HD6417760BP200ADV           2.2.1 Privileged Mode and Banks         Table amended           Table 2.1 Initial Register Values         Control registers         Initial Value*           Control registers         SR         MD bit = 1, RB bit = 1, BL bit = 1, FD bit = 0, IMASK = 1111 (H*F), reserved bits = 0, others = undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |          |                                                                                                             |

| Pin No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |          | 2. HD6417760BP200AD, HD6417760BP200ADV                                                                      |

| Notes: 1. HD6417760BL200A, HD6417760BL200AV,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      | 35 to 38 | Pin No. Memory Interface                                                                                    |

| ## HD6417760BL200AD, HD6417760BL200ADV  2. HD6417760BP200AD, HD6417760BP200ADV  2.2.1 Privileged Mode 41 Table amended and Banks Type Registers Initial Value*  Table 2.1 Initial Control registers SR MD bit = 1, RB bit = 1, FD bit = 0, IMASK = 1111 (H'F), reserved bits = 0, others = undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | 38       | Notes added                                                                                                 |

| 2.2.1 Privileged Mode 41 Table amended and Banks Type Registers Initial Value*  Table 2.1 Initial Control registers SR MD bit = 1, RB bit = 1, BL bit = 1, FD bit = 0, IMASK = 1111 (H'F), reserved bits = 0, others = undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |          |                                                                                                             |

| and Banks  Type Registers  Initial Value*  Control registers  SR  MD bit = 1, RB bit = 1, ED bit = 0, IMASK = 1111 (H'F), reserved bits = 0, others = undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |          | 2. HD6417760BP200AD, HD6417760BP200ADV                                                                      |

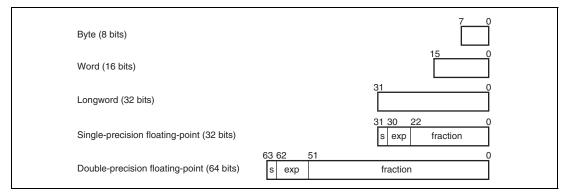

| Table 2.1 Initial  Register Values  Control registers SR  MD bit = 1, RB bit = 1, BL bit = 1, FD bit = 0, IMASK = 1111 (H'F), reserved bits = 0, others = undefined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                    | 41       |                                                                                                             |

| 3.1 Features 51 Description amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 2.1 Initial    |          | Control registers SR MD bit = 1, RB bit = 1, BL bit = 1, FD bit = 0, IMASK = 1111 (H'F), reserved bits = 0, |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3.1 Features         | 51       | Description amended                                                                                         |

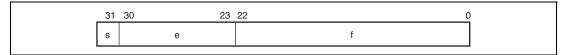

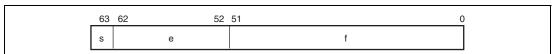

| Designed to meet IEEE754 standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |          | Designed to meet IEEE754 standard                                                                           |

| 3.7 Usage Notes 63 to 66 Newly added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.7 Usage Notes      | 63 to 66 | Newly added                                                                                                 |

| 4.4 Usage Note 84 to 86 Newly added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.4 Usage Note       | 84 to 86 | Newly added                                                                                                 |

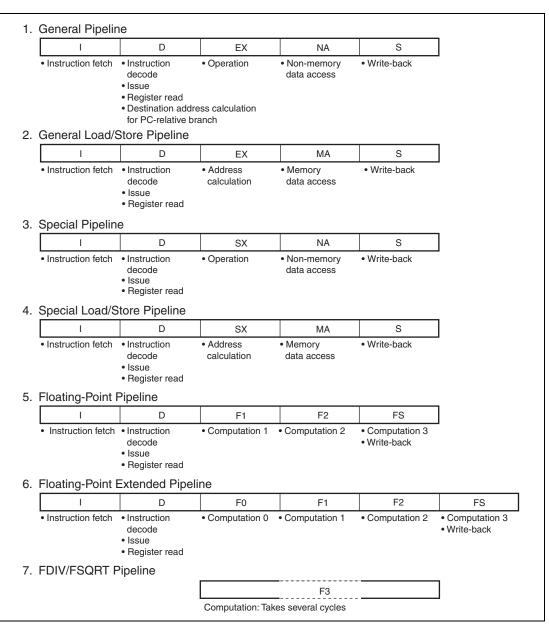

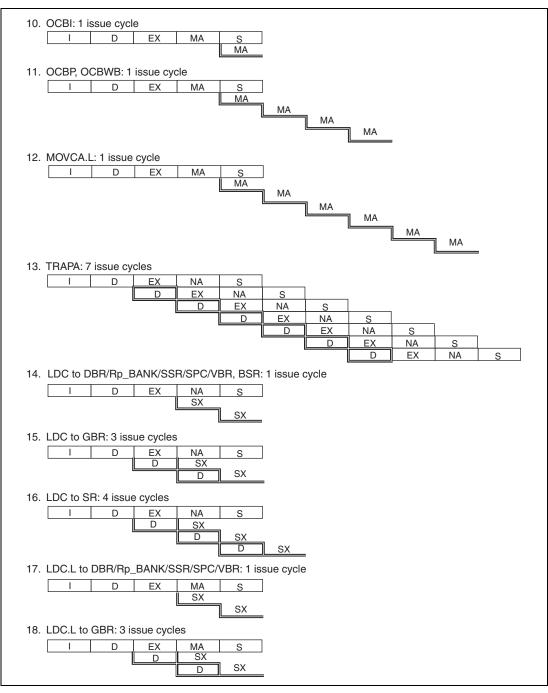

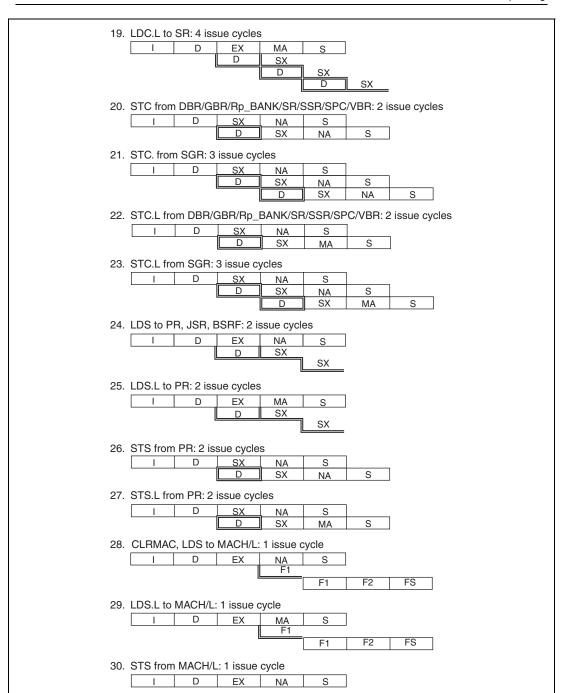

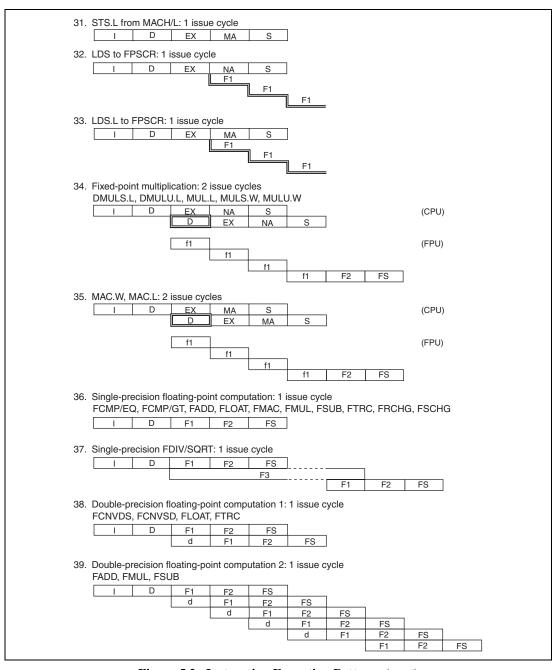

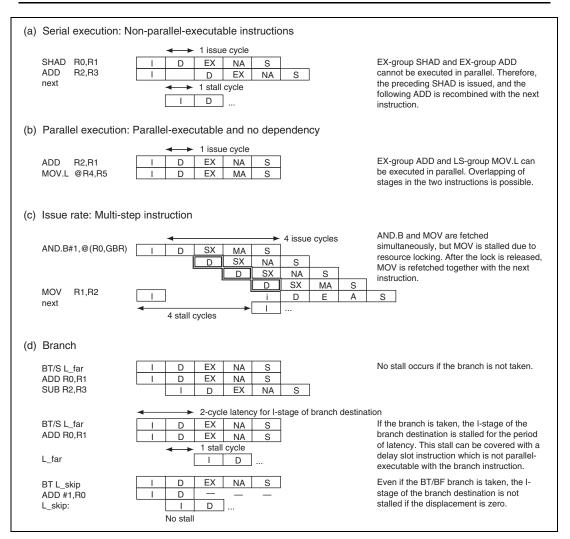

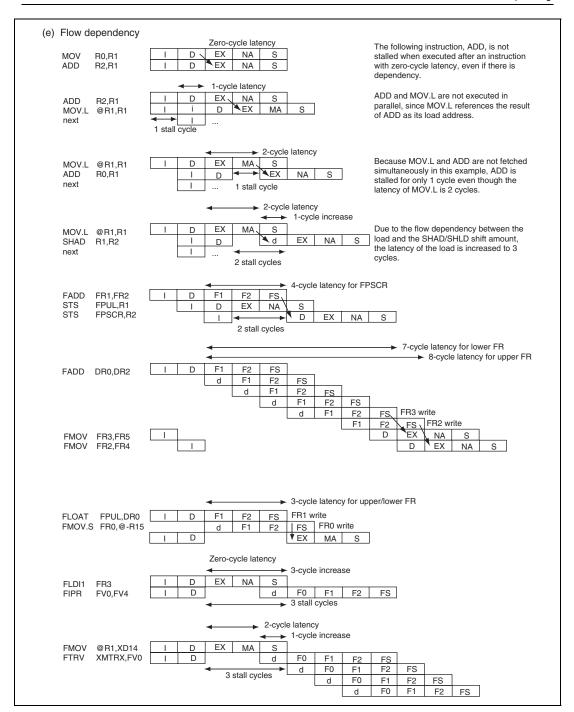

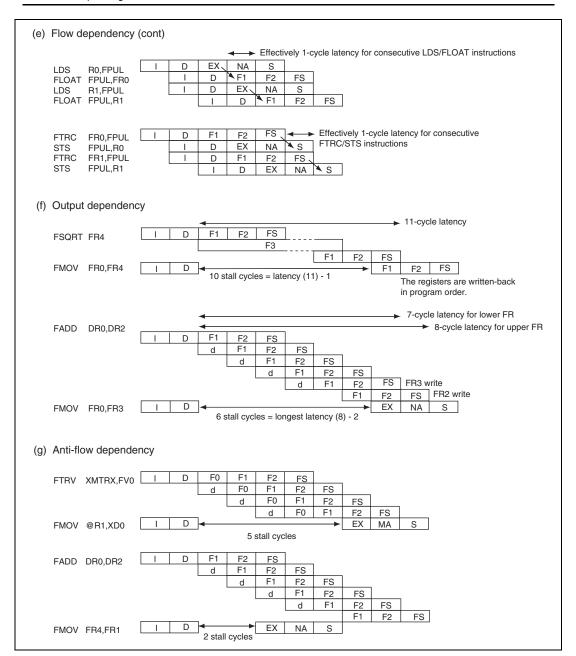

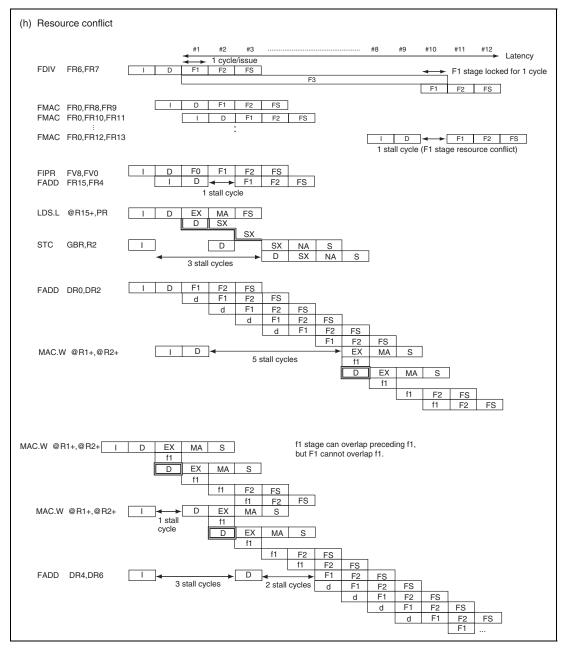

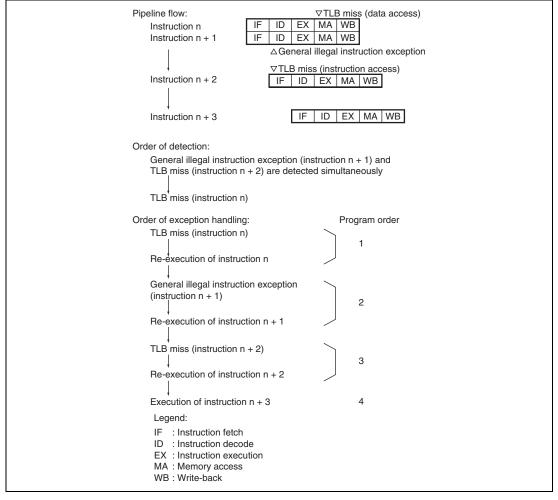

| Section 5 Pipelining 87 Description amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Section 5 Pipelining | 87       | •                                                                                                           |

| The definitions in this section may not be applied to the SH-4 products other than the SH7760.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |          |                                                                                                             |

| 5.4 Usage Note 112 Newly added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.4 Usage Note       | 112      | Newly added                                                                                                 |

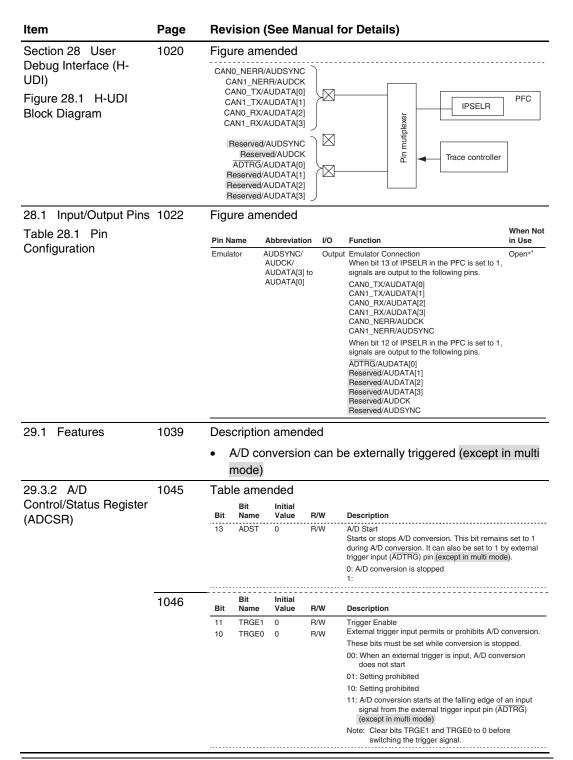

| Item                                                                           | Page          | Revision (See Manual for Details)                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

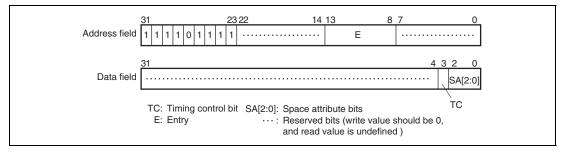

| 6.2.3 Page Table<br>Entry Assistance<br>Register (PTEA)                        | 124           | Description amended When performing access from the CPU in SH7760 to the PCMCIA interface area with the AT bit in MMUCR cleared to access is always performed using the values of the SA and TC bits in this register.                                           |  |  |  |  |  |  |  |

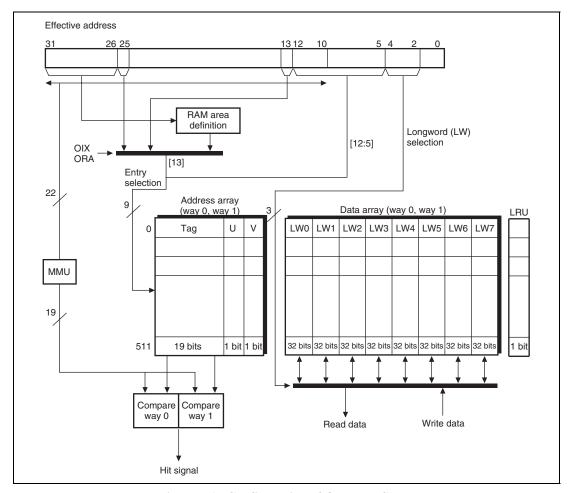

| 7.3.9 Note on Using Cache Enhanced Mode                                        | 164 to<br>166 | Newly added                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

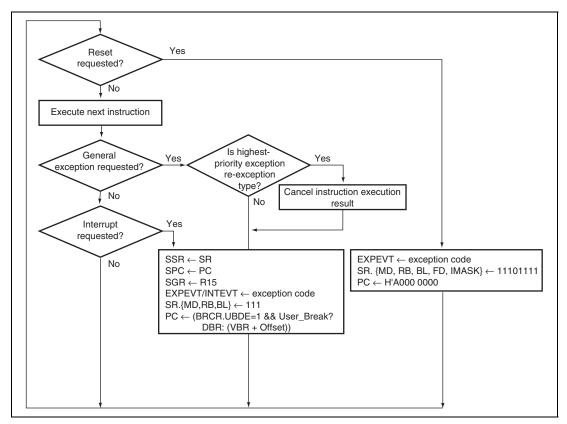

| 8.5.1 Resets (1) Power-On Reset                                                | 195           | Description amended SR.IMASK = B'1111;                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| (2) Manual Reset                                                               | 196           | Description amended SR.IMASK = B'1111;                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

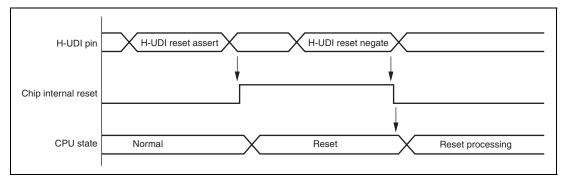

| (3) H-UDI Reset                                                                | 197           | Description amended SR.IMASK = B'1111;                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| (4) Instruction TLB<br>Multiple-Hit Exception                                  | 198           | Description amended SR.IMASK = B'1111;                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| (5) Data TLB Multiple-<br>Hit Exception                                        | 199           | Description amended SR.IMASK = B'1111;                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 8.7.1 Restrictions on<br>First Instruction in<br>Exception Handling<br>Routine | 220           | Note added  When the UBDE bit in BRCR is set to 1 and the user break debug support function* is used, do not locate a BT, BF, BT/S, BF/S, BRA, or BSR instruction at the address indicated by DBR.  Note: * See section 31.5, User Break Debug Support Function. |  |  |  |  |  |  |  |

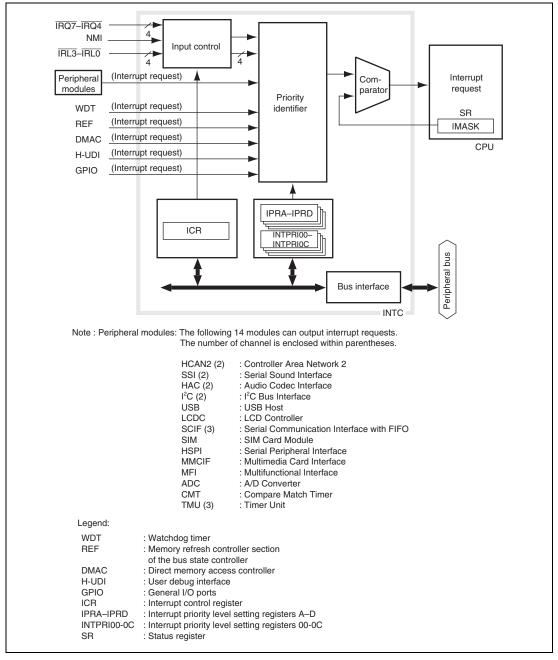

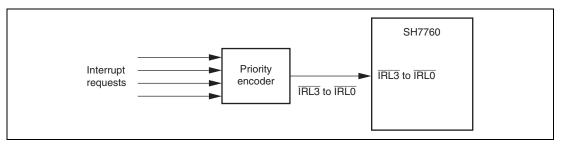

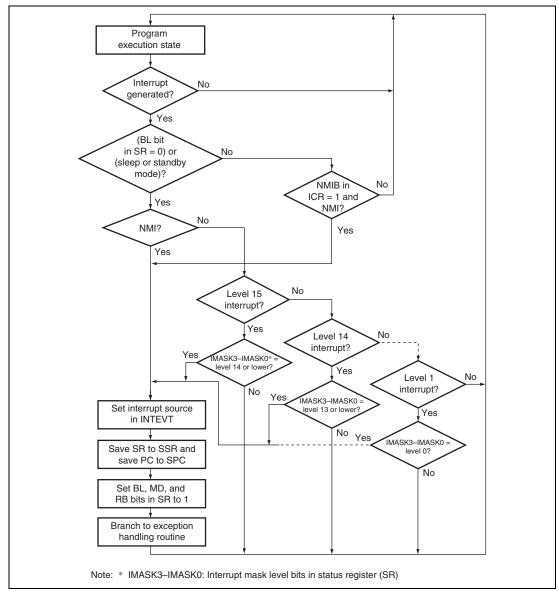

| 9.1 Features Figure 9.1 Block Diagram of INTC                                  | 222           | Figure amended  Interrupt request SR IMASK CPU                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| 9.2 Input/Output Pins<br>Table 9.1 Pin<br>Configuration                        | 223           | Table amended  Pin Name Abbreviation I/O Function  IRL interrupt input pins IRL3 to IRL0 Input Input of IRL interrupt request signals (maskable by the IMASK bits in SR)                                                                                         |  |  |  |  |  |  |  |