#### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## 32

# SH7780

### Hardware Manual

Renesas 32-Bit RISC Microcomputer SuperH<sup>™</sup> RISC Engine Family SH7780 Series

R8A77800A

#### Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

#### **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

#### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

#### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

#### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

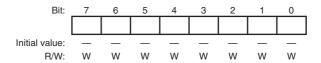

#### 5. Reading from/Writing Reserved Bit of Each Register

Note: Treat the reserved bit of register used in each module as follows except in cases where the specifications for values which are read from or written to the bit are provided in the description.

The bit is always read as 0. The write value should be 0 or one, which has been read immediately before writing.

Writing the value, which has been read immediately before writing has the advantage of preventing the bit from being affected on its extended function when the function is assigned.

Rev.1.00 Dec. 13, 2005 Page iv of I

### Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. Electrical Characteristics

- 8. Appendix

- 9. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

10. Index

#### **Preface**

This LSI is a RISC (Reduced Instruction Set Computer) microcomputer which includes a Renesas Technology-original RISC CPU as its core, and the peripheral functions required to configure a system.

Target Users: This manual was written for users who will be using this LSI in the design of

application systems. Users of this manual are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of this LSI to the above users.

Notes on reading this manual:

• In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts

on the CPU, system control functions, peripheral functions and electrical characteristics.

Rules: Bit order: The MSB is on the left and the LSB is on the right.

Number notation: Binary is B'xxxx, hexadecimal is H'xxxx, decimal is xxxx.

Signal notation: An overbar is added to a low-active signal: xxxx

#### **Abbreviations**

Arithmetic Logic Unit ALU

**ASID** Address Space Identifier

**BGA** Ball Grid Array

**CMT** Compare Match Timer (Timer/Counter)

**CPG** Clock Pulse Generator

CPU Central Processing Unit

DDR Double Data Rate

DDRIF **DDR-SDRAM** Interface

DMA **Direct Memory Access**

DMAC **Direct Memory Access Controller**

**FIFO** First-In First-Out

FLCTL NAND Flash Memory Controller

FPU Floating-point Unit

HAC Audio Codec

**HSPI** Serial Protocol Interface

User Debugging Interface H-UDI

Interrupt Controller **INTC**

Joint Test Action Group **JTAG**

**LBSC** Local Bus State Controller

LRAM L Memory

Least Recently Used LRU

Least Significant Bit LSB

MMCIF Multimedia Card Interface

MMU Memory Management Unit

MSB Most Significant Bit

PC Program Counter

PCI Peripheral Component Interconnect

PCIC PCI (local bus) Controller

RISC Reduced Instruction Set Computer

RTC Realtime Clock

SCIF Serial Communication Interface with FIFO

SIOF Serial Interface with FIFO

SSI Serial Sound Interface

TAP Test Access Port

TLB Translation Lookaside Buffer

TMU Timer Unit

UART Universal Asynchronous Receiver/Transmitter

UBC User Break Controller

WDT Watchdog Timer

### Contents

| Sec | tion 1 Overview                    | 1  |

|-----|------------------------------------|----|

| 1.1 | SH7780 Features                    | 1  |

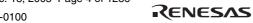

| 1.2 | Block Diagram                      | 9  |

| 1.3 | Pin Arrangement                    | 10 |

| 1.4 | Pin Functions                      | 11 |

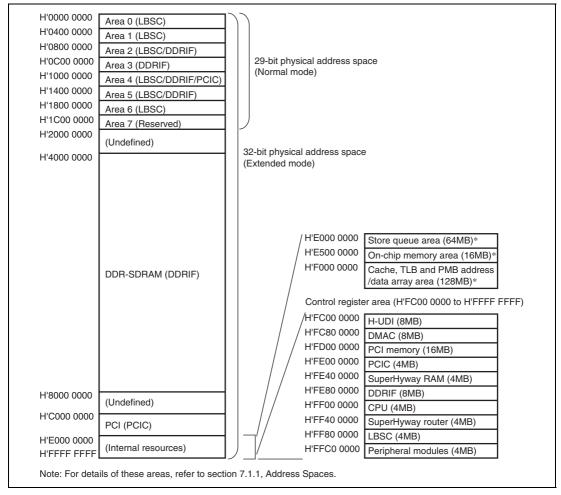

| 1.5 | Memory Address Map                 | 27 |

| 1.6 | SuperHyway Bus                     | 30 |

| 1.7 | SuperHyway Memory (SuperHyway RAM) | 31 |

| Sec | tion 2 Programming Model           | 33 |

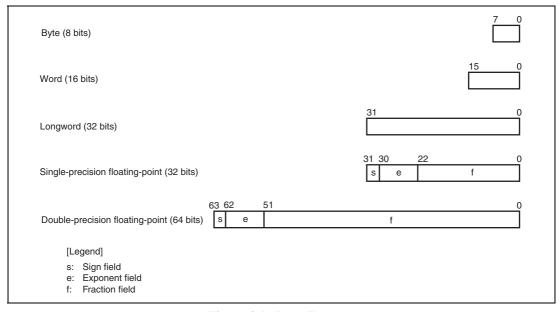

| 2.1 | Data Formats                       |    |

| 2.2 | Register Descriptions              |    |

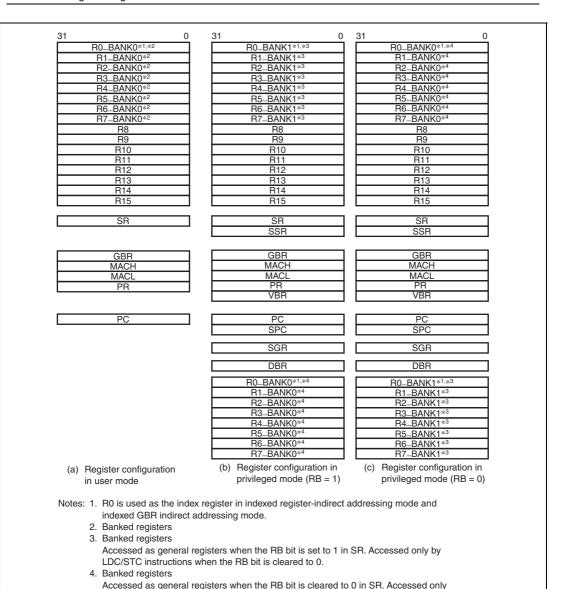

|     | 2.2.1 Privileged Mode and Banks    |    |

|     | 2.2.2 General Registers            | 37 |

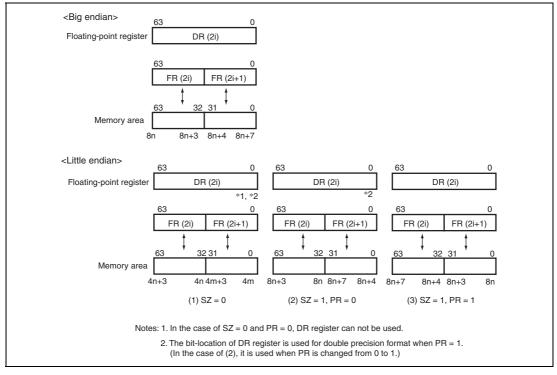

|     | 2.2.3 Floating-Point Registers     |    |

|     | 2.2.4 Control Registers            |    |

|     | 2.2.5 System Registers             |    |

| 2.3 | Memory-Mapped Registers            | 46 |

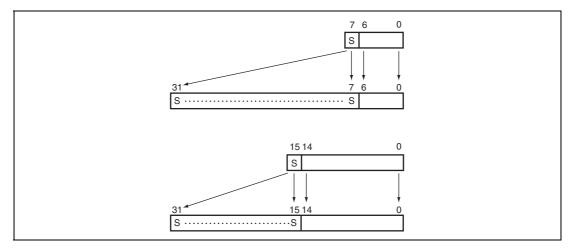

| 2.4 | Data Formats in Registers          |    |

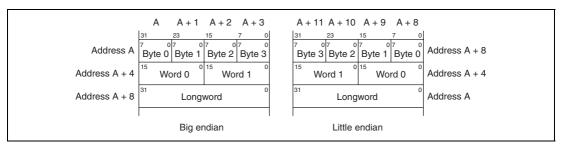

| 2.5 | Data Formats in Memory             | 48 |

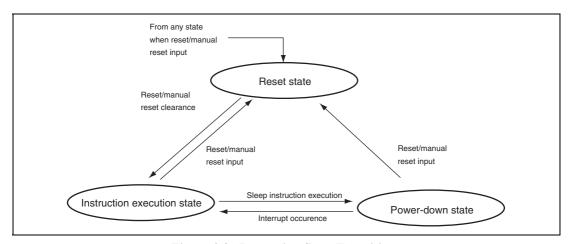

| 2.6 | Processing States                  | 49 |

| 2.7 | Usage Note                         | 50 |

|     | 2.7.1 Notes on self-modified codes | 50 |

| Sec | tion 3 Instruction Set             | 51 |

| 3.1 | Execution Environment              | 51 |

| 3.2 | Addressing Modes                   | 53 |

| 3.3 | Instruction Set                    | 57 |

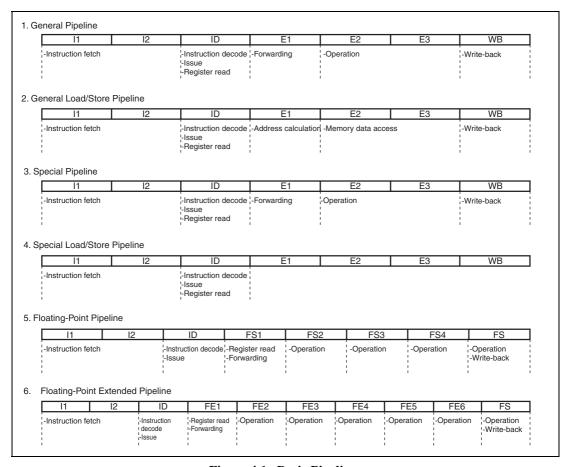

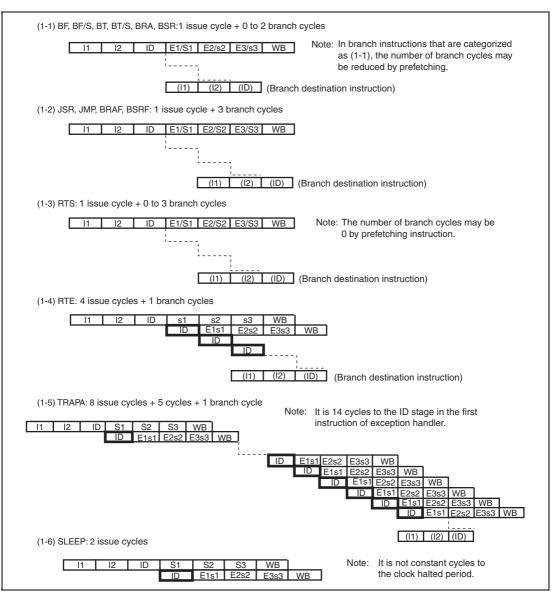

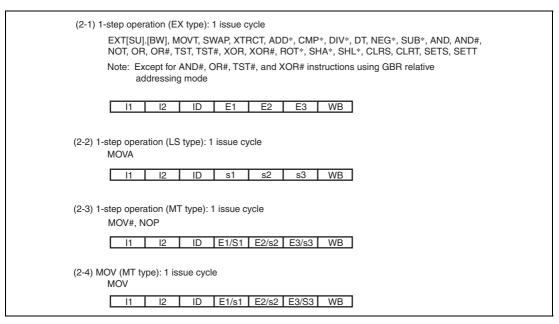

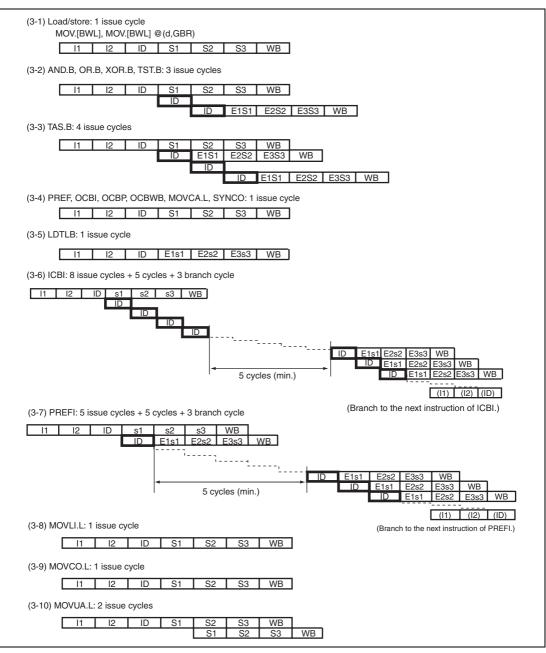

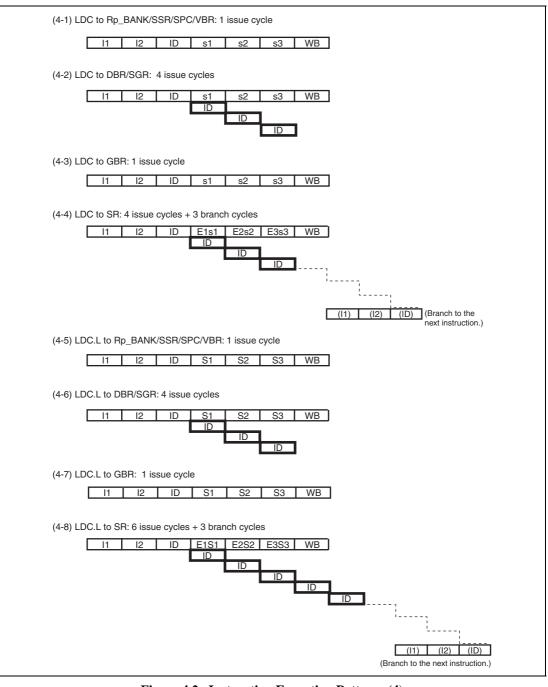

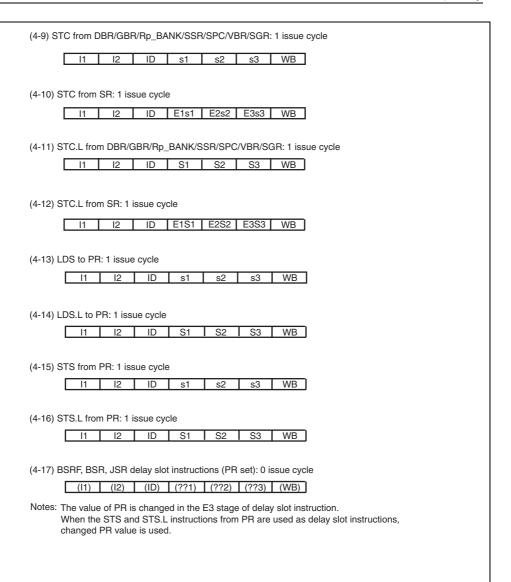

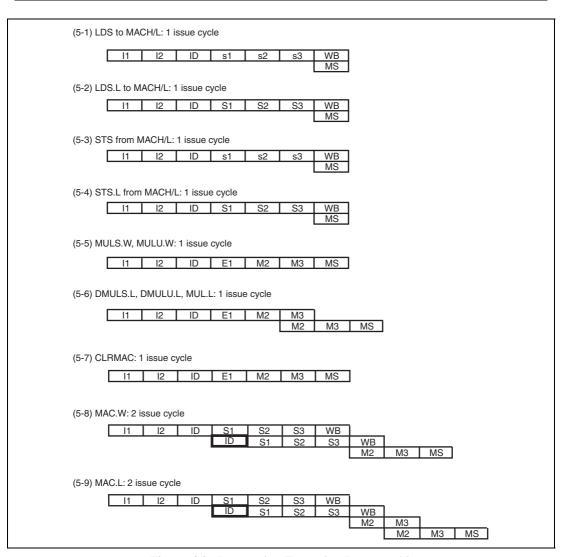

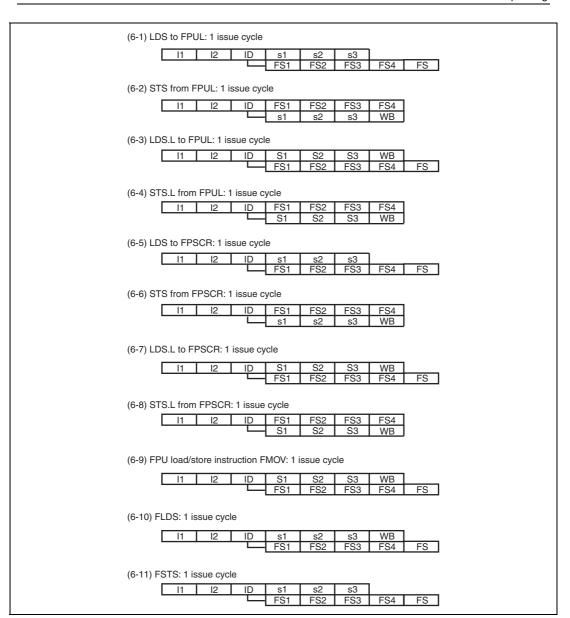

| Sec | tion 4 Pipelining                  | 73 |

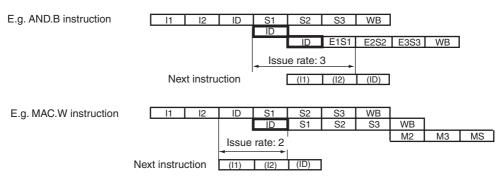

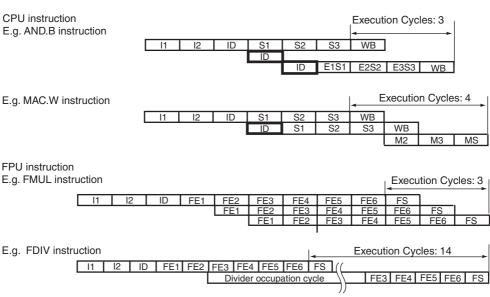

| 4.1 | Pipelines                          | 73 |

| 4.2 | Parallel-Executability             |    |

| 4.3 | Issue Rates and Execution Cycles   |    |

| Sec | tion 5 Exception Handling          | 97 |

| 5.1 | Summary of Exception Handling      |    |

| 5.2 | Regist | er Descriptions                                                       | 97  |

|-----|--------|-----------------------------------------------------------------------|-----|

|     | 5.2.1  | TRAPA Exception Register (TRA)                                        | 98  |

|     | 5.2.2  | Exception Event Register (EXPEVT)                                     | 99  |

|     | 5.2.3  | Interrupt Event Register (INTEVT)                                     | 100 |

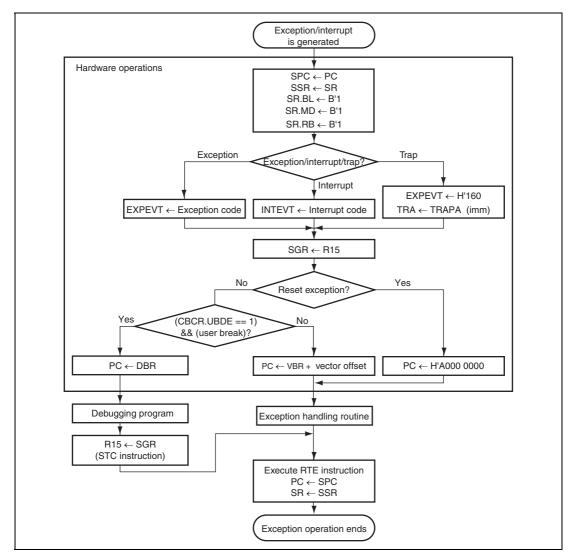

| 5.3 | Excep  | tion Handling Functions                                               | 101 |

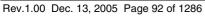

|     | 5.3.1  | Exception Handling Flow                                               | 101 |

|     | 5.3.2  | Exception Handling Vector Addresses                                   | 101 |

| 5.4 | Excep  | tion Types and Priorities                                             | 102 |

| 5.5 | Excep  | tion Flow                                                             | 104 |

|     | 5.5.1  | Exception Flow                                                        | 104 |

|     | 5.5.2  | Exception Source Acceptance                                           | 106 |

|     | 5.5.3  | Exception Requests and BL Bit                                         | 107 |

|     | 5.5.4  | Return from Exception Handling                                        | 107 |

| 5.6 | Descri | ption of Exceptions                                                   | 108 |

|     | 5.6.1  | Resets                                                                | 108 |

|     | 5.6.2  | General Exceptions                                                    | 110 |

|     | 5.6.3  | Interrupts                                                            | 124 |

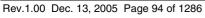

|     | 5.6.4  | Priority Order with Multiple Exceptions                               | 125 |

| 5.7 | Usage  | Notes                                                                 | 127 |

| Sac | tion 6 | Floating-Point Unit (FPU)                                             | 120 |

| 6.1 |        | res                                                                   |     |

| 6.2 |        | Formats                                                               |     |

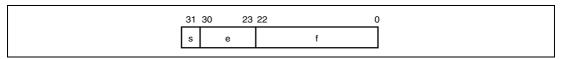

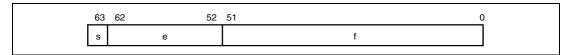

| 0.2 | 6.2.1  | Floating-Point Format                                                 |     |

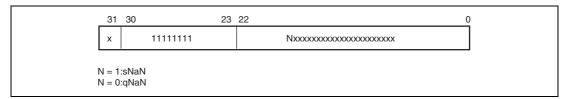

|     | 6.2.2  | Non-Numbers (NaN)                                                     |     |

|     | 6.2.3  | Denormalized Numbers                                                  |     |

| 6.3 | 0      | er Descriptions                                                       |     |

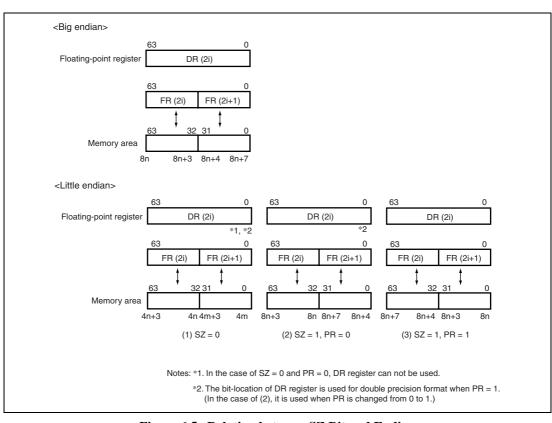

| 0.5 | 6.3.1  | Floating-Point Registers                                              |     |

|     | 6.3.2  | Floating-Point Status/Control Register (FPSCR)                        |     |

|     | 6.3.3  | Floating-Point Communication Register (FPUL)                          |     |

| 6.4 |        | ling                                                                  |     |

| 6.5 |        | ng-Point Exceptions                                                   |     |

| 0.5 | 6.5.1  | General FPU Disable Exceptions and Slot FPU Disable Exceptions        |     |

|     | 6.5.2  | FPU Exception Sources                                                 |     |

|     | 6.5.3  | •                                                                     |     |

| 66  |        | FPU Exception Handling                                                |     |

| 6.6 | 6.6.1  | ics Support Functions                                                 |     |

|     |        | Geometric Operation Instructions  Pair Single-Precision Data Transfer |     |

|     | 6.6.2  | ran Single-Precision Data Transfer                                    | 145 |

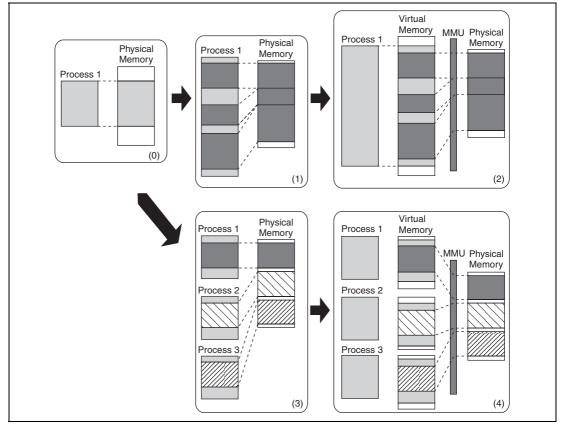

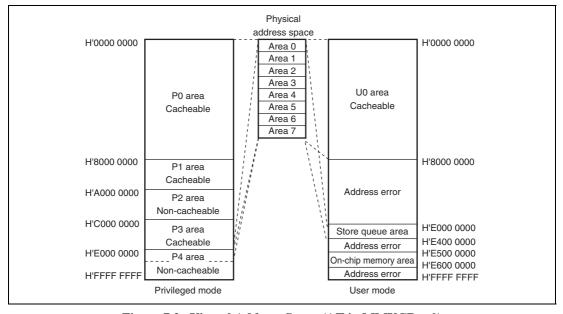

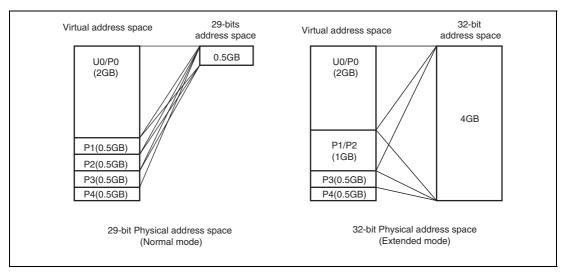

| Sect | ion 7  | Memory Management Unit (MMU)                          | 147 |

|------|--------|-------------------------------------------------------|-----|

| 7.1  |        | iew of MMU                                            |     |

|      | 7.1.1  | Address Spaces                                        |     |

| 7.2  | Regist | ter Descriptions                                      |     |

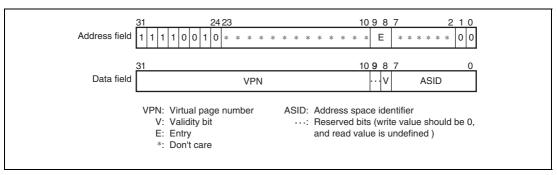

|      | 7.2.1  | Page Table Entry High Register (PTEH)                 |     |

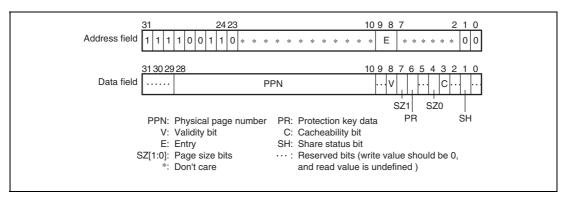

|      | 7.2.2  | Page Table Entry Low Register (PTEL)                  |     |

|      | 7.2.3  | Translation Table Base Register (TTB)                 |     |

|      | 7.2.4  | TLB Exception Address Register (TEA)                  |     |

|      | 7.2.5  | MMU Control Register (MMUCR)                          | 160 |

|      | 7.2.6  | Physical Address Space Control Register (PASCR)       |     |

|      | 7.2.7  | Instruction Re-Fetch Inhibit Control Register (IRMCR) |     |

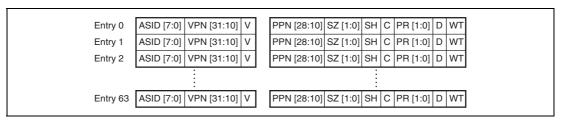

| 7.3  | TLB F  | Functions                                             |     |

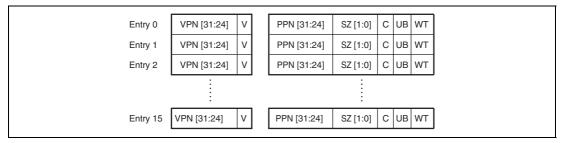

|      | 7.3.1  | Unified TLB (UTLB) Configuration                      |     |

|      | 7.3.2  | Instruction TLB (ITLB) Configuration                  | 170 |

|      | 7.3.3  | Address Translation Method                            |     |

| 7.4  | MMU    | Functions                                             | 173 |

|      | 7.4.1  | MMU Hardware Management                               | 173 |

|      | 7.4.2  | MMU Software Management                               | 173 |

|      | 7.4.3  | MMU Instruction (LDTLB)                               |     |

|      | 7.4.4  | Hardware ITLB Miss Handling                           | 175 |

|      | 7.4.5  | Avoiding Synonym Problems                             | 176 |

| 7.5  | MMU    | Exceptions                                            | 177 |

|      | 7.5.1  | Instruction TLB Multiple Hit Exception                | 177 |

|      | 7.5.2  | Instruction TLB Miss Exception                        |     |

|      | 7.5.3  | Instruction TLB Protection Violation Exception        | 179 |

|      | 7.5.4  | Data TLB Multiple Hit Exception                       |     |

|      | 7.5.5  | Data TLB Miss Exception                               | 180 |

|      | 7.5.6  | Data TLB Protection Violation Exception               | 181 |

|      | 7.5.7  | Initial Page Write Exception                          | 182 |

| 7.6  | Memo   | ory-Mapped TLB Configuration                          | 183 |

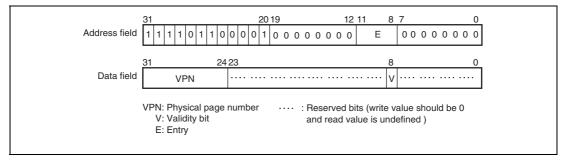

|      | 7.6.1  | ITLB Address Array                                    | 184 |

|      | 7.6.2  | ITLB Data Array                                       | 185 |

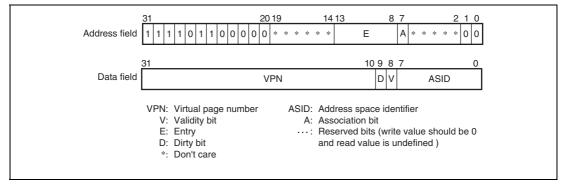

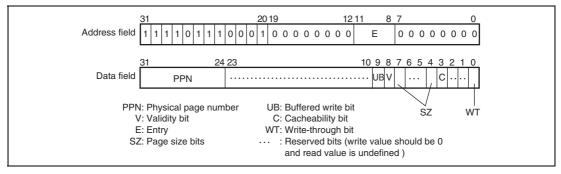

|      | 7.6.3  | UTLB Address Array                                    | 186 |

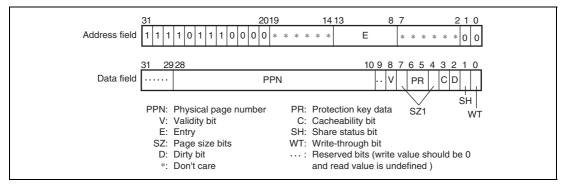

|      | 7.6.4  | UTLB Data Array                                       | 187 |

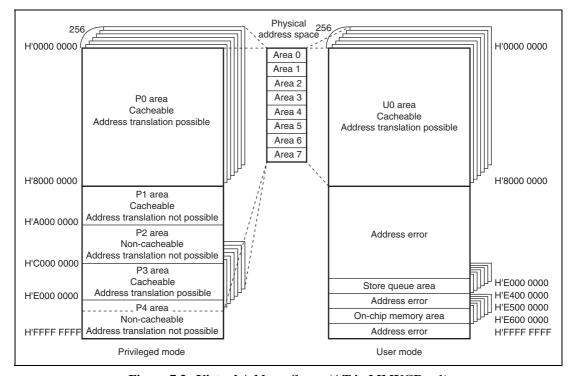

| 7.7  | 32-Bit | Address Extended Mode                                 | 188 |

|      | 7.7.1  | Overview of 32-Bit Address Extended Mode              | 189 |

|      | 7.7.2  | Transition to 32-Bit Address Extended Mode            |     |

|      | 7.7.3  | Privileged Space Mapping Buffer (PMB) Configuration   | 189 |

|      | 7.7.4  | PMB Function                                          | 191 |

|      | 7.7.5  | Memory-Mapped PMB Configuration             | 192 |

|------|--------|---------------------------------------------|-----|

|      | 7.7.6  | Notes on Using 32-Bit Address Extended Mode | 194 |

|      |        |                                             |     |

| Sect | ion 8  | Caches                                      | 197 |

| 8.1  | Featu  | res                                         | 197 |

| 8.2  | Regis  | ster Descriptions                           | 200 |

|      | 8.2.1  | Cache Control Register (CCR)                | 201 |

|      | 8.2.2  | Queue Address Control Register 0 (QACR0)    | 203 |

|      | 8.2.3  | Queue Address Control Register 1 (QACR1)    | 204 |

|      | 8.2.4  | On-Chip Memory Control Register (RAMCR)     | 205 |

| 8.3  | Opera  | and Cache Operation                         | 207 |

|      | 8.3.1  | Read Operation                              | 207 |

|      | 8.3.2  | Prefetch Operation                          | 208 |

|      | 8.3.3  | Write Operation                             | 209 |

|      | 8.3.4  | Write-Back Buffer                           | 211 |

|      | 8.3.5  | Write-Through Buffer                        | 211 |

|      | 8.3.6  | OC Two-Way Mode                             | 211 |

| 8.4  | Instru | action Cache Operation                      | 212 |

|      | 8.4.1  | Read Operation                              | 212 |

|      | 8.4.2  | Prefetch Operation                          | 213 |

|      | 8.4.3  | IC Two-Way Mode                             | 213 |

| 8.5  | Cach   | e Operation Instruction                     | 214 |

|      | 8.5.1  | Coherency between Cache and External Memory |     |

|      | 8.5.2  | Prefetch Operation                          | 215 |

| 8.6  | Mem    | ory-Mapped Cache Configuration              |     |

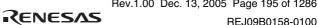

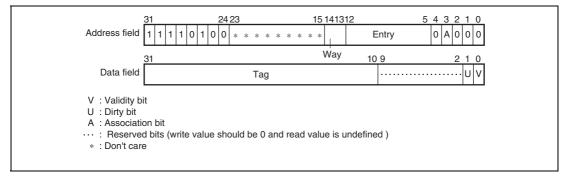

|      | 8.6.1  | IC Address Array                            |     |

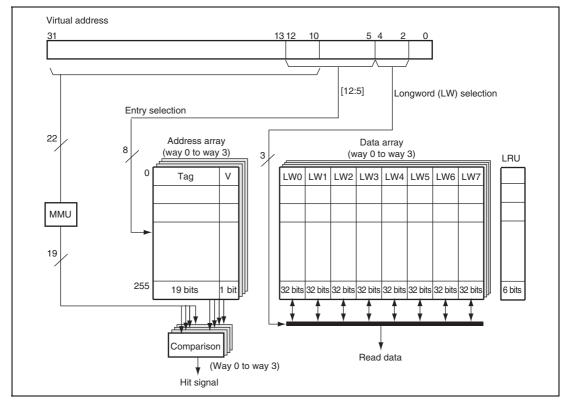

|      | 8.6.2  | IC Data Array                               | 219 |

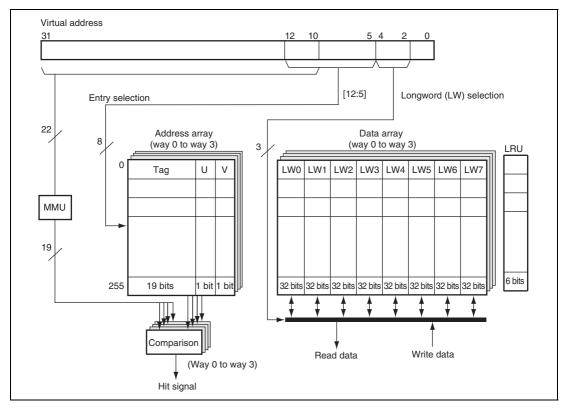

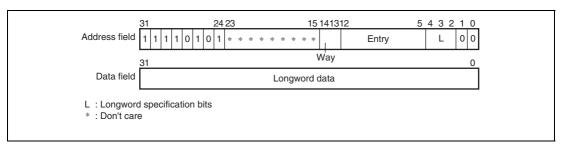

|      | 8.6.3  | OC Address Array                            |     |

|      | 8.6.4  | OC Data Array                               |     |

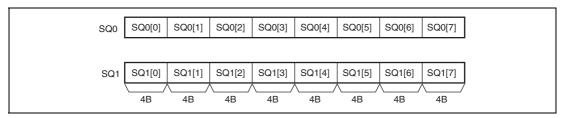

| 8.7  | Store  | Queues                                      |     |

|      | 8.7.1  | SQ Configuration                            |     |

|      | 8.7.2  | Writing to SQ                               |     |

|      | 8.7.3  | Transfer to External Memory                 |     |

|      | 8.7.4  | Determination of SQ Access Exception        |     |

|      | 8.7.5  | Reading from SQ                             |     |

| 8.8  | Notes  | s on Using 32-Bit Address Extended Mode     |     |

| Sect | ion 9  | L Memory                                    | 227 |

| 9.1  |        | res                                         |     |

| 9.2  |        | eter Descriptions                           | 228 |

|      | 9.2.1   | On-Chip Memory Control Register (RAMCR)                            | 229 |

|------|---------|--------------------------------------------------------------------|-----|

|      | 9.2.2   | L Memory Transfer Source Address Register 0 (LSA0)                 | 230 |

|      | 9.2.3   | L Memory Transfer Source Address Register 1 (LSA1)                 | 232 |

|      | 9.2.4   | L Memory Transfer Destination Address Register 0 (LDA0)            | 234 |

|      | 9.2.5   | L Memory Transfer Destination Address Register 1 (LDA1)            |     |

| 9.3  | Operat  | ion                                                                |     |

|      | 9.3.1   | Access from the CPU and FPU                                        | 238 |

|      | 9.3.2   | Access from the SuperHyway Bus Master Module                       |     |

|      | 9.3.3   | Block Transfer                                                     |     |

| 9.4  | L Men   | nory Protective Functions                                          |     |

| 9.5  |         | Notes                                                              |     |

|      | 9.5.1   | Page Conflict                                                      |     |

|      | 9.5.2   | L Memory Coherency                                                 | 241 |

|      | 9.5.3   | Sleep Mode                                                         |     |

| 9.6  | Note of | n Using 32-Bit Address Extended Mode                               |     |

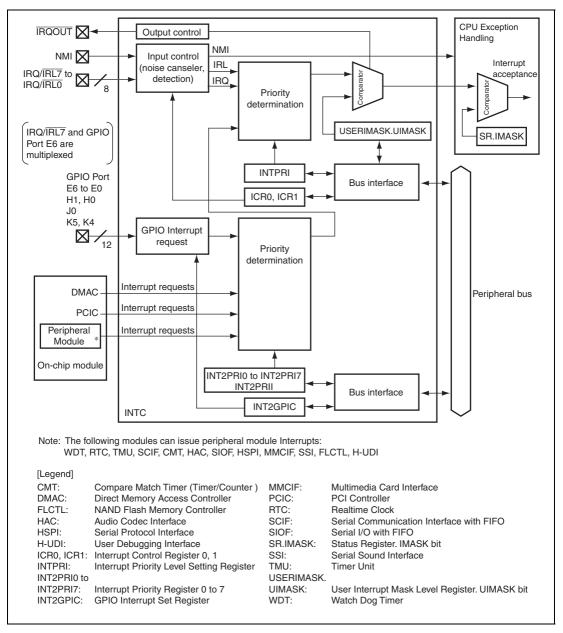

| Sect | ion 10  | Interrupt Controller (INTC)                                        | 243 |

| 10.1 |         | es                                                                 |     |

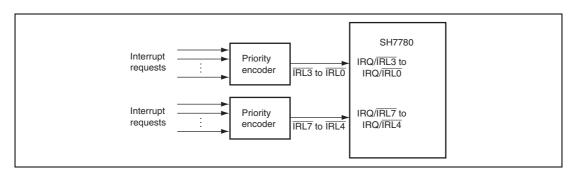

|      |         | Interrupt Method                                                   |     |

|      |         | Interrupt Types in INTC                                            |     |

| 10.2 |         | Output Pins                                                        |     |

| 10.3 | -       | er Descriptions                                                    |     |

|      | _       | Interrupt Control Register 0 (ICR0)                                |     |

|      |         | Interrupt Control Register 1 (ICR1)                                |     |

|      |         | Interrupt Priority Register (INTPRI)                               |     |

|      |         | Interrupt Source Register (INTREQ)                                 |     |

|      |         | Interrupt Mask Registers (INTMSK0 to INTMSK2)                      |     |

|      |         | Interrupt Mask Clear Registers (INTMSKCLR0 to INTMSKCLR2)          |     |

|      |         | NMI Flag Control Register (NMIFCR)                                 |     |

|      |         | User Interrupt Mask Level Register (USERIMASK)                     |     |

|      |         | On-chip Module Interrupt Priority Registers (INT2PRI0 to INT2PRI7) |     |

|      |         | Interrupt Source Register (INT2A0: Not affected by Mask States)    |     |

|      |         | I Interrupt Source Register (INT2A1: Affected by Mask States)      |     |

|      |         | 2 Interrupt Mask Register (INT2MSKR)                               |     |

|      |         | 3 Interrupt Mask Clear Register (INT2MSKCR)                        |     |

|      |         | 4 On-chip Module Interrupt Source Registers (INT2B0 to INT2B7)     |     |

|      |         | 5 GPIO Interrupt Set Register (INT2GPIC)                           |     |

| 10.4 |         | pt Sources                                                         |     |

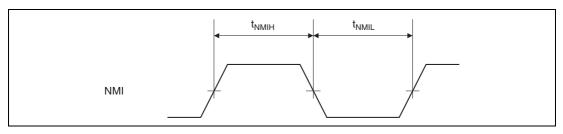

|      |         | NMI Interrupt                                                      |     |

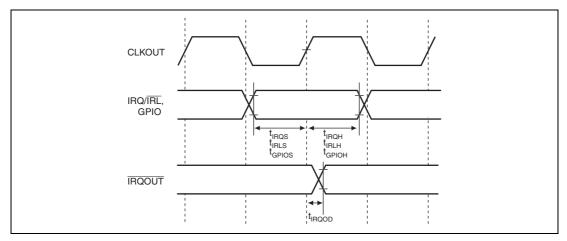

|      |         | IRQ Interrupts                                                     |     |

|      |         | •                                                                  |     |

RENESAS

|      | 10.4.3  | IRL Interrupts                                            | 297 |

|------|---------|-----------------------------------------------------------|-----|

|      | 10.4.4  | On-chip Module Interrupts                                 | 299 |

|      |         | Interrupt Priority Levels of On-chip Module Interrupts    |     |

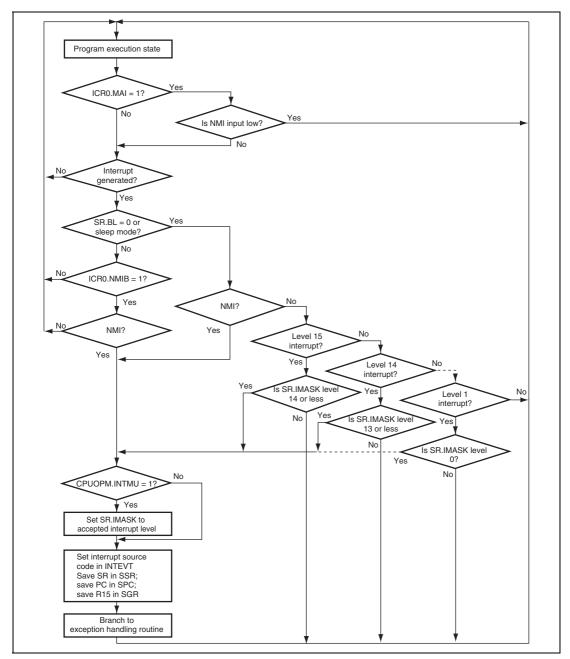

|      | 10.4.6  | Interrupt Exception Handling and Priority                 | 301 |

| 10.5 | Operat  | ion                                                       | 308 |

|      | 10.5.1  | Interrupt Sequence                                        | 308 |

|      | 10.5.2  | Multiple Interrupts                                       | 310 |

|      | 10.5.3  | Interrupt Masking by MAI Bit                              | 310 |

| 10.6 | Interru | pt Response Time                                          | 311 |

| 10.7 | Usage   | Notes                                                     | 312 |

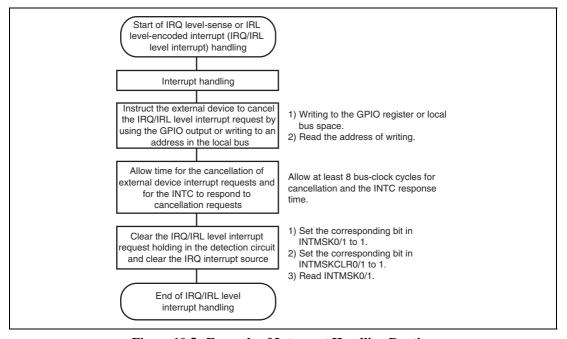

|      | 10.7.1  | To Clear Interrupt Request When Holding Function Selected | 312 |

|      | 10.7.2  | Notes on Setting IRQ/IRL[7:0] Pin Function                | 313 |

|      | 10.7.3  | To clear IRQ and IRL interrupt requests                   | 313 |

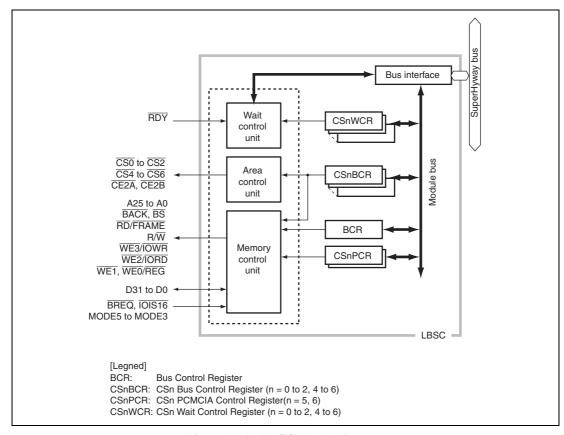

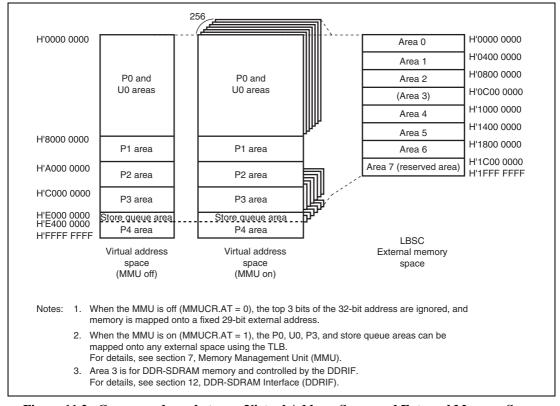

| Sact | ion 11  | Local Bus State Controller (LBSC)                         | 315 |

| 11.1 |         | es                                                        |     |

| 11.1 |         | Output Pins                                               |     |

| 11.3 |         | Overview                                                  |     |

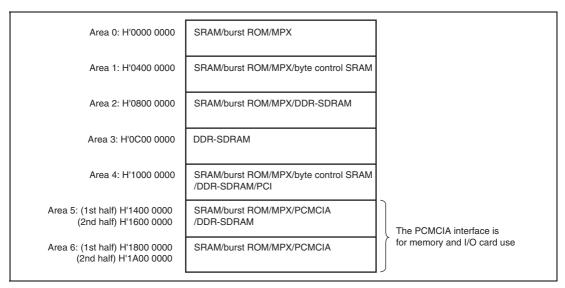

| 11.5 |         | Space Divisions                                           |     |

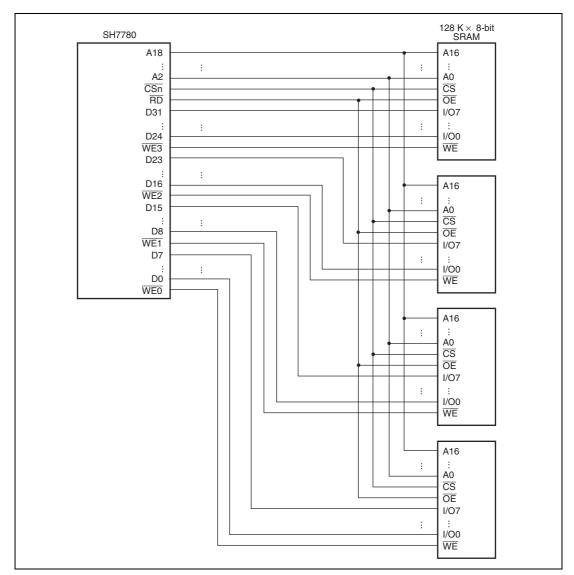

|      |         | Memory Bus Width                                          |     |

|      |         | Data Alignment                                            |     |

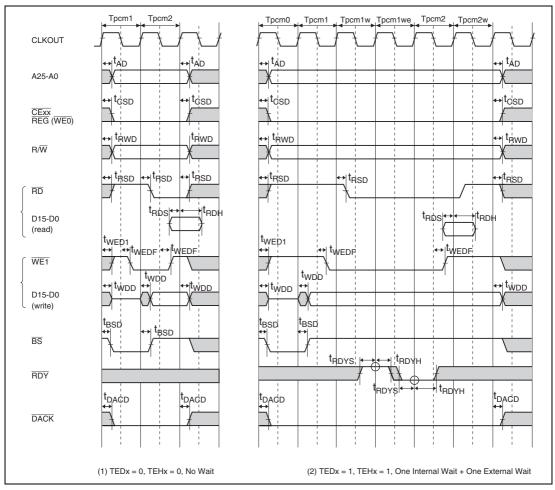

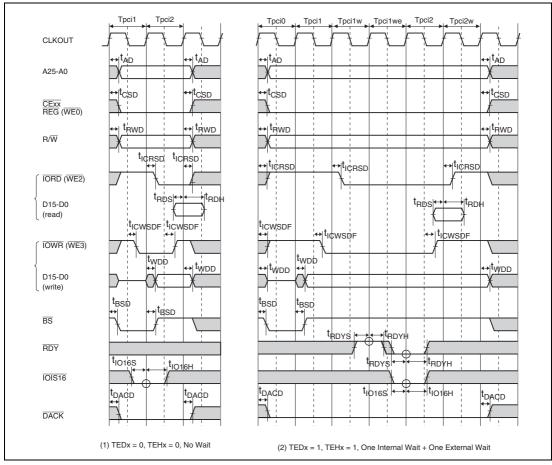

|      |         | PCMCIA Support                                            |     |

| 11.4 |         | er Descriptions                                           |     |

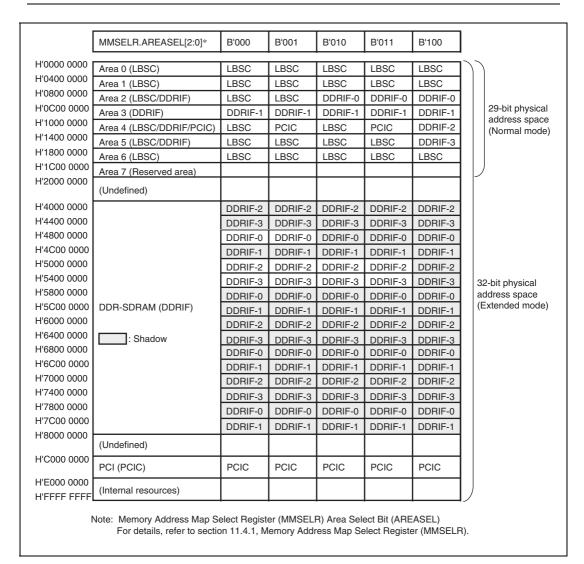

| 11.7 | _       | Memory Address Map Select Register (MMSELR)               |     |

|      |         | Bus Control Register (BCR)                                |     |

|      |         | CSn Bus Control Register (CSnBCR)                         |     |

|      |         | CSn Wait Control Register (CSnWCR)                        |     |

|      |         | CSn PCMCIA Control Register (CSnPCR)                      |     |

| 11.5 |         | ion                                                       |     |

| 11.5 | -       | Endian/Access Size and Data Alignment                     |     |

|      |         | Areas.                                                    |     |

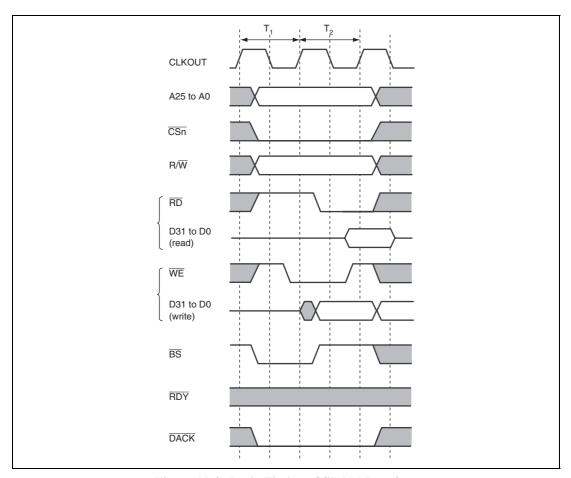

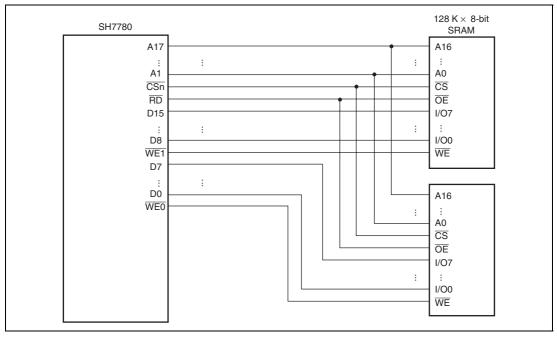

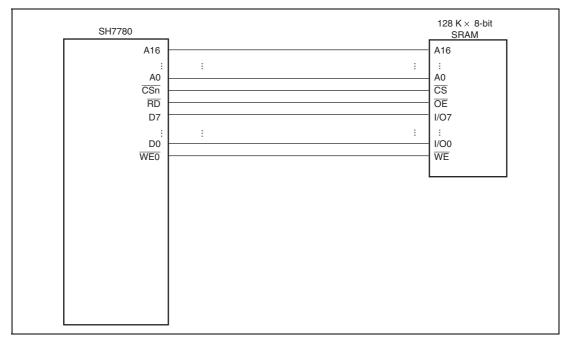

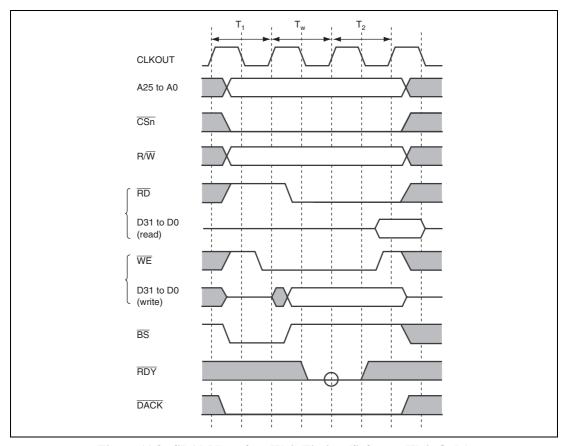

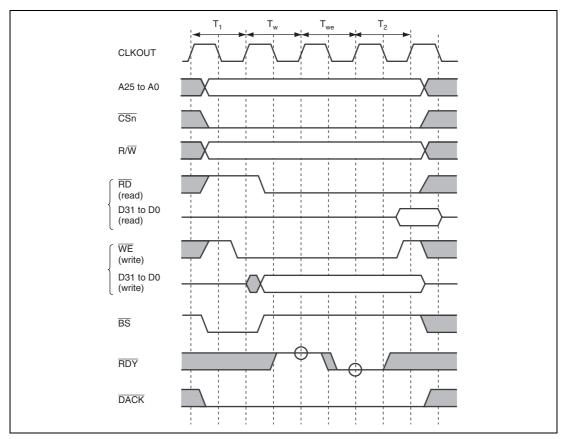

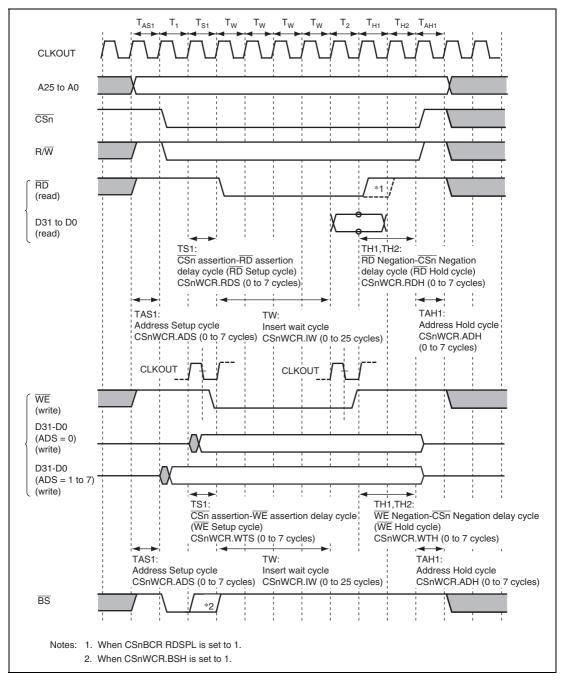

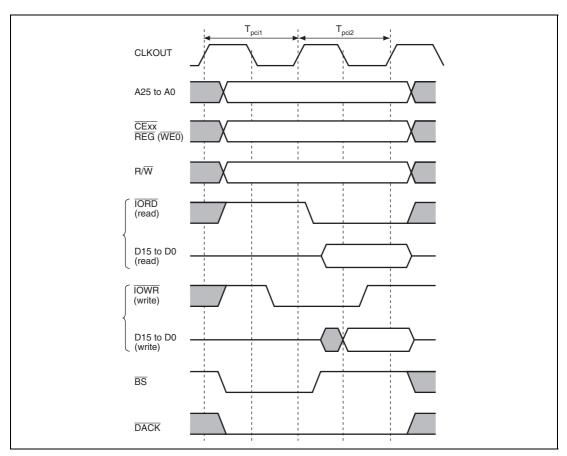

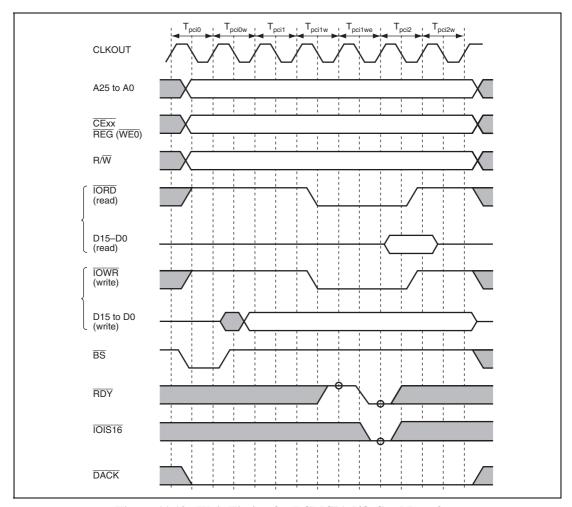

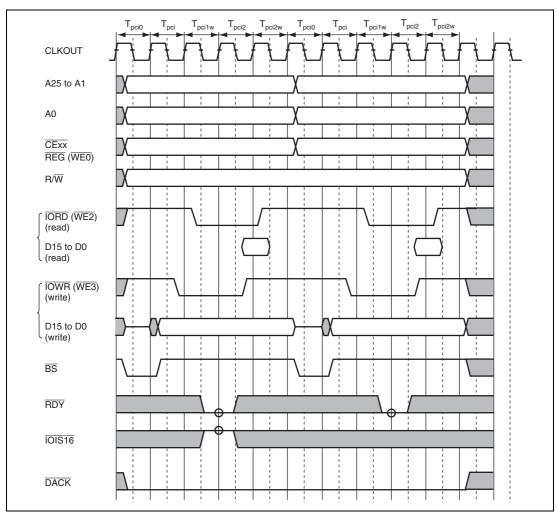

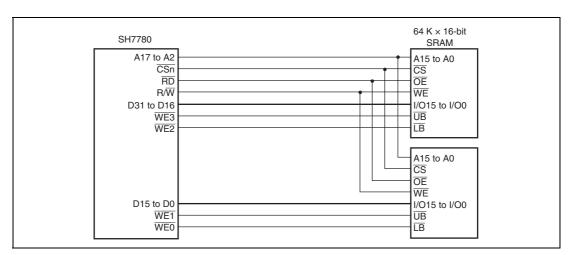

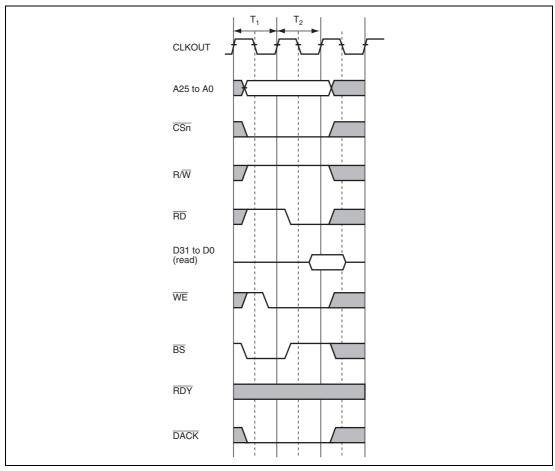

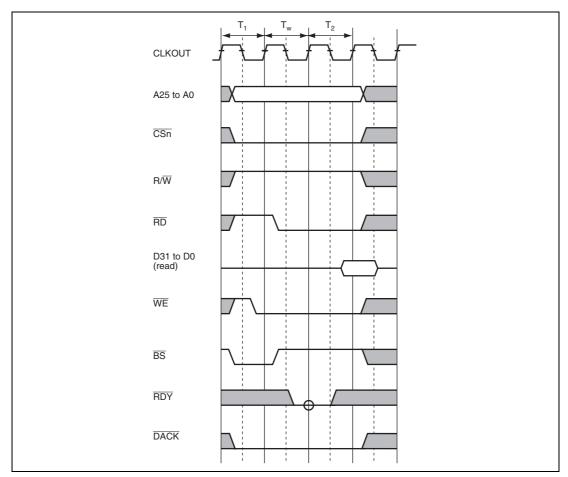

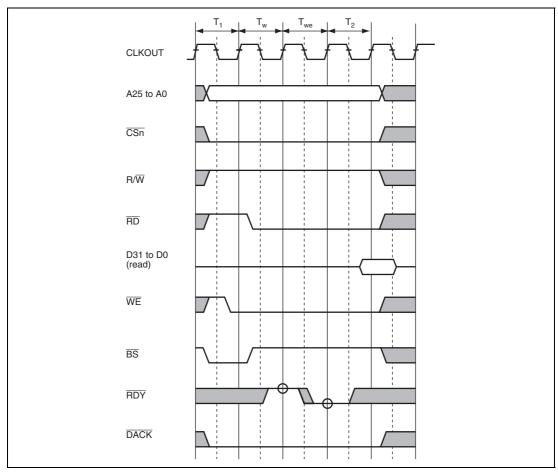

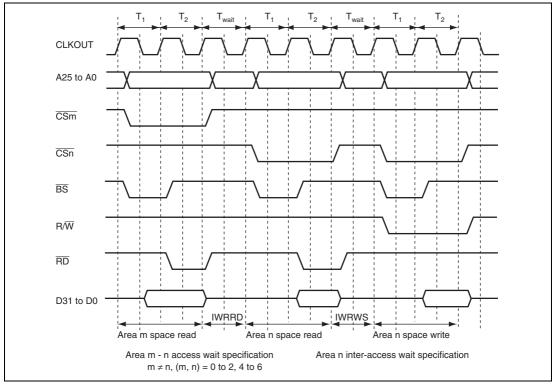

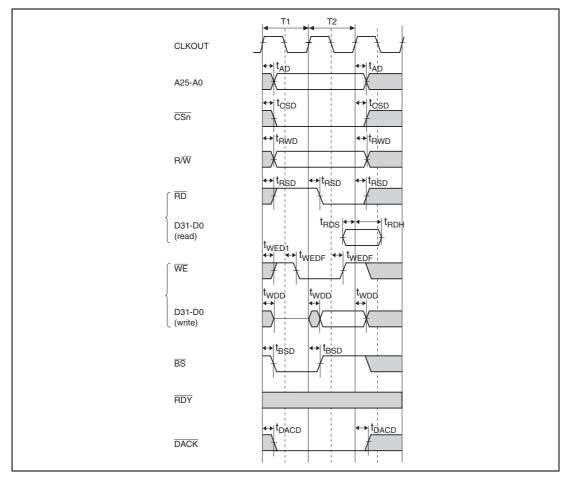

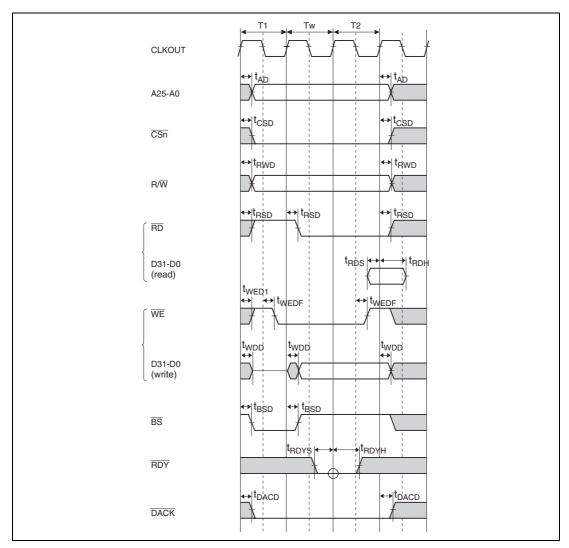

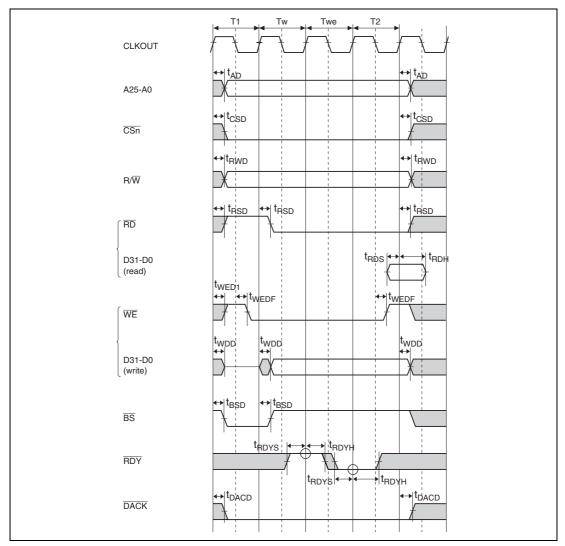

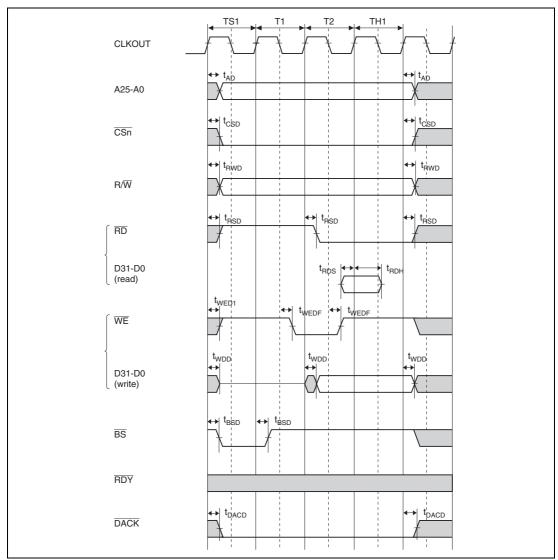

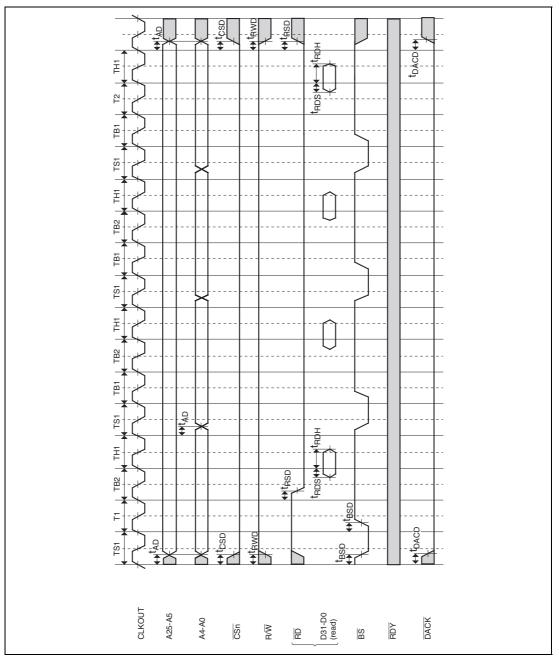

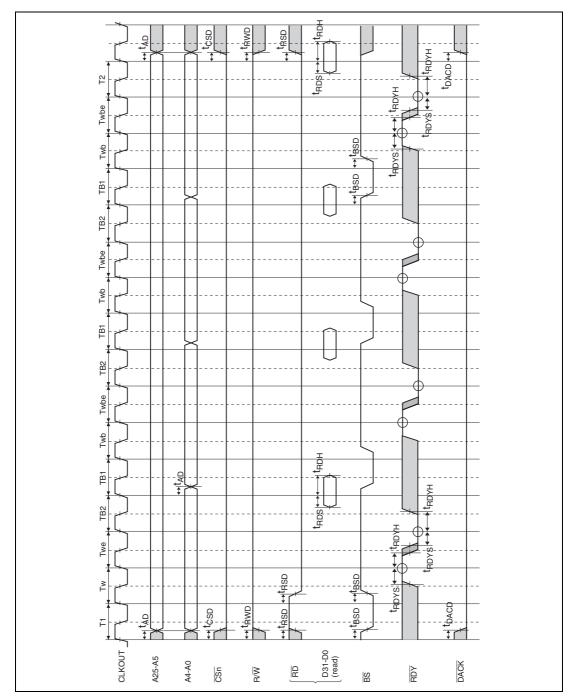

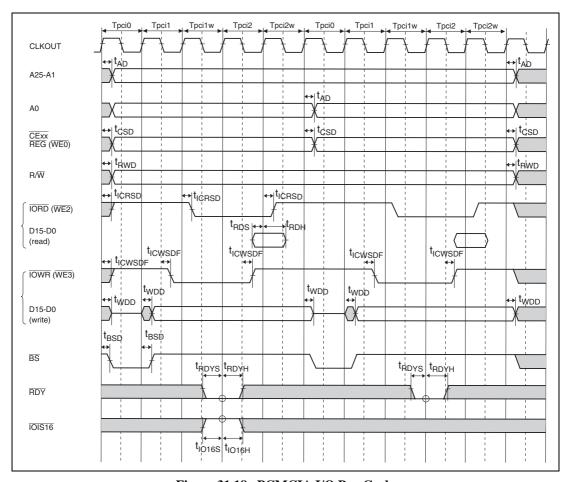

|      |         | SRAM interface                                            |     |

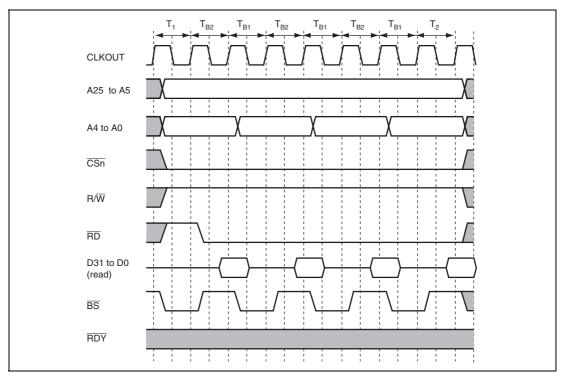

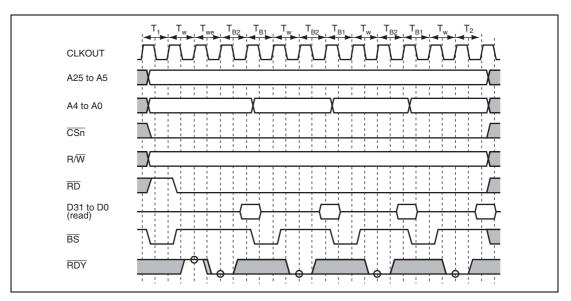

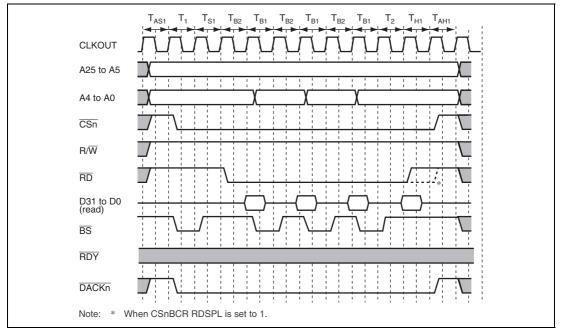

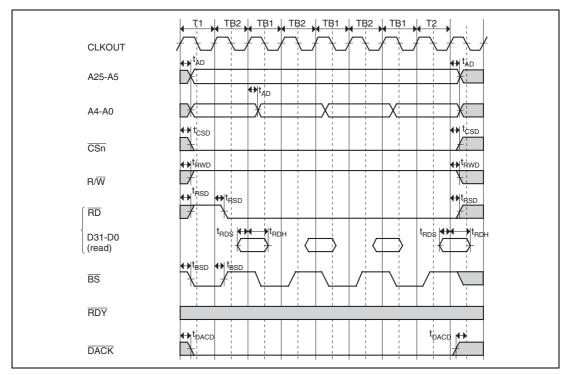

|      |         | Burst ROM (Clock Asynchronous) Interface                  |     |

|      |         | PCMCIA Interface                                          |     |

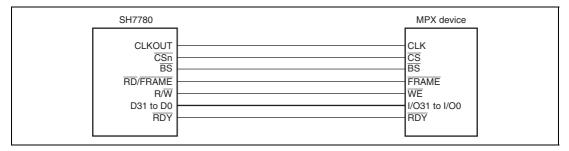

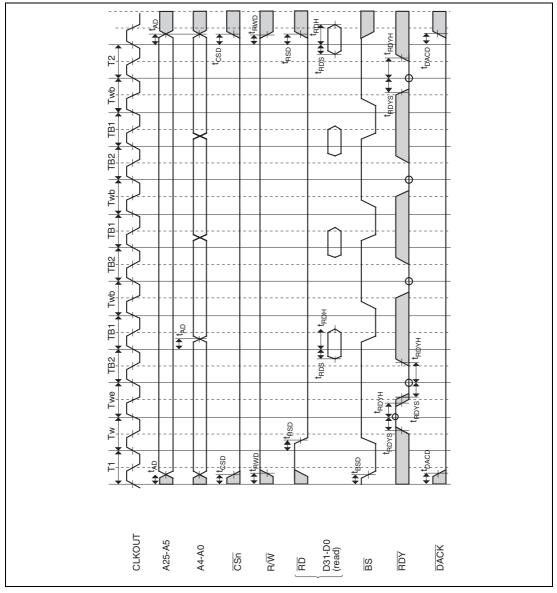

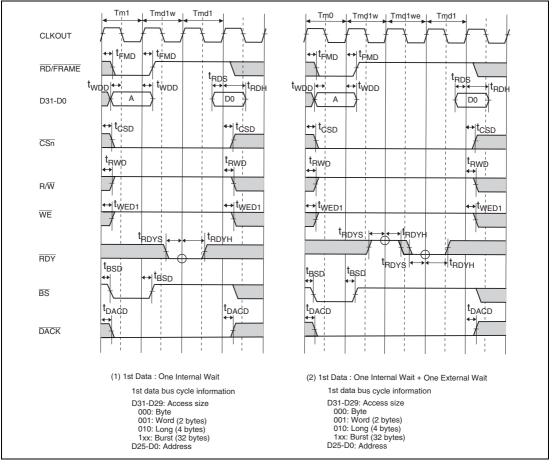

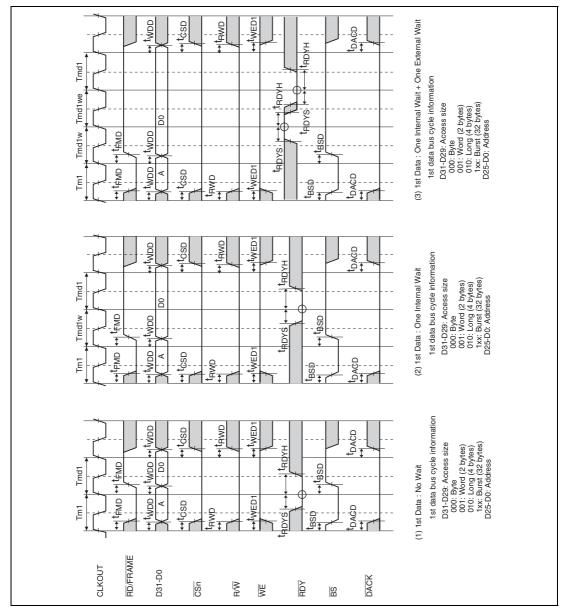

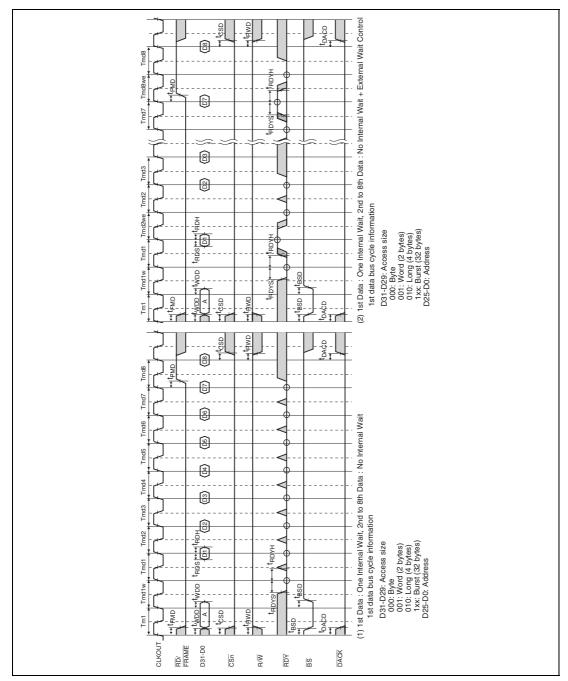

|      |         | MPX Interface                                             |     |

|      |         | Byte Control SRAM Interface                               |     |

|      |         | Wait Cycles between Accesses.                             |     |

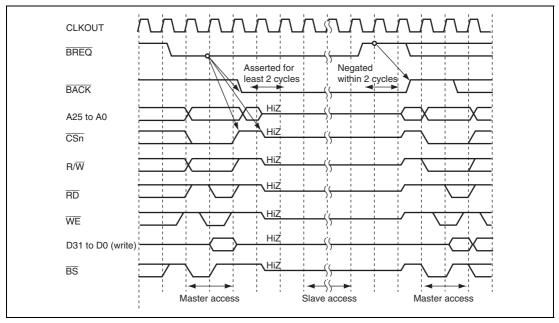

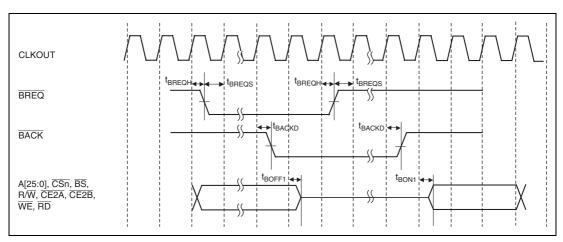

|      |         | Bus Arbitration                                           |     |

|      |         | ) Bus Release and Acquire Sequence                        |     |

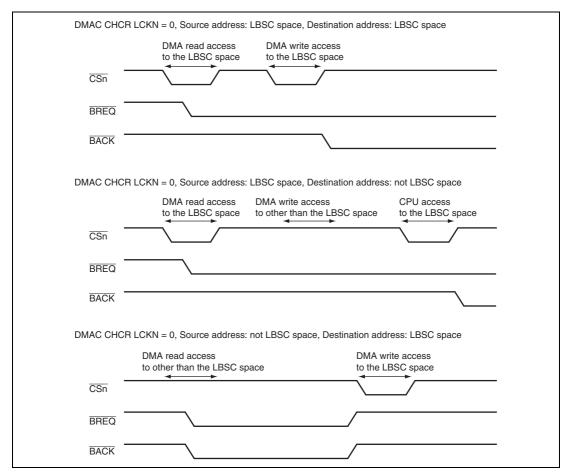

|      |         | Cooperation between Master and Slave                      |     |

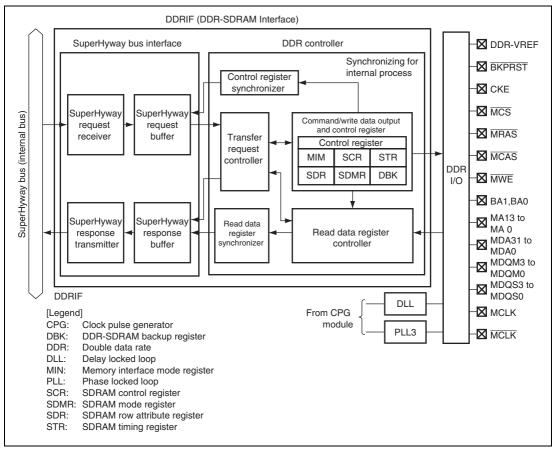

| Secti | on 12       | DDR-SDRAM Interface (DDRIF)                                           | 401 |

|-------|-------------|-----------------------------------------------------------------------|-----|

| 12.1  | Feature     | s                                                                     | 401 |

| 12.2  | Input/C     | Output Pins                                                           | 403 |

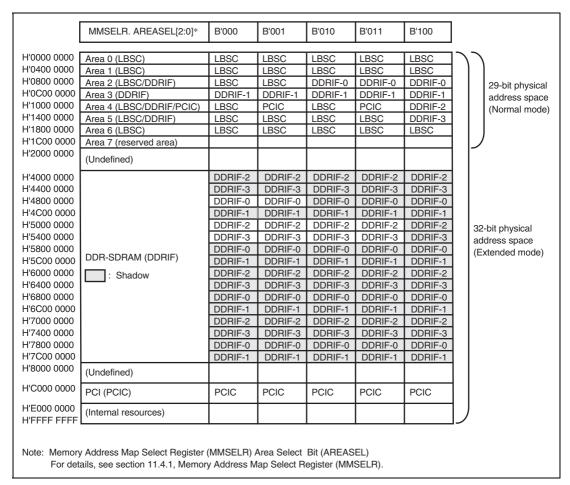

| 12.3  | Addres      | s Space, Bus Width, and Data Alignment                                | 404 |

|       | 12.3.1      | Address Space of the DDRIF                                            | 404 |

|       | 12.3.2      | Memory Data Bus Width                                                 | 405 |

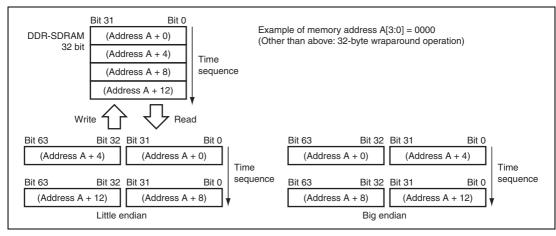

|       | 12.3.3      | Data Alignment                                                        | 406 |

| 12.4  |             | r Descriptions                                                        |     |

|       | 12.4.1      | Memory Interface Mode Register (MIM)                                  | 412 |

|       | 12.4.2      | SDRAM Control Register (SCR)                                          | 416 |

|       | 12.4.3      | SDRAM Timing Register (STR)                                           | 418 |

|       | 12.4.4      | SDRAM Row Attribute Register (SDR)                                    | 421 |

|       | 12.4.5      | SDRAM Mode Register (SDMR)                                            | 422 |

|       | 12.4.6      | DDR-SDRAM Back-up Register (DBK)                                      | 424 |

| 12.5  | Operati     | on                                                                    | 425 |

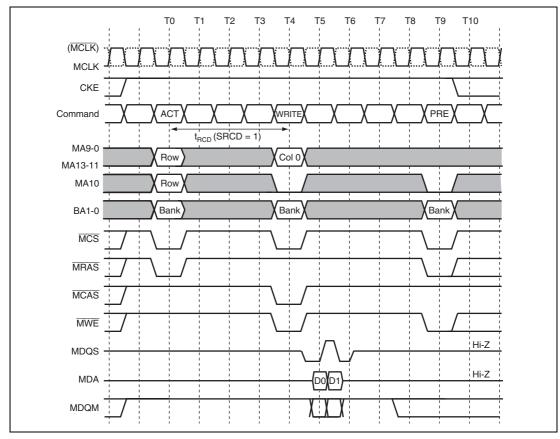

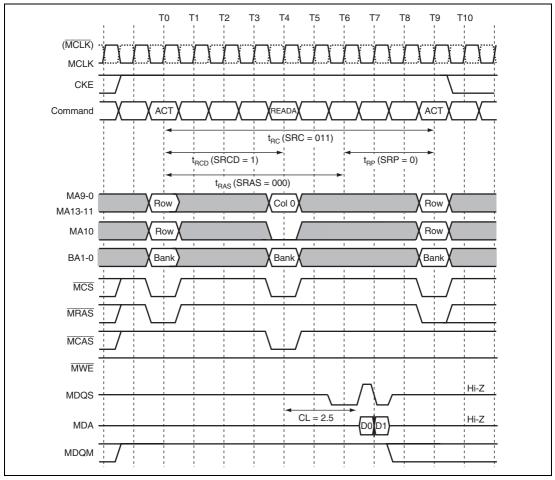

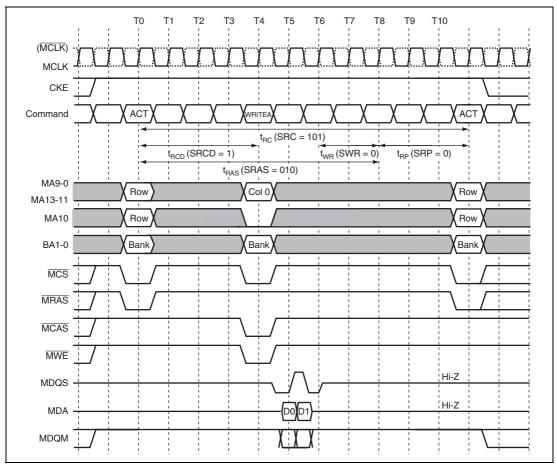

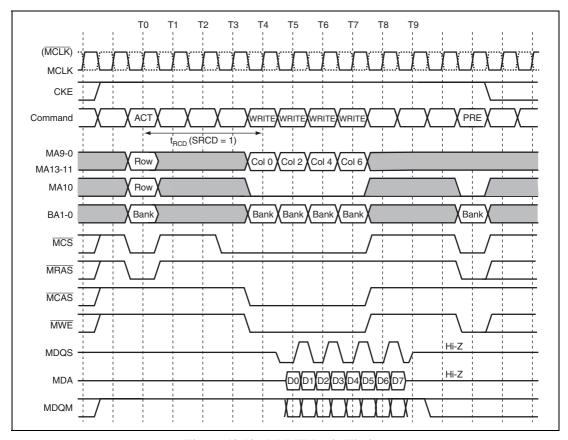

|       | 12.5.1      | DDR-SDRAM Access                                                      | 425 |

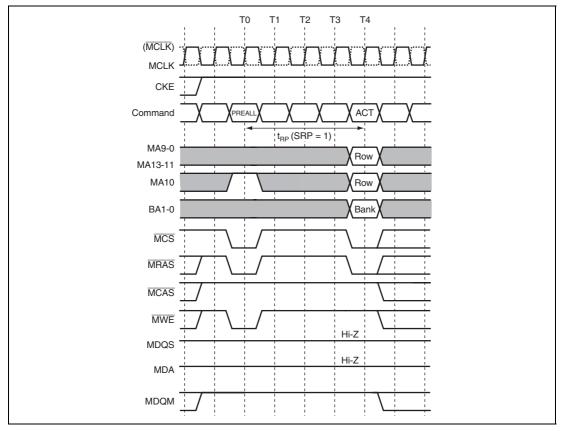

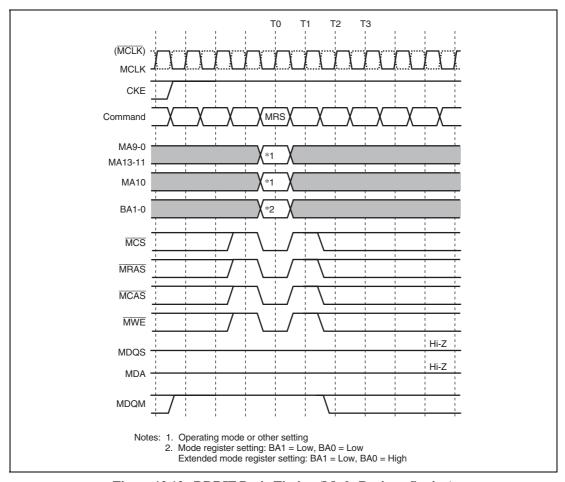

|       | 12.5.2      | DDR-SDRAM Initialization Sequence                                     | 425 |

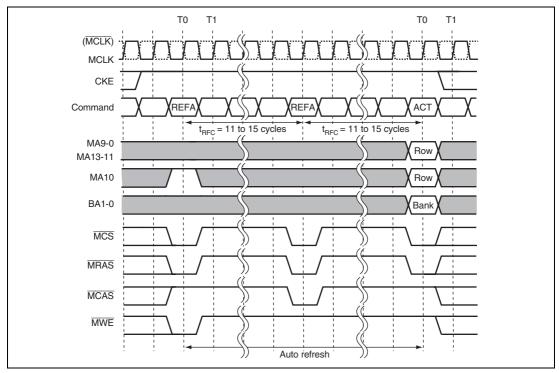

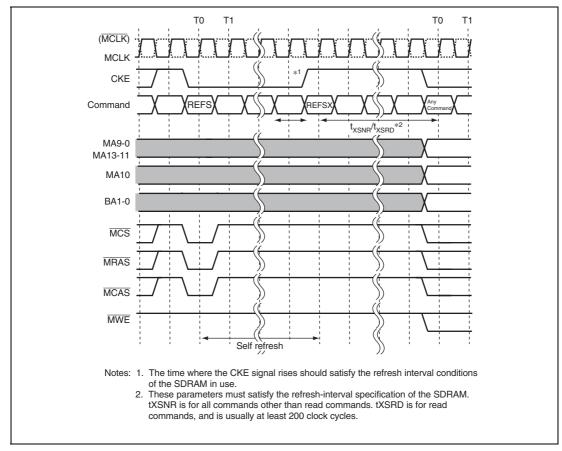

|       | 12.5.3      | Supported SDRAM Commands                                              | 426 |

|       | 12.5.4      | SDRAM Access Mode                                                     | 427 |

|       | 12.5.5      | Power-Down Modes                                                      | 427 |

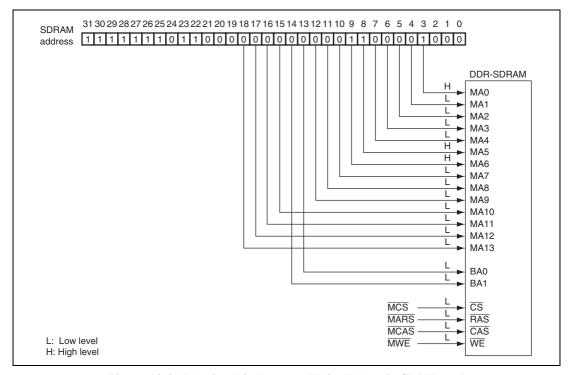

|       | 12.5.6      | Address Multiplexing                                                  | 429 |

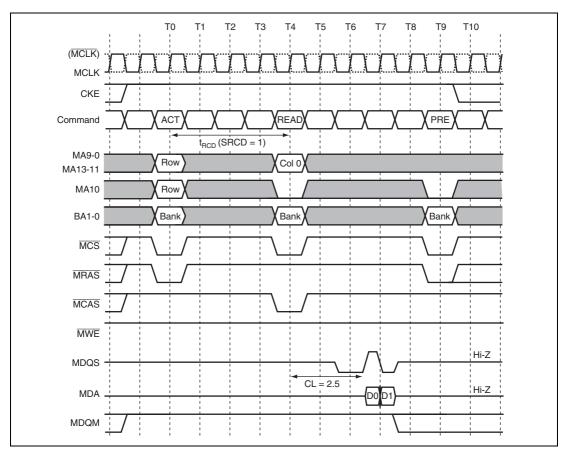

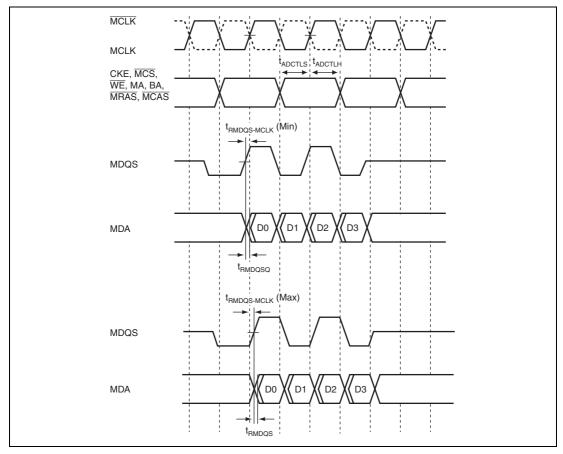

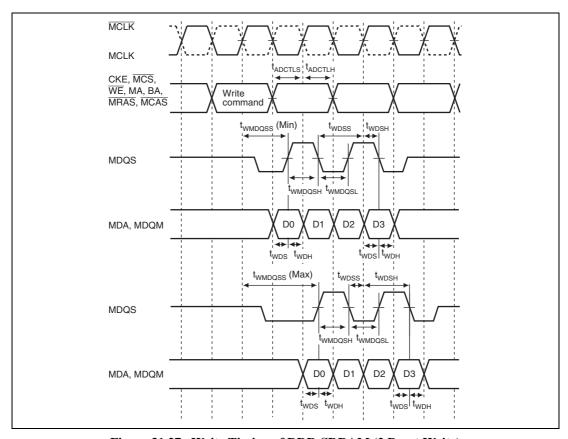

| 12.6  | DDR-S       | DRAM Basic Timing                                                     | 430 |

| 12.7  | Usage Notes |                                                                       |     |

|       | 12.7.1      | Operating Frequency                                                   | 440 |

|       | 12.7.2      | Stopping Clock                                                        | 440 |

|       | 12.7.3      | Using SCR to Issue REFA Command (Outside the Initialization Sequence) | 440 |

|       | 12.7.4      | Timing of Connected SDRAM                                             | 440 |

|       | 12.7.5      | Setting Auto-Refresh Interval                                         | 441 |

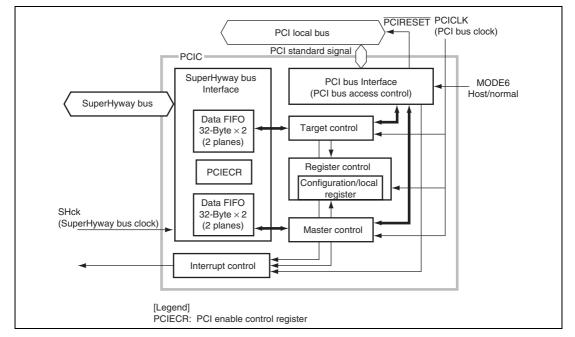

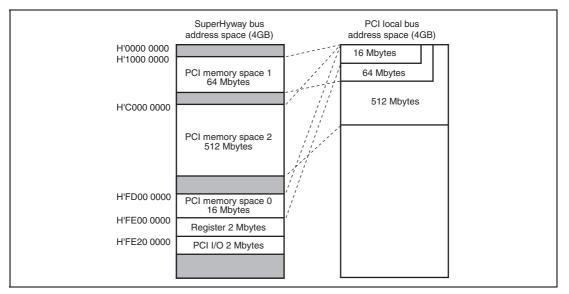

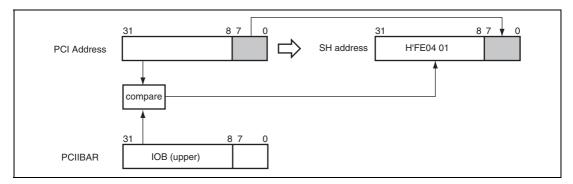

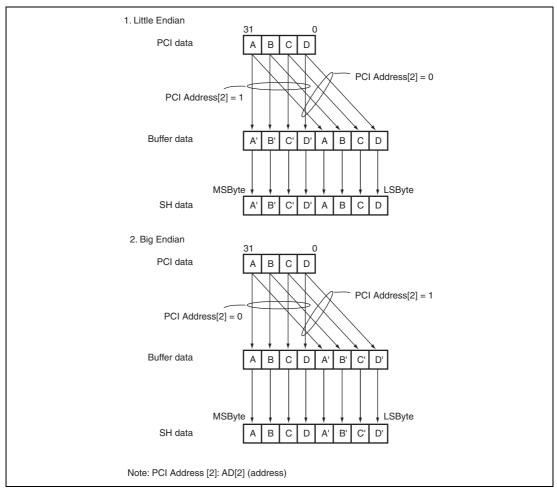

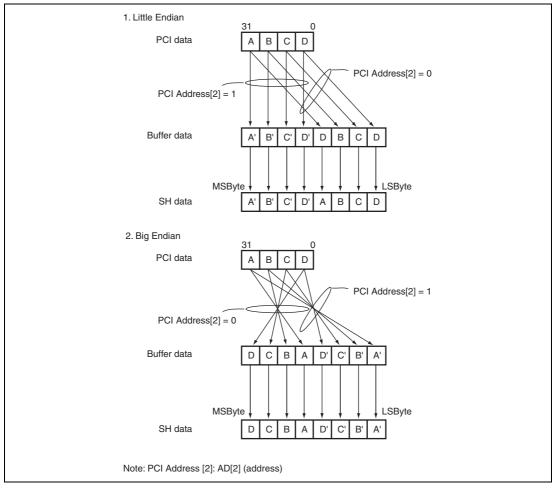

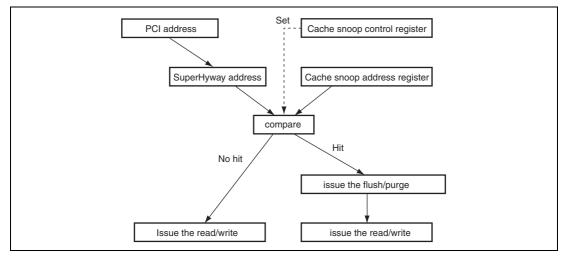

| Secti | on 13       | PCI Controller (PCIC)                                                 | 443 |

| 13.1  | Feature     | ·s                                                                    | 443 |

| 13.2  | Input/C     | Output Pins                                                           | 446 |

| 13.3  | Registe     | r Descriptions                                                        | 449 |

|       | 13.3.1      | PCIC Enable Control Register (PCIECR)                                 | 455 |

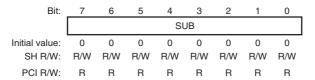

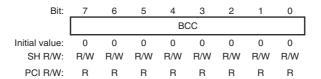

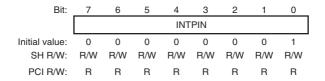

|       | 13.3.2      | Configuration Registers                                               | 456 |

|       | 13.3.3      | Local Register                                                        | 481 |

| 13.4  |             | on                                                                    |     |

|       | 13.4.1      | Supported PCI Commands                                                | 522 |

|       | 13.4.2      | PCIC Initialization                                                   | 523 |

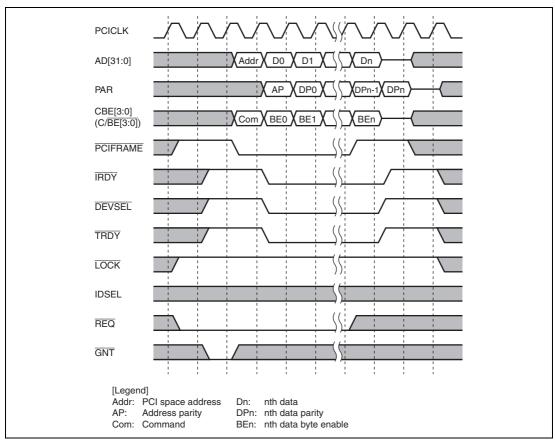

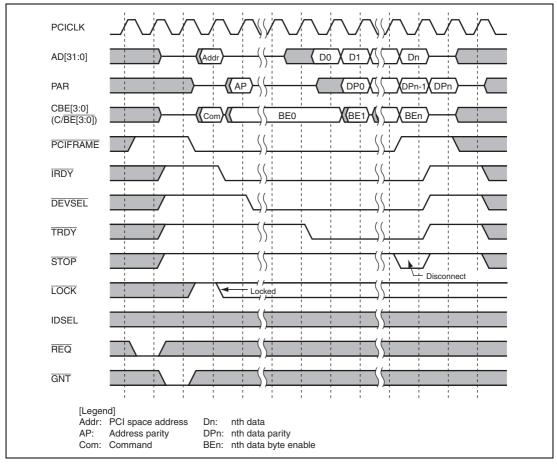

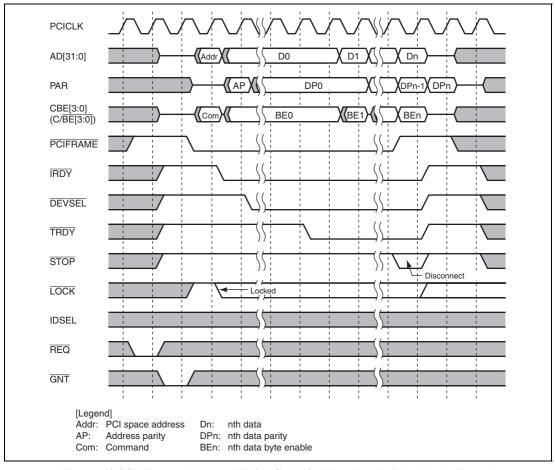

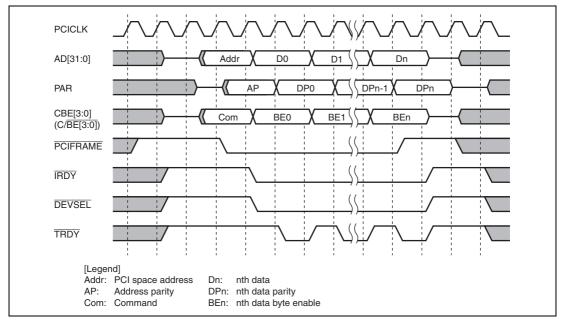

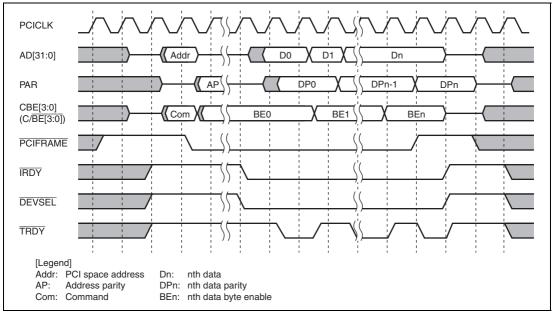

|       | 13 4 3      | Master Access                                                         | 524 |

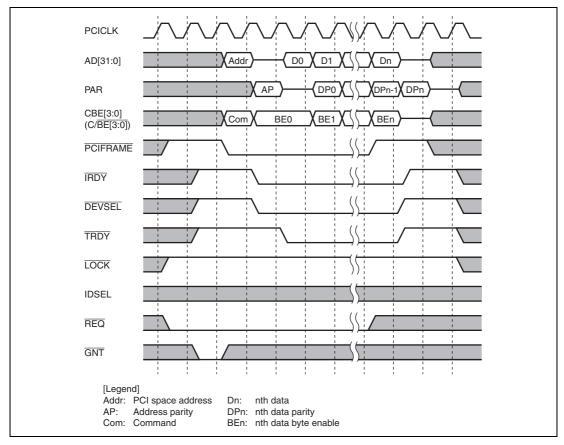

|      | 13.4.4  | Target Access                                                       | 532 |

|------|---------|---------------------------------------------------------------------|-----|

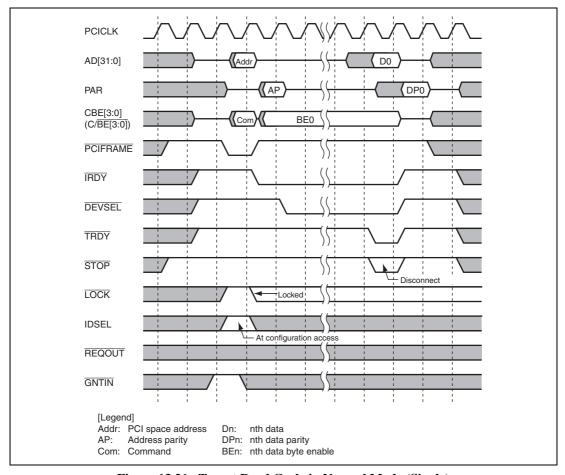

|      | 13.4.5  | Host Bus Bridge Mode                                                | 541 |

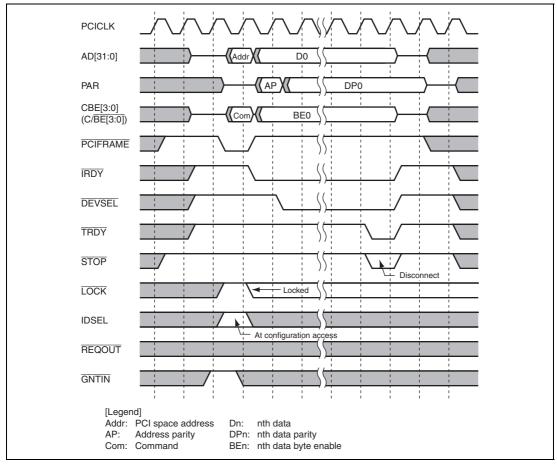

|      | 13.4.6  | Normal mode                                                         | 544 |

|      | 13.4.7  | Power Management                                                    | 544 |

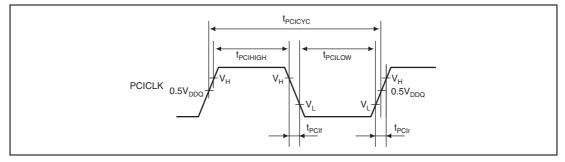

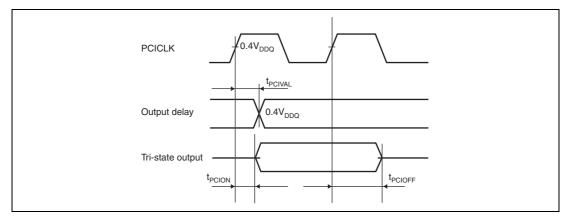

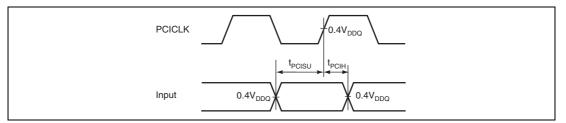

|      | 13.4.8  | PCI Local Bus Basic Interface                                       | 545 |

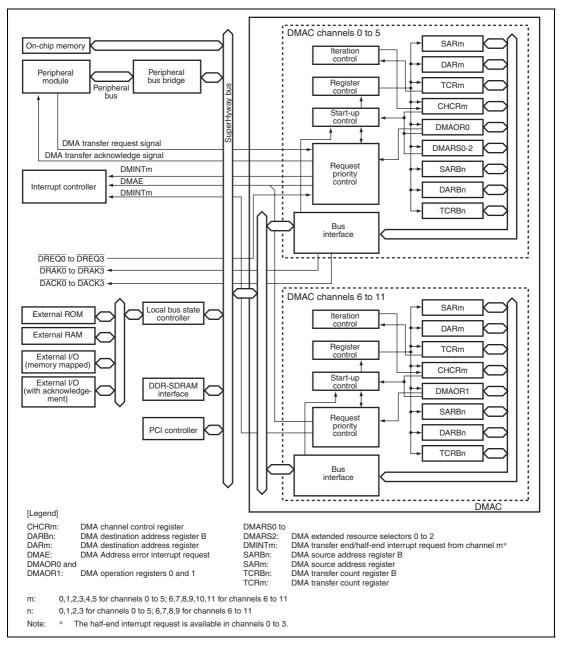

| Sect | ion 14  | Direct Memory Access Controller (DMAC)                              | 557 |

| 14.1 | Feature | es                                                                  | 557 |

| 14.2 | Input/C | Output Pins                                                         | 559 |

| 14.3 | Registe | er Descriptions                                                     | 561 |

|      | 14.3.1  | DMA Source Address Registers 0 to 11 (SAR0 to SAR11)                | 567 |

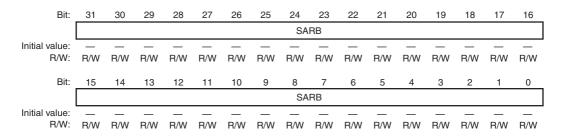

|      | 14.3.2  | DMA Source Address Registers B0 to B3, B6 to B9                     |     |

|      |         | (SARB0 to SARB3, SARB6 to SARB9)                                    | 568 |

|      | 14.3.3  | DMA Destination Address Registers 0 to 11 (DAR0 to DAR11)           | 568 |

|      | 14.3.4  | DMA Destination Address Registers B0 to B3, B6 to B9                |     |

|      |         | (DARB0 to DARB3, DARB6 to DARB9)                                    | 569 |

|      | 14.3.5  | DMA Transfer Count Registers 0 to 11 (TCR0 to TCR11)                | 570 |

|      | 14.3.6  | DMA Transfer Count Registers B0 to B3, B6 to B9                     |     |

|      |         | (TCRB0 to TCRB3, TCRB6 to TCRB9)                                    | 571 |

|      | 14.3.7  | DMA Channel Control Registers 0 to 11 (CHCR0 to CHCR11)             | 572 |

|      | 14.3.8  | DMA Operation Register 0, 1 (DMAOR0 and DMAOR1)                     | 581 |

|      | 14.3.9  | DMA Extended Resource Selectors (DMARS0 to DMARS2)                  | 584 |

| 14.4 | Operat  | ion                                                                 | 588 |

|      | 14.4.1  | DMA Transfer Requests                                               | 588 |

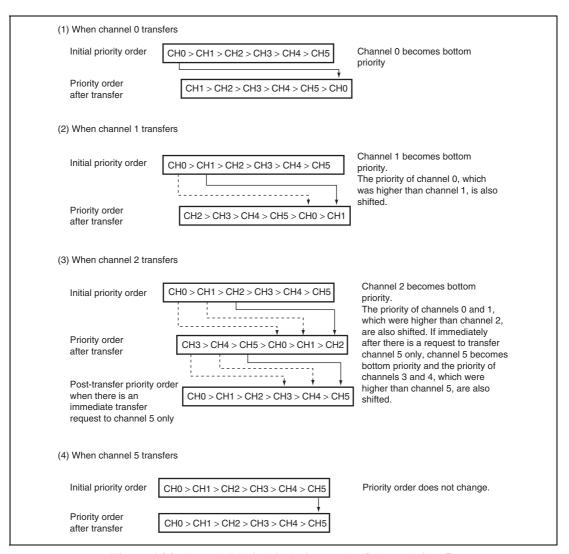

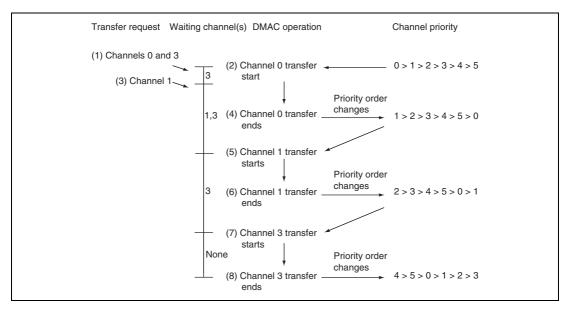

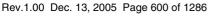

|      | 14.4.2  | Channel Priority                                                    | 592 |

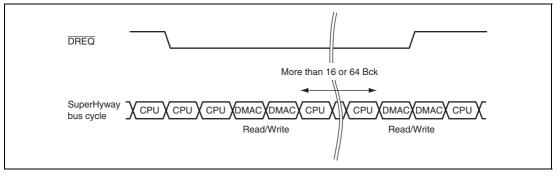

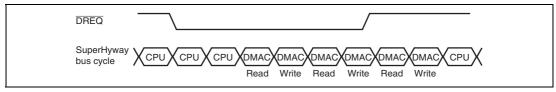

|      | 14.4.3  | DMA Transfer Types                                                  | 595 |

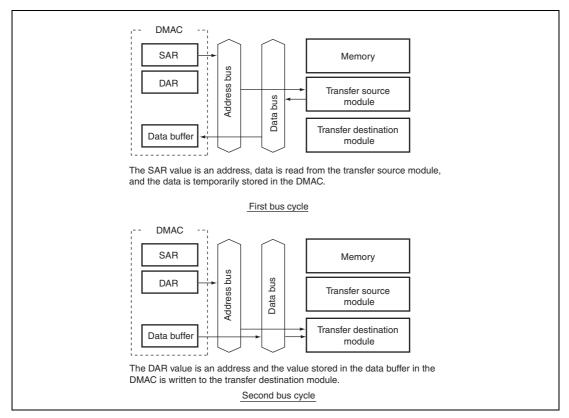

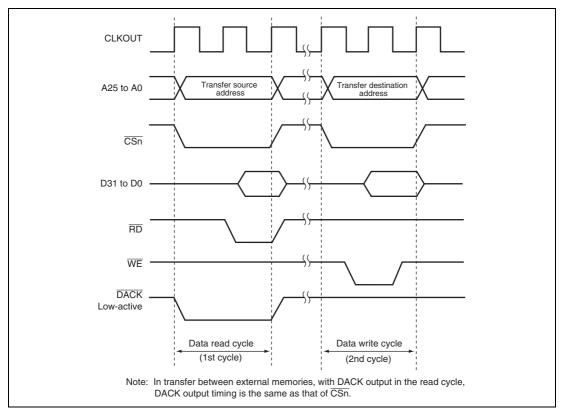

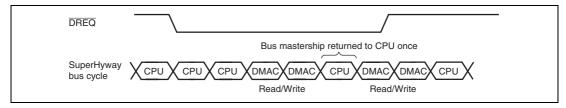

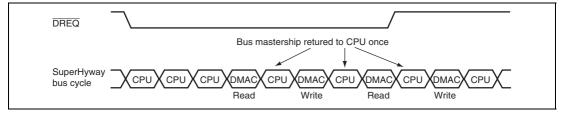

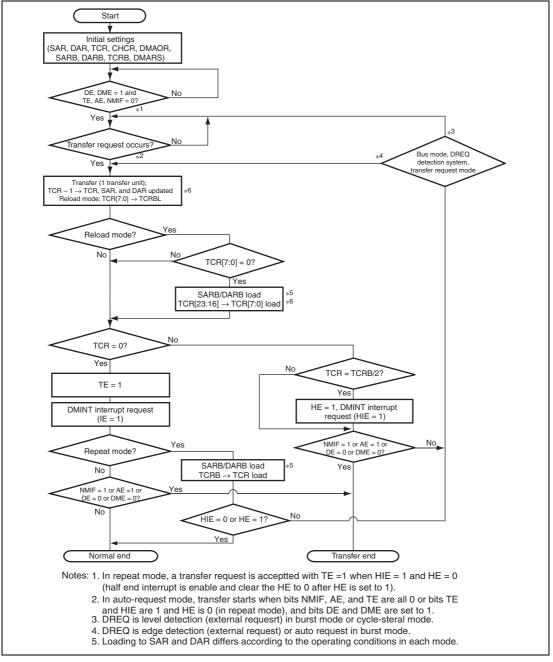

|      | 14.4.4  | DMA Transfer Flow                                                   | 602 |

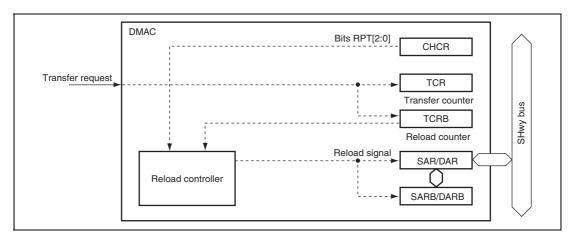

|      | 14.4.5  | Repeat Mode Transfer                                                | 604 |

|      | 14.4.6  | Reload Mode Transfer                                                | 605 |

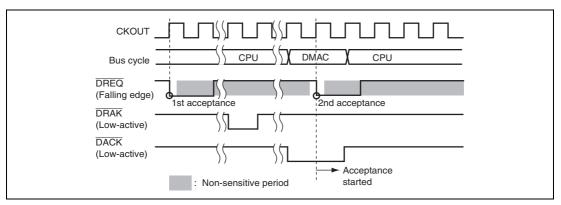

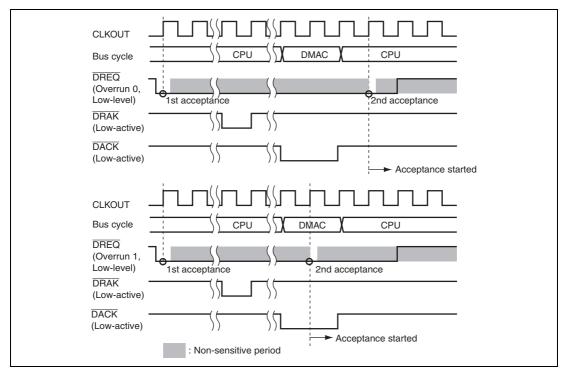

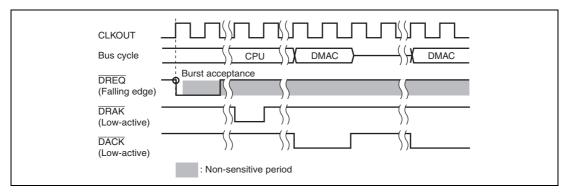

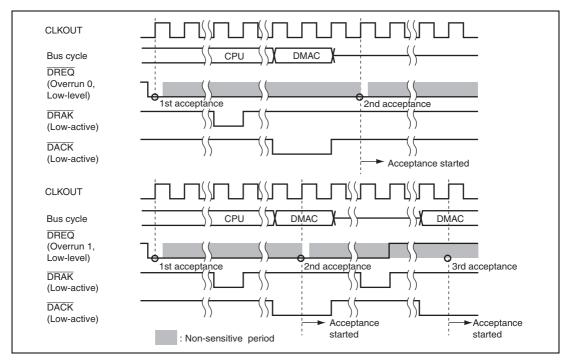

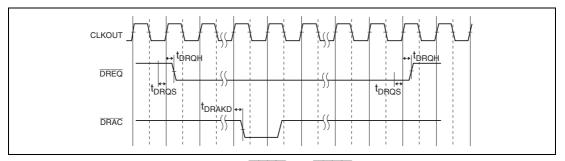

|      | 14.4.7  | DREQ Pin Sampling Timing                                            | 606 |

| 14.5 | Usage   | Notes                                                               | 608 |

|      | 14.5.1  | Module Stop                                                         | 608 |

|      | 14.5.2  | Address Error                                                       | 608 |

|      | 14.5.3  | Notes on Burst Mode Transfer                                        | 608 |

|      |         | DACK output division                                                |     |

|      |         | Clear DMINT Interrupt                                               |     |

|      |         | CS Output Settings and Transfer Size Larger than External Bus Width |     |

|      |         | DACK Assertion and DREO Sampling                                    |     |

| Sect | ion 15                                | Clock Pulse Generator (CPG)                     | 613 |

|------|---------------------------------------|-------------------------------------------------|-----|

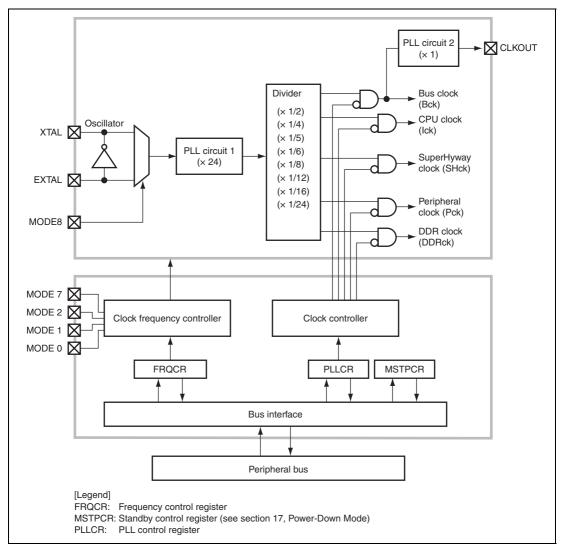

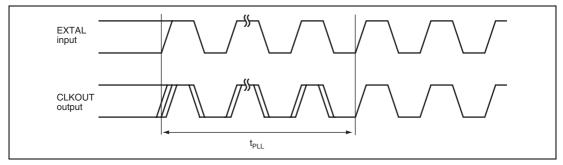

| 15.1 | Feature                               | es                                              | 613 |

| 15.2 | Input/C                               | Output Pins                                     | 616 |

| 15.3 | Clock                                 | Operating Modes                                 | 617 |

| 15.4 | Registe                               | er Descriptions                                 | 618 |

|      | 15.4.1                                | Frequency Control Register (FRQCR)              | 619 |

|      | 15.4.2                                | PLL Control Register (PLLCR)                    | 621 |

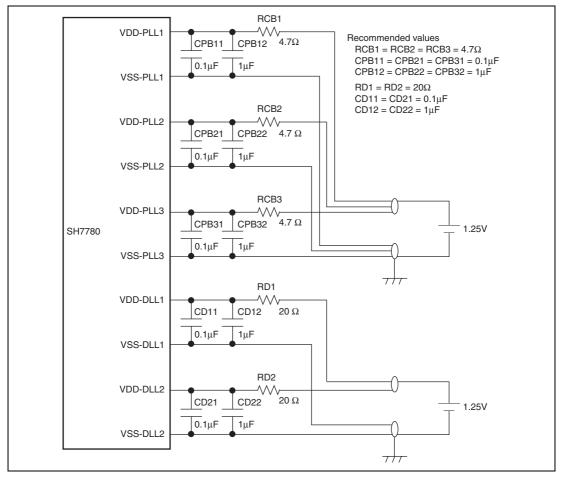

| 15.5 | Notes o                               | on Board Design                                 | 622 |

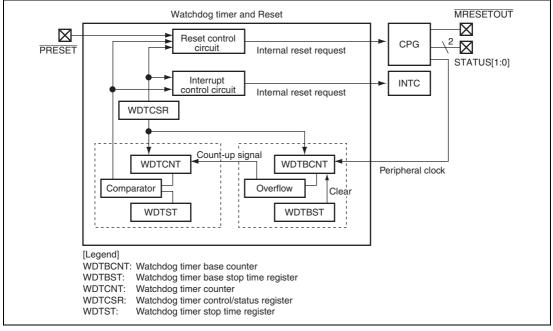

| Sect | ion 16                                | Watchdog Timer and Reset                        | 625 |

| 16.1 |                                       | es                                              |     |

| 16.2 |                                       | Output Pins                                     |     |

| 16.3 |                                       | er Descriptions                                 |     |

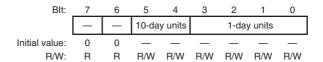

|      | 16.3.1                                | Watchdog Timer Stop Time Register (WDTST)       | 629 |

|      |                                       | Watchdog Timer Control/Status Register (WDTCSR) |     |

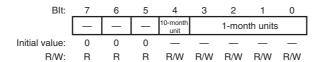

|      |                                       | Watchdog timer Base Stop Time Register (WDTBST) |     |

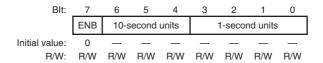

|      | 16.3.4                                | Watchdog Timer Counter (WDTCNT)                 | 632 |

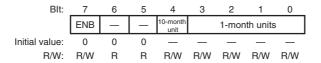

|      |                                       | Watchdog Timer Base Counter (WDTBCNT)           |     |

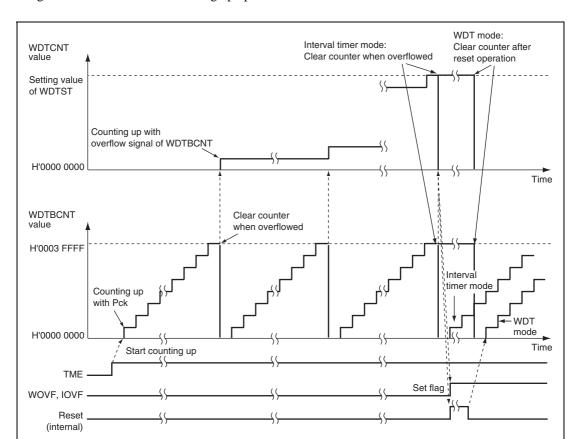

| 16.4 | Operati                               | ion                                             | 633 |

|      | 16.4.1                                | Reset request                                   | 633 |

|      |                                       | Using watchdog timer mode                       |     |

|      |                                       | Using Interval timer mode                       |     |

|      | 16.4.4                                | Time for WDT Overflow                           | 635 |

|      |                                       | Clearing WDT Counter                            |     |

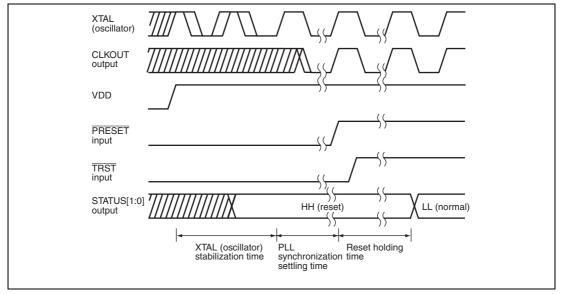

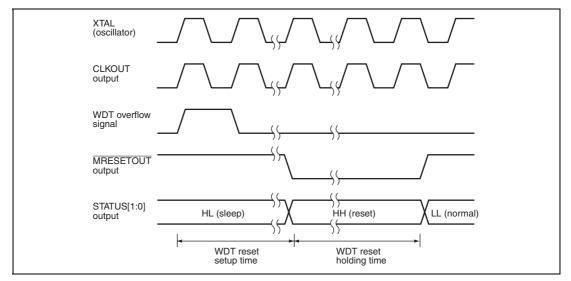

| 16.5 | Status Pin Change Timing during Reset |                                                 |     |

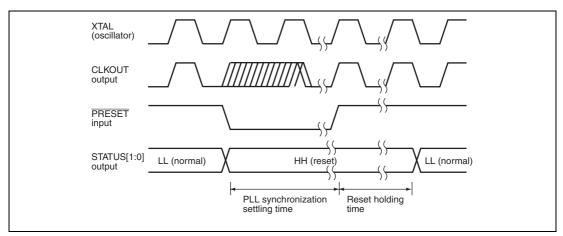

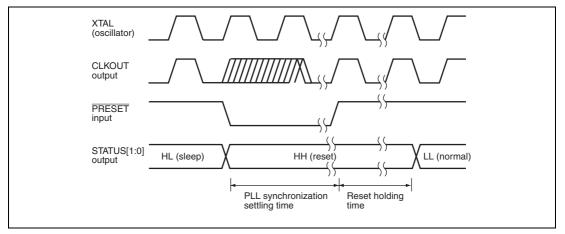

|      |                                       | Power-On Reset by PRESET                        |     |

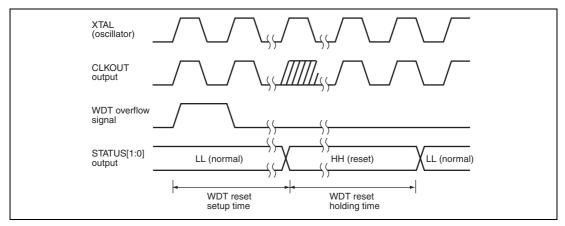

|      |                                       | Power-On Reset by Watchdog Timer Overflow       |     |

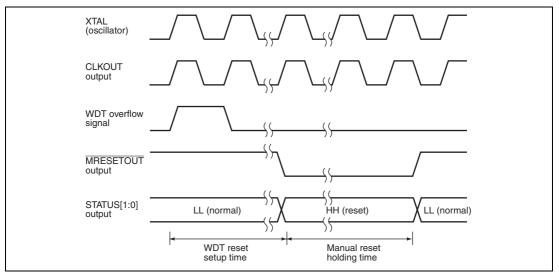

|      |                                       | Manual Reset by Watchdog Timer Overflow         |     |

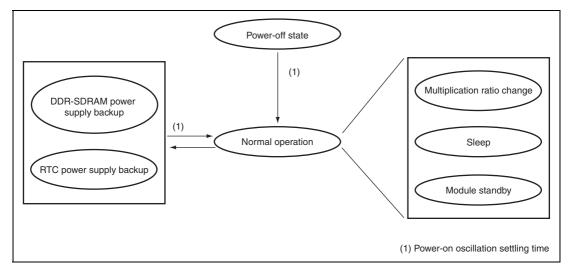

| Sect | ion 17                                | Power-Down Mode                                 | 643 |

| 17.1 | Feature                               | es                                              | 643 |

|      |                                       | Types of Power-Down Modes                       |     |

| 17.2 | Input/C                               | Output Pins                                     | 645 |

| 17.3 |                                       | er Descriptions                                 |     |

|      | _                                     | Standby Control Register (MSTPCR)               |     |

| 17.4 |                                       | Mode                                            |     |

|      |                                       | Transition to Sleep mode                        |     |

|      |                                       | Cancellation of Sleen Mode                      |     |

| 17.5  | Module  | e Standby State                                                | 649 |

|-------|---------|----------------------------------------------------------------|-----|

|       | 17.5.1  | Transition to Module Standby Mode                              | 649 |

|       | 17.5.2  | Cancellation of Module Standby Mode and Resume                 | 649 |

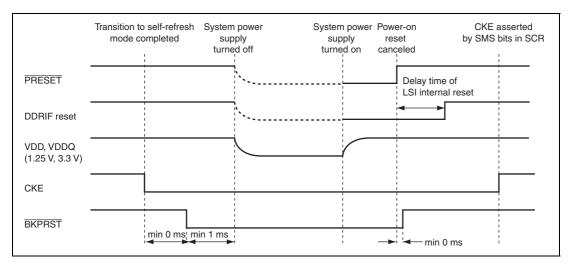

| 17.6  |         | DRAM Power Supply Backup                                       |     |

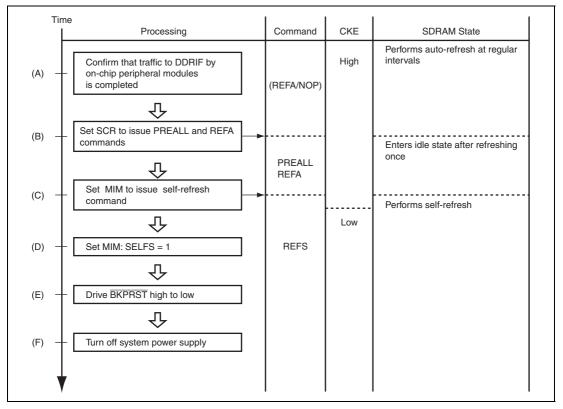

|       | 17.6.1  | Self-Refresh and Initialization                                | 650 |

|       | 17.6.2  | DDR-SDRAM Backup Sequence when Turning Off System Power Supply | 651 |

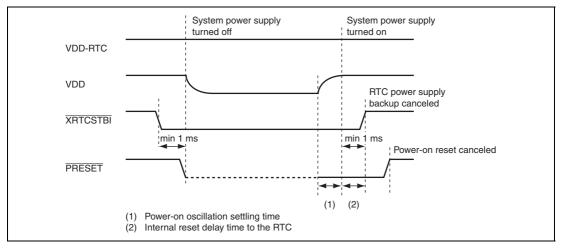

| 17.7  | RTC P   | ower Supply Backup                                             | 653 |

|       | 17.7.1  | Transition to RTC Power Supply Backup                          | 653 |

|       | 17.7.2  | Cancellation of RTC Power Supply Backup                        | 653 |

| 17.8  | Mode 7  | Fransitions                                                    | 655 |

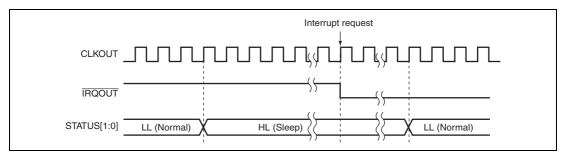

| 17.9  | STATU   | JS Pin Change Timing                                           | 656 |

|       | 17.9.1  | In Reset                                                       | 656 |

|       | 17.9.2  | In Sleep                                                       | 656 |

| Secti | ion 18  | Timer Unit (TMU)                                               | 657 |

| 18.1  | Feature | 28                                                             | 657 |

| 18.2  | Input/C | Output Pins                                                    | 659 |

| 18.3  | Registe | er Descriptions                                                | 660 |

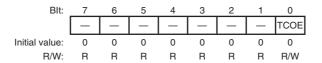

|       | 18.3.1  | Timer Output Control Register (TOCR)                           | 662 |

|       | 18.3.2  |                                                                |     |

|       | 18.3.3  | Timer Constant Register (TCORn) (n = 0 to 5)                   | 665 |

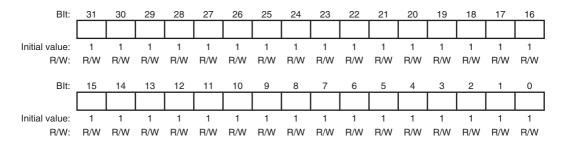

|       | 18.3.4  | Timer Counter (TCNTn) $(n = 0 \text{ to } 5)$                  | 665 |

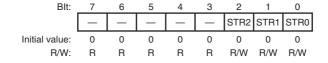

|       | 18.3.5  | Timer Control Registers (TCRn) (n = 0 to 5)                    | 666 |

|       | 18.3.6  | Input Capture Register 2 (TCPR2)                               | 668 |

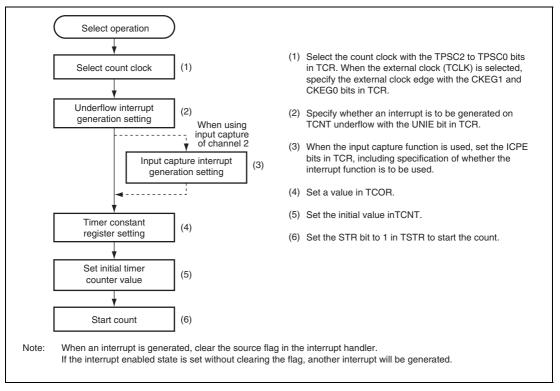

| 18.4  | Operat  | on                                                             | 669 |

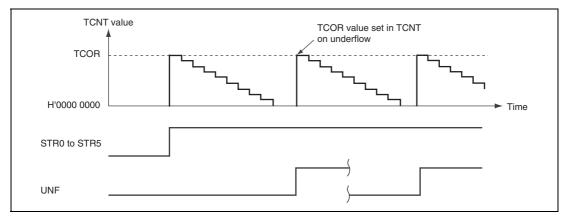

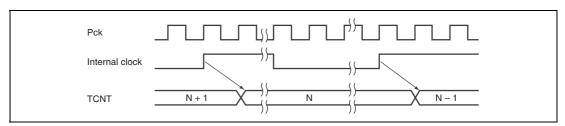

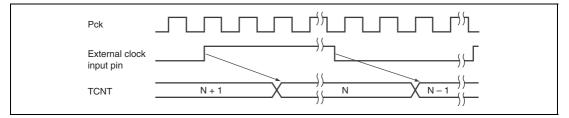

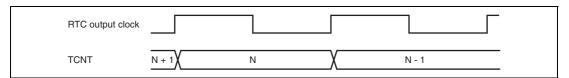

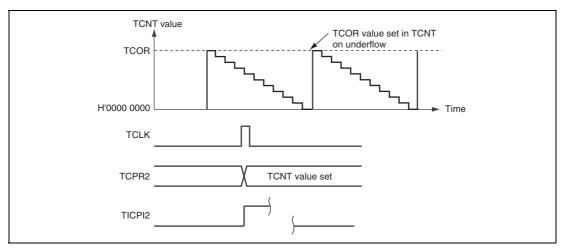

|       | 18.4.1  | Counter Operation                                              | 669 |

|       | 18.4.2  | Input Capture Function                                         | 673 |

| 18.5  | Interru | pts                                                            | 674 |

| 18.6  | Usage   | Notes                                                          | 675 |

|       | 18.6.1  | Register Writes                                                | 675 |

|       | 18.6.2  | Reading from TCNT                                              | 675 |

|       | 18.6.3  | Reset RTC Frequency Divider Circuit                            | 675 |

|       | 18.6.4  | External Clock Frequency                                       | 675 |

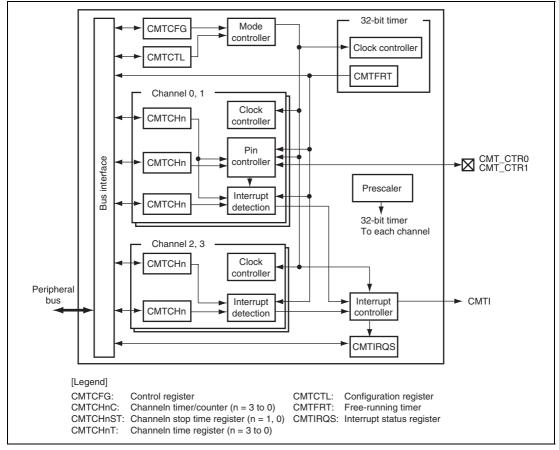

| Secti | ion 19  | Compare Match Timer (CMT)                                      | 677 |

| 19.1  |         | 28                                                             |     |

| 19.2  | Input/C | Output Pins                                                    | 679 |

| 19.3  |         | r Descriptions                                                 |     |

|       | _       | Configuration Register (CMTCFG)                                |     |

|       |         | Free-Running Timer (CMTFRT)                                    |     |

|       | 19.3.3  | Control Register (CMTCTL)                                  | 684 |

|-------|---------|------------------------------------------------------------|-----|

|       | 19.3.4  | Interrupt Status Register (CMTIRQS)                        | 688 |

|       | 19.3.5  | Channels 0 to 3 Time Registers (CMTCH0T to CMTCH3T)        | 689 |

|       | 19.3.6  | Channels 0 to 1 Stop Time Registers (CMTCH0ST to CMTCH1ST) | 689 |

|       | 19.3.7  | Channels 0 to 3 Counters (CMTCH0C to CMTCH3C)              | 690 |

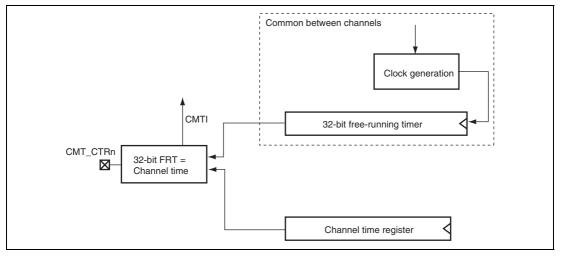

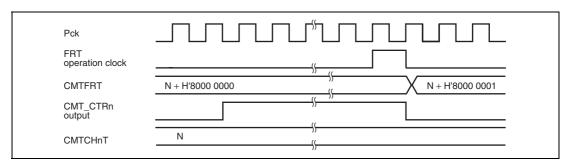

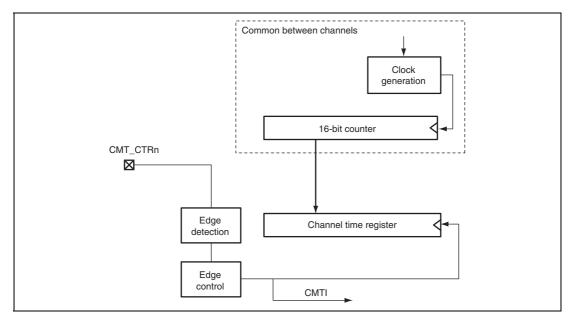

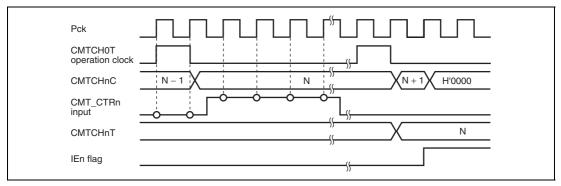

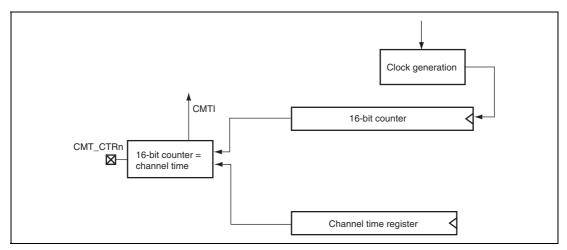

| 19.4  | Operati | on                                                         | 691 |

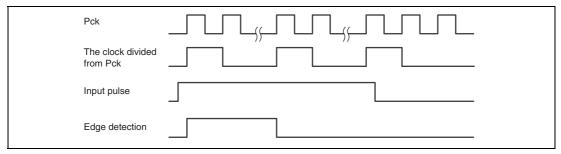

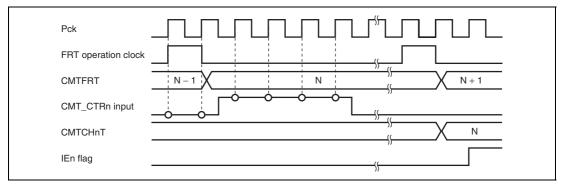

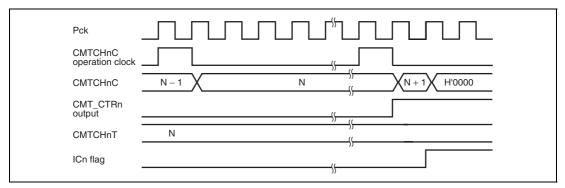

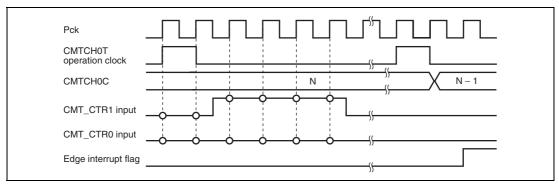

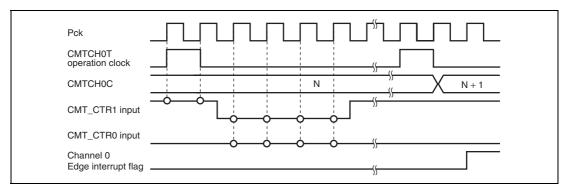

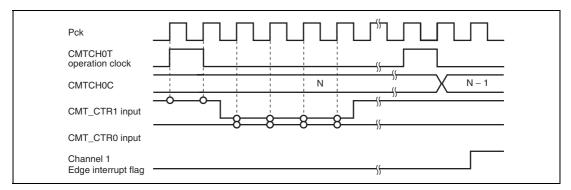

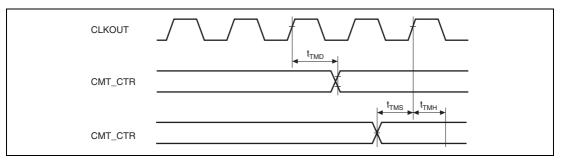

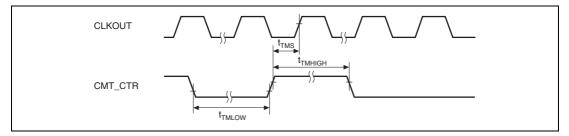

|       | 19.4.1  | Edge Detection                                             | 691 |

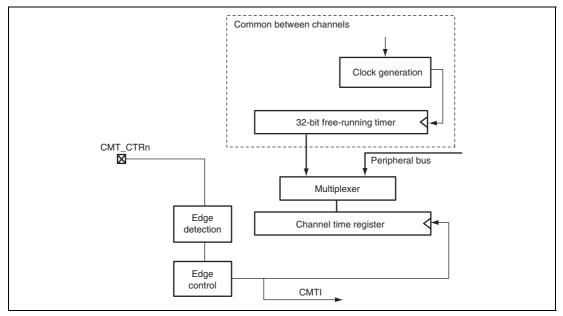

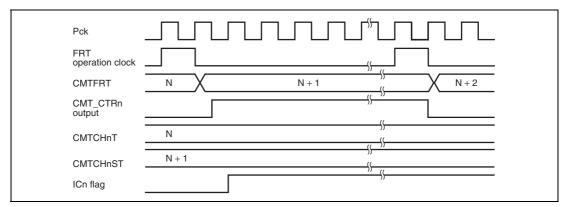

|       | 19.4.2  | 32-Bit Timer: Input Capture                                | 692 |

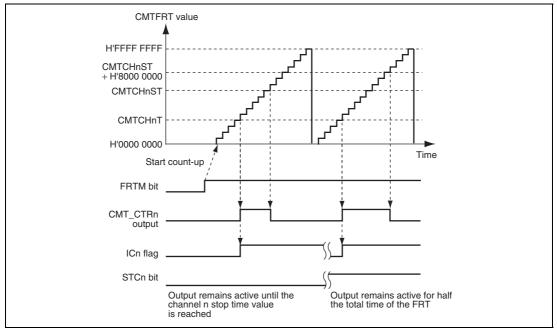

|       | 19.4.3  | 32-Bit Timer: Output Compare                               | 693 |

|       | 19.4.4  | 16-Bit Timer: Input Capture                                | 697 |

|       | 19.4.5  | 16-Bit Timer: Output Compare                               | 699 |

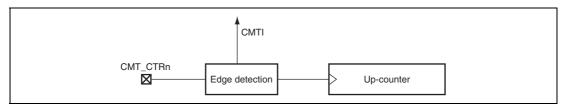

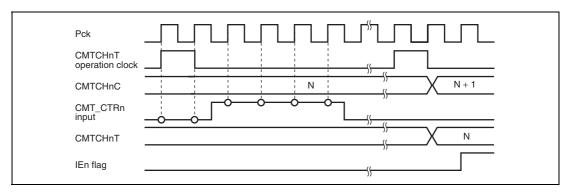

|       | 19.4.6  | Counter: Up-counter                                        | 701 |

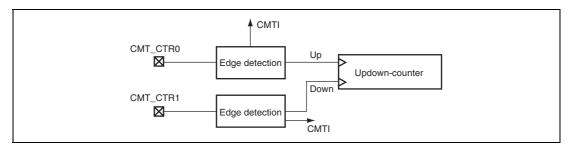

|       | 19.4.7  | Counter: Updown-counter                                    | 703 |

|       | 19.4.8  | Counter: Rotary Switch Operation of Updown-counter         | 705 |

|       | 19.4.9  | Interrupts                                                 | 706 |

|       |         |                                                            |     |

| Secti | on 20   | Realtime Clock (RTC)                                       | 707 |

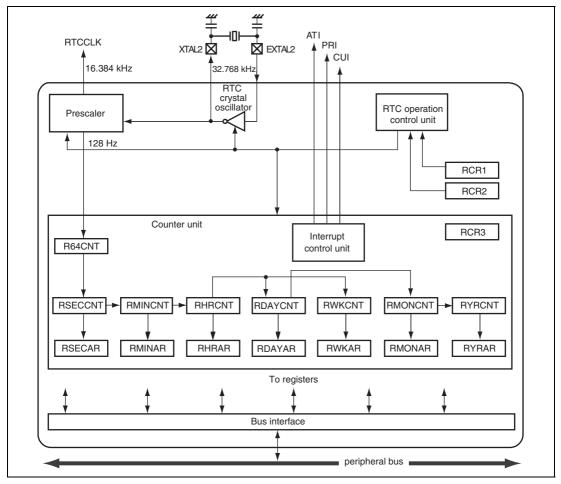

| 20.1  | Feature | S                                                          | 707 |

|       | 20.1.1  | Block Diagram                                              | 708 |

| 20.2  | Input/C | Output Pins                                                | 709 |

| 20.3  | Registe | er Descriptions                                            | 710 |

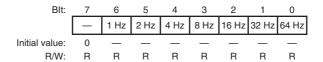

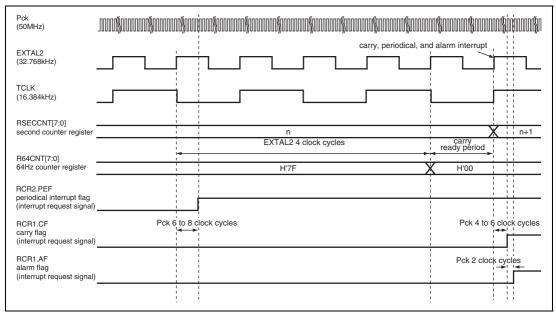

|       | 20.3.1  | 64 Hz Counter (R64CNT)                                     | 712 |

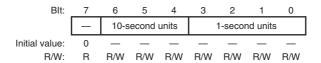

|       | 20.3.2  | Second Counter (RSECCNT)                                   | 712 |

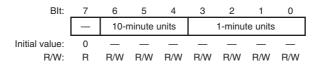

|       | 20.3.3  | Minute Counter (RMINCNT)                                   | 713 |

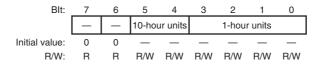

|       | 20.3.4  | Hour Counter (RHRCNT)                                      | 713 |

|       | 20.3.5  | Day-of-Week Counter (RWKCNT)                               | 714 |

|       | 20.3.6  | Day Counter (RDAYCNT)                                      | 715 |

|       | 20.3.7  | Month Counter (RMONCNT)                                    | 716 |

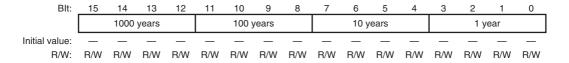

|       | 20.3.8  | Year Counter (RYRCNT)                                      | 716 |

|       | 20.3.9  | Second Alarm Register (RSECAR)                             | 717 |

|       | 20.3.10 | Minute Alarm Register (RMINAR)                             | 717 |

|       | 20.3.11 | Hour Alarm Register (RHRAR)                                | 718 |

|       | 20.3.12 | 2 Day-of-Week Alarm Register (RWKAR)                       | 718 |

|       | 20.3.13 | Day Alarm Register (RDAYAR)                                | 719 |

|       | 20.3.14 | Month Alarm Register (RMONAR)                              | 720 |

|       | 20.3.15 | Year-Alarm Register (RYRAR)                                | 720 |

|       | 20.3.16 | RTC Control Register 1 (RCR1)                              | 721 |

|       | 20.3.17 | RTC Control Register 2 (RCR2)                              | 723 |

|       | 20 3 18 | RTC Control Register (RCR3)                                | 726 |

| 20.4 | Operat    | ion                                             | 727 |

|------|-----------|-------------------------------------------------|-----|

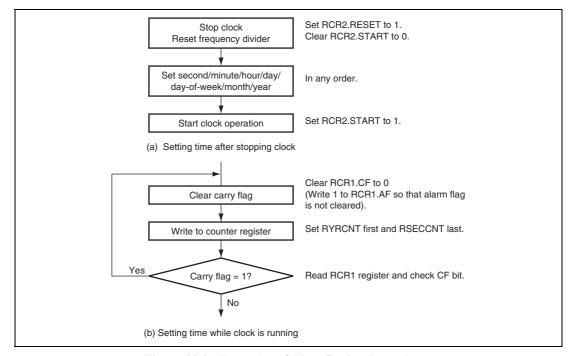

|      | 20.4.1    | Time Setting Procedures                         | 727 |

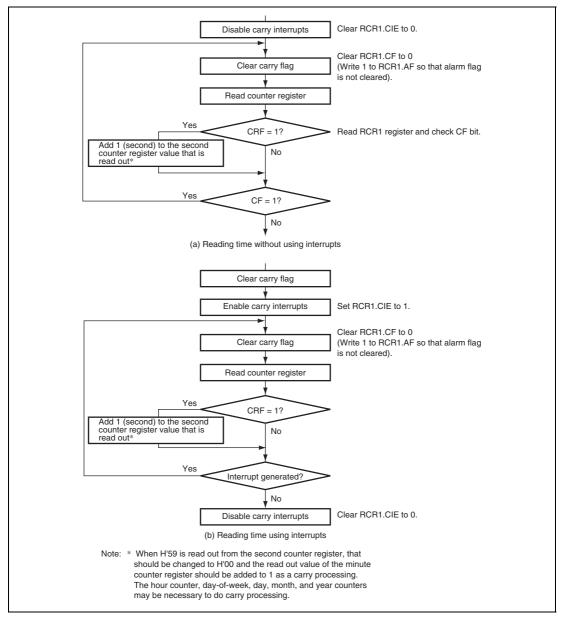

|      | 20.4.2    | Time Reading Procedures                         | 728 |

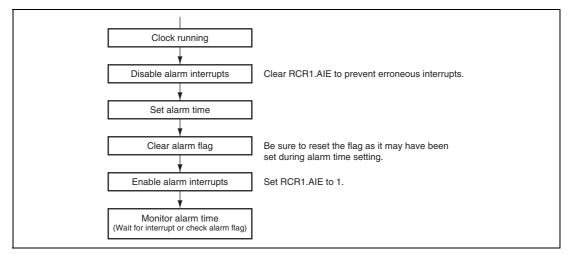

|      | 20.4.3    | Alarm Function                                  | 729 |

| 20.5 | Interru   | pts                                             | 730 |

| 20.6 | Usage     | Notes                                           | 730 |

|      | 20.6.1    | Register Initialization                         | 730 |

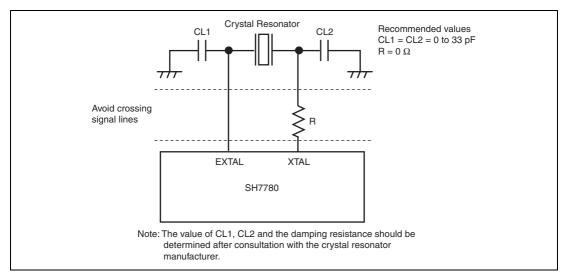

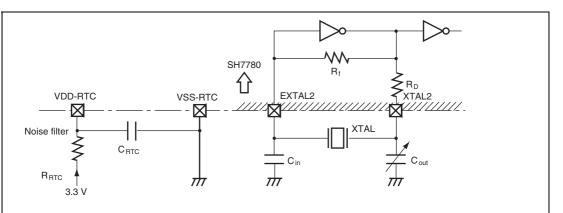

|      | 20.6.2    | Crystal Oscillator Circuit                      | 730 |

|      | 20.6.3    | Interrupt source and request generating order   | 732 |

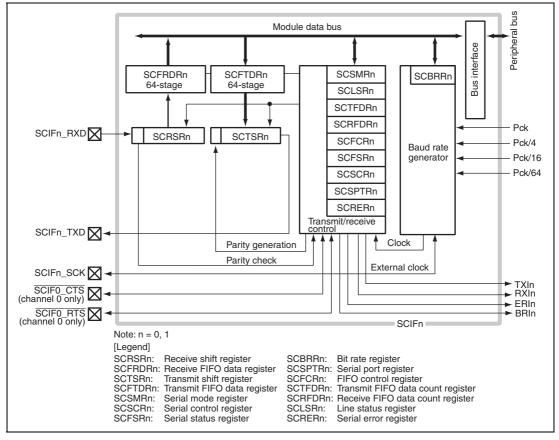

| Sect | ion 21    | Serial Communication Interface with FIFO (SCIF) | 733 |

| 21.1 | Feature   | es                                              |     |

| 21.2 | Input/C   | Output Pins                                     | 739 |

| 21.3 |           | er Descriptions                                 |     |

|      | 21.3.1    | Receive Shift Register (SCRSR)                  | 742 |

|      | 21.3.2    | Receive FIFO Data Register (SCFRDR)             | 742 |

|      | 21.3.3    | Transmit Shift Register (SCTSR)                 | 743 |

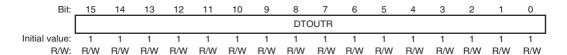

|      | 21.3.4    | Transmit FIFO Data Register (SCFTDR)            | 743 |

|      | 21.3.5    | Serial Mode Register (SCSMR)                    | 744 |

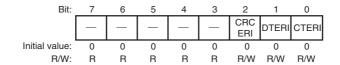

|      | 21.3.6    | Serial Control Register (SCSCR)                 | 747 |

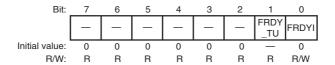

|      | 21.3.7    | Serial Status Register n (SCFSR)                | 751 |

|      | 21.3.8    | Bit Rate Register n (SCBRR)                     | 758 |

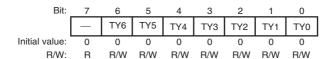

|      | 21.3.9    | FIFO Control Register n (SCFCR)                 | 759 |

|      | 21.3.10   | Transmit FIFO Data Count Register n (SCTFDR)    | 762 |

|      | 21.3.11   | 1 Receive FIFO Data Count Register n (SCRFDR)   | 763 |

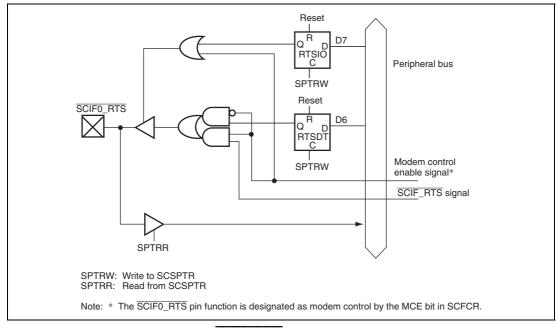

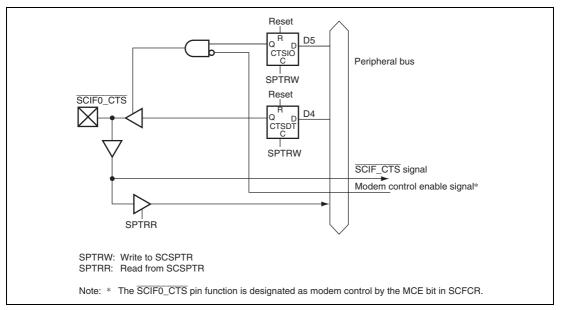

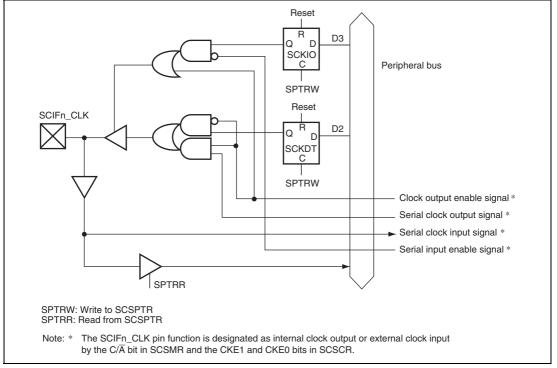

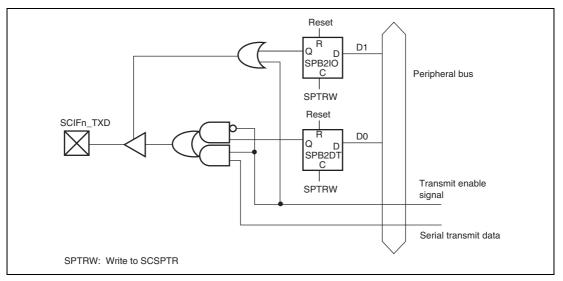

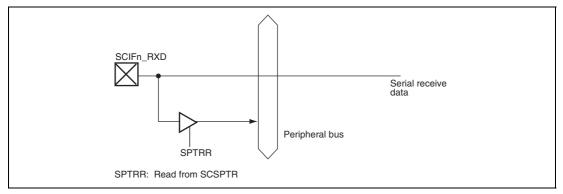

|      | 21.3.12   | 2 Serial Port Register n (SCSPTR)               | 764 |

|      | 21.3.13   | 3 Line Status Register n (SCLSR)                | 767 |

|      | 21.3.14   | 4 Serial Error Register n (SCRER)               | 768 |

| 21.4 | Operation |                                                 |     |

|      | 21.4.1    | Overview                                        | 769 |

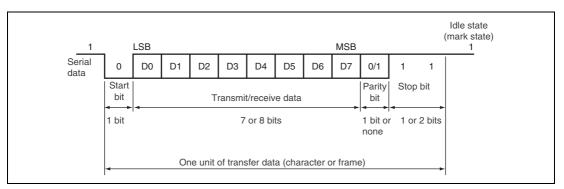

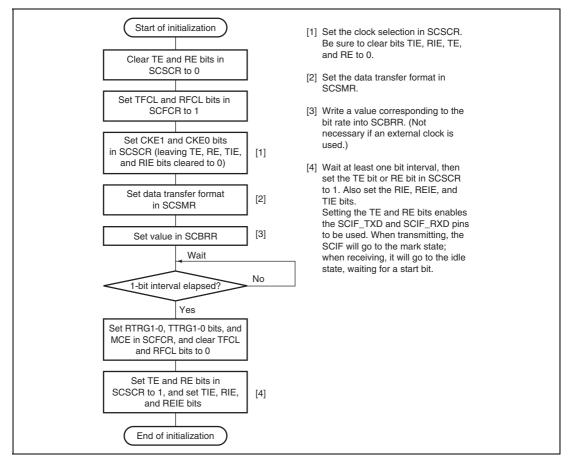

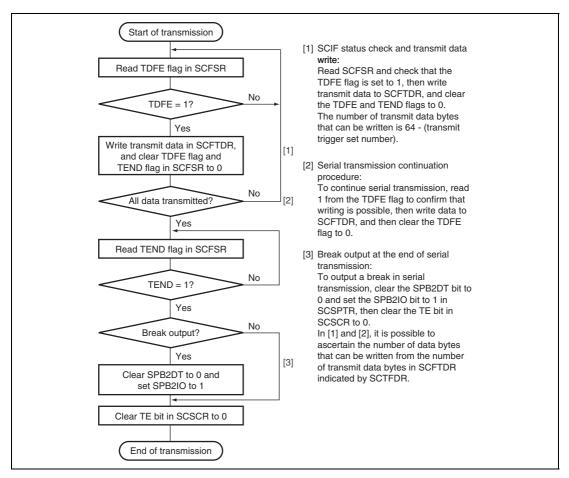

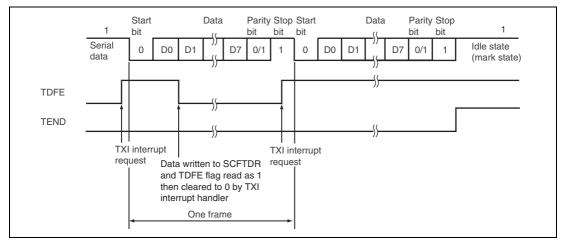

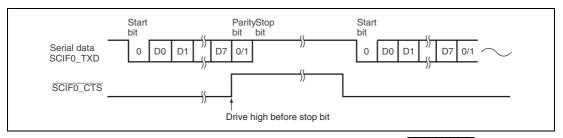

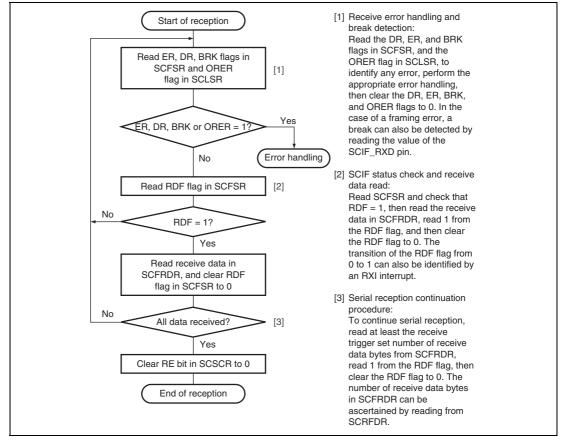

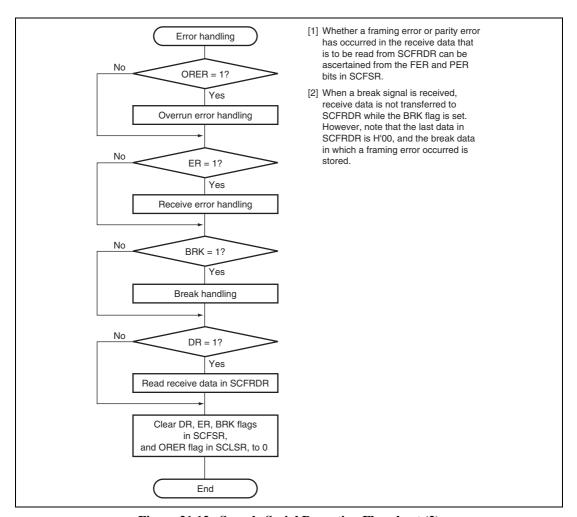

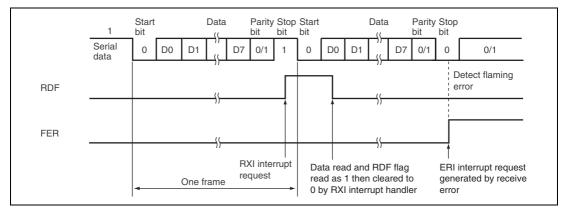

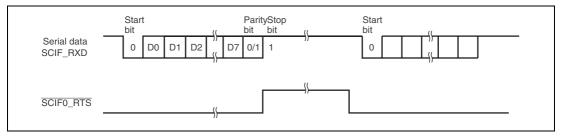

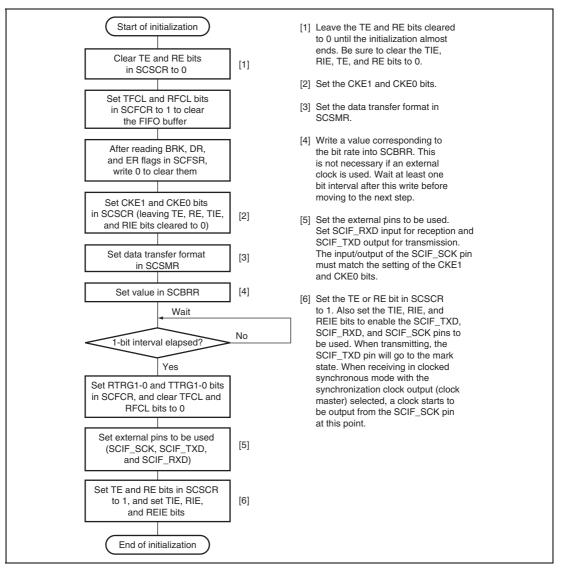

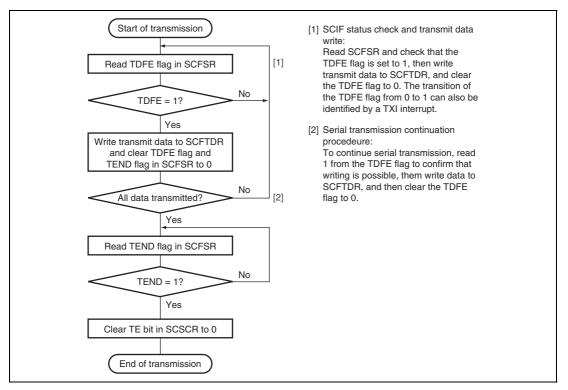

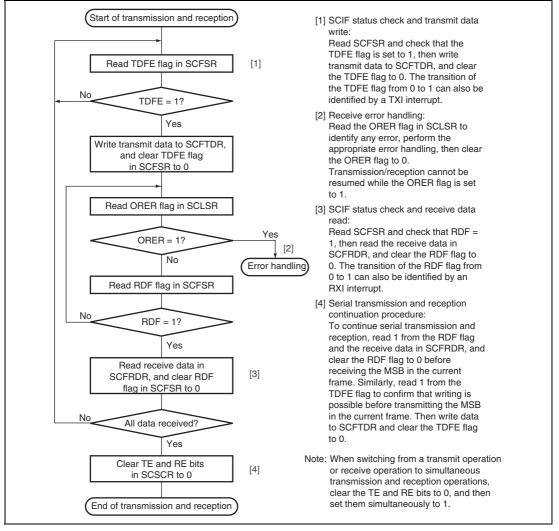

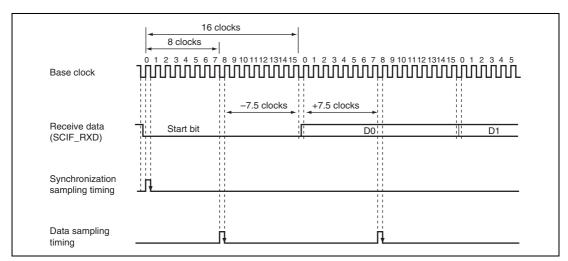

|      | 21.4.2    | Operation in Asynchronous Mode                  | 772 |

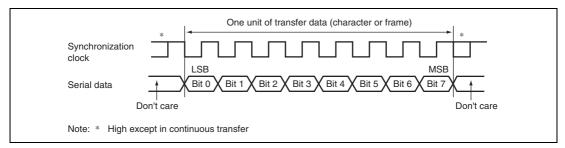

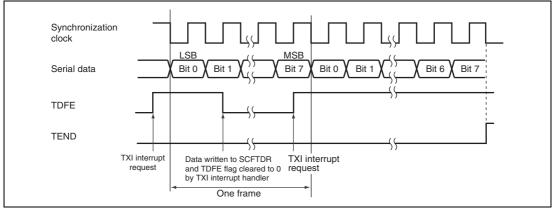

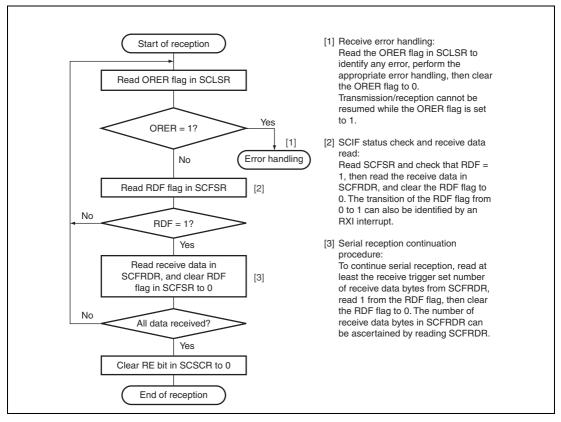

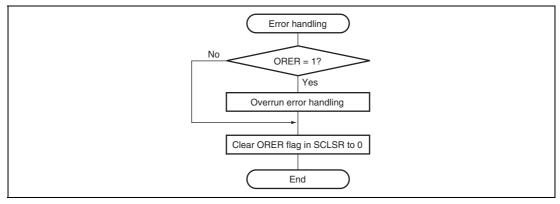

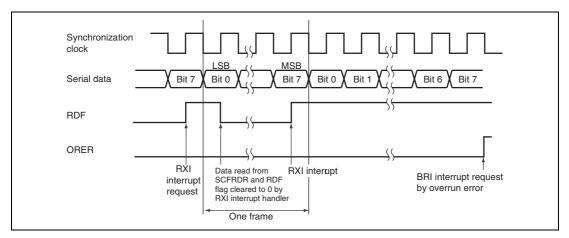

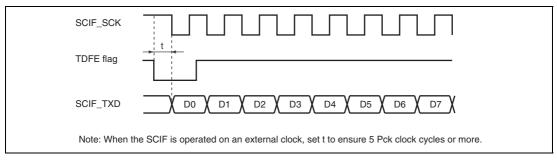

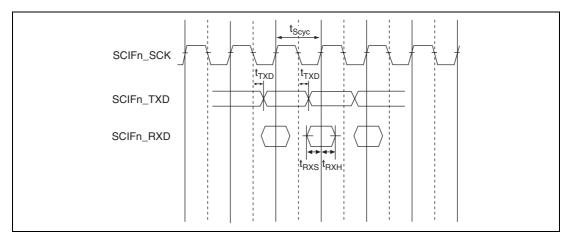

|      | 21.4.3    | Operation in Clocked Synchronous Mode           | 783 |

| 21.5 | SCIF I    | nterrupt Sources and the DMAC                   | 792 |

| 21.6 | Usage     | Notes                                           | 794 |

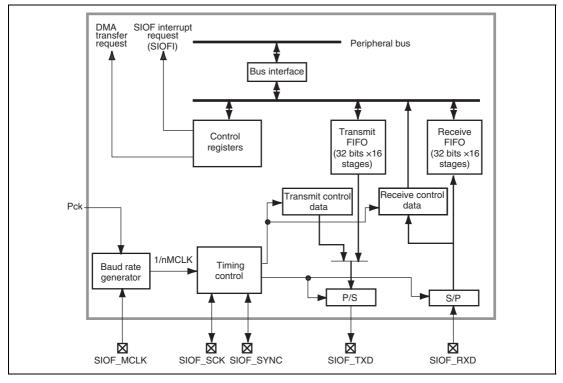

| Sect | ion 22    | Serial I/O with FIFO (SIOF)                     | 797 |

| 22.1 |           | es                                              |     |

| 22.2 | Input/C   | Output Pins                                     | 799 |

| 22.3 | Registe   | er Descriptions                                 | 800 |

|      | _         | Mode Register (SIMDR)                           |     |

|          | 22.3.2  | Clock Select Register (SISCR)           | 804  |

|----------|---------|-----------------------------------------|------|

|          | 22.3.3  | Control Register (SICTR)                | 806  |

|          | 22.3.4  | Transmit Data Register (SITDR)          | 809  |

|          | 22.3.5  | Receive Data Register (SIRDR)           | 810  |

|          | 22.3.6  | Transmit Control Data Register (SITCR)  | 811  |

|          | 22.3.7  | Receive Control Data Register (SIRCR)   | 812  |

|          | 22.3.8  | Status Register (SISTR)                 | 813  |

|          | 22.3.9  | Interrupt Enable Register (SIIER)       | 819  |

|          | 22.3.10 | FIFO Control Register (SIFCTR)          | 821  |

|          | 22.3.11 | Transmit Data Assign Register (SITDAR)  | 823  |

|          | 22.3.12 | Receive Data Assign Register (SIRDAR)   | 824  |

|          | 22.3.13 | S Control Data Assign Register (SICDAR) | 825  |

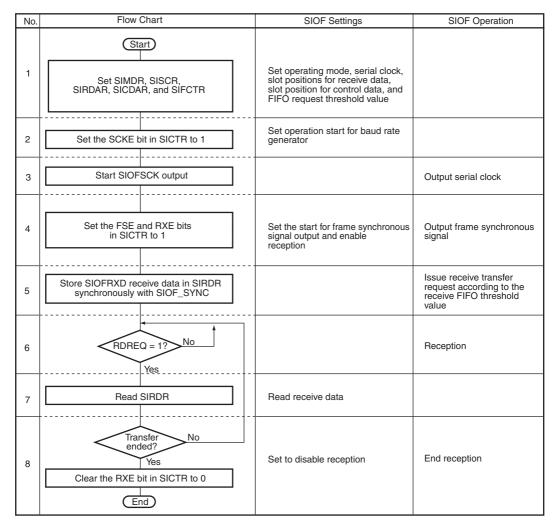

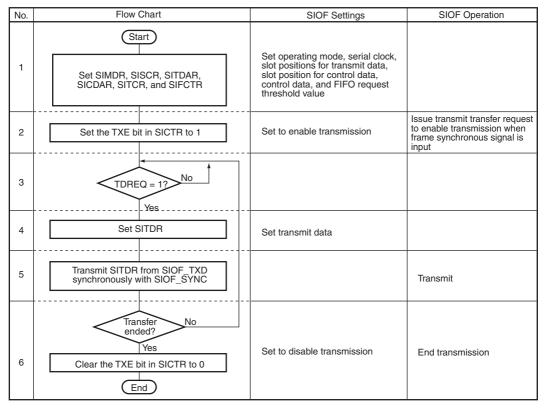

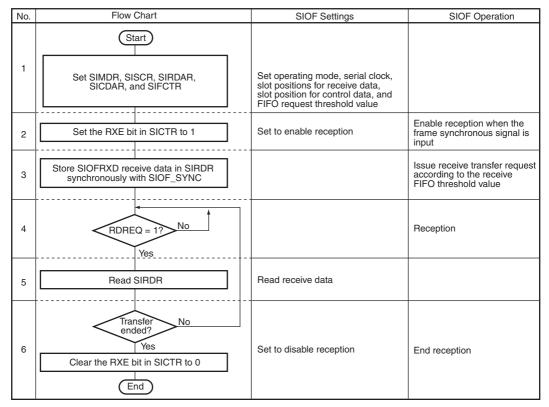

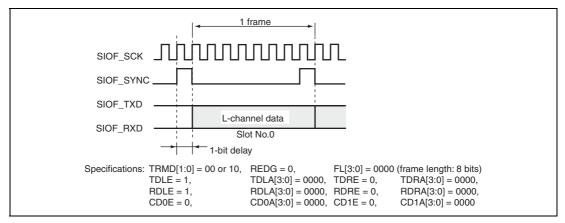

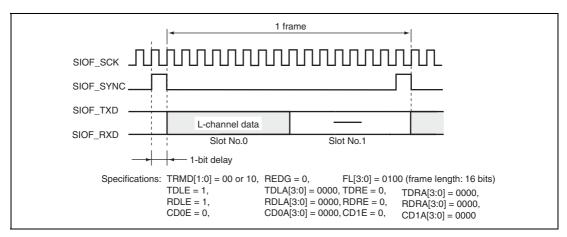

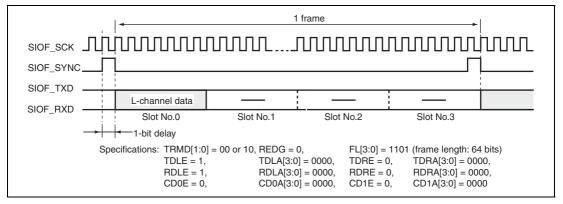

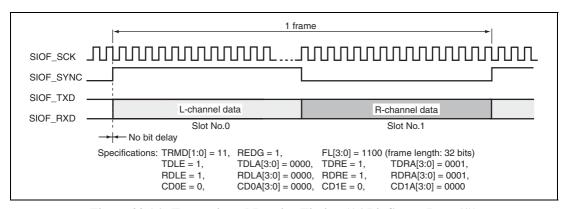

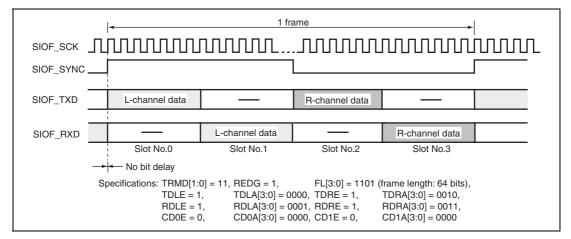

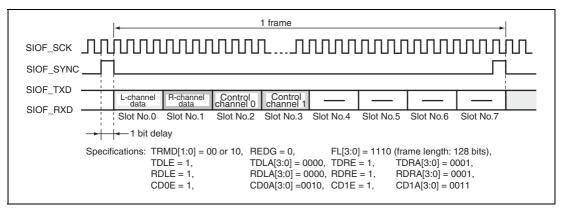

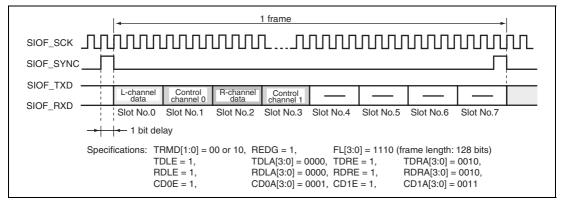

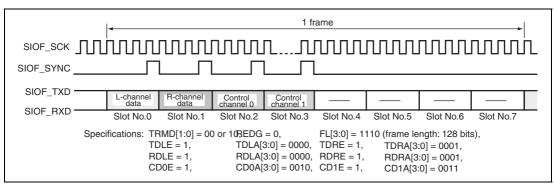

| 22.4     | Operati | ion                                     | 827  |

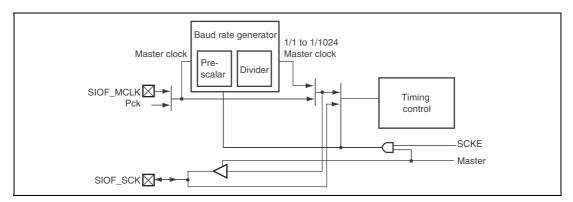

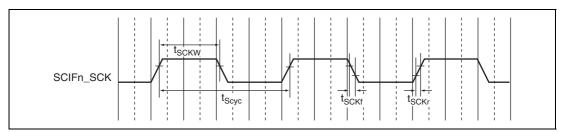

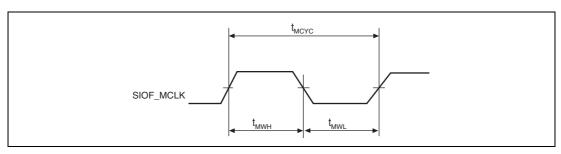

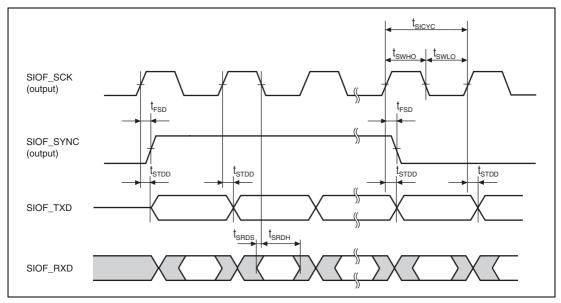

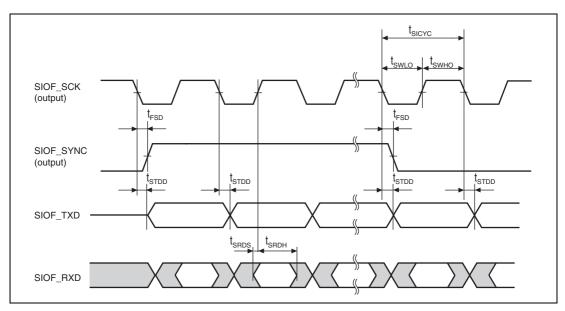

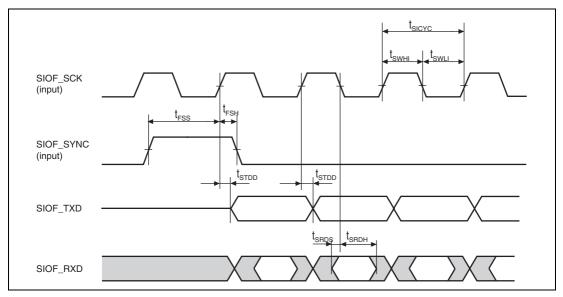

|          | 22.4.1  | Serial Clocks                           | 827  |

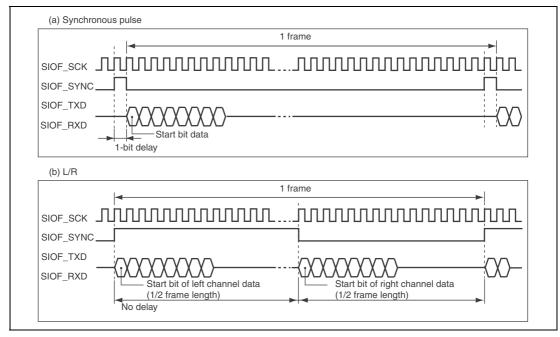

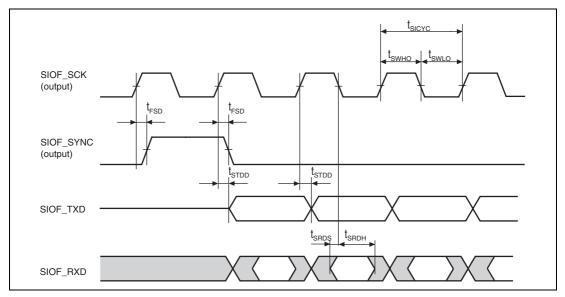

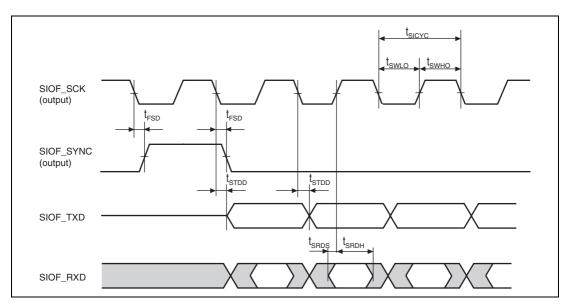

|          | 22.4.2  | Serial Timing                           | 829  |

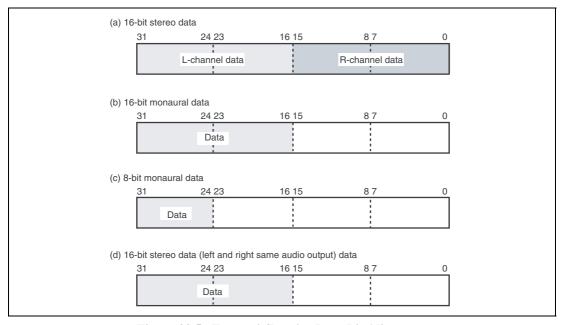

|          | 22.4.3  | Transfer Data Format                    | 830  |

|          | 22.4.4  | Register Allocation of Transfer Data    | 832  |

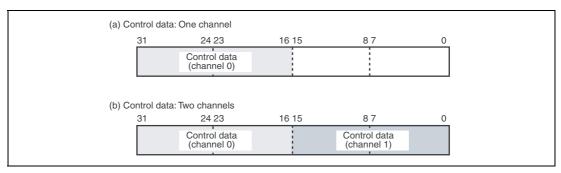

|          | 22.4.5  | Control Data Interface                  | 834  |

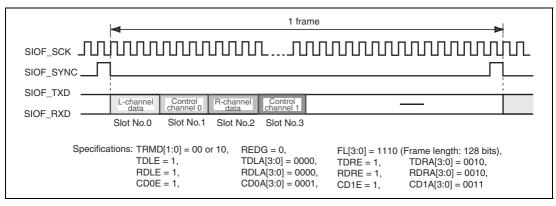

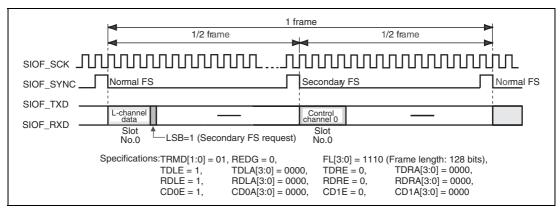

|          | 22.4.6  | FIFO                                    | 836  |

|          | 22.4.7  | Transmit and Receive Procedures         | 838  |

|          | 22.4.8  | Interrupts                              | 843  |

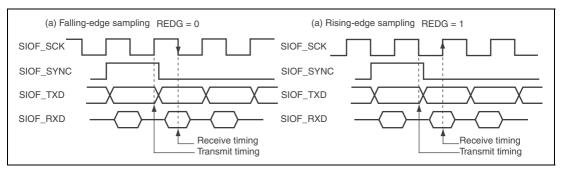

|          | 22.4.9  | Transmit and Receive Timing             | 845  |

| <b>a</b> | . 22    |                                         | 0.40 |

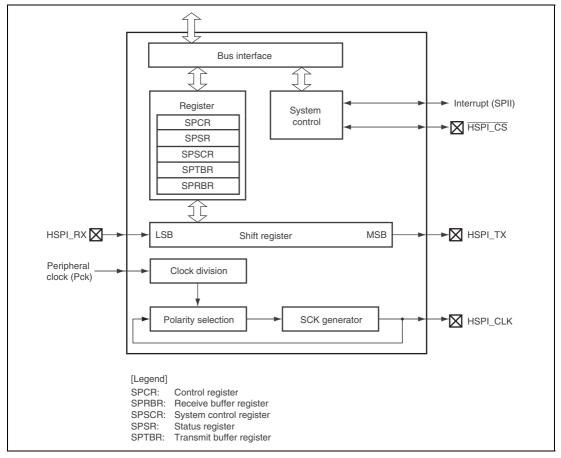

|          | ion 23  | ~                                       |      |

| 23.1     |         | 28                                      |      |

| 23.2     | _       | Output Pins                             |      |

| 23.3     | _       | er Descriptions                         |      |

|          |         | Control Register (SPCR)                 |      |

|          |         | Status Register (SPSR)                  |      |

|          |         | System Control Register (SPSCR)         |      |

|          |         | Transmit Buffer Register (SPTBR)        |      |

| 22.4     |         | Receive Buffer Register (SPRBR)         |      |

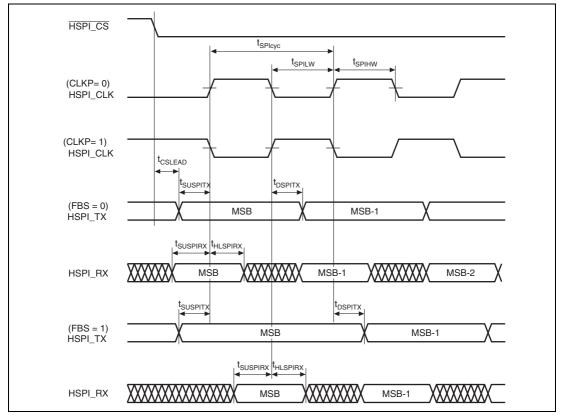

| 23.4     | -       | ion                                     |      |

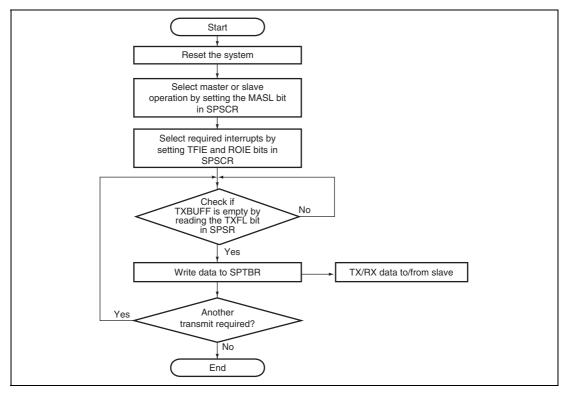

|          | 23.4.1  | ( )                                     |      |

|          |         | Operation Overview with DMA             |      |

|          |         | Operation with FIFO Mode Enabled        |      |

|          | 23.4.4  | 6 .6                                    |      |

|          |         | HSPI Software Reset                     |      |

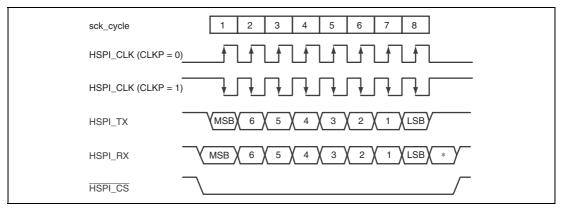

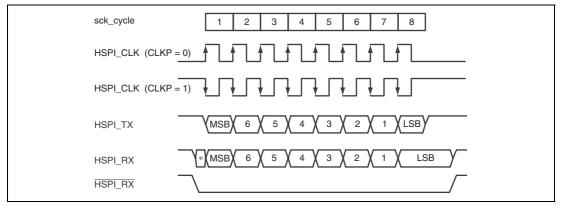

|          |         | Clock Polarity and Transmit Control     |      |

|          | 23 / 7  | Transmit and Receive Poutines           | 864  |

| Sect | ion 24  | Multimedia Card Interface (MMCIF)                        | 865 |

|------|---------|----------------------------------------------------------|-----|

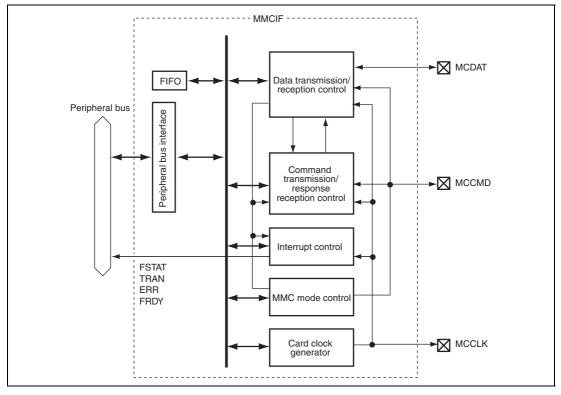

| 24.1 | Feature | es                                                       | 865 |

| 24.2 | Input/C | Output Pins                                              | 866 |

| 24.3 | Registe | er Descriptions                                          | 867 |

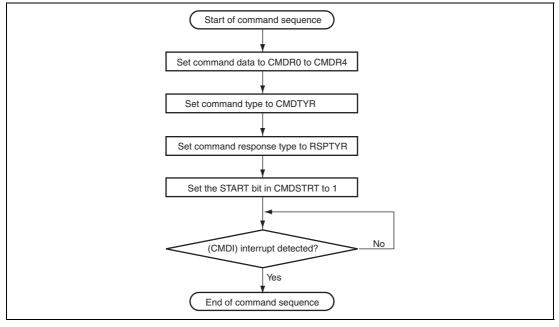

|      | 24.3.1  | Command Registers 0 to 5 (CMDR0 to CMDR5)                | 871 |

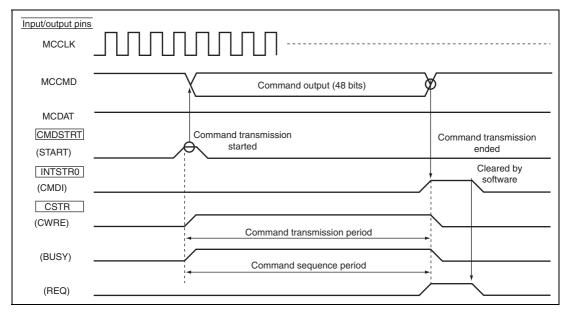

|      | 24.3.2  | Command Start Register (CMDSTRT)                         | 872 |

|      | 24.3.3  | Operation Control Register (OPCR)                        | 873 |

|      | 24.3.4  | Card Status Register (CSTR)                              | 875 |

|      | 24.3.5  | Interrupt Control Registers 0 to 2 (INTCR0 to INTCR2)    | 877 |

|      | 24.3.6  | Interrupt Status Registers 0 to 2 (INTSTR0 to INTSTR2)   | 880 |

|      | 24.3.7  | Transfer Clock Control Register (CLKON)                  | 885 |

|      | 24.3.8  | Command Timeout Control Register (CTOCR)                 | 886 |

|      | 24.3.9  | Transfer Byte Number Count Register (TBCR)               | 887 |

|      | 24.3.10 | ) Mode Register (MODER)                                  | 888 |

|      | 24.3.11 | 1 Command Type Register (CMDTYR)                         | 889 |

|      | 24.3.12 | 2 Response Type Register (RSPTYR)                        | 890 |

|      | 24.3.13 | 3 Transfer Block Number Counter (TBNCR)                  | 894 |

|      | 24.3.14 | 4 Response Registers 0 to 16, D (RSPR0 to RSPR16, RSPRD) | 895 |

|      | 24.3.15 | 5 Data Timeout Register (DTOUTR)                         | 897 |

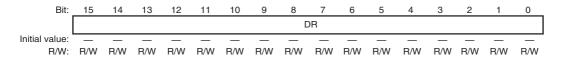

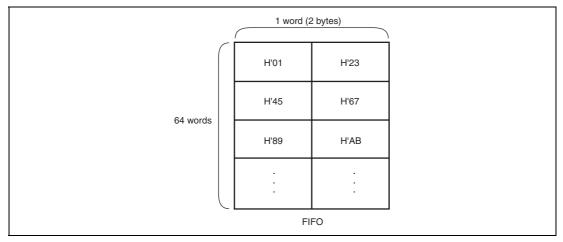

|      | 24.3.16 | 5 Data Register (DR)                                     | 898 |

|      | 24.3.17 | 7 FIFO Pointer Clear Register (FIFOCLR)                  | 899 |

|      | 24.3.18 | B DMA Control Register (DMACR)                           | 900 |

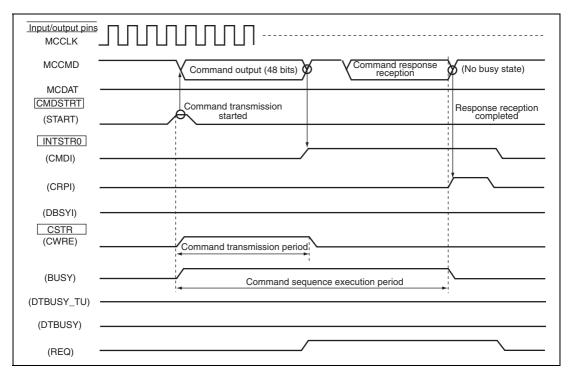

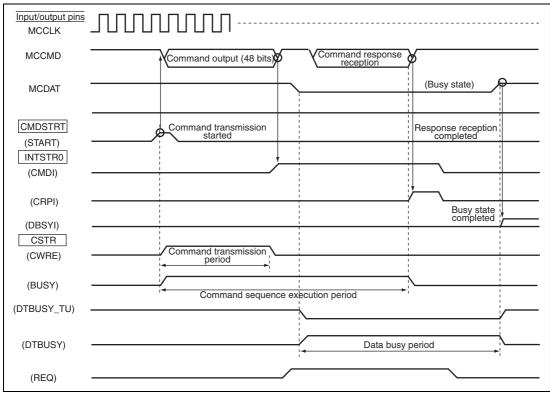

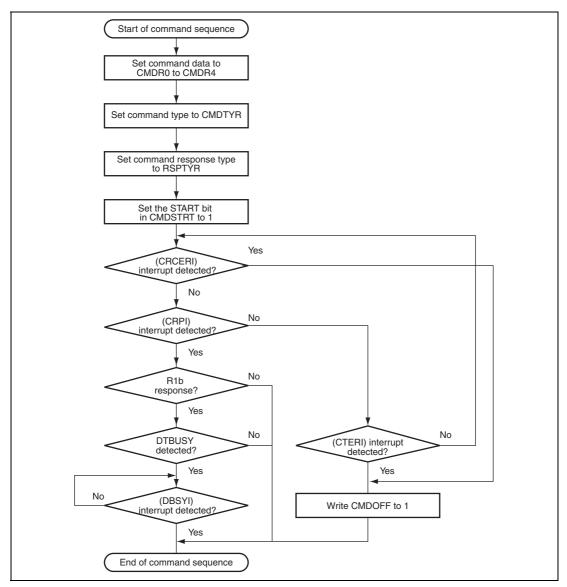

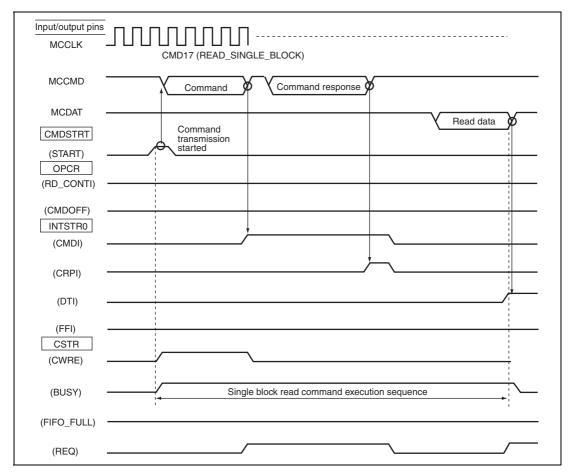

| 24.4 | Operat  | ion                                                      | 901 |

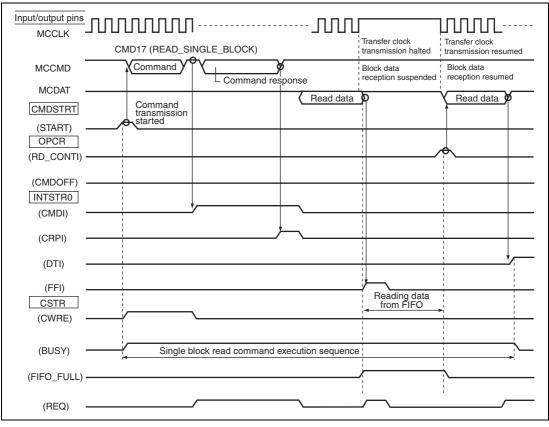

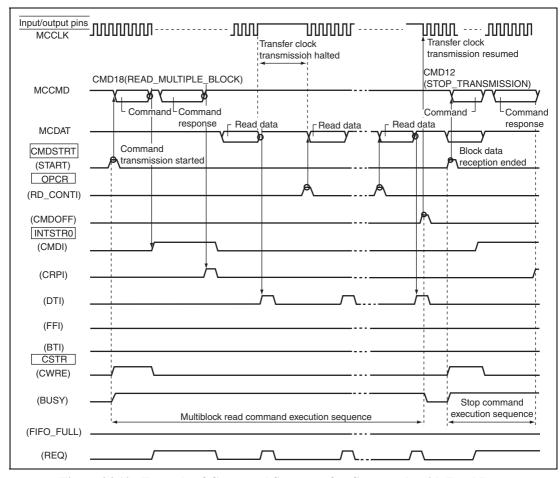

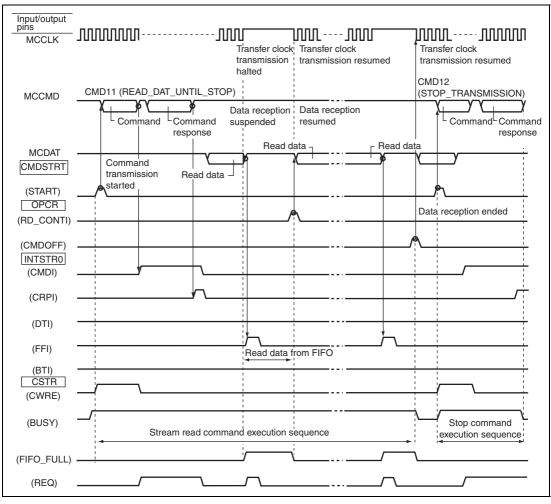

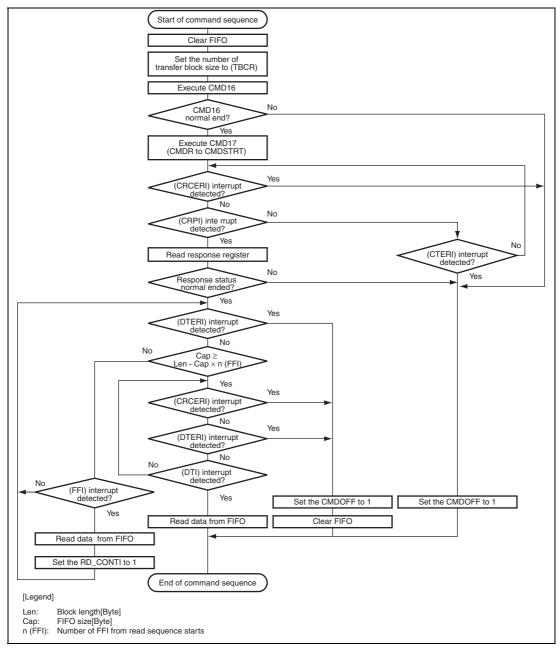

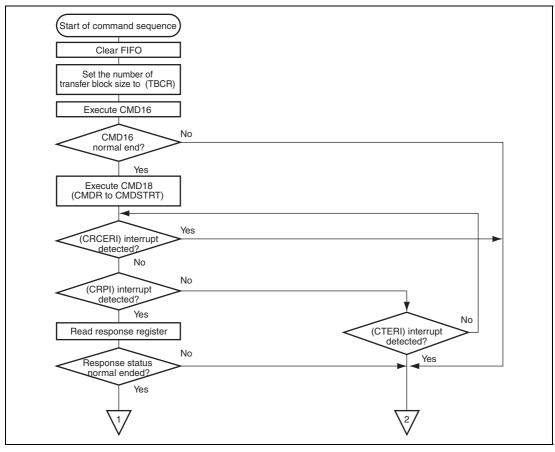

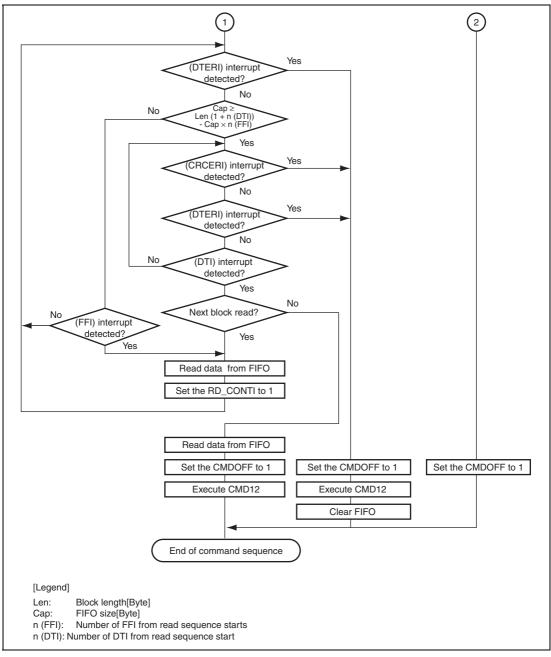

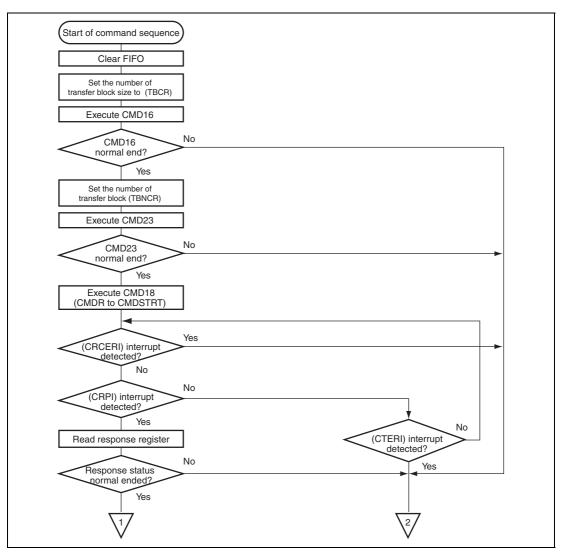

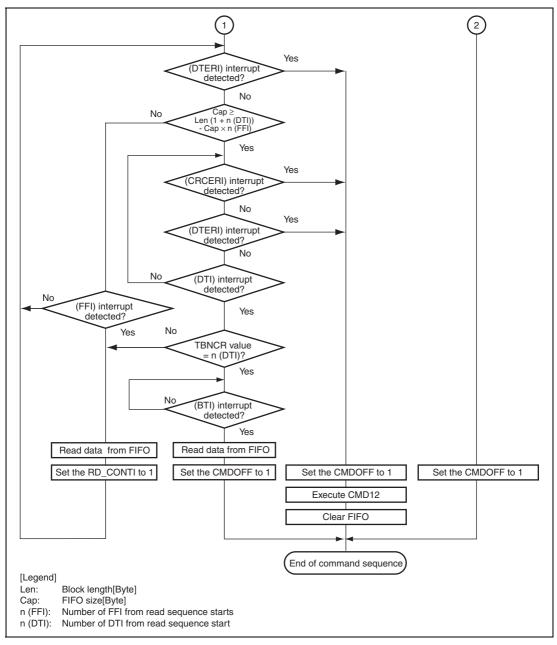

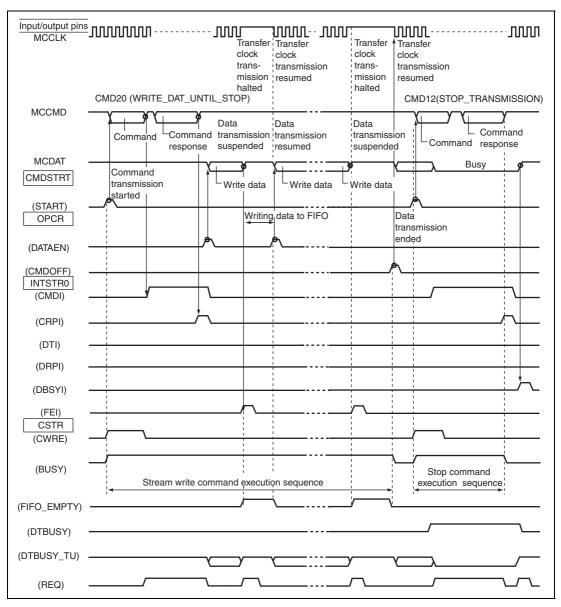

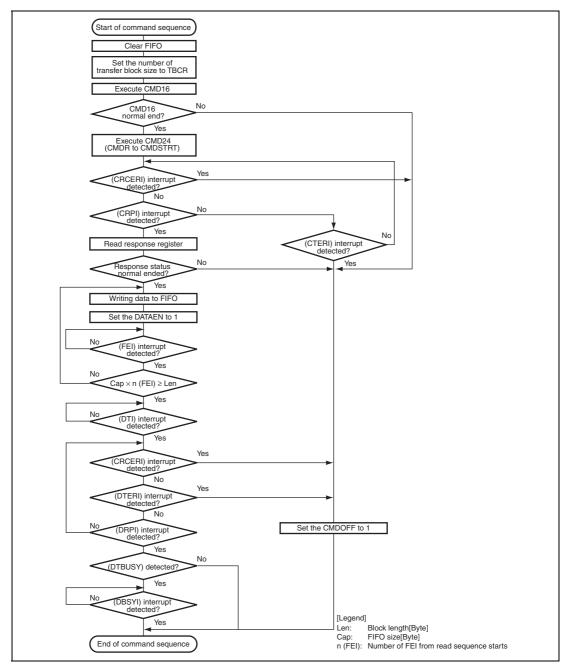

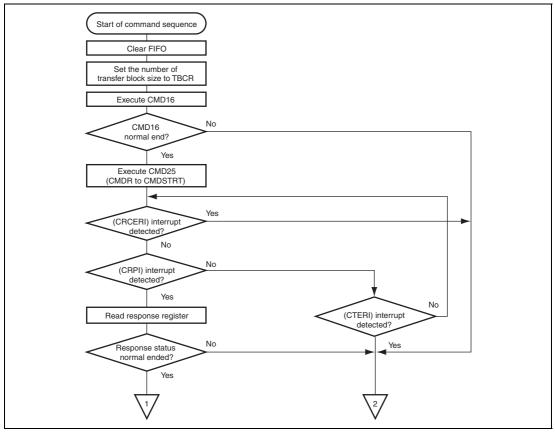

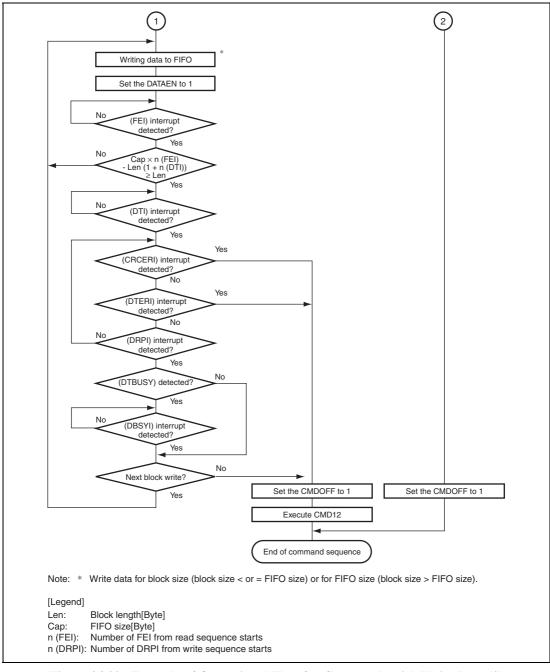

|      | 24.4.1  | Operations in MMC Mode                                   | 901 |

| 24.5 |         | F Interrupt Sources                                      |     |

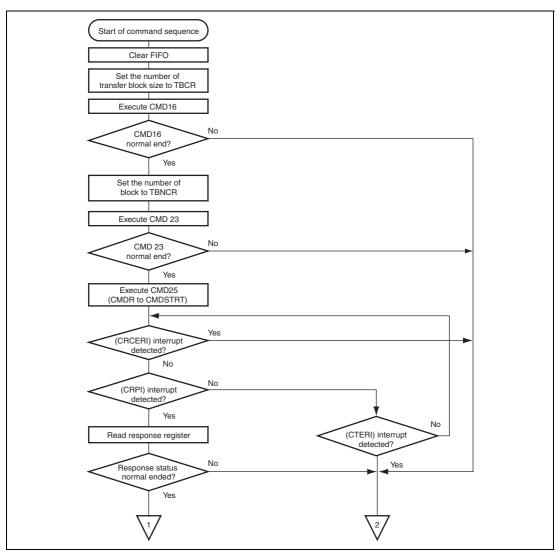

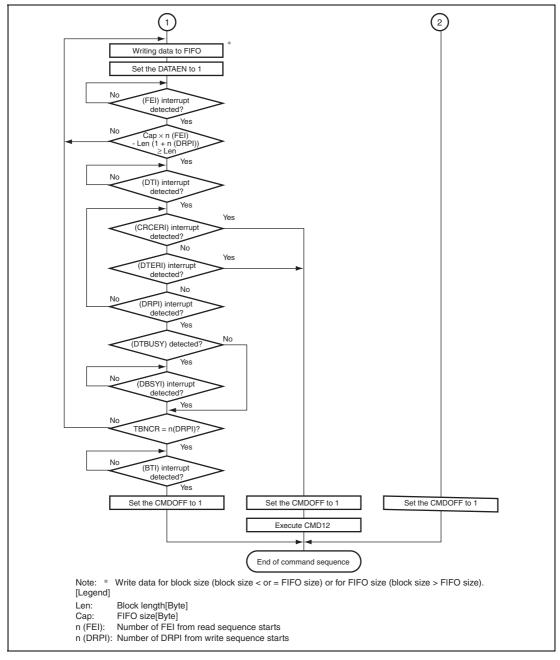

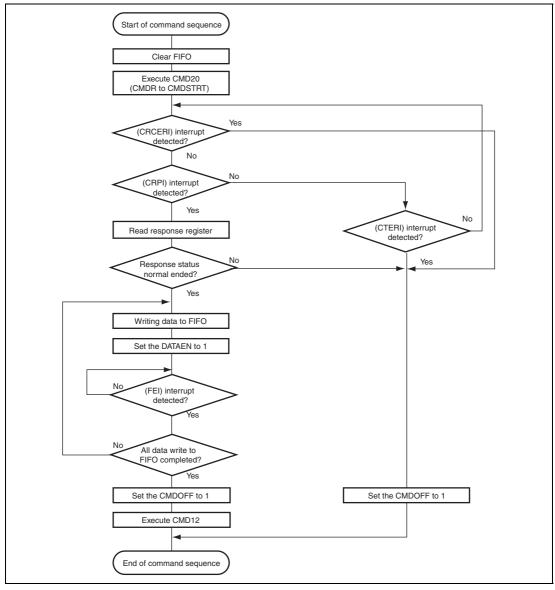

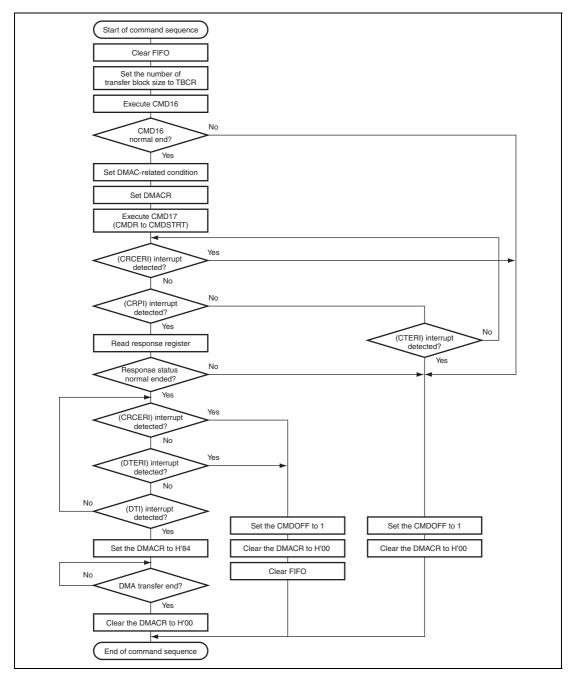

| 24.6 | Operat  | ions when Using DMA                                      | 932 |

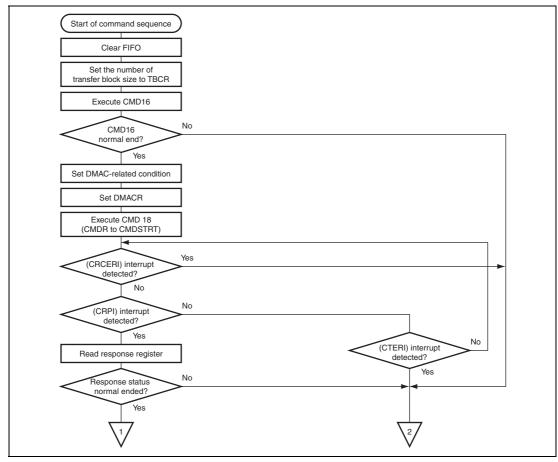

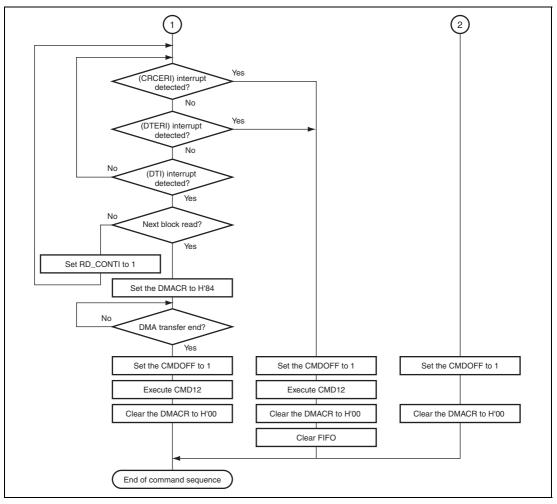

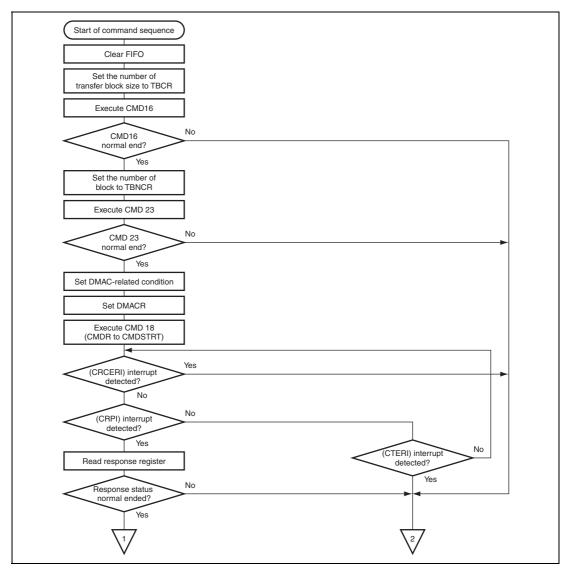

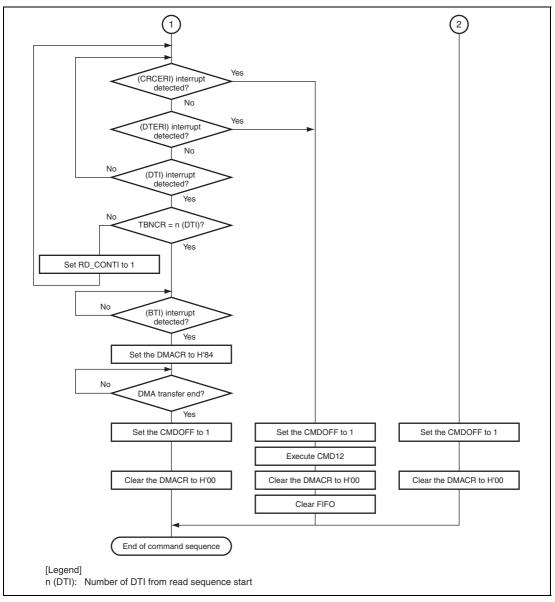

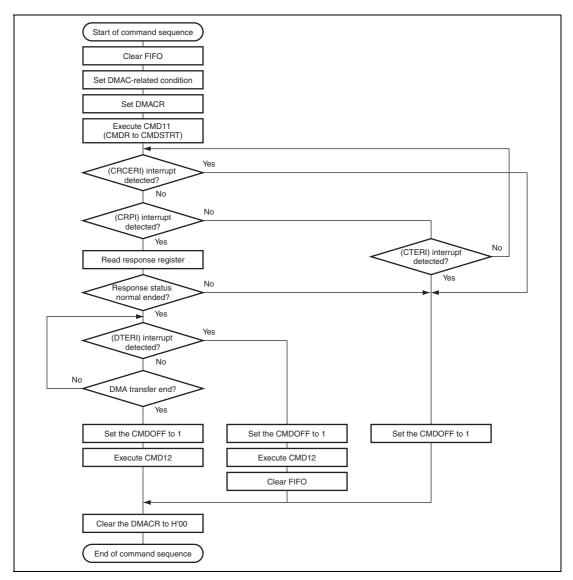

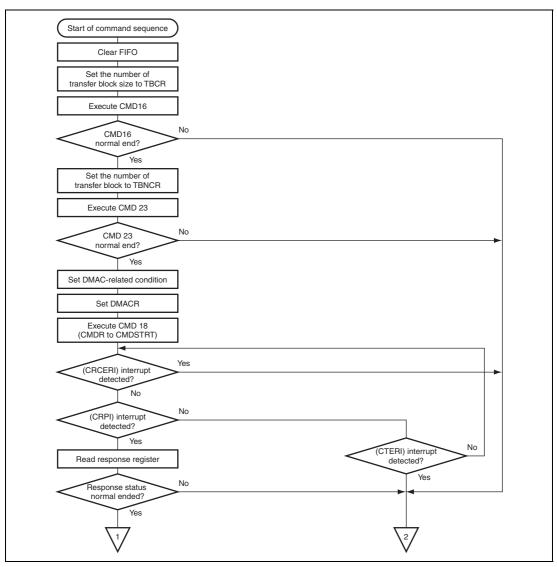

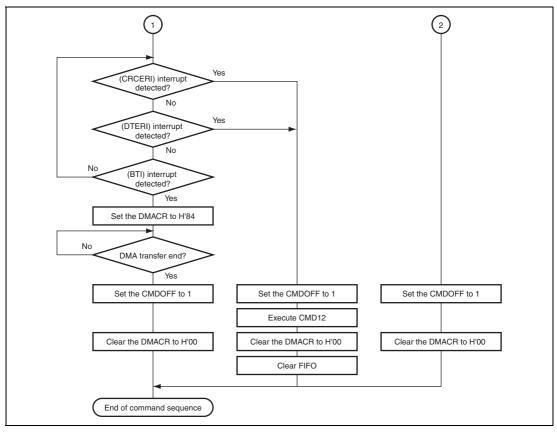

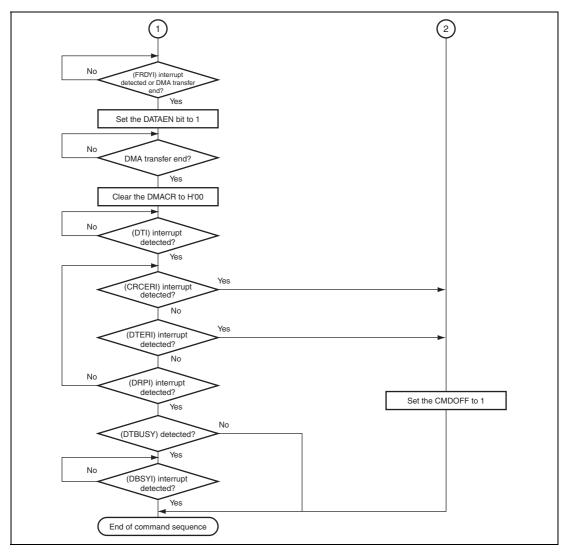

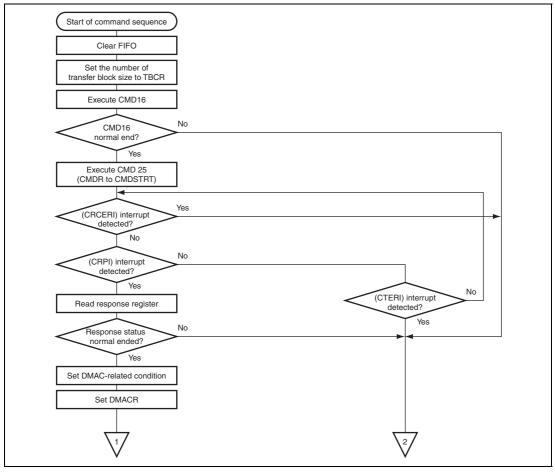

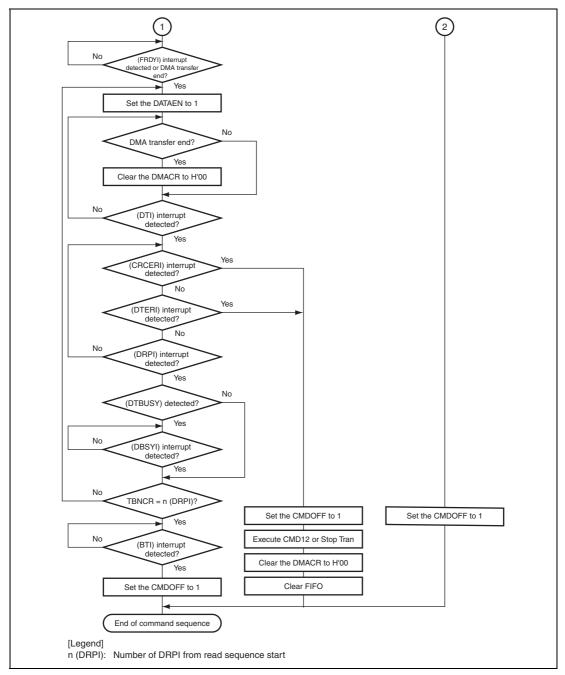

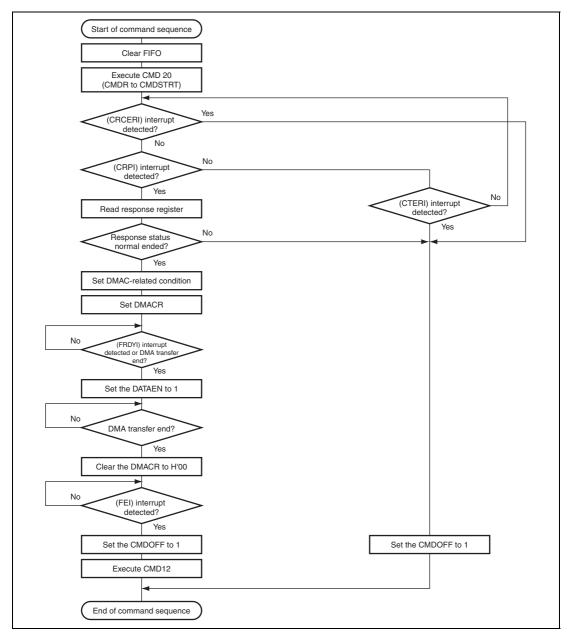

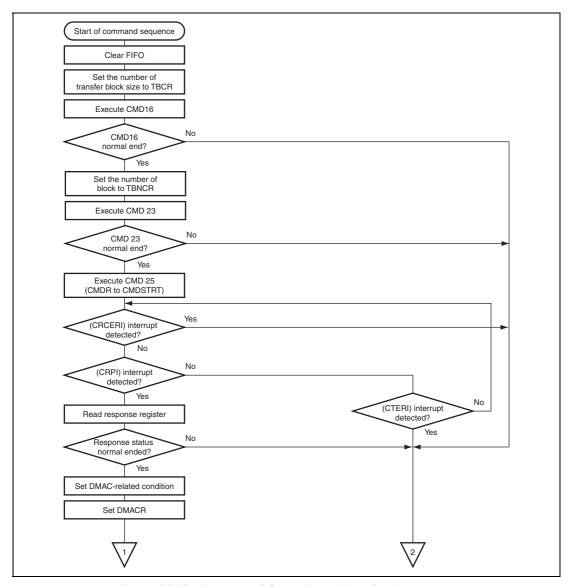

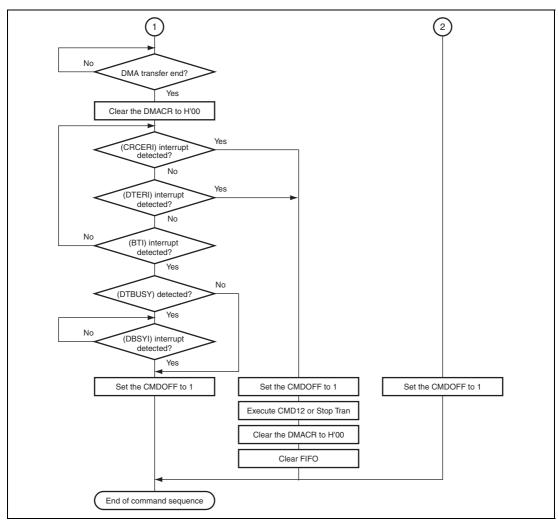

|      | 24.6.1  | Operation in Read Sequence                               | 932 |

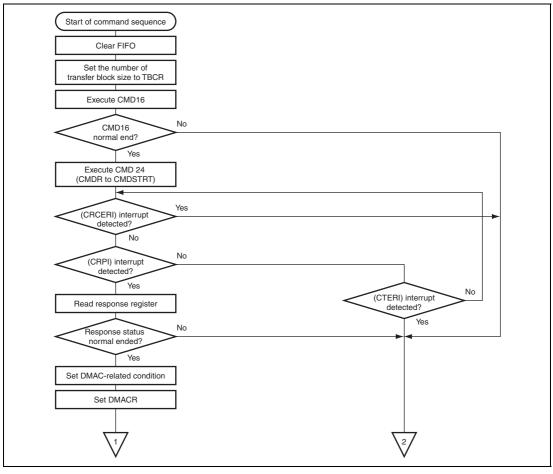

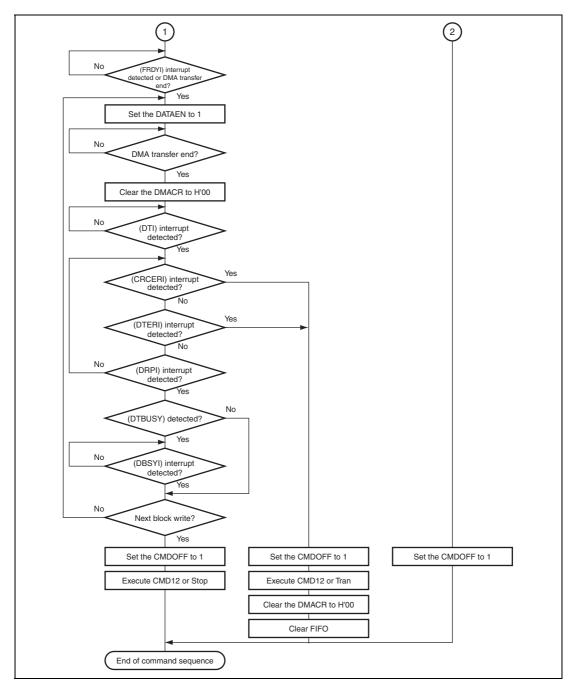

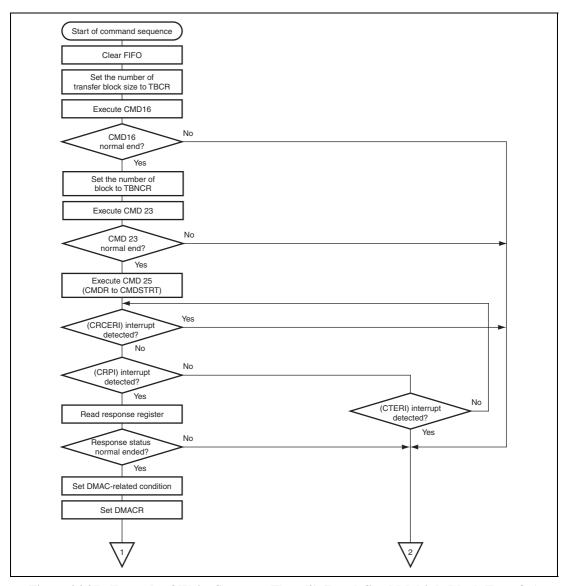

|      |         | Operation in Write Sequence                              |     |

| 24.7 | Registe | er Accesses with Little Endian Specification             | 953 |

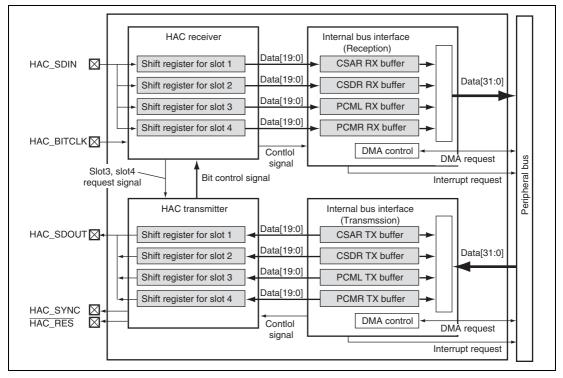

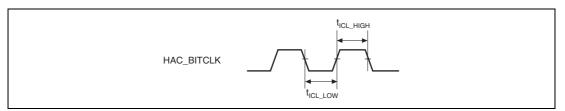

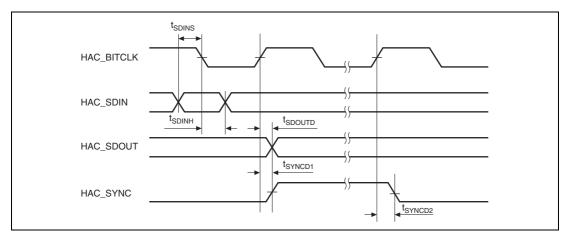

| Sect | ion 25  | Audio Codec Interface (HAC)                              | 955 |

| 25.1 | Feature | es                                                       | 955 |

| 25.2 | Input/C | Output Pins                                              | 956 |

| 25.3 | Registe | er Descriptions                                          | 957 |

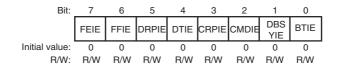

|      | 25.3.1  | Control and Status Register (HACCR)                      | 958 |

|      | 25.3.2  | Command/Status Address Register (HACCSAR)                | 960 |

|      | 25.3.3  | Command/Status Data Register (HACCSDR)                   | 962 |

|      | 25.3.4  | PCM Left Channel Register (HACPCML)                      | 963 |

|      | 25.3.5  | PCM Right Channel Register (HACPCMR)                     | 965 |

|      | 25.3.6  | TX Interrupt Enable Register (HACTIER)                   | 966 |

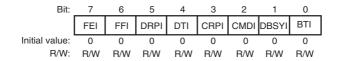

|      | 25.3.7  | TX Status Register (HACTSR)                                       | 967  |

|------|---------|-------------------------------------------------------------------|------|

|      | 25.3.8  | RX Interrupt Enable Register (HACRIER)                            | 969  |

|      | 25.3.9  | RX Status Register (HACRSR)                                       | 970  |

|      | 25.3.10 | HAC Control Register (HACACR)                                     | 971  |

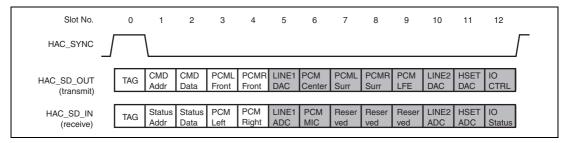

| 25.4 | AC 97   | Frame Slot Structure                                              | 973  |

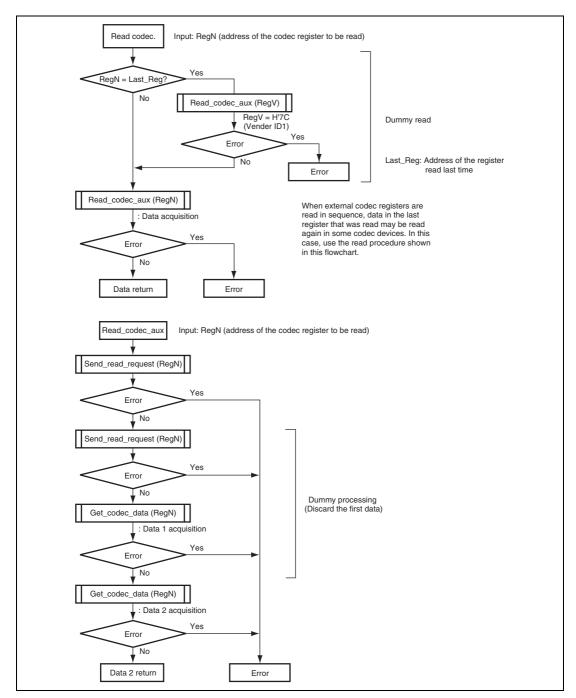

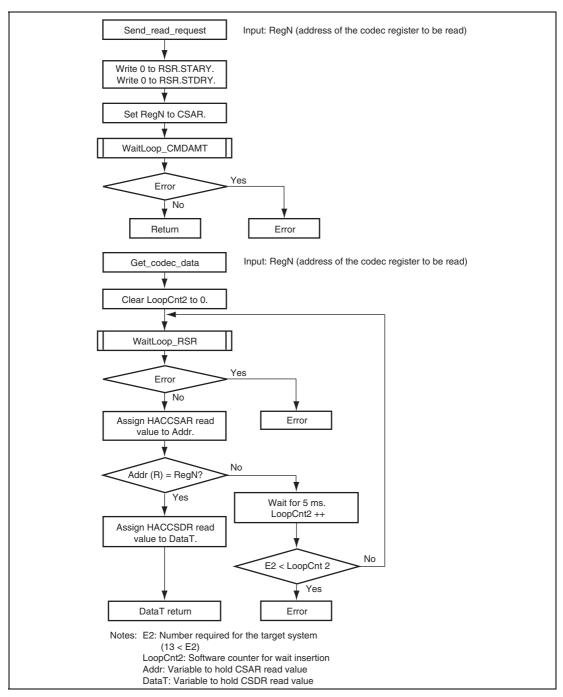

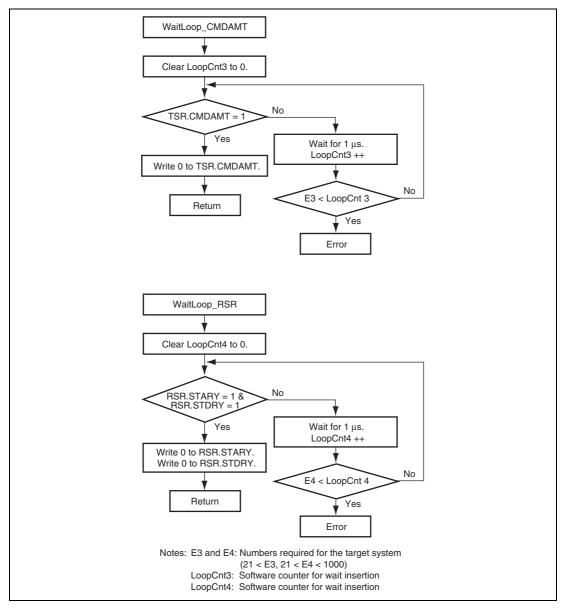

| 25.5 | Operati | ion                                                               | 974  |

|      | 25.5.1  | Receiver                                                          | 974  |

|      | 25.5.2  | Transmitter                                                       | 975  |

|      | 25.5.3  | DMA                                                               | 975  |

|      | 25.5.4  | Interrupts                                                        | 975  |

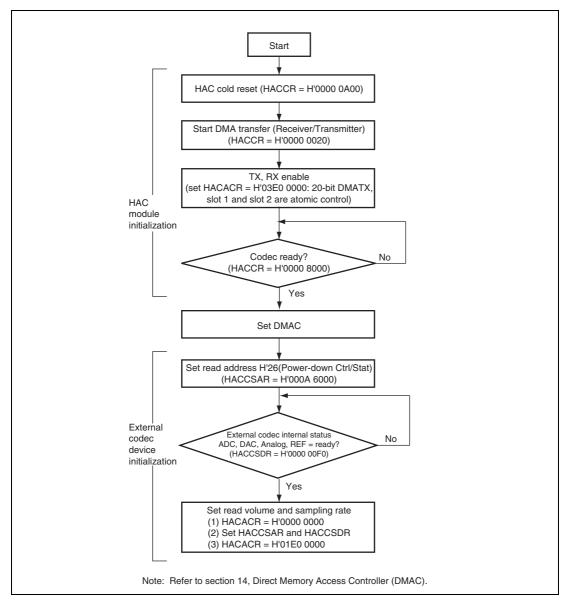

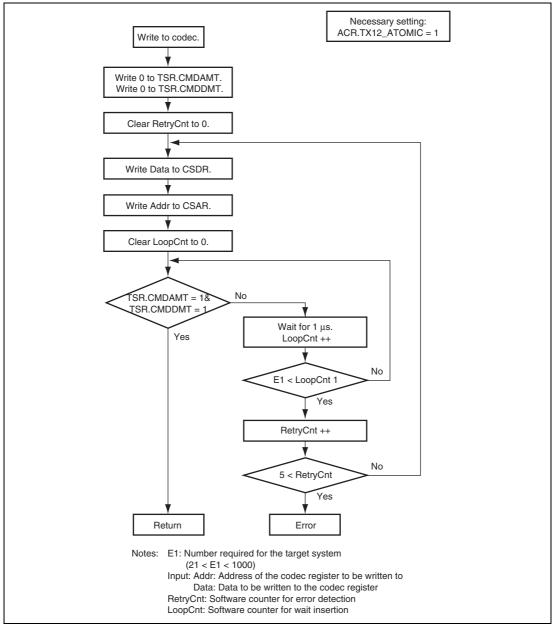

|      | 25.5.5  | Initialization Sequence                                           | 976  |

|      | 25.5.6  | Notes                                                             | 981  |

|      | 25.5.7  | Reference                                                         | 981  |

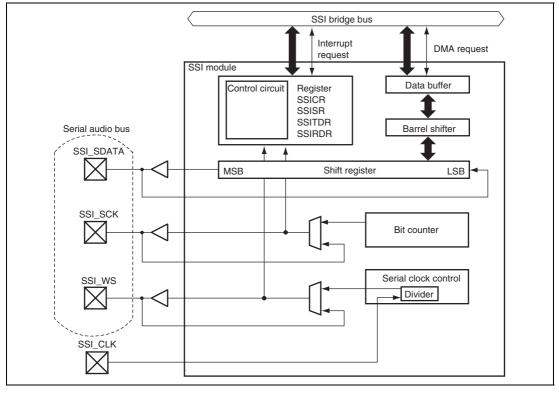

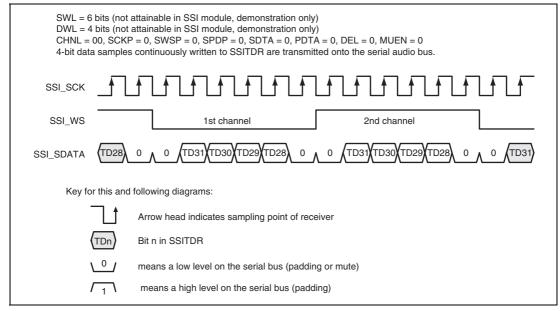

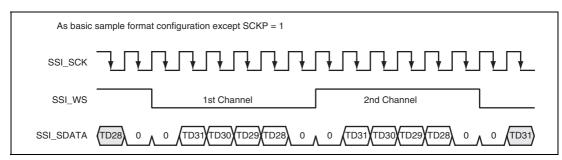

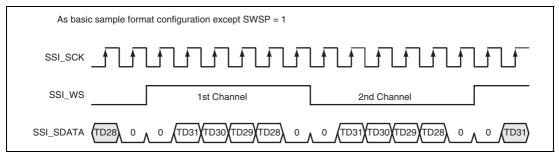

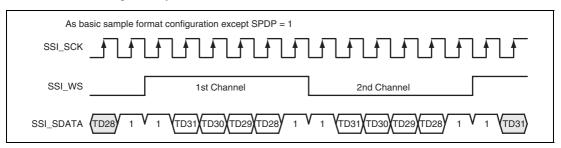

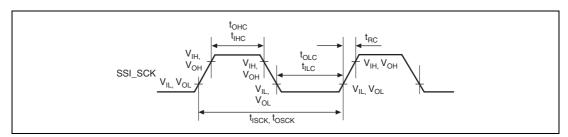

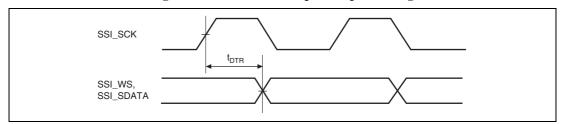

| Sect | ion 26  | Serial Sound Interface (SSI) Module                               | 983  |

| 26.1 |         | 28                                                                |      |

| 26.2 |         | Output Pins                                                       |      |

| 26.3 | -       | er Descriptions                                                   |      |

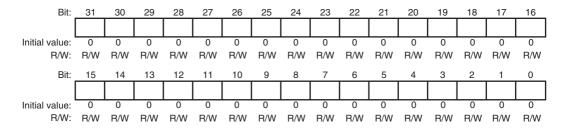

|      | 26.3.1  | Control Register (SSICR)                                          | 986  |

|      |         | Status Register (SSISR)                                           |      |

|      | 26.3.3  | Transmit Data Register (SSITDR)                                   | 997  |

|      |         | Receive Data Register (SSIRDR)                                    |      |

| 26.4 | Operat  | ion                                                               | 998  |

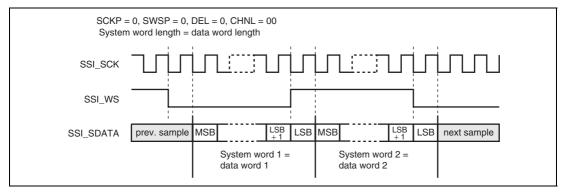

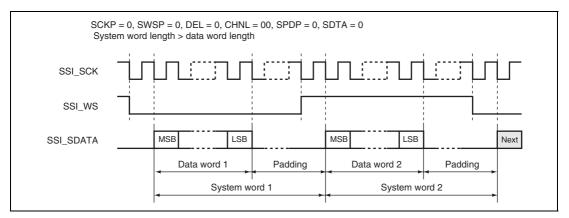

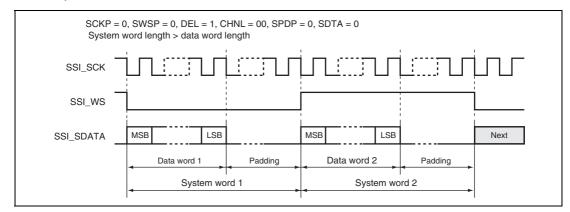

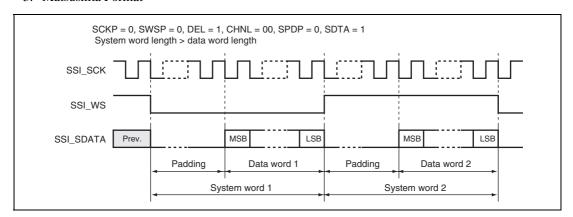

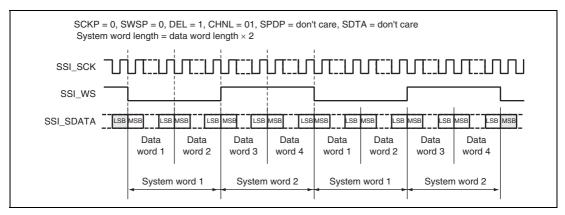

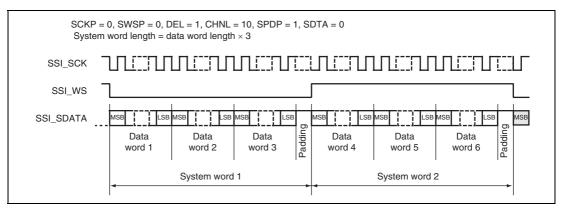

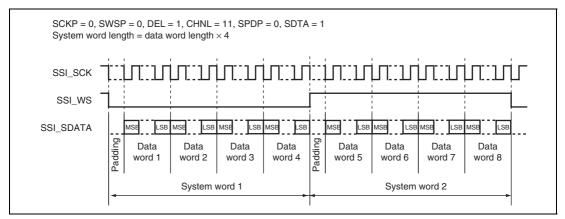

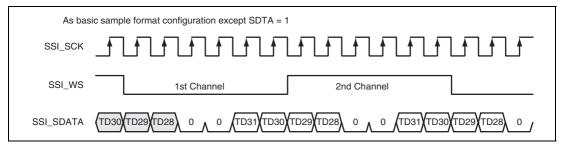

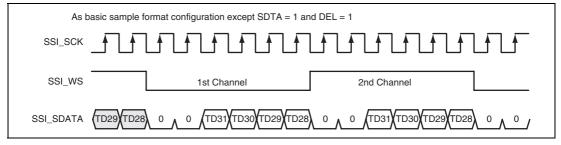

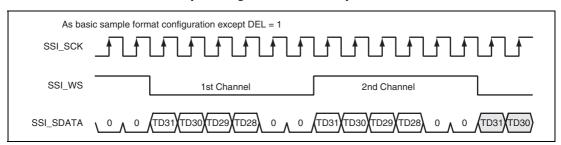

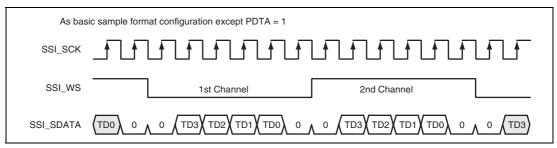

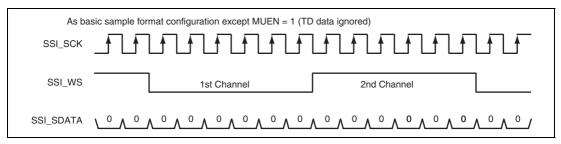

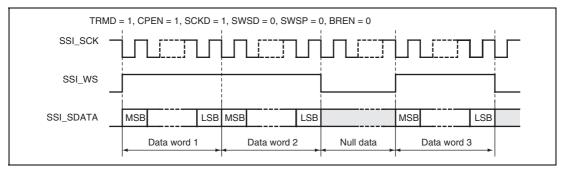

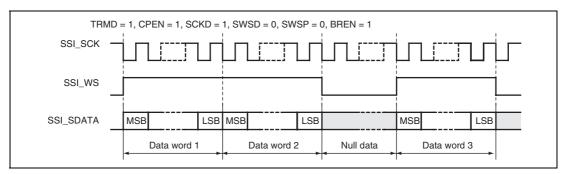

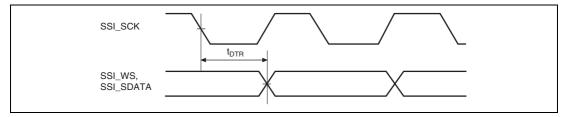

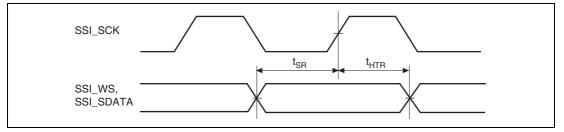

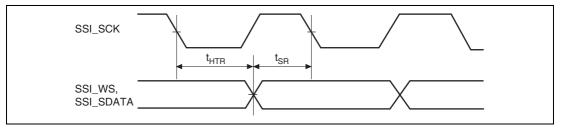

|      | 26.4.1  | Bus Format                                                        | 998  |

|      | 26.4.2  | Non-Compressed Modes                                              | 999  |

|      | 26.4.3  | Compressed Modes                                                  | 1008 |

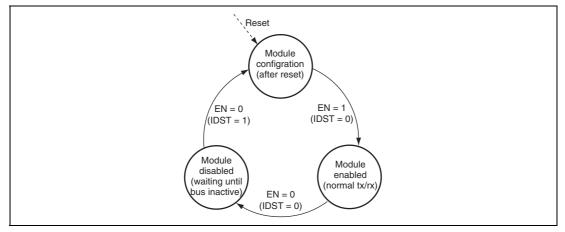

|      | 26.4.4  | Operation Modes                                                   | 1011 |

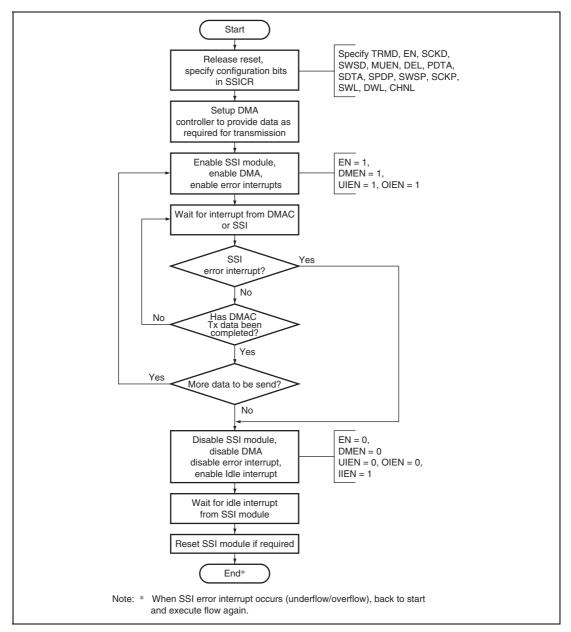

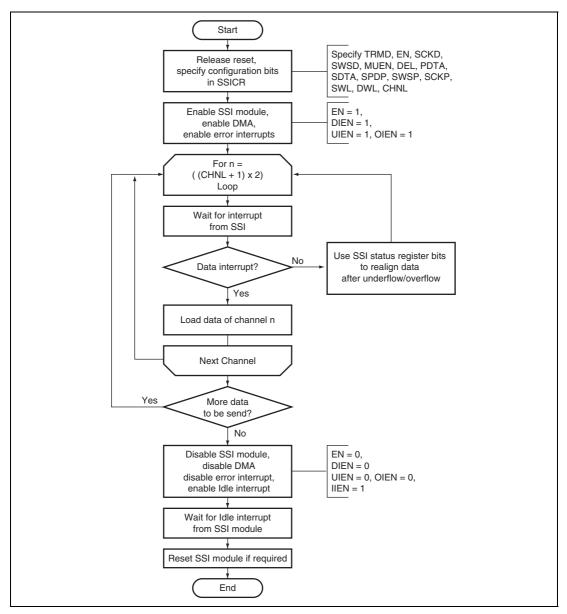

|      | 26.4.5  | Transmit Operation                                                | 1012 |

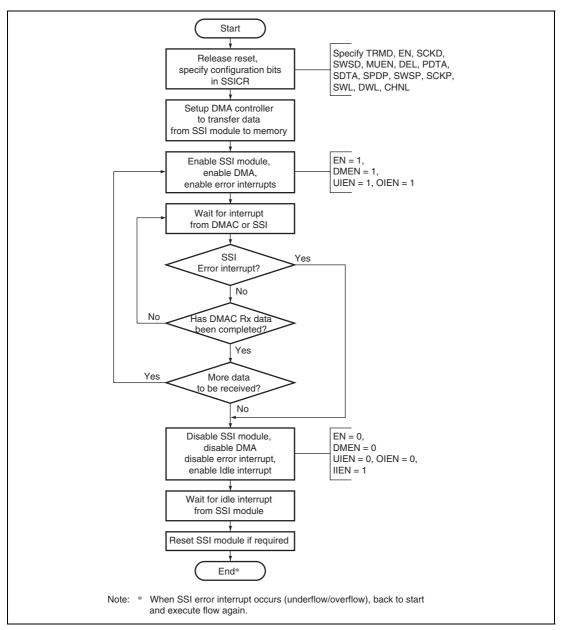

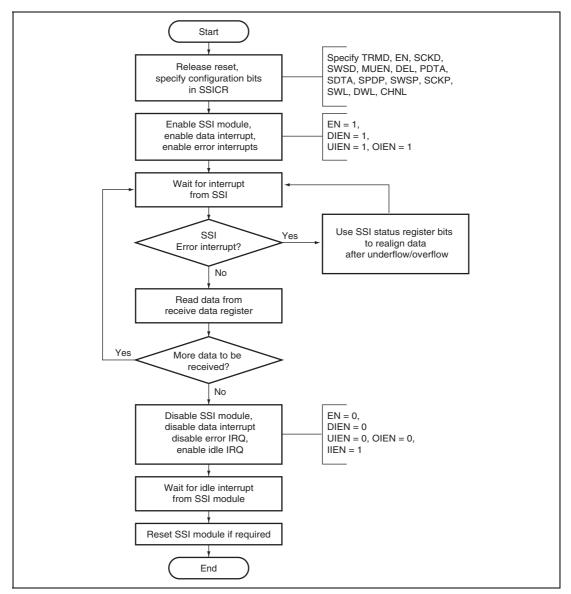

|      | 26.4.6  | Receive Operation                                                 | 1015 |

|      | 26.4.7  | Serial Clock Control                                              | 1018 |

| 26.5 | Usage   | Note                                                              | 1019 |

|      | 26.5.1  | Restrictions when an Overflow Occurs during Receive DMA Operation | 1019 |

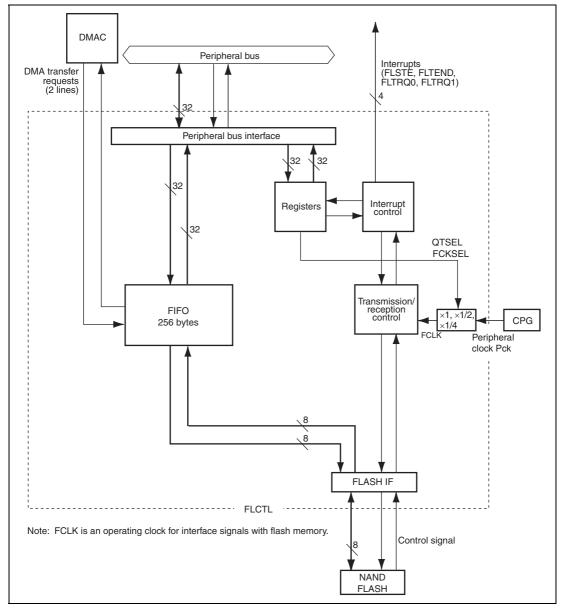

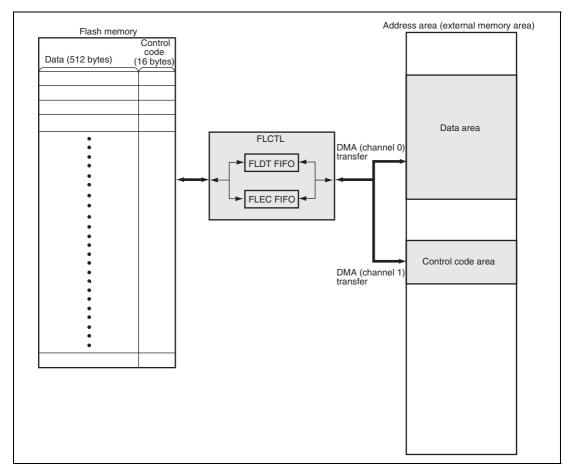

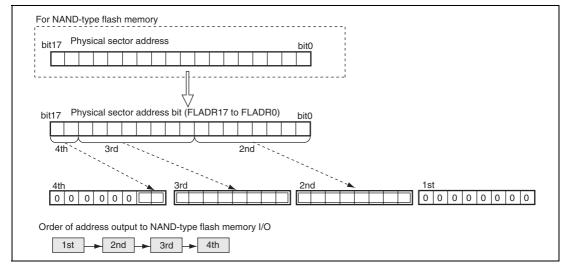

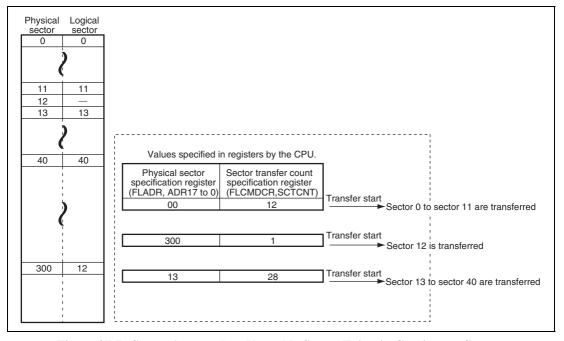

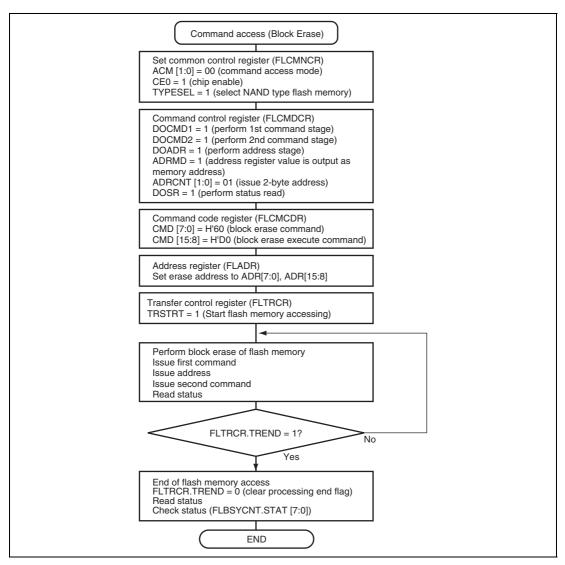

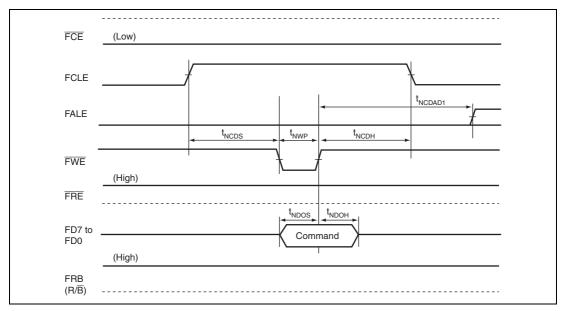

| Sect | ion 27  | NAND Flash Memory Controller (FLCTL)                              | 1021 |

| 27.1 |         | es                                                                |      |

| 27.2 | Input/C | Output Pins                                                       | 1024 |

| 27.3 |         | er Descriptions                                                   |      |

|      | _       | Common Control Register (FLCMNCR)                                 |      |

|      |         | Command Control Register (FLCMDCR)                                |      |

|      |         | Command Code Register (FLCMCDR)                                   |      |

|      | 27.3.4  | Address Register (FLADR)                       | 1030 |

|------|---------|------------------------------------------------|------|

|      | 27.3.5  | Data Counter Register (FLDTCNTR)               | 1032 |

|      | 27.3.6  | Data Register (FLDATAR)                        | 1033 |

|      | 27.3.7  | Interrupt DMA Control Register (FLINTDMACR)    | 1034 |

|      | 27.3.8  | Ready Busy Timeout Setting Register (FLBSYTMR) | 1039 |

|      | 27.3.9  | Ready Busy Timeout Counter (FLBSYCNT)          | 1040 |

|      | 27.3.10 | Data FIFO Register (FLDTFIFO)                  | 1041 |

|      | 27.3.11 | 1 Control Code FIFO Register (FLECFIFO)        | 1042 |

|      | 27.3.12 | 2 Transfer Control Register (FLTRCR)           | 1043 |

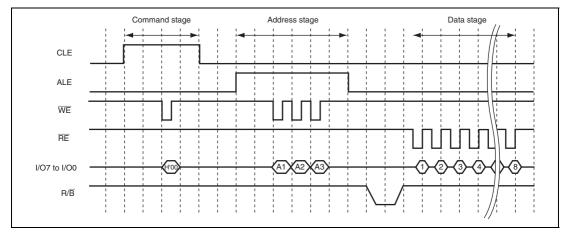

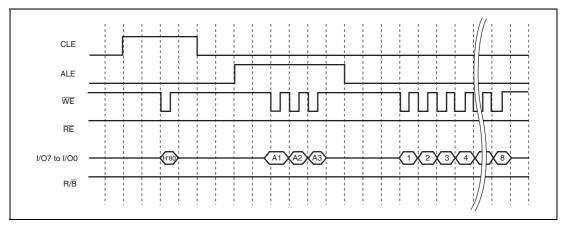

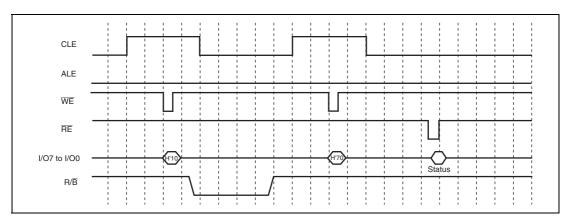

| 27.4 | Operat  | ion                                            | 1044 |

|      | 27.4.1  | Operating Modes                                | 1044 |

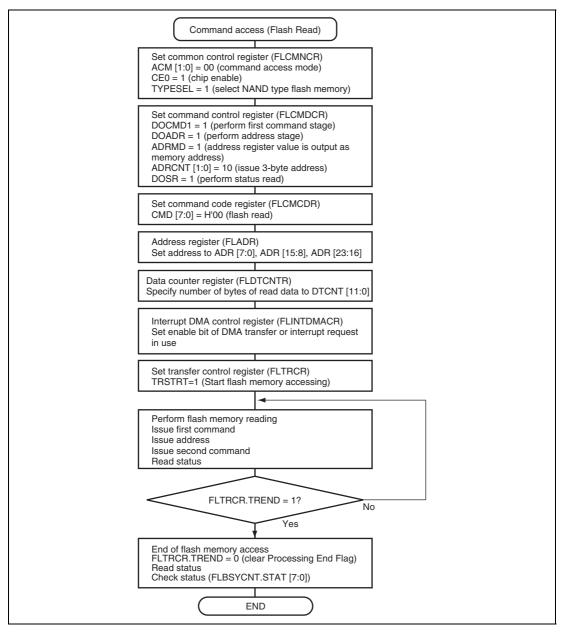

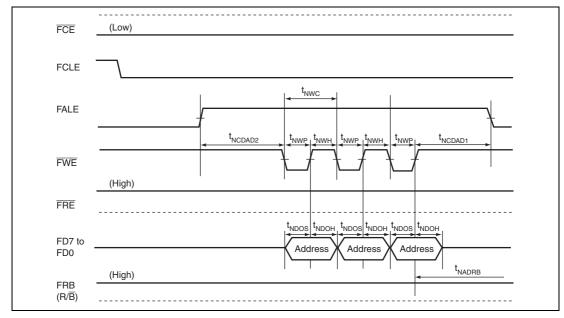

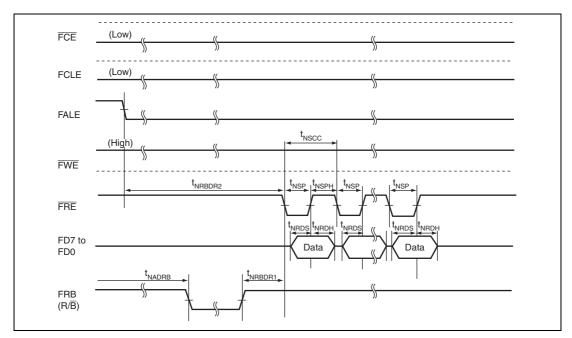

|      | 27.4.2  | Command Access Mode                            | 1044 |

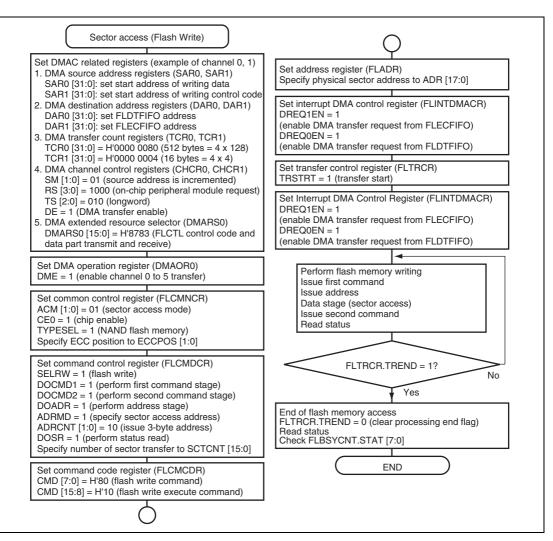

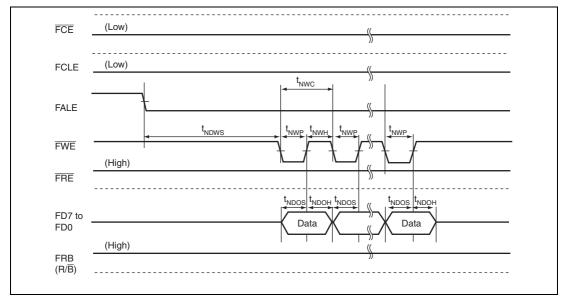

|      | 27.4.3  | Sector Access Mode                             | 1046 |

|      | 27.4.4  | ECC Error Correction                           | 1048 |

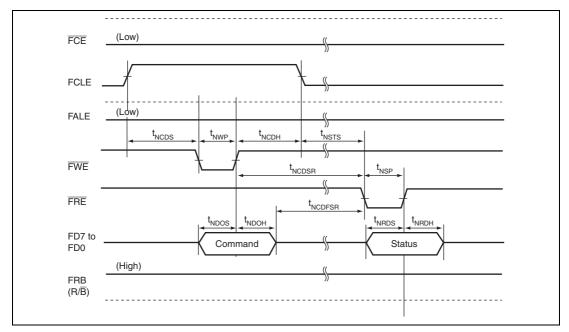

|      | 27.4.5  | Status Read                                    | 1049 |

| 27.5 | Examp   | le of Register Setting                         | 1050 |

| 27.6 | Interru | pt Sources                                     | 1053 |

| 27.7 | DMA 7   | Transfer Specifications                        | 1053 |

| Sect | ion 28  | General Purpose I/O (GPIO)                     | 1055 |

| 28.1 |         | es                                             |      |

| 28.2 | Registe | er Descriptions                                | 1060 |

|      | 28.2.1  | Port A Control Register (PACR)                 | 1063 |

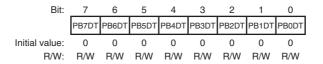

|      | 28.2.2  | Port B Control Register (PBCR)                 | 1064 |

|      | 28.2.3  | Port C Control Register (PCCR)                 | 1066 |

|      | 28.2.4  | Port D Control Register (PDCR)                 | 1067 |

|      | 28.2.5  | Port E Control Register (PECR)                 | 1069 |

|      | 28.2.6  | Port F Control Register (PFCR)                 | 1070 |

|      | 28.2.7  | Port G Control Register (PGCR)                 | 1072 |

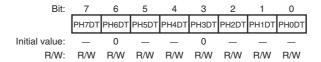

|      | 28.2.8  | Port H Control Register (PHCR)                 | 1074 |

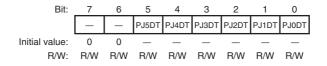

|      | 28.2.9  | Port J Control Register (PJCR)                 | 1075 |

|      | 28.2.10 | ) Port K Control Register (PKCR)               | 1077 |

|      | 28.2.11 | 1 Port L Control Register (PLCR)               | 1079 |

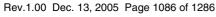

|      | 28.2.12 | 2 Port M Control Register (PMCR)               | 1080 |

|      | 28.2.13 | 3 Port A Data Register (PADR)                  | 1081 |

|      | 28.2.14 | 4 Port B Data Register (PBDR)                  | 1081 |

|      |         | 5 Port C Data Register (PCDR)                  |      |

|      | 28.2.16 | 5 Port D Data Register (PDDR)                  | 1082 |

|      | 28.2.17 | 7 Port E Data Register (PEDR)                  | 1083 |

|      | 28.2.18 | R Port F Data Register (PFDR)                  | 1084 |

|      | 28.2.19 | Port G Data Register (PGDR)                                    | 1084 |

|------|---------|----------------------------------------------------------------|------|

|      | 28.2.20 | Port H Data Register (PHDR)                                    | 1085 |

|      | 28.2.21 | Port J Data Register (PJDR)                                    | 1085 |

|      |         | Port K Data Register (PKDR)                                    |      |

|      | 28.2.23 | Port L Data Register (PLDR)                                    | 1086 |

|      | 28.2.24 | Port M Data Register (PMDR)                                    | 1087 |

|      | 28.2.25 | Fort E Pull-Up Control Register (PEPUPR)                       | 1087 |

|      | 28.2.26 | 5 Port H Pull-Up Control Register (PHPUPR)                     | 1088 |

|      | 28.2.27 | Port J Pull-Up Control Register (PJPUPR)                       | 1089 |

|      | 28.2.28 | Port K Pull-Up Control Register (PKPUPR)                       | 1090 |

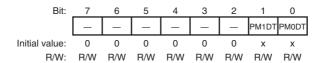

|      | 28.2.29 | Port M Pull-Up Control Register (PMPUPR)                       | 1091 |

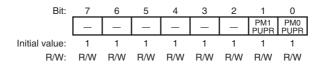

|      | 28.2.30 | Input-Pin Pull-Up Control Register 1 (PPUPR1)                  | 1092 |

|      | 28.2.31 | Input-Pin Pull-Up Control Register 2 (PPUPR2)                  | 1093 |

|      | 28.2.32 | 2 On-chip Module Select Register (OMSELR)                      | 1094 |

| 28.3 | Usage   | Example                                                        | 1097 |

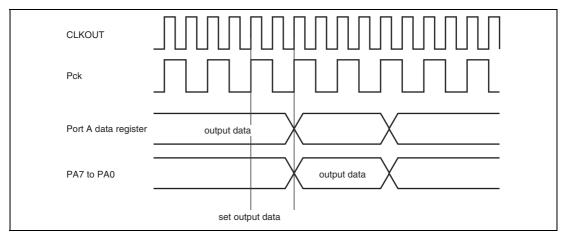

|      | 28.3.1  | Port Output Function                                           | 1097 |

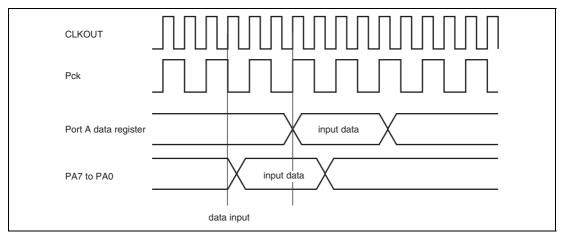

|      | 28.3.2  | Port Input function                                            | 1098 |

|      | 28.3.3  | On-chip Module Function                                        | 1099 |

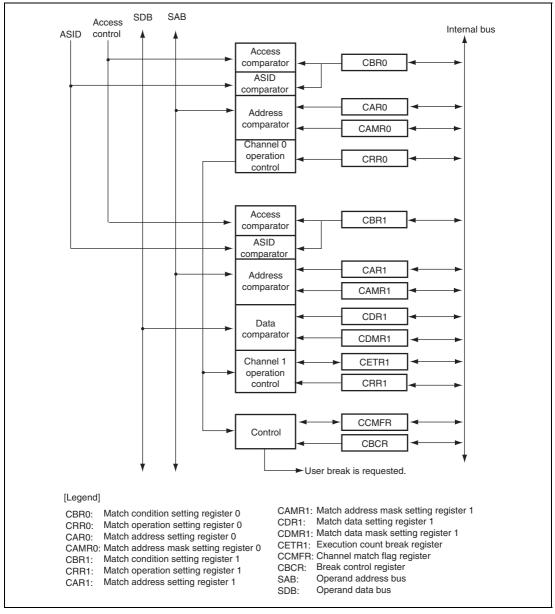

| Sect | ion 29  | User Break Controller (UBC)                                    | 1101 |

| 29.1 |         | 28                                                             |      |

| 29.2 | Registe | er Descriptions                                                | 1103 |

|      | 29.2.1  | Match Condition Setting Registers 0 and 1 (CBR0 and CBR1)      | 1105 |

|      | 29.2.2  | Match Operation Setting Registers 0 and 1 (CRR0 and CRR1)      | 1111 |

|      | 29.2.3  | Match Address Setting Registers 0 and 1 (CAR0 and CAR1)        | 1113 |

|      | 29.2.4  | Match Address Mask Setting Registers 0 and 1 (CAMR0 and CAMR1) | 1114 |

|      | 29.2.5  | Match Data Setting Register 1 (CDR1)                           | 1115 |

|      | 29.2.6  | Match Data Mask Setting Register 1 (CDMR1)                     | 1116 |

|      | 29.2.7  | Execution Count Break Register 1 (CETR1)                       | 1117 |

|      | 29.2.8  | Channel Match Flag Register (CCMFR)                            | 1118 |

|      | 29.2.9  | Break Control Register (CBCR)                                  | 1119 |

| 29.3 | Operat  | ion Description                                                | 1120 |

|      | 29.3.1  | Definition of Words Related to Accesses                        | 1120 |

|      | 29.3.2  | User Break Operation Sequence                                  | 1121 |

|      | 29.3.3  | Instruction Fetch Cycle Break                                  | 1122 |

|      | 29.3.4  | Operand Access Cycle Break                                     | 1123 |

|      | 29.3.5  | Sequential Break                                               | 1124 |

|      | 29.3.6  | Program Counter Value to be Saved                              | 1126 |

| 29.4 | User B  | reak Debugging Support Function                                | 1127 |

| 29.5 | User B  | reak Examples                                                  | 1128 |

| 29.6  | Usage I | Notes                                   | . 1132 |

|-------|---------|-----------------------------------------|--------|

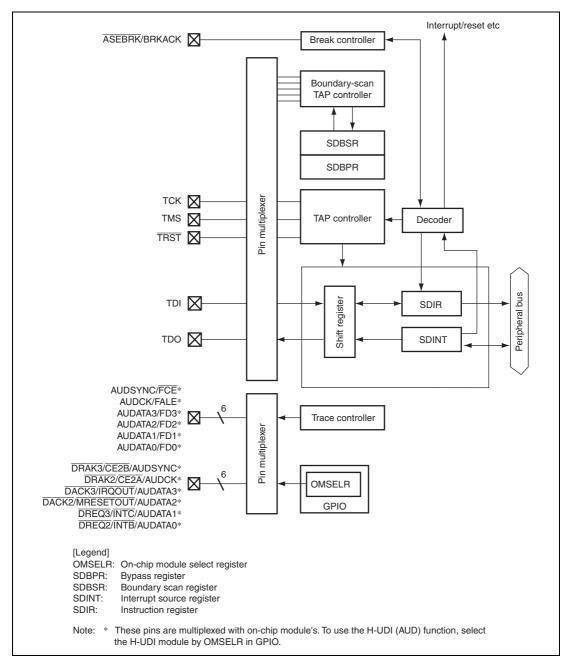

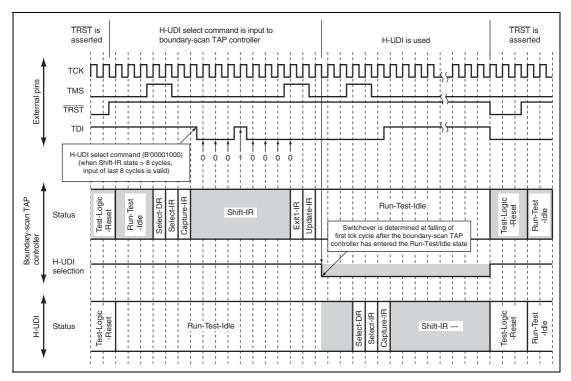

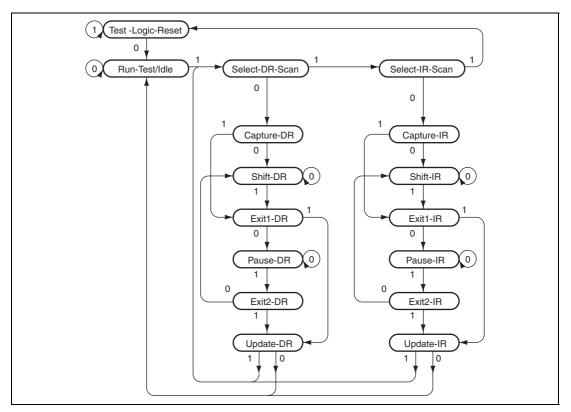

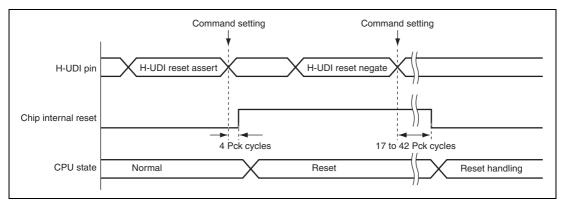

| Secti | on 30   | User Debugging Interface (H-UDI)        | 1135   |

| 30.1  | Feature | es                                      | . 1135 |

| 30.2  | Input/C | Output Pins                             | . 1137 |

| 30.3  | Bounda  | ary Scan TAP Controllers                |        |

|       | (IDCO   | DE, EXTEST, SAMPLE/PRELOAD, and BYPASS) | . 1138 |

| 30.4  | Registe | er Descriptions                         | . 1140 |

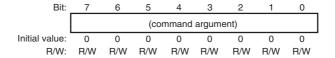

|       | 30.4.1  | Instruction Register (SDIR)             | . 1141 |

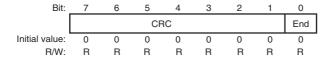

|       | 30.4.2  | Interrupt Source Register (SDINT)       | . 1142 |

|       | 30.4.3  | Bypass Register (SDBPR)                 | . 1142 |

|       | 30.4.4  | Boundary Scan Register (SDBSR)          | . 1143 |

| 30.5  | Operati | ion                                     | . 1152 |

|       | 30.5.1  | TAP Control                             | . 1152 |

|       | 30.5.2  | H-UDI Reset                             | . 1153 |

|       | 30.5.3  | H-UDI Interrupt                         | . 1153 |

| 30.6  | Usage l | Notes                                   | . 1154 |