# 16

# RL78/G1G Group

# Renesas Starter Kit User's Manual

RENESAS MCU RL78 Family / RL78/G1X Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corporation without notice. Please review the latest information published by Renesas Electronics Corporation through various means, including the Renesas Electronics Corporation website (http://www.renesas.com).

Renesas Electronics www.renesas.com

Rev. 1.00 Jan 2015

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

(Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority owned subsidiaries.

(Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

#### Disclaimer

By using this Renesas Starter Kit (RSK), the user accepts the following terms:

The RSK is not guaranteed to be error free, and the entire risk as to the results and performance of the RSK is assumed by the User. The RSK is provided by Renesas on an "as is" basis without warranty of any kind whether express or implied, including but not limited to the implied warranties of satisfactory quality, fitness for a particular purpose, title and non-infringement of intellectual property rights with regard to the RSK. Renesas expressly disclaims all such warranties. Renesas or its affiliates shall in no event be liable for any loss of profit, loss of data, loss of contract, loss of business, damage to reputation or goodwill, any economic loss, any reprogramming or recall costs (whether the foregoing losses are direct or indirect) nor shall Renesas or its affiliates be liable for any other direct or indirect special, incidental or consequential damages arising out of or in relation to the use of this RSK, even if Renesas or its affiliates have been advised of the possibility of such damages.

#### Precautions

The following precautions should be observed when operating any RSK product:

This Renesas Starter Kit is only intended for use in a laboratory environment under ambient temperature and humidity conditions. A safe separation distance should be used between this and any sensitive equipment. Its use outside the laboratory, classroom, study area or similar such area invalidates conformity with the protection requirements of the Electromagnetic Compatibility Directive and could lead to prosecution.

The product generates, uses, and can radiate radio frequency energy and may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment causes harmful interference to radio or television reception, which can be determined by turning the equipment off or on, you are encouraged to try to correct the interference by one or more of the following measures;

- ensure attached cables do not lie across the equipment

- reorient the receiving antenna

- increase the distance between the equipment and the receiver

- connect the equipment into an outlet on a circuit different from that which the receiver is connected

- power down the equipment when not in use

- consult the dealer or an experienced radio/TV technician for help NOTE: It is recommended that wherever

possible shielded interface cables are used.

The product is potentially susceptible to certain EMC phenomena. To mitigate against them it is recommended that the following measures be undertaken;

- The user is advised that mobile phones should not be used within 10m of the product when in use.

- The user is advised to take ESD precautions when handling the equipment.

The Renesas Starter Kit does not represent an ideal reference design for an end product and does not fulfil the regulatory standards for an end product.

## How to Use This Manual

#### 1. Purpose and Target Readers

This manual is designed to provide the user with an understanding of the RSK hardware functionality, and electrical characteristics. It is intended for users designing sample code on the RSK platform, using the many different incorporated peripheral devices.

The manual comprises of an overview of the capabilities of the RSK product, but does not intend to be a guide to embedded programming or hardware design. Further details regarding setting up the RSK and development environment can found in the tutorial manual.

Particular attention should be paid to the precautionary notes when using the manual. These notes occur within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. Refer to the text of the manual for details.

The following documents apply to the RL78/G1G Group. Make sure to refer to the latest versions of these documents. The newest versions of the documents listed may be obtained from the Renesas Electronics Web site.

| Document Type                     | Description                                                                                          | Document Title                                  | Document No.                                                 |

|-----------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------|

| User's Manual                     | Describes the technical details of the RSK hardware.                                                 | RSKRL78G1G<br>User's Manual                     | R20UT3022EG                                                  |

| Tutorial Manual                   | Provides a guide to setting up RSK environment,<br>running sample code and debugging programs.       | RSKRL78G1G<br>Tutorial Manual                   | CS+:<br>R20UT3019EG<br>e <sup>2</sup> studio:<br>R20UT3023EG |

| Quick Start Guide                 | Provides simple instructions to setup the RSK and run the first sample.                              | RSKRL78G1G<br>Quick Start Guide                 | CS+:<br>R20UT3020EG<br>e <sup>2</sup> studio:<br>R20UT3024EG |

| Code Generator<br>Tutorial Manual | Provides a guide to code generation and importing into the IDE (Integrated Development Environment). | RSKRL78G1G<br>Code Generator<br>Tutorial Manual | CS+:<br>R20UT3021EG<br>e <sup>2</sup> studio:<br>R20UT3025EG |

| Schematics                        | Full detail circuit schematics of the RSK.                                                           | RSKRL78G1G<br>Schematics                        | R20UT3017EG                                                  |

| Hardware Manual                   | Provides technical details of the RL78/G1G microcontroller.                                          | RL78/G1G Group<br>Hardware Manual               | R01UH0499EJ                                                  |

## 2. List of Abbreviations and Acronyms

| Abbreviation           | Full Form                                                                                                                                                                                |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC                    | Analog-to-Digital Converter                                                                                                                                                              |

| BC                     | Battery Charging                                                                                                                                                                         |

| bps                    | Bits per second                                                                                                                                                                          |

| CAN                    | Controller Area Network                                                                                                                                                                  |

| CPU                    | Central Processing Unit                                                                                                                                                                  |

| CRC                    | Cyclic Redundancy Check                                                                                                                                                                  |

| DAC                    | Digital-to-Analog Converter                                                                                                                                                              |

| DIP                    | Dual In-line Package                                                                                                                                                                     |

| DMA                    | Direct Memory Access                                                                                                                                                                     |

| DMAC                   | Direct Memory Access Controller                                                                                                                                                          |

| E1                     | Renesas On-chip Debugging Emulator                                                                                                                                                       |

| EEPROM                 | Electronically Erasable Programmable Read Only Memory                                                                                                                                    |

| EMC                    | Electromagnetic Compatibility                                                                                                                                                            |

| ESD                    | Electrostatic Discharge                                                                                                                                                                  |

| GPT                    | General PWM Timer                                                                                                                                                                        |

| I <sup>2</sup> C (IIC) | Philips™ Inter-Integrated Circuit Connection Bus                                                                                                                                         |

| IRQ                    | Interrupt Request                                                                                                                                                                        |

| LCD                    | Liquid Crystal Display                                                                                                                                                                   |

| LED                    | Light Emitting Diode                                                                                                                                                                     |

| LIN                    | Local Interconnect Network                                                                                                                                                               |

| MCU                    | Micro-controller Unit                                                                                                                                                                    |

| MTU                    | Multi-Function Timer Pulse Unit                                                                                                                                                          |

| n/a (NA)               | Not applicable                                                                                                                                                                           |

| n/c (NC)               | Not connected                                                                                                                                                                            |

| NMI                    | Non-maskable Interrupt                                                                                                                                                                   |

| OTG                    | On The Go™                                                                                                                                                                               |

| PC                     | Personal Computer                                                                                                                                                                        |

| PDC                    | Parallel Data Capture Unit                                                                                                                                                               |

| PLL                    | Phase Locked Loop                                                                                                                                                                        |

| Pmod™                  | This is a Digilent Pmod <sup>™</sup> Compatible connector. Pmod <sup>™</sup> is registered to Digilent Inc.<br><u>Digilent-Pmod Interface Specification</u> (Link valid at 14 Apr, 2014) |

| POE                    | Port Output Enable                                                                                                                                                                       |

| PWM                    | Pulse Width Modulation                                                                                                                                                                   |

| RAM                    | Random Access Memory                                                                                                                                                                     |

| ROM                    | Read Only Memory                                                                                                                                                                         |

| RSK                    | Renesas Starter Kit                                                                                                                                                                      |

| RTC                    | Realtime Clock                                                                                                                                                                           |

| SAU                    | Serial Array Unit                                                                                                                                                                        |

| SCI                    | Serial Communications Interface                                                                                                                                                          |

| SFR                    | Special Function Registers                                                                                                                                                               |

| SPI                    | Serial Peripheral Interface                                                                                                                                                              |

| SSI                    | Serial Sound Interface                                                                                                                                                                   |

| TAU                    |                                                                                                                                                                                          |

|                        | Timer Array Unit<br>Thin Film Transistor                                                                                                                                                 |

| TFT                    |                                                                                                                                                                                          |

| TPU                    | Timer Pulse Unit                                                                                                                                                                         |

| UART                   | Universal Asynchronous Receiver/Transmitter                                                                                                                                              |

| USB                    | Universal Serial Bus                                                                                                                                                                     |

| WDT                    | Watchdog timer<br>gistered trademarks are the property of their respective owners.                                                                                                       |

All trademarks and registered trademarks are the property of their respective owners.

## Table of Contents

| 1. O       | Dverview                                | 7                                       |

|------------|-----------------------------------------|-----------------------------------------|

| 1.1        | Purpose                                 | 7                                       |

| 1.2        | Features                                |                                         |

| 1.3        | Board specification                     |                                         |

| ~ ¬        |                                         | 0                                       |

|            | ower Supply                             |                                         |

| 2.1        | Requirements                            |                                         |

| 2.2        | Power-Up Behaviour                      | 8                                       |

| 3 B        | oard Layout                             | 9                                       |

| 3.1        | Component Layout                        | 9                                       |

| 3.2        | Board Dimensions                        |                                         |

| 3.2<br>3.3 | Component Placement                     |                                         |

| 0.0        |                                         |                                         |

|            | connectivity                            | 13                                      |

| 4.1        | Internal RSK Connections                |                                         |

| 4.2        | Debugger Connections                    | 14                                      |

| 5 11       | lser Circuitry                          | 15                                      |

| 5.0<br>5.1 | Reset Circuit                           |                                         |

| 5.1<br>5.2 |                                         |                                         |

| -          | Clock Circuit                           |                                         |

| 5.3        | Switches                                |                                         |

| 5.4        | LEDs                                    |                                         |

| 5.5        | Potentiometer                           |                                         |

| 5.6        | Pmod <sup>™</sup>                       |                                         |

| 5.7        | USB Serial Port                         |                                         |

| 5.8        | Simplified I <sup>2</sup> C             |                                         |

|            | configuration                           | 10                                      |

|            | Configuration                           |                                         |

| 6.1        | Modifying the RSK                       |                                         |

| 6.2        | Power Supply Configuration              |                                         |

| 6.3        | Clock Configuration                     |                                         |

| 6.4        | ADC & PGA & Comparator Configuration    | 21                                      |

| 6.5        | General I/O & LED Configuration         | 21                                      |

| 6.6        | I <sup>2</sup> C & EEPROM Configuration |                                         |

| 6.7        | IRQ Configuration                       |                                         |

| 6.8        | Timer Configuration                     |                                         |

| 6.9        | PMOD1 Interface Configuration           |                                         |

| 6.10       | PMOD2 Interface Configuration           |                                         |

| 6.11       | Serial & USB to Serial Configuration    |                                         |

|            |                                         |                                         |

|            | leaders                                 |                                         |

| 7.1        | Application Headers                     | 27                                      |

| 7.2        | Microcontroller Pin Headers             |                                         |

| 8. C       | ode Development                         | 33                                      |

| 8.1        | Overview                                |                                         |

| 8.2        | Compiler Restrictions                   |                                         |

|            |                                         |                                         |

| 8.3        | Mode Support                            |                                         |

| 8.4        | Debugging Support                       |                                         |

| 8.5        | Address Space                           |                                         |

| 9 A        | dditional Information                   | 34                                      |

| 5.70       |                                         | ••••••••••••••••••••••••••••••••••••••• |

# RENESAS

#### RSKRL78G1G

RENESAS STARTER KIT

#### 1.1 Purpose

This RSK is an evaluation tool for Renesas microcontrollers. This manual describes the technical details of the RSK hardware. The Quick Start Guide and Tutorial Manual provide details of the software installation and debugging environment.

#### 1.2 Features

This RSK provides an evaluation of the following features:

- Renesas microcontroller programming

- User code debugging

- User circuitry such as switches, LEDs and a potentiometer

- Sample application

- Sample peripheral device initialisation code

The RSK board contains all the circuitry required for microcontroller operation.

#### **1.3 Board specification**

Board specification was shown in **Table 1-1** below.

| Item                          | Specification                                              |  |

|-------------------------------|------------------------------------------------------------|--|

|                               | Part No : R5F11EFAAFP                                      |  |

| Microcontroller               | Package : 44-pin LQFP                                      |  |

|                               | On-Chip Memory : ROM 16KB, RAM 1.5KB                       |  |

| On-Board Memory               | I <sup>2</sup> C EEPROM : 16Kbit                           |  |

| Input Clock                   | RL78/G1G Main : 20MHz                                      |  |

| Input Clock                   | RL78/G1C Main: 12MHz                                       |  |

| Power Supply <sup>*1</sup>    | DC Power Jack : 5 V Input                                  |  |

| Fower Supply                  | Power IC: 5Vinput, 3.3V output                             |  |

| Debug Interface               | E1 14-pin box header                                       |  |

| Push Switch                   | Reset Switch x 1                                           |  |

| Fush Switch                   | User Switch x 3                                            |  |

| Potentiometer (for ADC)       | Single-turn, 10kΩ                                          |  |

| LED                           | Power indicator: green x 1                                 |  |

| EED                           | User : green x 1, orange x 1, red x 2                      |  |

| USB to Serial Converter       | Connector : USB-MiniB                                      |  |

| Interface                     | Driver : RL78/G1C Microcontroller (Part No R5F10JBCANA)    |  |

| Pmod <sup>™</sup>             | PMOD1 : Angle type, 12-pin Connector                       |  |

| i mou                         | PMOD2 : Straight type, 12-pin Connector                    |  |

| Application Board Interface 2 | 2.54mm pitch, 26-pin x 2 (JA1, JA2), 24-pin x 2 (JA5, JA6) |  |

#### Table 1-1: Board Specifications

<sup>1</sup>: Board can also supply 5V into RL78/G1G microcontroller without LDO regulator.

<sup>\*2</sup>: The connector is not included to a product.

Open

#### 2. **Power Supply**

#### 2.1 Requirements

This RSK is supplied with an E1 debugger. The debugger is able to power the RSK board with up to 200mA. When the RSK is connected to another system then that system should supply power to the RSK. This board has an optional centre positive supply connector using a barrel power jack.

Details of the external power supply requirements for the RSK, and configuration are shown in Table 2-2 below. The default RSK power configuration is shown in Bold, blue text.

| Connector | Supply voltage |

|-----------|----------------|

| PWR       | 5VDC Input     |

|                  |                                                 | licitis  |                     |

|------------------|-------------------------------------------------|----------|---------------------|

| J14 Setting *    | Supply Source                                   | Board_5V | Board_VDD<br>UC_VDD |

| Pin1-2 shorted   | PWR Connector/CON_5V/Unregulated_VDD<br>/E1(5V) | 5V       | 5V                  |

| Pin2-3 shorted   | PWR Connector/CON_5V/Unregulated_VDD            | 5V       | 3.3V                |

| (or R116 Fitted) | CON_3V3/E1(3V3)                                 | n/a      | 3.3V                |

Table 2-1: PWR connector Requirements

Table 2-2: Main Power Supply Requirements

DO NOT SET

DO NOT SET

\* By default, jumper J14 is not fitted to the RSK. R116 is fitted by default and becomes the same setting as 'J14 Pin2-3 shorted'.

The main power supply connected to PWR1 should supply a minimum of 5W to ensure full functionality.

#### 2.2 **Power-Up Behaviour**

DO NOT SET

When the RSK is purchased, the RSK board has the 'Release' build of the example tutorial software preprogrammed into the Renesas microcontroller. Please consult the 'Renesas Starter Kit Code Generator Tutorial Manual' for further information of this example.

## 3. Board Layout

#### 3.1 Component Layout

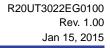

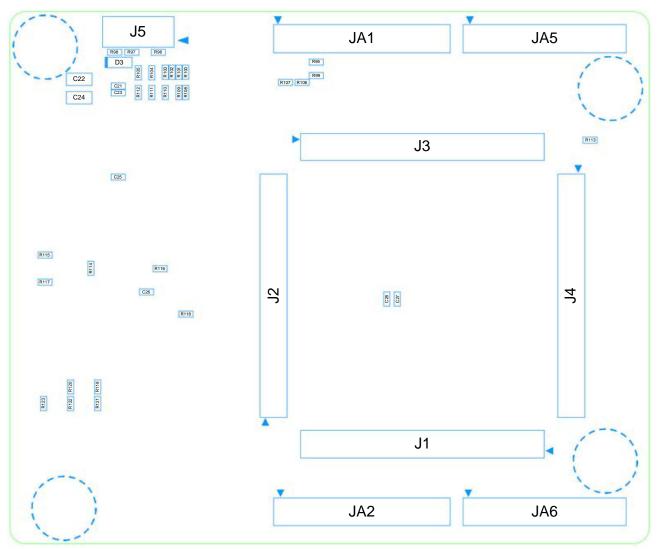

Figure 3-1 below shows the top component layout of the board.

Figure 3-1: Board Layout

#### 3.2 Board Dimensions

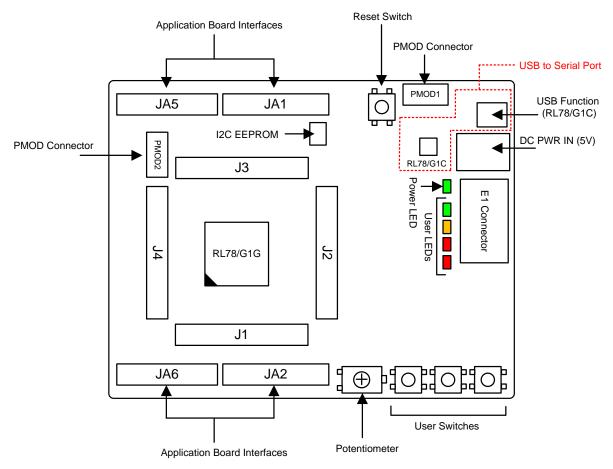

**Figure 3-2** below gives the board dimensions and connector positions. All the through-hole connectors are on a common 0.1 inch grid for easy interfacing.

Figure 3-2: Board Dimensions

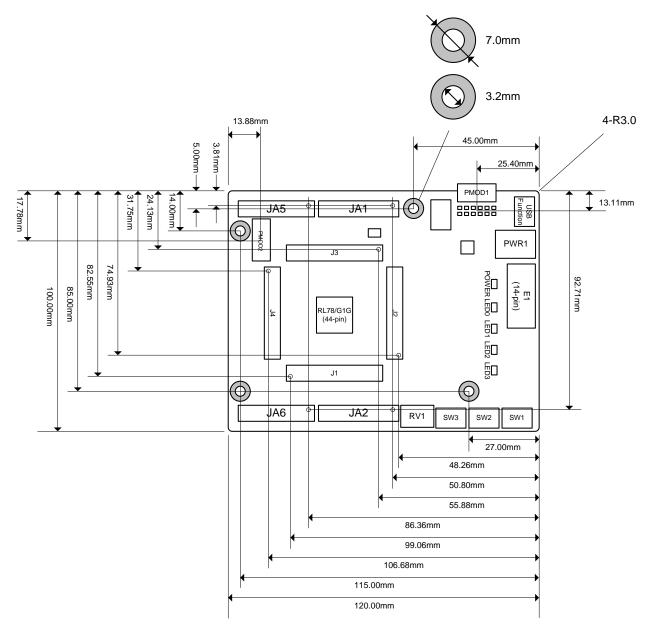

#### 3.3 Component Placement

**Figure 3-2** below shows placement of individual components on the top-side PCB – bottom-side component placement can be seen in **Figure 3-4**. Component types and values can be looked up using the board schematics.

Figure 3-3: Top-Side Component Placement

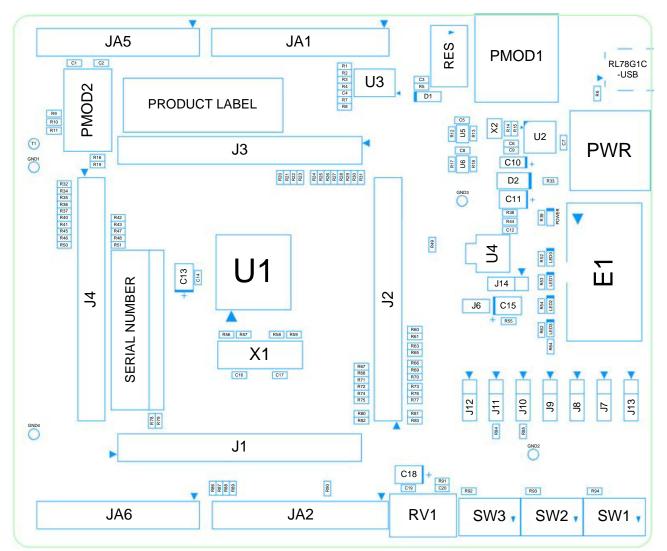

Figure 3-4 below shows the component placement on the bottom-side of the RSK board.

Figure 3-4: Bottom-Side Component Placement

## 4. Connectivity

#### 4.1 Internal RSK Connections

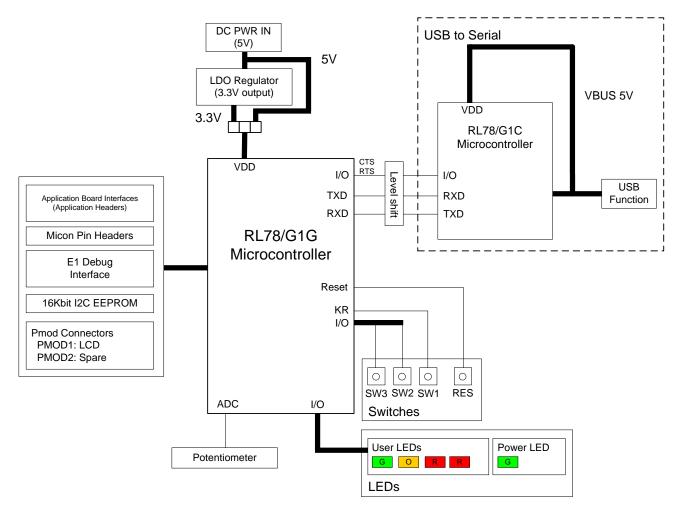

The diagram below shows the RSK board components and their connectivity to the MCU.

Figure 4-1: Internal RSK Block Diagram

#### 4.2 Debugger Connections

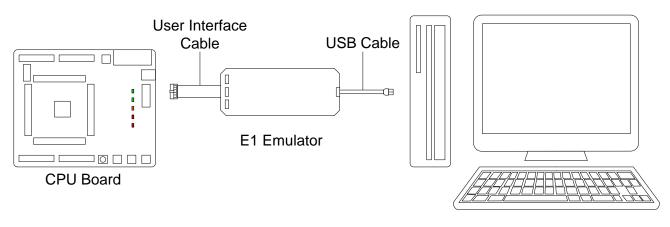

The diagram below shows the connections between the RSK, E1 debugger and the host PC.

Host PC

Figure 4-2: Debugger Connection Diagram

## 5. User Circuitry

#### 5.1 Reset Circuit

A reset control circuit is not fitted to the RSK, as the MCU is capable of voltage and power-on detection. Resets are handled internally, and the reset switch is connected directly to the RESET pin on the MCU.

#### 5.2 Clock Circuit

A clock circuit is fitted to the RSK to generate the required clock signal to drive the MCU, and associated peripherals. Refer to the RL78/G1G Group Hardware Manual for details regarding the clock signal requirements, and the RSKRL78/G1G board schematics for information regarding the clock circuitry in use on the RSK. Details of the oscillators fitted to the board are listed in **Table 5-1** below.

| Crystal | Function                      | Default Placement | Frequency | Device Package    |

|---------|-------------------------------|-------------------|-----------|-------------------|

| X1      | Main MCU crystal for RL78/G1G | Fitted            | 20MHz     | Encapsulated, SMT |

| X2      | Main MCU crystal for RL78/G1C | Fitted            | 12MHz     | Encapsulated, SMT |

Table 5-1: Oscillators

#### 5.3 Switches

There are four switches located on the RSK board. The function of each switch and its connection is shown in **Table 5-2**. For further information regarding switch connectivity, refer to the RSK schematics.

| Switch | Function                                            | MCU      |     |  |

|--------|-----------------------------------------------------|----------|-----|--|

| Switch | Switch                                              |          | Pin |  |

| RES    | When pressed, the microcontroller is reset          | RESETn   | 3   |  |

| SW1    | Connects to a key return input for user controls    | KR0(P70) | 20  |  |

| SW2    | Connects to a general purpose I/O for user controls | P124     | 4   |  |

| SW3    | Connects to a general purpose I/O for user controls | P123     | 5   |  |

#### Table 5-2: Switch Connections

#### 5.4 LEDs

There are five LEDs on the RSK. The function of each LED, its colour, and its connections are shown in **Table 5-3**.

| LED   | Colour              | Function                   | MCU  |     |  |

|-------|---------------------|----------------------------|------|-----|--|

| LED   | LED Colour Function |                            | Port | Pin |  |

| POWER | Green               | Indicates the power status | -    | -   |  |

| LED0  | Green               | User operated LED          | P41  | 1   |  |

| LED1  | Orange              | User operated LED          | P63  | 15  |  |

| LED2  | Red                 | User operated LED          | P72  | 18  |  |

| LED3  | Red                 | User operated LED          | P73  | 17  |  |

#### Table 5-3: LED Connections

#### 5.5 Potentiometer

A single-turn potentiometer is connected as a potential divider to analog input ANI0 (Port P20, Pin 41).

The potentiometer is fitted to offer an easy method of supplying a variable analog input to the microcontroller. It does not necessarily reflect the accuracy of the controller's ADC. Refer to the device User's Manual: Hardware for further details.

#### 5.6 Pmod<sup>™</sup>

A Pmod<sup>™</sup> Compatible debug LCD module is supplied with the RSK, and should be connected to the PMOD1 header.

Care should be taken when installing the LCD module to ensure pins are not bent or damaged. The LCD module is vulnerable to electrostatic discharge (ESD); therefore appropriate ESD protection should be used.

The Digilent Pmod<sup>™</sup> Compatible header uses a SPI interface. Some RSKs will be provided with a monochrome display, others will have a colour display. Code for the appropriate display will be included in the product software support. Connection information for the Digilent Pmod<sup>™</sup> Compatible header is provided in **Table 5-4 and Table 5-5** below.

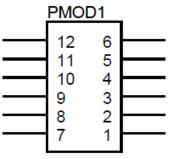

Please note that the connector numbering adheres to the Digilent Pmod<sup>™</sup> standard and is different from all other connectors on the RSK designs. Details can be found in the Digilent Pmod<sup>™</sup> Interface Specification Revision: November 20, 2011

Figure 5-1: Digilent Pmod<sup>™</sup> Compatible Header Pin Numbering

|     | Digilent Pmod™ Compatible Header Connections (PMOD1) |                                           |      |         |                  |     |    |  |

|-----|------------------------------------------------------|-------------------------------------------|------|---------|------------------|-----|----|--|

|     |                                                      | Circuit Net Name MCU Pin Circuit Net Name | CU   |         | Circuit Not Nome | MCU |    |  |

| Pin | Circuit Net Name                                     |                                           | Port | Pin     |                  |     |    |  |

| 1   | P62                                                  | P62                                       | 14   | 7       | P-INTP4          | P31 | 16 |  |

| 2   | 2 P-SO00_TxD0 P51                                    | DE1                                       | 23   | 8       | P71              | P71 | 19 |  |

| 2   |                                                      | 23 0                                      | 0    | P-INTP5 | P16              | 25  |    |  |

| 3   | P-SI00_RxD0                                          | P50                                       | 22   | 9       | P61              | P61 | 13 |  |

| 4   | P-SCK00                                              | P30                                       | 21   | 10      | P60              | P60 | 12 |  |

| 5   | GROUND                                               | -                                         | -    | 11      | GROUND           | -   | -  |  |

| 6   | Board_3V3                                            | -                                         | -    | 12      | Board_3V3        | -   | -  |  |

Table 5-4: Pmod<sup>™</sup>1 Header Connections (PMOD1)

|                 | Digilent Pmod™ Compatible Header Connections (PMOD2) |      |        |    |                  |      |     |    |

|-----------------|------------------------------------------------------|------|--------|----|------------------|------|-----|----|

| Pin Circuit Net | Circuit Net Name                                     | MCU  | CU Pin |    |                  | MCU  |     |    |

| FIII            | Circuit Net Name                                     | Port | Pin    |    | Circuit Net Name | Port | Pin |    |

| 1               | P17                                                  | P17  | 24     | 7  | P-INTP4          | P31  | 16  |    |

| 2               | 2 P-SO00_TxD0 P5                                     |      | D51    | 23 | 8                | P27  | P27 | 34 |

| 2               |                                                      | FJI  | 23     | 0  | P-INTP0          | P137 | 6   |    |

| 3               | P-SI00_RxD0                                          | P50  | 22     | 9  | P146             | P146 | 32  |    |

| 4               | P-SCK00                                              | P30  | 21     | 10 | P147             | P147 | 33  |    |

| 5               | GROUND                                               | -    | -      | 11 | GROUND           | -    | -   |    |

| 6               | Board_3V3                                            | -    | -      | 12 | Board_3V3        | -    | -   |    |

Table 5-5: Pmod<sup>™</sup>2 Header Connections (PMOD2)

#### 5.7 USB Serial Port

A USB serial port implemented in another Renesas low power microcontroller (RL78/G1C) is fitted on the RSK to the microcontroller UART1. Multiple options are provided to allow re-use of the serial interface. Connections between the USB to Serial converter and the microcontroller are listed in **Table 5-6** below.

| Serial Signal             | Function                       | MCU  |     |  |

|---------------------------|--------------------------------|------|-----|--|

| Senai Signai              |                                |      | Pin |  |

| A-SO00_TxD0 <sup>*1</sup> | UART0 Transmit Signal          | P51  | 23  |  |

| A-SI00_RxD0 <sup>*1</sup> | UART0 Receive Signal           | P50  | 22  |  |

| TxD1                      | UART1 Transmit Signal          | P00  | 43  |  |

| RxD1                      | UART1 Receive Signal           | P01  | 42  |  |

| RS232TX <sup>*1</sup>     | External RS232 Transmit Signal | -    | -   |  |

| RS232RX <sup>*1</sup>     | External RS232 Receive Signal  | -    | -   |  |

| RL78G1C_CTS <sup>*2</sup> | Clear To Send                  | P146 | 32  |  |

| RL78G1C_RTS <sup>*2</sup> | Request to Send                | P147 | 33  |  |

**Table 5-6: Serial Port Connections**

<sup>\*1</sup>: This connection is a not available in the default RSK configuration - refer to §6 for the required modifications.

<sup>\*2</sup>: CTS & RTS control is not supported on this RSK.

When the RSK board is first connected to a PC running Windows with the USB/Serial connection, the PC will look for a driver. This driver is installed during the installation process, so the PC should be able to find it. The PC will report that it is installing for a driver and then report that a driver has been installed successfully, as shown in **Figure 5-2**. The exact messages may vary depending upon operating system.

| Installing device driver software * ×<br>Click here for status. | <b>&gt;</b> 1             | RSK USB Serial Port (COM3) 🌂 🗙<br>Device driver software installed successfully. |

|-----------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------|

| •                                                               |                           | · .                                                                              |

| Figure 5-2: US                                                  | B-Serial Windows Installa | tion message                                                                     |

### 5.8 Simplified I<sup>2</sup>C

The RL78/G1G features one Simplified  $I^2C$  interface modules. IIC00 is connected to a 16Kbit EEPROM (Electronically-Erasable Programmable Read Only Memory). Specific details of the EEPROM device and the connections can be found in the board schematics.

On board EEPROM only supports single device on bus. To allow external  $I^2C$  device, option links have to be modified – refer to §6 for further details.

## 6. Configuration

#### 6.1 Modifying the RSK

This section lists the option links that are used to modify the way RSK operates in order to access different configurations. Configurations are made by modifying link resistors or headers with movable jumpers or by configuration DIP switches

A link resistor is a  $0\Omega$  surface mount resistor, which is used to short or isolate parts of a circuit. Option links are listed in the following sections, detailing their function when fitted or removed. **Bold, blue text** indicates the default configuration that the RSK is supplied with. Refer to the component placement diagram (§3) to locate the option links, jumpers and DIP switches.

When removing soldered components, always ensure that the RSK is not exposed to a soldering iron for intervals greater than 5 seconds. This is to avoid damage to nearby components mounted on the board.

When modifying a link resistor, always check the related option links to ensure there is no possible signal contention or short circuits. Because many of the MCU's pins are multiplexed, some of the peripherals must be used exclusively. Refer to the RL78/G1G Group Hardware Manual and RSKRL78G1G schematics for further information.

#### 6.2 Power Supply Configuration

Table 6-1 and Table 6-2 below details the function of the option links associated with power supply configuration.

| Reference         | Explanation                                 | Fit  | DNF  | Related Ref. |

|-------------------|---------------------------------------------|------|------|--------------|

| Board_5V          | Connects PWR to Board_5V                    | R33  | -    | U4.IN        |

| (PWR Connector)   | Disconnects PWR from Board_5V               | -    | R33  | U4.IN        |

| Board_5V          | Connects CON_5V to Board_5V                 | R38  | -    | U4.IN, JA1   |

| (CON_5V)          | Disconnects CON_5V from Board_5V            | -    | R38  | U4.IN, JA1.1 |

| Board_5V          | Connects Unregulated_VDD to Board_5V        | R44  | -    | JA6.23       |

| (Unregulated_VDD) | Disconnects Unregulated_VDD from Board_5V   | -    | R44  | JA6.23       |

| Board_VDD         | Connects Regulator output to Board_VDD      | R116 | -    | -            |

| (U4)              | Disconnects Regulator output from Board_VDD | -    | R116 | -            |

| Board_VDD         | Connects CON_3V3 to Board_VDD               | R55  | -    | JA1.3        |

| (CON_3V3)         | Disconnects CON_3V3 from Board_VDD          | -    | R55  | JA1.3        |

| Board_VDD         | Connects Board_3V3 to Board_VDD             | R49  | -    | PMOD1, PMOD2 |

| (Board_3V3)       | Disconnects Board_3V3 from Board_VDD        | -    | R49  | PMOD1, PMOD2 |

| Board_VDD         | Connects Board_VDD to UC_VDD                | R118 | -    | U1(VDD)      |

| (UC_VDD)          | Disconnects Board_VDD from UC_VDD           | -    | R118 | U1(VDD)      |

Table 6-1: Power Supply Option Links (1)

| Reference | Jumper Position | Explanation                                        | Related Ref. |

|-----------|-----------------|----------------------------------------------------|--------------|

|           | Shorted Pin1-2  | Connects 5V power rail to Board_VDD                | -            |

| J14 *1    | Shorted Pin2-3  | Connects Regulator output to Board_VDD             | R116         |

|           | All open        | DO NOT SET                                         | -            |

| 1/ *2     | Shorted Pin1-2  | Connects Board_VDD to UC_VDD                       | R118         |

| J6 *2     | All open        | Enables current probe for MCU current consumption. | -            |

Table 6-2: Power Supply Option Links (2)

<sup>\*1</sup>: By default, jumper J14 is not fitted to the RSK. R116 is fitted by default and becomes the same setting as 'J14 Shorted Pin2-3'.

<sup>\*2</sup>: By default, jumper J6 is not fitted to the RSK. R118 is fitted by default and becomes the same setting as 'J6 Shorted Pin1-2'.

#### 6.3 Clock Configuration

**Table 6-3** below details the function of the option links associated with clock configuration.

| Reference   | Explanation                       | Fit      | DNF      | Related Ref. |

|-------------|-----------------------------------|----------|----------|--------------|

| X1, CON_X1, | Connects crystal (X1) to RL78/G1G | R57, R58 | R59, R56 | U1(X1, X2)   |

| CON_EXTAL   | Connects CON_EXTAL to RL78/G1G.   | R56      | R57, R58 | U1(EXTAL)    |

Table 6-3: Clock Option Links

#### 6.4 ADC & PGA & Comparator Configuration

**Table 6-4** below details the function of the option links associated with ADC, PGA (Programmable Gain Amplifiers) and Comparator configuration.

|                 | Ν           | ICU | MCU F  | eripheral Se | election              | De                     | stination Selec  | tion                     |          |               |                          |                          |

|-----------------|-------------|-----|--------|--------------|-----------------------|------------------------|------------------|--------------------------|----------|---------------|--------------------------|--------------------------|

| Signal name     | Signal name |     | Signal | Fit          | DNF                   | Interface<br>/Function | Fit              | DNF                      |          |               |                          |                          |

|                 |             |     | TI00   | R47          | R48, <mark>R51</mark> | JA2.21                 | -                | -                        |          |               |                          |                          |

| TI00_TxD1_CMP0P | 43          | P00 | TxD1   | R48          | R47, R51              | JA6.8<br>U5.3          | -<br>R122/J7.2-3 | -<br>J7.1-2, <b>R120</b> |          |               |                          |                          |

|                 |             |     | CMP0P  | R51          | <b>R47</b> , R48      | JA6.20                 | -                | -                        |          |               |                          |                          |

|                 |             |     | TO00   | R45          | R46, <b>R50</b>       | JA2.19                 | -                | -                        |          |               |                          |                          |

| TO00_RxD1_PGA   | 42          | P01 | P01    | P01          | P01                   | P01                    | RxD1             | R46                      | R45, R50 | JA6.7<br>U6.4 | -<br><b>R121</b> /J8.2-3 | -<br>J8.1-2, <b>R119</b> |

|                 |             |     | PGA    | R50          | <b>R45</b> , R46      | JA2.24                 | R88              | R87                      |          |               |                          |                          |

|                 |             |     | AVREFP | R42          | R43                   | JA1.7                  | -                | -                        |          |               |                          |                          |

| ANIO_AVREFP     | 41          | P20 | ANIO   | R43          | R42                   | JA1.9<br>RV1           | -<br>R91         | -                        |          |               |                          |                          |

|                 | 10          | D21 | ANI1   | R40          | R41                   | JA1.10                 | -                | -                        |          |               |                          |                          |

| ANI1_AVREFM     | 40 P21      |     | AVREFM | R41          | R40                   | JA1.6                  | -                | -                        |          |               |                          |                          |

| P27 ANI7        | 34          | P27 | P27    | R34          | R32                   | PMOD2.8                | R35              | R36                      |          |               |                          |                          |

| _               |             |     | ANI7   | R32          | R34                   | JA5.4                  | -                | -                        |          |               |                          |                          |

Table 6-4: ADC & PGA & Comparator Option Links

#### 6.5 General I/O & LED Configuration

**Table 6-5** below details the function of the option links associated with General I/O and LED configuration.

|              | M               | CU   | MCU    | Peripheral Se | lection         | Destination            | n Selection |     |

|--------------|-----------------|------|--------|---------------|-----------------|------------------------|-------------|-----|

| Signal name  | Pin             | Port | Signal | Fit           | DNF             | Interface<br>/Function | Fit         | DNF |

| P60 100      | 12              | P60  | P60    | R81           | R83             | PMOD1.10               | -           | -   |

| P00_100      | <b>0_</b> 100   | POU  | 100    | R83           | R81             | JA1.15                 | -           | -   |

| D(1 101      | 13              | P61  | P61    | R82           | R80             | PMOD1.9                | -           | -   |

| P61_I01      |                 | POI  | 101    | R80           | R82             | JA1.16                 | -           | -   |

|              |                 |      | P62    | R73           | R76, R77        | PMOD1.1                | -           | -   |

| P62_IO2_M1UD | P62 IO2 M1UD 14 | P62  | 102    | R76           | R73, <b>R77</b> | JA1.17                 | -           | -   |

|              |                 |      | M1UD   | R77           | R73, <b>R76</b> | JA2.11                 | -           | -   |

|              | 15              | D42  | LED1   | R75           | R74             | LED1                   | -           | -   |

| LED1_IO3     | 15              | P63  | 103    | R74           | R75             | JA1.18                 | -           | -   |

| CIM1 104     | 20              | D70  | SW1    | R60           | R61             | SW1                    | -           | -   |

| SW1_IO4      | 20              | P70  | IO4    | R61           | R60             | JA1.19                 | -           | -   |

| D71 105      | 10              | D71  | P71    | R68           | R67             | PMOD1.8                | R24         | R25 |

| P71_IO5      | 19              | P71  | 105    | R67           | R68             | JA1.20                 | -           | -   |

|              | 10              | D72  | LED2   | R63           | R65             | LED2                   | -           | -   |

| LED2_IO6     | 18              | P72  | 106    | R65           | R63             | JA1.21                 | -           | -   |

|              | 17              | D72  | LED3   | R72           | R71             | LED3                   | -           | -   |

| LED3_107     | 17              | P73  | 107    | R71           | R72             | JA1.22                 | -           | -   |

#### Table 6-5: General I/O & LED Option Links

### 6.6 I<sup>2</sup>C & EEPROM Configuration

Table 6-6 and Table 6-7 below details the function of the option links associated with  $I^2C$  and EEPROM configuration.

|                                         | N   | ICU  | MC          | U Periphera | al Selection | Destin                 | ation Select | ion    |

|-----------------------------------------|-----|------|-------------|-------------|--------------|------------------------|--------------|--------|

| Signal name                             | Pin | Port | Signal      | Fit         | DNF          | Interface<br>/Function | Fit          | DNF    |

|                                         |     |      | SCL00       | J9.1-2      | J10.Open     | U3.6                   | R3           | -      |

|                                         |     |      | 3CL00       | J9.1-Z      | J 10.0pen    | JA1.26                 | -            | R3     |

| SCL00_P-SCK00_A-<br>SCK00_INTP3         | 21  | P30  | P-SCK00     | J9.2-3      | J10.Open     | PMOD1.4,               |              |        |

|                                         | 21  | F 30 |             |             | J 10.0pen    | PMOD2.4                | -            | -      |

|                                         |     |      | A-SCK00     | J10.1-2     | J9.Open      | JA2.10                 | -            | -      |

|                                         |     |      | INTP3       | J10.2-3     | J9.Open      | JA1.23                 | -            | -      |

|                                         |     |      | SDA00       | J11.1-2     | 112 Onon     | U3.5                   | R2           | -      |

|                                         |     |      |             |             | J12.Open     | JA1.25                 | -            | R2     |

|                                         |     |      | INTP1       | J11.2-3     | J12.Open     | JA2.7                  | -            | -      |

|                                         |     |      |             | 110.1.0     | 111 0        | PMOD1.3,               |              |        |

| SDA00_P-SI00_RxD0_A-<br>SI00_RxD0_INTP1 | 22  | P50  | P-SI00_RxD0 | J12.1-2     | J11.Open     | PMOD2.3                | -            | -      |

|                                         |     |      |             |             |              | JA2.8                  | -            | -      |

|                                         |     |      | A-SI00_RxD0 | 11222       | 111 Open     |                        |              | J8.2-3 |

|                                         |     |      |             | J12.2-3     | J11.Open     | U6.4                   | J8.1-2       | /R121, |

|                                         |     |      |             |             |              |                        |              | R119   |

#### Table 6-6: I<sup>2</sup>C & EEPROM Option Links (1)

| Reference          | MCU Periph                              | eral Selection      |           | Destination Selection |

|--------------------|-----------------------------------------|---------------------|-----------|-----------------------|

| Reference          | Function                                | Fit                 | DNF       | Interface/Function    |

| SDA00 (JA1_SDA00), | Operates with Board_VDD                 | R7                  | R8        | U3, JA1.25, JA1.26    |

| SCL00 (JA1_SCL00), | Operates with Board_5V                  | R8                  | R7        | U3, JA1.25, JA1.26    |

| SDA00, SCL00       | Enable EEPROM Write Protection          | R106                | -         | U3                    |

| SDAUU, SCLUU       | <b>Disables EEPROM Write Protection</b> | -                   | R106      | U3                    |

|                    | Table 6-7: I <sup>2</sup> C & EEP       | <b>ROM Option I</b> | Links (2) |                       |

#### 6.7 IRQ Configuration

|                         | Ν   | ACU  | MCU Pe      | ripheral Se | election              | Destina                | tion Selectio | n                   |

|-------------------------|-----|------|-------------|-------------|-----------------------|------------------------|---------------|---------------------|

| Signal name             | Pin | Port | Signal      | Fit         | DNF                   | Interface<br>/Function | Fit           | DNF                 |

|                         |     |      | P-INTP5     | R27         | R28, R29              | PMOD1.8                | R25           | R24                 |

| P-INTP5_A-INTP5_TRDIOC0 | 25  | P16  | A-INTP5     | R29         | R27, R28              | JA2.23                 | -             | -                   |

|                         |     |      | TRDIOC0     | R28         | R27, R29              | JA6.13                 | -             | -                   |

|                         |     |      |             | 10 1 0      | 110.0                 | U3.6                   | R3            | -                   |

|                         |     |      | SCL00       | J9.1-2      | J10.Open              | JA1.26                 | -             | R3                  |

| SCL00_P-SCK00_A-        | 21  | P30  | P-SCK00     | J9.2-3      | J10.Open              | PMOD1.4, PMOD2.4       | -             | -                   |

| SCK00_INTP3             |     |      | A-SCK00     | J10.1-2     | J9.Open               | JA2.10                 | -             | -                   |

|                         |     |      | INTP3       | J10.2-3     | J9.Open               | JA1.23                 | -             | -                   |

|                         |     |      | P-INTP4     | R66         |                       | PMOD1.7                | -             | -                   |

|                         | 17  | P31  |             |             | R69, <mark>R70</mark> | PMOD2.7                | R100          | -                   |

| P-INTP4_A-INTP4_TO03    | 16  |      | A-INTP4     | R69         | R66, R70              | JA2.9                  | -             | -                   |

|                         |     |      | TO03        | R70         | <b>R66</b> , R69      | JA2.20                 | -             | -                   |

|                         |     |      | 00400       | 111 1 0     | 140.0                 | U3.5                   | R2            | -                   |

|                         |     |      | SDA00       | J11.1-2     | J12.Open              | JA1.25                 | -             | R2                  |

|                         |     |      | INTP1       | J11.2-3     | J12.Open              | JA2.7                  | -             | -                   |

| SDA00_P-SI00_RxD0_A-    | 22  | P50  | P-SI00_RxD0 | J12.1-2     | J11.Open              | PMOD1.3, PMOD2.3       | -             | -                   |

| SI00_RxD0_INTP1         |     |      |             |             |                       | JA2.8                  | -             | -                   |

|                         |     |      | A-SI00_RxD0 | J12.2-3     | J11.Open              | U6.4                   | J8.1-2        | J8.2-3/R121<br>R119 |

|                         | /   | D107 | P-INTP0     | R78         | R79                   | PMOD2.8                | R36           | R35                 |

| P-INTP0_A-INTP0         | 6   | P137 | A-INTP0     | R79         | R78                   | JA2.24                 | R87           | R88                 |

Table 6-8 below details the function of the option links associated with the IRQ configuration.

Table 6-8: IRQ Option Links

#### 6.8 Timer Configuration

Table 6-9 below details the function of the option links associated with Timer configuration.

|                         | Ν   | /ICU | MCU P   | eripheral S | election              | D                      | estination Selec | tion                |

|-------------------------|-----|------|---------|-------------|-----------------------|------------------------|------------------|---------------------|

| Signal name             | Pin | Port | Signal  | Fit         | DNF                   | Interface<br>/Function | Fit              | DNF                 |

|                         |     |      | TI00    | R47         | R48, <b>R51</b>       | JA2.21                 | -                | -                   |

|                         | 43  | P00  | TxD1    | R48         | R47, R51              | JA6.8                  | -                | -                   |

| TI00_TxD1_CMP0P         | 43  | P00  | IXDI    | <b>K40</b>  | K47, KOT              | U5.3                   | R122/J7.2-3      | J7.1-2, <b>R120</b> |

|                         |     |      | CMP0P   | R51         | <b>R47</b> , R48      | JA6.20                 | -                | -                   |

|                         |     |      | TO00    | R45         | R46, <b>R50</b>       | JA2.19                 | -                | -                   |

|                         | 10  | P01  | RxD1    | R46         | R45, R50              | JA6.7                  | -                | -                   |

| TO00_RxD1_PGA           | 42  | PUI  | KXDT    | K40         | K40, K00              | U6.4                   | R121/J8.2-3      | J8.1-2, R119        |

|                         |     |      | PGA     | R50         | <b>R45</b> , R46      | JA2.24                 | R88              | R87                 |

|                         |     |      | P-INTP5 | R27         | R28, R29              | PMOD1.8                | R25              | R24                 |

| P-INTP5_A-INTP5_TRDIOC0 | 25  | P16  | A-INTP5 | R29         | R27, R28              | JA2.23                 | -                | -                   |

|                         |     |      | TRDIOC0 | R28         | <b>R27</b> , R29      | JA6.13                 | -                | -                   |

|                         | 24  | D17  | P17     | R31         | R30                   | PMOD2.1                | -                | -                   |

| P17_TI02                | 24  | P17  | TI02    | R30         | R31                   | JA2.22                 | -                | -                   |

|                         |     |      |         | D//         |                       | PMOD1.7                | -                | -                   |

|                         | 1/  | D01  | P-INTP4 | R66         | R69, <mark>R70</mark> | PMOD2.7                | R100             | -                   |

| P-INTP4_A-INTP4_TO03    | 16  | P31  | A-INTP4 | R69         | R66, R70              | JA2.9                  | -                | -                   |

|                         |     |      | TO03    | R70         | R66, R69              | JA2.20                 | -                | -                   |

|                         |     |      | P62     | R73         | R76, R77              | PMOD1.1                | -                | -                   |

| P62_IO2_M1UD            | 14  | P62  | 102     | R76         | R73, <b>R77</b>       | JA1.17                 | -                | -                   |

|                         |     |      | M1UD    | R77         | R73, <b>R76</b>       | JA2.11                 | -                | -                   |

#### Table 6-9: Timer Option Links

#### 6.9 **PMOD1** Interface Configuration

Table 6-10 below details the function of the option links associated with PMOD1 Interface configuration.

|                                         | Ν   | ICU  | MC            | U Peripheral Se     | lection          | Destinatio             | n Select | ion                           |

|-----------------------------------------|-----|------|---------------|---------------------|------------------|------------------------|----------|-------------------------------|

| Signal name                             | Pin | Port | Signal        | Fit                 | DNF              | Interface<br>/Function | Fit      | DNF                           |

|                                         |     |      | P-INTP5       | R27                 | R28, R29         | PMOD1.8                | R25      | R24                           |

| P-INTP5_A-INTP5_TRDIOC0                 | 25  | P16  | A-INTP5       | R29                 | R27, R28         | JA2.23                 | -        | -                             |

|                                         |     |      | TRDIOC0       | R28                 | <b>R27</b> , R29 | JA6.13                 | -        | -                             |

|                                         |     |      | 50100         | J9.1-2              | 110 Open         | U3.6                   | R3       | -                             |

| SCL00_P-SCK00_A-                        |     |      | SCL00         | J9.1-Z              | J10.Open         | JA1.26                 | -        | R3                            |

| SCK00_INTP3                             | 21  | P30  | P-SCK00       | J9.2-3              | J10.Open         | PMOD1.4, PMOD2.4       | -        | -                             |

| SCR00_INTES                             |     |      | A-SCK00       | J10.1-2             | J9.Open          | JA2.10                 | -        | -                             |

|                                         |     |      | INTP3         | J10.2-3             | J9.Open          | JA1.23                 | -        | -                             |

|                                         |     |      |               | D(/                 |                  | PMOD1.7                | -        | -                             |

|                                         | 16  | D21  | P-INTP4       | R66 R69, <b>R70</b> | PMOD2.7          | R100                   | -        |                               |

| P-INTP4_A-INTP4_TO03                    | 10  | P31  | A-INTP4       | R69                 | R66, R70         | JA2.9                  | -        | -                             |

|                                         |     |      | TO03          | R70                 | R66, R69         | JA2.20                 | -        | -                             |

|                                         |     |      | SDA00 J11.1-2 | 111 1 0             | 112 On on        | U3.5                   | R2       | -                             |

|                                         |     |      |               | JII.I-2             | J12.Open         | JA1.25                 | -        | R2                            |

|                                         |     |      | INTP1         | J11.2-3             | J12.Open         | JA2.7                  | -        | -                             |

| SDA00_P-SI00_RxD0_A-<br>SI00_RxD0_INTP1 | 22  | P50  | P-SI00_RxD0   | J12.1-2             | J11.Open         | PMOD1.3, PMOD2.3       | -        | -                             |

|                                         |     |      | A-SI00_RxD0   | J12.2-3             | J11.Open         | JA2.8                  | -        | -                             |

|                                         |     |      |               |                     |                  | U6.4                   | J8.1-2   | J8.2-3/R121,<br><b>R119</b>   |

|                                         |     |      |               |                     |                  | JA2.6                  | -        | -                             |

| P-SO00_TxD0_A-SO00_TxD0                 | 23  | P51  | A-SO00_TxD0   | J13.1-2             | J13.2-3, R123    | U5.3                   | J7.1-2   | J7.2-3,<br><b>R120</b> , R122 |

|                                         |     |      | P-SO00_TxD0   | J13.2-3/R123        | J13.1-2          | PMOD1.2, PMOD2.2       | -        | -                             |

| <b>B</b> (0,100                         | 12  | P60  | P60           | R81                 | R83              | PMOD1.10               | -        | -                             |

| P60_IO0                                 | 12  | P60  | 100           | R83                 | R81              | JA1.15                 | -        | -                             |

| D(1 101                                 | 10  | D41  | P61           | R82                 | R80              | PMOD1.9                | -        | -                             |

| P61_I01                                 | 13  | P61  | 101           | R80                 | R82              | JA1.16                 | -        | -                             |

|                                         |     |      | P62           | R73                 | R76, R77         | PMOD1.1                | -        | -                             |

| P62_IO2_M1UD                            | 14  | P62  | 102           | R76                 | R73, <b>R77</b>  | JA1.17                 | -        | -                             |

|                                         |     |      | M1UD          | R77                 | R73, <b>R76</b>  | JA2.11                 | -        | -                             |

| <b>P</b> 71 105                         | 10  | D71  | P71           | R68                 | R67              | PMOD1.8                | R24      | R25                           |

| P71_I05                                 | 19  | P71  | 105           | R67                 | R68              | JA1.20                 | -        | -                             |

Table 6-10: PMOD1 Interface Option Links

#### 6.10 PMOD2 Interface Configuration

**Table 6-11** below details the function of the option links associated with PMOD2 Interface configuration.

|                                 | Μ   | CU    | MC          | U Peripheral Sele | ection          | Destinatio             | on Selectio | n                                |

|---------------------------------|-----|-------|-------------|-------------------|-----------------|------------------------|-------------|----------------------------------|

| Signal name                     | Pin | Port  | Signal      | Fit               | DNF             | Interface<br>/Function | Fit         | DNF                              |

|                                 | 24  | P17   | P17         | R31               | R30             | PMOD2.1                | -           | -                                |

| P17_TI02                        | 24  | FI/   | TI02        | R30               | R31             | JA2.22                 | -           | -                                |

|                                 | 24  | P27   | P27         | R34               | R32             | PMOD2.8                | R35         | R36                              |

| P27_ANI7                        | 34  |       | ANI7        | R32               | R34             | JA5.4                  | -           | -                                |

|                                 |     |       | 601.00      | 10.1.0            | 110 On on       | U3.6                   | R3          | -                                |

|                                 |     |       | SCL00       | J9.1-2            | J10.Open        | JA1.26                 | -           | R3                               |

| SCL00_P-SCK00_A-<br>SCK00_INTP3 | 21  | P30   | P-SCK00     | J9.2-3            | J10.Open        | PMOD1.4, PMOD2.4       | -           | -                                |

|                                 |     |       | A-SCK00     | J10.1-2           | J9.Open         | JA2.10                 | -           | -                                |