# R1RP0408D Series

4M High Speed SRAM (512-kword × 8-bit)

R10DS0288EJ0100 Rev.1.00 Nov.18.19

# Description

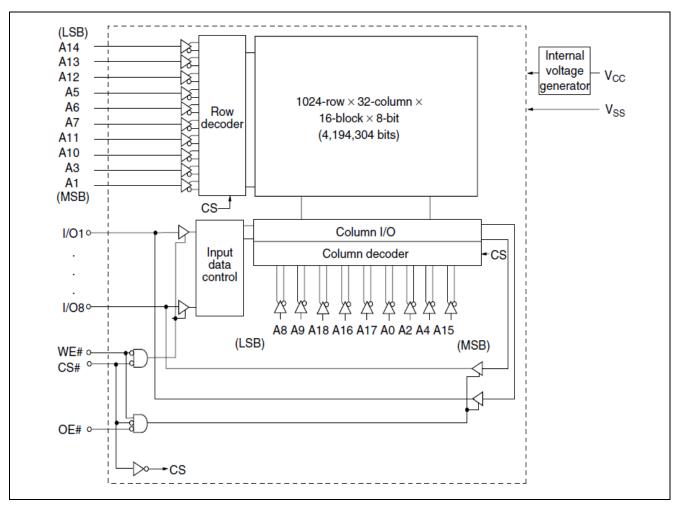

The R1RP0408D Series is a 4-Mbit high speed static RAM organized 512-k word  $\times$  8-bit. It has realized high speed access time by employing CMOS process (6-transistor memory cell) and high speed circuit designing technology. It is most appropriate for the application which requires high speed, high density memory and wide bit width configuration, such as cache and buffer memory in system. It is packaged in 400-mil 36-pin plastic SOJ.

# Features

- Single 5.0V supply: 5.0V ± 10%

- Access time: 12ns (max)

- Completely static memory

- No clock or timing strobe required

- Equal access and cycle times

- Directly TTL compatible

- All inputs and outputs

- Operating current: 130mA (max)

- TTL standby current: 40mA (max)

- CMOS standby current : 5mA (max)

- : 1.0mA (max) (L-version)

- Data retention current : 0.5mA (max) (L-version)

- Data retention voltage : 2.0V (min) (L-version)

- Center Vcc and Vss type pin out

# **Ordering Information**

| Type No.        | Access time | Version   | Package                     |

|-----------------|-------------|-----------|-----------------------------|

| R1RP0408DGE-2PR | 12ns        | Normal    | 400 mil 20 nin plantia CO I |

| R1RP0408DGE-2LR | 12ns        | L-Version | 400-mil 36-pin plastic SOJ  |

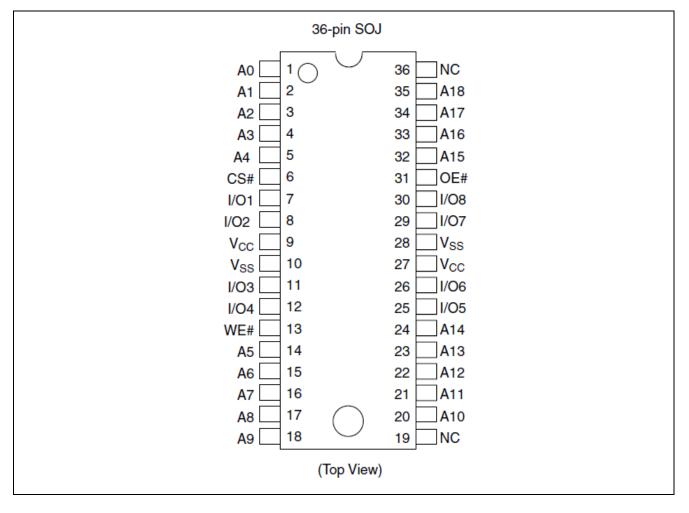

# **Pin Arrangement**

# **Pin Description**

| Pin name     | Function          |

|--------------|-------------------|

| A0 to A18    | Address input     |

| I/O1 to I/O8 | Data input/output |

| CS#          | Chip select       |

| OE#          | Output enable     |

| WE#          | Write enable      |

| Vcc          | Power supply      |

| Vss          | Ground            |

| NC           | No connection     |

# **Block Diagram**

## **Operation Table**

| CS# | OE# | WE# | Mode           | Vcc current | I/O              | Ref. cycle            |

|-----|-----|-----|----------------|-------------|------------------|-----------------------|

| Н   | ×   | ×   | Standby        | Isb, Isb1   | High-Z           | —                     |

| L   | Н   | Н   | Output disable | lcc         | High-Z           | —                     |

| L   | L   | Н   | Read           | Icc         | D <sub>OUT</sub> | Read cycle (1) to (3) |

| L   | Н   | L   | Write          | Icc         | D <sub>IN</sub>  | Write cycle (1)       |

| L   | L   | L   | Write          | Icc         | D <sub>IN</sub>  | Write cycle (2)       |

Note: H: VIH, L: VIL, X: VIH or VIL

# **Absolute Maximum Ratings**

| Parameter                                  | Symbol          | Value                 | Unit |

|--------------------------------------------|-----------------|-----------------------|------|

| Supply voltage relative to V <sub>SS</sub> | V <sub>CC</sub> | -0.5 to +7.0          | V    |

| Voltage on any pin relative to Vss         | VT              | -0.5*1 to Vcc + 0.5*2 | V    |

| Power dissipation                          | PT              | 1.0                   | W    |

| Operating temperature                      | Topr            | 0 to +70              | °C   |

| Storage temperature                        | Tstg            | -55 to +125           | °C   |

| Storage temperature under bias             | Tbias           | -10 to +85            | °C   |

Notes: 1.  $V_T$  (min) = -2.0V for pulse width (under shoot)  $\leq$  6ns.

2.  $V_T$  (max) =  $V_{CC}$  + 2.0V for pulse width (over shoot)  $\leq$  6ns.

# **Recommended DC Operating Conditions**

(Ta = 0 to +70°C)

| Parameter      | Symbol | Min                | Тур | Max         | Unit |

|----------------|--------|--------------------|-----|-------------|------|

| Supply voltage | Vcc*3  | 4.5                | 5.0 | 5.5         | V    |

|                | Vss*4  | 0                  | 0   | 0           | V    |

| Input voltage  | Vih    | 2.0                | —   | Vcc + 0.5*2 | V    |

|                | VIL    | -0.5* <sup>1</sup> | _   | 0.8         | V    |

Notes: 1.  $V_{IL}$  (min) = -2.0V for pulse width (under shoot)  $\leq$  6ns.

2.  $V_{IH}$  (max) =  $V_{CC}$  + 2.0V for pulse width (over shoot)  $\leq$  6ns.

3. The supply voltage with all  $V_{CC}$  pins must be on the same level.

4. The supply voltage with all  $V_{SS}$  pins must be on the same level.

# **DC Characteristics**

|                                |                  |     | (Ta = 0           | $(Ta = 0 \text{ to } +70^{\circ}C, V_{CC} = 5.0V \pm 10\%, V_{SS} = 0)$ |                                                                                                           |  |  |

|--------------------------------|------------------|-----|-------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| Parameter                      | Symbol           | Min | Max               | Unit                                                                    | Test conditions                                                                                           |  |  |

| Input leakage current          | I <sub>LI</sub>  |     | 2                 | μA                                                                      | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                             |  |  |

| Output leakage current         | I <sub>LO</sub>  | —   | 2                 | μA                                                                      | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                             |  |  |

| Operating power supply current | Icc              |     | 130               | mA                                                                      |                                                                                                           |  |  |

| Standby power supply current   | I <sub>SB</sub>  | _   | 40                | mA                                                                      | Min cycle, CS# = V <sub>IH</sub> ,<br>Other inputs = V <sub>IH</sub> /V <sub>IL</sub>                     |  |  |

|                                | I <sub>SB1</sub> |     | 5                 | mA                                                                      | $\label{eq:f_constraint} \begin{array}{l} f = 0 MHz \\ V_{CC} \geq CS \# \geq V_{CC} - 0.2V, \end{array}$ |  |  |

|                                |                  | *1  | 1.0* <sup>1</sup> | mA                                                                      | (1) $0V \le V_{IN} \le 0.2V$ or<br>(2) $V_{CC} \ge VIN \ge V_{CC} - 0.2V$                                 |  |  |

| Output voltage                 | Vol              |     | 0.4               | V                                                                       | I <sub>OL</sub> = 8mA                                                                                     |  |  |

|                                | Vон              | 2.4 |                   | V                                                                       | I <sub>OH</sub> = -4mA                                                                                    |  |  |

Note: 1. This characteristics is guaranteed only for L-version.

# Capacitance

$(Ta = +25^{\circ}C, f = 1.0MHz)$

| Parameter                  | Symbol | Min | Max | Unit | Test conditions |

|----------------------------|--------|-----|-----|------|-----------------|

| Input capacitance*1        | CIN    |     | 6   | pF   | $V_{IN} = 0V$   |

| Input/output capacitance*1 | Ci/o   |     | 8   | pF   | $V_{I/O} = 0V$  |

Note: 1. This parameter is sampled and not 100% tested.

# **AC Characteristics**

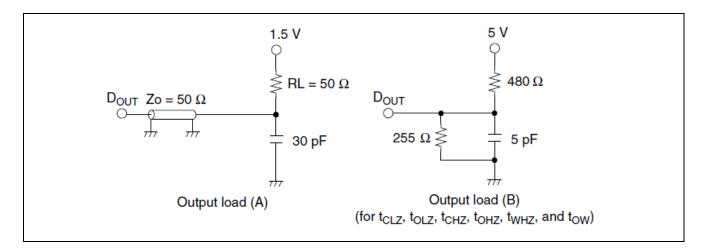

Test Conditions (Ta = 0 to +70°C, VCC =  $5.0V \pm 10\%$ , unless otherwise noted.)

- Input pulse levels: 3.0V/0.0V

- Input rise and fall time: 3ns

- Input and output timing reference levels: 1.5V

- Output load: See figures (Including scope and jig)

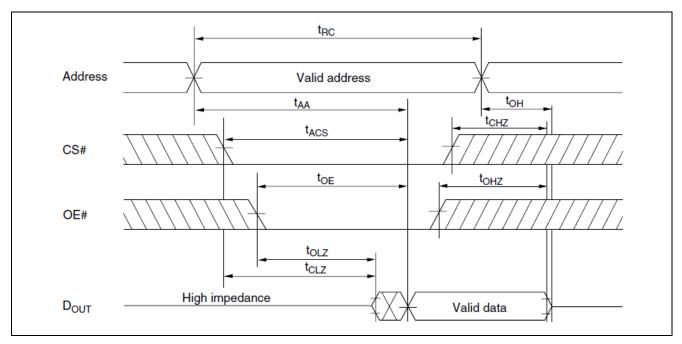

#### **Read Cycle**

|                                    |                 | R1RP | 0408D |      |       |

|------------------------------------|-----------------|------|-------|------|-------|

| Parameter                          | Symbol          | Min  | Max   | Unit | Notes |

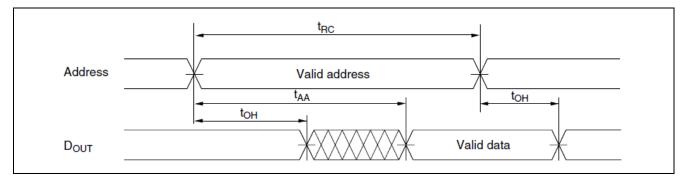

| Read cycle time                    | t <sub>RC</sub> | 12   |       | ns   |       |

| Address access time                | taa             |      | 12    | ns   |       |

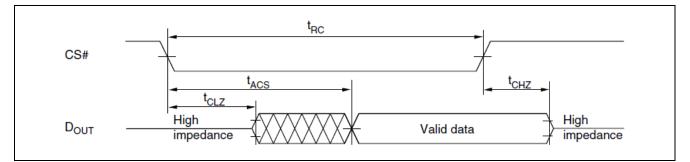

| Chip select access time            | tacs            |      | 12    | ns   |       |

| Output enable to output valid      | toe             |      | 6     | ns   |       |

| Output hold from address change    | tон             | 3    | _     | ns   |       |

| Chip select to output in low-Z     | tcLz            | 3    | _     | ns   | 1     |

| Output enable to output in low-Z   | tolz            | 0    | _     | ns   | 1     |

| Chip deselect to output in high-Z  | tснz            |      | 6     | ns   | 1     |

| Output disable to output in high-Z | tонz            |      | 6     | ns   | 1     |

#### Write Cycle

|                                    |                  | R1RP | 0408D |      |       |

|------------------------------------|------------------|------|-------|------|-------|

| Parameter                          | Symbol           | Min  | Max   | Unit | Notes |

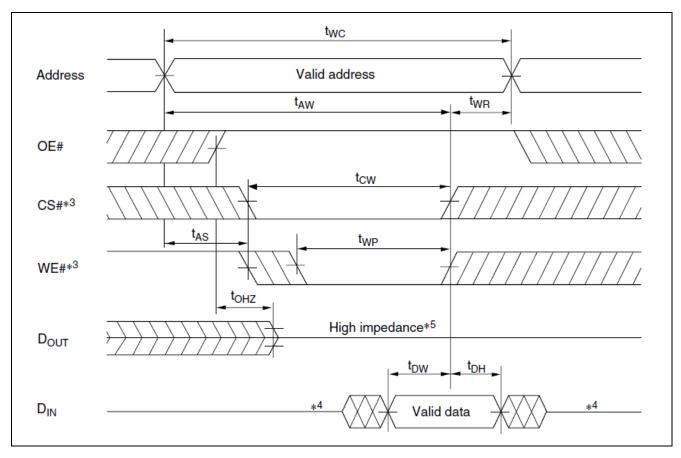

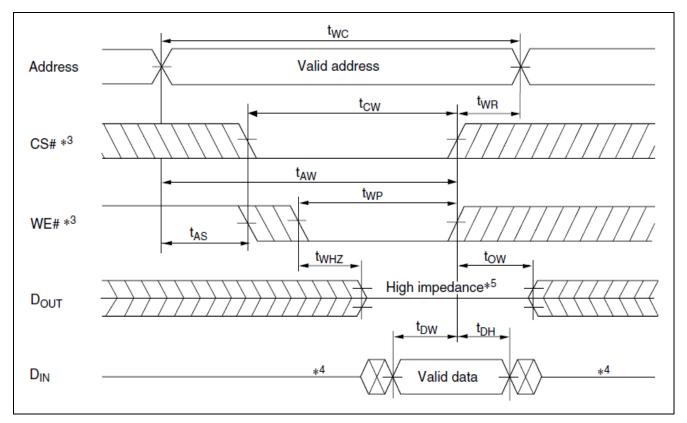

| Write cycle time                   | t <sub>WC</sub>  | 12   |       | ns   |       |

| Address valid to end of write      | t <sub>AW</sub>  | 8    |       | ns   |       |

| Chip select to end of write        | tcw              | 8    |       | ns   | 9     |

| Write pulse width                  | twp              | 8    | —     | ns   | 8     |

| Address setup time                 | tas              | 0    | —     | ns   | 6     |

| Write recovery time                | twR              | 0    |       | ns   | 7     |

| Data to write time overlap         | tow              | 6    |       | ns   |       |

| Data hold from write time          | t <sub>DH</sub>  | 0    |       | ns   |       |

| Write disable to output in low-Z   | tow              | 3    |       | ns   | 1     |

| Output disable to output in high-Z | tонz             |      | 6     | ns   | 1     |

| Write enable to output in high-Z   | t <sub>WHZ</sub> |      | 6     | ns   | 1     |

Notes: 1. Transition is measured  $\pm 200$ mV from steady voltage with output load (B). This parameter is sampled and not 100% tested.

- 2. Address should be valid prior to or coincident with CS# transition low.

- 3. WE# and/or CS# must be high during address transition time.

- 4. If CS# and OE# are low during this period, I/O pins are in the output state. Then, the data input signals of opposite phase to the outputs must not be applied to them.

- 5. If the CS# low transition occurs simultaneously with the WE# low transition or after the WE# transition, output remains a high impedance state.

- 6. t<sub>AS</sub> is measured from the latest address transition to the later of CS# or WE# going low.

- 7. t<sub>WR</sub> is measured from the earlier of CS# or WE# going high to the first address transition.

- 8. A write occurs during the overlap of a low CS# and a low WE#. A write begins at the latest transition among CS# going low and WE# going low. A write ends at the earliest transition among CS# going high and WE# going high. twp is measured from the beginning of write to the end of write.

- 9. tcw is measured from the later of CS# going low to the end of write.

# **Timing Waveforms**

### Read Timing Waveform (1) (WE# = VIH)

#### Read Timing Waveform (2) (WE# = $V_{IH}$ , LB# = $V_{IL}$ , UB# = $V_{IL}$ )

Read Timing Waveform (3) (WE# =  $V_{IH}$ , CS# =  $V_{IL}$ , OE# =  $V_{IL}$ )\*<sup>2</sup>

Write Timing Waveform (1) (WE# Controlled)

#### Write Timing Waveform (2) (CS# Controlled)

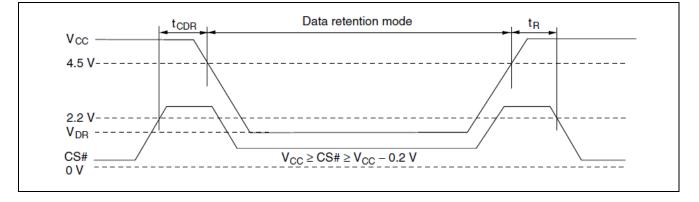

# Low Vcc Data Retention Characteristics

$(Ta = 0 \text{ to } +70^{\circ}C)$

| Parameter                            | Symbol           | Min | Max | Unit | Test conditions                                                                                                                                                            |

|--------------------------------------|------------------|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{CC}$ for data retention          | Vdr              | 2.0 | _   | V    | $ \begin{array}{l} V_{CC} \geq CS\# \geq V_{CC} - 0.2V, \\ (1) \ 0 \ V \leq V_{IN} \leq 0.2V \ or \\ (2) \ V_{CC} \geq V_{IN} \geq V_{CC} - 0.2V \end{array} $             |

| Data retention current               | ICCDR            | _   | 500 | μΑ   | $ \begin{array}{l} V_{CC} = 3V \\ V_{CC} \geq CS\# \geq V_{CC} - 0.2V, \\ (1) \ 0V \leq V_{IN} \leq 0.2V \ or \\ (2) \ V_{CC} \geq V_{IN} \geq V_{CC} - 0.2V \end{array} $ |

| Chip deselect to data retention time | t <sub>CDR</sub> | 0   |     | ns   | See retention waveform                                                                                                                                                     |

| Operation recovery time              | t <sub>R</sub>   | 5   |     | ms   |                                                                                                                                                                            |

This characteristics is guaranteed only for L-version.

# Low V<sub>CC</sub> Data Retention Timing Waveform

# **Revision History**

|      |           | Description |                      |  |  |  |  |

|------|-----------|-------------|----------------------|--|--|--|--|

| Rev. | Date      | Page        | Page Summary         |  |  |  |  |

| 1.00 | Nov.18.19 | -           | First Edition issued |  |  |  |  |

All documents should contain the following section break and paragraph as the last item. The footers of this document refer to the paragraph in order to reference the last page of the document.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Renesas Electronics: R1RP0408DGE-2LR#B1 R1RP0408DGE-2PR#B1