# RENESAS

# RAA489220

4 to 10 Cell Battery Front End and Protector

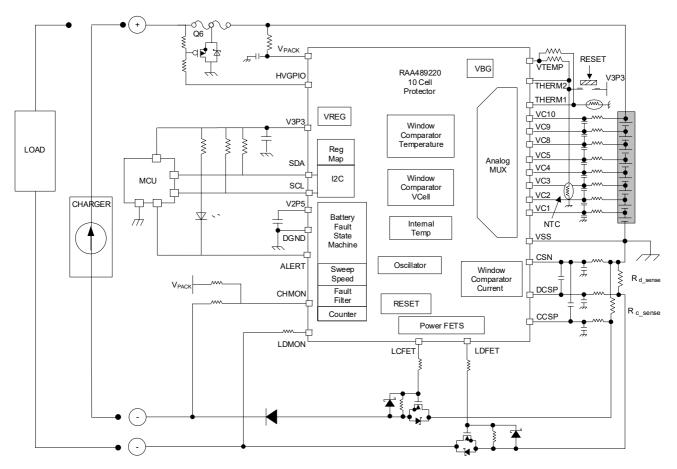

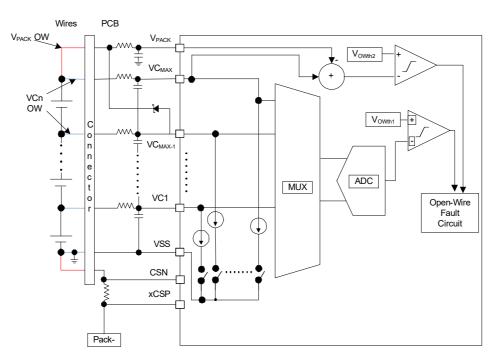

The RAA489220 is a 10-cell Battery management Front End (BFE IC) with both autonomous protection functions and battery health monitoring for packs with MCU control (Figure 1).

The RAA489220 monitors each cell for overvoltage, undervoltage, pack temperature, charge currents, and discharge currents. This device includes internal self test to confirm its own health, and system checks to confirm the system state.

The I<sup>2</sup>C interface includes optional CRC to reliably communicate with an MCU. The device has low-side charge and discharge FET controls to disconnect the pack from a load or charger. The RAA489220 has a low typical Low Power Mode current consumption of  $3\mu$ A to maximize battery shelf life and operational time.

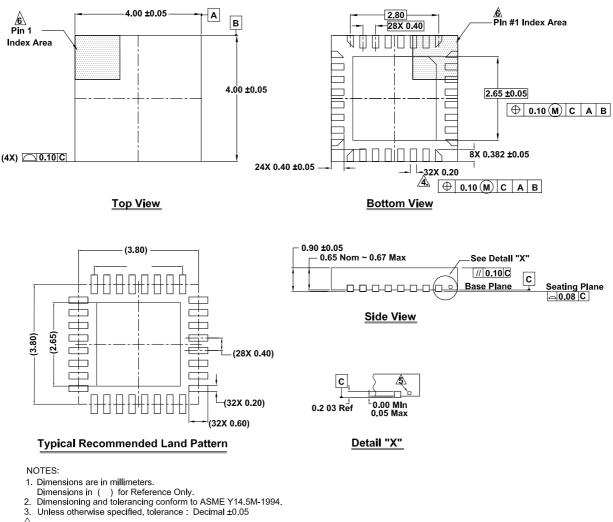

The RAA489220 is offered in a 32pin 4mm×4mm QFN package.

### Features

- VPACK voltages: 5V to 44V

- Hot plug tolerance

- Built-in low-side FET drivers

- Charger/load presence detection

- Cell open wire and system checks

- Autonomous detection and actions

- HVGPIO fuse blow configurable

- Support for wide range of current-sense resistors

### Applications

- Power tools

- Hand held electronics

- Battery protector

Figure 1. BFE Application

# Contents

| 1. | Over        | view           |                                           | 4 |

|----|-------------|----------------|-------------------------------------------|---|

|    | 1.1         | Block D        | iagram                                    | 4 |

| 2. | Pin I       | nformatio      | on                                        | 5 |

|    | 2.1         | Pin Con        | figuration                                | 5 |

|    | 2.2         | Pin Des        | criptions                                 | 5 |

| 3. | Spec        | ification      | s                                         | 7 |

|    | 3.1         |                | e Maximum Ratings                         |   |

|    | 3.2         |                | tings                                     |   |

|    | 3.3         |                | I Information                             |   |

|    | 3.4         |                | nended Operating Conditions               |   |

|    | 3.5         |                | al Specifications                         |   |

| 4. | Typi        |                | rmance Curves                             |   |

| 5. | • •         |                | e Overview                                |   |

| 5. |             |                |                                           |   |

|    | 5.1         |                | itate                                     |   |

|    | 5.2<br>5.3  |                | Jp State                                  |   |

|    | 5.3<br>5.4  |                | Aode                                      |   |

|    | 5.4<br>5.5  |                | OWER Mode                                 |   |

| •  |             |                |                                           |   |

| 6. |             |                |                                           |   |

|    | 6.1         |                | etection and Recovery                     |   |

|    | 6.2         |                | ET Fault Response                         |   |

| 7. | Syst        | -              | sters                                     |   |

|    | 7.1         | Calculat       | ting Thresholds and Readings              |   |

|    |             | 7.1.1          | Measurement Reads                         |   |

|    |             | 7.1.2          | Digital Thresholds                        |   |

|    | 7.2         | •              | r Definitions                             |   |

|    |             | 7.2.1          | 0x10 Faults                               |   |

|    |             | 7.2.2          | 0x11 Masks and Status                     |   |

|    |             | 7.2.3          | 0x40 System Config 1                      |   |

|    |             | 7.2.4          | 0x41 Measure Select                       |   |

|    |             | 7.2.5<br>7.2.6 | 0x42 System Config 2                      |   |

|    |             | 7.2.0          | 0x81 OV and EOC Thresholds                |   |

|    |             | 7.2.8          | 0x82 DV <sub>CFL1</sub> OV, UV Thresholds |   |

|    |             | 7.2.9          | 0x83 SCC, OT/UT Thresholds                |   |

|    |             | 7.2.10         | 0x84 Current Thresholds                   |   |

| 8. |             |                | erface                                    |   |

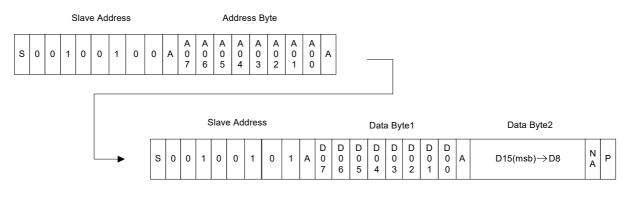

| 0. | 8.1         |                | /e Address                                |   |

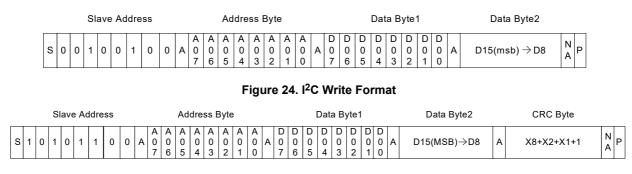

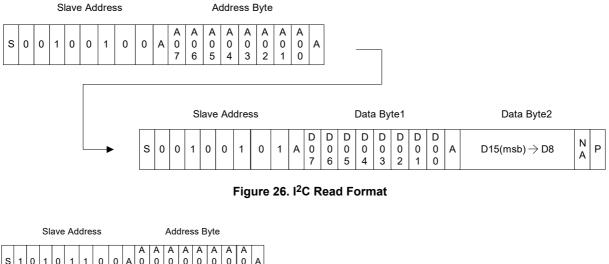

|    | o. i<br>8.2 |                | nication Packet Format                    |   |

|    | 8.3         |                | Redundancy Check (CRC)                    |   |

|    | 8.4         | •              |                                           |   |

|    | <b>V</b> .T | 8.4.1          | Write Operation                           |   |

|    |             | 8.4.2          | Write to Protected Registers 0x80-0x84    |   |

|    |             | 8.4.3          | Read Operation                            |   |

|     |       | 8.4.4      | Command Codes                    | 0  |

|-----|-------|------------|----------------------------------|----|

| 9.  | Pins  |            |                                  | 51 |

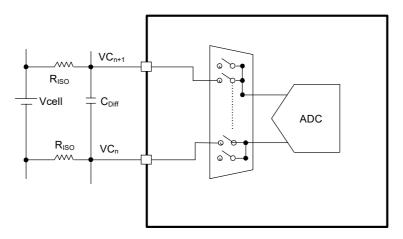

|     | 9.1   | VCn Pins   | s 5                              | 51 |

|     |       | 9.1.1      | Open Wire on VCn Pins            | 2  |

|     | 9.2   | VPACK I    | <sup>-</sup> in                  | 53 |

|     | 9.3   | HVGPIO     | Pin                              | 53 |

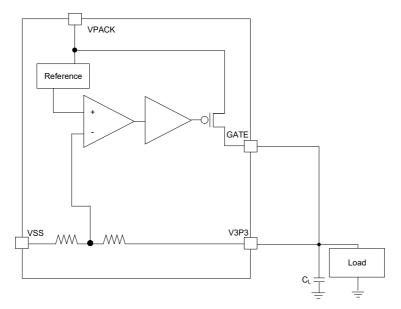

|     | 9.4   | V3P3 Re    | egulator and GATE Pins           | 53 |

|     |       | 9.4.1      | V3P3 Pin                         | 3  |

|     |       | 9.4.2      | GATE Pin                         | 3  |

|     | 9.5   | V2P5 Pir   | n 5                              | 3  |

|     | 9.6   | DGND P     | 'in                              | 4  |

|     | 9.7   | ALERT F    | Pin                              | 4  |

|     | 9.8   | SCL Pin    |                                  | 4  |

|     | 9.9   | SDA Pin    |                                  | 5  |

|     | 9.10  | VTEMP      | and THERM Pins                   | 5  |

|     |       |            | Hard RESET                       |    |

|     |       |            | Thermistor Pins Open-Wire Test 5 |    |

|     | 9.11  | LDMON      | Pin                              | 6  |

|     |       |            | Pin                              |    |

|     |       | -          | Pin                              | -  |

|     |       |            | Pin                              |    |

|     |       | ,          | CSP, and CSN Pins                |    |

|     | 9.16  | VSS Pin    |                                  | 7  |

| 10. | Packa | age Outli  | ne Drawing                       | 8  |

| 11. | Orde  | ring Infor | mation                           | 9  |

| 12. | Revis | ion Histo  | ory                              | 9  |

# 1. Overview

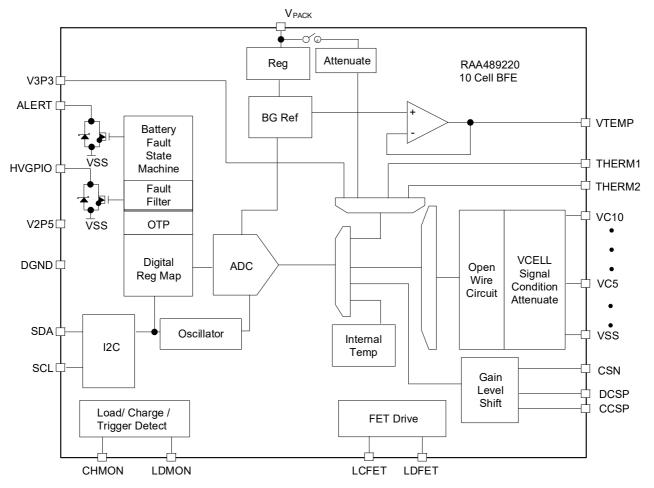

# 1.1 Block Diagram

Figure 2. RAA489220 Block Diagram

# 2. Pin Information

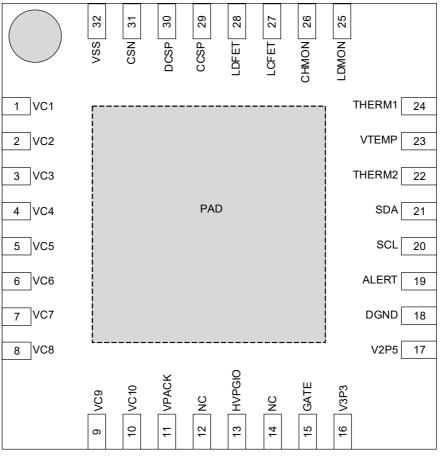

# 2.1 Pin Configuration

Top View

# 2.2 Pin Descriptions

| Pin Number                       | Pin Name          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 4, 5, 6, 7,<br>8, 9, 10 | VCn (n = 1 to 10) | <b>Battery cell voltage inputs.</b> For applications with a 10-cell battery string, where cell number 1 connects to the lowest voltage and cell number 10 connects to the highest voltage, VCn connects to the positive terminal of cell n. The negative terminal of cell n connects to VC n-1. All connections from cell to pin are made as a Kelvin sense route and through a low-pass filter network (VC10 connects only to the positive terminal of Cell 10). |

| 11                               | VPACK             | <b>VPACK Pin.</b> Connect this pin to the pack voltage. A voltage at this pin powers the IC. Connect a minimum of $10\mu$ F capacitor from pin to VSS.                                                                                                                                                                                                                                                                                                            |

| 12, 14                           | NC                | No Connected                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13                               | HVGPIO            | <b>High Voltage GPIO Pin.</b> The function of the pin can be configurable as a secondary alert or as a high voltage GPIO.                                                                                                                                                                                                                                                                                                                                         |

| 15                               | GATE              | Regulator Feedback Pin. Connect this pin to the V3P3 pin.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16                               | V3P3              | <b>3.3V supply voltage input.</b> Connect directly to the source of the external NMOS FET, Connect a 4.7µF capacitor between this pin and VSS.                                                                                                                                                                                                                                                                                                                    |

| 17                               | V2P5              | Internal 2.5v supply decoupling Pin. Connect a $10\mu F$ capacitor between V2P5 and DGND.                                                                                                                                                                                                                                                                                                                                                                         |

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18         | DGND     | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                            |

| 19         | ALERT    | <b>ALERT Pin.</b> The pin is the fault and status indicator for the pack. The Fault and Status bits can change the state of the ALERT pin. The pin is an open-drain NMOS. The pin asserts to the VSS level when an unmasked fault or status bit is set. Otherwise, the pin is in a high impedance state. A pull-up resistor greater than $10k\Omega$ to MCU voltage is typically required. |

| 20         | SCL      | <b>Serial Clock Pin.</b> This pin is the clock signal for the I <sup>2</sup> C communication interface. An optional pull-up resistor greater than $4.7k\Omega$ to $3.3V$ can be attached.                                                                                                                                                                                                  |

| 21         | SDA      | <b>Serial Data Pin.</b> This is an open-drain serial data I/O for the I <sup>2</sup> C communication interface. A pull-up resistor greater than $4.7k\Omega$ to $3.3V$ is required.                                                                                                                                                                                                        |

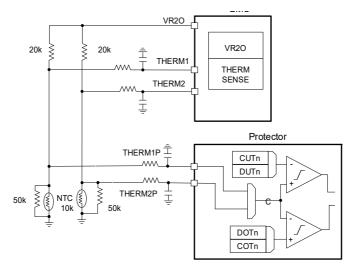

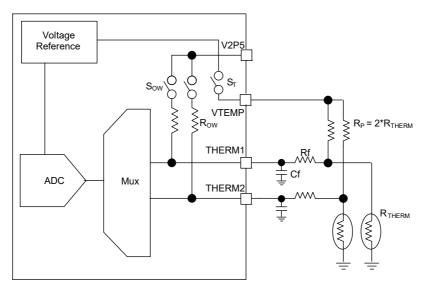

| 23         | VTEMP    | VTEMP Pin. Connect this pin to the pull-up resistors of the thermistor circuits.                                                                                                                                                                                                                                                                                                           |

| 24         | THERM1   | Thermistor Pins. Connect a thermistor to each of these pins. COTn, CUTn, DOTn, and                                                                                                                                                                                                                                                                                                         |

| 22         | THERM2   | <ul> <li>DUTn thresholds are compared to the measurement of the respective thermistor. Reset<br/>the device by connecting the THERM2 pin to V3P3 pin.</li> </ul>                                                                                                                                                                                                                           |

| 25         | LDMON    | <b>Load Monitor Pin.</b> When the voltage difference between VPACK and LDMON falls below threshold $V_{CHTHR}$ , the LD PRESI bit transitions from 0 to 1.Connect this pin to the negative load terminal. This pin has an internal pull-down resistor connected to VSS.                                                                                                                    |

| 26         | CHMON    | <b>Charge Monitor Pin.</b> When the voltage on CHMON pin falls below the $V_{CHTHR}$ , the CH PRESI bit transition from 0 to 1. Connect this pin to the negative charger terminal. The pin could be used as a triggered wakeup. This pin has an internal pull-down resistor and requires an external pull-up resistor to VPACK for some applications.                                      |

| 27         | LCFET    | <b>Low-Side Charge FET control Pin.</b> When the FET Driver is disabled, the pin is resistively connected to VSS. When the FET Driver is enabled, the gate of the power FET is pulled up.                                                                                                                                                                                                  |

| 28         | LDFET    | <b>Low-Side Discharge FET control Pin.</b> When the FET Driver is disabled, the pin is resistively connected to VSS. When the FET Driver is enabled, the gate of the power FET is pulled up.                                                                                                                                                                                               |

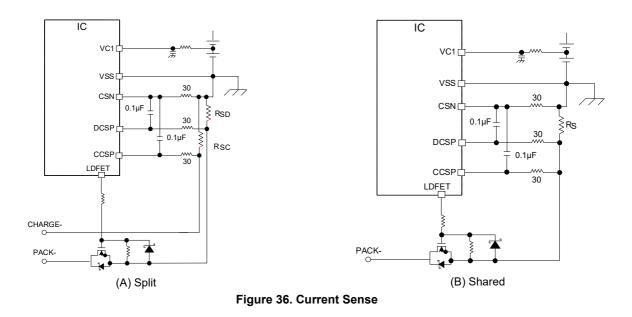

| 29         | CCSP     | <b>Charge Current Sense Positive.</b> Connect a resistor between this pin and the CSN pin to detect charge current.                                                                                                                                                                                                                                                                        |

| 30         | DCSP     | <b>Discharge Current Sense Positive.</b> Connect a resistor between this pin and the CSN pin to detect discharge current.                                                                                                                                                                                                                                                                  |

| 31         | CSN      | <b>Current Sense Negative.</b> Connect this pin to the PCB ground and the negative terminal of the battery pack.                                                                                                                                                                                                                                                                           |

| 32         | VSS      | <b>Analog Ground.</b> VSS is the negative reference voltage for the chip. In most applications, the pin is connected to GND. This pin also serves as the negative reference pin for cell1 voltage measurement.                                                                                                                                                                             |

|            | EPAD     | Electrical Pad. Connect to VSS                                                                                                                                                                                                                                                                                                                                                             |

# 3. Specifications

# 3.1 Absolute Maximum Ratings

**CAUTION:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                             | Minimum   | Maximum | Unit |

|---------------------------------------|-----------|---------|------|

| VPACK, CHMON, LDMON, HVGPIO           | -0.3      | +54     | V    |

| LCFET, LDFET                          | -0.3      | VPACK   | V    |

| VPACK - LDMON                         | -0.7      | +54     | V    |

| VC9, VC10                             | -0.3      | VPACK   | V    |

| VC8                                   | -0.3      | +50     | V    |

| VC7                                   | -0.3      | +42.5   | V    |

| VC6                                   | -0.3      | +36.5   | V    |

| VC5                                   | -0.3      | +30     | V    |

| VC4                                   | -0.3      | +25     | V    |

| VC3                                   | -0.3      | +19     | V    |

| VC2                                   | -0.3      | +13     | V    |

| VC1                                   | -0.3      | +6.5    | V    |

| VCn - VC(n-1) (n = 2 to 10)           | -0.3      | 6.5     | V    |

| DGND                                  | -0.3      | 0.5     | V    |

| V3P3, GATE                            | -0.3      | 6.5     | V    |

| V2P5                                  | -0.3      | 2.9     | V    |

| CCSP, DCSP, CSN, THERM1,VTEMP, THERM2 | -0.3      | 6.5     | V    |

| SDA, SCL, ALERT                       | DGND -0.3 | 6.5     | V    |

| LDMON, CHMON                          | 0         | 10      | mA   |

| ALERT, SDA, HVGPIO                    | -10       | 0       | mA   |

| LCFET, LDFET                          | 0         | 5       | mA   |

## 3.2 ESD Ratings

| ESD Model/Test                                  | Value | Unit |

|-------------------------------------------------|-------|------|

| Human Body Model (Tested per JS-001-2017)       | 2     | kV   |

| Charged Device Model (Tested per JS-002-2018)   | 750   | V    |

| Latch-Up (Tested per JESD78E; Class 2, Level A) | 100   | mA   |

# 3.3 Thermal Information

| Thermal Resistance (Typical) | θ <sub>JA</sub> (°C/W) <sup>[1]</sup> | θ <sub>JC</sub> (°C/W) <sup>[2]</sup> |

|------------------------------|---------------------------------------|---------------------------------------|

| 32 Ld 4x4 QFN Package        | 38                                    | 2.5                                   |

1.  $\theta_{JA}$  is measured with the component mounted on a high-effective thermal conductivity test board in free air. See TB379.

2. For  $\theta_{JC}$ , the case temperature location is the center of the exposed metal pad on the package underside.

| Parameter                         | Minimum | Maximum   | Unit |

|-----------------------------------|---------|-----------|------|

| Maximum Junction Temperature      |         | +125      | °C   |

| Maximum Storage Temperature Range | -65     | +150      | °C   |

| Pb-Free Reflow Profile            |         | see TB493 |      |

# 3.4 Recommended Operating Conditions

| Parameter                              | Minimum | Maximum | Unit |

|----------------------------------------|---------|---------|------|

| Supply Voltage, VPACK                  | 6       | 44      | V    |

| Ambient Temperature                    | -40     | +85     | °C   |

| VCn - VC(n-1) (n = 2 to 10); VC1 - VSS | 1.5     | 4.5     | V    |

| CCSP - CSN, DCSP - CSN                 | -50     | 50      | mV   |

| HVGPIO, LDMON, CHMON                   | 0       | VPACK   | V    |

| ALERT, SDA, SCL                        | 0       | 3.3     | V    |

| THERM1, THERM2                         | 0       | 1.9     | V    |

| VTEMP                                  | 2.0     | )48     | V    |

| V2P5                                   | 2       | .5      | V    |

| V3P3, GATE                             | 3       | .3      | V    |

| DGND-VSS, CSN - VSS                    | -0.1    | 0.1     | V    |

| LDFET                                  | 0       | 10      | V    |

# 3.5 Electrical Specifications

| Parameter                                | Symbol                  | Test Conditions                                                                                                                     | Min  | Тур | Max | Units |

|------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|-------|

| Power Supply                             |                         |                                                                                                                                     |      |     |     |       |

| Power-On Reset Voltage                   | V <sub>PORf</sub>       | Falling Edge                                                                                                                        |      |     | 5   | V     |

| at VPACK                                 | V <sub>PORr</sub>       | Rising Edge                                                                                                                         |      | 6   | 7   | V     |

| Power-On Hysteresis                      | V <sub>PORhys</sub>     |                                                                                                                                     |      | 1.8 |     | V     |

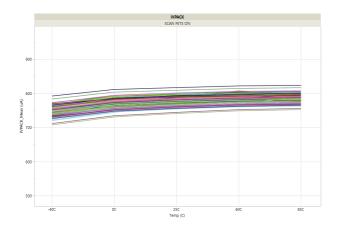

|                                          |                         | SCAN Mode (During Scan),<br>FETS ON                                                                                                 |      | 750 | 980 | μA    |

| Current Consumed by                      | I <sub>VPACK</sub>      | IDLE Mode; FETS ON                                                                                                                  |      | 110 | 160 | μA    |

| the IC                                   |                         | LOW POWER Mode, LP Reg =1                                                                                                           |      | 35  | 55  | μA    |

|                                          |                         | LOW POWER Mode, LP Reg = 0                                                                                                          |      | 3   | 8   | μA    |

| V <sub>CELL</sub>                        |                         |                                                                                                                                     | L    | I   | •   |       |

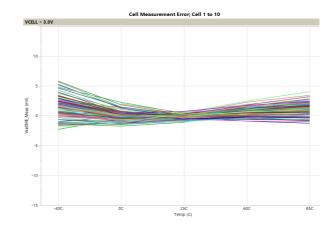

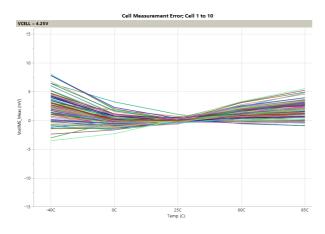

| Cell Measurement Error                   | V <sub>CELL_ME</sub>    | Cells 1 to 10; T = 0°C to 60°C;<br>V <sub>CELL</sub> = 1.5V to 4.25V, RS = 1k $\Omega$ ,<br>CS = 0.1µF, Single Triggered<br>Measure | -16  | ±5  | 16  | mV    |

| V <sub>CELL</sub> Leakage Current<br>OFF | V <sub>Cell_lbOff</sub> |                                                                                                                                     | -200 |     | 200 | nA    |

| V <sub>CELL</sub> Bias Current ON        | V <sub>Cell_IbOn</sub>  |                                                                                                                                     |      | 3   |     | μA    |

| Parameter                                                          | Symbol                  | Test Conditions                                          | Min         | Тур   | Max  | Units  |

|--------------------------------------------------------------------|-------------------------|----------------------------------------------------------|-------------|-------|------|--------|

| V <sub>CELL</sub> Bias Current<br>Match ON                         | V <sub>Cell_los</sub>   |                                                          |             | ±0.3  |      | μA     |

| I <sub>PACK</sub> (xCSP - CSN)                                     | •                       |                                                          |             |       | •    |        |

| I <sub>PACK</sub> Comparison Vos                                   | I <sub>PACK_VOS</sub>   | xCSP = CSN = 0V                                          |             | 110   |      | μV     |

| I <sub>PACK</sub> Comparison Vos<br>TC                             | I <sub>PACK_VOSTC</sub> | xCSP = CSN = 0V                                          |             | 0.3   |      | μV/C   |

| I <sub>PACK</sub> Bias Current                                     | I <sub>PACK_LC</sub>    |                                                          | -1.9        | -1.7  | -0.5 | μA     |

| IPACK Bias Current Offset                                          | I <sub>PACK_IOS</sub>   |                                                          |             | ±500  |      | nA     |

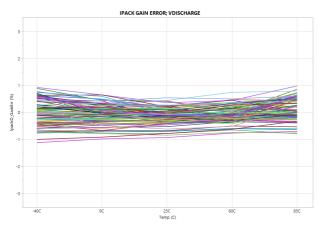

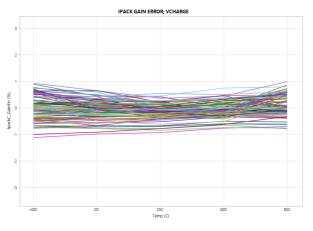

| I <sub>PACK</sub> Gain Error                                       | I <sub>PACK_GE</sub>    | Vdischarge = 10mV to 50mV;<br>Vcharge = -10mV to -50mV   | -3          | ±0.5  | 3    | %      |

| I <sub>PACK</sub> Charge Detect<br>(CHRGI)                         | I <sub>CHRGI</sub>      | Digital Compare (0x012E)                                 |             | -0.6  |      | mV     |

| I <sub>PACK</sub> Discharge Detect<br>(DCHRGI)                     | I <sub>DCHRGI</sub>     | Digital Compare (0x012E)                                 |             | 0.6   |      | mV     |

| I <sub>PACK</sub> Threshold (xCSP -                                | CSN)                    |                                                          |             |       |      |        |

| DSC Hysteresis<br>(DCSP-CSN)                                       | DSC <sub>Hys</sub>      |                                                          |             | 12    |      | mV     |

| Charge Short-Circuit<br>Voltage Analog Compare<br>Range (CCSP-CSN) | CSC                     |                                                          |             | -200  |      | mV     |

| CSC Hysteresis<br>(CCSP-CSN)                                       | CSC <sub>Hys</sub>      |                                                          |             | 12    |      | mV     |

| CSC Delay (CCSP-CSN)                                               | CSC <sub>dly</sub>      |                                                          |             | 0.1   |      | ms     |

| V <sub>Pack</sub>                                                  | _                       |                                                          |             |       | _    |        |

| VPACK Attenuation                                                  | V <sub>PACKAttn</sub>   |                                                          |             | 40    |      | V/V    |

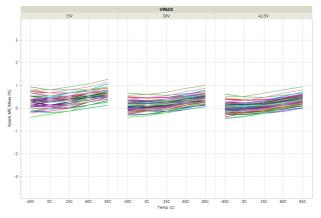

| VPACK Measurement<br>Error                                         | V <sub>PACK_ME</sub>    | 15V < VPACK < 42.5V                                      |             | ±0.5  |      | %      |

| VPACK Measurement<br>Error TC                                      | V <sub>PACKME_TC</sub>  |                                                          |             | ±100  |      | ppm/°C |

| V <sub>TEMP</sub>                                                  |                         |                                                          |             |       |      |        |

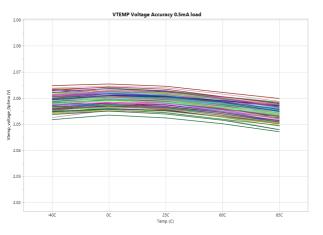

| V <sub>TEMP</sub> Voltage Accuracy                                 |                         | 0.5mA load                                               | 2.03        | 2.06  | 2.09 | V      |

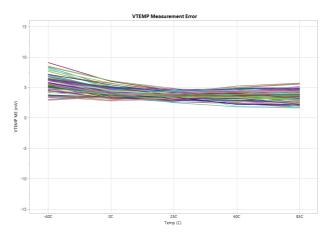

| V <sub>TEMP</sub> Measurement<br>Error                             | V <sub>VTEMP_ME</sub>   |                                                          |             | ±4.5  |      | mV     |

| Settling Time for VTEMP<br>before a THERM1,<br>THERM2 measurement  | t <sub>VTEMP</sub>      | V <sub>TEMP</sub> Turn ON to 1st thermistor measurement. |             | 18    |      | ms     |

| V <sub>TEMP</sub> Threshold                                        | •                       |                                                          | · · · · · · |       | •    | ·      |

| V <sub>TEMP</sub> Max Threshold                                    | V <sub>TEMP_max</sub>   | Code > 0x06CC = OWF                                      |             | 2.253 |      | V      |

| V <sub>TEMP</sub> Min Threshold                                    | V <sub>TEMP_min</sub>   | Code < 0x0533 = OWF                                      |             | 1.843 |      | V      |

| Thermistor                                                         |                         |                                                          | · .         |       | ·    |        |

| Thermistor Leakage<br>Current                                      |                         |                                                          | -1          |       | 1    | μA     |

|                                                                    | 1                       |                                                          |             |       | 1    |        |

| Parameter                                                                     | Symbol                | Test Conditions                                                                                                             | Min   | Тур          | Мах   | Units |

|-------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|--------------|-------|-------|

| Open-Wire Threshold<br>Code                                                   | OW <sub>VTHERM</sub>  | Code greater than<br>0x0FD7 = OWF                                                                                           |       | 1.9          |       | V     |

| RESET Voltage<br>Threshold (THERM2)                                           | RST <sub>VTHERM</sub> | Threshold Voltage above V2P5.                                                                                               |       | 0.4          |       | V     |

| RESET time (THERM2)                                                           | t <sub>RESET</sub>    | The time the THERM2 pin is above RST <sub>VTHERM</sub> before the device resets                                             |       | 500          |       | ms    |

| Power-On Reset Startup<br>Time to the completion of<br>the first system scan. | t <sub>StartUp</sub>  | VPACK > V <sub>POR</sub> , RESET falling<br>edge or soft reset or exiting LOW<br>POWER Mode to the first<br>measure command |       |              | 100   | ms    |

| Thermistor Measurement<br>Error                                               | THERM <sub>ME</sub>   | VTHERMx = 1V                                                                                                                |       | ±4           |       | mV    |

| Internal Over-Temperatur                                                      | re Sensor             |                                                                                                                             |       |              |       |       |

| Internal Temperature<br>Sensor Output Code                                    |                       | @25C                                                                                                                        |       | 1577         |       | Bits  |

| Internal<br>Over-Temperature<br>Threshold                                     | IOT                   | Analog Comparator                                                                                                           |       | 100          |       | с     |

| V3P3 Regulator                                                                |                       |                                                                                                                             |       |              |       | •     |

| Regulation Voltage<br>Accuracy                                                | V3P3 <sub>V</sub>     | At V3P3 Pin, 0-5mA load                                                                                                     | 3.201 | 3.32         | 3.399 | V     |

| Pin Measurement Error                                                         | REG <sub>ME</sub>     |                                                                                                                             |       | ±7.5         |       | mV    |

| V3P3 & V2P5 Thresholds                                                        |                       |                                                                                                                             |       |              |       | •     |

| V3P3 Overvoltage<br>Threshold                                                 | dV3P3 <sub>OV</sub>   | Digital Comparator (Self Test)<br>(0xBE0)                                                                                   |       | 3.553        |       | V     |

| V3P3 Undervoltage<br>Threshold                                                | dV3P3 <sub>UV</sub>   | Digital Comparator (Self Test)<br>(0x999)                                                                                   |       | 2.97         |       | V     |

| V3P3 Power-Good OV<br>Threshold                                               | PG <sub>V3P3_OV</sub> | Analog Comparator                                                                                                           |       | 3.8          |       | V     |

| V3P3 Power-Good UV<br>Threshold                                               | PG <sub>V3P3_UV</sub> | Analog Comparator                                                                                                           |       | 2.57         |       | V     |

| V2P5 Overvoltage<br>Threshold                                                 | dV2P5 <sub>OV</sub>   | Digital Comparator (Self Test)<br>(0x8BD)                                                                                   |       | 2.75         |       | V     |

| V2P5 Undervoltage<br>Threshold                                                | dV2P5 <sub>UV</sub>   | Digital Comparator (Self Test)<br>(0x6CA)                                                                                   |       | 2.25         |       | V     |

| V2P5 Power-Good OV<br>Threshold                                               | PG <sub>V2P5_OV</sub> | Analog Comparator                                                                                                           |       | 2.8          |       | V     |

| V2P5 Power-Good UV<br>Threshold                                               | PG <sub>V2P5_UV</sub> | Analog Comparator                                                                                                           |       | 2.0          |       | V     |

| Low-Side FET Drivers (L                                                       | CFET and LDF          | ET)                                                                                                                         |       |              |       |       |

| Pull-Up Voltage                                                               | LxFET <sub>GV</sub>   | LxFET En = 1, VPACK >11V                                                                                                    | 9     | 10.5         | 12    | V     |

| i un-op vollage                                                               | LVLEIGA               | LxFET En = 1, VPACK <11V                                                                                                    |       | VPACK - 1.5V |       | V     |

| LxFET Pull-Up<br>Resistance                                                   | R <sub>LxFET</sub>    | LxFET En = 1                                                                                                                |       | 6            |       | kΩ    |

| Parameter                             | Symbol                 | Test Conditions                                         | Min | Тур  | Max | Units |

|---------------------------------------|------------------------|---------------------------------------------------------|-----|------|-----|-------|

| LCFET Pull-Down<br>Resistance         | R <sub>LCFET</sub>     | First 500µs after LCFET_EN = 0<br>(to VSS)              |     | 2.3  |     | kΩ    |

| LCFET Off-Resistance                  | R <sub>LCFET_OFF</sub> | Beyond 500µs after LCFET<br>En = 0                      |     | 1    |     | MΩ    |

| LDFET Pull-Down to<br>VSS Resistance  | R <sub>LDFET</sub>     |                                                         |     | 2.5  |     | kΩ    |

| LxFET Input Low<br>Threshold (Status) | LxFET <sub>VIL</sub>   | LxFET - VSS<br>(Pin Voltage, Falling Edge)              |     | 1.62 |     | V     |

| LxFET Input Hysteresis<br>(Status)    | LxFET <sub>HY</sub>    |                                                         |     | 350  |     | mV    |

| Charge Detection Monite               | or (CHMON)             |                                                         |     |      |     | •     |

| Charge Detection<br>Threshold         | V <sub>CHTHR</sub>     | Falling Edge, V <sub>CHMON</sub> - V <sub>SS</sub>      | 0.8 | 1.2  | 1.6 | V     |

| Charge Detection<br>Hysteresis        | V <sub>CHHys</sub>     |                                                         |     | 100  |     | mV    |

| CHMON Detection<br>Current            | CH <sub>DC</sub>       | CHMON ON (>3V), into pin                                |     | 3    |     | μΑ    |

| CHMON Pin Internal<br>Pull-Down       | R <sub>CHPD</sub>      | 0V to VPACK; CHMON OFF                                  |     | 15   |     | MΩ    |

| Charge Monitor<br>Debounce            | t <sub>CHdb</sub>      | The time the pin is in a state before the device reacts |     | 4    |     | ms    |

| CHMON Enable Delay<br>Time            | t <sub>CHEN</sub>      | FET(s) off to CHMON Detect                              |     | 100  |     | ms    |

| Load Detection Monitor                | (LDMON)                |                                                         |     |      |     |       |

| Load Detection<br>Threshold           | V <sub>LDThr</sub>     | Rising Edge, VPACK - V <sub>LDMON</sub>                 | 0.9 | 1.5  | 1.8 | V     |

| Load Detection<br>Hysteresis          | V <sub>LDHys</sub>     |                                                         |     | 100  |     | mV    |

| LDMON Pull-down<br>Resistance         | R <sub>LDPD</sub>      | From LDMON to VSS                                       | 0.7 | 1    | 1.2 | MΩ    |

| LDMON Enable Delay<br>Time            | t <sub>LDEN</sub>      | FET(s) off to LDMON Detect                              |     | 100  |     | ms    |

| Open-Wire                             | ·                      |                                                         |     |      |     |       |

| Open-Wire Current                     | CUR <sub>OW</sub>      | From VC pin to VSS                                      |     | 275  |     | μA    |

| Open-Wire Detection<br>Time           | t <sub>OWON</sub>      | Open-wire current source on-time                        |     | 15   |     | ms    |

| Open-Wire ADC read<br>time            |                        | Reference to OW Assertion. Time to first compare        |     | 10   |     | ms    |

| Detection Threshold<br>(Cells)        | V <sub>OWth1</sub>     | All VCells (ADC code 0x0058)                            |     | 0.6  |     | V     |

| Detection Threshold<br>(VSS)          | V <sub>OWth3</sub>     | VSS - VC1                                               |     | 0.25 |     | V     |

| Detection Threshold<br>(VPACK)        | V <sub>OWth2</sub>     | VC10 - VPACK                                            |     | 0.5  |     | V     |

| Parameter                                                              | Symbol                    | Test Conditions                                                                                                                     | Min                  | Тур                   | Max                   | Units |

|------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|-----------------------|-------|

| System                                                                 | L                         |                                                                                                                                     |                      |                       |                       |       |

| 4MHz Oscillator<br>Accuracy                                            |                           |                                                                                                                                     | -7.5                 |                       | 7.5                   | %     |

| 31.5kHz Oscillator<br>Accuracy                                         |                           |                                                                                                                                     | -25                  |                       | 25                    | %     |

| ALERT                                                                  | I                         |                                                                                                                                     |                      |                       |                       |       |

| ALERT Low-Level<br>Output Voltage                                      | AT <sub>VOL</sub>         | I <sub>sink</sub> = 2mA                                                                                                             |                      | 0.25                  | 0.6                   | V     |

| ALERT Low-Level Input<br>Voltage                                       | AT <sub>VIL</sub>         |                                                                                                                                     | 0                    |                       | 0.8                   | V     |

| ALERT Leakage Current                                                  | AT <sub>LIH</sub>         | ALERT = 0V to 3.3V                                                                                                                  | -1                   | ±0.25                 | 1                     | μA    |

| HVGPIO                                                                 |                           |                                                                                                                                     |                      |                       |                       |       |

| HVGPIO Low-Level<br>Output Voltage                                     | HVGPIO <sub>VOL</sub>     | I <sub>sink</sub> = 2mA;                                                                                                            |                      | 0.1                   | 0.6                   | V     |

| HVGPIO Low-Level Input<br>Voltage                                      | HVGPIO <sub>VIL</sub>     |                                                                                                                                     | 0                    |                       | 0.8                   | V     |

| HVGPIO Leakage<br>Current                                              | HVGPIO <sub>LIH</sub>     | HVGPIO = VPACK                                                                                                                      |                      |                       | 1                     | μA    |

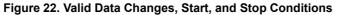

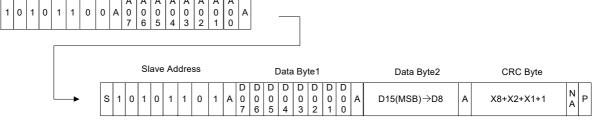

| I <sup>2</sup> C Interface Specificatio                                | ns                        |                                                                                                                                     |                      |                       |                       |       |

| SDA and SCL Input<br>Buffer LOW Voltage                                | V <sub>IL</sub>           |                                                                                                                                     | -0.3                 |                       | 0.3×V3p3              | V     |

| SDA and SCL Input<br>Buffer HIGH Voltage                               | V <sub>IH</sub>           |                                                                                                                                     | 0.7×V <sub>3p3</sub> |                       | V <sub>3p3</sub> +0.3 | V     |

| SDA and SCL Input<br>Buffer Hysteresis                                 | I2C <sub>Hysteresis</sub> |                                                                                                                                     |                      | 0.05xV <sub>3p3</sub> |                       | V     |

| SDA Output Buffer LOW<br>Voltage                                       | V <sub>OL</sub>           | Sinking 2mA                                                                                                                         | 0                    | 0.25                  | 0.6                   | V     |

| Pin Leakage Current for<br>SDA and SCL Pins                            | l <sub>leak</sub>         |                                                                                                                                     | -1                   |                       | 1                     | μA    |

| SCL Frequency                                                          | f <sub>SCL</sub>          |                                                                                                                                     |                      |                       | 400                   | kHz   |

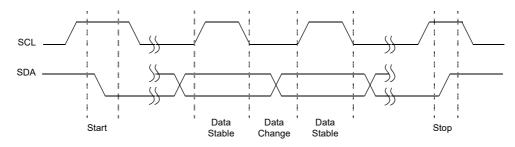

| Pulse Width Suppression<br>Time at SDA and SCL<br>Inputs               | t <sub>IN</sub>           | Any pulse narrower than the max spec is suppressed                                                                                  |                      |                       | 50                    | ns    |

| SCL Falling Edge to SDA<br>Output Data Valid                           | t <sub>AA</sub>           | SCL falling edge crossing 30% of $V_{DD}$ , until SDA exits the 30% to 70% of $V_{DD}$ window                                       |                      |                       | 900                   | ns    |

| Time the Bus Must be<br>Free Before the Start of a<br>New Transmission | t <sub>BUF</sub>          | SDA crossing 70% of $V_{DD}$ during<br>a STOP condition, to SDA<br>crossing 70% of $V_{DD}$ during the<br>following START condition | 1300                 |                       |                       | ns    |

| Clock LOW Time                                                         | t <sub>LOW</sub>          | Measured at the 30% of V <sub>DD</sub> crossing                                                                                     | 1300                 |                       |                       | ns    |

| Clock HIGH Time                                                        | t <sub>HIGH</sub>         | Measured at the 70% of V <sub>DD</sub> crossing                                                                                     | 600                  |                       |                       | ns    |

#### RAA489220 Datasheet

| T <sub>A</sub> = +25°C, VPACK = 36V; VCell = 3.6V, DGND = VSS = 0V, unless otherwise specified. All voltages are with resp | ect to VSS.           |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------|

|                                                                                                                            | <i>,</i> or to v 000. |

| Parameter                                                                  | Symbol                             | Test Conditions                                                                                                                                                                        | Min           | Тур | Max | Units |

|----------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|-----|-------|

| SDA Low Timeout<br>I <sup>2</sup> C communication is<br>reset bus released | t <sub>timeout</sub>               |                                                                                                                                                                                        | 25            | 32  |     | ms    |

| 8th Bit to ACK Bit Delay<br>(Applies to reading ADC<br>Output Data Only)   | I <sup>2</sup> C_t <sub>WAIT</sub> | Time between the rising edge of<br>the clock pulse corresponding to<br>the last bit of any byte, and the<br>falling edge of the clock pulse<br>corresponding to the<br>Acknowledge bit | 7             |     |     | μs    |

| START Condition Setup<br>Time                                              | t <sub>SU:STA</sub>                | SCL rising edge to SDA falling edge. Both crossing 70% of $\rm V_{\rm DD}$                                                                                                             | 600           |     |     | ns    |

| START Condition Hold<br>Time                                               | t <sub>HD:STA</sub>                | From SDA falling edge crossing 30% of $V_{DD}$ to SCL falling edge crossing 70% of $V_{DD}$                                                                                            | 600           |     |     | ns    |

| Input Data Setup Time                                                      | t <sub>SU:DAT</sub>                | From SDA exiting the 30% to 70% of $V_{DD}$ window, to SCL rising edge crossing 30% of $V_{DD}$                                                                                        | 100           |     |     | ns    |

| Input Data Hold Time                                                       | t <sub>HD:DAT</sub>                | From SCL falling edge crossing 30% of $V_{DD}$ to SDA entering the 30% to 70% of $V_{DD}$ window                                                                                       | 20            |     | 900 | ns    |

| STOP Condition Setup<br>Time                                               | t <sub>SU:STO</sub>                | From SCL rising edge crossing 70% of $V_{DD}$ , to SDA rising edge crossing 30% of $V_{DD}$                                                                                            | 600           | 17  |     | ns    |

| STOP Condition Hold<br>Time                                                | t <sub>HD:STO</sub>                | From SDA rising edge to SCL falling edge. Both crossing 70% of $V_{\text{DD}}$                                                                                                         | 600           | 45  |     | ns    |

| Output Data Hold Time                                                      | t <sub>DH</sub>                    | From SCL falling edge crossing $30\%$ of V <sub>DD</sub> , until SDA enters the $30\%$ to 70% of V <sub>DD</sub> window                                                                | 0             | 150 |     | ns    |

| SDA and SCL Rise Time                                                      | t <sub>R</sub>                     | From 30% to 70% of V <sub>DD</sub>                                                                                                                                                     | 20+0.1x<br>Cb |     | 300 | ns    |

| SDA and SCL Fall Time                                                      | t <sub>F</sub>                     | From 70% to 30% of V <sub>DD</sub>                                                                                                                                                     | 20+0.1x<br>Cb |     | 300 | ns    |

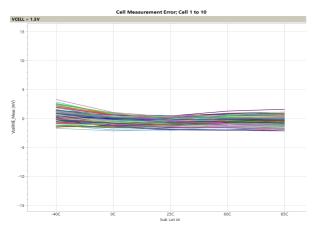

# 4. Typical Performance Curves

Figure 3. Average Cell ME at 1.5V

Figure 4. Average Cell ME at 3.0V

Figure 5. Average Cell ME at 4.25V

Figure 6. VPACK Pin Voltage ME

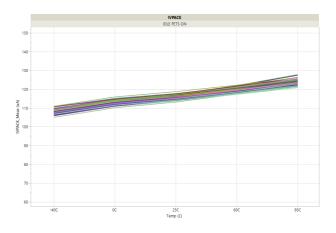

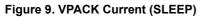

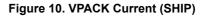

Figure 7. VPACK Current (SCAN, FETS on)

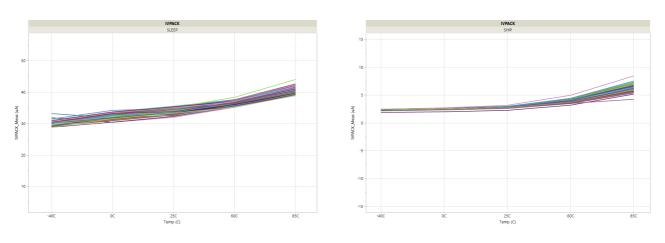

Figure 8. VPACK Current (IDLE, FETS on)

Figure 11. Discharge Current GE

Figure 13. VTEMP Pin Voltage

Figure 12. Charge Current GE

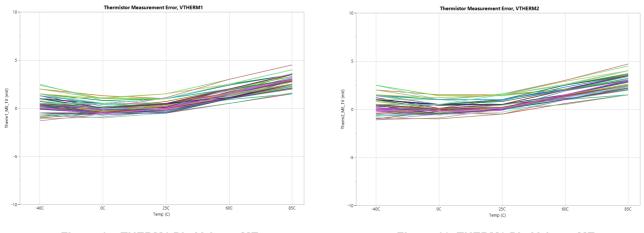

Figure 14. VTEMP Pin Voltage ME

Figure 15. THERM1 Pin Voltage ME

Figure 16. THERM2 Pin Voltage ME

# 5. State Machine Overview

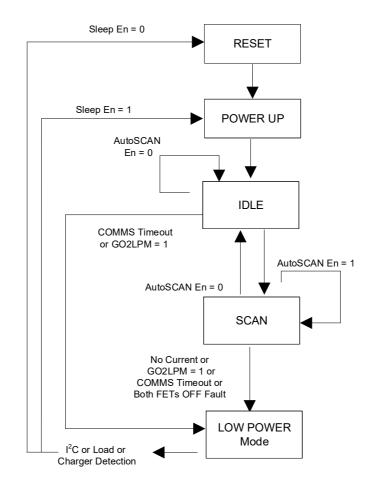

The State Machine flow diagram is illustrated in Figure 17. This diagram shows the relationships between the device States and Modes. A State executes its function and then moves to the next state or Mode, while Modes can loop or remain static until another function or status change forces a transition out of the Mode.

Figure 17. State Machine Flow Diagram

### 5.1 Reset State

At initial device power-up, the RAA489220 enters the RESET State. This state has the highest priority and is initiated by a momentary connection of the THERM2 pin to the V3P3 pin (Hard RESET) or a VPACK voltage lower than V<sub>POR</sub> (page 8) or the V2P5 or V3P3 voltages (page 10) falling below their Power On Reset (POR) thresholds. A RESET interrupts any action the device is performing. Entering the RESET State also occurs when exiting the LOW POWER Mode if the bit 0x80.7 Sleep En is clear or from a Soft RESET (0x40.7 Soft Reset).

The device turns off all regulators and oscillators when entering this state from a Hard RESET or Soft RESET. On completion of RESET, the device transitions to the Power Up State.

### 5.2 Power Up State

The Power Up State is entered from the RESET State, or LOW POWER Mode if the bit 0x80.7 Sleep En is set. This state prepares the device for normal operation by executing device initialization followed by a self test that checks the status of the IC.

The device turns on and checks the 4MHz oscillator and initializes logic states. It then reads trim/fuse settings, checks for pin faults, powers the monitor pins, powers the analog comparators and measurement amps, and enables the FET driver and the ADC. Any faults detected in the Power Up State, set the bit 0x10.10 STF and force the device to transition to LOW POWER Mode.

When successful completion of initialization and self test (no faults that force both power FETs to turn OFF) occurs, the device transitions to IDLE Mode.

### 5.3 IDLE Mode

By default the MCU is in control of the system with the device in IDLE Mode (bit 0x80.8 AutoSCAN En is clear unless otherwise noted). The MCU is responsible for triggering device measurements, enabling/disabling the power FETs and fault reaction. Faults detected in this state do not automatically turn off the power FETs, except for short-circuit detections.

In IDLE Mode, the device executes commands from the MCU. The MCU is responsible for the state of the power FETs and acting on faults or status changes. Section Fault Detection and Recovery lists the analog and digital faults. The ALERT pin asserts for faults and can assert for status bits provided the respective mask bit is cleared (see 0x81 OV and EOC Thresholds).

Communication timeout in IDLE Mode is controlled by bits 0x80.[14:13] Communication TO. If the SDA pin does not make a high to low transition while the SCL pin is high within the selected period of time, the device transitions to LOW POWER Mode. Setting bit 0x40.5 Go2LPM to 1 also transitions the device to LP Mode.

Executing 0x41.7 Trigger Measurement causes a temporary transition to SCAN Mode to execute the 0x41.[4:0] Measurement Selection. When completed, the device transitions back to IDLE Mode to await the next MCU instruction.

Setting bit 0x80.8 AutoSCAN En to 1 causes the device to transition to SCAN Mode. Renesas recommends setting 0x40.6 Clear All Faults to 1 before enabling AutoSCAN to initialize counters to 0.

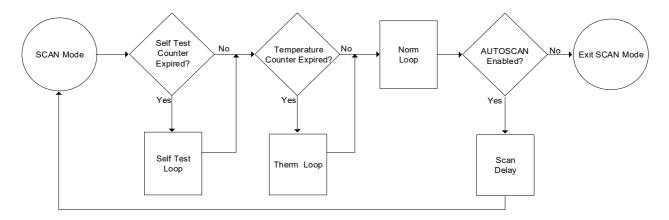

## 5.4 SCAN Mode

SCAN Mode operation is dependent on the setting of the AutoSCAN Enable bit. If the bit is clear (default), the device enters SCAN from IDLE when a measurement is triggered, and remains in SCAN Mode until the triggered measurement completes, then it transitions back to IDLE. If the AutoSCAN Enable bit is set to 1, the device continuously loops through the system scan sequence (Figure 18) and remains in SCAN Mode. The only exceptions to these two cases is a fault or Go2LPM instruction, which causes a transition to LP Mode.

In SCAN Mode with AutoSCAN enabled, the device continuously performs a scan sequence that measures the pack current, pack and cell voltages during each scan (Normal Loop). Every four scans, the thermistor voltages are measured. Every 100 scans, a series of self tests are executed. Measurement results are compared to the

relevant thresholds during each scan they are executed. If the pack current is too low to register either a 0x11.0 CHRGI or 0x11.1 DCHRGI for more than six complete system scans, the device transitions to LP Mode.

If a fault is detected during AutoSCAN that requires both power FETs to turn OFF, the device asserts the ALERT pin to signal the MCU to read the fault and status registers, then transitions to LP Mode after a 100ms delay. During the transition, no other functions are allowed.

After exiting LP back to IDLE Mode, the MCU should issue a 0x40.6 Clear All Faults to initialize counters to 0.

Communications Timeout is active in both IDLE and SCAN Modes. The MCU has to initiate communication with the device within the selected time period (0x80.[14:13] Communication TO). Allowing the communication timer to expire causes a transition from IDLE or SCAN to LOW POWER Mode.

Figure 18. System Scan Sequence

### 5.5 LOW POWER Mode

The RAA489220 consumes the lowest current in LOW POWER (LP) Mode. Power FETs and non-essential circuitry are OFF. In LP Mode, the device waits for a 0x11.3 CH PRESI or 0x11.2 LD PRESI bit transition from low to high to exit. Asserting the SDA pin while the SCL pin is high also exits this state.

The device transitions to LP Mode when any faults that require both power FETs to turn OFF, when a communication timeout occurs, when the bit 0x40.5 Go2LPM is set to 1, or if a sufficient number of scans with no current flow is detected.

Entry into LP Mode turns off both power FETs and stops the communication timeout timer. The ALERT pin is asserted, and then the state does nothing for 100ms before proceeding to turn OFF the remainder of the sub blocks. The 100ms time delay allows the MCU to read the fault and status registers and prepare itself for LP Mode. No other functions are allowed during this 100ms.

Two bits control power dissipation during and status on exit from LP Mode. The regulator has two possible settings in this Mode (see 0x42.13 LP Regulator) one keeps it fully enabled, and the other reduces current consumption to a minimum. The 0x80.7 Sleep En determines if register settings are retained in LP Mode and which state the device exits to. The lowest powered state of the device is selected by setting both LP Reg and Sleep En bits to 0, see Table 1.

When the Sleep En bit is set to 0, the register values are not retained in LP Mode, and the device exits to the RESET state. If the Sleep En bit is set to 1, the register values are retained in LP Mode, and the device exits to the Power Up state. If the LP Reg bit is clear, only the weak regulator is enabled, so register values may or may not be retained.

After exiting LOW POWER back to IDLE Mode, the MCU should issue a 0x40.6 Clear All Faults to initialize counters to 0.

| Table 1 | l. LP | Mode | Settings |

|---------|-------|------|----------|

|---------|-------|------|----------|

| LP REG<br>(0x42.13) | Sleep En<br>(0x80.7) | Result                                                                          |  |  |

|---------------------|----------------------|---------------------------------------------------------------------------------|--|--|

| 0                   | 0                    | Lowest Power, Weak Regulators; Register values are not retained                 |  |  |

| 0                   | 1                    | Weak Regulators; Register values may or may not be retained                     |  |  |

| 1                   | 0                    | Strong Regulator; Register values are not retained                              |  |  |

| 1                   | 1                    | Strong Regulator; Register and counter values are retained; VTEMP can be Active |  |  |

# 6. FAULTS

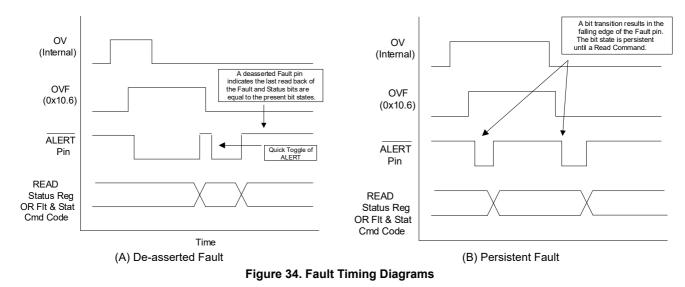

### 6.1 Fault Detection and Recovery

A fault is reported when the related fault threshold is exceeded for consecutive readings. For digital comparisons fault delay is implemented with counters that are incremented for consecutive faulty readings; for analog comparisons, fault delay is accomplished with timers. These counters/timers are cleared if the fault condition clears before they reach their limit(s).

A counter is incremented each time the device detects a fault while in SCAN Mode. If the fault counter exceeds the threshold, the device sets the respective fault bit and then transitions to LP Mode.

When an analog comparison threshold is exceeded a timer is started. If the timer also exceeds its threshold, the device sets the respective fault bit and then transitions to LP Mode.

When a fault is reported, action is taken to turn OFF the respective FET(s). Table 2, Table 4, and Table 5 show the power FET action related to specific fault conditions. These tables list the number of consecutive faults required before setting the fault bit.

Faults that only turn OFF one power FET have recovery thresholds. Recovery thresholds are compared to the most recent measurement as long as the fault is present. Cell over/undervoltage, and charge over/under-temperature faults have separate recovery thresholds. The recovery threshold is fixed relative to the fault detection threshold voltage plus/minus a hysteresis. Overvoltage and charge over-temperature recovery thresholds are defined as the original threshold minus the respective hysteresis threshold. Under-temperature and undervoltage recovery thresholds are defined as the original threshold minus the respective hysteresis value. If a measurement parameter does not have a recovery threshold, the fault detection threshold is also used for the recovery limit.

If a fault detection occurs during a thermistor, cell voltage, or pack current measurement as part of a system scan, the device completes the scan before dropping to LP Mode.

During the first and every 100th scan that follows, the Self Test Loop is executed. A Self Test fault (0x10.10 STF) requires two consecutive detections to set. The device executes the Self Test Loop twice to determine if a fault is present. If a fault is present with each check, the fault is set and the device transition to LP Mode.

# 6.2 Power FET Fault Response

The following tables show the FET reaction for each specific fault. Table 2 details the fault response for Self Test (if enabled) digital compare faults that have no dependency on the power FET configuration bit 0x82.7 CPWR. Digital Compares occur following a measurement while in Scan Mode and require consecutive violations to set the fault bit. Table 3 details the fault response for analog compare faults that have no dependency on the CPWR bit. Analog compares do not require measurements and include debounce timers.

| FAULT        | FET  | State |              | Seq Count | Comments                        |

|--------------|------|-------|--------------|-----------|---------------------------------|

| (Fault Flag) | CFET | DFET  | Compare Type | Seq Count | Comments                        |

| V3P3 (REGF)  | Off  | Off   | Digital      | 2         |                                 |

| V2P5 (REGF)  | Off  | Off   | Digital      | 2         |                                 |

| VBG2 (REGF)  | Off  | Off   | Digital      | 2         | Device controls<br>FETs only in |

| OWF          | Off  | Off   | Digital      | 2         | AutoSCAN Mode                   |

| VTMPF        | Off  | Off   | Digital      | 2         |                                 |

| OW THERM     | Off  | Off   | Digital      | 2         |                                 |

#### Table 2. Self Test Fault Response

#### Table 3. Analog Fault Response

| FAULT                                  | FET State |      | Compare | Time Base | Debounce            | Comments                                                                                              |  |  |

|----------------------------------------|-----------|------|---------|-----------|---------------------|-------------------------------------------------------------------------------------------------------|--|--|

| (Flag)                                 | CFET      | DFET | Туре    |           | Rise/Fall Time (ms) | comments                                                                                              |  |  |

| Oscillator,<br>VPACK & VSS<br>OW (STF) | Off       | Off  | Analog  | No        | 0.5                 | Device controls FETs in SCAN and IDL<br>Modes.                                                        |  |  |

| СОММТО                                 | Off       | Off  | Timer   | Yes       | 0x80.[13:12]        | An STF, COMMTO or SCF disables the                                                                    |  |  |

| DSCF (SCF)                             | Off       | Off  | Analog  | No        | 0x83.[15:14]        | FETs and forces a transition to Low-Power<br>Mode.                                                    |  |  |

| CSCF (SCF)                             | Off       | Off  | Analog  | No        | 0.1/ 0.1            |                                                                                                       |  |  |

| V3P3F                                  | Off       | Off  | Analog  | No        | 1/1                 | A low level detection sets state machine to<br>WAIT<br>Device controls FETs in SCAN and IDLE<br>Modes |  |  |

| V2P5                                   | Off       | Off  | Analog  | No        | 1/0.002             | A low level detection triggers POR                                                                    |  |  |

| IOTF                                   | Off       | Off  | Analog  | No        | 1/ 1                | Device controls FETs in SCAN and IDLE<br>Modes                                                        |  |  |

The power FET fault response for the parallel FET configuration setting (CPWR = 1) is shown in Table 4.

The power FET fault response for the series FET configuration setting (CPWR = 0) is shown in Table 5.

The RAA489220 controls the FETs when bit 0x80.8 AutoSCAN En is enabled for CPWR dependent faults; otherwise, the MCU is expected to control the power FETs in IDLE Mode.

| CPWR = 1     | Power FET State |      |                         | Number    | Comments                                   |

|--------------|-----------------|------|-------------------------|-----------|--------------------------------------------|

| FAULT (Flag) | CFET            | DFET | Delay Time(s)           | Of Faults | Comments                                   |

| DOT (OTF)    | Off             | Off  | 0x80.[10:9] Fault Delay | 2         |                                            |

| COT (OTF)    | Off             | On   | 0x80.[12:11] Scan Delay | 2         |                                            |

| CUT (UTF)    | Off             | On   | 0x80.[12:11] Scan Delay | 2         |                                            |

| DUT (UTF)    | Off             | Off  | 0x80.[10:9] Fault Delay | 2         |                                            |

| OVLO (OVF)   | Off             | Off  | 0x80.[10:9] Fault Delay | 2         |                                            |

| OV (OVF)     | Off             | On   | 0x80.[12:11] Scan Delay | 2         | CPWR=1 FET Fault response is not dependent |

| UV (UVF)     | On              | Off  | 0x80.[12:11] Scan Delay | 2         | on current direction bits                  |

| UVLO (UVF)   | Off             | Off  | 0x80.[10:9] Fault Delay | 2         |                                            |

| DCVF         | Off             | Off  | 0x80.[10:9] Fault Delay | 8         |                                            |

| IEOC         | Off             | On   | 0x80.[12:11] Scan Delay | 2         |                                            |

| DOCF         | Off             | Off  | 0x80.[12:11] Scan Delay | 8         |                                            |

| COCF         | OFF             | OFF  | 0x80.[12:11] Scan Delay | 8         |                                            |

#### Table 4. Parallel FET Digital Fault Response

#### Table 5. Series FET Digital Fault Response

| CPWR = 0            | Current | urrent Direction |      | State |                         | Number       | _                                              |

|---------------------|---------|------------------|------|-------|-------------------------|--------------|------------------------------------------------|

| FAULT (Flag)        | CHRGI   | DCHRGI           | CFET | DFET  | Delay Time(s)           | Of<br>Faults | Comments                                       |

| DOT (OTF)           | Х       | х                | Off  | Off   | 0x80.[10:9] Fault Delay | 2            |                                                |

| COT (OTF)           | 0       | 1                | On   | On    | N/A                     | N/A          |                                                |

| COT (OTF)           | х       | 0                | Off  | On    | 0x80.[12:11] Scan Delay | 2            | FETs remain on as long as a                    |

| CUT (UTF)           | 0       | 1                | On   | On    | N/A                     | N/A          | discharge current is detected (0x11.1 DCHRGI). |

| CUT (UTF)           | х       | 0                | Off  | On    | 0x80.[12:11] Scan Delay | 2            |                                                |

| DUT (UTF)           | х       | Х                | Off  | Off   | 0x80.[10:9] Fault Delay | 2            |                                                |

| OVLO (OVF & LOF)    | х       | х                | Off  | Off   | 0x80.[10:9] Fault Delay | 2            |                                                |

| OV (OVF)            | 0       | 1                | On   | On    | N/A                     | N/A          | FETs remain on as long as a                    |

| OV (OVF)            | х       | 0                | Off  | On    | 0x80.[12:11] Scan Delay | 2            | discharge current is detected (0x11.1 DCHRGI). |

| UV (UVF)            | 1       | 0                | On   | On    | N/A                     | N/A          | FETs remain on as long as a                    |

| UV (UVF)            | 0       | Х                | On   | Off   | 0x80.[12:11] Scan Delay | 2            | charge current is detected (0x11.0 CHRGI).     |

| UVLO (UVF &<br>LOF) | x       | х                | Off  | Off   | 0x80.[10:9] Fault Delay | 2            |                                                |

| DCVF                | х       | Х                | Off  | Off   | 0x80.[10:9] Fault Delay | 8            |                                                |

| IEOC                | х       | Х                | Off  | Off   | 0x80.[12:11] Scan Delay | 2            |                                                |

| DOCF                | х       | 1                | Off  | Off   | 0x80.[12:11] Scan Delay | 8            |                                                |

| COCF                | 1       | х                | Off  | Off   | 0x80.[12:11] Scan Delay | 8            |                                                |

# 7. System Registers

| Addr<br>(Hex) | Register<br>Name                                         | Pg# | Register Description <sup>[1]</sup>                                                                                                                                                                                                                                                                                                                                | Default<br>(Hex)                           |

|---------------|----------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

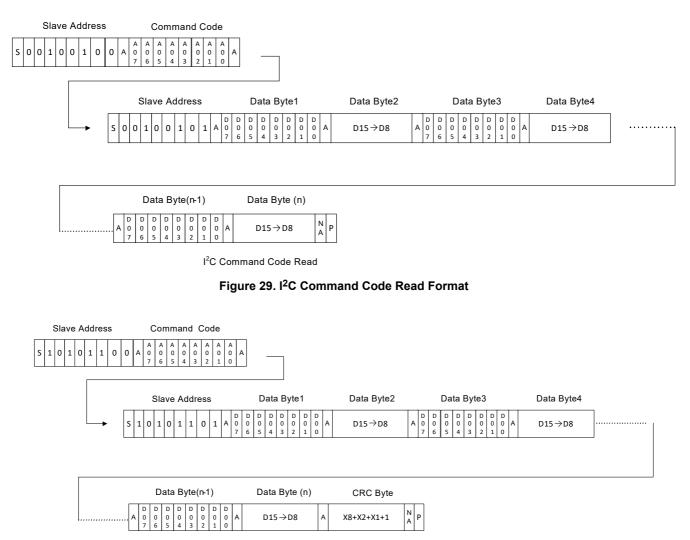

| Measu         | rement Results (RO)                                      | •   |                                                                                                                                                                                                                                                                                                                                                                    |                                            |