# Hardware

# V850ES/Fx3

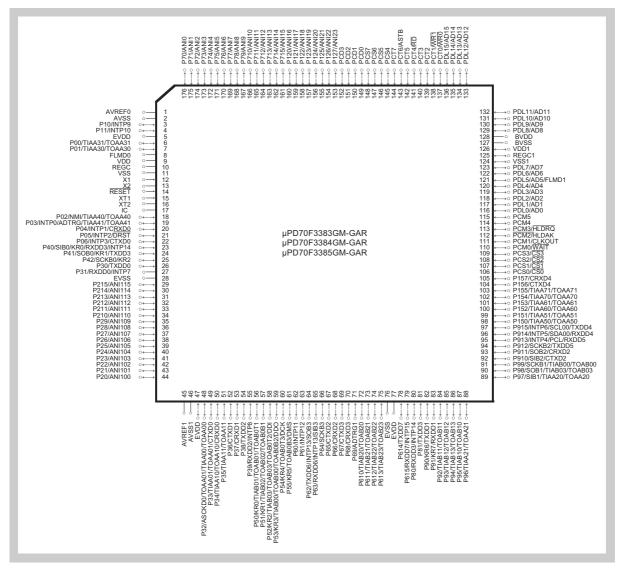

32-bit Single-Chip Microcontroller

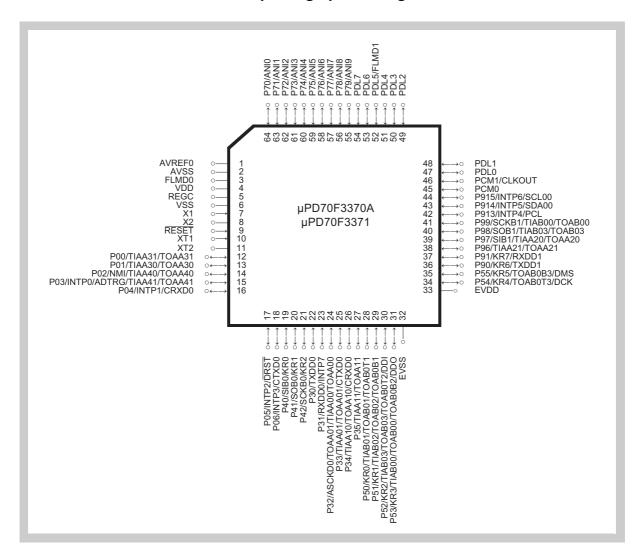

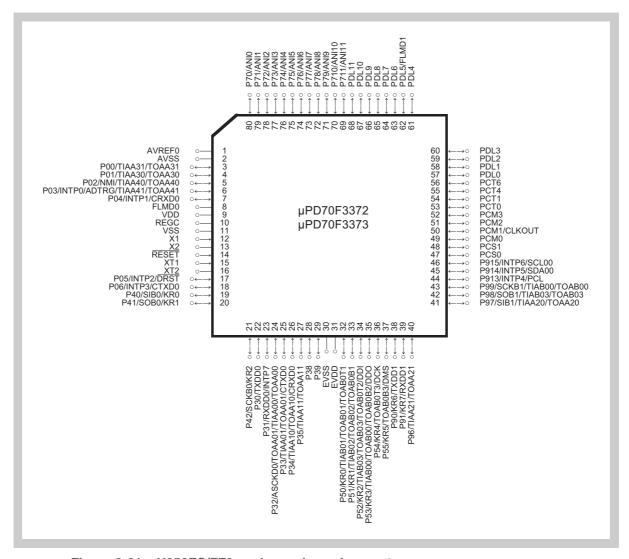

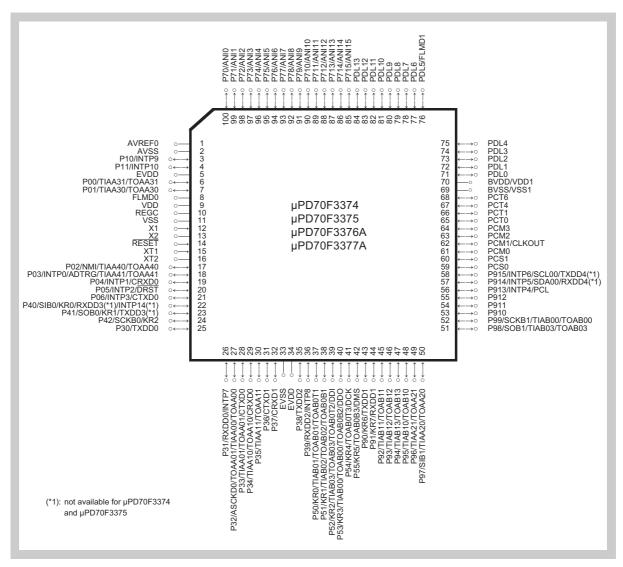

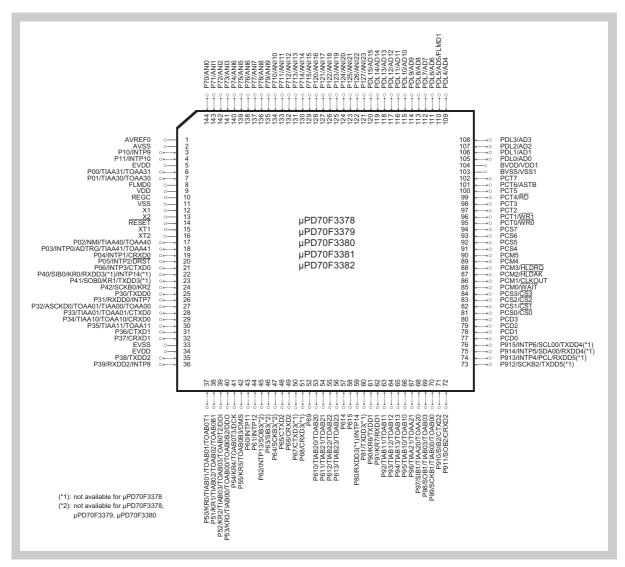

| µPD70F3370A | μPD70F3377A | μPD70F3384 |

|-------------|-------------|------------|

| μPD70F3371  | μPD70F3378  | μPD70F3385 |

| µPD70F3372  | μPD70F3379  |            |

| µPD70F3373  | μPD70F3380  |            |

| µPD70F3374  | μPD70F3381  |            |

| μPD70F3375  | μPD70F3382  |            |

| μPD70F3376A | μPD70F3383  |            |

|             |             |            |

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

### **Notice**

- Descriptions of circuits, software and other related information in this document are provided only to

illustrate the operation of semiconductor products and application examples. You are fully

responsible for the incorporation of these circuits, software, and information in the design of your

equipment. Renesas Electronics assumes no responsibility for any losses incurred by youor third

parties arising from the use of these circuits, software, or information.

- 2. 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and

measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots

etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control

systems; anti-disaster systems; anticrime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the even t of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(2012.4)

### **General Precautions in the Handling of MPU/MCU Products**

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

### 1. Handling of unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, anassociated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

#### 2. Processing at power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset functionare not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

#### 3. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

### 4. Clock signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal.

Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

#### 5. Differences between products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

The characteristics of an MPU or MCU in the same group but having a different part number may differ in terms of the internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

# **Table of Contents**

| 1.1 General       18         1.2 Features Summary       19         1.3 Description       22         1.3.1 Internal units       26         1.3.2 Structure of the manual       27         1.4 Ordering Information       28         1.4.1 V850ES/FE3 ordering information       28         1.4.2 V850ES/FG3 ordering information       29         1.4.4 V850ES/FG3 ordering information       29         1.4.4 V850ES/FG3 ordering information       30         1.4.5 V850ES/FK3 ordering information       31         Chapter 2 Pin Functions       32         2.1 Overview       32         2.1.1 Description       33         2.1.2 Terms       37         2.1.3 Noise elimination       37         2.2.1 Overview       38         2.2.2 Port Group Configuration Registers       38         2.2.2 Pin function configuration       38         2.2.2 Pin function configuration       38         2.2.2 Pin function configuration       38         2.2.3 Pin data input/output       45         2.2.4 Configuration of pull-up resistors       47         2.2.5 Open drain configuration       38         2.2.1 Port type Diaperams       52         2.4 Port Type Diagrams | Cha | oter 1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2       Features Summary       19         1.3       Description.       22         1.3.1       Internal units       26         1.3.2       Structure of the manual.       27         1.4       Ordering Information       28         1.4.1       V850ES/FE3 ordering information       28         1.4.2       V850ES/FG3 ordering information       29         1.4.3       V850ES/FG3 ordering information       30         1.4.4       V850ES/FK3 ordering information       30         1.4.5       V850ES/FK3 ordering information       30         1.4.5       V850ES/FK3 ordering information       30         2.1       Verview.       32         2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination.       37         2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination.       37         2.1.1       Description       33         2.1.2       Terms       37         2.2.2       Pin function configuration       38         2.2.1       Overview.       38                                                                                             | 1.1 | Genera | al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18 |

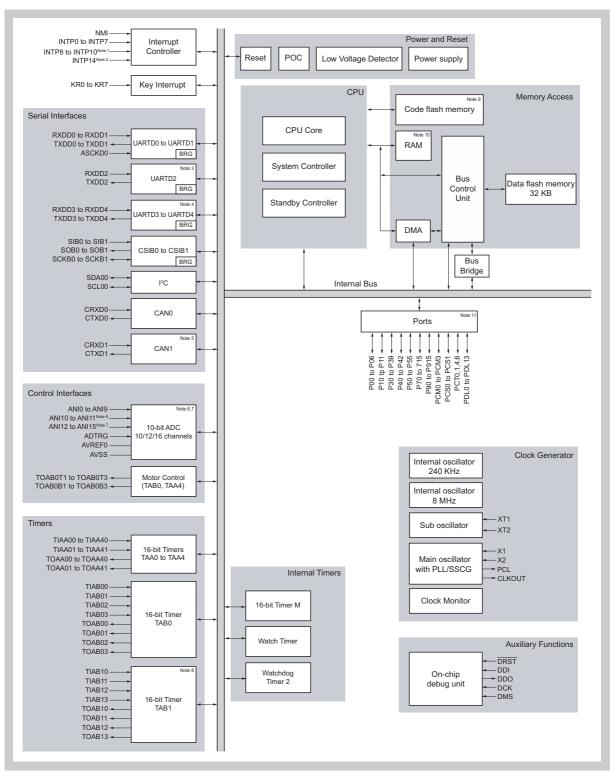

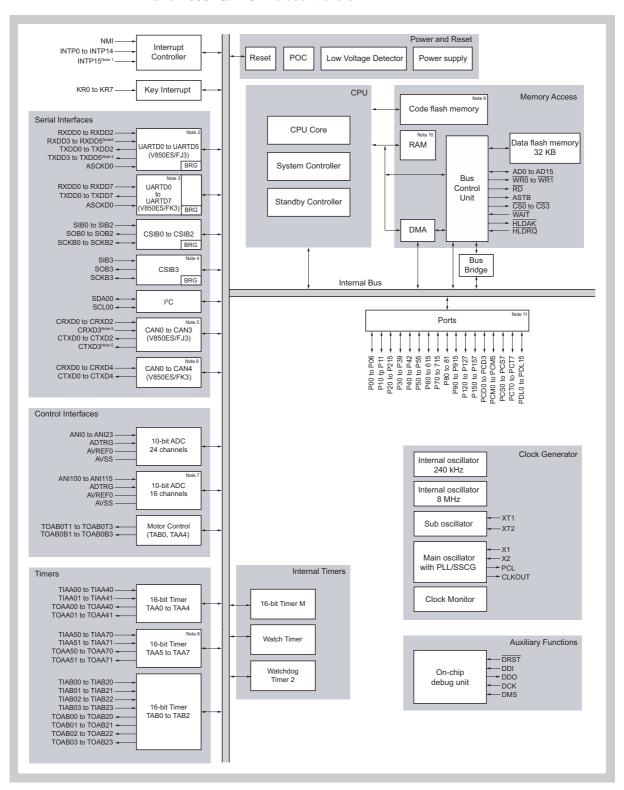

| 1.3.1       Internal units       26         1.3.2       Structure of the manual.       27         1.4       Ordering Information       28         1.4.1       V850ES/FE3 ordering information       28         1.4.2       V850ES/FE3 ordering information       29         1.4.3       V850ES/FG3 ordering information       30         1.4.4       V850ES/FJ3 ordering information       30         1.4.5       V850ES/FK3 ordering information       31         Chapter 2 Pin Functions         2.1       Overview.       32         2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination.       37         2.2.1       Overview.       38         2.2.1       Overview.       38         2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination.       37         2.2.1       Overview.       38         2.2.1       Overview.       38         2.2.1       Overview.       38         2.2.1       Infunction configuration       39         2.2.1       Pin function co                                                                                           | 1.2 |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 1.3.1       Internal units       26         1.3.2       Structure of the manual.       27         1.4       Ordering Information.       28         1.4.1       V850ES/F3 ordering information.       28         1.4.2       V850ES/F3 ordering information.       29         1.4.4       V850ES/F43 ordering information.       30         1.4.5       V850ES/FK3 ordering information.       30         1.4.5       V850ES/FK3 ordering information.       31         Chapter 2 Pin Functions         2.1       Description.       33         2.1.1       Description.       33         2.1.2       Terms.       37         2.1.3       Noise elimination.       37         2.1.3       Noise elimination.       37         2.2.1       Overview.       38         2.2.1       Overview.       38         2.2.2       Pin function configuration Registers       38         2.2.1       Porritye.       38         2.2.2       Pin function configuration       39         2.2.3       Pin dari input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.3       Pin drain configurati                                               | 1.3 |        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 1.4       Ordering Information.       28         1.4.1       V850ES/FE3 ordering information.       28         1.4.2       V850ES/FG3 ordering information.       28         1.4.3       V850ES/FG3 ordering information.       29         1.4.4       V850ES/FG3 ordering information.       30         1.4.5       V850ES/FK3 ordering information.       31         Chapter 2 Pin Functions.         2.1       Overview.       32         2.1.1       Description.       33         2.1.2       Terms.       37         2.1.3       Noise elimination.       37         2.2.1       Overview.       38         2.2.1       Port Group Configuration Registers.       38         2.2.1       Port Overview.       38         2.2.2       Pin function configuration.       39         2.2.3       Pin data input/output.       45         2.2.4       Configuration of pull-up resistors.       47         2.2.3       Pin data input/output.       48         2.2.3       Port Buffers Diagrams.       52         2.4       Port Type Diagrams.       52         2.4.1       Port type C.U       53         2.4.2       Port                                                |     | -      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 1.4.1       V850ES/FE3 ordering information       28         1.4.2       V850ES/FE3 ordering information       28         1.4.3       V850ES/FG3 ordering information       29         1.4.4       V850ES/FG3 ordering information       30         1.4.5       V850ES/FK3 ordering information       31         Chapter 2 Pin Functions         2.1       Overview       32         2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination.       37         2.2       Port Group Configuration Registers       38         2.2.1       Overview       38         2.2.2       Pin function configuration       39         2.2.3       Pin data input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration       48         2.3       Port Buffers Diagrams       49         2.4       Port Type Diagrams       52         2.4.1       Port type C       52         2.4.2       Port type DI       53         2.4.1       Port type DI       55         2.4.2       Port type DI-U       55 </td <td></td> <td>_</td> <td></td> <td></td>            |     | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 1.4.1       V850ES/FE3 ordering information       28         1.4.2       V850ES/FG3 ordering information       29         1.4.3       V850ES/FG3 ordering information       30         1.4.4       V850ES/FK3 ordering information       31         Chapter 2 Pin Functions         2.1       V850ES/FK3 ordering information       31         Chapter 2 Pin Functions         2.1       Description       33         2.1       Terms       33         2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination       37         2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination       37         2.1.1       Description       38         2.1.2       Terms       37         2.1.3       Noise elimination       37         2.2.4       Porf Group Configuration Registers       38         2.2.2       Pin function configuration       38         2.2.2       Pin function configuration       39         2.2.3       Pin function configuration       49         2.4.4 <t< td=""><td>1.4</td><td>_</td><td></td><td></td></t<>                                  | 1.4 | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 1.4.2       V850ES/FF3 ordering information       28         1.4.3       V850ES/FG3 ordering information       29         1.4.4       V850ES/FK3 ordering information       30         1.4.5       V850ES/FK3 ordering information       31         Chapter 2 Pin Functions       32         2.1       Overview.       32         2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination       37         2.2.1       Overview.       38         2.2.1       Overview.       38         2.2.2       Pin function configuration Registers       38         2.2.1       Overview.       38         2.2.2       Pin function configuration       39         2.2.3       Pin data input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration       48         2.3       Port Buffers Diagrams       49         2.4       Port Type Diagrams       52         2.4.1       Port type C.       52         2.4.2       Port type Diagrams       52         2.4.1       Port type Diagrams                                                                   |     |        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 1.4.3       V850ES/FG3 ordering information       29         1.4.4       V850ES/FJ3 ordering information       30         1.4.5       V850ES/FK3 ordering information       31         Chapter 2 Pin Functions         2.1       Overview.       32         2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination       37         2.2.1       Overview       38         2.2.1       Overview       38         2.2.2       Pin function configuration       39         2.2.3       Pin data input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration       48         2.3       Port Buffers Diagrams       52         2.4       Port Type Diagrams       52         2.4.1       Port type C-U       53         2.4.2       Port type C-U       53         2.4.3       Port type D0-U       54         2.4.5       Port type D1-U       54         2.4.6       Port type D1-U       56         2.4.7       Port type D1-U       56         2.4.9 <td< td=""><td></td><td></td><td>3</td><td></td></td<>                                          |     |        | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 1.4.4       V850ES/FJ3 ordering information       30         1.4.5       V850ES/FK3 ordering information       31         Chapter 2 Pin Functions       32         2.1       Overview.       32         2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination.       37         2.2       Port Group Configuration Registers       38         2.2.1       Overview.       38         2.2.2       Pin function configuration       39         2.2.3       Pin data input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration       48         2.3       Port Buffers Diagrams       49         2.4       Port Type Diagrams       52         2.4.1       Port type C       52         2.4.2       Port type C-U       53         2.4.3       Port type Do       53         2.4.4       Port type DO-U       54         2.4.5       Port type D1-U       55         2.4.6       Port type D1-U       56         2.4.7       Port type D1-U       56         <                                                                                       |     |        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 1.4.5       V850ES/FK3 ordering information       31         Chapter 2       Pin Functions       32         2.1       Overview.       32         2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination       37         2.2       Port Group Configuration Registers       38         2.2.1       Overview       38         2.2.2       Pin function configuration       38         2.2.3       Pin data input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration       48         2.3       Port Buffers Diagrams       49         2.4       Port Type Diagrams       52         2.4       Port type C       52         2.4.1       Port type C-U       53         2.4.2       Port type D0-U       53         2.4.3       Port type D0-U       54         2.4.5       Port type D1-U       55         2.4.6       Port type D1-U       56         2.4.7       Port type D3-U       57         2.4.8       Port type D1-U       56         2.4.1                                                                                                |     |        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| Chapter 2       Pin Functions       32         2.1       Overview.       32         2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination       37         2.2       Port Group Configuration Registers       38         2.2.1       Overview       38         2.2.2       Pin function configuration       39         2.2.3       Pin data input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration       48         2.3       Port Buffers Diagrams       49         2.4       Port Type Diagrams       52         2.4.1       Port type C-U       53         2.4.2       Port type C-U       53         2.4.3       Port type C-U       53         2.4.4       Port type D0-U       54         2.4.5       Port type D1-U       55         2.4.6       Port type D1-U       55         2.4.7       Port type D1-U       56         2.4.8       Port type D1-U       56         2.4.9       Port type D1-U       59         2.4.10       Port                                                                                                  |     |        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 2.1       Overview.       32         2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination       37         2.2       Port Group Configuration Registers       38         2.2.1       Overview       38         2.2.2       Pin function configuration       39         2.2.3       Pin data input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration       48         2.3       Port Buffers Diagrams       49         2.4       Port Type Diagrams       52         2.4.1       Port type C       52         2.4.2       Port type C-U       53         2.4.3       Port type DO       53         2.4.4       Port type DO-U       54         2.4.5       Port type D1-U       54         2.4.6       Port type D1-U       55         2.4.7       Port type D1-U       56         2.4.8       Port type D1-U       56         2.4.9       Port type D1-U       59         2.4.1       Port type E01-U.       61         2.4.1       Port type                                                                                                  |     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

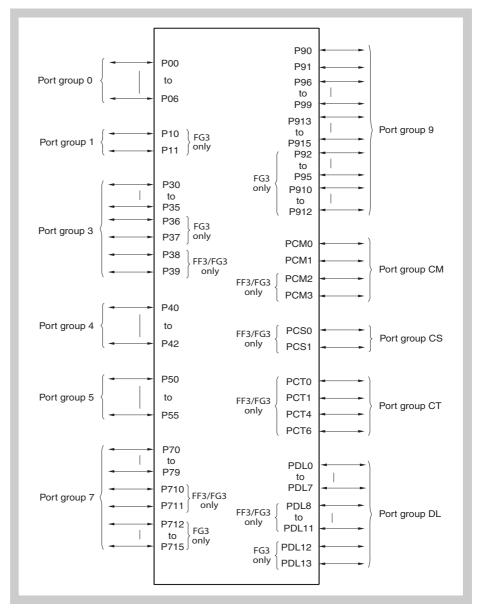

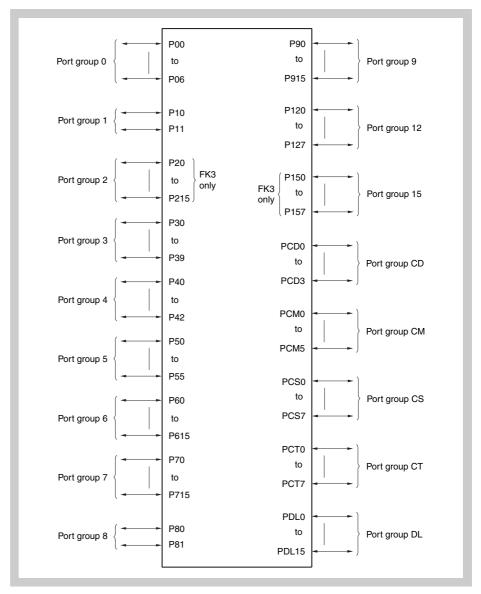

| 2.1.1       Description       33         2.1.2       Terms       37         2.1.3       Noise elimination       37         2.2       Port Group Configuration Registers       38         2.2.1       Overview       38         2.2.2       Pin function configuration       39         2.2.3       Pin data input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration       48         2.3       Port Buffers Diagrams       49         2.4       Port Type Diagrams       52         2.4.1       Port type C       52         2.4.2       Port type C-U       53         2.4.3       Port type DO-U       54         2.4.4       Port type DO-U       54         2.4.5       Port type D1-U       55         2.4.6       Port type D1-U       56         2.4.7       Port type D1-U       56         2.4.8       Port type D1-U       56         2.4.9       Port type D1-U       56         2.4.1       Port type E01-U.       61         2.4.1.1       Port type E01-U.       61         2.4.1.2                                                                                                   | Cha | oter 2 | Pin Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32 |

| 2.1.2       Terms       37         2.1.3       Noise elimination       37         2.2       Port Group Configuration Registers       38         2.2.1       Overview       38         2.2.2       Pin function configuration       39         2.2.3       Pin data input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration       48         2.3       Port Buffers Diagrams       49         2.4       Port Type Diagrams       52         2.4.1       Port type C-U       53         2.4.2       Port type D0       53         2.4.3       Port type D0-U       54         2.4.5       Port type D1-U       55         2.4.7       Port type D1-U       55         2.4.8       Port type D3-UI       57         2.4.9       Port type D1A       58         2.4.10       Port type D1O1-UI       59         2.4.11       Port type E01-U       61         2.4.12       Port type E10-U       62         2.4.13       Port type E10-U       63         2.4.15       Port type E11-U       66         2.4.16 </th <th>2.1</th> <th>Overvi</th> <th>ew</th> <th>32</th>                                | 2.1 | Overvi | ew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32 |

| 2.1.2       Terms       37         2.1.3       Noise elimination       37         2.2       Port Group Configuration Registers       38         2.2.1       Overview       38         2.2.2       Pin function configuration       39         2.2.3       Pin data input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration       48         2.3       Port Buffers Diagrams       49         2.4       Port Type Diagrams       52         2.4.1       Port type C-U       53         2.4.2       Port type D0       53         2.4.3       Port type D0-U       54         2.4.5       Port type D1-U       55         2.4.7       Port type D1-U       55         2.4.8       Port type D3-UI       57         2.4.9       Port type D1A       58         2.4.10       Port type D1O1-UI       59         2.4.11       Port type E01-U       61         2.4.12       Port type E10-U       62         2.4.13       Port type E10-U       63         2.4.15       Port type E11-U       66         2.4.16 </td <td></td> <td>2.1.1</td> <td>Description</td> <td>33</td>                           |     | 2.1.1  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33 |

| 2.1.3       Noise elimination.       37         2.2       Port Group Configuration Registers       38         2.2.1       Overview.       38         2.2.2       Pin function configuration       39         2.2.3       Pin data input/output.       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration.       48         2.3       Port Buffers Diagrams       49         2.4       Port Type Diagrams       52         2.4.1       Port type C.       52         2.4.2       Port type C-U       53         2.4.3       Port type D0.       53         2.4.4       Port type D1.       54         2.4.5       Port type D1.       54         2.4.6       Port type D1-U       55         2.4.7       Port type D1-U       56         2.4.8       Port type D3-U       57         2.4.9       Port type D1A       58         2.4.10       Port type D1O1-UI       59         2.4.11       Port type E0-U       61         2.4.12       Port type E10-U       62         2.4.15       Port type E10-U       63         2.                                                                                        |     | 2.1.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

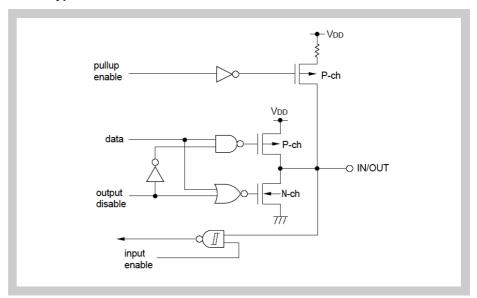

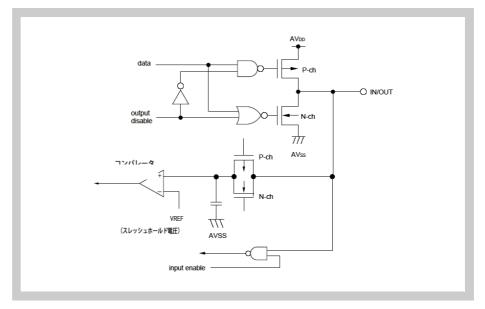

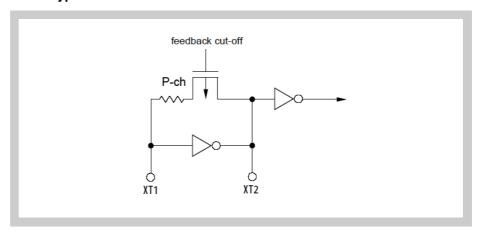

| 2.2       Port Group Configuration Registers       38         2.2.1       Overview       38         2.2.2       Pin function configuration       39         2.2.3       Pin data input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration       48         2.3       Port Buffers Diagrams       49         2.4       Port Type Diagrams       52         2.4.1       Port type C-U       53         2.4.2       Port type C-U       53         2.4.3       Port type D0-U       54         2.4.4       Port type D1-U       54         2.4.5       Port type D1-U       55         2.4.7       Port type D3-UI       56         2.4.8       Port type D3-UI       56         2.4.9       Port type D1A       58         2.4.10       Port type D1O-UI       59         2.4.11       Port type E01-U       61         2.4.12       Port type E01-U       62         2.4.13       Port type E11-UI       63         2.4.14       Port type E11-UI       64         2.4.15       Port type E11-UI       66                                                                                             |     | 2.1.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

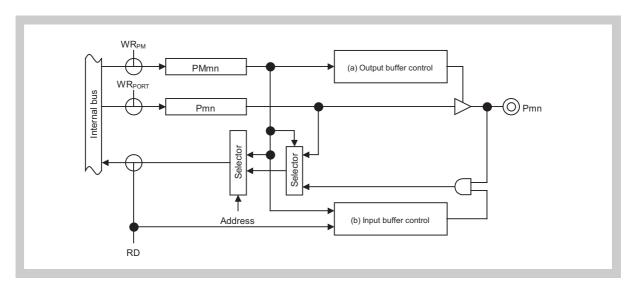

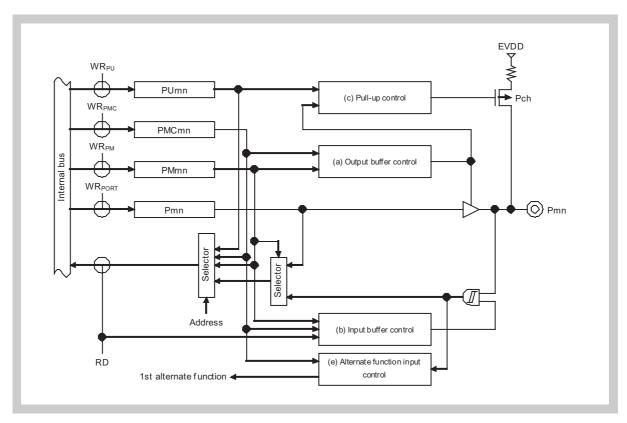

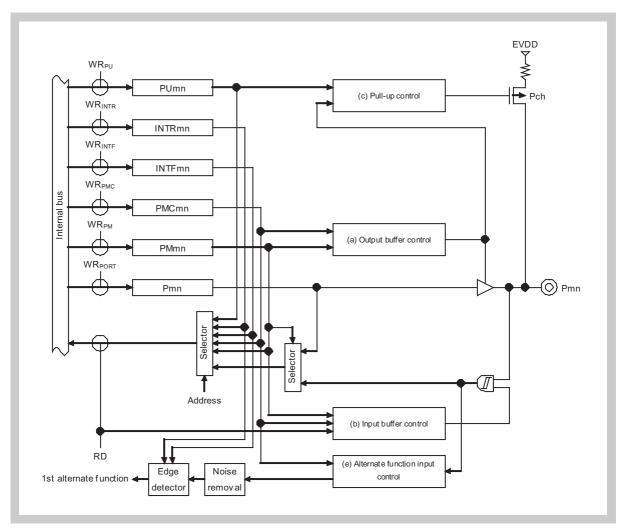

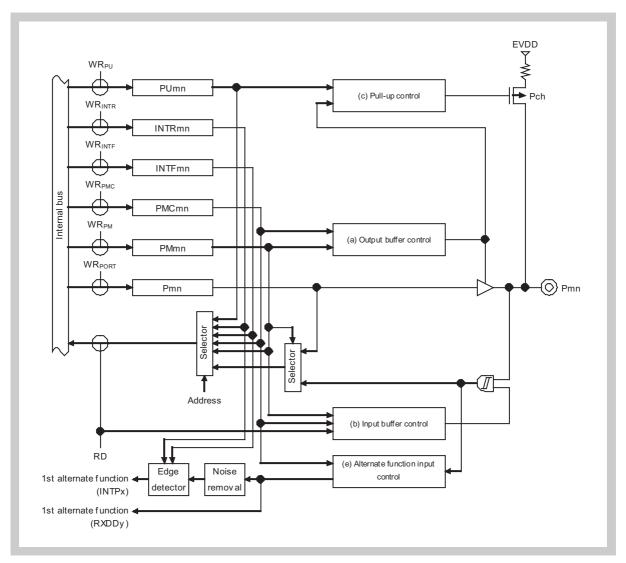

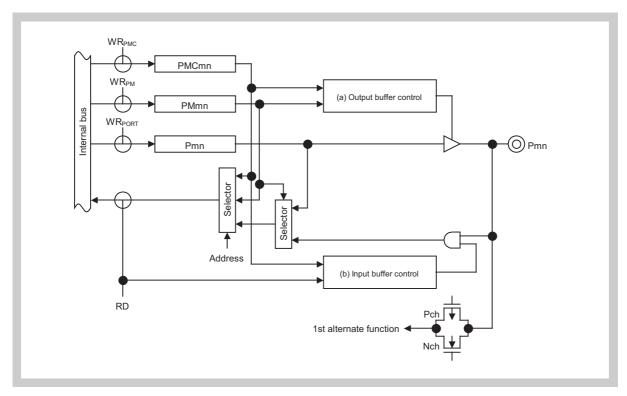

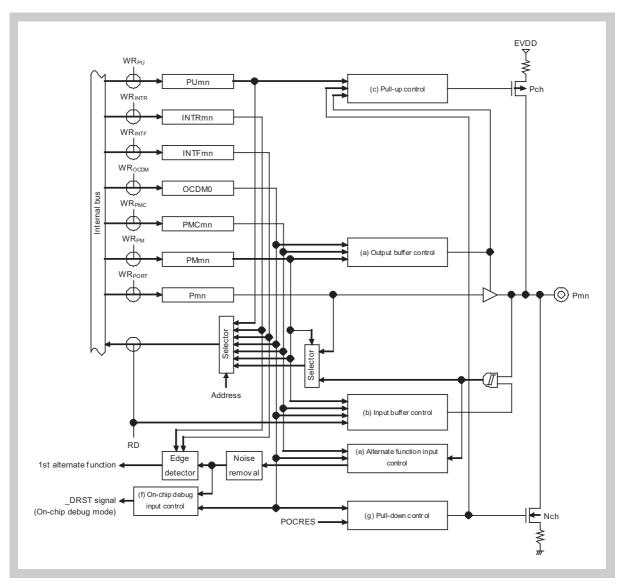

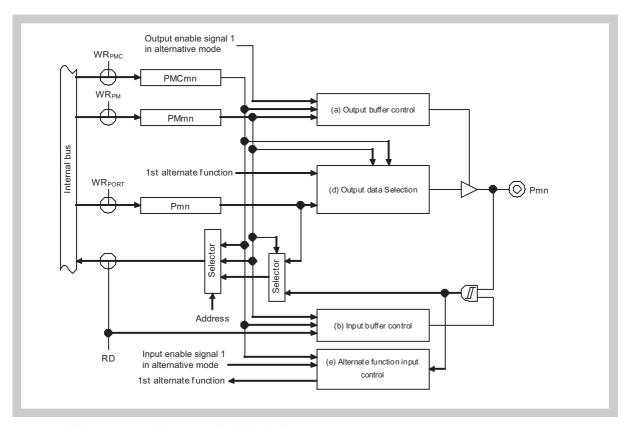

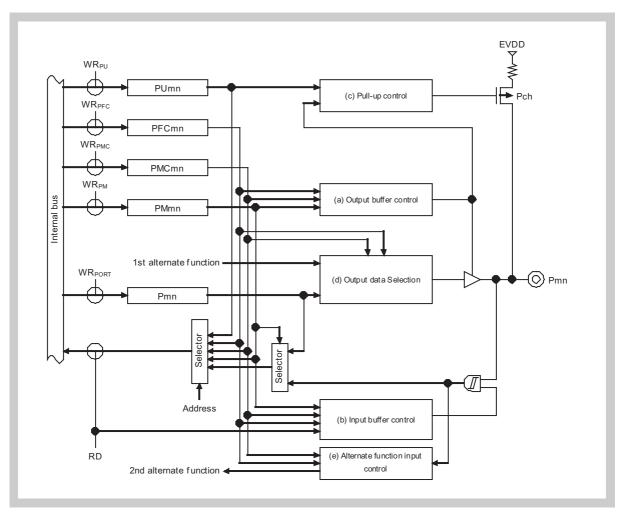

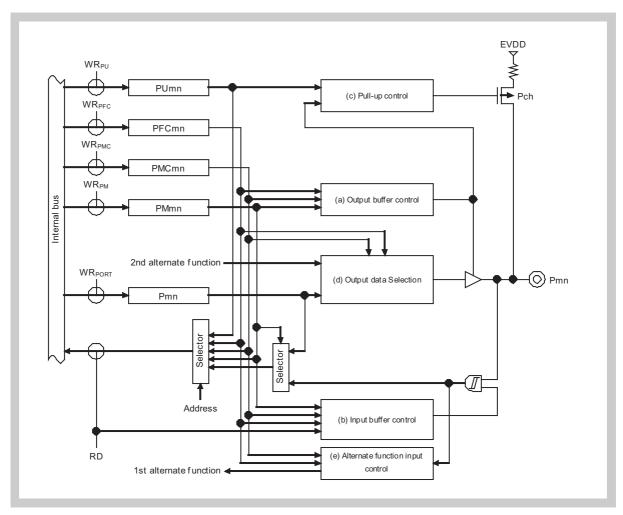

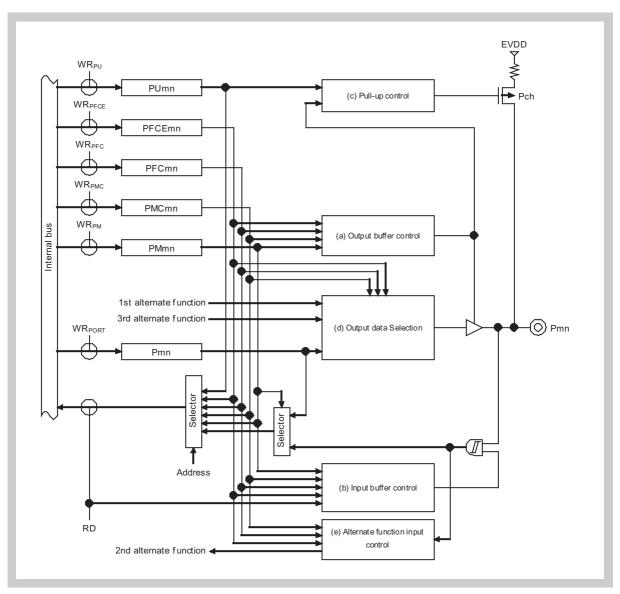

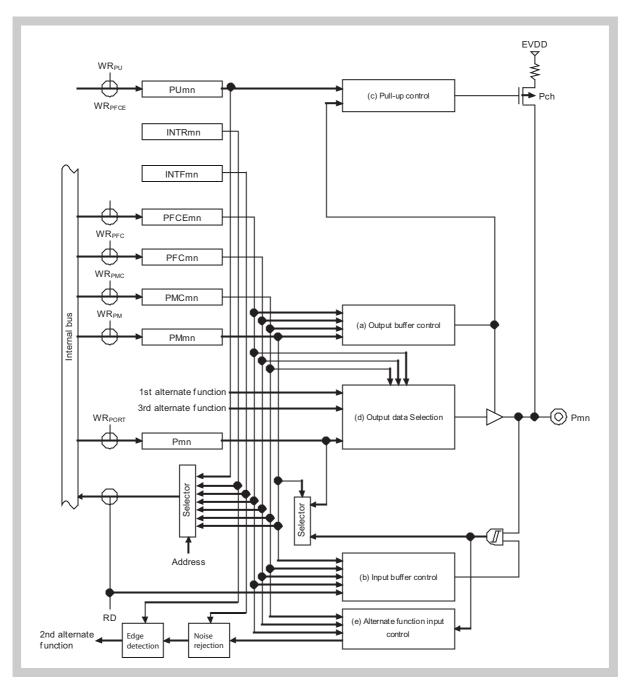

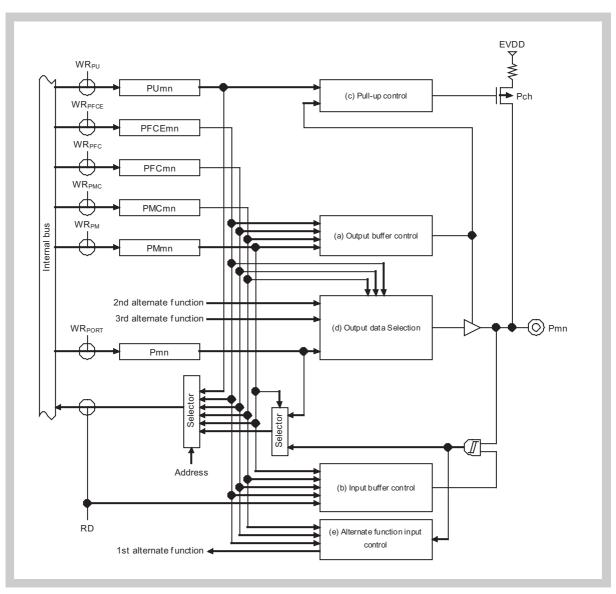

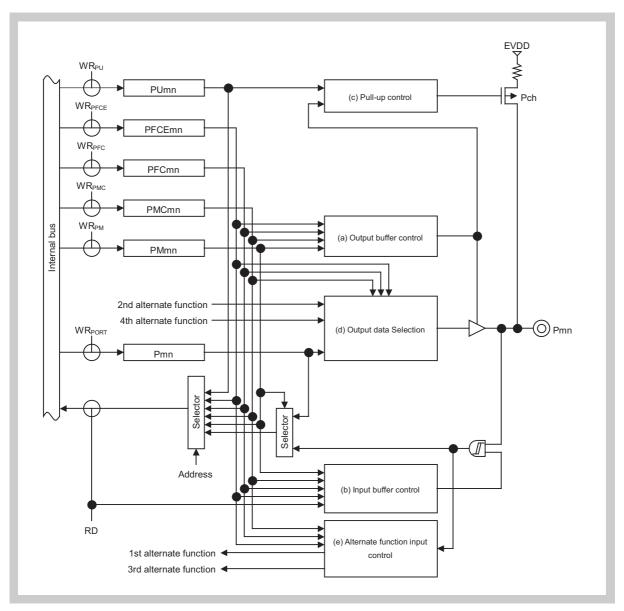

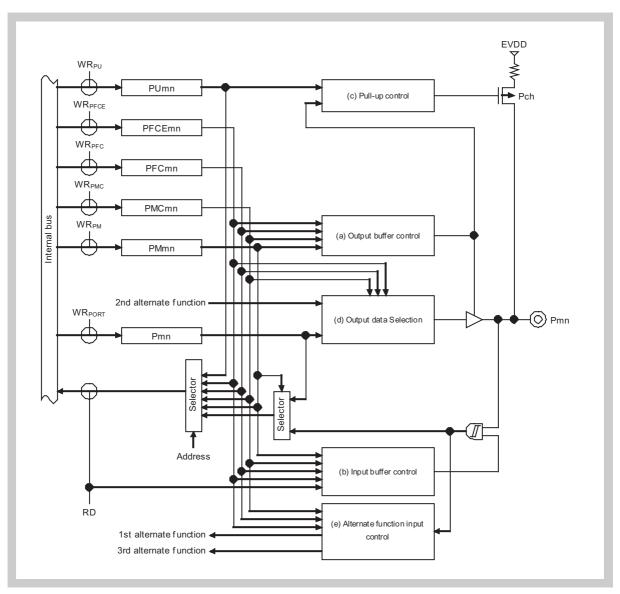

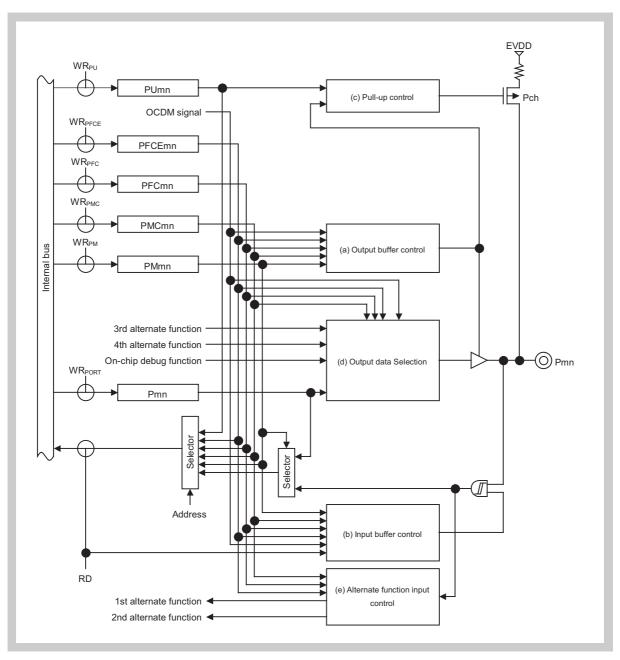

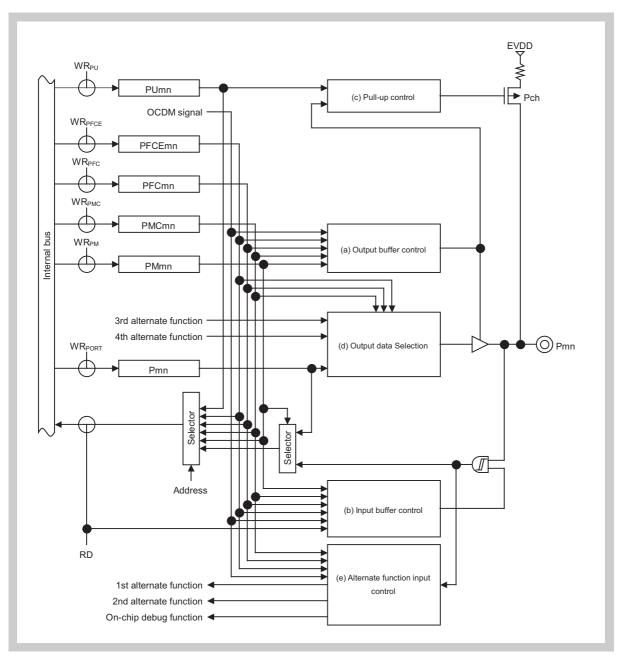

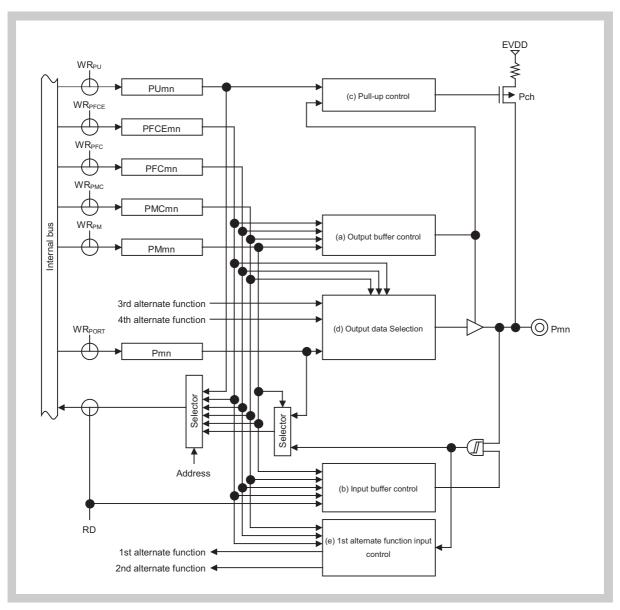

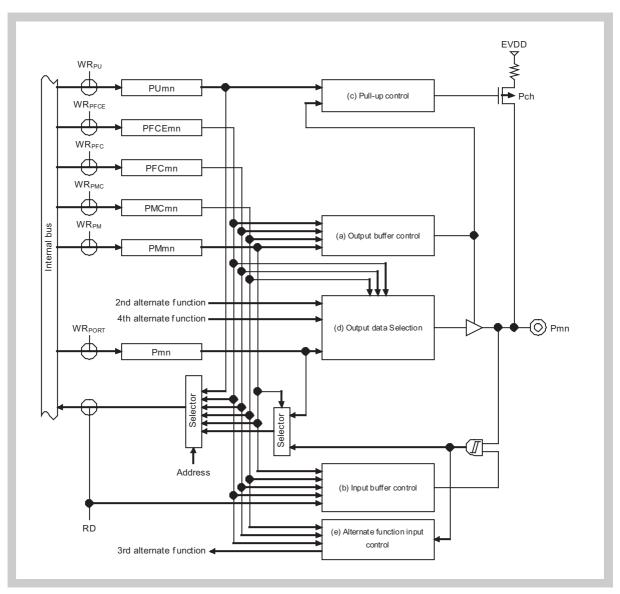

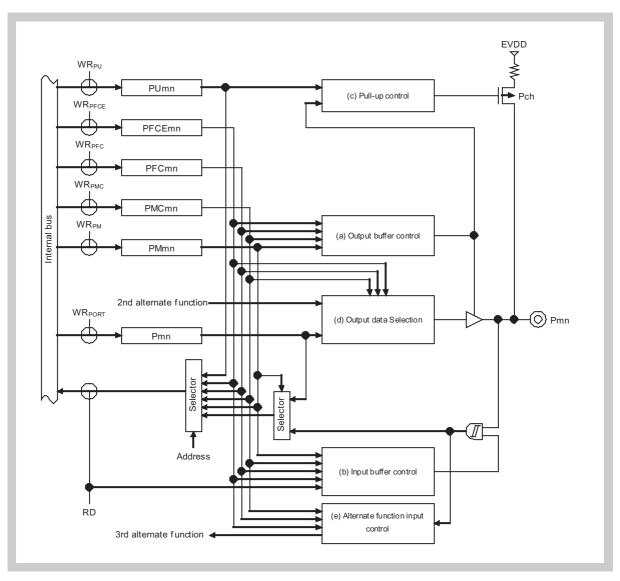

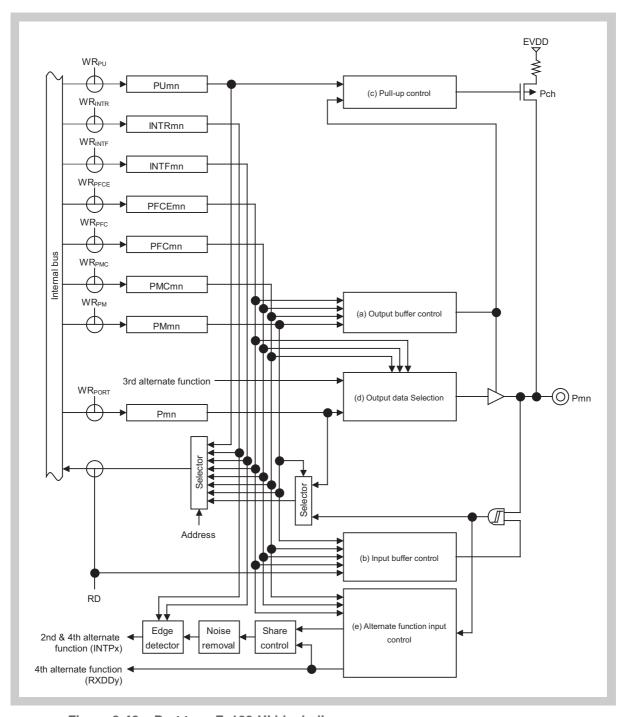

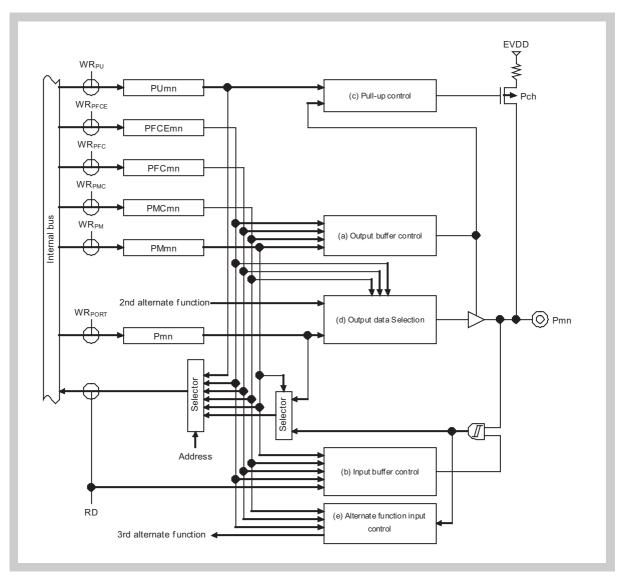

| 2.2.1       Overview       38         2.2.2       Pin function configuration       39         2.2.3       Pin data input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration       48         2.3       Port Buffers Diagrams       49         2.4       Port Type Diagrams       52         2.4.1       Port type C-U       52         2.4.2       Port type C-U       53         2.4.3       Port type D0       53         2.4.4       Port type D0-U       54         2.4.5       Port type D1       54         2.4.6       Port type D1-U       55         2.4.7       Port type D1-U       56         2.4.8       Port type D3-UI       57         2.4.9       Port type D1A       58         2.4.10       Port type D1O1-UI       59         2.4.11       Port type E01-U       61         2.4.12       Port type E10-U       62         2.4.14       Port type E11-U       63         2.4.15       Port type E11-U       65         2.4.17       Port type E21-U       66         2.4.18 <td< td=""><td>2.2</td><td>Port G</td><td></td><td></td></td<>                                        | 2.2 | Port G |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 2.2.2       Pin function configuration       39         2.2.3       Pin data input/output       45         2.2.4       Configuration of pull-up resistors       47         2.2.5       Open drain configuration       48         2.3       Port Buffers Diagrams       49         2.4       Port Type Diagrams       52         2.4.1       Port type C       52         2.4.2       Port type C-U       53         2.4.3       Port type D0       53         2.4.4       Port type D0-U       54         2.4.5       Port type D1       54         2.4.6       Port type D1-U       55         2.4.7       Port type D1-UI       56         2.4.8       Port type D3-UI       57         2.4.9       Port type D1A       58         2.4.10       Port type D1O1-UI       59         2.4.11       Port type E01-U       61         2.4.12       Port type E01-U       62         2.4.14       Port type E10-U       63         2.4.15       Port type E11-U       64         2.4.16       Port type E11-U       65         2.4.17       Port type E11-U       66         2.4.18                                                                                                |     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |