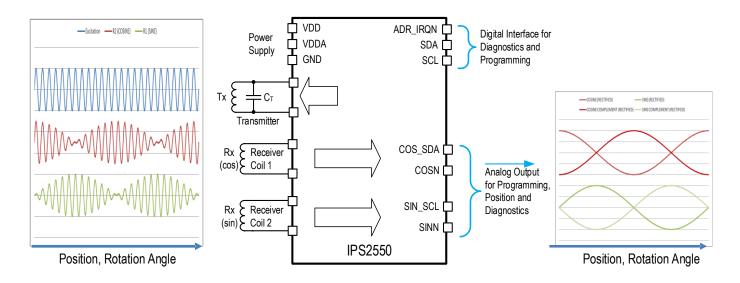

## **Description**

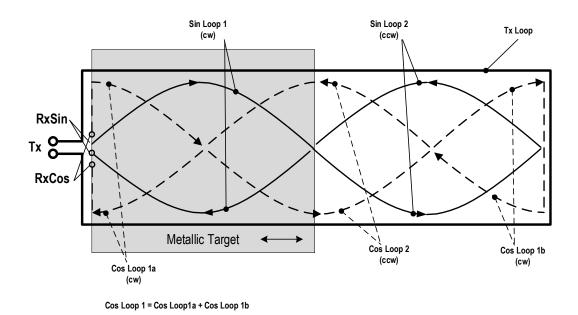

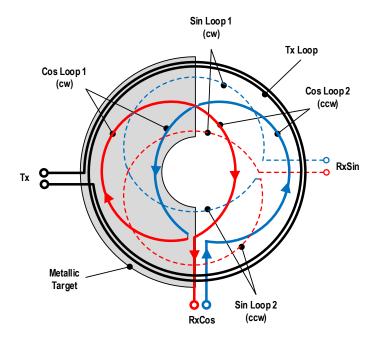

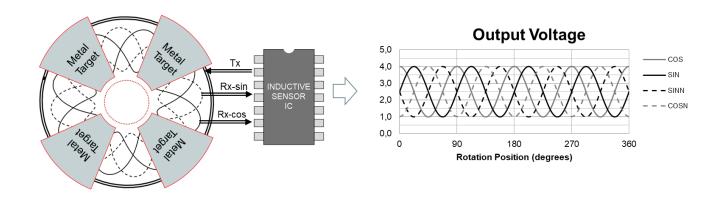

The IPS2550 is a magnet-free, inductive position sensor IC that can be used for high-speed absolute position sensing in automotive, industrial, medical, and consumer applications. The IPS2550 uses the physical principle of eddy currents to detect the position of a simple metallic target that is moving above a set of coils, consisting of one transmitter coil and two receiver coils.

The three coils are typically printed as copper traces on a printed circuit board (PCB). They are arranged such that the transmitter coil induces a secondary voltage in the two receiver coils, which depends on the position of the metallic target above the coils.

A signal representative of the target's position over the coils is obtained by demodulating and processing the secondary voltages from the receiver coils. The target can be any kind of metal, such as aluminum, steel, or a PCB with a printed copper layer.

The IPS2550 provides two independent output interfaces:

- A high-speed analog interface providing position information in the form of demodulated analog sine/cosine raw data

- An I2C digital interface for diagnostics and programming

The IPS2550 operates at rotation speeds up to 600000 RPM (relating to coil designs using 1 period per turn). An ultra-low propagation delay of  $4\mu s$  provides high dynamic control for fast spinning motors.

The IPS2550 has been developed according to ISO26262 for implementation in safety-relevant systems up to ASIL C. It can also be used in ASIL D system-level requirements according to ASIL Decomposition rules (i.e. ISO 26262:2018, Part 9, Clause 5") or proper risk analysis by the system integrator.

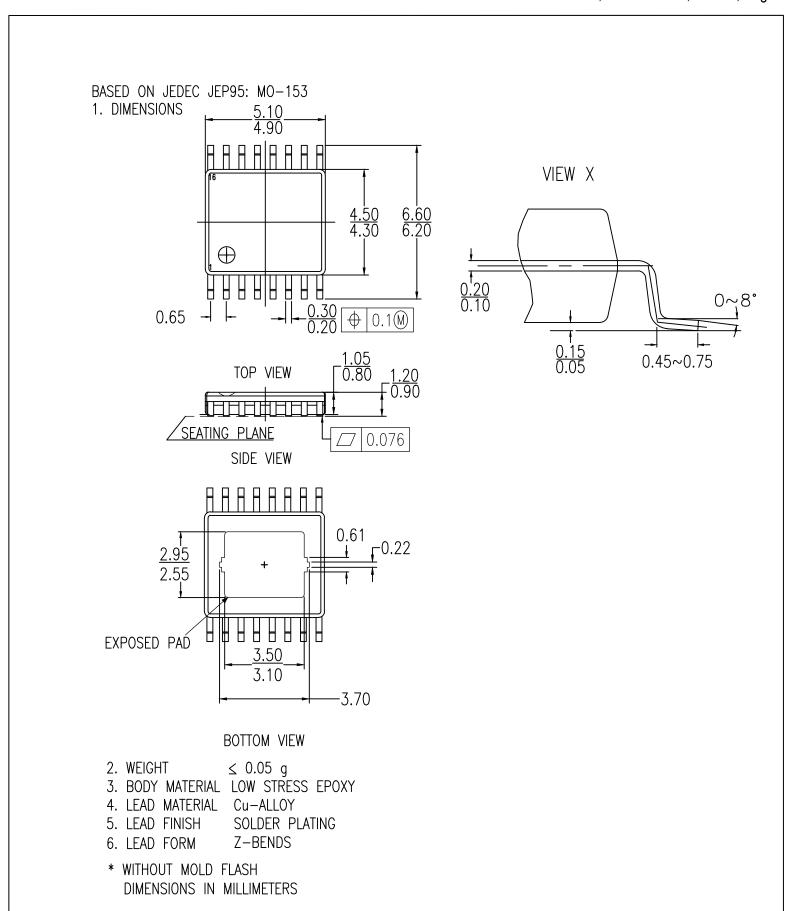

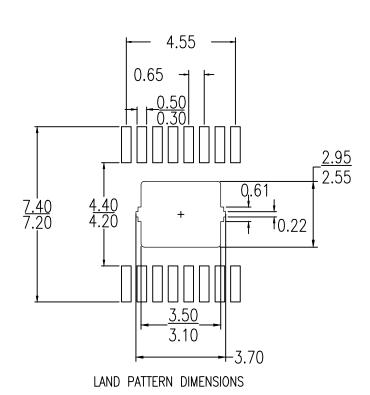

The IPS2550 is available in a 16-pin exposed pad TSSOP package and qualified for automotive use at -40°C to +160°C ambient temperature.

# **Available Support**

Renesas provides reference designs that demonstrate IPS2550 rotary position sensing applications.

# Typical Applications

- Rotor position detection for brushless DC motors; adaptable to any pole pair count

- Replacement of resolvers

#### **Features**

- Position sensing based on an inductive principle

- Cost-effective; no magnet required

- Immune to magnetic stray fields; no shielding required

- Suitable for harsh environments and extreme temperatures

- Differential and single-ended sine and cosine outputs

- Automatic gain control with programmable limits

- Nonvolatile user-configurable memory, programmable via I2C interface

- Programmable through analog or digital interface

- Single IC supports on-axis and off-axis rotation, linear motion, and arc motion sensing

- Adaptable to any full-scale angle range through coil design

- High accuracy: ≤ 0.1% full scale (with ideal coils)

- Rotation sensing up to a 360° angle range

- Over-voltage and reverse-polarity protection:

±18V on both supply and output pins

- Facilitates redundant design requirements

- Suitable for implementation in safety-related systems compliant to ISO26262 up to ASIL-C on a single IC and ASIL-D on dual ICs

- Fast diagnostic alarm via interrupt pin

- Wide operation temperature: -40 C up to +160°C

- Supply voltage programmable for 3.3V±0.3V or 5.0V±0.5V

- Small 16-TSSOP exposed pad package (4.4mm ×5.0mm)

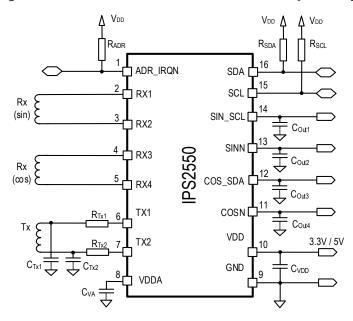

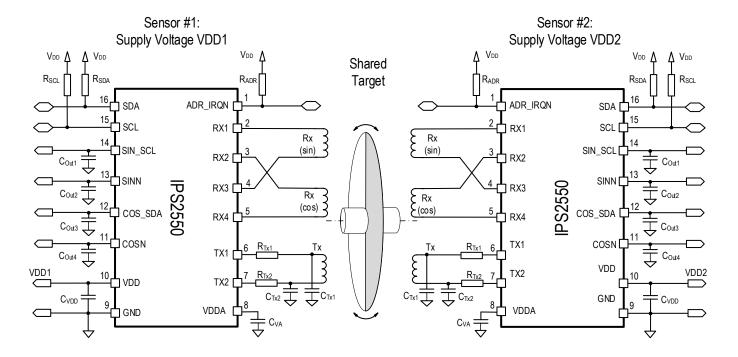

# **Application Circuit Example**

# **Contents**

| 1.  | Pin Assignments                                                                         | 5  |

|-----|-----------------------------------------------------------------------------------------|----|

| 2.  | Pin Descriptions                                                                        | 5  |

| 3.  | Receiver Coil Connection Options                                                        | 7  |

| 4.  | Absolute Maximum Ratings                                                                | 9  |

| 5.  | Operating Conditions                                                                    | 10 |

| 6.  | Ambient Temperature Range                                                               | 11 |

| 7.  | Electrical Characteristics                                                              | 12 |

| 8.  | Circuit Description                                                                     | 20 |

|     | 8.1 Overview                                                                            | 21 |

| 9.  | Sampling Rate, Resolution, Output Data Rate, and Propagation Delay                      | 24 |

| 10. | Output Modes                                                                            | 24 |

| 11. | Operating at High Speed                                                                 | 25 |

| 12. | Digital Diagnostics and Programming Interfaces                                          | 26 |

| 13. | Block Diagram                                                                           | 26 |

| 14. | Detailed Block Descriptions                                                             | 27 |

|     | 14.1 Power Management                                                                   | 27 |

|     | 14.2 LC Oscillator                                                                      | 27 |

|     | 14.3 Analog Signal Path                                                                 | 27 |

|     | 14.3.1 Rx Coil Diagnostics                                                              | 27 |

|     | 14.3.2 Receiver Signal Low-Pass Filter                                                  | 27 |

|     | 14.3.3 Offset and Gain Matching                                                         | 28 |

|     | 14.3.4 Demodulation                                                                     | 28 |

|     | 14.3.5 Automatic Gain Control (AGC)                                                     | 28 |

|     | 14.4 Signal Channel Swapping                                                            | 28 |

|     | 14.5 Output Buffers                                                                     | 28 |

|     | 14.6 Temperature Sensor                                                                 | 29 |

| 15. | ECU Connection Options                                                                  | 29 |

|     | 15.1 Embedded vs. Remote Connection                                                     | 29 |

|     | 15.2 Supply Voltage Operation: 3.3V or 5V                                               | 32 |

|     | 15.3 I2C Interface                                                                      | 32 |

|     | 15.3.1 I2C with Address Selection (Default)                                             | 32 |

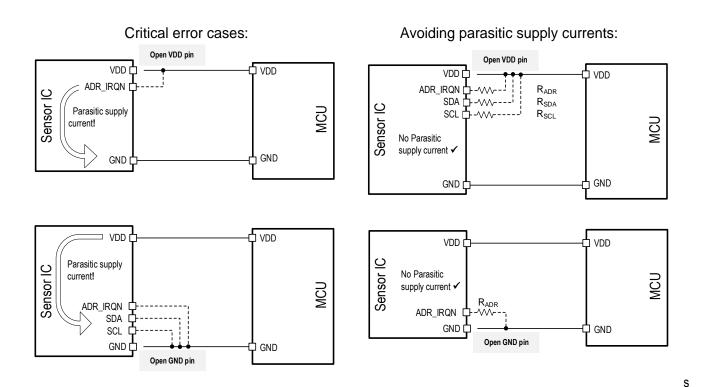

|     | 15.3.2 Avoiding a Parasitic Path through ADR_IRQN Pin during Loss of GND or Loss of VDD | 33 |

|     | 15.3.3 I2C Interface with Interrupt (Programming Option)                                | 34 |

| 16. | Over-Voltage Protection                                                                 | 35 |

|     | 16.1 I/O Protection                                                                     | 35 |

| 17. | Programming Options                                                                     | 35 |

|     | 17.1 Programming the Device to Use the Other Supply Voltage Option                      | 37 |

|     | 17.2 Lock Feature (Cyber Security)                                                      | 37 |

|     |                                                                                         |    |

| 1            | 17.3 Programming Options                                                                   | 37 |

|--------------|--------------------------------------------------------------------------------------------|----|

|              | Functional Safety and Diagnostics                                                          |    |

| 1            | 18.1 Functional Safety ASIL and ISO Compliance                                             | 38 |

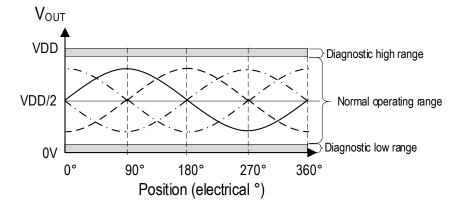

| 1            | 18.2 Diagnostic Mode Indication through Analog Outputs                                     | 38 |

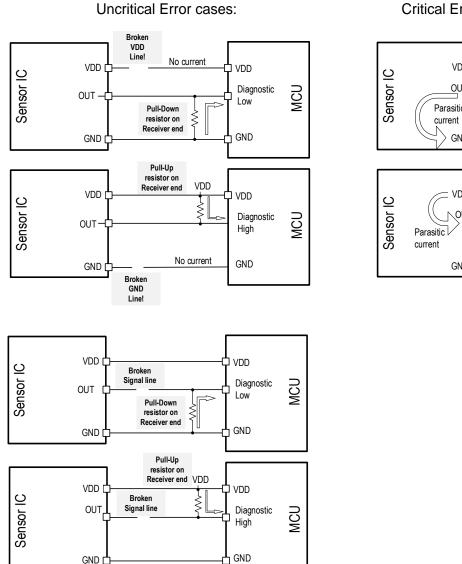

|              | 18.2.1 Shorted and Broken Wire Detection                                                   | 40 |

| 1            | 18.3 Diagnostic Features                                                                   | 42 |

| 1            | 18.4 Internal Register and Memory Errors                                                   | 44 |

| 1            | 18.5 LC Oscillator Frequency Out of Range                                                  | 44 |

| 19. F        | Redundant Connections                                                                      | 45 |

| 20. <i>A</i> | Application Examples                                                                       | 46 |

| 21. E        | Electromagnetic Compatibility (EMC)                                                        | 47 |

| 22. 1        | 16-TSSOP Package Outline Drawings                                                          | 47 |

| 23. N        | Marking Diagram                                                                            | 48 |

| 2            | 23.1 Marking of Production Parts                                                           | 48 |

| 24. (        | Ordering Information                                                                       | 48 |

| 25. F        | Revision History                                                                           | 49 |

|              |                                                                                            |    |

|              | t of Figures                                                                               |    |

| -            | e 1. Pin Assignments for 16-TSSOP Package – Top View                                       |    |

| -            | e 2. LC Oscillator Connection in ASIL-C Configuration with Split TX Capacitors             |    |

| -            | e 3. LC Oscillator Connection in Compatibility Mode Configuration with Split TX Capacitors |    |

| Figure       |                                                                                            |    |

| Figure       |                                                                                            |    |

| Figure       | ·                                                                                          |    |

| Figure       | Ÿ                                                                                          |    |

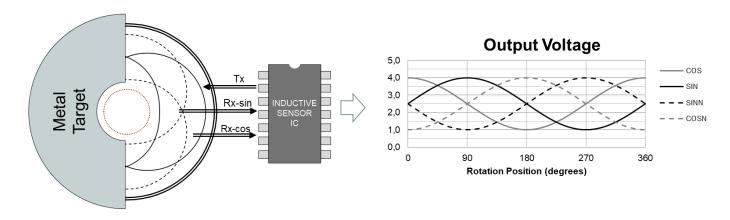

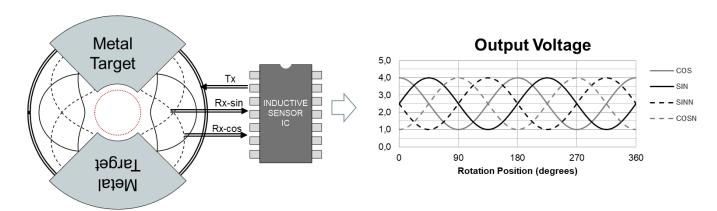

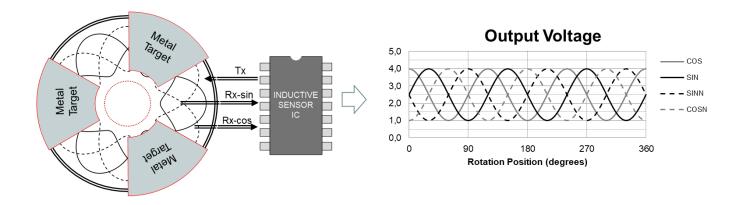

| -            | e 8. Coil Design for a 360° Rotary Sensor                                                  |    |

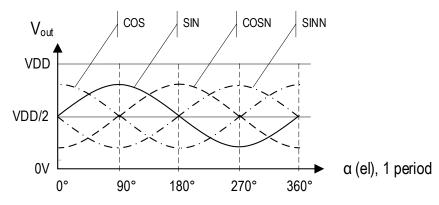

| •            | e 9. Output Signals: Sine-Cosine Analog Differential Mode                                  |    |

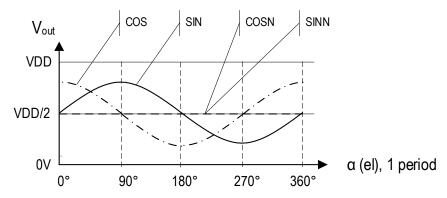

|              | e 10. Output Signals: Sine-Cosine Analog Single-Ended Mode                                 |    |

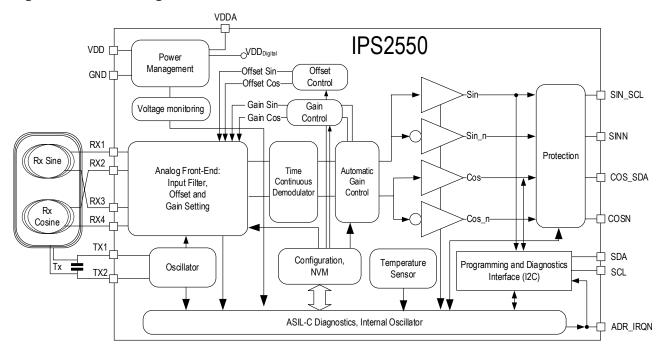

| U            | e 11. Block Diagram                                                                        |    |

| _            | e 12. AGC Magnitude ranges                                                                 |    |

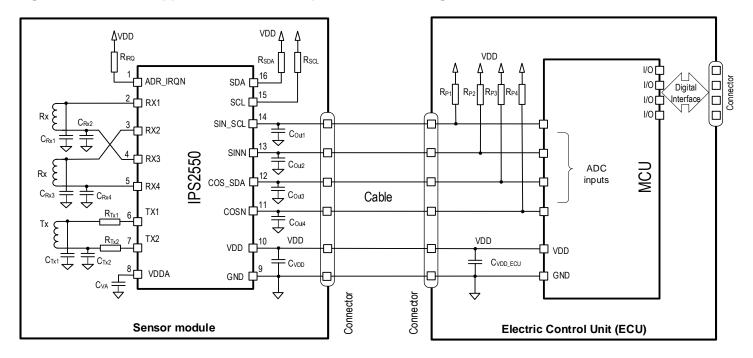

| •            | e 13. Embedded Application: Sensor and MCU are on the same PCB                             |    |

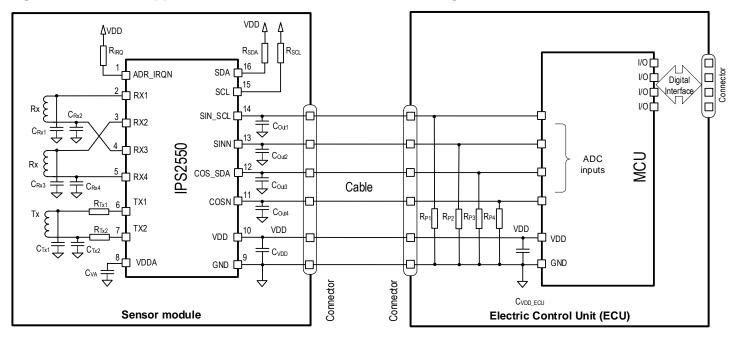

| _            | e 14. Remote Application with Pull-Up Resistors for Diagnosis                              |    |

| •            | e 15. Remote Application with Pull-Down Resistors for Diagnosis                            |    |

| _            | e 16. I2C Address Select Bits                                                              |    |

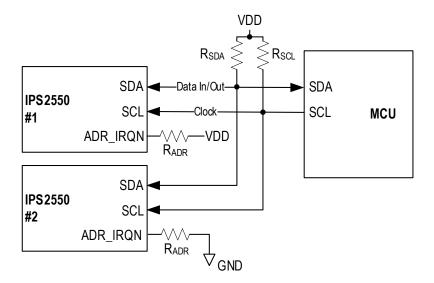

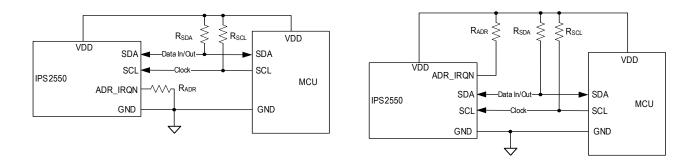

| •            | e 17. I2C Interface with Address Select                                                    |    |

| •            | e 18. I2C Interface with Address Selection by Hardware Pin Strapping Through ADR_IRQN Pin  |    |

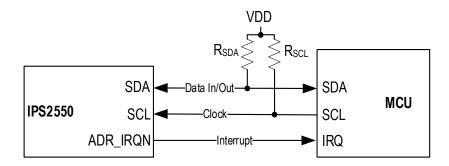

| •            | e 19. I2C Interface Configuration with Interrupt on a Single Slave                         |    |

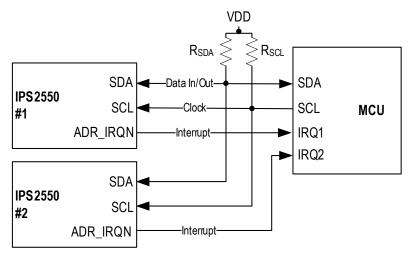

| _            | e 20. I2C Interface Configuration with Multi-slave Interrupt                               |    |

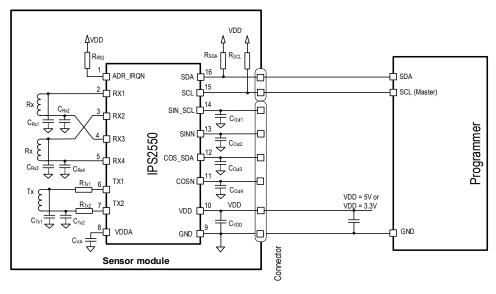

| -            | e 21. Programming the IPS2550 over the I2C Interface                                       |    |

| Figure       | e 22. End of Line Programming of the IPS2550 Through the Analog Outputs                    | 36 |

| Figure 23. | . Operating Range and Diagnostic Range                                   | 38 |

|------------|--------------------------------------------------------------------------|----|

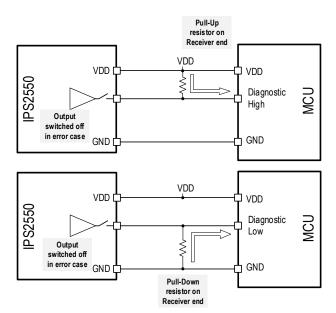

| Figure 24. | . Selection of Diagnostic Range                                          | 39 |

| Figure 25. | Parasitic Currents on Analog Outputs with Broken VDD or Broken GND Lines | 41 |

| Figure 26. | Parasitic Supply Currents through ADR_IRQN, SDA and SCL Pins             | 42 |

| Figure 27. | . Application Diagram: Dual Redundant Sensors, Dual Supply               | 45 |

| Figure 28. | . Coil Design and Signal Output for a 360° Rotary Sensor                 | 46 |

| Figure 29. | . Coil Design and Signal Output for a 2 × 180° Rotary Sensor             | 46 |

| Figure 30. | . Coil Design and Signal Output for a 3 × 120° Rotary Sensor             | 47 |

| Figure 31. | . Coil Design and Signal Output for a $4 \times 90^\circ$ Rotary Sensor  | 47 |

| List o     | of Tables                                                                |    |

| Table 1.   | Pin Descriptions                                                         | 5  |

| Table 2.   | Output Configuration                                                     | 6  |

| Table 3.   | Digital Interface Configuration                                          | 7  |

| Table 4.   | Absolute Maximum Ratings                                                 | 9  |

| Table 5.   | Electrostatic Discharges (ESD)                                           | 9  |

| Table 6.   | Operating Conditions                                                     | 10 |

| Table 7.   | IPS2550 Electrical Characteristics, 3.3V Mode                            | 12 |

| Table 8.   | IPS2550 Electrical Characteristics, 5.0V Mode                            | 13 |

| Table 9.   | LC Oscillator Specifications                                             | 14 |

| Table 10.  | Coil Receiver Front-End Specifications                                   | 15 |

| Table 11.  | Automatic Gain Control (AGC)                                             | 16 |

| Table 12.  | Diagnostic Checks                                                        | 17 |

| Table 13.  | Back-End Specification, Analog Outputs SIN_SCL, SINN, COS_SDA, COSN      | 17 |

| Table 14.  | Digital I2C Control Interface, Pins SDA and SCL                          | 18 |

| Table 15.  | I2C Interface via Analog Outputs                                         | 19 |

| Table 16.  | Digital I2C Control Interface, Pin ADR_IRQN                              | 20 |

| Table 17.  | Nonvolatile Memory                                                       | 20 |

| Table 18.  | Propagation Delay                                                        | 24 |

| Table 19.  | Output Modes and Maximum Speed                                           | 25 |

| Table 20.  | Internal Chip Temperature Sensor Characteristics                         | 29 |

| Table 21.  | I2C Address Selection Options in NVM                                     | 32 |

| Table 22.  | Programming Options Overview                                             | 37 |

| Table 23.  | Detection of Shorts between Wires                                        | 40 |

| Table 24.  | Diagnostic Levels with Pull-Up Resistors                                 | 41 |

| Table 25.  | Diagnostic Levels with Pull-Down Resistors                               | 42 |

| Table 26   | Diagnostic Features                                                      | 43 |

# 1. Pin Assignments

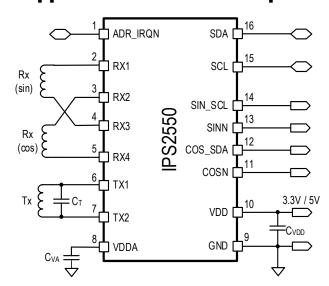

The IPS2550 is available in a 16-TSSOP 4.4mm  $\times$  5.0mm RoHS package with exposed pad RoHS package. It is qualified for an ambient temperature of -40°C to +160°C.

Figure 1. Pin Assignments for 16-TSSOP Package - Top View

# 2. Pin Descriptions

Table 1. Pin Descriptions

| Pin Number | Name                      | Туре                    | Descrip                                                                                                                                                                                                                            | tion                                                                |  |  |  |

|------------|---------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|

| 1          | ADR_IRQN                  | Digital<br>Input/Output | Address-select digital input for I2C interface address selection; push/pull interrupt output (programmable options, see Table 3).  Use the pull-up or pull-down resistor R <sub>ADR</sub> to define the I2C address, see Table 14. |                                                                     |  |  |  |

| 2          | RX1                       |                         | ASIL-C Configuration Mode (default) : receiver coil 1 (Sine, see Figure 2)                                                                                                                                                         | Compatibility Mode: receiver coil 1 (Sine, see Figure 3)            |  |  |  |

| 3          | RX2                       |                         | ASIL-C Configuration Mode (default): receiver coil 2 (Cosine, see Figure 2)                                                                                                                                                        | Compatibility Mode: receiver coil 1 (inverted sine, see Figure 3)   |  |  |  |

| 4          | RX3                       | Analog Input            | ASIL-C Configuration Mode (default): receiver coil 1 (inverted sine, see Figure 2)                                                                                                                                                 | Compatibility Mode: receiver coil 2 (Cosine, see Figure 3)          |  |  |  |

| 5          | RX4                       |                         | ASIL-C Configuration Mode (default): receiver coil 2 (inverted cosine, see Figure 2)                                                                                                                                               | Compatibility Mode: receiver coil 2 (inverted cosine, see Figure 3) |  |  |  |

| 6          | TX1                       | A 1                     | Connect the transmitter coil between the TX1 and TX2 pins. The resonant frequency                                                                                                                                                  |                                                                     |  |  |  |

| 7          | 7 TX2 Analog Input/Output |                         | with capacitors $C_{Tx1}$ from TX1 to GND and $C_{Tx2}$ from TX2 to GND as shown in Figure 2 and Figure 3. $C_{Tx1}$ and $C_{Tx2}$ must have the same capacitance value. They can be calculated with Equation 3.                   |                                                                     |  |  |  |

| Pin Number | Name                  | Туре                            | Description                                                                                                                                                                                                                                                       |

|------------|-----------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8          |                       |                                 | Internally regulated analog voltage supply, depending on selected VDD supply mode. Connect the capacitor C <sub>VA</sub> to the GND pin (see Table 6).  For 5V operation, see VDDA <sub>5</sub> in Table 8, for 3.3V operation, see VDDA <sub>3</sub> in Table 7. |

| 9          | GND                   | Committee                       |                                                                                                                                                                                                                                                                   |

| 9          | GND                   | Supply                          | Common ground connection.                                                                                                                                                                                                                                         |

| 10         | VDD                   | Supply                          | External supply voltage. Connect capacitor CVDD to the GND pin (see Table 6).                                                                                                                                                                                     |

| 11         | COSN                  | Analog Output                   | Buffered analog output; see Table 2.                                                                                                                                                                                                                              |

| 12         | COS_SDA               | Analog Output,<br>Digital I/O   | Buffered analog output; digital I2C data input/output during Programming Mode; see Table 2.                                                                                                                                                                       |

| 13         | SINN                  | Analog Output                   | Buffered analog output; see Table 2.                                                                                                                                                                                                                              |

| 14         | SIN_SCL               | Analog Output,<br>Digital Input | Buffered analog output; digital I2C clock input during Programming Mode; see Table 2.                                                                                                                                                                             |

| 15         | SCL                   | Digital Input                   | Clock input for digital programming and diagnostic I2C interface.  Connect a pull-up resistor R <sub>SCL</sub> to this pin, see Table 14.                                                                                                                         |

| 16         | SDA                   | Digital<br>Input/Output         | Open drain bi-directional data I/O line for digital programming and diagnostic I2C interface.  Connect a pull-up resistor R <sub>SDA</sub> to this pin, see Table 14.                                                                                             |

|            | Exposed Pad Heat sink |                                 | Heat sink only. It can be connected with short, direct connection to GND (pin #9), or left unconnected. Refer to Figure 4 for details.  Do not connect the exposed pad to any other potential than GND.                                                           |

### **Table 2. Output Configuration**

| Pin (See Figure 1) |          | Output Depending on Mode |                         |             | Diagnostic State, Program Options |       |       |       |

|--------------------|----------|--------------------------|-------------------------|-------------|-----------------------------------|-------|-------|-------|

| Pin Number         | Pin Name | Analog<br>Differential   | Analog Single-<br>Ended | Programming | Disabled                          | Mode1 | Mode2 | Mode3 |

| 14                 | SIN_SCL  | SIN                      | SIN                     | SCL         | SIN                               | SIN   | Hi-Z  | Hi-Z  |

| 13                 | SINN     | SINN                     | REF                     | Not used    | SINN                              | Hi-Z  | SINN  | Hi-Z  |

| 12                 | COS_SDA  | cos                      | COS                     | SDA         | cos                               | COS   | Hi-Z  | Hi-Z  |

| 11                 | COSN     | COSN                     | REF                     | Not used    | COSN                              | Hi-Z  | COSN  | Hi-Z  |

### [a] Abbreviations used in Table 2:

SIN: Sine channel output, bias voltage = VDD/2

SIN: Inverted sine channel output, bias voltage = VDD/2

COS: Cosine channel output, bias voltage = VDD/2

COSN: Inverted cosine channel output, bias voltage = VDD/2

REF: DC output bias voltage, VDD/2

SCL: Serial clock input for I2C programming

SDA: Serial bi-directional data I/O port for I2C programming

Hi-Z: Output is high ohmic; diagnostics are indicated by external pull-up or pull-down resistors

Table 3. Digital Interface Configuration

| Pin (See Fig     | ure 1)                                             | Input/Output Depending on Interface Mode [a] |                    |  |  |

|------------------|----------------------------------------------------|----------------------------------------------|--------------------|--|--|

| TSSOP Pin Number | per Pin Name I2C with Address Select I2C with Inte |                                              | I2C with Interrupt |  |  |

| 16               | SDA                                                | SDA                                          |                    |  |  |

| 15               | SCL                                                | SCL                                          |                    |  |  |

| 1                | ADR_IRQN                                           | ADR                                          | IRQN               |  |  |

[a] Abbreviations used in Table 3:

ADR\_IRQN: Combined address select input and interrupt output

ADR: Hardware address-select input for I2C Mode (two address options, depending on digital input level at the ADR\_IRQN pin)

SDA: Serial bi-directional data I/O port for I2C Modes`

SCL: Serial clock input for I2C Modes

IRQN: Interrupt output

# 3. Receiver Coil Connection Options

The IPS2550 can be configured in two user-programmable modes related to the connection of the receiver coils:

- The ASIL-C Configuration Mode (default) improves the failure detection rate of the chip because it avoids a short circuit of any receiver coil by a short between two neighboring pins.

- The Compatibility Mode (programming option) provides pin-to-pin compatibility with the IPS2200 inductive sensor IC.

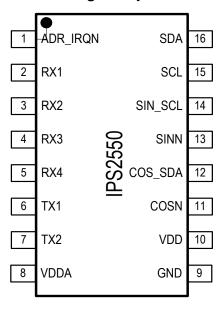

Figure 2. LC Oscillator Connection in ASIL-C Configuration with Split TX Capacitors

Configuration in ASIL-C mode with split capacitors  $C_{Tx1} = C_{Tx2}$ , Tx coil series resistors  $R_{Tx1} = R_{Tx2}$  and Output capacitors  $C_{Out1} = C_{Out2} = C_{Out3} = C_{Out4}$  for improved EMC performance.

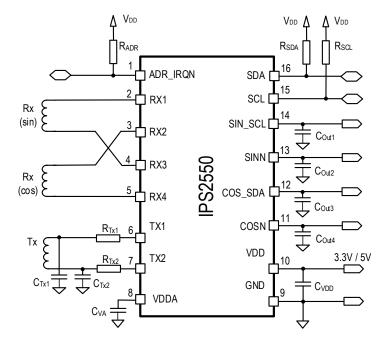

Figure 3. LC Oscillator Connection in Compatibility Mode Configuration with Split TX Capacitors

Configuration in compatibility mode with split capacitors  $C_{Tx1} = C_{Tx2}$ ,  $T_{x}$  coil series resistors  $R_{Tx1} = R_{Tx2}$  and Output capacitors  $C_{Out1} = C_{Out2} = C_{Out3} = C_{Out4}$  for improved EMC performance.

The oscillator frequency is determined by the values of coil L and capacitors CTx1 and CTx2 as the following:

Oscillator frequency:

$$f_{TX} = \frac{1}{2\pi \sqrt{\frac{L \times C_{Tx1} \times C_{Tx2}}{C_{Tx1} + C_{Tx2}}}}$$

**Equation 1**

For  $C_{Tx1} = C_{Tx2}$ :

$$f_{TX} = \frac{1}{2\pi \sqrt{L\frac{C_{Tx1}}{2}}}$$

**Equation 2**

$$CTx1 = CTx2 = \frac{2}{L(2\pi f_{TX})^2}$$

**Equation 3**

Where:

$\begin{array}{l} f_{TX} = Oscillator \ frequency \ in \ MHz \\ L = Coil \ impedance \ in \ \mu Henry \\ C_{Tx1}, \ C_{Tx2} = Capacitance \ in \ \mu Farad \end{array}$

Note: RTx1 = RTx2 = 220hm (typical)

# 4. Absolute Maximum Ratings

The absolute maximum ratings are stress ratings only. Stresses greater than those listed below can cause permanent damage to the device. Functional operation of the IPS2550 at the absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions could affect device reliability.

All voltage levels refer to GND.

Table 4.

Absolute Maximum Ratings

| Symbol               | Parameter                                     | Conditions                                                                                             | Minimum                                                                                    | Maximum | Units |

|----------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|-------|

| V <sub>VDDmax</sub>  | External supply voltage                       | Continuous                                                                                             | -18                                                                                        | 18      | V     |

| V <sub>OUT</sub>     | SIN_SCL, SINN,COS_SDA and COSN output voltage | Continuous                                                                                             | -18                                                                                        | 18      | V     |

| V <sub>RX1</sub>     | Receiver coil pin: RX1                        |                                                                                                        |                                                                                            |         |       |

| V <sub>RX2</sub>     | Receiver coil pin: RX2                        |                                                                                                        | 10                                                                                         | 12      | V     |

| V <sub>RX3</sub>     | Receiver coil pin: RX3                        |                                                                                                        | -12                                                                                        |         | V     |

| $V_{RX4}$            | Receiver coil pin: RX4                        |                                                                                                        |                                                                                            |         |       |

| V <sub>DIGITAL</sub> | Digital IO pins: SCL, SDA, ADR_IRQN           |                                                                                                        | -0.3                                                                                       | VDD+0.3 | V     |

| V <sub>Tx1_2</sub>   | Transmitter pins, TX1, TX2                    |                                                                                                        | -0.3                                                                                       | 5.6     | V     |

| VvDDAmax             | VDDA internal LDO output                      | VDDA is internally regulated with external capacitor to GND. No other connection to external voltages. | For 5V operation, see<br>VDDA₅ in Table 8,<br>for 3.3V operation, see<br>VDDA₃ in Table 7. |         | V     |

Table 5. Electrostatic Discharges (ESD)

| Symbol                | Parameter                                                                                                                      | Conditions                                   | Minimum | Typical | Maximum | Units |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------|---------|---------|-------|

| V <sub>ESD</sub>      | ESD tolerance for all pins: Human Body Model (HBM) 100pF/1.5kΩ                                                                 | According to AEC-Q100-002 classification H2  | ±2      |         |         | kV    |

| V <sub>ESD</sub> ,OUT | ESD tolerance for pins with potential external cable connection: SIN_SCL, COS_SDA, SINN, COSN, ADR_IRQN, VDD (HBM 100pF/1.5kΩ) | According to AEC-Q100-002 classification H3A | ±4      |         |         | kV    |

| V <sub>CDM</sub>      | ESD tolerance for all pins: Charged-Device Model (CDM)                                                                         | According to AEC-Q100-011 classification C3B | ±500    |         |         | V     |

| V <sub>CDM,C</sub>    | ESD tolerance for corner pins ADR_IRQN, SDA, VDDA, GND (CDM)                                                                   | According to AEC-Q100-011 classification C3B | ±750    |         |         | V     |

# 5. Operating Conditions

Conditions: VDD =  $3.3V\pm0.3V$  or  $5.0V\pm0.5V$ ,  $T_{AMB}$  =  $-40^{\circ}C$  to  $+160^{\circ}C$ , unless otherwise noted.

**Table 6. Operating Conditions**

| Symbol                   | Parameter                                                                 | Conditions                                                                                          | Minimum  | Typical                  | Maximum | Units |

|--------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------|--------------------------|---------|-------|

| T <sub>AMB_TSSOP</sub>   | Ambient temperature                                                       | 16-TSSOP package with exposed pad                                                                   | -40      |                          | 160¹    | °C    |

| TJ                       | Junction temperature                                                      |                                                                                                     | -40      |                          | 165     | °C    |

| Tstor                    | Storage temperature                                                       | Unmounted units must be limited to 10 hours at temperatures above 125°C                             | -55      |                          | 160     | °C    |

|                          | Thermal resistance junction to                                            | Copper ground planes under exposed pad on 4 layer PCB, 3x3 thermal vias between layers.             |          | 35.48                    |         |       |

| R <sub>THJA_TSSOP</sub>  | ambient: 16-TSSOP package with exposed pad. Velocity = 0m/s JEDEC MO-153. | Copper ground planes under exposed pad on 2 layer PCB, 3x3 thermal vias between layers.             |          | 39.96                    |         | K/W   |

|                          | 02520 MO 100.                                                             | Without PCB ground plane under exposed pad.                                                         |          | 61.26                    |         |       |

| R <sub>THJC_TSSOP</sub>  | Thermal resistance junction to case                                       | Junction to bottom of package                                                                       |          | 6.42                     |         | K/W   |

| t <sub>pup</sub>         | Start-up time                                                             | Power-on reset (POR) to valid output signal                                                         |          |                          | 5       | ms    |

| .,                       | Input rotational velocity,                                                | Electrical revolutions per minute                                                                   |          |                          | 600 000 | rpm   |

| V <sub>EL</sub>          | Electrical speed; sine or cosine periods                                  | Input frequency                                                                                     |          |                          | 10      | kHz   |

| Vvdda_th_h               | Power-on reset (POR), high threshold                                      | The device is activated when VDDA increases above this threshold                                    |          |                          | 2.49    | ٧     |

| Vvdda_th_l:              | Power-on reset, low threshold                                             | The device is deactivated when VDDA decreases below this threshold                                  | 2.08     |                          |         | V     |

| VDDA <sub>POR_HYST</sub> | Power-on reset hysteresis                                                 | At VDDA pins                                                                                        |          | 110                      |         | mV    |

| Ivdda                    | VDDA short circuit current limitation                                     | VDDA must be connected to a capacitor C <sub>VA</sub> . No other external load allowed at this pin. | 40       |                          | 85      | mA    |

|                          |                                                                           | Without coils, no load                                                                              | 5        |                          | 12      | mA    |

| lcc                      | Current consumption                                                       | Programmable transmitter coil drive current (depending on inductance of the transmitter coil)       | For valu | alues, refer to Table 9. |         | mA    |

| Cva                      | Capacitor from VDDA pin to GND                                            |                                                                                                     |          | 100                      |         | nF    |

| C <sub>VDD</sub>         | Capacitor from VDD pin to GND                                             | Nominal value                                                                                       | 70       |                          |         | nF    |

$<sup>^{\</sup>rm 1}$  Ambient temperature above 155  $^{\rm \circ}{\rm C}$  limited to 120 hours over lifetime.

\_\_\_

| Symbol              | Parameter                                                         | Conditions                                                                                                      | Minimum | Typical | Maximum | Units |

|---------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| INL <sub>uv3V</sub> | Accuracy, 3.3V Mode, VDD=<br>under-voltage alarm level to<br>3.0V |                                                                                                                 |         |         | ±0.2    | % FS  |

| INL <sub>3V</sub>   | Accuracy, 3.3V Mode,<br>VDD= 3.0 to 3.6V                          | With ideal sinusoidal input signals,                                                                            |         |         | ±0.1    | % FS  |

| INL <sub>ov3V</sub> | Accuracy, 3.3V Mode, VDD= 3.6V to over-voltage alarm level        | 150mV <sub>pk-pk</sub> Differential output mode, Transmitter frequency = 3.5MHz AGC = on Channel swapping = 0ff |         |         | ±0.2    | % FS  |

| INL <sub>uv5V</sub> | Accuracy, 5V Mode, VDD=<br>under-voltage alarm level to<br>4.5V   |                                                                                                                 |         |         | ±0.2    | % FS  |

| INL <sub>5V</sub>   | Accuracy, 5.0V Mode,<br>VDD= 4.5 to 5.5V                          |                                                                                                                 |         |         | ±0.1    | % FS  |

| INL <sub>ov5V</sub> | Accuracy, 5.0V Mode, VDD=<br>5.5V to over-voltage alarm level     |                                                                                                                 |         |         | ±0.2    | % FS  |

<sup>[</sup>a] % FS = percent of full scale = accuracy in % per period, where 100% is the angle range of one electrical period.

For rotary multi-period designs, one electrical period = 360° (one full turn) divided by the number of periods per turn, see examples in section 20.

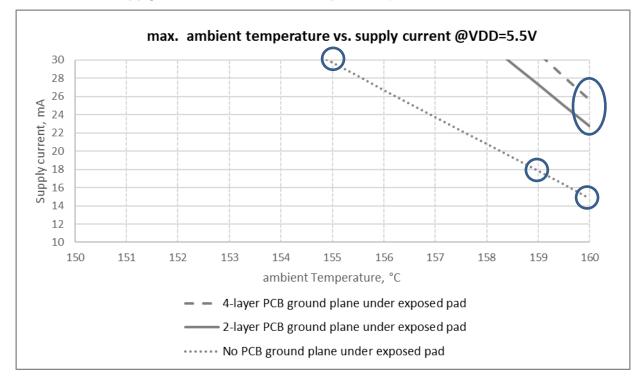

## 6. Ambient Temperature Range

The minimum ambient temperature for the IPS2550 is -40°C.

The maximum ambient temperature depends on the following factors:

- The maximum junction temperature, see Table 6 for details.

- The supply current. The total power consumption of the chip depends on the supply voltage, the internal supply current, and the user programmable transmitter coil current. The programmable transmitter coil current is shown in Table 9 and the internal circuit current consumption is shown in Table 6.

- The minimum usable coil current in a given application. Typically, smaller coils require more transmitter coil current and larger coils can operate with less coil current. Typical coil designs in the range of 25mm to 30mm coil diameter can require approximately 3mA to 5mA coil current, respectively around 12mA to 14mA supply current. The IPS2550 can drive as high as 20mA of transmitter coil current.

- The temperature range of the supplier part qualification. The IPS2550 is qualified for -40°C to +160°C ambient temperature.

- The thermal resistance of the package in combination with a copper ground plane area on the PCB.

The maximum supply current at VDD = 5.5V versus the ambient temperature with different PCB layers and no airflow cooling is shown in the circled areas of Figure 4. For example, the maximum supply current (internal current + transmitter coil current) at T<sub>ambient</sub> = 160°C for a PCB with copper ground plane under the exposed pad is 25.6mA for a 4-layer PCB and 22.8mA for a 2-layer PCB. The ground plane is assumed having minimum the same rectangular area as the exposed pad and copied to all layers with a 3x3 array of interconnect vias between each layer.

Note: ignore the small half circles extended at each short side of the exposed pad on the package drawing at the end of this document, they do not need to be copied to the PCB ground plane.

Without copper ground plane(s) under the exposed pad, the maximum current consumption at 160°C ambient temperature is 14.8mA. If the maximum ambient temperature is less than 155°C and the maximum current consumption is below 29.7mA, no PCB ground planes are needed. If the maximum supply current is below 18mA, no PCB ground planes are needed up to an ambient temperature of 159°C

Figure 4. Maximum Supply Current vs Ambient Temperature, with and without Ground Plane

## 7. Electrical Characteristics

The following electrical specifications are valid for the operating conditions as specified in Table 6: (T<sub>AMB</sub> is -40°C to 160°C).

Table 7. IPS2550 Electrical Characteristics, 3.3V Mode

| Symbol            | Parameter                            | Conditions                                                                                         | Minimum | Typical | Maximum | Units |

|-------------------|--------------------------------------|----------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| VDD3              | Supply voltage                       |                                                                                                    | 3.0     | 3.3     | 3.6     | V     |

| V3 <sub>OVR</sub> | Over-voltage detection, VDD rising   | An over-voltage alarm is created if VDD rises above this limit                                     | 3.7     | 3.86    | 4.1     | V     |

| V3 <sub>OVF</sub> | Over-voltage detection, VDD falling  | An over-voltage alarm is cleared if VDD falls below this limit                                     | 3.65    | 3.79    | 4.0     | V     |

| V3 <sub>оvн</sub> | Over-voltage detection hysteresis    |                                                                                                    |         | 70      |         | mV    |

| V3 <sub>UVR</sub> | Under-voltage detection, VDD falling | An under-voltage alarm is created if VDD falls below this limit                                    | 2.65    | 2.75    | 2.90    | V     |

| V3 <sub>UVF</sub> | Under-voltage detection, VDD rising  | An under-voltage alarm is cleared if VDD rises above this limit                                    | 2.70    | 2.85    | 3.00    | V     |

| V3 <sub>UVH</sub> | Under-voltage detection hysteresis   |                                                                                                    |         | 100     |         | mV    |

| VDDA₃             | Analog supply voltage                | Internally regulated. Connect capacitor C <sub>VA</sub> = 100nF between VDDA and GND (see Table 6) | 2.85    | 3.0     | 3.1     | V     |

| Symbol                 | Parameter                               | Conditions                                                          | Minimum | Typical | Maximum | Units |

|------------------------|-----------------------------------------|---------------------------------------------------------------------|---------|---------|---------|-------|

| V3VDDA <sub>UVF</sub>  | VDDA under-voltage detection            | An under-voltage alarm is created if VDDA falls below these limits. | 2.59    |         | 2.80    | ٧     |

| V3VDDA <sub>UVRr</sub> | VDDA under-voltage detection            | An under-voltage alarm is cleared if VDDA rises above these limits. | 2.63    |         | 2.85    | ٧     |

| V3VDDA <sub>UVH</sub>  | VDDA Under-voltage detection hysteresis |                                                                     |         | 45      |         | mV    |

# Table 8. IPS2550 Electrical Characteristics, 5.0V Mode

| Symbol                 | Parameter                               | Conditions                                                                                           | Minimum | Typical | Maximum | Units |

|------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| VDD <sub>5</sub>       | Supply voltage                          |                                                                                                      | 4.5     | 5.0     | 5.5     | V     |

| V5 <sub>ovr</sub>      | Over-voltage detection, VDD rising      | An over-voltage alarm is created if VDD rises above this limit                                       | 5.60    | 5.84    | 6.10    | V     |

| V5 <sub>ovf</sub>      | Over-voltage detection, VDD falling     | An over-voltage alarm is cleared if VDD falls below this limit                                       | 5.55    | 5.76    | 6.05    | V     |

| V5 <sub>ovн</sub>      | Over-voltage detection hysteresis       |                                                                                                      |         | 80      |         | mV    |

| V5 <sub>UVR</sub>      | Under-voltage detection, VDD falling    | An under-voltage alarm is created if VDD falls below this limit                                      | 4.10    | 4.33    | 4.45    | V     |

| V5 <sub>UVF</sub>      | Under-voltage detection, VDD rising     | An under-voltage alarm is cleared if VDD rises above this limit                                      |         |         | 4.49    | V     |

| V5 <sub>UVH</sub>      | Under-voltage detection hysteresis      |                                                                                                      |         | 70      |         | mV    |

| VDDA₅                  | Analog supply voltage                   | Internally regulated. Connect a capacitor C <sub>VA</sub> = 100nF between VDDA and GND (see Table 6) | 3.9     | 4.0     | 4.1     | V     |

| V5VDDA <sub>UVF</sub>  | VDDA under-voltage detection            | A VDDA under-voltage alarm is triggered when VDDA falls below these limits.                          | 3.50    |         | 3.79    | V     |

| V5VDDA <sub>UVRr</sub> | VDDA under-voltage detection            | A VDDA under-voltage alarm is cleared if VDDA rises above these limits.                              |         |         | 3.87    | ٧     |

| V5VDDA <sub>UVH</sub>  | VDDA Under-voltage detection hysteresis |                                                                                                      |         | 65      |         | mV    |

Table 9. LC Oscillator Specifications

| Symbol            | Parameter                                                 | Conditions                                                                      | Minimum | Typical | Maximum | Units |

|-------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------|---------|---------|---------|-------|

| R <sub>Peq</sub>  | Equivalent parallel resistance of the LC resonant circuit | See Equation 4                                                                  | 250     |         |         | Ω     |

| fLC               | Excitation frequency                                      | LC oscillator frequency is determined by external components L and C.           |         |         | 5.6     | MHz   |

| V <sub>TX_P</sub> | LC oscillator amplitude                                   | Peak-to-peak voltage; pins TX1 vs. TX2; all modes. Adjustable by coil current.  |         | 6       | 11      | Vpp   |

| ILC               | Programmable transmitter coil drive current               | Equivalent DC current.  Programmable, depending on transmitter coil inductance. | 0       | 3       | 20      | mA    |

| RTx1,RTx2         | TX Series resistor                                        | For reduced EMC emission                                                        |         | 22      |         | Ω     |

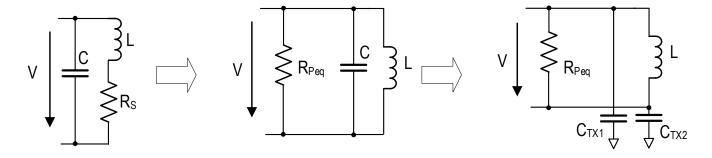

Figure 5. Parallel Resonator Circuit

The equivalent parallel resistance  $R_{Peq}$  of the LC oscillator can be calculated using Equation 4. It defines the minimum loss resistance that the oscillator can drive for safe operation.

Note: for improved EMC performance, it is recommended to split capacitor C into two equal capacitors with double capacitance, connected to GND:  $C_{TX1} = C_{TX2} = 2C$ . See also Figure 2 and Figure 3 for further details.

$$R_{Peq} = \frac{1}{R_S} \times \frac{L}{C}$$

Equation 4

Where

$R_{Peq}$  Equivalent parallel resistance of the LC oscillator.

R<sub>S</sub> Serial resistance of the transmitter coil at the transmitter frequency.

- L Coil reactance at the resonant frequency.

- C Capacitance of the parallel capacitor

Note that the capacitor losses are not included in the equation, since in case of C0G or NP0 ceramics they can be neglected.

**Table 10. Coil Receiver Front-End Specifications**

| Symbol                  | Parameter                                                                    | Conditions                                                                                          | Minimum | Typical | Maximum | Units           |

|-------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------|---------|---------|-----------------|

|                         |                                                                              | Input signal full range to maintain AGC target levels: 3.0V p-p AGC target, gain boost bit disabled | 25      |         | 1500    |                 |

| V <sub>RX</sub>         |                                                                              | Input signal full range to maintain AGC target levels: 3.0V p-p AGC target, gain boost bit enabled  | 13      |         | 780     | m\/             |

| VKX                     | Receiver coil amplitude.                                                     | Input signal full range to maintain AGC target levels: 1.8V p-p AGC target, gain boost bit disabled | 15      |         | 920     | ${\sf mV_{pp}}$ |

|                         |                                                                              | Input signal full range to maintain AGC target levels: 1.8V p-p AGC target, gain boost bit enabled  | 8       |         | 470     |                 |

| A <sub>IN_mm</sub>      | Maximum amplitude mismatch correction                                        | Programmable individual gain mismatch correction of Receiver coil                                   | 13      |         | 20      | %               |

| _                       | Amplitude mismatch step size                                                 | signals (SIN and COS)                                                                               | 0.1     |         | 0.15    | %               |

| Ain_offset_pos%         | Maximum positive input offset correction.                                    |                                                                                                     | +0.17   |         | +0.23   | %               |

| Ain_offset_neg%         | Maximum negative input offset correction.                                    | Differential input offsets of sine or cosine signal, percentage of transmitter                      | -0.25   |         | -0.17   | %               |

| AIN_OFFSET_mV           | Input offset correction range at typical oscillator amplitude (see Table 9). | coil amplitude.                                                                                     | -7.5    |         | 7.5     | mV              |

| OFF <sub>CORR_RES</sub> | Input offset correction step size                                            |                                                                                                     |         | 0.0015  |         | %               |

| D-                      | Coil receiver DC input                                                       | Common mode to GND                                                                                  |         | 20      |         | kΩ              |

| R <sub>Rx</sub>         | resistance                                                                   | Differential                                                                                        |         | 100     |         | kΩ              |

| C <sub>RX1</sub>        |                                                                              |                                                                                                     |         |         |         |                 |

| C <sub>RX2</sub>        | Receiver input filter                                                        | For improved EMC immunity                                                                           |         | 100     |         | pF              |

| C <sub>RX3</sub>        | capacitors                                                                   | TO IMPIOVED LIVIO IMMUNITY                                                                          |         | 100     |         | ρı              |

| C <sub>RX4</sub>        |                                                                              |                                                                                                     |         |         |         |                 |

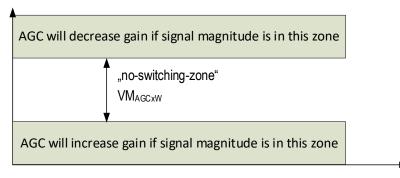

## Table 11. Automatic Gain Control (AGC)

| Symbol               | Parameter                                            | Conditions                                                                    | Minimum                          | Typical                | Maximum | Units           |

|----------------------|------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------|------------------------|---------|-----------------|

| VOUT <sub>AGC1</sub> | Output signal amplitude, single ended, AGC enabled   | Program option1, for 3.3V Mode and 5V mode (default)                          |                                  | 1.8                    | 2.2     | $V_{PP}$        |

| VM <sub>AGC1W</sub>  | AGC1, no-switching window                            | AGC1 signal magnitude window, in which gain setting is not changed            | 200                              | 207                    | 218     | mV              |

| VOUT <sub>AGC2</sub> | Output signal amplitude, single ended, AGC enabled   | Program option2, for 5V mode                                                  | Program option2, for 5V mode 2.6 |                        | 3.4     | V <sub>PP</sub> |

| VM <sub>AGC2W</sub>  | AGC2, no-switching window                            | AGC2 signal magnitude window, in which gain setting is not changed            |                                  |                        | 208     | mV              |

|                      | Overall gain adjustment Default setting 2            |                                                                               | 2                                |                        | 120     |                 |

| GAINAFE              | range, sine and cosine signal channel                | With gain boost bit set                                                       | 4                                |                        | 240     | V/V             |

| AGCAttack            | AGC attack time, increase/decrease in same direction |                                                                               |                                  | 10                     |         | μs              |

| AGCDecay             | AGC decay time                                       | AGC reversing direction, programmable decay time                              |                                  | 0<br>30<br>100<br>300  |         | ms              |

| tswap                | Channel swapping cadence                             | Channel swapping functional safety feature enabled, programmable cadence time |                                  | 10<br>50<br>100<br>200 |         | μs              |

**Table 12. Diagnostic Checks**

| Symbol                   | Parameter                                                                                          | Conditions                                                                                                                                                                           | Minimum                                                                       | Typical | Maximum           | Units |

|--------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------|-------------------|-------|

| t <sub>fail</sub>        | Failure reaction time, (time to flag an error condition at the ADR_IRQN pin)                       | Chip internal diagnostic checks                                                                                                                                                      |                                                                               |         | 500               | μs    |

| t <sub>oc_assert</sub>   | Debounce time for switching off the analog output amplifiers in case of over-current               | If the load current on any analog output exceeds the current limit (I <sub>OvL</sub> ), all four analog outputs are switched off (tri-state) after this time. [a]                    | tput exceeds the nit (I <sub>OvL</sub> ), all four 135 tputs are switched off |         | t <sub>fail</sub> | μs    |

| tcm_assert               | Debounce time for switching off the analog output amplifiers in case of output common mode failure | If the common mode voltage on any analog output exceeds the V <sub>CM</sub> limit (DC <sub>OFF_AL</sub> ), all four analog outputs are switched off (tri-state) after this time. [b] | 40                                                                            |         | <sup>†</sup> fail | μs    |

| toc_deassert             | Debounce time for temporary release of analog outputs after over-current failure                   | Following an over-current switch-off condition, all outputs are turned on again after this time                                                                                      | 4.61                                                                          | 4.68    | 4.75              | ms    |

| t <sub>cm_deassert</sub> | Debounce time for temporary release of analog outputs after output common mode failure             | Following an output common mode switch-off condition, all outputs are turned on again after this time                                                                                | See toc_deassert                                                              |         |                   | ms    |

| R_open_th                | Resistance of Rx coil, open coil detection                                                         | Rx coil error flag activated                                                                                                                                                         | 91                                                                            |         | 154               | kΩ    |

| R_short_GND              | External resistance from any coil input to GND, short-to-ground detection                          | Rx coil error flag activated                                                                                                                                                         | 68                                                                            |         | 117               | kΩ    |

| R_short_VDD              | External resistance from any coil input to VDD, short to VDD detection                             | Rx coil error flag activated;<br>VDD = 3.0 to 5.5V                                                                                                                                   | 14                                                                            |         | 233               | kΩ    |

| R_short_th               | Rx coil error flag cleared                                                                         | Rx coil error flag cleared                                                                                                                                                           | coil error flag cleared 50                                                    |         | 130               | kΩ    |

| DCoff_AL                 | DC common mode output offset alarm limits                                                          | Absolute value relative to VDD/2. Output offset alarm flag activated.                                                                                                                | 75                                                                            |         | 195               | mV    |

<sup>[</sup>a] Over-current durations shorter than these limits are ignored.

Table 13. Back-End Specification, Analog Outputs SIN\_SCL, SINN, COS\_SDA, COSN

| Symbol                | Parameter                                     | Conditions                         | Minimum   | Typical | Maximum   | Units |

|-----------------------|-----------------------------------------------|------------------------------------|-----------|---------|-----------|-------|

| V3 <sub>out</sub>     | Analog output range, 3.3V option              | $-1.5$ mA ≤ $I_{OUT}$ ≤ $1.5$ mA   | GND + 0.4 |         | VDD – 0.4 | V     |

| V5 <sub>out</sub>     | Analog output range, 5V option                | $-2.5$ mA ≤ $I_{OUT}$ ≤ $2.5$ mA   | GND + 0.4 |         | VUU – 0.4 | V     |

| VDD <sub>OUT_CM</sub> | Output DC offset voltage, common mode voltage | All modes,<br>Deviation from VDD/2 | -35       | 0       | 35        | mV    |

| DCoffdrift            | DC offset voltage drift                       | Over temperature range             | -50       |         | 50        | μV/°C |

<sup>[</sup>b] Common Mode failure durations shorter than these limits are ignored.

| Symbol | Parameter                   | Conditions Minimu                                      |    | Typical | Maximum | Units             |

|--------|-----------------------------|--------------------------------------------------------|----|---------|---------|-------------------|

| Іоитз  | Output current; 3.3V option | Voltage change ±6mV relative to no load -3             |    |         | +3      | mA                |

| Іоит5  | Output current; 5V option   | Voltage change ±10mV relative to no load               |    |         | +5      | mA                |

| lovL   | Output overload current     | Short circuit current limit                            | 15 |         | 30      | mA                |

| Noise  | Device output noise         | Maximum gain, no output filtering, shorted coil inputs |    | 2       | 5       | mV <sub>rms</sub> |

| Соит1  |                             |                                                        |    |         |         |                   |

| Соит2  | Output filter consoiters    | For improved EMC                                       |    |         | 47      | nF                |

| Соитз  | Output filter capacitors    | immunity, placed close to IC output                    |    |         | 4/      | IIF               |

| Соит4  |                             |                                                        |    |         |         |                   |

# Table 14. Digital I2C Control Interface, Pins SDA and SCL

| Symbol                                 | Parameter                                                   | Conditions                                                                                | Minimum | Typical | Maximum | Units |

|----------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| VIH                                    | High level input voltage, all modes                         | IRQN address select input,                                                                | 0.7•VDD |         | VDD+0.3 | V     |

| VIL                                    | Low level input voltage, all modes                          | SCL clock input,<br>SDA data input                                                        | -0.3    |         | 0.3•VDD | V     |

| ILEAK                                  | Input leakage current                                       | VDD = 0V to 5.5V                                                                          | -8      |         | 1.5     | μΑ    |

| V <sub>I_STR_hyst</sub>                | Hysteresis of Schmitt trigger input                         | SCL clock input                                                                           | 0.1     |         |         | V     |

| $V_{\text{OL\_SDA}}$                   | SDA low level output voltage, open drain                    | 3mA sink current                                                                          | 0       |         | 0.4     | V     |

| $I_{OL\_SDA}$                          | SDA Low level output current                                | $V_{OL}$ = 0.4V, VDD=5.5V, $R_P$ =2k $\Omega$                                             | 3       |         |         | mA    |

| C <sub>IN</sub>                        | Capacitance of SDA/SCL pin                                  | Pad and ESD protection                                                                    |         |         | 10      | pF    |

| f <sub>SCL</sub>                       | SCL clock frequency                                         |                                                                                           | 0       |         | 100     | kHz   |

| $t_{LOW}$                              | LOW period of SCL clock                                     |                                                                                           | 4.7     |         |         | μs    |

| <b>t</b> HIGH                          | HIGH period of SCL clock                                    |                                                                                           | 4.0     |         |         | μs    |

| <b>t</b> <sub>R</sub>                  | Rise time SDA/SCL                                           | V <sub>IHmin</sub> to V <sub>ILmax</sub>                                                  |         |         | 1       | μs    |

| t <sub>F</sub>                         | Fall time SDA/SCL                                           | V <sub>IHmax</sub> to V <sub>ILmin</sub>                                                  |         |         | 0.3     | μs    |

| Св                                     | External capacitive load for each bus line                  |                                                                                           |         |         | 400     | pF    |

| R <sub>SDA</sub> ,<br>R <sub>SCL</sub> | External pull-up resistor at pins SDA and SCL               | Resistor value and capacitive load on these pins are limiting the maximum clock frequency | 1.8     | 4.7     |         | kΩ    |

| R <sub>ADR</sub>                       | External resistor at pin ADR_IRQN for I2C address selection | Pull-up or pull-down, depending on I2C address setting.                                   | 1.8     | 4.7     |         | kΩ    |

Table 15. I2C Interface via Analog Outputs

| Symbol                  | Parameter                                                 | Conditions                                               | Minimum | Typical      | Maximum | Units |

|-------------------------|-----------------------------------------------------------|----------------------------------------------------------|---------|--------------|---------|-------|

| VIH                     | SIN_SCL/COS_SDA high level input voltage                  |                                                          | 0.7•VDD |              | VDD+0.3 | V     |

| V <sub>IL</sub>         | SIN_SCL/COS_SDA low level input voltage                   |                                                          | -0.3    |              | 0.3•VDD | V     |

| Vi_STR_hyst             | Hysteresis of Schmitt trigger inputs, SIN_SCL and COS_SDA |                                                          | 0.1     |              |         | V     |

| Vol_cos_sda             | COS_SDA low level output voltage, open-drain              | 3mA sink current                                         | 0       |              | 0.4     | V     |

| I <sub>OL_COS_SDA</sub> | COS_SDA Low level output current                          | $V_{OL}$ = 0.4V, VDD=5.5V, $R_P$ =1.8k $\Omega$          | 3       |              |         | mA    |

| l <sub>IN</sub>         | SIN_SCL/COS_SDA input leakage current                     | VDD = 0V to 5.5V                                         | -1.5    |              | 8       | μA    |

| Cin                     | Capacitance of SCL and SDA pins                           | Pad and ESD protection                                   |         |              | 10      | pF    |

| fscL                    | SCL clock frequency                                       |                                                          | 4       |              | 25      | kHz   |

| tLOW                    | LOW period of SCL clock                                   |                                                          | 20      |              | 125     | μs    |

| thigh                   | HIGH period of SCL clock                                  |                                                          | 20      |              | 125     | μs    |

| t <sub>F</sub>          | Fall time SIN_SCL/COS_SDA                                 | VIHmin to VILmax                                         |         | 0.8          | 1.2     | μs    |

| Св                      | External capacitive load for SIN_SCL and COS_SDA          |                                                          |         |              | 47      | nF    |

| <b>t</b> PEU            | Program Entry window after POR                            | First time window to start sending unlock command        | 1.5     |              | 5       | ms    |

| t <sub>PW</sub>         | Program Start window after Unlock                         | Second time window to complete first programming command |         |              | 75      | ms    |

|                         |                                                           | Optional; for diagnostic indication                      |         | See Table 24 |         | kΩ    |

| Rpu                     | External pull-up resistors                                | Optional; during programming on pins SIN_SCL and COS_SDA | 1.8     |              |         | kΩ    |

| R <sub>PD</sub>         | External pull-down resistors                              | Optional; for diagnostic indication                      | _       | See Table 25 |         | kΩ    |

Table 16. Digital I2C Control Interface, Pin ADR\_IRQN

| Symbol                  | Parameter                          | Conditions          | Minimum | Typical | Maximum | Units |

|-------------------------|------------------------------------|---------------------|---------|---------|---------|-------|

| V <sub>IH</sub>         | ADR_IRQN High level input voltage  |                     | 0.7•VDD |         | VDD+0.3 | V     |

| V <sub>IL</sub>         | ADR_IRQN Low level input voltage   |                     | -0.3    |         | 0.3•VDD | V     |

| V <sub>I_STR_hyst</sub> | Hysteresis Schmitt trigger input   |                     | 0.1     |         |         | V     |

| ILEAK                   | Input leakage current              |                     | -8      |         | 1.5     | μA    |

| V <sub>OH</sub>         | ADR_IRQN high level output voltage | ADR_IRQN configured | 0.8•VDD |         | VDD+0.3 | V     |

| VoL                     | ADR_IRQN low level output voltage  | as interrupt pin    | -0.3    |         | 0.2•VDD | V     |

**Table 17. Nonvolatile Memory**

| Symbol              | Parameter                | Conditions                      | Minimum             | Typical                       | Maximum | Units            |

|---------------------|--------------------------|---------------------------------|---------------------|-------------------------------|---------|------------------|

| DR <sub>NVM</sub>   | Data retention           | According to AEC Q100           |                     | > 100 at 25°C<br>>15 at 100°C |         | Years            |

| t <sub>Wr_NVM</sub> | Write temperature        | Allowed ambient temperature     | -40                 |                               | 135     | °C               |

| t <sub>Rd_NVM</sub> | Read temperature         | range for read and write access | -40                 |                               | 160     | °C               |

| Cwr_Nvm             | Endurance <sup>[a]</sup> | Over product lifetime           |                     |                               | 1000    | NVM Write Cycles |

| C <sub>Rd_NVM</sub> | Read Cycles              | Over product lifetime           | 5x 10 <sup>11</sup> | 1x 10 <sup>12</sup>           |         | NVM Read events  |

<sup>[</sup>a] Verified number of program/erase cycles. Qualified with 2000 cycles

# 8. Circuit Description