#### **GENERAL DESCRIPTION**

This document describes the specification for the IDTF1953 Digital Step Attenuator. The F1953 is part of a family of *Glitch-Free*<sup>TM</sup> DSAs optimized for the demanding requirements of communications Infrastructure. These devices are offered in a compact 4x4 QFN package with 50  $\Omega$  impedances for ease of integration.

#### COMPETITIVE ADVANTAGE

Digital step attenuators are used in Receivers and Transmitters to provide gain control. The IDTF1953 is a 6-bit step attenuator optimized for these demanding applications. The silicon design has very low insertion loss and low distortion (> +60 dBm IP3<sub>I</sub>.) The device has pinpoint accuracy and settles to final attenuation value within 400 ns. Most importantly, the F1953 includes IDT's *Glitch-Free*<sup>TM</sup> technology which results in less than 0.5 dB of overshoot ringing during MSB transitions. This is in stark contrast to competing DSAs that *glitch as much as 10 dB* (see p. 10.)

- ✓ Lowest insertion loss for best SNR

- ✓ Glitch-Free<sup>™</sup> when transitioning won't damage PA or ADC

- ✓ Extremely accurate with low distortion

#### **APPLICATIONS**

- Base Station 2G, 3G, 4G, TDD radio-cards

- · Repeaters and E911 systems

- Digital Pre-Distortion

- Point to Point Infrastructure

- Public Safety Infrastructure

- WIMAX Receivers and Transmitters

- Military Systems, JTRS radios

- · RFID handheld and portable readers

- Cable Infrastructure

#### PART# MATRIX

| Part# | Freq range | Resolution<br>/ Range | Control              | IL   | Pinout             |

|-------|------------|-----------------------|----------------------|------|--------------------|

| F1950 | 150 - 4000 | 0.25 / 31.75          | Parallel &<br>Serial | -1.3 | PE43702<br>PE43701 |

| F1951 | 100 - 4000 | 0.50 / 31.5           | Serial Only          | -1.2 | HMC305             |

| F1952 | 100 – 4000 | 0.50 / 15.5           | Serial Only          | -0.9 | HMC305             |

| F1953 | 400 - 4000 | 0.50 / 31.5           | Parallel &<br>Serial | -1.3 | PE4302<br>DAT-31R5 |

#### **FEATURES**

- Glitch-Free<sup>™</sup>, < 0.6 dB transient overshoot

- Spurious Free Design

- 2.7 to 3.6 V supply

- Attenuation Error < 0.5 dB @ 2 GHz

- Low Insertion Loss < 1.4 dB @ 2 GHz</li>

- Excellent Linearity >+60 dBm IP3<sub>I</sub>

- Fast settling time, < 400 ns</li>

- Serial or Parallel Interface 31.5 dB Range

- Stable Integral Non-Linearity over temperature

- Low Power Consumption < 200 uA</li>

- Integrated DC blocking capacitors

- Drop-In replacement

- 4x4 mm Thin QFN 20 pin package

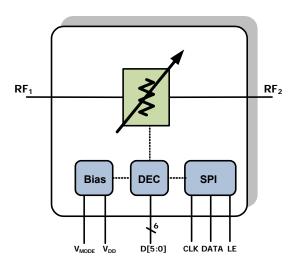

#### **DEVICE BLOCK DIAGRAM**

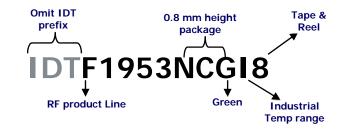

#### ORDERING INFORMATION

#### **ABSOLUTE MAXIMUM RATINGS**

-0.3 V to +4.0 V V<sub>DD</sub> to GND D[5:0], DATA, CLK, LE, VMODE -0.3 V to 3.6 V RF Input Power (RF1, RF2) calibration and testing +29 dBm RF Input Power (RF1, RF2) continuous RF operation +23 dBm  $\theta_{JA}$  (Junction – Ambient) +50 °C/W  $\theta_{\text{JC}}$  (Junction – Case) The Case is defined as the exposed paddle +3 °C/W Operating Temperature Range (Case Temperature)  $T_C = -40$  °C to +100 °C Maximum Junction Temperature 140 °C -65 °C to +150 °C Storage Temperature Range Lead Temperature (soldering, 10s) +260 °C

Stresses above those listed above may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD Caution**

This product features proprietary protection circuitry. However, it may be damaged if subjected to high energy ESD. Please use proper ESD precautions when handling to avoid damage or loss of performance.

#### **IDTF1953 Recommended Operating Conditions**

| Parameter         | Comment                | Sym              | Min | Тур | Max  | Units |

|-------------------|------------------------|------------------|-----|-----|------|-------|

| Supply Voltage    | Main Supply            | V <sub>DD</sub>  | 2.7 | 3.0 | 3.6  | V     |

| Temperature Range | Operating Range (Case) | Tc               | -40 |     | +100 | °C    |

| Frequency Range   | Operating Range        | F <sub>RF</sub>  | 400 |     | 4000 | MHz   |

| RF1 Impedance     | Single Ended           | Z <sub>RF1</sub> |     | 50  |      | Ω     |

| RF2 Impedance     | Single Ended           | Z <sub>RF2</sub> |     | 50  |      | Ω     |

# IDTF1953 SPECIFICATION (31.5 dB Range)

Specifications apply at  $V_{DD}$  = +3.0 V,  $f_{RF}$  = 2000 MHz,  $T_{C}$ = +25°C,  $V_{MODE}$  >  $V_{IH}$  (Serial Mode) EVkit losses are de-embedded (see p. 17)

| Parameter                                                        | Comment                                                                                                                            | Sym                                 | Min                 | Тур        | Max                 | Units |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------|------------|---------------------|-------|

| Logic Input High                                                 | CLK, DATA, LE, V <sub>MODE</sub> ,<br>D[5:0]                                                                                       | V <sub>IH</sub>                     | 0.7xV <sub>DD</sub> |            | V <sub>DD</sub>     | V     |

| Logic Input Low                                                  | CLK, DATA, LE, V <sub>MODE</sub> ,<br>D[5:0]                                                                                       | VIL                                 |                     |            | 0.3xV <sub>DD</sub> | V     |

| Logic Current                                                    | V <sub>MODE</sub> , D[5:0]                                                                                                         | lıн, lı∟                            | -5                  |            | +5                  | μA    |

| Logic Current                                                    | LE                                                                                                                                 | lıн, lı∟                            | -35                 |            | +35                 | μA    |

| Supply Current                                                   | Total V <sub>DD</sub> = 3V                                                                                                         | I <sub>DD</sub>                     |                     | 0.16       | 0.25 <sup>1</sup>   | mA    |

| RF1,RF2 Return Loss                                              | 20*log( <b>S</b> <sub>11</sub> ), 20*log( <b>S</b> <sub>22</sub> )                                                                 | S <sub>11</sub> ,S <sub>22</sub>    |                     | -23        |                     | dB    |

| Minimum Attenuation                                              | D[5:0] = [000000]                                                                                                                  | Amin                                |                     | 1.35       | 1.90                | dB    |

| Maximum Attenuation                                              | D[5:0] = [111111]                                                                                                                  | Amax                                | 32.0                | 32.4       |                     | dB    |

| Minimum Gain Step                                                | Least Significant Bit                                                                                                              | LSB                                 |                     | 0.50       |                     | dB    |

| Phase Delta                                                      | Phase change A <sub>MIN</sub> vs. A <sub>MAX</sub>                                                                                 | ΦΔ                                  |                     | 39         |                     | deg   |

| Differential ATTN Error                                          | Between adjacent steps                                                                                                             | DNL                                 |                     | 0.09       |                     | dB    |

| Integral ATTN Error                                              | Error vs. line (A <sub>MIN</sub> ref) to 13.5dB ATTN                                                                               | INL <sub>1</sub>                    |                     | 0.20       | 0.60                | dB    |

| Integral ATTN Error                                              | Error vs. line (A <sub>MIN</sub> ref) to 31.5dB ATTN                                                                               | INL <sub>2</sub>                    |                     | 0.47       | 0.75                | dB    |

|                                                                  | D[5:0] = [000000] = A <sub>MIN</sub>                                                                                               | IP3I <sub>1</sub>                   | +572                | +66        |                     |       |

| Input IP3                                                        | D[5:0] = [011111] = $A_{15.5}$<br>D[5:0] = [111111] = $A_{MAX}$<br>• $P_{IN}$ = +10 dBm per tone<br>• 50 MHz Tone Separation       | IP3I <sub>2</sub> IP3I <sub>3</sub> | +53<br>+53          | +60<br>+60 |                     | dBm   |

| 0.1 dB Compression Please note ABS MAX P <sub>IN</sub> on Page 2 | <ul> <li>D[5:0] = [000101] = A<sub>2.5</sub></li> <li>Baseline P<sub>IN</sub> = 20 dBm</li> </ul>                                  | P <sub>0.1</sub>                    |                     | 28.5       |                     | dBm   |

| Settling Time (parallel mode)                                    | <ul> <li>Start LE rising edge &gt; V<sub>IH</sub></li> <li>End +/-0.10 dB Pout settling</li> <li>15.5 – 16.0 transition</li> </ul> | T <sub>LSB</sub>                    |                     | 400        |                     | ns    |

| Serial Clock Speed                                               | SPI 3 wire bus                                                                                                                     | Fclk                                |                     | 10         | 50                  | MHz   |

| Serial Setup Time                                                | From rising edge of Vmode to rising edge of CLK for D5                                                                             | A                                   | 20                  |            |                     | ns    |

| Clock width                                                      | Clock high pulse width                                                                                                             | В                                   | 10                  |            |                     | ns    |

| LE setup time                                                    | From rising edge of CLK pulse for D0 to LE rising edge                                                                             | С                                   | 10                  |            |                     | ns    |

| LE pulse                                                         | LE minimum pulse width                                                                                                             | D                                   | 30                  |            |                     | ns    |

## **SPECIFICATION NOTES:**

- 1 Items in min/max columns in **bold italics** are Guaranteed by Test

- 2 All other Items in min/max columns are Guaranteed by Design Characterization

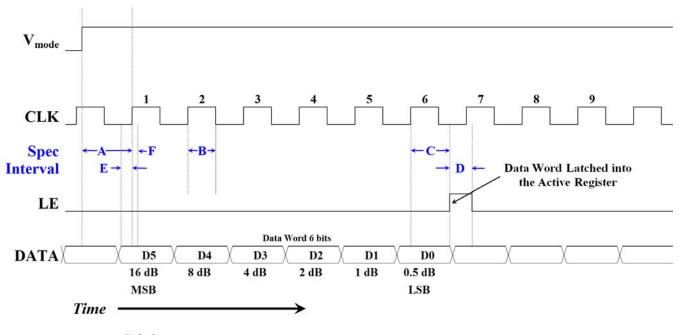

#### SERIAL CONTROL

Serial mode is selected when  $V_{\text{MODE}}$  is pulled high (>  $V_{\text{IH}}$ ), In serial mode the F1953 attenuation setting is programmed via the 3 wire bus (LE, CLK, DATA). In serial mode data is clocked in MSB first. Note the timing diagram below.

Note – The IDTF1953 includes a CLK inhibit feature designed to minimize sensitivity to CLK bus noise when the device is not being programmed. When Latch enable is high ( $> V_{IH}$ ), the CLK input is disabled and DATA will not be clocked into the shift register. It is recommended that LE be pulled high ( $> V_{IH}$ ) when the device is not being programmed.

#### **SERIAL REGISTER DEFAULT CONDITION**

If the device is powered up in Serial Mode, the device will default to whatever attenuation state is defined by the six parallel data input pins D5,D4,D3,D2,D1,D0 thus allowing *any attenuation setting* to be specified as the power up state.

#### SERIAL REGISTER TIMING DIAGRAM: (Note the Timing Spec Intervals in Blue)

#### **Polarity**

- 1 = Attenuator Switch IN

- 2 = Attenuator Switch OUT

#### **SERIAL REGISTER TIMING TABLE**

| Interval<br>Symbol | Description                                            | Min<br>Spec | Max<br>Spec | Units |

|--------------------|--------------------------------------------------------|-------------|-------------|-------|

| A                  | From rising edge of Vmode to rising edge of CLK for D5 | 20          |             | ns    |

| В                  | Clock high pulse width                                 | 10          |             | ns    |

| С                  | From rising edge of CLK pulse for D0 to LE rising edge | 10          |             | ns    |

| D                  | LE minimum pulse width                                 | 30          |             | ns    |

| E                  | Serial data set-up time before clock rising edge       | 10          |             | ns    |

| F                  | Serial data hold time after clock rising edge          | 10          |             | ns    |

#### PARALLEL CONTROL MODE

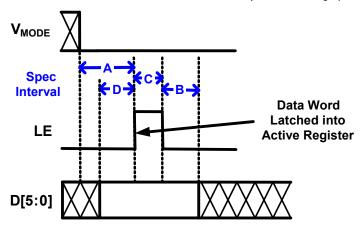

The user has the option of running in one of two parallel modes: Direct Parallel Mode or Latched Parallel Mode.

#### **DIRECT-PARALLEL MODE:**

Direct-parallel mode is selected when  $V_{\text{MODE}}$  (pin 13) is <  $V_{\text{IL}}$  and LE (pin 5) is >  $V_{\text{IH}}$ . In this mode the device will immediately react to any voltage changes to the parallel control pins [pins 1, 15, 16, 17, 19, 20]. Use direct-parallel mode for the fastest settling time.

#### **LATCHED-PARALLEL MODE:**

Latched-parallel mode is selected when V<sub>MODE</sub> (pin 13) is < V<sub>IL</sub> and LE (pin 5) is toggled from < V<sub>IL</sub> to > V<sub>IH</sub>

To utilize latched-parallel mode:

- Set LE < V<sub>IL</sub>

- Adjust pins [1, 15, 16, 17, 19, 20] to the desired attenuation setting. (Note the device will not react to these pins while LE < V<sub>IL</sub>.)

- Pull LE > V<sub>IH</sub>. The device will then transition to the attenuation settings reflected by these pins.

When the device is powered up In Latched Parallel Mode [ $V_{MODE} < V_{IL}$  and LE >  $V_{IH}$ ] the attenuation setting defaults to the state defined by the six parallel data pins [pins 1, 15, 16, 17, 19, 20]

LATCHED PARALLEL MODE TIMING DIAGRAM: (Note the Timing Spec Intervals in Blue)

#### **LATCHED PARALLEL MODE TIMING TABLE:**

| Interval<br>Symbol | Description                        | Min<br>Spec | Max<br>Spec | Units |

|--------------------|------------------------------------|-------------|-------------|-------|

| A                  | Serial to Parallel Mode Setup Time | 100         |             | ns    |

| В                  | Parallel Data Hold Time            | 10          |             | ns    |

| С                  | LE minimum pulse width             | 10          |             | ns    |

| D                  | Parallel Data Setup Time           | 10          |             | ns    |

## TYPICAL OPERATING PARAMETRIC CURVES (EVKit loss de-embedded, 3.0V unless otherwise noted)

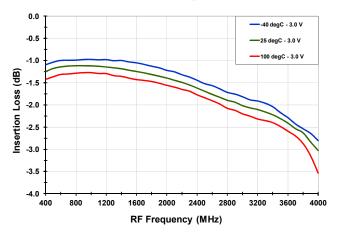

## Insertion Loss vs. Frequency [AMIN]

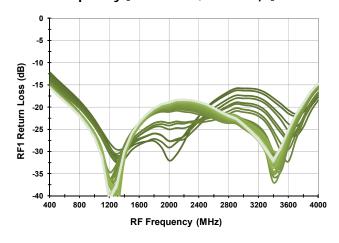

$S_{11}$  vs. Frequency [T<sub>CASE</sub> = +25C, 0.5 dB steps]

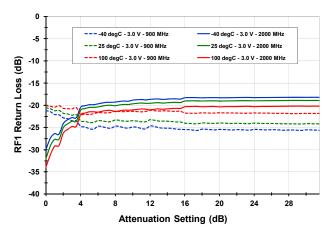

S<sub>11</sub> vs. Attenuation State

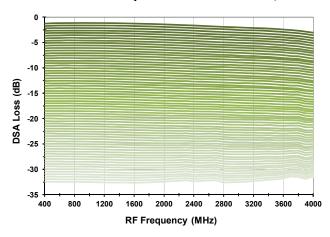

Attenuation vs. Freq [T<sub>CASE</sub> = +25C, 0.5 dB steps]

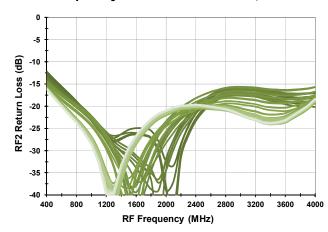

$S_{22}$  vs. Frequency [T<sub>CASE</sub> = +25C, 0.5 dB steps]

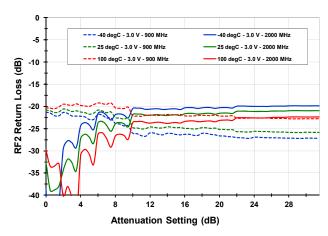

S<sub>22</sub> vs. Attenuation State

## **TOCs CONTINUED (-2-)**

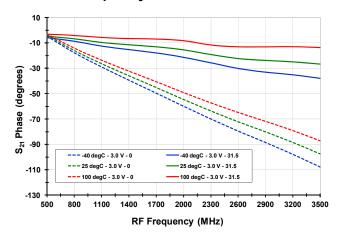

#### Phase vs. Frequency

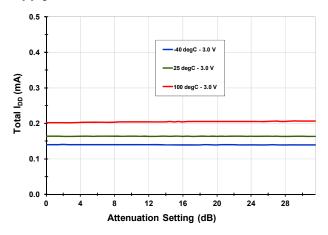

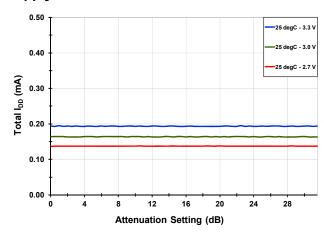

## Supply Current IDD [vs. Temp]

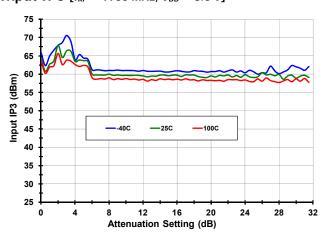

Input IP3 [ $f_{RF} = 1900 \text{ MHz}, V_{DD} = 3.0 \text{ V}$ ]

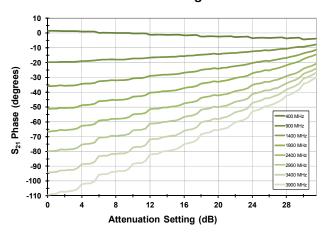

# Phase vs. Attenuation Setting

## Supply Current IDD [vs. VDD]

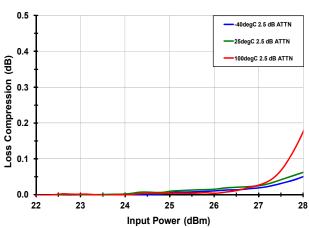

# Compression [ $f_{RF} = 2000 \text{ MHz}$ , ATTN = 2.5 dB]

## **TOCs CONTINUED (-3-)**

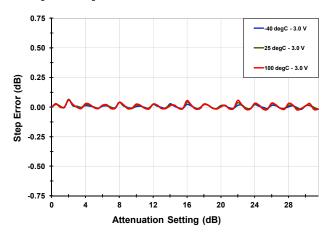

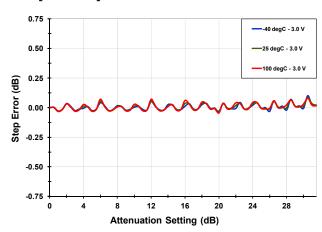

## **DNL** [400 MHz]

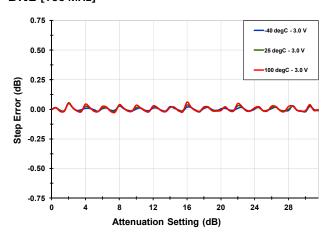

## **DNL** [900 MHz]

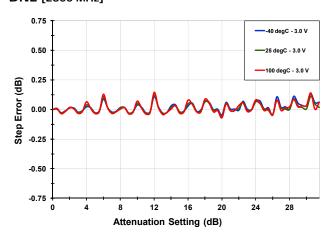

## **DNL** [2800 MHz]

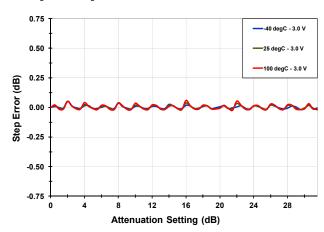

## **DNL** [700 MHz]

## **DNL** [1900 MHz]

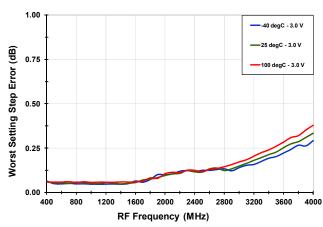

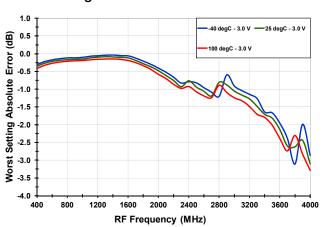

# **Worst Setting DNL**

## **TOCs CONTINUED (-4-)**

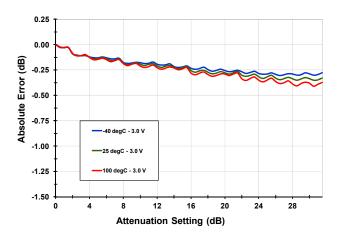

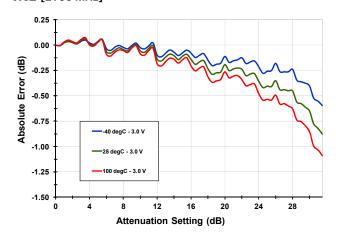

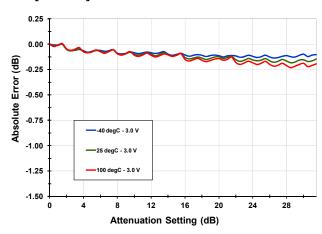

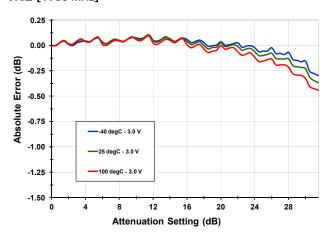

## **INL** [400 MHz]

#### **INL** [900 MHz]

#### INL [2900 MHz]

## **INL** [700 MHz]

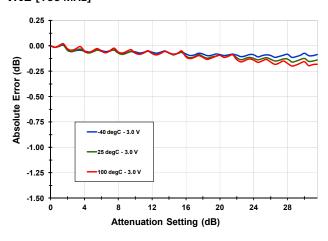

#### **INL** [1900 MHz]

## **Worst Setting INL**

#### TOCS CONTINUED (-5-) $[f_{RF} = 900 \text{ MHz}]$

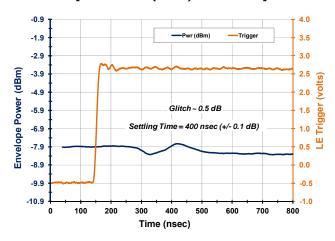

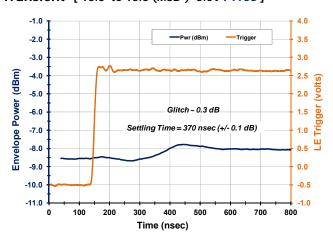

#### Transient [ 15.5 to 16.0 (MSB+) 3.3V F1953]

The graphs ABOVE show the transient overshoot and settling time performance for both the MSB+ and MSB- cases for the F1953. The device settles very quickly ( $\sim$ 400) ns with benign ( $\sim$ 0.5) dB overshoot.

#### Transient [ 16.0 to 15.5 (MSB-) 5.0V F1953]

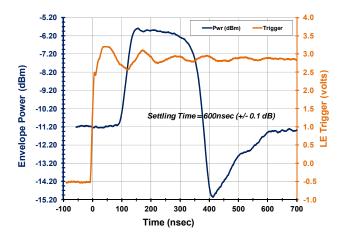

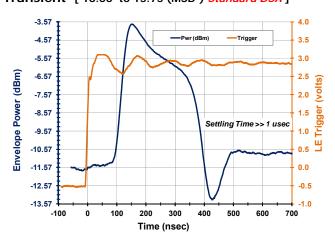

The graphs *BELOW* show the transient overshoot and settling time performance for a popular competing DSA. *Note the overshoot/undershoot excursion of almost 10 dB* and the very long settling time. For the MSB- case, the settling time is off the scale, ~ 3 µsec.

## Transient [ 15.75 to 16.00 (MSB+) Standard DSA ]

## Transient [ 16.00 to 15.75 (MSB-) Standard DSA ]

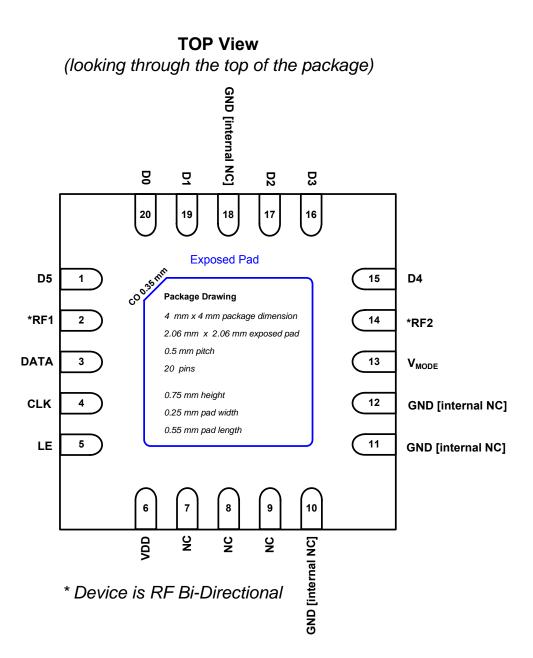

## **PIN DIAGRAM**

## **PACKAGE DRAWINGS**

The package outline drawings are appended at the end of this document and are accessible from the link below. The package information is the most current data available.

$\underline{www.idt.com/document/psc/20-qfn-package-outline-drawing-40-x-40-x-075-mm-body-05mm-pitch-epad-206-x-206-mm-ncq20p1}$

# **PIN DESCRIPTIONS**

| Pin# | Pin Name          | Pin Function                                                                                                       |

|------|-------------------|--------------------------------------------------------------------------------------------------------------------|

| 1    | D5                | 16 dB Attenuation Control Bit. Pull high for 16 dB ATTN.                                                           |

| 2    | RF1               | Device RF input or output (bi-directional). Internally DC blocked.                                                 |

| 3    | DATA              | Serial interface Data Input.                                                                                       |

| 4    | CLK               | Serial interface Clock Input.                                                                                      |

| 5    | LE                | Serial interface Latch Enable Input. Internal pullup (100K ohm).                                                   |

| 6    | VDD               | Power supply pin.                                                                                                  |

| 7    | NC                | No internal connection. These pins can be left unconnected, voltage applied, or connected to ground (recommended). |

| 8    | NC                | No internal connection. These pins can be left unconnected, voltage applied, or connected to ground (recommended). |

| 9    | NC                | No internal connection. These pins can be left unconnected, voltage applied, or connected to ground (recommended). |

| 10   | NC                | No internal connection. These pins can be left unconnected, voltage applied, or connected to ground (recommended). |

| 11   | NC                | No internal connection. These pins can be left unconnected, voltage applied, or connected to ground (recommended). |

| 12   | NC                | No internal connection. These pins can be left unconnected, voltage applied, or connected to ground (recommended). |

| 13   | VMODE             | Pull high for serial mode. Ground for Parallel control mode.                                                       |

| 14   | RF2               | Device RF input or output (bi-directional). Internally DC blocked.                                                 |

| 15   | D4                | 8 dB Attenuation Control Bit. Pull high for 8 dB ATTN.                                                             |

| 16   | D3                | 4 dB Attenuation Control Bit. Pull high for 4 dB ATTN.                                                             |

| 17   | D2                | 2 dB Attenuation Control Bit. Pull high for 2 dB ATTN.                                                             |

| 18   | NC                | No internal connection. These pins can be left unconnected, voltage applied, or connected to ground (recommended). |

| 19   | D1                | 1 dB Attenuation Control Bit. Pull high for 1 dB ATTN.                                                             |

| 20   | D0                | 0.5 dB Attenuation Control Bit. Pull high for 0.5 dB ATTN.                                                         |

| EP   | Exposed<br>Paddle | Connect to Ground with multiple vias for good thermal relief.                                                      |

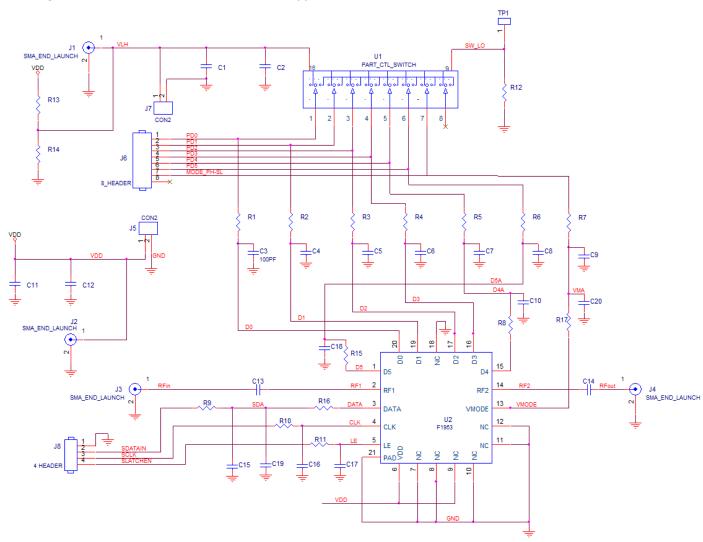

## **EVKIT SCHEMATIC**

The diagram below describes the recommended applications / EVkit circuit:

# **EVKIT OPERATION (Email: <u>RFsupport@IDT.com</u>** to request an EVkit and Controller)

The picture and graphic below describe how to operate the EVkit

# **EVKIT BOM (F1953)**

F1953 BOM Rev 01 PCB Rev 01 11/15/2012

| Item# | Value                   | Size  | Desc                             | Mfr. Part #         | Mfr.            | Part Reference  | Qty |

|-------|-------------------------|-------|----------------------------------|---------------------|-----------------|-----------------|-----|

| 1     | 10nF                    | 0402  | CAP CER 10000PF 16V 10% X7R 0402 | GRM155R71C103KA01D  | MURATA          | C2,12           | 2   |

| 2     | 0.1uF                   | 0402  | CAP CER 0.1UF 16V 10% X7R 0402   | GRM155R71C104KA88D  | MURATA          | C1,11           | 2   |

| 3     | Header 2 Pin            | TH 2  | CONN HEADER VERT SGL 2POS GOLD   | 961102-6404-AR      | 3M              | J5,7            | 2   |

| 4     | Header 4 Pin            | TH 4  | CONN HEADER VERT SGL 4POS GOLD   | 961104-6404-AR      | 3M              | J8              | 1   |

| 5     | Header 8 Pin            | TH 8  | CONN HEADER VERT SGL 8POS GOLD   | 961108-6404-AR      | 3M              | J6              | 1   |

| 6     | SMA_END_LAUNCH          | .062  | SMA_END_LAUNCH (Small)           | 142-0711-821        | Emerson Johnson | J2,3,4          | 3   |

| 7     | 0                       | 0402  | RES 0.0 OHM 1/10W 0402 SMD       | ERJ-2GE0R00X        | Panasonic       | R1-7,12,C13,C14 | 10  |

| 8     | 3K                      | 0402  | RES 3.00K OHM 1/10W 1% 0402 SMD  | ERJ-2RKF3001X       | Panasonic       | R9-11           | 3   |

| 9     | 10K                     | 0402  | RES 10K OHM 1/10W 1% 0402 SMD    | ERJ-2RKF1002X       | Panasonic       | R8,15-17        | 4   |

| 10    | 100K                    | 0402  | RES 100KOHM 1/10W 1% 0402 SMD    | ERJ-2RKF104X        | Panasonic       | R13             | 1   |

| 11    | 267K                    | 0402  | RES 267K OHM 1/10W 1% 0402 SMD   | ERJ-2RKF2673X       | Panasonic       | R14             | 1   |

| 12    | DIPSwitch               | TH 10 | 8 POSITION DIP SWITCH            | KAT1108E            | E-Switch        | U1              | 1   |

| 13    | Digital Step Attenuator |       | F1953Z                           | F1953Z              | IDT             | U2              | 1   |

| 14    | РСВ                     |       | PCB Rev 01                       | F1953S Evkit Rev 01 | SBC             |                 | 1   |

| 15    | 100pF                   | 0402  | CAP CER 100PF 16V 10% X7R 0402   | GRM155R71C103KA01D  | MURATA          | C3-10,15-20     | DNP |

| 16    | SMA_END_LAUNCH          | .062  | SMA_END_LAUNCH (Small)           | 142-0711-821        | Emerson Johnson | J1              | DNP |

Total 33

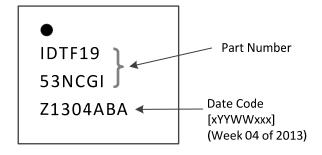

# **TOPMARKINGS**

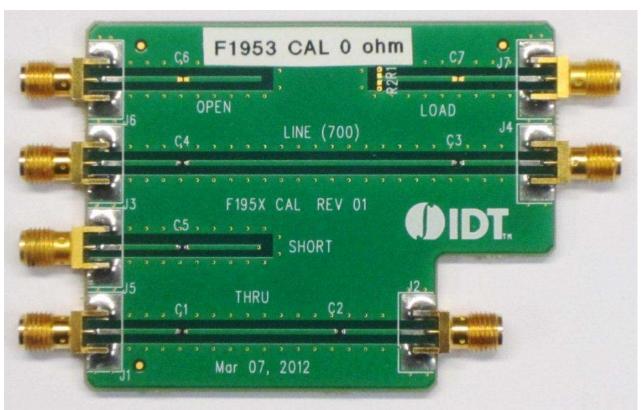

## **EVKIT THROUGH-REFLECT-LINE (TRL) CALIBRATION**

The "Through-Reflect-Line" (TRL) method [1] is used to de-embed the evaluation board losses from the S-parameter measurements of the F1953. This method requires the use of three standards: a through, a reflection, and a line. The TRL method has the advantage over other calibration methods in that it requires only one of these three standards to be well defined.

The TRL through which is used for the F1953 TRL calibration was constructed identically to the evaluation board, minus the DUT and its corresponding length. Therefore, the through corresponds to a precise zero length connection between the input and output reference planes of the DUT. This through satisfies the requirement of the TRL method that one of the three standards be precisely specified.

The TRL reflection standard used is constructed identically to the input and output lines of the evaluation board, with a short placed at the reference plane of the DUT. In accordance with the TRL method's requirements, the actual magnitude and phase were not accurately specified, but the phase was known to within 90 degrees and the TRL reflection standard has a magnitude close to one.

The TRL line standard is identical to the TRL through, but with an additional length of 0.8 inches (2 cm). This satisfies the TRL method's requirement that the TRL be a different length than the TRL through, that it have the same impedance and propagation constant as the through, and that the phase difference between the through and the line be between 20 degrees and 160 degrees. The difference in length yields a phase difference of approximately 20 degrees at 500 MHz, and a phase difference of 160 degrees at 4 GHz.

Standards used for F195x TRL calibration

F1953 evaluation circuit

Engen, G.F.; Hoer, C.A.; "Thru-Reflect-Line: An Improved Technique for Calibrating the Dual Six-Port Automatic Network Analyzer," **IEEE Transactions on Microwave Theory and Techniques**, Volume: 27 Issue:12, pp. 987 – 993, Dec 1979.

# **Revision History**

| Revision Date     | Description of Change                                                                                                                   |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| September 5, 2018 | Updated document template.                                                                                                              |

|                   | <ul> <li>Updated Package Outline Drawings section. Now references the latest official drawing. No changes to<br/>dimensions.</li> </ul> |

|                   | Added disclaimer paragraph.                                                                                                             |

| December 3, 2015  | Corrected logic voltage.                                                                                                                |

|                   | Add recommended operating conditions table.                                                                                             |

|                   | <ul> <li>Updated serial timing figure.</li> </ul>                                                                                       |

|                   | <ul> <li>Updated pin description table.</li> </ul>                                                                                      |

|                   | <ul> <li>Updated evaluation board schematic.</li> </ul>                                                                                 |

| April 10, 2014    | Correct top marking drawing.                                                                                                            |

| March 30, 2013    | Initial release.                                                                                                                        |

**Corporate Headquarters**

6024 Silver Creek Valley Road San Jose, CA 95138 www.IDT.com Sales

1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.IDT.com/go/sales **Tech Support**

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its affiliated companies (herein referred to as "IDT") reserve the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit <a href="www.idt.com/go/glossary">www.idt.com/go/glossary</a>. All contents of this document are copyright of Integrated Device Technology, Inc. All rights reserved.

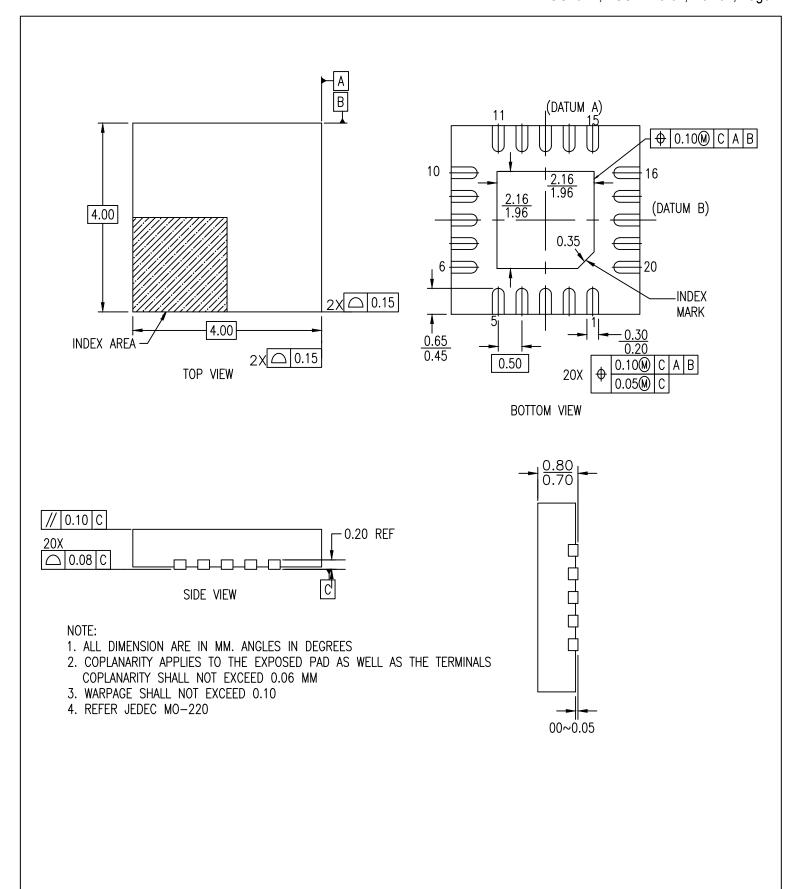

# 20-QFN, Package Outline Drawing

4.0 x 4.0 x 0.75 mm Body, 0.5mm Pitch, Epad 2.06 x 2.06 mm NCG20P1, PSC-4445-01, Rev 01, Page 1

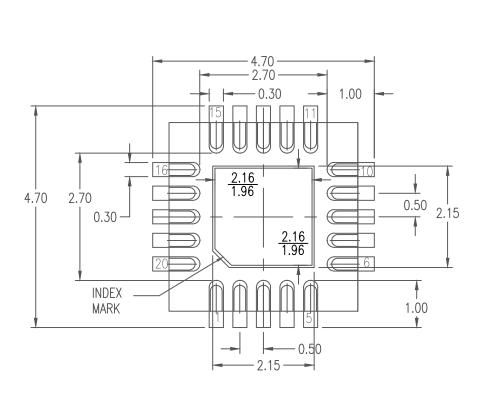

# 20-QFN, Package Outline Drawing

4.0 x 4.0 x 0.75 mm Body, 0.5mm Pitch, Epad 2.06 x 2.06 mm NCG20P1, PSC-4445-01, Rev 01, Page 2

RECOMMENDED LAND PATTERN DIMENSION

## NOTE:

- 1. ALL DIMENSION ARE IN MM. ANGLES IN DEGREES

- 2. TOP DOWN VIEW AS VIEWED ON PCB

- 3. LAND PATTERN RECOMMENDATION PER IPC-7351B GENERIC REQUIREMENT FOR SURFACE MPOUNT DESIGN AND LAND PATTERN

| Package Revision History |         |                 |  |  |

|--------------------------|---------|-----------------|--|--|

| Date Created             | Rev No. | Description     |  |  |

| Sept 12, 2017            | Rev 01  | Correct Title   |  |  |

| Sept 11, 2017            | Rev 00  | Initial Release |  |  |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Renesas Electronics:

F1953NCGI8 F1953NCGI F1953EVBI F1953EVS