## **General Description**

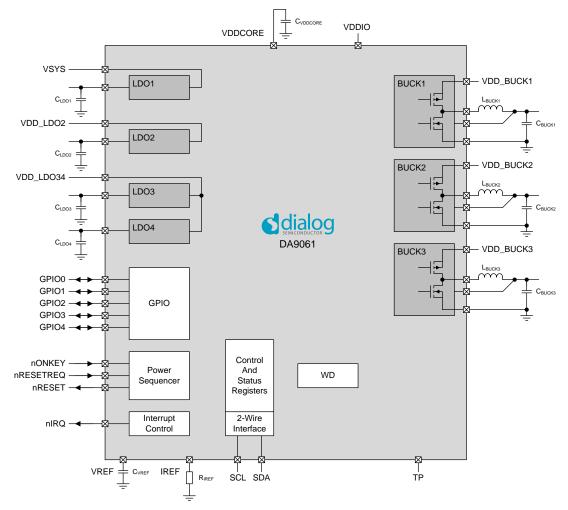

DA9061 is a power management integrated circuit (PMIC) optimized for supplying systems with single- and dual-core processors, I/O, DDR memory, and peripherals. It targets mobile device, medical equipment, IVI systems, and FPGA based applications.

DA9061 features three buck converters providing a total current of 6 A. High efficiency is achieved over a wide load range with PFM mode available for low power or sleep modes. All power switches are integrated, therefore, external Schottky diodes are not required. Furthermore, low-profile inductors can be used with DA9061. The four LDO regulators with programmable output voltage provide up to 300 mA.

Dynamic voltage control (DVC) allows dynamic control of DA9061 supply voltages according to the operating point of the system. It is controlled by writing directly to the registers using the I<sup>2</sup>C compatible 2-wire interface or the GPIOs.

DA9061 features a programmable power sequencer that handles start-up and shutdown sequences. Power mode transitions can be triggered with software control, GPIOs, or with the on-key. Several types of on-key presses can be detected to trigger different power mode transitions.

An integrated watchdog timer monitors the system.

Five GPIOs are able to perform system functions, including: keypad supervision, application buck, and timing-controlled external regulators/power switches or other ICs.

DA9061 is also available as an automotive AEC-Q100 Grade 2 version.

## **Key Features**

- Input voltage 2.8 V to 5.5 V

- Three buck converters with dynamic voltage control:

- Buck1: 0.3 V to 1.57 V, 2.5 A

- □ Buck2: 0.8 V to 3.34 V, 2 A

- □ Buck3: 0.53 V to 1.8 V, 1.5 A

- 3 MHz switching frequency (enables low profile inductors)

- Four LDO regulators:

- □ LDO1: 0.9 V to 3.6 V, 100 mA

- LDO2, LDO3, LDO4: 0.9 V to 3.6 V, 300 mA

# **Applications**

- Single and dual core application processors such as ARM Cortex or i.MX6 series

- Entry-level FPGAs

- Programmable power mode sequencer

- System supply and junction temperature monitoring

- Watchdog timer

- Five GPIOs

- -40 °C to +125 °C junction temperature range

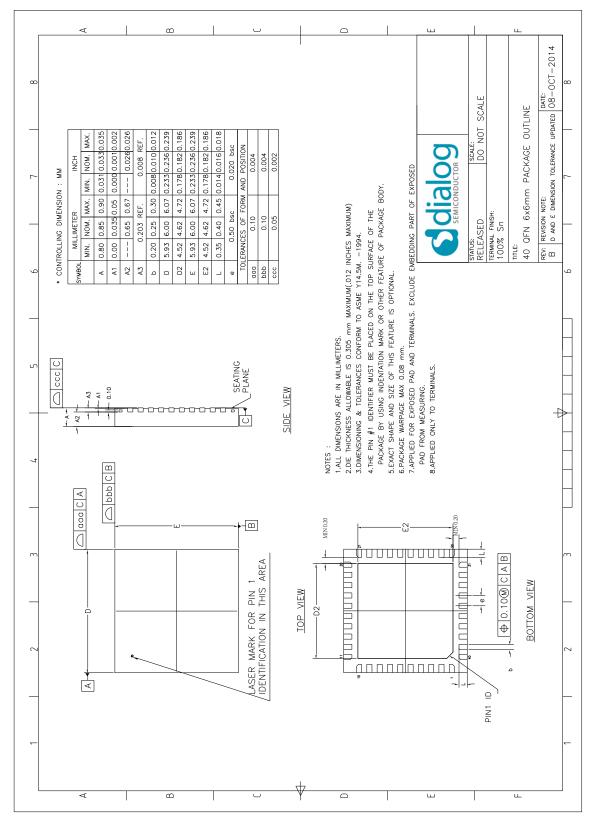

- 40-pin QFN, 6 mm × 6 mm package, 0.5 mm pitch

- Automotive AEC-Q100 Grade 2 version available

- Automotive infotainment

- Portable industrial and medical devices

- e-book readers

# **Block Diagram**

Figure 1: DA9061 Block Diagram

# PMIC for Applications Requiring up to 6 A

## **Contents**

| Ge  | neral   | Description    | on                                     | 1  |

|-----|---------|----------------|----------------------------------------|----|

| Ke  | y Feat  | ures           |                                        | 1  |

| Ар  | plicati | ions           |                                        | 1  |

| Blo | ock Dia | agram          |                                        | 2  |

| Co  | ntents  | -<br>5         |                                        | 3  |

| 1   | Pack    | age Infor      | mation                                 | 6  |

| •   | 1.1     | •              |                                        |    |

|     | 1.2     |                | Outline Drawing                        |    |

| 2   | Requ    | -              | rview                                  |    |

| -   | •       |                | mum Ratings                            |    |

| 4   |         |                | d Operating Conditions                 |    |

|     | 4.1     |                | Characteristics                        |    |

|     |         | 4.1.1          | Power Derating Curves                  | 12 |

| 5   | Elect   | rical Cha      | racteristics                           | 13 |

|     | 5.1     | Digital I/0    | D                                      | 13 |

|     | 5.2     | Watchdo        | g                                      | 14 |

|     | 5.3     | 2-Wire Ir      | nterface                               | 14 |

|     | 5.4     | LDOs           |                                        | 16 |

|     |         | 5.4.1          | LDO1                                   | 16 |

|     |         | 5.4.2          | LDO2, LDO3, LDO4                       | 17 |

|     |         | 5.4.3          | LDOCORE                                | 18 |

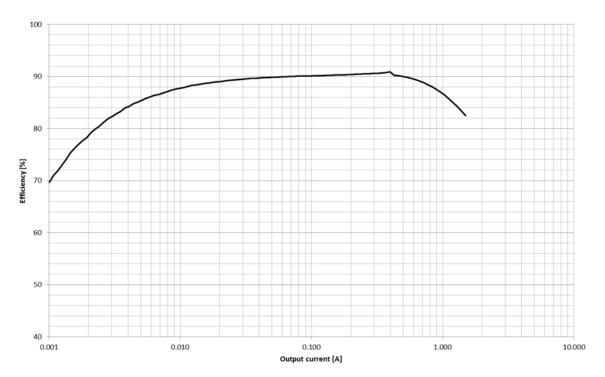

|     | 5.5     | Buck Co        | nverters                               | 19 |

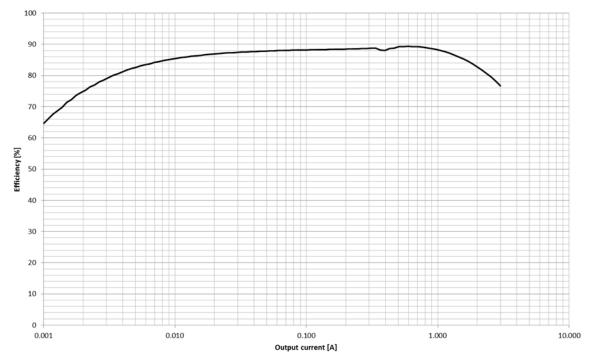

|     |         | 5.5.1          | Buck1                                  |    |

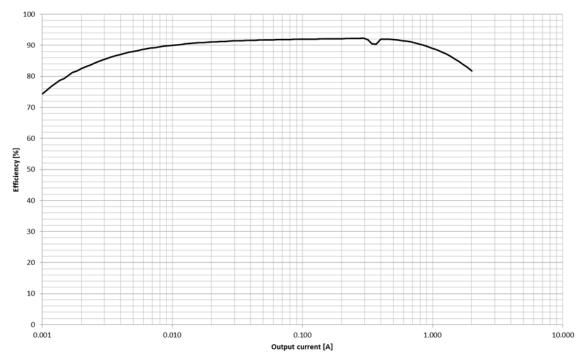

|     |         | 5.5.2          | Buck2                                  |    |

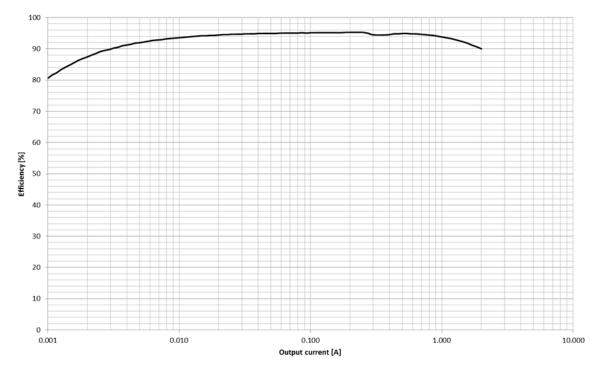

|     |         | 5.5.3          | Buck3                                  |    |

|     | 5.6     |                | Dscillator                             |    |

|     | 5.7     | •              | Supply Voltage Supervision             |    |

|     | 5.8     |                | Temperature Supervision                |    |

|     | 5.9     | Current (      | Consumption                            | 26 |

| 6   | Туріс   | al Chara       | cteristics                             | 27 |

| 7   | Func    | tional De      | scription                              | 29 |

|     | 7.1     | Control S      | Signals                                |    |

|     |         | 7.1.1          | nONKEY                                 |    |

|     |         | 7.1.2          | nRESETREQ                              |    |

|     |         | 7.1.3          | nRESET                                 |    |

|     |         | 7.1.4          | nIRQ                                   |    |

|     | 7.2     |                | iterface                               |    |

|     |         | 7.2.1          | Register Map Paging                    |    |

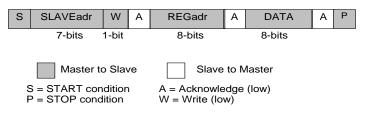

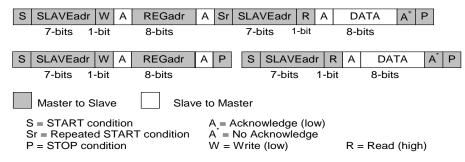

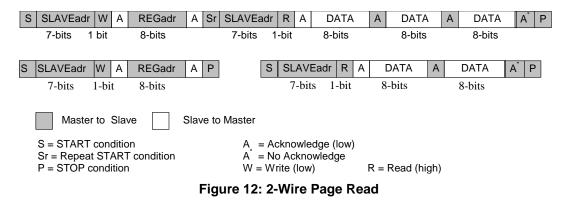

|     | 70      | 7.2.2          | Details of the 2-Wire Protocol         |    |

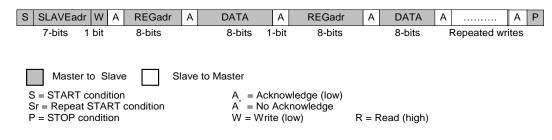

|     | 7.3     | GPIOs<br>7.3.1 |                                        |    |

|     |         | 7.3.1          | GPI Functionality<br>GPO Functionality |    |

|     |         | 7.3.2          | Alternate Functions                    |    |

|     |         | 7.0.0          |                                        | 55 |

|     |       | 7.3.4      | GPIO Forwarding                              | 36 |

|-----|-------|------------|----------------------------------------------|----|

|     | 7.4   | Dynamic    | Voltage Control                              | 36 |

|     | 7.5   | Regulato   | or Voltage A and B Selection                 | 36 |

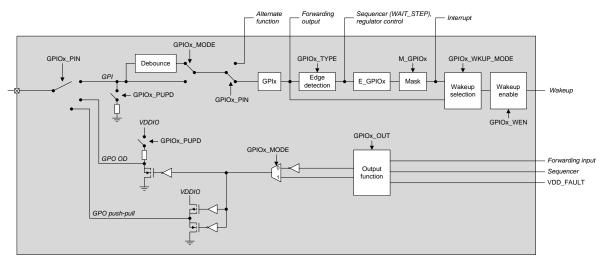

|     | 7.6   | LDOs       |                                              | 37 |

|     |       | 7.6.1      | Control                                      | 37 |

|     |       | 7.6.2      | Current Limit                                | 37 |

|     |       | 7.6.3      | Output Pull-Down                             | 37 |

|     | 7.7   | Switching  | g Regulators                                 | 38 |

|     |       | 7.7.1      | Control                                      | 38 |

|     |       | 7.7.2      | Output Voltage Slewing                       | 38 |

|     |       | 7.7.3      | Soft-Start                                   | 38 |

|     |       | 7.7.4      | Active Discharge                             | 38 |

|     |       | 7.7.5      | Peak Current Limit                           | 38 |

|     |       | 7.7.6      | Operating Mode                               | 39 |

|     |       | 7.7.7      | Half-Current Mode                            | 39 |

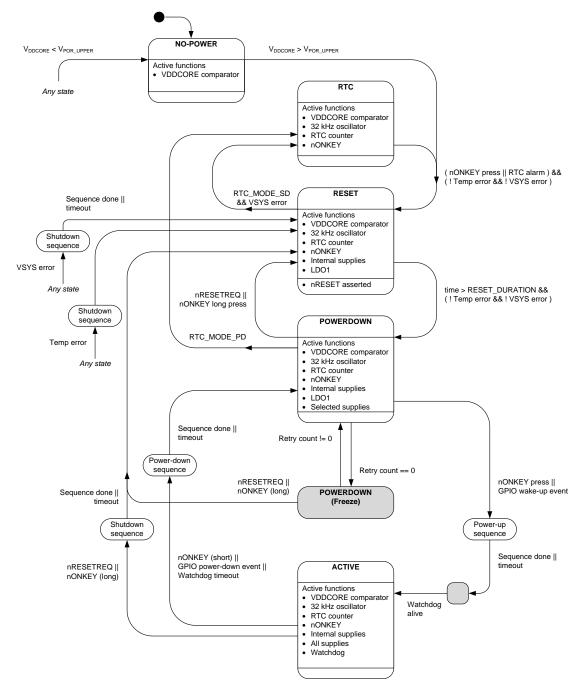

|     | 7.8   | Power M    | lodes                                        | 40 |

|     |       | 7.8.1      | NO-POWER Mode                                | 40 |

|     |       | 7.8.2      | RESET Mode                                   | 41 |

|     |       | 7.8.3      | POWERDOWN Mode                               | 42 |

|     |       | 7.8.4      | Power-Up, Power-Down, and Shutdown Sequences | 43 |

|     |       | 7.8.5      | ACTIVE Mode                                  | 43 |

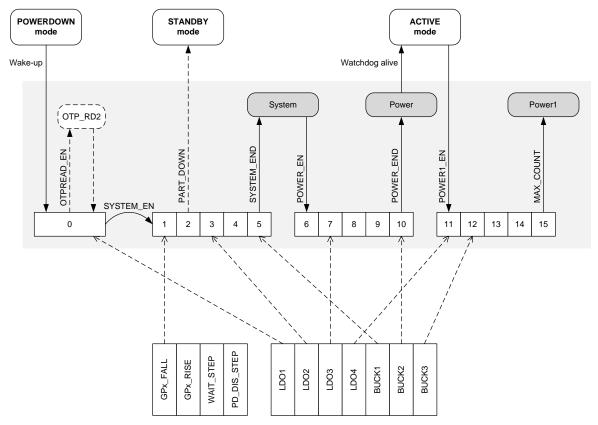

|     | 7.9   | Power S    | upply Sequencer                              | 44 |

|     |       | 7.9.1      | Programmable Slot Delays                     | 45 |

|     |       | 7.9.2      | Sub-Sequences                                | 45 |

|     |       | 7.9.3      | Regulator Control                            | 45 |

|     |       | 7.9.4      | GPO Control                                  | 46 |

|     |       | 7.9.5      | Wait Step                                    | 47 |

|     |       | 7.9.6      | Power-Down Disable                           |    |

|     | 7.10  |            | Temperature Supervision                      |    |

|     | 7.11  | •          | Supply Voltage Supervision                   |    |

|     |       |            | Oscillator                                   |    |

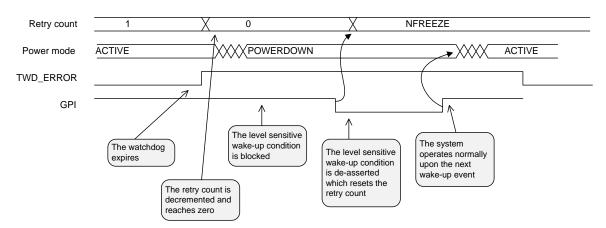

|     | 7.13  | Watchdo    | )g                                           | 48 |

| 8   | Regis | ster Map.  |                                              | 49 |

|     | 8.1   | Register   | Page Control                                 | 49 |

|     | 8.2   | Overviev   | V                                            | 49 |

| 9   | Appli | cation In  | formation                                    | 52 |

|     | 9.1   | Compon     | ent Selection                                | 52 |

|     |       | 9.1.1      | Resistors                                    | 52 |

|     |       | 9.1.2      | Capacitors                                   | 52 |

|     |       | 9.1.3      | Inductors                                    | 53 |

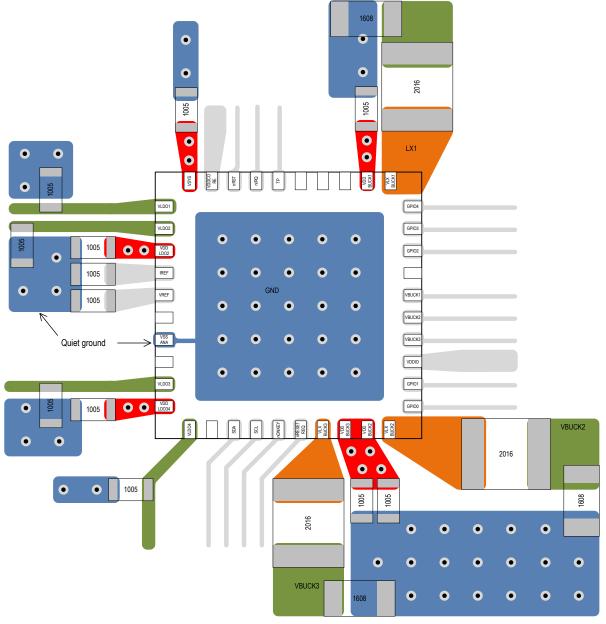

|     | 9.2   | PCB Lay    | /out                                         | 54 |

|     |       | 9.2.1      | General Recommendations                      | 54 |

|     |       | 9.2.2      | LDOs and Switched Mode Supplies              | 55 |

|     |       | 9.2.3      | Optimizing Thermal Performance               | 55 |

| 10  | Orde  | ring Infor | mation                                       | 56 |

|     |       | -          | ing                                          |    |

| • • |       |            | J                                            |    |

|   | - | ta | - |   | - | - | ۰. |

|---|---|----|---|---|---|---|----|

|   |   |    |   | n | 0 |   | г  |

| _ | • |    |   |   | • | • | •  |

# PMIC for Applications Requiring up to 6 A

| Appendix | x A Regis | ter Descriptions                     | 57 |

|----------|-----------|--------------------------------------|----|

| A.1      | PAGE 0    |                                      | 57 |

|          | A.1.1     | Page Control                         | 57 |

|          | A.1.2     | Power Manager Control and Monitoring | 57 |

|          | A.1.3     | IRQ Events                           | 58 |

|          | A.1.4     | IRQ Masks                            | 59 |

|          | A.1.5     | System Control                       | 60 |

|          | A.1.6     | GPIO Control                         | 62 |

|          | A.1.7     | Power Supply Control                 | 65 |

| A.2      | PAGE 1    |                                      | 70 |

|          | A.2.1     | Power Sequencer                      | 70 |

|          | A.2.2     | Power Supply Control                 | 74 |

| A.3      | PAGE 2    |                                      | 78 |

|          | A.3.1     | Customer Trim and Configuration      | 78 |

|          | A.3.2     | Customer Device Specific             | 81 |

| A.4      | PAGE 3    |                                      | 84 |

|          | A.4.1     | Device Identification                | 84 |

# **1** Package Information

## 1.1 Pin List

## Table 1: Pin Description

| Pin No. | Pin Name  | Type<br>Table 2 | Description                                |

|---------|-----------|-----------------|--------------------------------------------|

| Paddle  | GND       | GND             | Power grounds of the bucks, digital ground |

| 1       | VLDO1     | AO              | LDO1 output voltage                        |

| 2       | VLDO2     | AO              | LDO2 output voltage                        |

| 3       | VDD_LDO2  | PS              | LDO2 supply                                |

| 4       | IREF      | AO              | Reference current                          |

| 5       | VREF      | AIO             | Reference voltage                          |

| 6       | NC        |                 | Connect to GND                             |

| 7       | VSS_ANA   | GND             | Analog ground                              |

| 8       | NC        |                 | Connect to GND                             |

| 9       | VLDO3     | AO              | LDO3 output voltage                        |

| 10      | VDD_LDO34 | PS              | LDO3 and LDO4 supply                       |

| 11      | VLDO4     | AO              | LDO4 output voltage                        |

| 12      | NC        |                 | Do not use. Leave floating                 |

| 13      | SDA       | DIO             | Data signal of the 2-wire interface        |

| 14      | SCL       | DI              | Clock signal of the 2-wire interface       |

| 15      | nONKEY    | DI              | Input for power-on key                     |

| 16      | nRESETREQ | DI              | Reset request input                        |

| 17      | VLX_BUCK3 | AO              | Switching node of Buck3                    |

| 18      | VDD_BUCK3 | PS              | Buck3 supply                               |

| 19      | VDD_BUCK2 | PS              | Buck2 supply                               |

| 20      | VLX_BUCK2 | AO              | Switching node of Buck2                    |

| 21      | GPIO0     | DIO             | General purpose I/O, WDKICK                |

| 22      | GPIO1     | DIO             | General purpose I/O                        |

| 23      | VDDIO     | PS              | IO supply                                  |

| 24      | VBUCK3    | AI              | Voltage feedback of Buck3                  |

| 25      | VBUCK2    | AI              | Voltage feedback of Buck2                  |

| 26      | VBUCK1    | AI              | Voltage feedback of Buck1                  |

| 27      | NC        |                 | Do not use. Leave floating                 |

| 28      | GPIO2     | DIO             | General purpose I/O, PWR_EN                |

| 29      | GPIO3     | DIO             | General purpose I/O                        |

| 30      | GPIO4     | DIO             | General purpose I/O, SYS_EN                |

| 31      | VLX_BUCK1 | AO              | Switching node of Buck1                    |

| 32      | VDD_BUCK1 | PS              | Buck1 supply                               |

| 33      | NC        |                 | Connect to GND                             |

#### Datasheet

## **Revision 3.8**

# PMIC for Applications Requiring up to 6 A

| Pin No. | Pin Name | Type<br>Table 2 | Description                        |

|---------|----------|-----------------|------------------------------------|

| 34      | NC       |                 | Do not use. Leave floating         |

| 35      | NC       |                 | Do not use. Leave floating         |

| 36      | ТР       | DIO             | Test pin                           |

| 37      | nIRQ     | DO              | Interrupt signal to host processor |

| 38      | nRESET   | DO              | Reset output                       |

| 39      | VDDCORE  | AO              | Internal supply                    |

| 40      | VSYS     | PS              | System supply, LDO1 supply         |

## Table 2: Pin Type Definition

| Pin type | Description          | Pin type | Description         |

|----------|----------------------|----------|---------------------|

| DI       | Digital Input        | AI       | Analog Input        |

| DO       | Digital Output       | AO       | Analog Output       |

| DIO      | Digital Input/Output | AIO      | Analog Input/Output |

| PS       | Power Supply         | GND      | Ground connection   |

## PMIC for Applications Requiring up to 6 A

## 1.2 Package Outline Drawing

## 2 **Regulator Overview**

#### Table 3: Regulators

| Regulator | Supplied<br>Pins | Supplied<br>Voltage<br>(V) | Supplied<br>Maximum<br>Current<br>(mA) | External<br>Component  | Notes                                                                                                                                                                                |

|-----------|------------------|----------------------------|----------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Buck1     | VBUCK1           | 0.3 to<br>1.57             | 2500<br>Note 1                         | 1.0 μH,<br>44 μF/88 μF | <ul> <li>GPIO and host interface-controlled<br/>DVC with variable slew rate (10 mV in<br/>[0.5, 1.0, 2.0, 4.0] µs)</li> <li>10 mV steps</li> <li>&lt; 0.7 V PFM mode only</li> </ul> |

| Buck2     | VBUCK2           | 0.8 to<br>3.34             | 2000<br>Note 2                         | 1.0 μH,<br>44 μF/88 μF | <ul> <li>GPIO and host interface-controlled<br/>DVC with variable slew rate (10 mV in<br/>[0.5, 1.0, 2.0, 4.0] µs)</li> <li>20 mV steps</li> </ul>                                   |

| Buck3     | VBUCK3           | 0.53 to<br>1.8             | 1500<br>Note 2                         | 1.0 μH,<br>44 μF       | <ul> <li>GPIO and host interface-controlled<br/>DVC with variable slew rate (10 mV in<br/>[0.5, 1.0, 2.0, 4.0] µs)</li> <li>10 mV steps</li> <li>&lt; 0.7 V PFM mode only</li> </ul> |

| LDO1      | VLDO1            | 0.9 to 3.6                 | 100                                    | 1.0 μF                 | <ul> <li>Configurable as always-on</li> <li>50 mV steps</li> <li>Internally supplied from VSYS</li> </ul>                                                                            |

| LDO2      | VLDO2            | 0.9 to 3.6                 | 300                                    | 2.2 µF                 | <ul><li>Low noise LDO</li><li>50 mV steps</li></ul>                                                                                                                                  |

| LDO3      | VLDO3            | 0.9 to 3.6                 | 300                                    | 2.2 µF                 | <ul><li>Low noise LDO</li><li>50 mV steps</li><li>Common supply with LDO4</li></ul>                                                                                                  |

| LDO4      | VLDO4            | 0.9 to 3.6                 | 300                                    | 2.2 µF                 | <ul> <li>Low noise LDO</li> <li>50 mV steps</li> <li>Common supply with LDO3</li> </ul>                                                                                              |

**Note 1** For short durations, to meet peak current requirements, I<sub>OUT</sub> for Buck1 can be operated at up to 20 % higher than the specified maximum operating condition. The part should not be operated in this mode for extended periods and is not guaranteed for continuous operation.

**Note 2** For short durations, to meet peak current requirements, I<sub>OUT</sub> for Buck2 and Buck3 can be operated at up to 10 % higher than the specified maximum operating condition. The part should not be operated in this mode for extended periods and is not guaranteed for continuous operation.

## 3 Absolute Maximum Ratings

Table 4 lists the absolute maximum ratings of the device. Exceeding these ratings may cause permanent damage to the device. Device functionality is only guaranteed under the conditions listed in Sections 4 and 5. Operating the device in conditions exceeding those listed in Sections 4 and 5, but compliant with the absolute maximum ratings listed in Table 4, for extended periods of time may affect device reliability.

| Parameter            | Symbol           | Note           | Min  | Тур | Max                              | Unit |

|----------------------|------------------|----------------|------|-----|----------------------------------|------|

| Storage temperature  |                  |                | -65  |     | +150                             | °C   |

| Junction temperature | TJ               |                | -40  |     | +150<br>Note 1                   | °C   |

| Supply voltage       | V <sub>SYS</sub> |                | -0.3 |     | 6.0                              | V    |

|                      | VBBAT            |                | -0.3 |     | 3.2                              | V    |

|                      | Buck VDD         |                | -0.3 |     | V <sub>SYS</sub> + 0.4<br>Note 2 | V    |

|                      | VTP              |                | -0.3 |     | 8.0<br>Note 3                    | V    |

|                      | All other pins   |                | -0.3 |     | V <sub>SYS</sub> + 0.3<br>Note 2 | V    |

| ESD protection HBM   | Vesd_hbm         |                | 2000 |     |                                  | V    |

| ESD protection CDM   | Vesd_cdm         | Corner pins    | 750  |     |                                  | V    |

|                      |                  | All other pins | 500  |     |                                  |      |

Note 1 See Sections 5.8 and 7.10 for more detail.

Note 2 Voltage must not exceed 5.5 V.

**Note 3** Voltage on TP pin should be 0 V except during in-circuit programming.

# 4 Recommended Operating Conditions

## Table 5: Recommended Operating Conditions

| Parameter                      | Symbol            | Note   | Min  | Тур | Max  | Unit |

|--------------------------------|-------------------|--------|------|-----|------|------|

| Operating junction temperature | TJ                |        | -40  |     | +125 | °C   |

| Main supply                    | V <sub>SYS</sub>  |        | 0    |     | 5.5  | V    |

| Backup supply                  | VBBAT             |        | 0    |     | 3.15 | V    |

| I/O supply                     | V <sub>DDIO</sub> | Note 1 | 1.2  |     | 3.6  | V    |

| TP programming supply          | VTP_PROG          | Note 2 | 7.25 | 7.5 | 7.75 | V    |

Note 1  $V_{DDIO}$  must not exceed  $V_{SYS}$ .

**Note 2** Voltage on TP pin should be 0 V except during in-circuit programming.

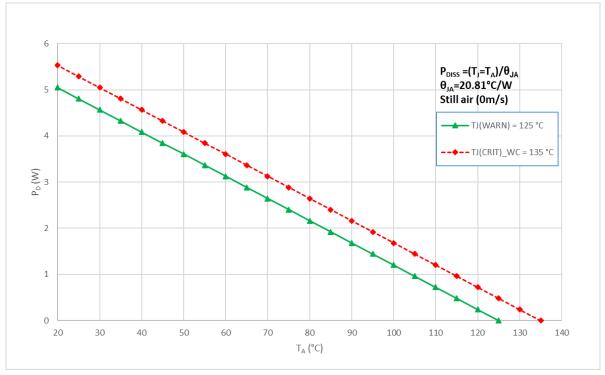

## 4.1 Thermal Characteristics

#### **Table 6: QFN Package Ratings**

| Parameter                              | Symbol            | Note                                                      | Тур   | Unit |

|----------------------------------------|-------------------|-----------------------------------------------------------|-------|------|

| Thermal resistance junction to ambient | R <sub>θ_JA</sub> | Note 1                                                    | 20.81 | °C/W |

| Thermal resistance junction to Board   | R <sub>θ_JB</sub> | Note 1                                                    | 5.9   | °C/W |

| Thermal resistance junction to case    | R <sub>θ_JC</sub> | Note 1                                                    | 18.72 | °C/W |

| Maximum power dissipation<br>Note 1    | PDISS             | Derating factor above T <sub>A</sub> = 70 °C: 48.05 mW/°C | 3120  | mW   |

**Note 1** Obtained from package thermal simulation, 76 mm x 114 mm x 1.6 mm (JEDEC), 6-layer board, 70 μm thick copper top/bottom layers, 35 μm thick copper inside layers, 49 x 0.2 mm thermal vias beneath the device, natural convection (still air).

## 4.1.1 **Power Derating Curves**

#### **Table 7: Typical Temperatures**

|                   | T <sub>A</sub> = 70 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C |

|-------------------|------------------------|------------------------|-------------------------|

| Twarn             | P <sub>D</sub> =3.12 W | P <sub>D</sub> =1.92 W | P <sub>D</sub> =0.96 W  |

| T <sub>CRIT</sub> | P <sub>D</sub> =2.64 W | P <sub>D</sub> =2.40 W | P <sub>D</sub> =1.44 W  |

## **5** Electrical Characteristics

## 5.1 Digital I/O

Unless otherwise noted, the following is valid for  $T_J = -40$  °C to +125 °C,  $V_{SYS} = 2.8$  V to 5.5 V.

#### Table 8: Digital I/O Electrical Characteristics

| Parameter                                                | Symbol          | Test Conditions                                                         | Min                     | Тур | Max                     | Unit |

|----------------------------------------------------------|-----------------|-------------------------------------------------------------------------|-------------------------|-----|-------------------------|------|

| Input high voltage                                       | Vih             | VDDCORE mode                                                            | 1.0                     |     | Vsys                    | V    |

| (GPI0 to GPI4,<br>nRESETREQ)                             |                 | VDDIO mode                                                              | 0.7 * V <sub>DDIO</sub> |     | V <sub>SYS</sub>        |      |

| Input low voltage                                        | VIL             | VDDCORE mode                                                            | -0.3                    |     | 0.4                     | V    |

| (GPI0 to GPI4,<br>nRESETREQ)                             |                 | VDDIO mode<br>V <sub>DDIO</sub> ≥ 1.5 V                                 | -0.3                    |     | 0.3 * Vddio             | -    |

| Input high voltage<br>(nONKEY)                           | VIH             |                                                                         | 1.0                     |     | V <sub>SYS</sub>        | V    |

| Input low voltage<br>(nONKEY)                            | VIL             |                                                                         | -0.3                    |     | 0.4                     | V    |

| Input high voltage                                       | VIH             | VDDCORE mode                                                            | 1.0                     |     | V <sub>SYS</sub>        | V    |

| (SCL, SDA)                                               |                 | VDDIO mode                                                              | 0.7 * V <sub>DDIO</sub> |     | Vsys                    |      |

| Input low voltage                                        | VIL             | VDDCORE mode                                                            | -0.3                    |     | 0.4                     | V    |

| (SCL, SDA)                                               |                 | VDDIO mode<br>V <sub>DDIO</sub> ≥ 1.5 V                                 | -0.3                    |     | 0.3 * V <sub>DDIO</sub> | -    |

| Output high voltage<br>(GPIO0 to GPIO4,<br>nRESET, nIRQ) | Vон             | lou⊤ = 1 mA<br>Push-pull mode                                           | 0.7 * V <sub>DDIO</sub> |     |                         | V    |

| Output low voltage<br>(GPIO0 to GPIO4,<br>nRESET, nIRQ)  | V <sub>OL</sub> | I <sub>OUT</sub> = 1 mA                                                 |                         |     | 0.3                     | V    |

| Output low voltage                                       | V <sub>OL</sub> | I <sub>OUT</sub> = 8 mA                                                 |                         |     | 0.4                     | V    |

| (SDA)                                                    |                 | Iout = 3 mA                                                             |                         |     | 0.4                     |      |

| Source current<br>capability<br>(GPIO0 to GPIO4)         | Іон             | V <sub>OUT</sub> = 0.7 * V <sub>DDIO</sub><br>V <sub>DDIO</sub> ≥ 1.8 V |                         | -1  |                         | mA   |

| Sink current capability (GPIO0 to GPIO4)                 | Iol             | Vout = 0.3 V                                                            |                         | 1   |                         | mA   |

| Input capacitance<br>(SCL, SDA)                          | CIN             |                                                                         |                         |     | 10                      | pF   |

| Pull-down resistance<br>(GPIO0 to GPIO4)                 | R <sub>PD</sub> |                                                                         | 50                      | 100 | 250                     | kΩ   |

| Pull-up resistance                                       | Rpu             | V <sub>DDIO</sub> = 1.5 V                                               | 60                      | 180 | 310                     | kΩ   |

| (GPIO0 to GPIO4)                                         |                 | V <sub>DDIO</sub> = 1.8 V                                               | 45                      | 120 | 190                     | 1    |

|                                                          |                 | V <sub>DDIO</sub> = 3.3 V                                               | 20                      | 40  | 60                      | 1    |

## **PMIC for Applications Requiring up to 6 A**

## 5.2 Watchdog

Unless otherwise noted, the following is valid for  $T_J$  = -40 °C to +125 °C,  $V_{SYS}$  = 2.8 V to 5.5 V.

| Table 9: Watchdog Electrical Characteristics |  |

|----------------------------------------------|--|

|----------------------------------------------|--|

| Parameter                     | Symbol     | Test conditions            | Min | Тур | Max | Unit |

|-------------------------------|------------|----------------------------|-----|-----|-----|------|

| Minimum watchdog time         | twdmin     | Internal 25 kHz oscillator |     |     | 200 | ms   |

| Maximum watchdog time         | twdmax     | Internal 25 kHz oscillator | 2.5 |     |     | s    |

| Minimum assert time of WDKICK | twdkickmin |                            |     | 150 |     | μs   |

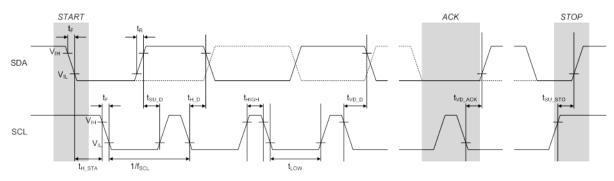

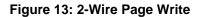

## 5.3 2-Wire Interface

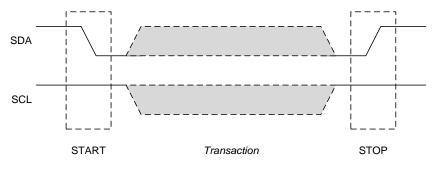

### Figure 4: 2-Wire Interface Timing

Unless otherwise noted, the following is valid for  $T_J = -40$  °C to +125 °C,  $V_{SYS} = 2.8$  V to 5.5 V.

| Parameter                      | Symbol           | Test Conditions                     | Min | Тур | Max  | Unit |

|--------------------------------|------------------|-------------------------------------|-----|-----|------|------|

| Bus free time<br>STOP to START | t <sub>BUF</sub> |                                     | 0.5 |     |      | μs   |

| Bus line capacitive load       | Св               |                                     |     |     | 150  | pF   |

| Standard/Fast/Fast+ Mode       |                  |                                     |     |     |      |      |

| SCL clock frequency            | fsc∟             | V <sub>DDIO</sub> ≥ 1.5 V<br>Note 1 | 0   |     | 1.0  | MHz  |

| Start condition set-up time    | tsu_sta          |                                     | 260 |     |      | ns   |

| Start condition hold time      | th_sta           |                                     | 260 |     |      | ns   |

| SCL low time                   | tw_cL            |                                     | 500 |     |      | ns   |

| SCL high time                  | tw_сн            |                                     | 260 |     |      | ns   |

| 2-wire SCL and SDA rise time   | t <sub>R</sub>   | (input requirement)                 |     |     | 1000 | ns   |

| 2-wire SCL and SDA fall time   | tF               | (input requirement)                 |     |     | 300  | ns   |

| Data set-up time               | tsu_D            |                                     | 50  |     |      | ns   |

| Data hold-time                 | t <sub>H_D</sub> |                                     | 0   |     |      | ns   |

| Data valid time                | t∨D_D            |                                     |     |     | 450  | ns   |

| Data valid time acknowledge    | tvd_аск          |                                     |     |     | 450  | ns   |

**Revision 3.8**

Datasheet

# PMIC for Applications Requiring up to 6 A

| Parameter                    | Symbol            | Test Conditions                  | Min | Тур | Max | Unit |

|------------------------------|-------------------|----------------------------------|-----|-----|-----|------|

| Stop condition set-up time   | tsu_sto           |                                  | 260 |     |     | ns   |

| High Speed Mode              |                   | ÷                                |     |     |     |      |

| SCL clock frequency          | fsc∟              | V <sub>DDIO</sub> ≥ 1.8 V Note 1 | 0   |     | 3.4 | MHz  |

| Start condition set-up time  | tsu_sta           |                                  | 160 |     |     | ns   |

| Start condition hold time    | th_sta            |                                  | 160 |     |     | ns   |

| SCL low time                 | tw_cL             |                                  | 160 |     |     | ns   |

| SCL high time                | t <sub>W_CH</sub> |                                  | 60  |     |     | ns   |

| 2-wire SCL and SDA rise time | t <sub>R</sub>    | (input requirement)              |     |     | 160 | ns   |

| 2-wire SCL and SDA fall time | t⊧                | (input requirement)              |     |     | 160 | ns   |

| Data set-up time             | tsu_D             |                                  | 10  |     |     | ns   |

| Data hold-time               | t <sub>H_D</sub>  |                                  | 0   |     |     | ns   |

| Stop condition set-up time   | tsu_sто           |                                  | 160 |     |     | ns   |

Note 1 Minimum clock frequency is 10 kHz if TWOWIRE\_TO is enabled.

## **PMIC for Applications Requiring up to 6 A**

### 5.4 LDOs

### 5.4.1 LDO1

Unless otherwise noted, the following is valid for  $T_J = -40$  °C to +125 °C.

#### **Table 11: LDO1 Electrical Characteristics**

| Parameter                        | Symbol               | Test Conditions                                                                                                                   | Min  | Тур                     | Max  | Unit   |

|----------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|-------------------------|------|--------|

| Input voltage                    | Vdd                  | V <sub>DD</sub> = V <sub>SYS</sub><br>(Internally connected)                                                                      | 2.8  |                         | 5.5  | V      |

| Maximum output<br>current        | IOUT_MAX             |                                                                                                                                   | 100  |                         |      | mA     |

| Output voltage                   | Vldo                 | Programmable in 50 mV steps                                                                                                       | 0.9  |                         | 3.6  | V      |

| Output accuracy                  |                      | lout = lout_MAX including static line/load regulation                                                                             | -3%  |                         | +3%  |        |

| Stabilization capacitor          | Соит                 | Including voltage and<br>temperature coefficient                                                                                  | -55% | 1.0                     | +35% | μF     |

| Output capacitor ESR             | RCOUT_ESR            | f > 1 MHz<br>Including wiring parasitics                                                                                          | 0    |                         | 300  | mΩ     |

| Short circuit current            | I <sub>SHORT</sub>   |                                                                                                                                   |      | 200                     |      | mA     |

| Dropout voltage                  | Vdropout             | VLDO = 3.3 V<br>Iout = Iout_max                                                                                                   |      | 100                     | 150  | mV     |

| Static line regulation           | Vs_line              | $V_{DD} = 3.0 \text{ V to } 5.5 \text{ V}$<br>Iout = Iout_MAX                                                                     |      | 5                       | 20   | mV     |

| Static load regulation           | Vs_load              | IOUT = 1 mA to IOUT_MAX                                                                                                           |      | 5                       | 20   | mV     |

| Line transient response          | Vtr_line             | $\label{eq:VDD} \begin{array}{l} V_{DD} = 3.0 \ V \ to \ 3.6 \ V \\ I_{OUT} = I_{OUT\_MAX} \\ t_R = t_F = 10 \ \mu s \end{array}$ |      | 5                       | 20   | mV     |

| Load transient response          | Vtr_load             |                                                                                                                                   |      | 30                      | 50   | mV     |

| Power supply rejection ratio     | PSRR                 | $V_{DD} = 3.6 V$ $V_{DD} - V_{LDO} \ge 0.6 V$ $I_{OUT} = I_{OUT\_MAX} / 2$ $f = f_{VDD\_LDO}$                                     |      |                         |      |        |

|                                  |                      | f = 10 Hz to 10 kHz                                                                                                               | 40   | 60                      |      | dB     |

| Output noise                     | N                    | V <sub>DD</sub> = 3.6 V, V <sub>LDO</sub> = 2.8 V                                                                                 |      | 70                      |      | μV rms |

|                                  |                      | $I_{OUT} = 5 \text{ mA to } I_{OUT\_MAX}$<br>f = 10 Hz to 100 kHz<br>$T_A = 25 \text{ °C}$                                        |      |                         |      |        |

| Quiescent current in ON mode     | IQ_ON                | $T_A = 25  {}^{\circ}\text{C}$                                                                                                    |      | 9 <b>+</b><br>0.9% Іоит |      | μA     |

| Quiescent current in SLEEP mode  | I <sub>Q_SLEEP</sub> | T <sub>A</sub> = 25 °C                                                                                                            |      | 1.5 +<br>1.6% Іоυт      |      | μA     |

| Quiescent current in<br>OFF mode | IQ_OFF               | V <sub>LDO</sub> < 0.5 V<br>T <sub>A</sub> = 25 °C                                                                                |      |                         | 1    | μA     |

| Parameter                           | Symbol | Test Conditions                                    | Min | Тур | Мах | Unit |

|-------------------------------------|--------|----------------------------------------------------|-----|-----|-----|------|

| Turn-on time                        | ton    | 10 % to 90 %                                       |     |     | 350 | μs   |

|                                     |        | SLEEP mode                                         |     |     | 450 |      |

| Turn-off time                       | toff   | 90 % to 10%<br>Pull-down enabled                   |     |     | 1   | ms   |

| Pull-down resistance in<br>OFF mode | Roff   | VLDO = 0.5 V<br>Can be disabled via<br>LDO1_PD_DIS |     | 50  |     | Ω    |

### 5.4.2 LDO2, LDO3, LDO4

Unless otherwise noted, the following is valid for  $T_{\rm J}$  = -40 °C to +125 °C.

#### Table 12: LDO2, LDO3, LDO4 Electrical Characteristics

| Parameter                    | Symbol              | Test Conditions                                                                                       | Min            | Тур            | Max  | Unit |

|------------------------------|---------------------|-------------------------------------------------------------------------------------------------------|----------------|----------------|------|------|

| Input voltage                | V <sub>DD</sub>     | V <sub>DD</sub> = V <sub>SYS</sub>                                                                    | 2.8            |                | 5.5  | V    |

|                              |                     | Supplied from buck converter                                                                          | 1.5            |                |      |      |

| Maximum output current       | IOUT_MAX            | V <sub>DD</sub> ≥ 1.8 V<br>(Iout = Iout_max/3, V <sub>DD</sub> < 1.8 V)                               | 300            |                |      | mA   |

| Output voltage               | V <sub>LDO</sub>    | Programmable in 50 mV steps                                                                           | 0.9            |                | 3.6  | V    |

| Output accuracy              |                     | lout = lout_MAX<br>Including static line/load<br>regulation                                           | -3%            |                | +3%  |      |

| Stabilization capacitor      | C <sub>OUT</sub>    | Including voltage and<br>temperature coefficient                                                      | -55%           | 2.2            | +35% | μF   |

| Output capacitor<br>ESR      | RCOUT_ESR           | f > 1 MHz<br>Including wiring parasitics                                                              | 0              |                | 300  | mΩ   |

| Short circuit current        | I <sub>SHORT</sub>  |                                                                                                       |                | 600            |      | mA   |

| Dropout voltage              | Vdropout            | Iout= Iout_max<br>(Vdd < 1.8 V, Iout = Iout_max/3)<br>Note 1                                          |                | 100            | 150  | mV   |

| Static line regulation       | V <sub>S_LINE</sub> | V <sub>DD</sub> = 3.0 V to 5.5 V<br>lout = lout_max                                                   |                | 5              | 20   | mV   |

| Static load regulation       | Vs_load             | IOUT = 1 mA to IOUT_MAX                                                                               |                | 5              | 20   | mV   |

| Line transient response      | Vtr_line            | $V_{DD} = 3.0 \text{ V to } 3.6 \text{ V}$ $I_{OUT} = I_{OUT\_MAX}$ $t_{R} = t_{F} = 10  \mu\text{s}$ |                | 5              | 20   | mV   |

| Load transient response      | Vtr_load            |                                                                                                       |                | 30             | 50   | mV   |

| Power supply rejection ratio | PSRR                | $V_{DD} = 3.6 V$ $V_{DD} - V_{LDO} \ge 0.6 V$ $I_{OUT} = I_{OUT\_MAX}/2$ $f = f_{VDD\_LDO}$           |                |                |      |      |

|                              |                     | f = 10 Hz to 1 kHz<br>f = 1 kHz to 10 kHz<br>f = 10 kHz to 100 kHz                                    | 70<br>60<br>40 | 80<br>70<br>50 |      | dB   |

| Parameter                           | Symbol          | Test Conditions                                                                                               | Min | Тур               | Max | Unit   |

|-------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------|-----|-------------------|-----|--------|

| Output noise                        | N               | $V_{DD} = 3.6 V$<br>$V_{LDO} = 2.8 V$<br>$I_{OUT} = 5 \text{ mA to } I_{OUT\_MAX}$<br>f = 10  Hz to  100  kHz |     | 50                |     | μV rms |

| Quiescent current in<br>ON mode     | Iq_on           | T <sub>A</sub> = 25 °C                                                                                        |     | 9 +<br>0.34% Іоит |     | μA     |

| Quiescent current in SLEEP mode     | $I_{Q_{SLEEP}}$ | T <sub>A</sub> = 25 °C                                                                                        |     | 2 +<br>0.7% Іолт  |     | μA     |

| Quiescent current in<br>OFF mode    | IQ_OFF          | V <sub>LDO</sub> < 0.5 V<br>T <sub>A</sub> = 25 °C                                                            |     |                   | 1   | μA     |

| Turn-on time                        | Ton             | 10 % to 90 %                                                                                                  |     |                   | 200 | μs     |

|                                     |                 | SLEEP mode                                                                                                    |     |                   | 300 |        |

| Turn-off time                       | Toff            | 90 % to 10 %<br>Pull-down enabled                                                                             |     |                   | 1   | ms     |

| Pull-down resistance<br>in OFF mode | Roff            | V <sub>LDO</sub> = 0.5 V<br>Can be disabled via<br>LDO <x>_PD_DIS</x>                                         |     | 50                |     | Ω      |

**Note 1** At  $V_{DD} = 1.8$  V, the dropout voltage at  $I_{OUT\_MAX}$  increases by 70%.

### 5.4.3 LDOCORE

Unless otherwise noted, the following is valid for  $T_J = -40$  °C to +125 °C,  $V_{SYS} = 2.8$  V to 5.5 V.

| Table 13: LDOCORE Electrical Characteristics |

|----------------------------------------------|

|----------------------------------------------|

| Parameter               | Symbol    | Test Conditions                                     | Min  | Тур | Max  | Unit |

|-------------------------|-----------|-----------------------------------------------------|------|-----|------|------|

| Output voltage          | Vddcore   | Note 1                                              | 2.45 | 2.5 | 2.55 | V    |

|                         |           | RESET mode                                          |      | 2.2 |      | V    |

| Stabilization capacitor | Соит      | Including voltage<br>and temperature<br>coefficient | -55% | 2.2 | +35% | μF   |

| Output capacitor ESR    | RCOUT_ESR | f > 1 MHz<br>including wiring<br>parasitics         | 0    |     | 300  | mΩ   |

| Dropout voltage         | Vdropout  | Note 2                                              |      | 50  | 100  | mV   |

**Note 1** Setting  $V_{DD_{FAULT_LOWER}} \ge 2.65$  V avoids LDOCORE dropout, see Section 5.7.

Note 2 The LDOCORE supply, VSYS, must be maintained above VDDCORE + VDROPOUT

## NOTE

LDOCORE is only used to supply internal circuits.

## **PMIC for Applications Requiring up to 6 A**

### 5.5 Buck Converters

#### 5.5.1 Buck1

Unless otherwise noted, the following is valid for  $T_J = -40$  °C to +125 °C.

#### Table 14: Buck1 Electrical Characteristics

| $\begin{tabular}{ c c c c c } \hline \begin{tabular}{ c c c c } \hline \begin{tabular}{ c c c c c c } \hline \begin{tabular}{ c c c c c c c } \hline \begin{tabular}{ c c c c c c c c } \hline \begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Parameter                 | Symbol               | Test Conditions                                          | Min  | Тур    | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------|----------------------------------------------------------|------|--------|------|------|

| $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Input voltage             | V <sub>DD</sub>      | V <sub>DD</sub> = V <sub>SYS</sub>                       | 2.8  |        | 5.5  | V    |

| $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Output capacitor          | Соит                 | voltage and temperature                                  | E0%/ | 2 * 22 | 120% | μF   |

| $ \begin{array}{ c c c c c } \hline \begin{tabular}{ c c c } \hline \end{tabular}{c c c c c } \hline \end{tabular}{c c c c c c c } \hline \end{tabular}{c c c c c c c c } \hline \end{tabular}{c c c c c c c c c c } \hline \end{tabular}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |                      | voltage and temperature                                  | -50% | 2 * 47 | +30% |      |

| $ \begin{array}{ c c c c c c } \hline   1 > 100 \ kHz \\ Including wiring parasitics &   1 &   1 &   1 \\ \hline   1ncluding wiring parasitics &   1 &   1 &   1 \\ \hline   1ncluding current and temperature dependence &   1 &   55 &   100 & mode \\ \hline \\ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Output capacitor ESR      | RCOUT_ESR            | f > 100 kHz                                              |      | 15     | 50   | mΩ   |

| $\begin{tabular}{ c                                   $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |                      | f > 100 kHz                                              |      | 7.5    | 25   |      |

| PWM ModeProgrammable in 10 mV steps0.31.57VOutput voltageVBUCK_ACCProgrammable in 10 mV steps0.31.57VOutput voltage accuracyVBUCK_ACCVDD = 4.2 V, VBUCK = 1.03 V<br>Excluding static line/load<br>regulation and voltage ripple<br>TA = 25 °C-1%+1%Transient load regulationVTR_LOADVDD = 3.6 V, VBUCK = 1.15 V<br>lour = 200 mA to 1000 mA<br>di/dt = 3 A/µs<br>L = 1 µH-3%+3%Transient line regulationVTR_LINEVDD = 3.6 V, VBUCK = 1.15 V<br>lour = 200 mA to 1000 mA<br>di/dt = 3 A/µs<br>L = 1 µH3045mVOutput currentIourVTR_LINEVDD = 3.0 V to 3.6 V<br>lour = 500 mA<br>tR = tr = 10 µs0.23mVOutput currentIourHalf-current mode<br>controlled in BUCK <x>_ILIM7002200mACurrent limitILIMHalf-current mode<br/>controlled in BUCK<x>_ILIM14004400mA</x></x>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Inductor value            | Lвиск                |                                                          | 0.7  | 1.0    | 1.3  | μH   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Inductor resistance       | RL_DCR               |                                                          |      | 55     | 100  | mΩ   |

| Note 1Note 1Image: Constraint of the second          | PWM Mode                  |                      |                                                          | •    |        |      |      |

| Excluding static line/load<br>regulation and voltage ripple<br>T_A = 25 °CExcluding static line/load<br>regulation and voltage ripple<br>Note 2-3%+3%Transient load regulation $V_{TR\_LOAD}$ $V_{DR\_LOAD}$ $V_{DDC} = 3.6 V, V_{BUCK} = 1.15 V \\IoUT = 200 mA to 1000 mA do 1000 mA do//dt = 3 A/\mus L = 1 \muH3045mNTransient line regulationV_{TR\_LINE}V_{DD} = 3.0 V to 3.6 V \\IOUT = 500 mA to 1000 mA t_R = t_F = 10 \mu s0.2345mNOutput currentIoUTFull-current mode1250mACurrent limitILIMHalf-current modecontrolled in BUCK_ILIMin 100 mA steps7002200mAFull-current modecontrolled in BUCK_ILIMin 200 mA steps14004400mA$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output voltage            | Vвиск                |                                                          | 0.3  |        | 1.57 | V    |

| regulation and voltage ripple<br>Note 2Image: second | Output voltage accuracy   | VBUCK_ACC            | Excluding static line/load regulation and voltage ripple | -1%  |        | +1%  |      |

| $\begin{bmatrix} I & I & I & I & I & I & I & I & I & I $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           |                      | regulation and voltage ripple                            | -3%  |        | +3%  |      |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Transient load regulation | V <sub>TR_LOAD</sub> | I <sub>OUT</sub> = 200 mA to 1000 mA<br>di/dt = 3 A/μs   |      | 30     | 45   | mV   |

| Output current       IouT       Full-current mode<br>Note 3       Image: Second                              | Transient line regulation | Vtr_line             | Iout = 500 mA                                            |      | 0.2    | 3    | mV   |

| Current limit     ILIM     Half-current mode<br>controlled in BUCK <x>_ILIM     700     2200       Full-current mode<br/>controlled in BUCK<x>_ILIM     1400     4400</x></x>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                           |                      | Half-current mode                                        |      |        | 1250 |      |