# 8V9705x Evaluation Board User Guide IDT Applications

October 2016

### 8V9705x Rev C EVB Evaluation Board User Guide

| <b>Contents</b> |

|-----------------|

| Introduction    |

| Introduction                                                                                               | 3            |

|------------------------------------------------------------------------------------------------------------|--------------|

| Contents                                                                                                   | 3            |

| Requirements                                                                                               | 3            |

| Quick Start                                                                                                | 3            |

| Default Power-Up Condition                                                                                 | 3            |

| Board Overview                                                                                             | 4            |

| Schematics                                                                                                 | 7            |

| Powering from an External Supply                                                                           | 10           |

| External Signal Reference Configuration                                                                    |              |

| DC Controls                                                                                                |              |

| Figures  Figure 1 Evaluation Pound Ton View                                                                | 4            |

| Figure 1. Evaluation Board Top View.                                                                       |              |

| Figure 2. Evaluation Board Bottom View                                                                     |              |

| Figure 3. Input Schematic                                                                                  |              |

| Figure 5. Loop Filter Schematic                                                                            |              |

|                                                                                                            | 0            |

|                                                                                                            |              |

| Figure 6 . Power Source Selection Schematic                                                                | 8            |

| Figure 7. LDO Power Schematic                                                                              |              |

| Figure 7. LDO Power Schematic                                                                              |              |

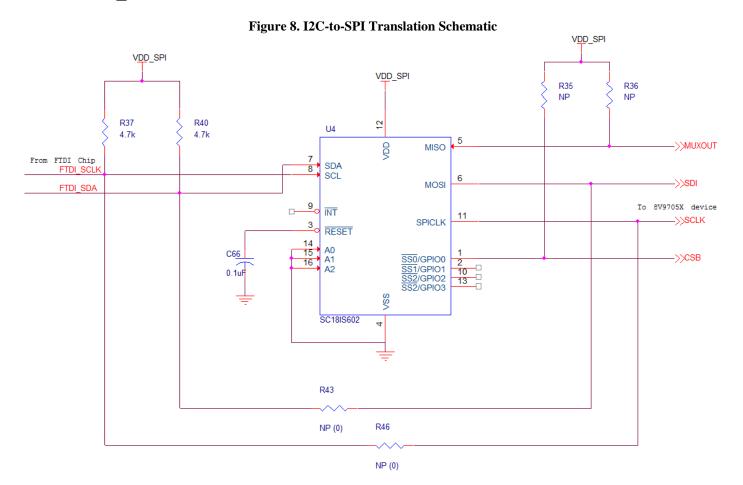

| Figure 7. LDO Power Schematic  Figure 8. I2C-to-SPI Translation Schematic  Figure 9. 8V9705x DUT Schematic | 9<br>9<br>9  |

| Figure 7. LDO Power Schematic                                                                              | 9<br>9<br>10 |

### Introduction

The 8V9705x evaluation board is designed to help the customer evaluate the 8V97051, 8V97051L, 8V97053 and 8V97053L IDT Wideband RF synthesizers. When the board is connected to a PC running IDT Timing Commander Software through USB, the device can be configured and programmed to generate frequencies with best-in-class performances.

### **Contents**

The 8V9705x evaluation board kit ships with the following:

- (1) 8V9705x Evaluation Board

- (1) USB Cable

### Requirements

PC Requirements:

- IDT Timing Commander Software Installed.

- USB 2.0 or USB 3.0 interface.

- Windows XP SP3 or later.

- Processor: Minimum 1GHz.

- Memory: Minimum 512MB, recommended 1GB.

- Available Disk Space: Min 600MB (1.5GB 64bit), recommended 1GB (2GB 64bit)

- Network access during installation if the .NET framework is not currently installed on the system.

### **Quick Start**

- (1) Connect a cable from a PC to the Evaluation Board USB port.

- (2) Verify that the board is configured to power from the USB (see JP3 jumper position in Fig.1)

- (3) JP2 and JP3 can be left floating.

- (4) Connect 50ohm cables from the RF OUTA output to the measurement equipment.

- (5) Configure the device using Timing Commander.

### **Default Power-Up Condition**

The board ships with a 25MHz TXCO and is configured to power from the USB. No external reference is required and no external power source, aside from the USB connection, is required. Outputs are disabled by default. The device must be configured using Timing Commander in order to activate the output.

Note: this device also has an RF\_OUTb differential output that is not routed out on the evaluation board.

### **Board Overview**

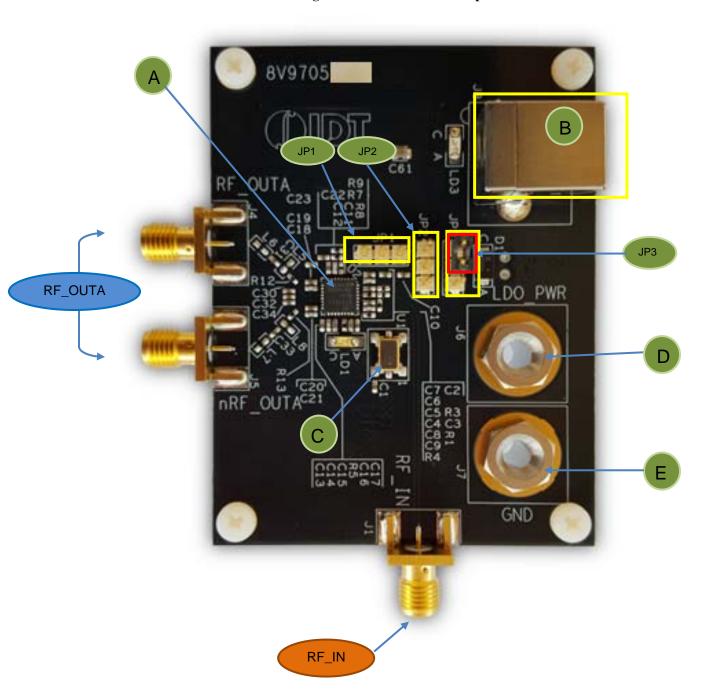

Use the following diagram to identify: power supply jacks, USB connector, input and output SMA connectors, TCXO, etc.

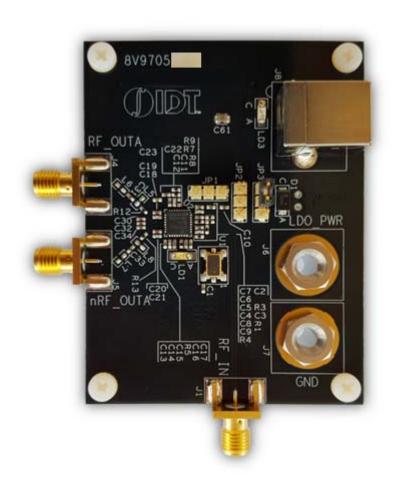

Figure 1. Evaluation Board Top View

## **Legend** Inputs

RF\_IN Reference input (the board requires re-work to enable this option)

### **Outputs**

RF\_OUTA Open-drain, ac-coupled output.

### **Other**

- A IDT8V9705x- the device to be evaluated

- B USB connector (also powers the board)

- C 25 MHz TXCO (default reference source)

- D External LDO\_POWER (alternate power source)

- E GND

- JP1 MUTE control (can be left floating)

- JP2 CE control (can be left floating)

- JP3 Power Source selector (USB vs LDO\_PWR power source)

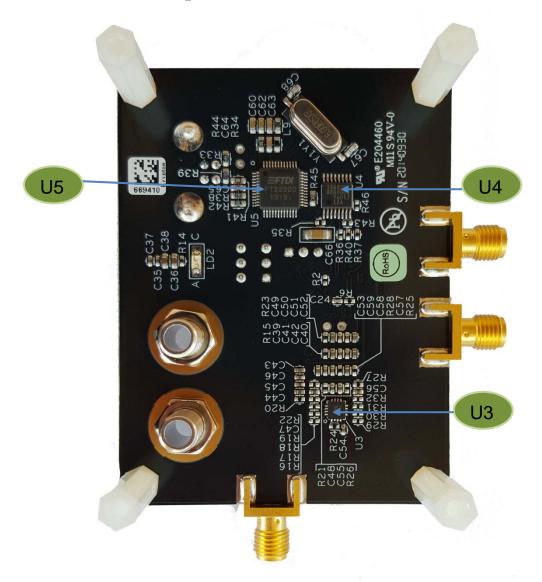

Figure 2. Evaluation Board Bottom View

### Legend

U5 FTDI USB-to-I2C chip

U4 USB-to-SPI translator

U3 LDO

### **Schematics**

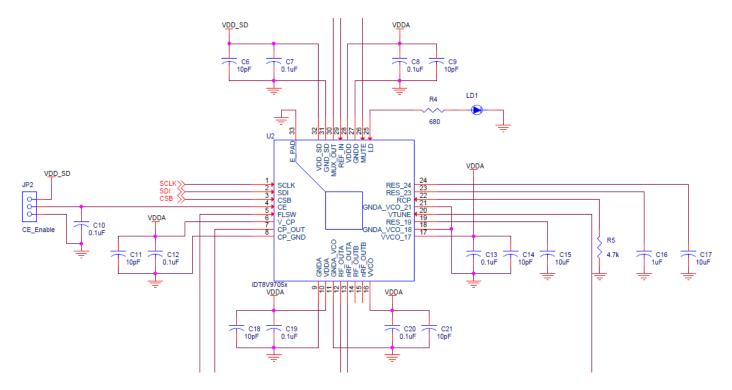

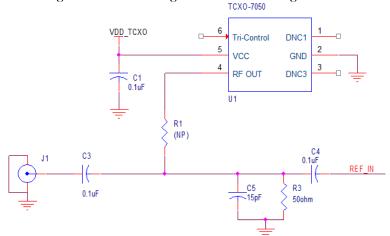

The following figures are schematics that are applicable to specific sections of this User Guide. The complete schematics are available in a separate document.

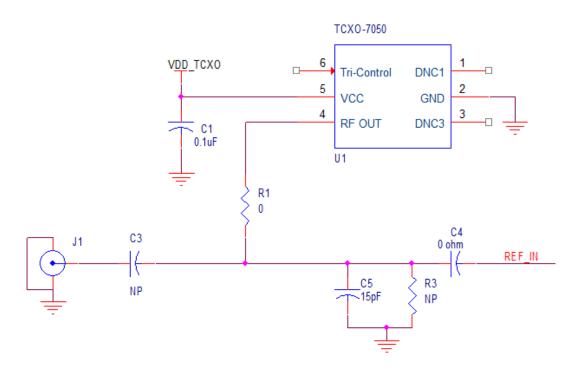

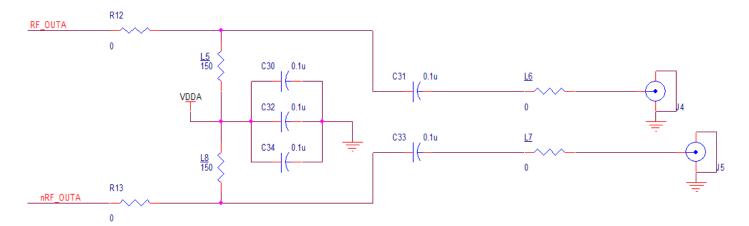

Figure 3. Input Schematic

**Figure 4. Output Termination Schematic**

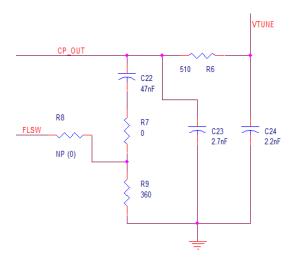

Figure 5. Loop Filter Schematic

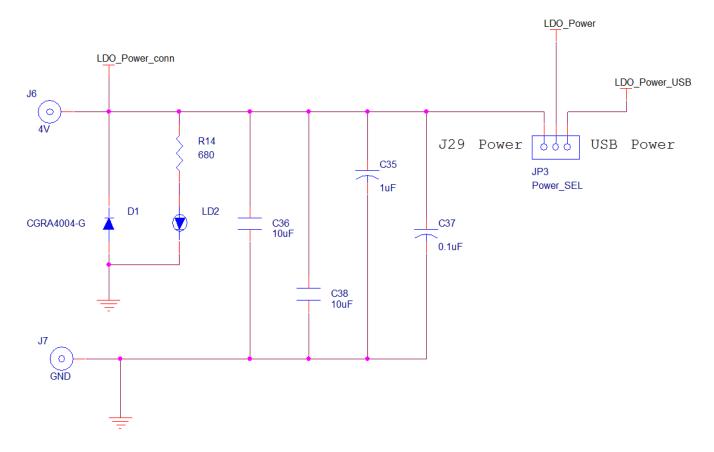

Figure 6. Power Source Selection Schematic

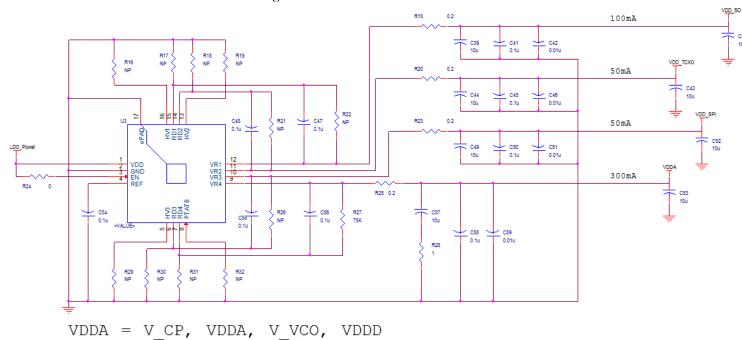

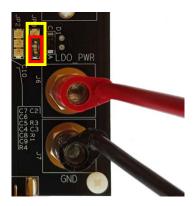

Figure 7. LDO Power Schematic

VDDA = V\_CP, VDDA, V\_VCO, VDDD VDD SPI = Translator, I2C PU, SPI PU

Figure 9. 8V9705x DUT Schematic

### **Powering from an External Supply**

The evaluation board is by default configured to power through USB. (See JP3 jumper position in Fig. 1). To power the device from an external supply:

- 1) Set JP3 to the position shown in Figure 9.

- 2) Connect an external 4V supply to LDO\_PWR (J6).

- 3) Connect the external supply Ground to GND (J7).

Figure 10. External Power Configuration

### **External Signal Reference Configuration**

An on-board 25MHz TXCO provides the default source for RF\_IN. In order to evaluate the device using an external signal reference, the following changes must be implemented:

- 1) Remove R20. This powers down the TXCO.

- 2) Remove R1. This disconnects the TXCO from the input path.

- 3) If the external signal can be ac-coupled, then populate C3=0.1uF. For dc termination to ground, C3=0ohm.

- 4) Populate R3=50ohm. This provides a termination for the input signal.

- 5) Replace C4=0.1uF. The input is ac-coupled into the device, which provides its own internal re-bias.

- 6) Connect the external signal reference to J1 using a 50-ohm cable.

Figure 11. External Signal Reference Configuration

### **DC Controls**

- JP1 MUTE control: RF\_OUTA and RF\_OUTB Power-Down. A logic low on this pin mutes the RF\_OUT outputs and puts them in High-Impedance. This function is also SPI controllable and in this case also allows the power down of either RF\_OUTA or RF\_OUTB. This jumper can be left floating for normal operation.

- JP2 Chip Enable: Powers down the device on logic Low, with charge pump put into a High-Impedance mode. Powers up the device on logic High. This jumper can be left floating for normal operation.

For more questions or support, feel free to contact us at <a href="mailto:clocks@idt.com">clocks@idt.com</a>

October 2016

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/

### **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Renesas Electronics:

EVK-8V97051 8V97053L-EVK 8V97051L-EVK