## HIGH-SPEED 4K x 9DUAL-PORT STATIC RAM

#### Features:

- True Dual-Ported memory cells which allow simultaneous reads of the same memory location

- High-speed access

- Commercial: 12ns (max.)

- Standard-power operation

- IDT7014S

- Active: 750mW (typ.)

- Fully asynchronous operation from either port

- ◆ TTL-compatible; single 5V (±10%) power supply

- Available in 52-pin PLCC and a 64-pin TQFP

### Description:

The IDT7014 is a high-speed 4K x 9 Dual-Port Static RAM designed to be used in systems where on-chip hardware port arbitration is not needed. This part lends itself to high-speed applications which do not rely on BUSY signals to manage simultaneous access.

The IDT7014 provides two independent ports with separate control, address, and I/O pins that permit independent, asynchronous access for reads or writes to any location in memory. See functional description.

The IDT7014 utilizes a 9-bit wide data path to allow for parity at the user's option. This feature is especially useful in data communication applications where it is necessary to use a parity bit for transmission/reception error checking.

Fabricated using a high-performance technology, these Dual-Ports typically operate on only 750mW of power at maximum access times as fast as 12ns.

The IDT7014 is packaged in a 52-pin PLCC and a 64-pin thin quad flatpack, (TQFP).

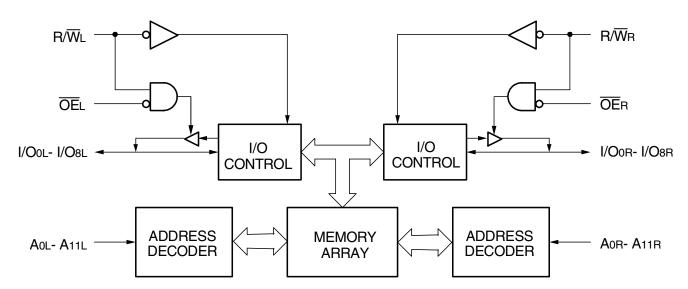

## Functional Block Diagram

2528 drw 01

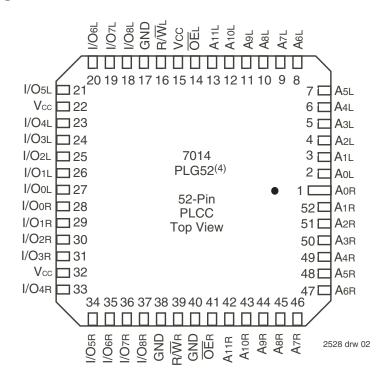

# Pin Configuration(1,2,3)

#### NOTES:

- 1. All Vcc pins must be connected to power supply.

- 2. All GND pins must be connected to ground supply.

- PLG52 package body is approximately .75 in x. 75 in x .17 in.

PNG64 package body is approximately 14mm x 14mm x 1.4mm.

- 4. This package code is used to reference the package diagram.

# Absolute Maximum Ratings (1)

| Symbol               | Rating                                     | Commercial<br>& Industrial | Unit |

|----------------------|--------------------------------------------|----------------------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage<br>with Respect<br>to GND | -0.5 to +7.0               | V    |

| VTERM <sup>(2)</sup> | Terminal Voltage                           | -0.5 to +Vcc               | V    |

| TBIAS                | Temperature<br>Under Bias                  | -55 to +125                | °C   |

| Tstg                 | Storage<br>Temperature                     | -65 to +150                | °C   |

| ЮИТ                  | DC Output<br>Current                       | 50                         | mA   |

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- VTERM must not exceed Vcc + 10% for more than 25% of the cycle time or 10ns maximum, and is limited to ≤ 20mA for the period of VTERM ≥ Vcc + 10%.

# Maximum Operating Temperature and Supply Voltage<sup>(1,2)</sup>

|            | )                      |     |                   |

|------------|------------------------|-----|-------------------|

| Grade      | Ambient<br>Temperature | GND | Vcc               |

| Commercial | 0°C to +70°C           | 0V  | 5.0V <u>+</u> 10% |

| Industrial | -40°C to +85°C         | 0V  | 5.0V <u>+</u> 10% |

2528 tbl 02

#### NOTES:

2528 tbl 01

1. This is the parameter Ta. This is the "instant on" case temperature.

# Recommended DC Operating Conditions

| Symbol | Parameter          | Min.                | Тур. | Max.   | Unit |

|--------|--------------------|---------------------|------|--------|------|

| Vcc    | Supply Voltage     | 4.5                 | 5.0  | 5.5    | ٧    |

| GND    | Ground             | 0                   | 0    | 0      | ٧    |

| VIH    | Input High Voltage | 2.2                 | _    | 6.0(2) | ٧    |

| VIL    | Input Low Voltage  | -0.5 <sup>(1)</sup> | _    | 0.8    | V    |

#### NOTES

- 2528 tbl 03

- 1.  $VIL \ge -1.5V$  for pulse width less than 10ns.

- 2. VTERM must not exceed Vcc + 10%.

# DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range $^{(1)}$ (Vcc = 5.0V $\pm$ 10%)

|        |                        |                                 | 7014S |      |      |

|--------|------------------------|---------------------------------|-------|------|------|

| Symbol | Parameter              | Test Conditions                 | Min.  | Max. | Unit |

| ILI    | Input Leakage Current  | Vcc = 5.5V, $VIN = 0V$ to $Vcc$ | 1     | 10   | μΑ   |

| ILO    | Output Leakage Current | Vout = 0V to Vcc                | 1     | 10   | μΑ   |

| Vol    | Output Low Voltage     | lol = +4mA                      | -     | 0.4  | ٧    |

| Voh    | Output High Voltage    | loн = -4mA                      | 2.4   | _    | V    |

#### NOTE:

1. At  $Vcc \le 2.0V$  input leakages are undefined.

2528 tbl 04

# DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (Vcc = 5V ± 10%)

|        |                                |                                                     |         |      | 4S12<br>I Only |      | IS15<br>Only |      |

|--------|--------------------------------|-----------------------------------------------------|---------|------|----------------|------|--------------|------|

| Symbol | Parameter                      | Test Condition                                      | Version | Тур. | Max            | Тур. | Max          | Unit |

| lcc    | Dynamic Operating              | Outputs Open<br>f = f <sub>MAX</sub> <sup>(1)</sup> | COM'L S | 160  | 250            | 160  | 250          | mA   |

|        | Current<br>(Both Ports Active) | I = IMAX**                                          | IND S   | _    |                | _    | _            |      |

2528 tbl 05a

|        |                             |                |         | 7014S20<br>Com'l & Ind |      |     | 1S25<br>Only |      |      |

|--------|-----------------------------|----------------|---------|------------------------|------|-----|--------------|------|------|

| Symbol | Parameter                   | Test Condition | Version | 1                      | Тур. | Max | Тур.         | Max. | Unit |

| lcc    | Dynamic Operating           | Outputs Open   | COM'L   | S                      | 155  | 245 | 150          | 240  | mA   |

|        | Current $f = f_{MAX}^{(1)}$ | IND            | S       | 155                    | 260  |     |              |      |      |

2528 tbl 05b

#### NOTES:

1. At f = fmax, address inputs are cycling at the maximum read cycle of 1/trc using the "AC Test Conditions" input levels of GND to 3V.

### **AC Test Conditions**

| Input Pulse Levels            | GND to 3.0V       |

|-------------------------------|-------------------|

| Input Rise/Fall Times         | 3ns Max.          |

| Input Timing Reference Levels | 1.5V              |

| Output Reference Levels       | 1.5V              |

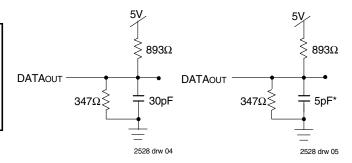

| Output Load                   | Figures 1,2 and 3 |

2528 tbl 06

2528 tbl 07

Figure 1. AC Output Test Load.

Figure 2. Output Test Load (for thz, twz, and tow) \*Including scope and jig.

## Capacitance<sup>(1)</sup>

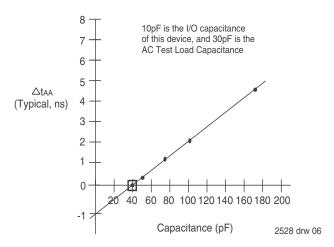

(Ta = +25°C, f = 1.0MHz) TQFP Package Only

| Symbol | Parameter          | Conditions <sup>(2)</sup> | Max. | Unit |

|--------|--------------------|---------------------------|------|------|

| CIN    | Input Capacitance  | VIN = 3dV                 | 9    | pF   |

| Соит   | Output Capacitance | Vout = 3dV                | 10   | pF   |

#### NOTES:

- This parameter is determined by device characteristics but is not production tested.

- 2. 3dv references the interpolated capacitance when the input and output signals with from 0V to 3V or from 3V to 0V.

Figure 3. Typical Output Derating (Lumped Capacitive Load).

# AC Electrical Characteristics Over the Operating Temperature and Supply Voltage

|            |                                     | 7014S12<br>Com'l Only |      | 7014S15<br>Com'l Only |      |      |

|------------|-------------------------------------|-----------------------|------|-----------------------|------|------|

| Symbol     | Parameter                           | Min.                  | Max. | Min.                  | Max. | Unit |

| READ CYCLE |                                     |                       |      |                       |      |      |

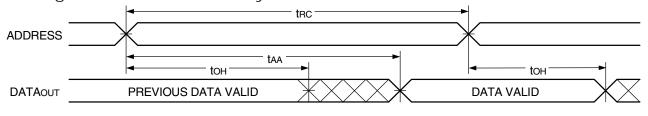

| trc        | Read Cycle Time                     | 12                    | 1    | 15                    | ı    | ns   |

| taa        | Address Access Time                 |                       | 12   | _                     | 15   | ns   |

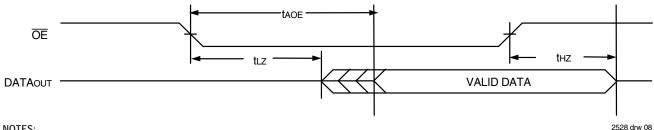

| taoe       | Output Enable Access Time           |                       | 8    | _                     | 8    | ns   |

| tон        | Output Hold from Address Change     | 3                     | 1    | 3                     |      | ns   |

| tLz        | Output Low-Z Time <sup>(1,2)</sup>  | 3                     |      | 3                     |      | ns   |

| tHZ        | Output High-Z Time <sup>(1,2)</sup> | _                     | 7    | _                     | 7    | ns   |

2528 tbl 08a

|            |                                     | 7014S20<br>Com'l & Ind |      | 7014S25<br>Com'l Only |      |      |

|------------|-------------------------------------|------------------------|------|-----------------------|------|------|

| Symbol     | Parameter                           | Min.                   | Max. | Min.                  | Max. | Unit |

| READ CYCLE |                                     |                        |      |                       |      |      |

| trc        | Read Cycle Time                     | 20                     | -    | 25                    | 1    | ns   |

| taa        | Address Access Time                 | _                      | 20   | _                     | 25   | ns   |

| taoe       | Output Enable Access Time           | _                      | 10   | _                     | 12   | ns   |

| tон        | Output Hold from Address Change     | 3                      |      | 3                     |      | ns   |

| tLZ        | Output Low-Z Time <sup>(1,2)</sup>  | 3                      | _    | 3                     | _    | ns   |

| tHZ        | Output High-Z Time <sup>(1,2)</sup> |                        | 9    | _                     | 11   | ns   |

#### NOTES

2528 tbl 08b

- 1. Transition is measured 0mV from Low or High-impedance voltage with Output Test Load (Figure 2).

- 2. This parameter is determined by device characterization, but is not production tested.

2528 drw 07

## Timing Waveform of Read Cycle No. 1, Either Side<sup>(1,2)</sup>

## Timing Waveform of Read Cycle No. 2, Either Side<sup>(1, 3)</sup>

#### NOTES:

- 1.  $R/\overline{W} = V_{IH}$  for Read Cycles.

- 2.  $\overline{OE} = VIL$ .

- 3. Addresses valid prior to  $\overline{\text{OE}}$  transition LOW.

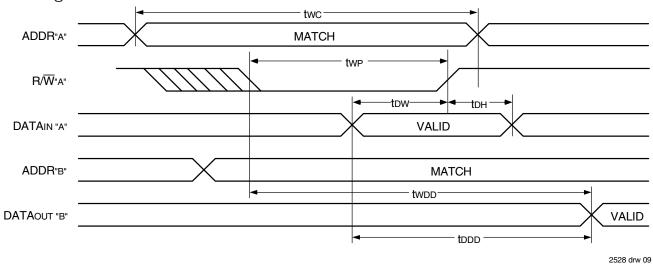

# Timing Waveform of Write with Port-to-Port Read (1,2)

#### NOTES:

- 1.  $R/\overline{W}^{"}B^{"} = V_{IH}$ , read cycle pass through.

- 2. All timing is the same for left and right ports. Port "A" may be either left or right port. Port "B" is opposite from port "A".

# AC Electrical Characteristics Over the Operating Temperature and Supply Voltage

|             |                                                    | 7014S12<br>Com'l Only |      | 7014S15<br>Com'l Only |      |      |

|-------------|----------------------------------------------------|-----------------------|------|-----------------------|------|------|

| Symbol      | Parameter                                          | Min.                  | Max. | Min.                  | Max. | Unit |

| WRITE CYCLE |                                                    |                       |      |                       |      |      |

| twc         | Write Cycle Time                                   | 12                    | _    | 15                    | _    | ns   |

| taw         | Address Valid to End-of-Write                      | 10                    | _    | 14                    | _    | ns   |

| tas         | Address Set-up Time                                | 0                     | _    | 0                     | _    | ns   |

| twp         | Write Pulse Width                                  | 10                    | _    | 12                    | _    | ns   |

| twr         | Write Recovery Time                                | 1                     | _    | 1                     | _    | ns   |

| tow         | Data Valid to End-of-Write                         | 8                     | _    | 10                    | _    | ns   |

| tHZ         | Output High-Z Time <sup>(1,2)</sup>                |                       | 7    | _                     | 7    | ns   |

| toн         | Data Hold Time <sup>(3)</sup>                      | 0                     | _    | 0                     | _    | ns   |

| twz         | Write Enable to Output in High-Z <sup>(1,2)</sup>  | _                     | 7    | _                     | 7    | ns   |

| tow         | Output Active from End-of-Write <sup>(1,2,3)</sup> | 0                     | _    | 0                     | _    | ns   |

| twdd        | Write Pulse to Data Delay <sup>(4)</sup>           | _                     | 25   | _                     | 30   | ns   |

| todd        | Write Data Valid to Read Data Delay <sup>(4)</sup> |                       | 22   | _                     | 25   | ns   |

2528 tbl 09a

|             |                                                    | 7014S20<br>Com'l & Ind |      | 7014S25<br>Com'l Only |      |      |

|-------------|----------------------------------------------------|------------------------|------|-----------------------|------|------|

| Symbol      | Parameter                                          | Min.                   | Max. | Min.                  | Max. | Unit |

| WRITE CYCLE |                                                    |                        |      |                       |      |      |

| twc         | Write Cycle Time                                   | 20                     | _    | 25                    | _    | ns   |

| taw         | Address Valid to End-of-Write                      | 15                     | _    | 20                    | _    | ns   |

| tas         | Address Set-up Time                                | 0                      | -    | 0                     | _    | ns   |

| twp         | Write Pulse Width                                  | 15                     | -    | 20                    | _    | ns   |

| twr         | Write Recovery Time                                | 2                      | _    | 2                     | _    | ns   |

| tow         | Data Valid to End-of-Write                         | 12                     | _    | 15                    | _    | ns   |

| tHZ         | Output High-Z Time <sup>(1,2)</sup>                |                        | 9    | _                     | 11   | ns   |

| tон         | Data Hold Time <sup>(3)</sup>                      | 0                      | _    | 0                     | _    | ns   |

| twz         | Write Enable to Output in High-Z <sup>(1,2)</sup>  |                        | 9    | _                     | 11   | ns   |

| tow         | Output Active from End-of-Write <sup>(1,2,3)</sup> | 0                      | _    | 0                     | _    | ns   |

| twdd        | Write Pulse to Data Delay <sup>(4)</sup>           | _                      | 40   | _                     | 45   | ns   |

| todd        | Write Data Valid to Read Data Delay <sup>(4)</sup> | _                      | 30   | _                     | 35   | ns   |

#### **NOTES**

2528 tbl 09b

- 1. Transition is measured 0mV from Low or High-impedance voltage with Output Test Load (Figure 2).

- 2. This parameter is guaranteed by device characterization, but is not production tested.

- 3. The specification for ton must be met by the device supplying write data to the RAM under all operating conditions. Although ton and tow values will vary over voltage and temperature, the actual ton will always be smaller than the actual tow.

- 4. Port-to-port delay through RAM cells from writing port to reading port, refer to "Timing Waveform of Write With Port-to-Port Read".

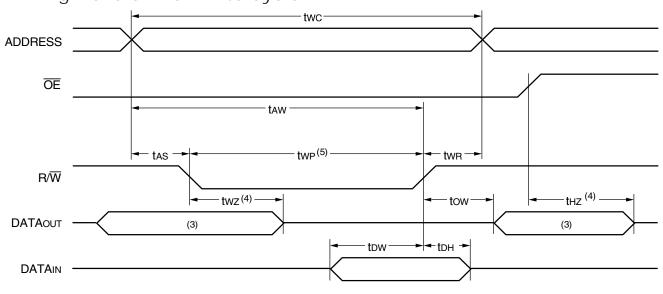

# Timing Waveform of Write Cycle<sup>(1,2,3,4,5)</sup>

NOTES:

2528 drw 10

2528 tbl 10

- 1. R/W must be HIGH during all address transitions.

- 2. twn is measured from  $R/\overline{W}$  going HIGH to the end of write cycle.

- 3. During this period, the I/O pins are in the output state, and input signals must not be applied.

- 4. Transition is measured 0mV from the Low or High-impedance voltage with the Output Test Load (Figure 2).

- 5. If  $\overline{OE}$  is LOW during a R/W controlled write cycle, the write pulse width must be the larger of twp or (twz + tbw) to allow the I/O drivers to turn off data to be placed on the bus for the required tow. If  $\overline{\text{OE}}$  is HIGH during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified twp.

## **Functional Description**

The IDT7014 provides two ports with separate control, address, and I/O pins that permit independent access for reads or writes to any location in memory. It lacks the chip enable feature of CMOS Dual Ports, thus it operates in active mode as soon as power is applied. Each port has its own Output Enable control  $(\overline{OE})$ . In the read mode, the port's OE turns on the output drivers when set LOW. The user application should avoid simultaneous write operations to the same memory location. There is no on-chip arbitration circuitry to resolve write priority and partial data from both ports may be written. READ/WRITE conditions are illustrated in Table 1.

### Truth Table I - Read/Write Control

| Left or Right Port <sup>(1)</sup> |    |         |                               |

|-----------------------------------|----|---------|-------------------------------|

| R/W                               | ŌĒ | D0-8    | Function                      |

| L                                 | Х  | DATAIN  | Data written into memory      |

| Н                                 | L  | DATAOUT | Data in memory output on port |

| Х                                 | Н  | Z       | High-impedance outputs        |

1. AoL - A11L is not equal to AoR - A11R.

'H' = HIGH, 'L' = LOW, 'X' = Don't Care, and 'Z' = HIGH Impedance.

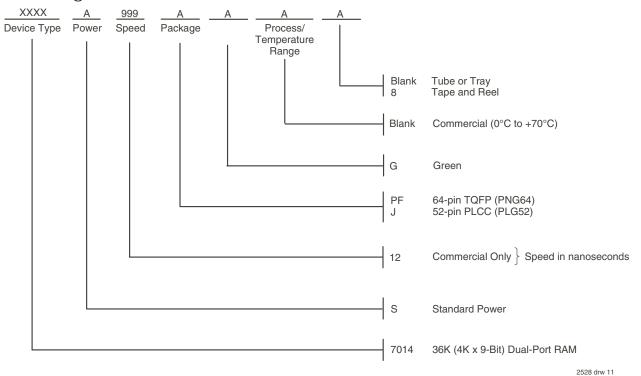

## Ordering Information

#### NOTES:

LEAD FINISH (SnPb) parts are Obsolete. Product Discontinuation Notice - PDN# SP-17-02

Note that information regarding recently obsoleted parts is included in this datasheet for customer convenience.

### Orderable Part Information

| Speed (ns) | Orderable Part ID | Pkg.<br>Code | Pkg.<br>Type | Temp.<br>Grade |

|------------|-------------------|--------------|--------------|----------------|

| 12         | 7014S12JG         | PLG52        | PLCC         | С              |

|            | 7014S12JG8        | PLG52        | PLCC         | С              |

|            | 7014S12PFG        | PNG64        | TQFP         | С              |

|            | 7014S12PFG8       | PNG64        | TQFP         | С              |

# Datasheet Document History

01/06/99: Initiated datasheet document history

Converted to new format

Cosmetic and typographical corrections Added additional notes to pin configurations

Page 2 Added additional notes to pin

Changed drawing format

Page 1 Corrected DSC number

06/03/99:

# Datasheet Document History (con't)

| 03/10/00:  |                | Added Industrial Temperature Ranges and deleted corresponding notes                                                                 |

|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------|

|            |                | Replaced IDT logo                                                                                                                   |

|            | Page 1         | Made corrections to drawing                                                                                                         |

|            |                | Changed ±200mV to 0mV in notes                                                                                                      |

|            | Page 6         | Made changes to drawings                                                                                                            |

| 05/19/00:  | Page 3         | Increased storage temperature parameter                                                                                             |

|            |                | Clarified TA parameter                                                                                                              |

| 10/16/01:  | Page 2         | Added date revision for pin configuration                                                                                           |

|            | Pages 4, 5 & 7 | Removed Industrial temp values and column headings for 15 & 25ns speeds from                                                        |

|            |                | DC and AC Electrical Characteristics                                                                                                |

|            | Page 9         | Removed Industrial temp offering from 15 & 25ns ordering information                                                                |

|            | D 1 0 0        | Added Industrial temp footnote to ordering information                                                                              |

| 0.4/0.4/07 | Pages 1 & 9    | Replaced ™ logo with ® logo                                                                                                         |

| 04/04/06:  | Page 1         | Added green availability to features                                                                                                |

| 10/11/00   | Page 9         | Added green indicator to ordering information                                                                                       |

| 12/11/08:  | Page 9         | Removed "IDT" from orderable part number                                                                                            |

| 08/18/14:  | Page 9         | Added Tape and Reel to Ordering Information  The peakings godes PN941.8 LEG 1 shanged to PN94.8 LEG respectively to match standard. |

|            | Page 2 & 9     | The package codes PN84-1 & J52-1 changed to PN84 & J52 respectively to match standard                                               |

| 03/16/16:  | Page 2         | package codes<br>Changed diagram for the PN64 pin configuration by rotating package pin labels and pin                              |

| 03/10/10.  | r age z        | numbers 90 degrees counter clockwise to reflect pin 1 orientation and added pin 1 dot at pin 1                                      |

|            |                | Removed the PN64 chamfer and aligned the top and bottom pin labels in the standard direction                                        |

|            |                | Added the IDT logo to the PN64 pin configurations and changed the text to be in                                                     |

|            |                | alignment with new diagram marking specs                                                                                            |

|            |                |                                                                                                                                     |

|            |                | Removed the date revision indicator for each pin configuration                                                                      |

|            | Dago 4         | Updated footnote references for PN64 pin configuration                                                                              |

| 10/10/17:  | Page 4         | Figure 3 Typical Output Derating Graph, corrected a typo                                                                            |

| 10/10/17.  |                | Product Discontinuation Notice - PDN# SP-17-02                                                                                      |

| 05/44/40   |                | Last time buy expires June 15, 2018                                                                                                 |

| 05/14/19:  | Page 1         | Removed Industrial speed grade offering and updated Commercial speed grade offering in Features                                     |

|            | Page 2         | Changed diagram for the PLG52 pin configuration by rotating package pin labels and pin                                              |

|            |                | numbers 90 degrees clockwise to reflect pin 1 orientation and added pin 1 dot at pin 1                                              |

|            |                | Aligned the top and bottom pin labels in the standard direction                                                                     |

|            |                | Added the IDT logo to the PLG52 pin configuration and changed the text to be in                                                     |

|            |                | alignment with new diagram marking specs                                                                                            |

|            |                | Updated footnote references for PNG64 and PLG52                                                                                     |

|            | Page 2 & 9     | The package codes PN64 & J52 changed to PNG64 & PLG52 respectively to match standard                                                |

|            | D 0            | package codes                                                                                                                       |

|            | Page 9         | Removed Industrial speed grade offering and updated Commercial speed grade offering in Ordering                                     |

|            |                | Information                                                                                                                         |

|            |                | Removed industrial temp footnote from ordering information                                                                          |

|            |                | Revised LEAD FINISH note to indicate Obsolete Added Orderable Part Information                                                      |

| 12/13/21:  | Page 1 - 11    | Source file updated to reflect previous Corporate Marketing rebranding                                                              |

| 12/13/21.  | Page 2         | Package codes updated by removing IDT                                                                                               |

|            | Page 10        | Ordering information updated by removing green footnote reference                                                                   |

|            | i age iu       | Oracing information updated by removing green toothole release                                                                      |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Renesas Electronics:

7014S20PF8 7014S12J 7014S15J 7014S25J 7014S20J 7014S15PF 7014S12PF8 7014S12PF 7014S12JG 7014S12PFG8 7014S12PFG 7014S15J8 7014S12J8 7014S20PF 7014S25PF 7014S25PF8 7014S25J8 7014S20J8 7014S15PF8 7014S20JI 7014S20PFI8 7014S20JI8 7014S20PFI 7014S12JG8