## GS-EVM-DRG-100V7R-GS2

# 100 V Driver GaN Fully Integrated 7mΩ DC/DC Power Stage

### **Technical Manual**

Visit www.gansystems.com for the latest version of this technical manual.

#### **WARNING:**

PCB surface can become hot. Contact may cause burns. Do not touch!

#### **CAUTION!**

This product contains parts that are susceptible to damage by electrostatic discharge (ESD). Always follow ESD prevention procedures when handling the product.

### Overview

GS-EVM-DRG-100V7R-GS2 is fully-integrated 100V GaN Half-Bridge power stage for use in multiple high-efficiency small form-factor 48V Applications. Module construction embeds all components without using bond wires, minimizing inductance, achieving ultra-low voltage spikes on gate and switch nodes, and minimizing RFI. This DrGaN thermal design achieves ultra-low Junction-to-Case thermal resistance which reduces junction operating temperature. GS-EVM-DRG-100V7R-GS2 "Drop-In" GaN power stages create designs with high efficiency and power density for 48V DC-DC applications. GS-EVM-DRG-100V7R-GS2 is intended and made available for testing and evaluation purposes only.

#### **Features**

- Integrated  $7m\Omega$  half-bridge power stage

- 10 x 7.8 mm<sup>2</sup> SMT surface mount technology package

- Includes two GS61008 Die (100V 7mW E-mode GaN) onboard

- Dual PWM input

- Ultra-low Rojo

- Ultra-fast rise/fall time

- High power density at 1MHz+ fsw operation

- High efficiency for 48V board power

- Small footprint

### **Applications**

- 48 V Step Down Converters

- CPU/GPU/DDR

- High-performance Class D Audio systems

- Forward Converter, ZVS, Buck/Boost topologies

### **Contents and Requirements**

The GS-EVM-DRG-100V7R-GS2 includes the following hardware.

Table 1 GS-EVM-DRG-100V7R-GS2 Evaluation Kit Contents

| Quantity | Description                                                                          |

|----------|--------------------------------------------------------------------------------------|

| 1        | GS-EVM-DRG-100V7R-GS2 100V Driver GaN – Integrated 7mΩ DC/DC half-bridge power stage |

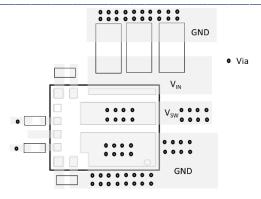

Figure 1 DrGaN Power Stage

# **Technical Specifications**

### **Absolute Maximum Ratings**

Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional Operation should be restricted to the conditions specified in the Normal Operating section of this technical manual.

Table 2 Absolute Macximum Ratings (T<sub>CASE</sub> = 25 °C)

| Parameter                                                              | Sym.                                       | Value        | Unit |

|------------------------------------------------------------------------|--------------------------------------------|--------------|------|

| Max Input Voltage (GaN Devices, V <sub>IN</sub> to Vsw, Vsw to PGND)   | V <sub>DS_MAX</sub>                        | 100          | V    |

| Max Input Voltage (Drive circuit, V <sub>IN</sub> to V <sub>SW</sub> ) | V <sub>IN_MAX</sub>                        | 6.2 to 85    | V    |

| Max Output Voltage (Drive circuit, Vsw to PGND)                        | V <sub>OUT_MAX</sub>                       | 0.9 to 85    | V    |

| Continuous I <sub>DS</sub> Current (T <sub>JUNC</sub> = 25 °C)         | I <sub>DS_MAX_25C</sub>                    | 90           | Α    |

| Continuous I <sub>DS</sub> Current (T <sub>JUNC</sub> = 100 °C)        | I <sub>DS_MAX_100C</sub>                   | 65           | Α    |

| Max Driver-side Voltages to GND (V <sub>cc</sub> , DLH, DHL, PWM)      | V <sub>CC_MAX</sub><br>V <sub>IO_MAX</sub> | -0.3 to +7.0 | V    |

| Maximum Junction Temperature (GaN)                                     | T <sub>JUNC_MAX</sub>                      | 150          | °C   |

| Maximum Operating Temperature (Module)                                 | T <sub>CASE</sub>                          | -40 to +125  | °C   |

| Maximum Storage Temperature Range (Module)                             | T <sub>STOR</sub>                          | -55 to +150  | °C   |

#### Thermal Characteristics

GS-EVM-DRG-100V7R-GS2 is Surface Mount Device (SMD) with Bottom-side Cu Pads for Surface Mount PCB attach. RøJUNC-AMB value based on recommended Via Pattern with multi-layer FR4 PCB. No Airflow (zero LFM) and no Top-side Heat Sink required to meet RøJUNC-AMB (Conduction Heat Transfer). GS-EVM-DRG-100V7R-GS2 has a much more effective competitive thermal design.

Table 3 Thermal Characterictics

| Parameter                                  | Sym.                    | Min. | Тур. | Max. | Unit |

|--------------------------------------------|-------------------------|------|------|------|------|

| Thermal Resistance (Junction to Board)     | R <sub>O_JUNC-BRD</sub> | -    | 0.6  | -    | °C/W |

| Thermal Resistance (Junction to Ambient)   | R <sub>O_JUNC-AMB</sub> | -    | 8.4  | -    | °C/W |

| Maximum Soldering Temperature (MSL2 rated) | T <sub>SOLDER</sub>     | -    | -    | 260  | °C   |

### **Normal Operation Conditions**

GS-EVM-DRG-100V7R-GS2 is surface mount device with bottom-side Cu pads for surface mount PCB attach.  $R_{\bullet JC-AMB}$  value based on recommended via pattern with multi-layer FR4 PCB. No airflow (zero LFM) and no top-side heat sink required to meet  $R_{\bullet JC-AMB}$  (conduction heat transfer).

| Table 4 Normal Operation Conditions (TJUNG | $c = 25 ^{\circ}\text{C.}$ and $V_{CC} = V_{GS} = 6.0 ^{\circ}\text{V}$ |

|--------------------------------------------|-------------------------------------------------------------------------|

|--------------------------------------------|-------------------------------------------------------------------------|

| Parameter                                                | Sym.                 | Min. | Тур. | Max. | Unit | Conditions                                        |

|----------------------------------------------------------|----------------------|------|------|------|------|---------------------------------------------------|

| Nominal V <sub>IN</sub> Range                            | V <sub>IN_NOM</sub>  | 6.2  | -    | 100  | V    |                                                   |

| Nominal V <sub>SW</sub> Range                            | V <sub>OUT_NOM</sub> | 0.9  | -    | 80   | V    |                                                   |

| Nominal V <sub>CC</sub> Range                            | V <sub>CC_NOM</sub>  | 5.0  | -    | 6.0  | V    |                                                   |

| Nominal I/O Voltage                                      | V <sub>IO_NOM</sub>  | 0    | -    | 5.5  | V    | DLH, DHL, PWM                                     |

| Continuous I <sub>OUT</sub> (T <sub>JUNC</sub> = 100 °C) | I <sub>DS_NOM</sub>  | -    | -    | 16.6 | А    | V <sub>OUT</sub> = 12V, T <sub>JUNC</sub> = 100°C |

| Operating Temp (Module)                                  | T <sub>CASE</sub>    | -40  | -    | +105 | °C   |                                                   |

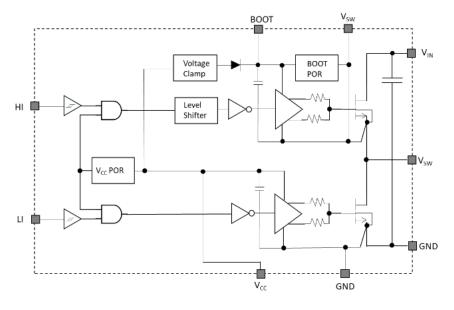

### **Block Diagram**

Figure 2 DrGaN Power Module Block Diagram

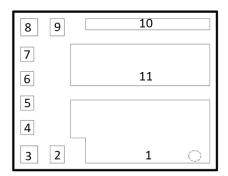

Pin

Figure 3 DrGaN Power Module Bottom View

Table 5 Pinout Table

| Pin  | Pinout          |              |                                                            |  |  |  |  |  |

|------|-----------------|--------------|------------------------------------------------------------|--|--|--|--|--|

| #    | Name            | I/O Type     | Description and Operation                                  |  |  |  |  |  |

|      | GS2             |              |                                                            |  |  |  |  |  |

| 1,2  | GND             | Power GND    | Connect to PCB GND thru multiple Via's                     |  |  |  |  |  |

| 3    | V <sub>CC</sub> | Supply       | Gate Drive power supply, connect to Regulated 5.5V or 6.0V |  |  |  |  |  |

| 4    | LI              | Input        | Dual PWM Low Side Gate Input                               |  |  |  |  |  |

| 5    | НІ              | Input        | Dual PWM High Side Gate Input                              |  |  |  |  |  |

| 6    | N/C             | Input        | No Connect                                                 |  |  |  |  |  |

| 7    | N/C             | -            | No Connect                                                 |  |  |  |  |  |

| 8    | воот            | Supply       | Floating High Side Gate Drive power supply                 |  |  |  |  |  |

| 9,11 | V <sub>SW</sub> | Power Output | Half-Bridge power stage output (switching node)            |  |  |  |  |  |

| 10   | V <sub>IN</sub> | Power Input  | Supply Voltage to Half-Bridge power stage                  |  |  |  |  |  |

## **Application Specifications**

### **Integrated GaN Gate Drive**

- GaN E-mode Gate Drive Voltage (Vcs) is nominally 0V to +6.0V for optimal RDSo<sub>N</sub> performance and Lifetime Reliability. Absolute Maximum Vcs Rating is +7.0V (DC voltage), but GaN E-modes are Rated for transients up to +10V and -20V for pulses up to 1μs. In order to simplify system-level power design, these specifications for GaN E-mode Vcs are incorporated into the DrGaN design. Connect Vcc Pin to +6V (optimal), or +5V (optional), to provide for GaN Gate Drive.

- While +6.0V Gate Drive voltage puts the Enhancement Mode High Electron Mobility Transistors full Enhancement (i.e., optimal efficiency), +5.0V Gate Drive supply can also be used, resulting in slightly lower DrGaN Efficiency.

- Gate and Commutation loop inductances are minimized in the DrGaN design, and DC Link is decoupled, providing for fastest Gate dV/dt (lowest Switching Loss) and optimized Switching Waveforms at high-FSW, full-Load operation.

- Driver Latch-Up Immunity (ΔV<sub>LATCH</sub>) supports ultra-fast Gate dV/dt in an ultra-low inductance module.

- Rise Time, Fall Time, Prop Delay, and Prop Delay Matching are designed for sub-20 ns Dead Time.

- Integrated Gate Resistors for High Side and Low Side Gates for Turn-On and Turn-Off, and a Zener

- Diode in the Bootstrap, are optimized for highest Efficiency (fastest dV/dt with reliable Switching Waveforms).

#### **GaN** reverse conduction

- GaN E-modes do not have a parasitic Body Diode or a parasitic Bi-Polar in their Substrate, therefore the GaN E-mode has Zero QRR and extremely high dV/dt Ruggedness. But despite not having a Body Diode, the GaN E-mode will inherently conduct in Reverse Current flow (Source-to-Drain) through the 2DEG Channel, when Source-to-Drain potential (VsD) is greater than VTH (approximately 1.3V)

- During reverse conduction, V<sub>GS</sub> can be zero Volts (no Gate Bias is required for Reverse Conduction operation), and anti-parallel Diodes are not required for reverse conduction.

- For optimal efficiency Dead Time should be minimized, with Synchronous Rectification operation.

#### GaN blocking voltage

- GaN E-HEMT Blocking Voltage (BVDS) is defined by the value of Drain Leakage Current (IDSS). Hard Breakdown (unrecoverable) will occur above the Rated BVDS value, similar to Si MOSFET or IGBT. As a general practice, the applied Drain voltage should be de-rated in a similar manner as Si MOSFET or IGBT.

- All GaN power transistors do not Avalanche and thus do not have an Avalanche Breakdown Rating.

- The maximum Drain-to-Source Rating does not change if negative Gate voltage is applied.

### Full-Bridge or 3-phase operation

GS-EVM-DRG-100VR7-GS2 can easily be interleaved for Full-Bridge or 3-phase operation by using a Controller IC with multiple PWM outputs and separate Control Loops.

#### **Boost mode operation**

- For Boost Mode operation, Start-Up Timing is critical due to the fact that when Low Side Gate is "H" level as VCC clears POR, a short circuit path can be created: Input voltage → Inductor → LS GaN → GND. Start-Up Sequence for VCC must assert LAST during Power On Reset (POR), and de-assert FIRST during Power Off.

- GS-EVM-DRG-100VR7-GS2 can easily be interleaved for Full-Bridge or 3-phase operation by using a Controller IC with multiple PWM outputs and separate Control Loops.

#### Dead time design and operation

- Typical Delay Matching Time is 1.5ns which limits minimum Dead Time to 1.5ns, however, at least a

10ns Dead Time is recommended for switching reliability. Because the Dual PWM DrGaN version has

HI and LI PWM inputs, switching control is feasible especially in ZVS Mode and in Pulse Skip or power

save mode during light load operation.

- In ZVS operation, controlling Dead Time low-to-high (Tdt,LH) can be achieved using output inductor and the Coss of the GaN Switch to generate a resonant period, using HI and LI to adjust Tdt,LH.

### Thermal design

- DrGaN μModule designed using PowerCore™ technology has ultra-low Thermal Resistance Junction-to-Case. GS-EVM-DRG-100V7R-GS2 has R<sub>®\_JUNC-CASE</sub> value < 0.6 °C/W, many times lower than other DrGaN solutions.</li>

- The GaN E-mode devices in GS-EVM-DRG-100V7R-GS2 are Rated to  $T_{JUNC}$  = 150 °, however, the DrGaN  $\mu$ Module and integrated Gate Driver circuit have a Normal Operating temperature range of -40 °C to +105 0°C.

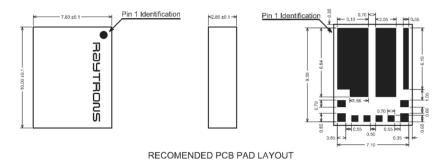

#### PCB layout

GS-EVM-DRG-100V7R-GS2 is designed to accommodate the high dV/dt of GaN switches, and commutation and gate loop inductances are ultra-low. Additionally, R<sub>⊕JUNC-CASE</sub> is ultra-low, allowing tight Layout and small Footprint. PCB Layout example is shown below. *Utilize multiple Via's to connect PCB Power and GND Planes to the DrGaN Pads*.

Figure 4 PCB Layout Example

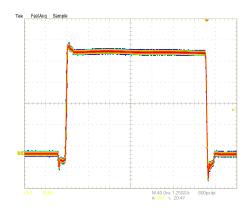

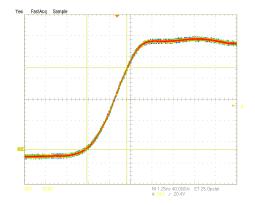

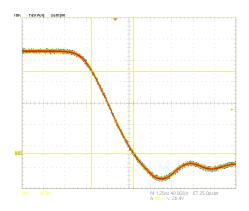

### **Typical Switching Waveforms**

(48V  $V_{IN}$ , Duty Cycle = 25%,  $I_{OUT}$  = 10A, 1GHz B.W. measurement)

Figure 5 Switching Node (10V per Division)

Figure 6 Rise Time (10V per Division)

Figure 7 Fall Time (10V per Division)

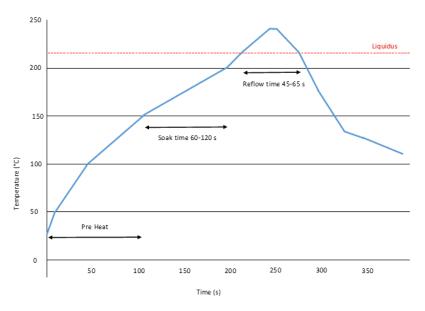

### **SMT** manufacturing

IPC/JEDED J-STD Reflow Profile is recommended for Surface Mount (SMT) manufacturing

Figure 8 SMT Manufacturing

# **Electrical Specifications**

All Parameters listed apply to each GaN Device in the DrGaN Half-Bridge power stage

| Parameter                                                                            | Sym.                 | Min.   | Тур.     | Max.     | Unit   | Conditions                                                                                                                            |  |

|--------------------------------------------------------------------------------------|----------------------|--------|----------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>IN</sub> to V <sub>SW</sub> , and V <sub>SW</sub> to PGND<br>Blocking Voltage | BV <sub>DS</sub>     | 100    | -        | -        | V      | $I_{DSS}$ = 50 $\mu$ A, $V_{GS}$ = 0 $V$                                                                                              |  |

| Drain to Source ON Resistance                                                        | R <sub>DS(ON)</sub>  | -      | 7        | 9.5      | mΩ     | T <sub>JUNC</sub> = 25 °C, I <sub>DS</sub> = 36 A                                                                                     |  |

| Drain to Source ON Resistance                                                        | R <sub>DS(ON)</sub>  | -      | 16.8     | -        | mΩ     | T <sub>JUNC</sub> = 150 °C, I <sub>DS</sub> = 36 A                                                                                    |  |

| Drain to Source Leakage Current                                                      | $I_{	extsf{DSS}}$    | -      | 0.5      | 50       | μΑ     | $V_{DS} = 100 \text{ V}, V_{GS} = 0 \text{ V},$ $T_{JUNC} = 25  {}^{0}\text{C}$                                                       |  |

| Drain to Source Leakage Current                                                      | I <sub>DSS</sub>     | -      | 100      | -        | μΑ     | $V_{DS} = 100 \text{ V}, V_{GS} = 0 \text{ V},$ $T_{JUNC} = 150  ^{0}\text{C}$                                                        |  |

| Switching Characteristics (e                                                         | each GaN             | Device | in the I | Half-Bri | dge po | wer stage):                                                                                                                           |  |

| Input Capacitance                                                                    | C <sub>ISS</sub>     | -      | 588      | -        | pF     | V <sub>DS</sub> = 50 V                                                                                                                |  |

| Output Capacitance                                                                   | Coss                 | -      | 254      | -        | pF     | $V_{GS} = 0 V$                                                                                                                        |  |

| Reverse Transfer Capacitance                                                         | $C_{RSS}$            | -      | 9.9      | -        | pF     | f = 1 MHz                                                                                                                             |  |

| Total Gate Charge                                                                    | $Q_{G\_TOT}$         | -      | 12       | -        | nC     | V <sub>DS</sub> = 50V                                                                                                                 |  |

| Gate to Source Charge                                                                | $Q_{GS}$             | -      | 4.5      | -        | nC     | $V_{GS} = 0 \text{ V to } 6.0 \text{ V}$ $I_{DS} = 80 \text{ A}$                                                                      |  |

| Gate to Drain Charge                                                                 | $Q_{GD}$             | -      | 1.5      | -        | nC     |                                                                                                                                       |  |

| Output Charge                                                                        | Qoss                 | -      | 21.3     | -        | nC     | V <sub>DS</sub> = 50 V, V <sub>GS</sub> = 0 V                                                                                         |  |

| Reverse Recovery Charge                                                              | $Q_{RR}$             | -      | Zero     | -        | nC     |                                                                                                                                       |  |

| Turn-On Prop Delay                                                                   | t <sub>PD(ON)</sub>  | -      | 15       | -        | ns     |                                                                                                                                       |  |

| Rise Time (Driver)                                                                   | t <sub>RISE</sub>    | -      | 4        | -        | ns     | $V_{IN} = 48 \text{ V} \text{ and } V_{OUT} = 5 \text{ V}$<br>$I_{DS} = 20 \text{ A}, V_{GS} = 0 \text{ V} \text{ to } 6.0 \text{ V}$ |  |

| Turn-Off Prop Delay                                                                  | t <sub>PD(OFF)</sub> | -      | 15       | 20       | ns     | $R_{GATE\_ON\_HS/LS} = 2.2 \Omega$                                                                                                    |  |

| Fall Time (Driver)                                                                   | t <sub>FALL</sub>    | -      | 4        | -        | ns     | $R_{GATE\_OFF\_HS/LS} = 0 \Omega$<br>$C_{LOAD} = C_{ISS} = 588 \text{ pF}$                                                            |  |

| Prop Delay Matching (Dual PWM)                                                       | t <sub>PD(HB)</sub>  | -      | 1.5      | -        | ns     | LICAD - CISS - 388 PF                                                                                                                 |  |

| Driver Block Characteristics:                                                        |                      |        |          |          |        |                                                                                                                                       |  |

| UVLO High Threshold                                                                  | UVLO <sub>HI</sub>   | 3.8    | 4.0      | 4.2      | V      | VCC to GND, Rising Edge                                                                                                               |  |

| UVLO Hysteresis                                                                      | UVLO <sub>HYS</sub>  | -      | 350      | -        | mV     | VCC to GND                                                                                                                            |  |

| PWM High Threshold (Single PWM)                                                      | PWM <sub>HI</sub>    | 2.0    | 2.2      | 2.4      | V      | PWM to GND, Rising Edge                                                                                                               |  |

| PWM Low Threshold (Single PWM)      | PWM <sub>LO</sub>        | 0.8 | 1.0  | 1.2  | V    | PWM to GND, Falling Edge                                                                                           |

|-------------------------------------|--------------------------|-----|------|------|------|--------------------------------------------------------------------------------------------------------------------|

| PWM Tri-State (Single PWM)          | PWM <sub>TRI</sub>       | 1.2 | 1.6  | 2.0  | V    | PWM to GND, Tri-State                                                                                              |

| Tri-State S/D Hold-Off (Single PWM) | TRI <sub>OFF</sub>       | -   | 25   | 40   | ns   | Time to Shut-Down during T/S                                                                                       |

| PWM Input Current (Single PWM)      | $I_{PWM}$                | -   | -120 | -240 | μΑ   | PWM = 0V                                                                                                           |

|                                     |                          | -   | 120  | 240  |      | PWM = 3.3V                                                                                                         |

|                                     |                          | -   | 120  | 240  |      | PWM = 5V                                                                                                           |

| PWM High Threshold (Dual PWM)       | PWM <sub>HI</sub>        | 2.3 | -    | -    | V    | PWM to GND, Rising Edge                                                                                            |

| PWM Low Threshold (Dual PWM)        | PWM <sub>LO</sub>        | -   | -    | 0.5  | V    | PWM to GND, Falling Edge                                                                                           |

| PWM Pull-Down (Dual PWM)            | R <sub>PWM</sub>         | -   | 200  | -    | kΩ   |                                                                                                                    |

| PWM Hysteresis (Dual PWM)           | PWM <sub>HYS</sub>       | -   | 400  | -    | mV   | PWM to GND                                                                                                         |

| Driver Latch-Up Immunity            | $\Delta V_{	ext{LATCH}}$ | -   | -    | 100  | V/ns | $V_{IN}$ = 48 V and $V_{OUT}$ = 5 V $I_{DS}$ = 20 A, $V_{GS}$ = 0 V to 6.0 V $C_{LOAD}$ = 588 pF, $F_{SW}$ = 1 MHz |

| Driver-side Quiescent Current       | $I_{CC(Q)}$              | -   | 550  | 1000 | μΑ   | RP007U1, PWM = 0V                                                                                                  |

|                                     |                          | -   | 120  | -    | μΑ   | RP007U2, PWM = 0V                                                                                                  |

# Mechanical Drawings

<sup>\*</sup>All dimensions are in units mm.

\*General tolerance is 0.05mm unless otherwise noted.

Figure 9 Mechanical Drawing

#### **Evaluation Board/kit Important Notice**

GaN Systems Inc. (GaN Systems) provides the enclosed product(s) under the following AS IS conditions:

This evaluation board/kit being sold or provided by GaN Systems is intended for use for ENGINEERING DEVELOPMENT, DEMONSTRATION, and OR EVALUATION PURPOSES ONLY and is not considered by GaN Systems to be a finished end-product fit for general consumer use. As such, the goods being sold or provided are not intended to be complete in terms of required design-, marketing-, and/or manufacturing-related protective considerations, including but not limited to product safety and environmental measures typically found in end products that incorporate such semiconductor components or circuit boards. This evaluation board/kit does not fall within the scope of the European Union directives regarding electromagnetic compatibility, restricted substances (RoHS), recycling (WEEE), FCC, CE or UL, and therefore may not meet the technical requirements of these directives, or other related regulations.

If this evaluation board/kit does not meet the specifications indicated in the Technical Manual, the board/kit may be returned within 30 days from the date of delivery for a full refund. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY THE SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. EXCEPT TO THE EXTENT OF THIS INDEMNITY, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user indemnifies GaN Systems from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge.

No License is granted under any patent right or other intellectual property right of GaN Systems whatsoever. GaN Systems assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or any other intellectual property rights of any kind.

GaN Systems currently services a variety of customers for products around the world, and therefore this transaction **is not exclusive**.

Please read the Technical Manual and, specifically, the Warnings and Restrictions notice in the Technical Manual prior to handling the product. Persons handling the product(s) must have electronics training and observe good engineering practice standards.

This notice contains important safety information about temperatures and voltages. For further safety concerns, please contact a GaN Systems' application engineer.

In Canada:

GaN Systems Inc. 1145 Innovation Drive Suite 101 Ottawa, Ontario, Canada K2K 3G8 T+1613-686-1996 In Europe:

GaN Systems Ltd., German Branch Terminalstrasse Mitte 18, 85356 München, Germany T +49 (o) 8165 9822 7260 In the United States:

GaN Systems Corp. 2723 South State Street, Suite 150, Ann Arbor, MI. USA 48104 T+1 248-609-7643

#### www.gansystems.com

Important Notice — Unless expressly approved in writing by an authorized representative of GaN Systems, GaN Systems components are not designed, authorized or warranted for use in lifesaving, life sustaining, military, aircraft, or space applications, nor in products or systems where failure or malfunction may result in personal injury, death, or property or environmental damage. The information given in this document shall not in any event be regarded as a guarantee of performance. GaN Systems hereby disclaims any or all warranties and liabilities of any kind, including but not limited to warranties of non-infringement of intellectual property rights. All other brand and product names are trademarks or registered trademarks of their respective owners. Information provided herein is intended as a guide only and is subject to change without notice. The information contained herein or any use of such information does not grant, explicitly, or implicitly, to any party any patent rights, licenses, or any other intellectual property rights. General Sales and Terms Conditions apply.

© 2009-2020 GaN Systems Inc. All rights reserved.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

GaN Systems:

GS-EVM-DRG-100V7R-GS2