# NAND Flash Memory

## MT29F2G08ABAEAH4, MT29F2G08ABAEAWP, MT29F2G08ABBEAH4 MT29F2G08ABBEAHC, MT29F2G16ABAEAWP, MT29F2G16ABBEAH4 MT29F2G16ABBEAHC

## **Features**

- Open NAND Flash Interface (ONFI) 1.0-compliant<sup>1</sup>

- Single-level cell (SLC) technology

- Organization

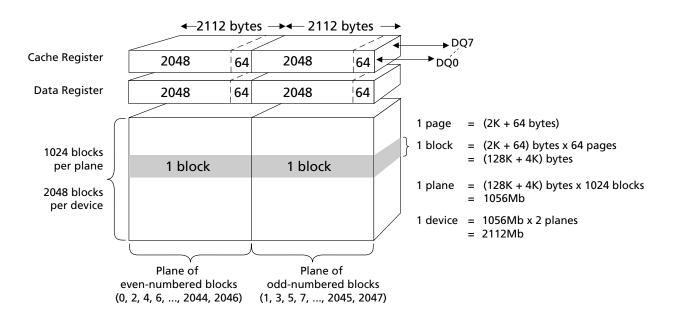

- Page size x8: 2112 bytes (2048 + 64 bytes)

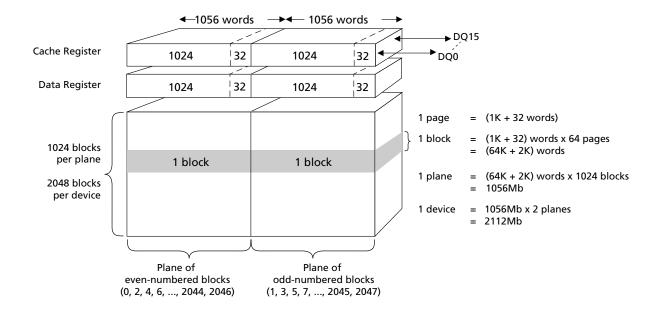

- Page size x16: 1056 words (1024 + 32 words)

- Block size: 64 pages (128K + 4K bytes)

- Plane size: 2 planes x 1024 blocks per plane

- Device size: 2Gb: 2048 blocks

- Asynchronous I/O performance - <sup>t</sup>RC/<sup>t</sup>WC: 20ns (3.3V), 25ns (1.8V)

- Array performance

- Read page: 25µs<sup>3</sup>

- Program page: 200µs (TYP: 1.8V, 3.3V)<sup>3</sup>

- Erase block: 700µs (TYP)

- Command set: ONFI NAND Flash Protocol

- Advanced command set

- Program page cache mode<sup>4</sup>

- Read page cache mode<sup>4</sup>

- One-time programmable (OTP) mode

- Two-plane commands<sup>4</sup>

- Interleaved die (LUN) operations

- Read unique ID

- Block lock (1.8V only)

- Internal data move

- Operation status byte provides software method for detecting

- Operation completion

- Pass/fail condition

- Write-protect status

- Ready/Busy# (R/B#) signal provides a hardware method of detecting operation completion

- WP# signal: Write protect entire device

- · First block (block address 00h) is valid when shipped from factory with ECC. For minimum required ECC, see Error Management.

- Block 0 requires 1-bit ECC if PROGRAM/ERASE cycles are less than 1000

- RESET (FFh) required as first command after power-on

- · Alternate method of device initialization (Nand Init) after power up (contact factory)

- Internal data move operations supported within the plane from which data is read

- Quality and reliability

- Data retention: 10 years

- Endurance: 100,000 PROGRAM/ERASE cycles

- Operating voltage range

- V<sub>CC</sub>: 2.7-3.6V

- V<sub>CC</sub>: 1.7-1.95V

- Operating temperature

- Commercial: 0°C to +70°C

- Industrial (IT): -40°C to +85°C \_

- Automotive Industrial (AIT): -40°C to +85°C

- Automotive (AAT): -40°C to +105°C

- Package

- 48-pin TSOP type 1, CPL<sup>2</sup>

- 63-ball VFBGA

- Notes: 1. The ONFI 1.0 specification is available at www.onfi.org.

- 2. CPL = Center parting line.

- 3. See Electrical Specifications Program/Erase Characteristics for <sup>t</sup>R ECC and <sup>t</sup>PROG ECC specifications.

- 4. These commands supported only with ECC disabled.

1

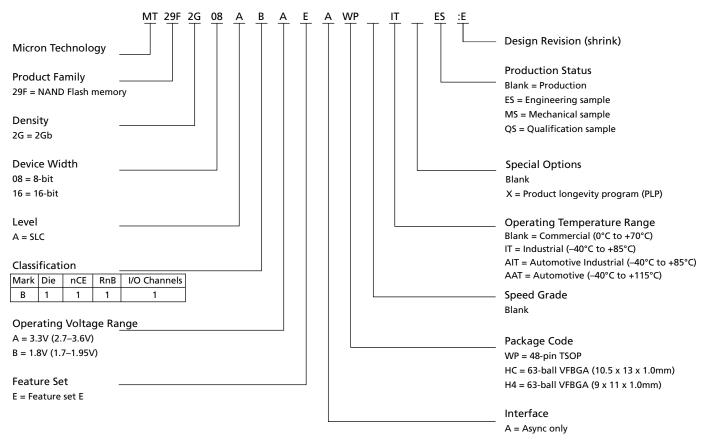

## **Part Numbering Information**

Micron NAND Flash devices are available in different configurations and densities. Verify valid part numbers by using Micron's part catalog search at www.micron.com. To compare features and specifications by device type, visit www.micron.com/products. Contact the factory for devices not found.

#### **Figure 1: Marketing Part Number Chart**

## Contents

| General Description                   |    |

|---------------------------------------|----|

| Signal Descriptions                   |    |

| Signal Assignments                    |    |

| Package Dimensions                    |    |

| Architecture                          | 15 |

| Device and Array Organization         | 16 |

| Asynchronous Interface Bus Operation  |    |

| Asynchronous Enable/Standby           | 18 |

| Asynchronous Commands                 | 18 |

| Asynchronous Addresses                | 20 |

| Asynchronous Data Input               |    |

| Asynchronous Data Output              |    |

| Write Protect#                        | 23 |

| Ready/Busy#                           |    |

| Device Initialization                 | 28 |

| Command Definitions                   | 29 |

| Reset Operations                      | 32 |

| RESET (FFh)                           |    |

| Identification Operations             | 33 |

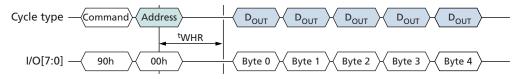

| READ ID (90h)                         |    |

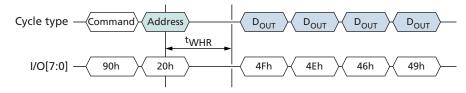

| READ ID Parameter Tables              | 34 |

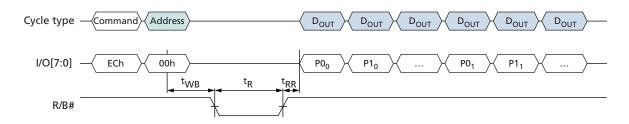

| READ PARAMETER PAGE (ECh)             |    |

| Parameter Page Data Structure Tables  |    |

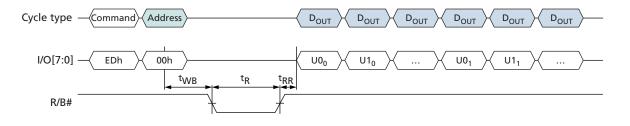

| READ UNIQUE ID (EDh)                  |    |

| Feature Operations                    | 42 |

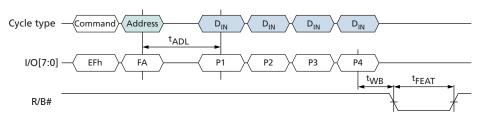

| SET FEATURES (EFh)                    |    |

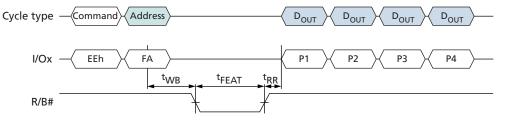

| GET FEATURES (EEh)                    |    |

| Status Operations                     |    |

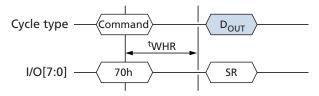

| READ STATUS (70h)                     |    |

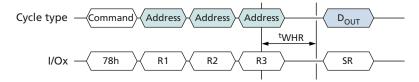

| READ STATUS ENHANCED (78h)            | 48 |

| Column Address Operations             |    |

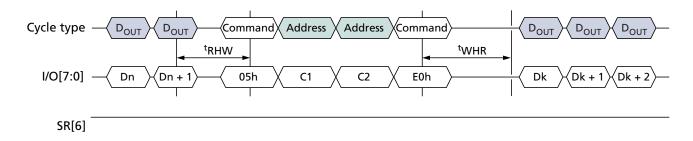

| RANDOM DATA READ (05h-E0h)            |    |

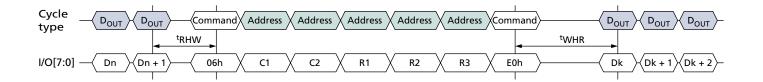

| RANDOM DATA READ TWO-PLANE (06h-E0h)  |    |

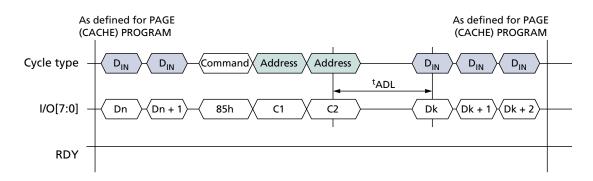

| RANDOM DATA INPUT (85h)               |    |

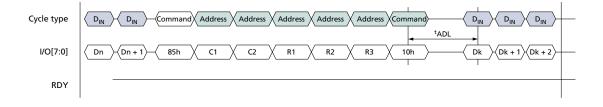

| PROGRAM FOR INTERNAL DATA INPUT (85h) |    |

| Read Operations                       |    |

| READ MODE (00h)                       |    |

| READ PAGE (00h-30h)                   |    |

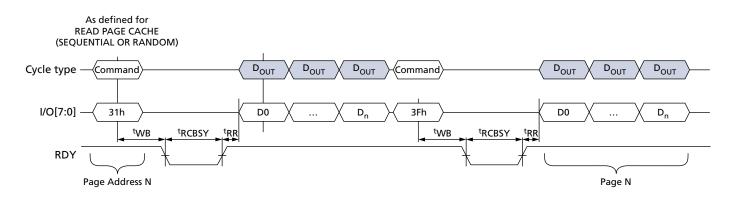

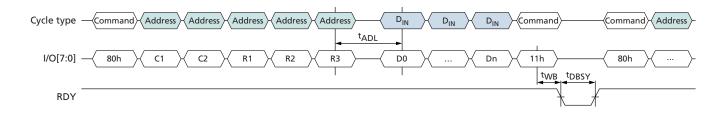

| READ PAGE CACHE SEQUENTIAL (31h)      |    |

| READ PAGE CACHE RANDOM (00h-31h)      |    |

| READ PAGE CACHE LAST (3Fh)            |    |

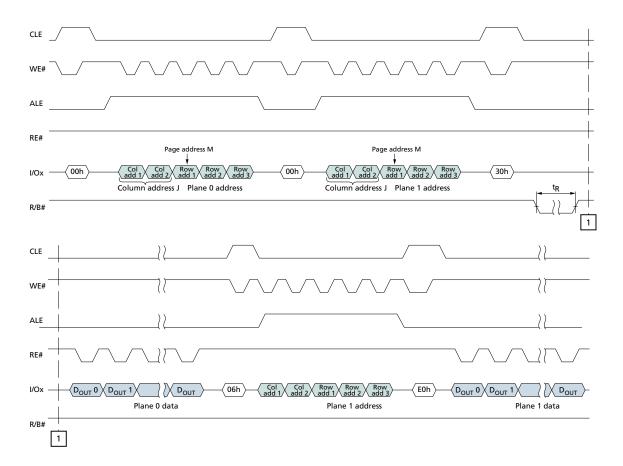

| READ PAGE TWO-PLANE 00h-00h-30h       |    |

| Program Operations                    |    |

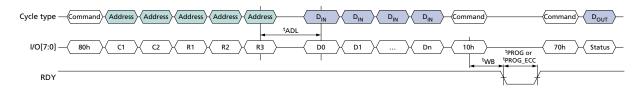

| PROGRAM PAGE (80h-10h)                |    |

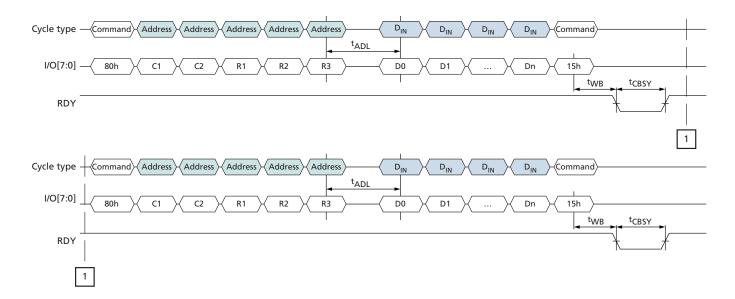

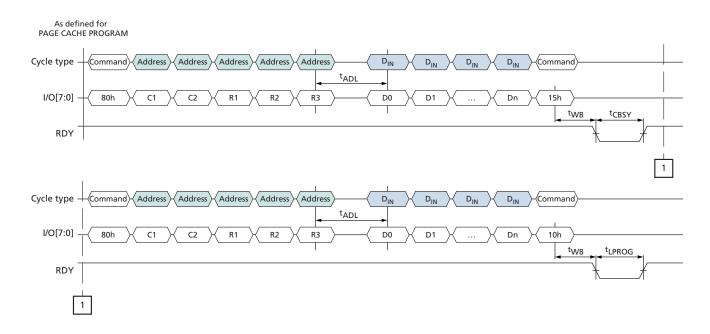

| PROGRAM PAGE CACHE (80h-15h)          |    |

| PROGRAM PAGE TWO-PLANE (80h-11h)      |    |

| Erase Operations                      |    |

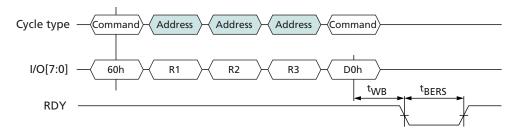

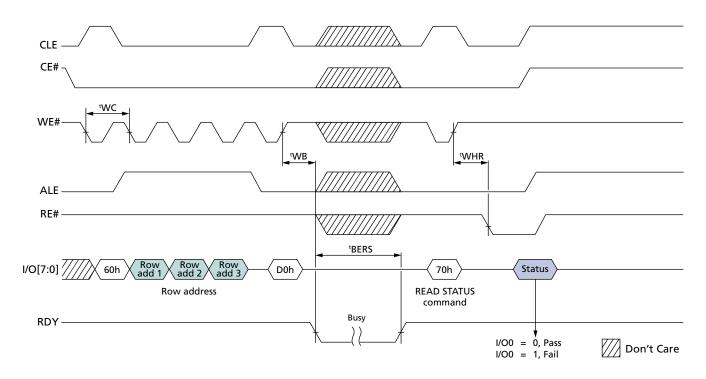

| ERASE BLOCK (60h-D0h)                 |    |

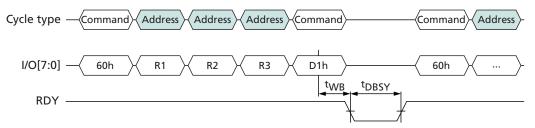

| ERASE BLOCK TWO-PLANE (60h-D1h)       |    |

| Internal Data Move Operations         | 72 |

| READ FOR INTERNAL DATA MOVE (000-35h)         73           PROGRAM FOR INTERNAL DATA MOVE (85h-10h)         74           PROGRAM FOR INTERNAL DATA MOVE (85h-10h)         75           Block Lock Feature         76           WP# and Block Lock         76           UNLOCK (23h-24h)         76           DOCK TIGHT (2Ch)         80           BLOCK TIGHT (2Ch)         80           BLOCK TIGHT (2Ch)         81           One-Time Programmable (OTP) Operations         83           Legacy OTP Commands         83           Legacy OTP Commands         83           OTP DATA PROGRAM (80h-10h)         84           RANDOM DATA INPUT (85h)         85           OTP DATA PROGRAM (80h-10h)         88           Two-Plane Addressing         90           Interleaved Die (Multi-LUN) Operations         90           Interleaved Die (Multi-LUN) Operations         90           Ectrical Specifications - DC Characteristics and Operating Conditions         100           Electrical Specifications - DC Characteristics and Operating Conditions         106           Electrical Specifications - DC Characteristics and Operating Conditions         106           Electrical Specifications - DC Characteristics and Operating Conditions         104           Rev. R - 04/14 <th></th> <th>=0</th>     |                                                                           | =0  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|

| PROGRAM FOR INTERNAL DATA MOVE TWO-PLANE (85h-11h)         75           Block Lock Feature         76           WP# and Block Lock         76           UNLOCK (23h-24h)         76           LOCK (2Ah)         79           LOCK TIGHT (2Ch)         80           BLOCK LOCK RAD STATUS (7Ah)         81           Done-Time Programmable (OTP) Operations         83           Legacy OTP Commands         83           Orb DATA PROGRAM (80h-10h)         84           ANNDOM DATA INPUT (85h)         85           OTP DATA PROTECT (80h-10)         86           OTP DATA READ (00h-30h)         86           Two-Plane Operations         90           Two-Plane Addressing         90           Two-Plane Addressing         90           Forror Management         100           Interleaved Die (Multi-LUN) Operations         99           Electrical Specifications – DC Characteristics and Operating Conditions         106           Electrical Specifications – DC Characteristics and Operating Conditions         108           Electrical Specifications – DC Characteristics and Operating Conditions         108           Electrical Specifications – Program/Erase Characteristics         111           Asynchronous Interface Timing Diagrams         124                                           |                                                                           |     |

| Block Lock Feature       76         WP# and Block Lock       76         UNLOCK (23h-24h)       76         LOCK CK (2Ah)       79         DOCK TIGHT (2Ch)       80         BLOCK LOCK READ STATUS (7Ah)       80         DOCK TIGHT (2Ch)       81         Done-Time Programmable (OTP) Operations       83         OTP DATA PROGRAM (80h-10h)       84         RANDOM DATA INPUT (85h)       85         OTP DATA READ (00h-30h)       86         Two-Plane Operations       90         Two-Plane Operations       90         Two-Plane Operations       90         Terror Management       100         Interleaved Dic (Multi-UN) Operations.       90         Electrical Specifications – DC Characteristics and Operating Conditions       104         Electrical Specifications – DC Characteristics and Operating Conditions       108         Electrical Specifications – DC Characteristics and Operating Conditions       111         Asynchronous Interface Timing Diagrams       112         Rev R - 04/14       124         Rev N - 02/12                                                                                                                                         |                                                                           |     |

| WP# and Block Lock         76           UNLOCK (23h-24h)         76           LOCK (2Ah)         79           LOCK TIGHT (2Ch)         80           BLOCK KEAD STATUS (7Ah)         81           One-Time Programmable (OTP) Operations         83           Orp DATA PROGRAM (80h-10h)         84           RANDOM DATA INPUT (85h)         85           OTP DATA PROFICT (80h-10)         86           Two-Plane Operations         90           Two-Plane Operations         90           Two-Plane Operations         90           Two-Plane Adressing         90           Interleaved Die (Multi-LUN) Operations         99           Error Management         100           Interlaved Die (Multi-LUN) Operations         99           Electrical Specifications - DC Characteristics and Operating Conditions         104           Electrical Specifications - NC Characteristics and Operating Conditions         108           Electrical Specifications - NC Characteristics and Operating Conditions         108           Electrical Specifications - NC Characteristics and Operating Conditions         108           Electrical Specifications - Program/Erase Characteristics         111           Asynchronous Interface Timing Diagrams         112           Revision History </td <td></td> <td></td> |                                                                           |     |

| UNLOCK (23h-24h)         76           LOCK TICHT (2Ch)         80           BLOCK ICHT (2Ch)         81           One-Time Programmable (OTP) Operations         83           Legacy OTP Commands         83           OTP DATA PROGRAM (80h-10h)         84           RANDOM DATA INPUT (85h)         85           OTP DATA PROTECT (80h-10h)         86           TOTP DATA PROTECT (80h-10h)         86           Two-Plane Operations         90           Two-Plane Addressing         90           Two-Plane Addressing         90           Two-Plane Addressing         90           Internal ECC and Spare Area Mapping for ECC         100           Electrical Specifications - DC Characteristics and Operating Conditions         104           Electrical Specifications - AC Characteristics and Operating Conditions         108           Electrical Specifications - AC Characteristics and Operating Conditions         108           Electrical Specifications - AC Characteristics and Operating Conditions         104           Rev R = 04/14         124           Rev Q = 02/14         124           Rev N = 06/13         124           Rev N = 01/12         124           Rev M = 01/12         124           Rev N = 01/12                                                                     |                                                                           |     |

| LOCK (2Ah)         79           LOCK TIGHT (2Ch)         80           BLOCK LOCK READ STATUS (7Ah)         81           One-Time Programmable (OTP) Operations         83           Legacy OTP Commands         83           OTP DATA PROGRAM (80h-10h)         84           RANDOM DATA INPUT (85h)         85           OTP DATA PROTECT (80h-10h)         86           OTP DATA READ (00h-30h)         86           Two-Plane Operations         90           Two-Plane Addressing         90           Interalezed Die (Multi-LUN) Operations         99           Error Management         100           Internal ECC and Spare Area Mapping for ECC         102           Electrical Specifications - DC Characteristics and Operating Conditions         108           Electrical Specifications - AC Characteristics and Operating Conditions         108           Electrical Specifications - Program/Erase Characteristics         111           Asynchronous Interface Timing Diagrams         112           Revision History         124           Rev Q - 02/14         124           Rev N - 04/14         124           Rev N - 04/12         124           Rev N - 04/14         124           Rev N - 04/14         124                                                                                    |                                                                           |     |

| LOCK TIGHT (2Ch)         80           BLOCK LOCK READ STATUS (7Ah)         81           One-Time Programmable (OTP) Operations         83           Legacy OTP Commands         83           OTP DATA PROGRAM (80h-10h)         84           ANDOM DATA INPUT (85h)         85           OTP DATA PROTECT (80h-10)         86           OTP DATA READ (00h-30h)         86           OTP DATA READ (00h-30h)         88           Two-Plane Addressing         90           Two-Plane Addressing         90           Two-Plane Addressing         90           Interleaved Die (Multi-IUN) Operations         100           Internal ECC and Spare Area Mapping for ECC         102           Electrical Specifications – DC Characteristics and Operating Conditions         106           Electrical Specifications – DC Characteristics and Operating Conditions         108           Electrical Specifications – Program/Erase Characteristics         111           Revision Histo                        |                                                                           |     |

| BLOCK LOCK READ STATUS (7Ah)       81         One-Time Programmable (OTP) Operations       83         OTP DATA PROGRAM (80h-10h)       84         RANDOM DATA INPUT (85h)       85         OTP DATA PROTECT (80h-10)       86         OTP DATA PROTECT (80h-10)       86         OTP DATA READ (00h-30h)       88         Two-Plane Operations       90         Two-Plane Addressing       90         Interleaved Die (Multi-LUN) Operations       99         Error Management       100         Internal ECC and Spare Area Mapping for ECC       102         Electrical Specifications – DC Characteristics and Operating Conditions       104         Electrical Specifications – DC Characteristics and Operating Conditions       108         Electrical Specifications – Program/Erase Characteristics       111         Asynchronous Interface Timing Diagrams       112         Revison History       124         Rev. R – 04/14       124         Rev. N – 02/12       124         Rev. N – 02/12       124         Rev. K – 01/11       124         Rev. K – 01/11       124         Rev. K – 01/11       124         Rev. H – 09/10       125         Rev. K – 08/10       125      <                                                                                                                             |                                                                           |     |

| One-Time Programmable (OTP) Operations       83         Legacy OTP Commands       83         OTP DATA PROGRAM (80h-10h)       84         RANDOM DATA INPUT (85h)       85         OTP DATA READ (00h-30h)       86         OTP DATA READ (00h-30h)       86         Two-Plane Operations       90         Two-Plane Operations       90         Two-Plane Addressing       90         Interleaved Die (Multi-LUN) Operations       99         Error Management       100         Interleaved Die (Multi-LUN) Operations       100         Interleaved Die (Multi-LUN) Operations       100         Electrical Specifications – DC Characteristics and Operating Conditions       104         Electrical Specifications – DC Characteristics and Operating Conditions       108         Electrical Specifications – POC Characteristics and Operating Conditions       108         Electrical Specifications – POC Characteristics       111         Asynchronous Interface Timing Diagrams       112         Rev. R - 04/14       124         Rev. P - 08/13       124         Rev. N - 01/12       124         Rev. M - 01/12       124         Rev. M - 01/12       124         Rev. M - 01/12       124         Rev.                                                                                                      |                                                                           |     |

| Legacy OTP Commands       83         OTP DATA PROGRAM (80h-10h)       84         RANDOM DATA INPUT (85h)       85         OTP DATA PROTECT (80h-10)       86         OTP DATA READ (00h-30h)       88         Two-Plane Operations       90         Two-Plane Addressing       90         Internleaved Die (Multi-LUN) Operations       99         Error Management       100         Internal ECC and Spare Area Mapping for ECC       102         Electrical Specifications       104         Electrical Specifications – DC Characteristics and Operating Conditions       106         Electrical Specifications – AC Characteristics and Operating Conditions       108         Electrical Specifications – Program/Erase Characteristics       111         Asynchronous Interface Timing Diagrams       112         Rev R - 04/14       124         Rev Q - 02/14       124         Rev N - 08/13       124         Rev N - 02/12       124         Rev N - 01/12       124         Rev K - 01/11       124         Rev K - 01/12       124         Rev M - 01/12 <t< td=""><td></td><td></td></t<>                                                                                                                     |                                                                           |     |

| OTP DATA PROGRAM (80h-10h)       84         RANDOM DATA INPUT (85h)       85         OTP DATA PROTECT (80h-10)       86         OTP DATA READ (00h-30h)       88         Two-Plane Operations       90         Two-Plane Addressing       90         Interleaved Die (Multi-LUN) Operations       99         Error Management       100         Interleaved Die (Multi-LUN) Operations       99         Electrical Specifications       104         Electrical Specifications       104         Electrical Specifications       104         Electrical Specifications – DC Characteristics and Operating Conditions       108         Electrical Specifications – AC Characteristics and Operating Conditions       108         Electrical Specifications – Program/Erase Characteristics       111         Asynchronous Interface Timing Diagrams       112         Revision History       124         Rev. R - 04/14       124         Rev. N - 02/12       124         Rev. N - 02/12       124         Rev. N - 01/12       124         Rev. L - 11/11       124         Rev. L - 01/12       124         Rev. K - 01/11       124         Rev. K - 01/11       124         Rev.                                                                                                                                         |                                                                           |     |

| RANDOM DATA INPUT (85h)       85         OTP DATA PROTECT (80h-10)       86         OTP DATA READ (00h-30h)       88         Two-Plane Operations       90         Two-Plane Addressing       90         Interleaved Die (Multi-LUN) Operations       99         Error Management       100         Internal ECC and Spare Area Mapping for ECC       102         Electrical Specifications – DC Characteristics and Operating Conditions       106         Electrical Specifications – AC Characteristics and Operating Conditions       108         Electrical Specifications – Program/Erase Characteristics       111         Asynchronous Interface Timing Diagrams       112         Revision History       124         Rev. Q - 02/14       124         Rev. N - 02/12       124         Rev. N - 02/12       124         Rev. K - 01/12       124         Rev. K - 01/11       124         Rev. K - 01/11       124         Rev. H - 09/10       125         Rev. F - 06/10       125                                                                                                                                                           |                                                                           |     |

| OTP DATA PROTECT (80h-10)         86           OTP DATA READ (00h-30h)         88           Two-Plane Operations         90           Two-Plane Addressing         90           Interleaved Die (Multi-LUN) Operations         99           Error Management         100           Internal ECC and Spare Area Mapping for ECC         102           Electrical Specifications         DC Characteristics and Operating Conditions         106           Electrical Specifications – DC Characteristics and Operating Conditions         108         112           Reverstright         124         124         124           Rev. R – 04/14         124         124         124           Rev. Q – 02/14         124         124         124           Rev. N – 04/13         124         124         124           Rev. N – 01/12         124 <td></td> <td></td>                                                                                                   |                                                                           |     |

| OTP DATA READ (00h-30h)         88           Two-Plane Operations         90           Two-Plane Addressing         90           Interleaved Die (Multi-LUN) Operations         99           Error Management         100           Internal ECC and Spare Area Mapping for ECC         102           Electrical Specifications         104           Electrical Specifications – DC Characteristics and Operating Conditions         106           Electrical Specifications – AC Characteristics and Operating Conditions         108           Electrical Specifications – Program/Erase Characteristics         111           Asynchronous Interface Timing Diagrams         112           Rev. R – 04/14         124           Rev. Q – 02/14         124           Rev. P – 08/13         124           Rev. N – 02/12         124           Rev. N – 01/12         124           Rev. N – 01/12         124           Rev. L – 11/11         124           Rev. L – 11/11         124           Rev. J – 12/10         124           Rev. J – 12/10         124           Rev. L – 11/11         124           Rev. J – 12/10         124           Rev. J – 12/10         125           Rev. K – 06/10 <td< td=""><td></td><td></td></td<>                                                                           |                                                                           |     |

| Two-Plane Operations       90         Two-Plane Addressing       90         Interleaved Die (Multi-LUN) Operations       99         Error Management       100         Internal ECC and Spare Area Mapping for ECC       102         Electrical Specifications – DC Characteristics and Operating Conditions       104         Electrical Specifications – DC Characteristics and Operating Conditions       108         Electrical Specifications – AC Characteristics and Operating Conditions       111         Asynchronous Interface Timing Diagrams       112         Rev. R – 04/14       124         Rev. Q – 02/14       124         Rev. P – 08/13       124         Rev. N – 02/12       124         Rev. M – 01/12       124         Rev. L – 11/11       124         Rev. K – 01/12       124         Rev. L – 11/10       124         Rev. L – 11/10       124         Rev. J – 12/10       124         Rev. H – 09/10       124         Rev. H – 09/10       125         Rev. E – 05/10       125         Rev. E – 05/10       125         Rev. C – 01/10       125         Rev. C – 01/10       125         Rev. C – 01/10       125 <tr< td=""><td></td><td></td></tr<>                                                                                                                                     |                                                                           |     |

| Two-Plane Addressing       90         Intereleaved Die (Multi-LUN) Operations       99         Error Management       100         Internal ECC and Spare Area Mapping for ECC       102         Electrical Specifications       104         Electrical Specifications – DC Characteristics and Operating Conditions       106         Electrical Specifications – AC Characteristics and Operating Conditions       108         Electrical Specifications – Program/Erase Characteristics       111         Asynchronous Interface Timing Diagrams       112         Rev R – 04/14       124         Rev. Q – 02/14       124         Rev. Q – 04/14       124         Rev. N – 01/12       124         Rev. K – 01/11       124         Rev. N – 01/12       124         Rev. K – 01/11       124         Rev. K – 01/11       124         Rev. K – 01/11       124         Rev. M – 01/12       124         Rev. J – 12/10       124                                                                                                                                                                                 |                                                                           |     |

| Interleaved Die (Multi-LUN) Operations       99         Error Management       100         Internal ECC and Spare Area Mapping for ECC       102         Electrical Specifications – DC Characteristics and Operating Conditions       106         Electrical Specifications – DC Characteristics and Operating Conditions       108         Electrical Specifications – AC Characteristics and Operating Conditions       108         Electrical Specifications – Program/Erase Characteristics       111         Asynchronous Interface Timing Diagrams       112         Rev. R – 04/14       124         Rev. Q – 02/14       124         Rev. P – 08/13       124         Rev. N – 02/12       124         Rev. N – 01/12       124         Rev. N – 01/12       124         Rev. L – 11/11       124         Rev. K – 01/11       124         Rev. J – 12/10       124         Rev. J – 12/10       124         Rev. F – 06/10       125         Rev. F – 06/10       125         Rev. F – 05/10       125         Rev. E – 05/10       125         Rev. D – 03/10                                                                                                                                                  | 1                                                                         |     |

| Error Management       100         Internal ECC and Spare Area Mapping for ECC       102         Electrical Specifications       104         Electrical Specifications – DC Characteristics and Operating Conditions       106         Electrical Specifications – AC Characteristics and Operating Conditions       108         Electrical Specifications – AC Characteristics and Operating Conditions       108         Electrical Specifications – Program/Erase Characteristics       111         Asynchronous Interface Timing Diagrams       112         Rev. R – 04/14       124         Rev. Q – 02/14       124         Rev. Q – 02/14       124         Rev. N – 08/13       124         Rev. N – 02/12       124         Rev. N – 02/12       124         Rev. N – 01/12       124         Rev. N – 01/12       124         Rev. N – 01/12       124         Rev. K – 01/11       124         Rev. G – 08/10       124         Rev. G – 08/10       125         Rev. F – 06/10       125         Rev. F – 06/10       125 </td <td></td> <td></td>                                                                                                                           |                                                                           |     |

| Internal ECC and Spare Area Mapping for ECC       102         Electrical Specifications       104         Electrical Specifications – DC Characteristics and Operating Conditions       106         Electrical Specifications – AC Characteristics and Operating Conditions       108         Electrical Specifications – Program/Erase Characteristics       111         Asynchronous Interface Timing Diagrams       112         Revision History       124         Rev. R – 04/14       124         Rev. P – 08/13       124         Rev. P – 08/13       124         Rev. N – 02/12       124         Rev. N – 02/12       124         Rev. N – 02/12       124         Rev. K – 01/12       124         Rev. K – 01/11       124         Rev. K – 01/10       124         Rev. H – 09/10       124         Rev. H – 09/10       124         Rev. G – 08/10       125         Rev. E – 05/10       125         Rev. E – 05/10                                                                                                                                                                                      |                                                                           |     |

| Electrical Specifications       104         Electrical Specifications – DC Characteristics and Operating Conditions       106         Electrical Specifications – AC Characteristics and Operating Conditions       108         Electrical Specifications – Program/Erase Characteristics       111         Asynchronous Interface Timing Diagrams       112         Revision History       124         Rev. R – 04/14       124         Rev. Q – 02/14       124         Rev. O – 08/13       124         Rev. N – 02/12       124         Rev. N – 02/12       124         Rev. N – 01/12       124         Rev. K – 01/11       124         Rev. K – 01/12       124         Rev. J – 12/10       124         Rev. H – 09/10       124         Rev. H – 09/10       124         Rev. G – 08/10       125         Rev. F – 06/10       125         Rev. F – 05/10       125         Rev. C – 01/10       125         Rev. N – 03/10       125         Rev. N – 03/10       125                                                                                                                                                                                                                                                                                                                                             | Error Management 1                                                        | .00 |

| Electrical Specifications – DC Characteristics and Operating Conditions       106         Electrical Specifications – AC Characteristics and Operating Conditions       108         Electrical Specifications – Program/Erase Characteristics       111         Asynchronous Interface Timing Diagrams       112         Revision History       124         Rev. R – 04/14       124         Rev. Q – 02/14       124         Rev. Q – 02/14       124         Rev. N – 04/12       124         Rev. N – 02/12       124         Rev. N – 02/12       124         Rev. N – 01/12       124         Rev. K – 01/11       124         Rev. I – 12/10       124         Rev. H – 09/10       124         Rev. F – 06/10       125         Rev. F – 06/10       125         Rev. F – 05/10       125         Rev. D – 03/10       125         Rev. C – 01/10       125         Rev. B – 09/09       125 <td></td> <td></td>                                                                                                                                                                                                |                                                                           |     |

| Electrical Specifications – AC Characteristics and Operating Conditions       108         Electrical Specifications – Program/Erase Characteristics       111         Asynchronous Interface Timing Diagrams       112         Revision History       124         Rev. R – 04/14       124         Rev. P – 08/13       124         Rev. O – 10/12       124         Rev. N – 02/12       124         Rev. N – 02/12       124         Rev. K – 01/11       124         Rev. K – 01/12       124         Rev. K – 01/11       124         Rev. I – 12/10       124         Rev. I – 11/10       124         Rev. G – 08/10       125         Rev. F – 06/10       125         Rev. E – 05/10       125         Rev. D – 03/10       125         Rev. C – 01/10       125         Rev. B – 09/09       125                                                                                                                                                                                                                                                                             | Electrical Specifications 1                                               | .04 |

| Electrical Specifications – Program/Erase Characteristics       111         Asynchronous Interface Timing Diagrams       112         Revision History       124         Rev. R – 04/14       124         Rev. Q – 02/14       124         Rev. P – 08/13       124         Rev. N – 01/12       124         Rev. N – 02/12       124         Rev. N – 02/12       124         Rev. N – 01/12       124         Rev. N – 01/11       124         Rev. K – 01/11       124         Rev. J – 12/10       124         Rev. I – 11/10       124         Rev. H – 09/10       125         Rev. G – 08/10       125         Rev. F – 06/10       125         Rev. C – 01/10       125         Rev. C – 01/10       125         Rev. B – 09/09       125                                                                                                                                                                                                                                                                                                                                                                       | Electrical Specifications – DC Characteristics and Operating Conditions 1 | .06 |

| Asynchronous Interface Timing Diagrams       112         Revision History       124         Rev. R - 04/14       124         Rev. Q - 02/14       124         Rev. P - 08/13       124         Rev. N - 02/12       124         Rev. N - 02/12       124         Rev. M - 01/12       124         Rev. M - 01/12       124         Rev. M - 01/12       124         Rev. K - 01/11       124         Rev. K - 01/11       124         Rev. J - 12/10       124         Rev. I - 11/10       124         Rev. H - 09/10       124         Rev. G - 08/10       125         Rev. E - 05/10       125         Rev. E - 05/10       125         Rev. C - 01/10       125         Rev. C - 01/10       125         Rev. B - 09/09       125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Electrical Specifications – AC Characteristics and Operating Conditions 1 | .08 |

| Revision History124Rev. R - 04/14124Rev. Q - 02/14124Rev. Q - 02/14124Rev. P - 08/13124Rev. N - 01/12124Rev. N - 02/12124Rev. M - 01/12124Rev. K - 01/11124Rev. K - 01/11124Rev. J - 12/10124Rev. H - 09/10124Rev. F - 06/10125Rev. F - 05/10125Rev. C - 01/10125Rev. C - 01/10125Rev. C - 01/10125Rev. B - 09/09125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                           |     |

| Rev. R - $04/14$ 124         Rev. Q - $02/14$ 124         Rev. P - $08/13$ 124         Rev. O - $10/12$ 124         Rev. N - $02/12$ 124         Rev. M - $01/12$ 124         Rev. L - $11/11$ 124         Rev. K - $01/11$ 124         Rev. J - $12/10$ 124         Rev. I - $11/10$ 124         Rev. I - $09/10$ 124         Rev. H - $09/10$ 124         Rev. F - $06/10$ 125         Rev. E - $05/10$ 125         Rev. E - $05/10$ 125         Rev. C - $01/10$ 125         Rev. C - $01/10$ 125         Rev. B - $09/09$ 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |     |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                           |     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                           |     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                           |     |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                           |     |

| Rev. E - 05/10       125         Rev. D - 03/10       125         Rev. C - 01/10       125         Rev. B - 09/09       125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Rev. G – 08/10 1                                                          | .25 |

| Rev. D - 03/10       125         Rev. C - 01/10       125         Rev. B - 09/09       125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Rev. F – 06/10                                                            | .25 |

| Rev. C – 01/10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Rev. E – 05/10                                                            | .25 |

| Rev. B – 09/09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Rev. D – 03/10 1                                                          | .25 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |     |

| Boy A 07/09 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |     |

| Rev. A = 07/05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Rev. A – 07/09                                                            | .25 |

## List of Tables

|            | Signal Definitions                                            |     |

|------------|---------------------------------------------------------------|-----|

| Table 2:   | Array Addressing – MT29F2G08 (x8)                             | 16  |

| Table 3:   | Array Addressing – MT29F2G16 (x16)                            | 17  |

| Table 4:   | Asynchronous Interface Mode Selection                         | 18  |

|            | Command Set                                                   |     |

|            | Two-Plane Command Set                                         |     |

| Table 7: 1 | READ ID Parameters for Address 00h                            | 34  |

| Table 8:   | READ ID Parameters for Address 20h                            | 35  |

|            | Parameter Page Data Structure                                 |     |

| Table 10:  | Feature Address Definitions                                   | 42  |

| Table 11:  | Feature Address 90h – Array Operation Mode                    | 43  |

|            | Feature Addresses 01h: Timing Mode                            |     |

| Table 13:  | Feature Addresses 80h: Programmable I/O Drive Strength        | 46  |

| Table 14:  | Feature Addresses 81h: Programmable R/B# Pull-Down Strength   | 46  |

| Table 15:  | Status Register Definition                                    | 47  |

| Table 16:  | Block Lock Address Cycle Assignments                          | 78  |

|            | Block Lock Status Register Bit Definitions                    |     |

|            | Error Management Details 1                                    |     |

| Table 19:  | Absolute Maximum Ratings 1                                    | 04  |

| Table 20:  | Recommended Operating Conditions 1                            | 04  |

| Table 21:  | Valid Blocks 1                                                | 04  |

| Table 22:  | Capacitance 1                                                 | 05  |

|            | Test Conditions 1                                             |     |

|            | DC Characteristics and Operating Conditions (3.3V) 1          |     |

|            | DC Characteristics and Operating Conditions (1.8V) 1          |     |

| Table 26:  | AC Characteristics: Command, Data, and Address Input (3.3V) 1 | 08  |

| Table 27:  | AC Characteristics: Command, Data, and Address Input (1.8V) 1 | 08  |

| Table 28:  | AC Characteristics: Normal Operation (3.3V) 1                 | 109 |

| Table 29:  | AC Characteristics: Normal Operation (1.8V) 1                 | 09  |

| Table 30:  | Program/Erase Characteristics 1                               | 11  |

|            |                                                               |     |

## **List of Figures**

| Figure 1: 1 | Marketing Part Number Chart                                                                                              | . 2 |

|-------------|--------------------------------------------------------------------------------------------------------------------------|-----|

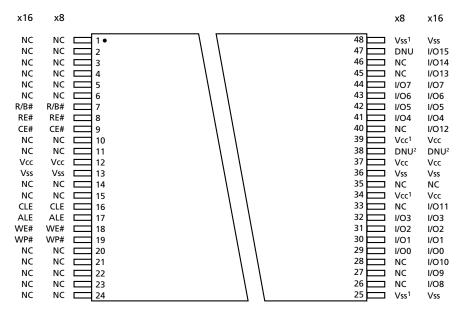

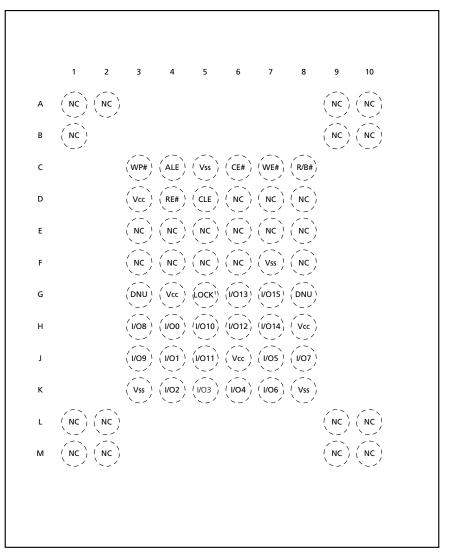

|             | 48-Pin TSOP – Type 1, CPL (Top View)                                                                                     |     |

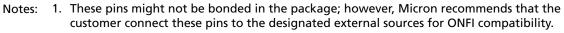

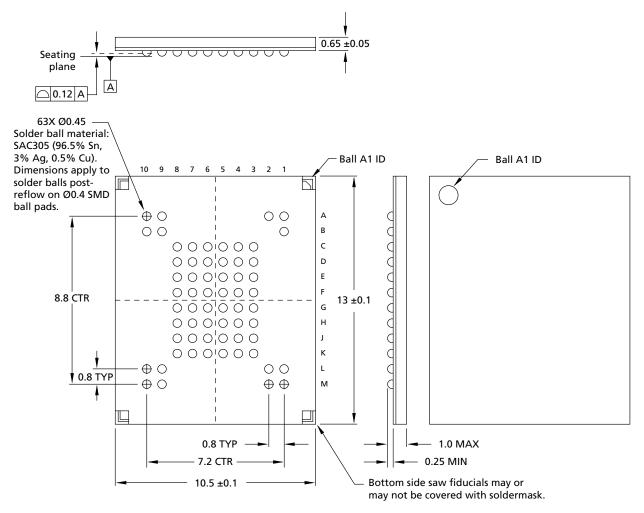

| Figure 3: 6 | 63-Ball VFBGA, x8 (Balls Down, Top View)                                                                                 | 10  |

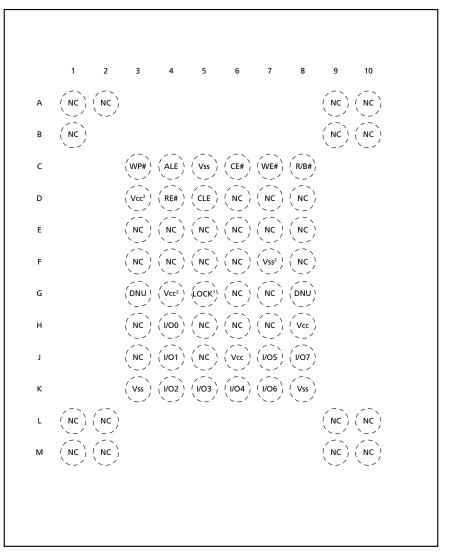

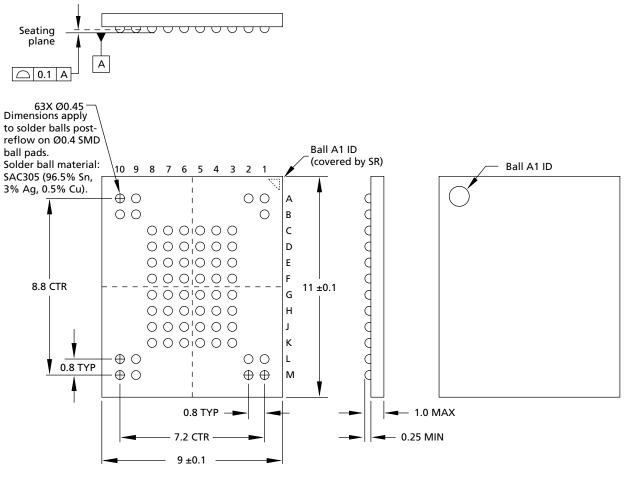

| Figure 4: 6 | 53-Ball VFBGA, x16 (Balls Down, Top View)                                                                                | 11  |

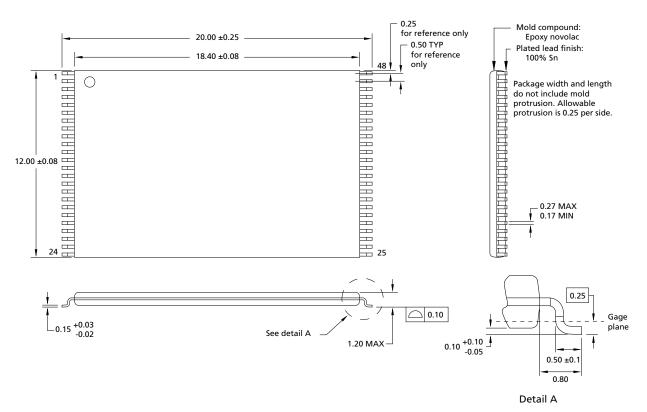

| Figure 5: 4 | 48-Pin TSOP – Type 1, CPL                                                                                                | 12  |

| Figure 6: 6 | 63-Ball VFBGA (10.5mm x 13mm)                                                                                            | 13  |

| Figure 7: 6 | 53-Ball VFBGA (9mm x 11mm)                                                                                               | 14  |

| Figure 8: 1 | NAND Flash Die (LUN) Functional Block Diagram                                                                            | 15  |

| Figure 9: A | Array Organization – MT29F2G08 (x8)                                                                                      | 16  |

| Figure 10:  | Array Organization – MT29F2G16 (x16)                                                                                     | 17  |

|             | Asynchronous Command Latch Cycle                                                                                         |     |

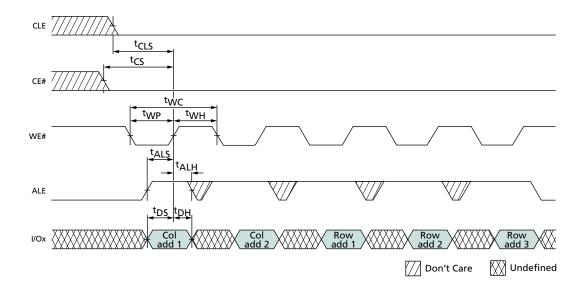

| Figure 12:  | Asynchronous Address Latch Cycle                                                                                         | 20  |

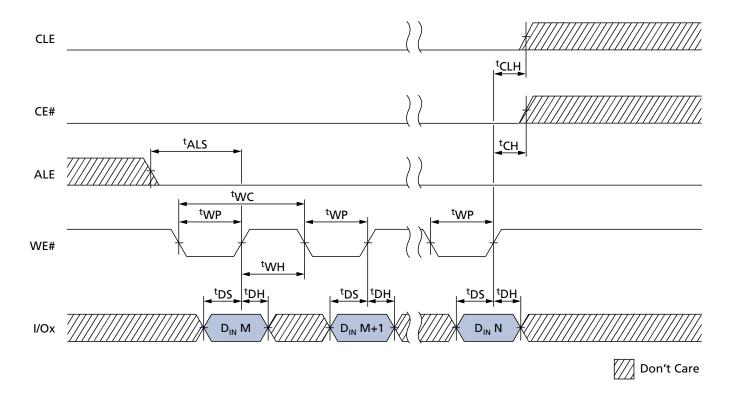

| Figure 13:  | Asynchronous Data Input Cycles                                                                                           | 21  |

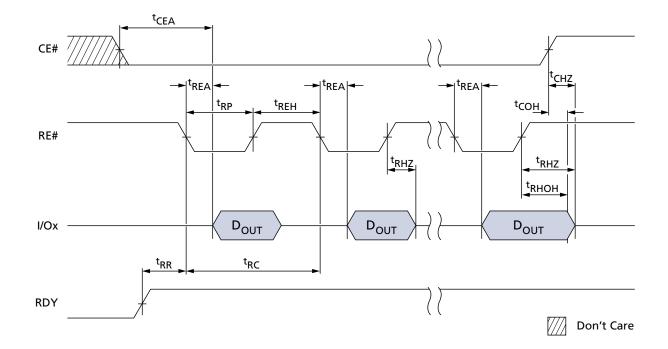

|             | Asynchronous Data Output Cycles                                                                                          |     |

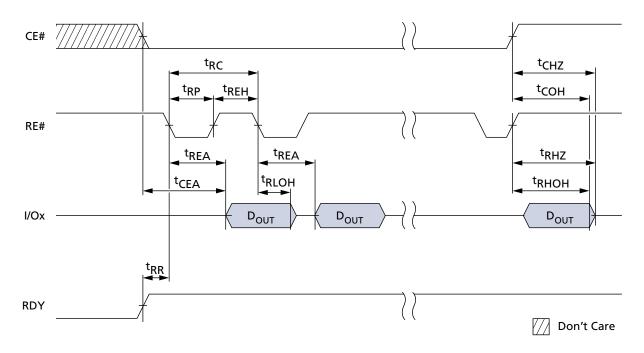

|             | Asynchronous Data Output Cycles (EDO Mode)                                                                               |     |

|             | READ/BUSY# Open Drain                                                                                                    |     |

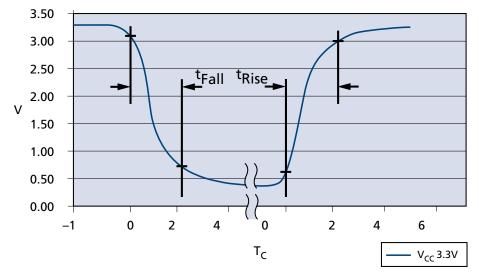

|             | <sup>t</sup> Fall and <sup>t</sup> Rise (3.3VV <sub>CC</sub> )                                                           |     |

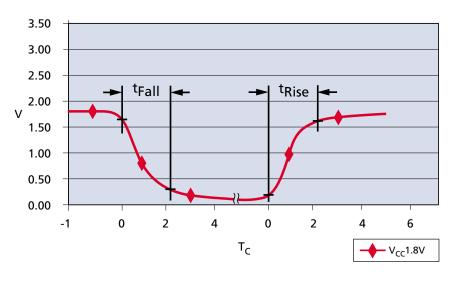

|             | <sup>t</sup> Fall and <sup>t</sup> Rise (1.8VV <sub>CC</sub> )                                                           |     |

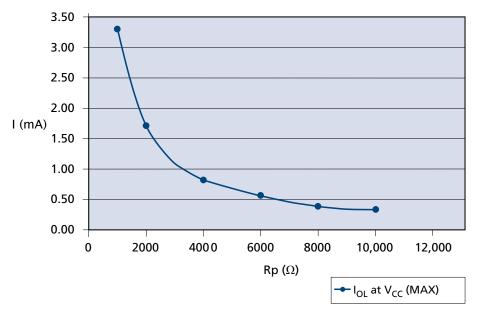

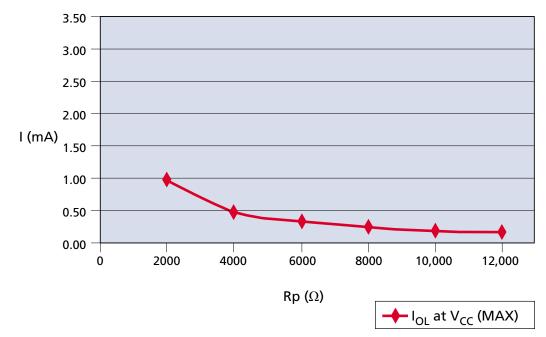

|             | $I_{OL}$ vs. Rp ( $V_{CC} = 3.3VV_{CC}$ )                                                                                |     |

| Figure 20:  | $I_{OL}$ vs. Rp (1.8VV <sub>CC</sub> )                                                                                   | 26  |

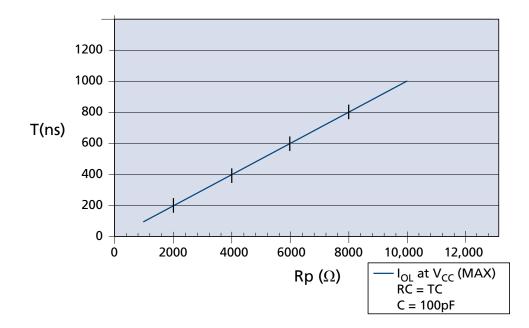

| Figure 21:  | TC vs. Rp                                                                                                                | 27  |

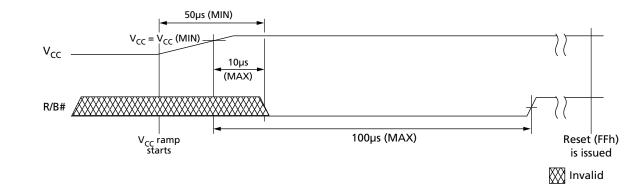

|             | R/B# Power-On Behavior                                                                                                   |     |

|             | RESET (FFh) Operation                                                                                                    |     |

|             | READ ID (90h) with 00h Address Operation                                                                                 |     |

|             | READ ID (90h) with 20h Address Operation                                                                                 |     |

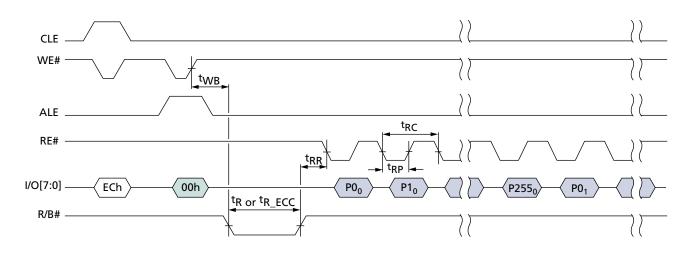

|             | READ PARAMETER (ECh) Operation                                                                                           |     |

|             | READ UNIQUE ID (EDh) Operation                                                                                           |     |

|             | SET FEATURES (EFh) Operation                                                                                             |     |

|             | GET FEATURES (EEh) Operation                                                                                             |     |

| Figure 30:  | READ STATUS (70h) Operation                                                                                              | 48  |

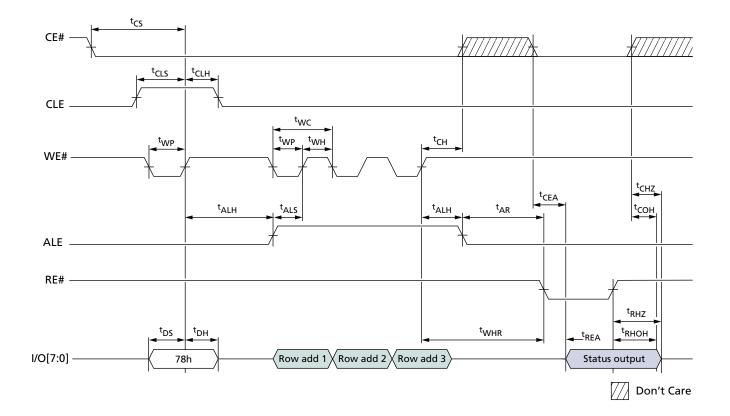

|             | READ STATUS ENHANCED (78h) Operation                                                                                     |     |

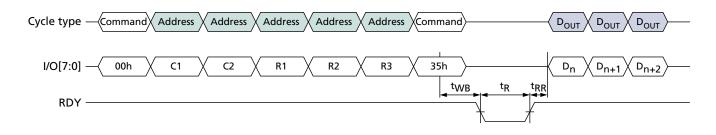

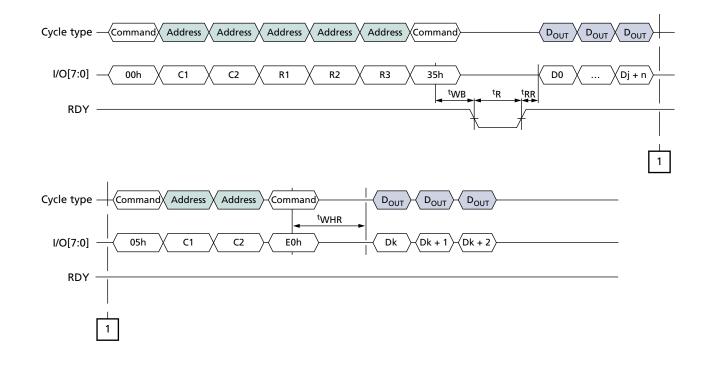

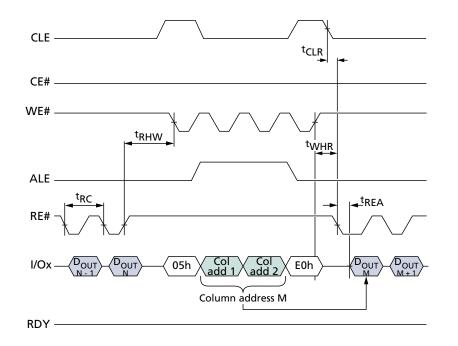

|             | RANDOM DATA READ (05h-E0h) Operation                                                                                     |     |

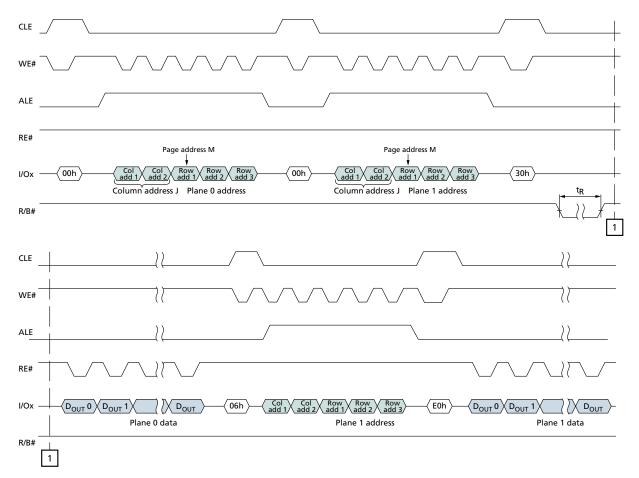

|             | RANDOM DATA READ TWO-PLANE (06h-E0h) Operation                                                                           |     |

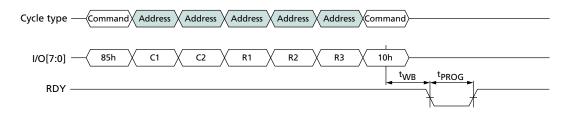

| Figure 34:  | RANDOM DATA INPUT (85h) Operation                                                                                        | 52  |

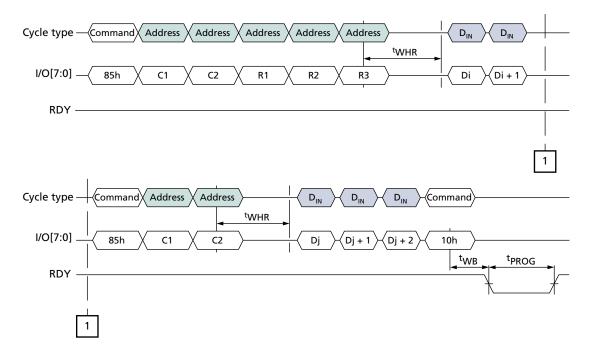

| Figure 35:  | PROGRAM FOR INTERNAL DATA INPUT (85h) Operation                                                                          | 54  |

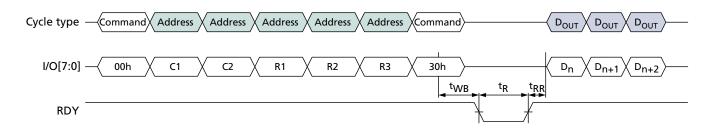

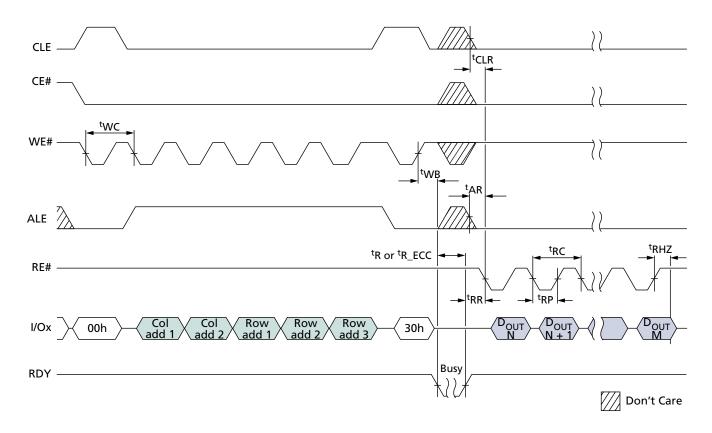

| Figure 36   | READ PAGE (00h-30h) Operation                                                                                            | 58  |

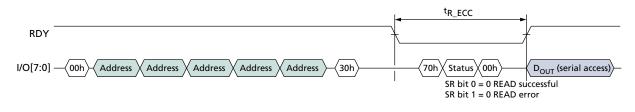

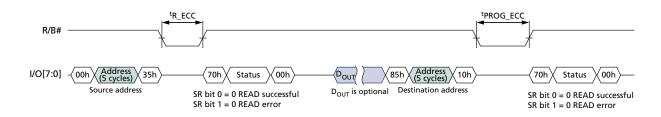

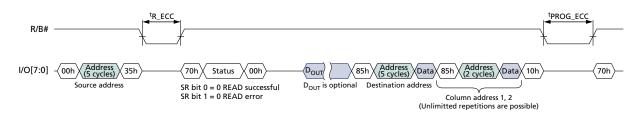

| Figure 37   | READ PAGE (00h-30h) Operation with Internal ECC Enabled                                                                  | 58  |

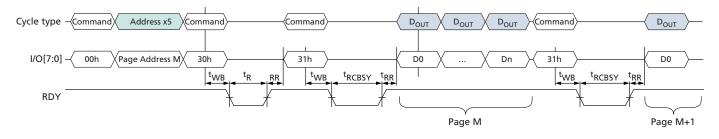

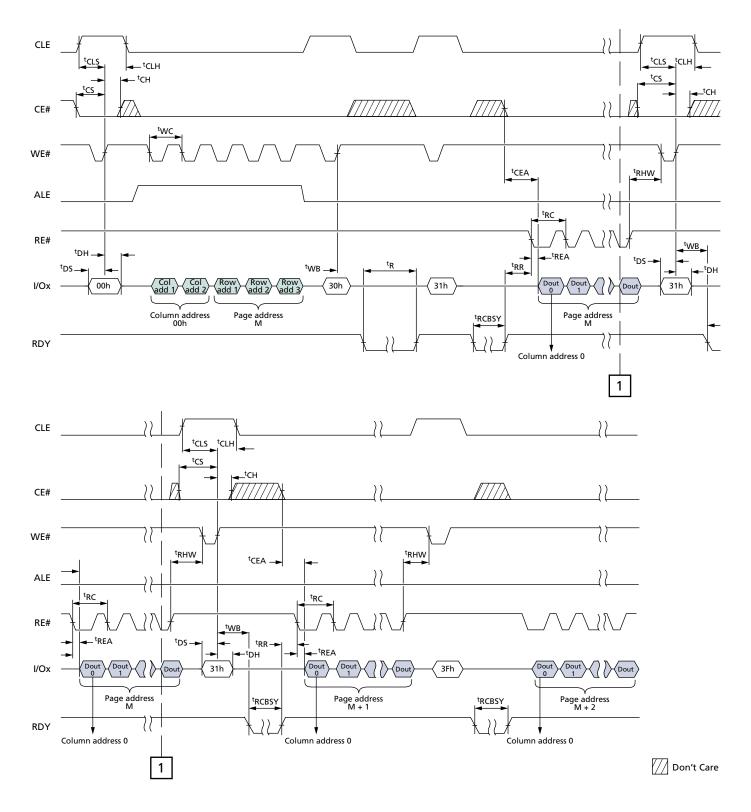

|             | READ PAGE CACHE SEQUENTIAL (31h) Operation                                                                               |     |

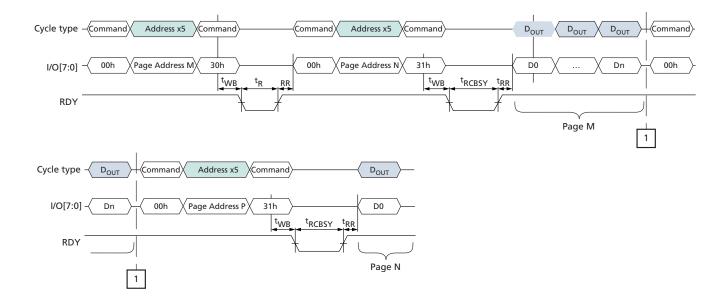

|             | READ PAGE CACHE RANDOM (00h-31h) Operation                                                                               |     |

| 0           | READ PAGE CACHE LAST (3Fh) Operation                                                                                     |     |

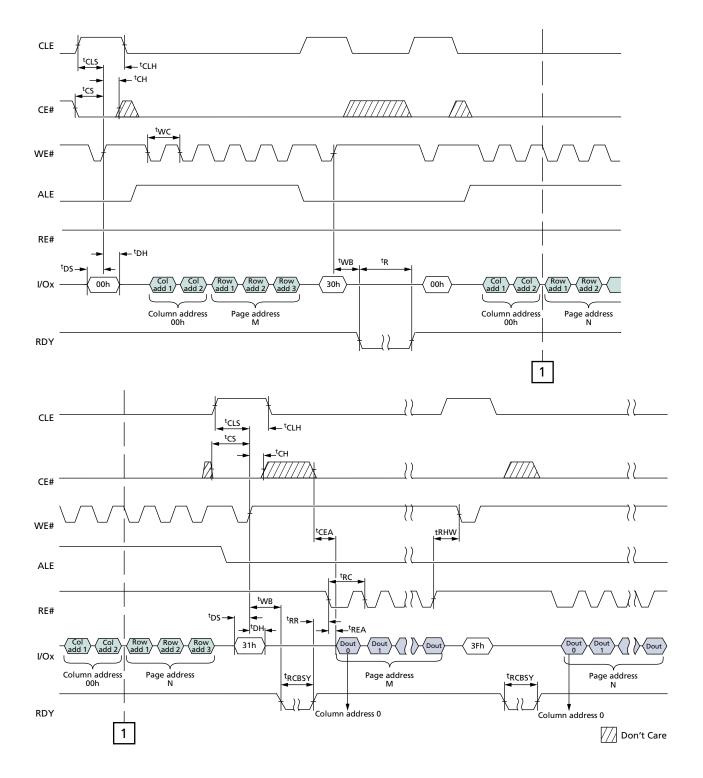

|             | READ PAGE TWO-PLANE (00h-00h-30h) Operation                                                                              |     |

|             | PROGRAM PAGE (80h-10h) Operation                                                                                         |     |

|             | PROGRAM PAGE CACHE (80h–15h) Operation (Start)                                                                           |     |

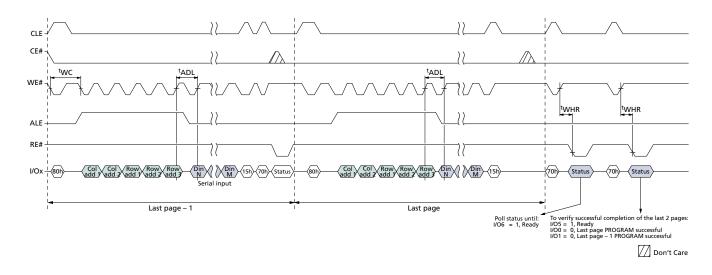

|             | PROGRAM PAGE CACHE (80h–15h) Operation (End)                                                                             |     |

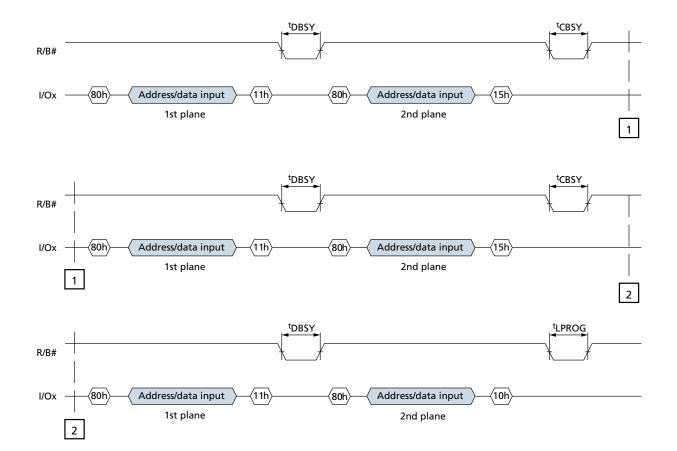

|             | PROGRAM PAGE TWO-PLANE (80h–11h) Operation                                                                               |     |

|             | ERASE BLOCK (60h-D0h) Operation                                                                                          |     |

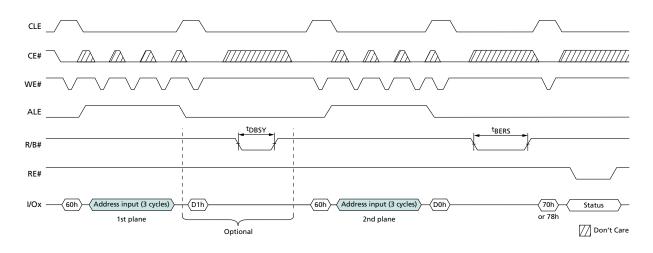

|             | ERASE BLOCK (60h-D0h) Operation<br>ERASE BLOCK TWO-PLANE (60h–D1h) Operation                                             |     |

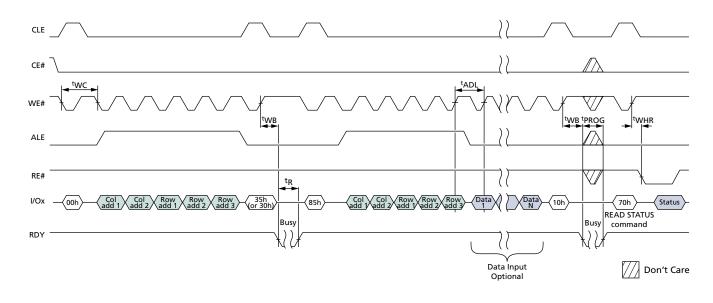

|             | READ FOR INTERNAL DATA MOVE (00h-35h) Operation                                                                          |     |

|             | READ FOR INTERNAL DATA MOVE (001-35h) Operation<br>READ FOR INTERNAL DATA MOVE (00h–35h) with RANDOM DATA READ (05h–E0h) |     |

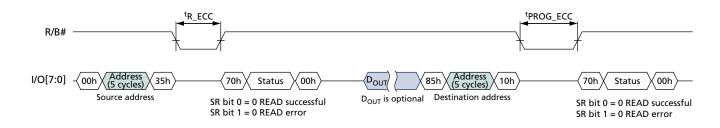

|             | INTERNAL DATA MOVE (001–351) with RANDOM DATA READ (051–601)                                                             |     |

| rigure 50:  | INTERIVAL DATA MOVE (05II-10II) WIII IIITEITIAI ECC EIIADIEU                                                             | 14  |

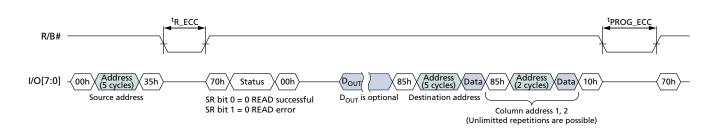

| Figure 51:  | INTERNAL DATA MOVE (85h-10h) with RANDOM DATA INPUT with Internal ECC Enabled                                                           | 74         |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------|

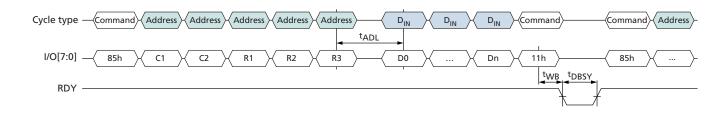

|             | PROGRAM FOR INTERNAL DATA MOVE (85h–10h) Operation                                                                                      |            |

|             | PROGRAM FOR INTERNAL DATA MOVE (85h-10h) with RANDOM DATA INPUT (85h)                                                                   |            |

|             | PROGRAM FOR INTERNAL DATA MOVE TWO-PLANE (85h-11h) Operation                                                                            |            |

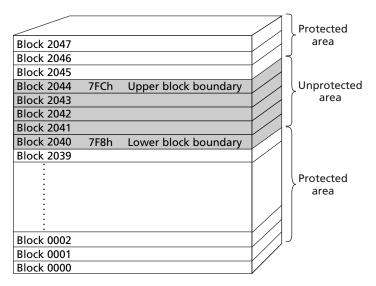

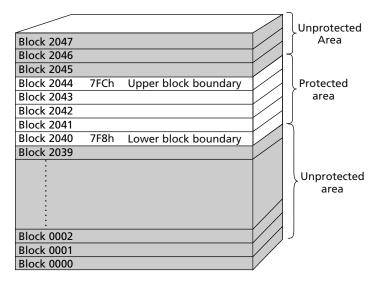

|             | Flash Array Protected: Invert Area Bit = 0                                                                                              |            |

|             | Flash Array Protected: Invert Area Bit = 1                                                                                              |            |

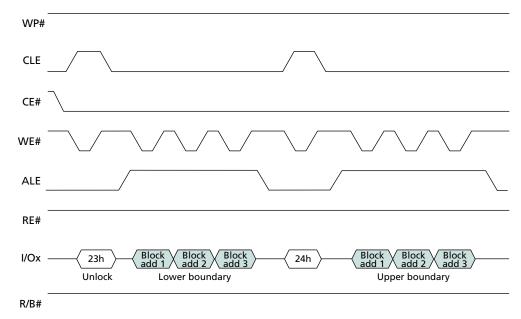

|             | UNLOCK Operation                                                                                                                        |            |

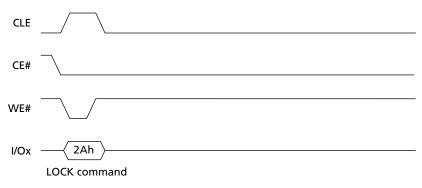

|             | LOCK Operation                                                                                                                          |            |

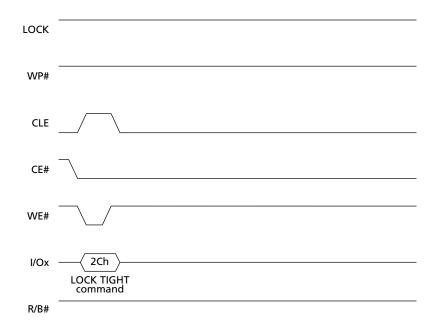

|             | LOCK TIGHT Operation                                                                                                                    |            |

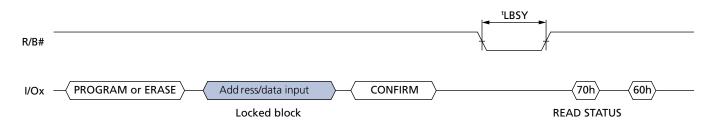

|             | PROGRAM/ERASE Issued to Locked Block                                                                                                    |            |

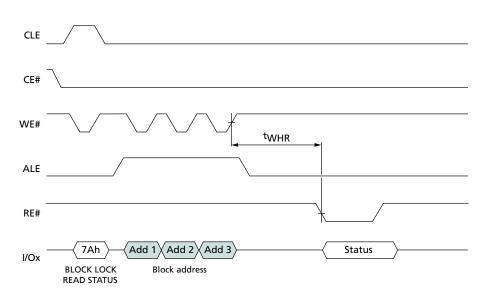

|             | BLOCK LOCK READ STATUS                                                                                                                  |            |

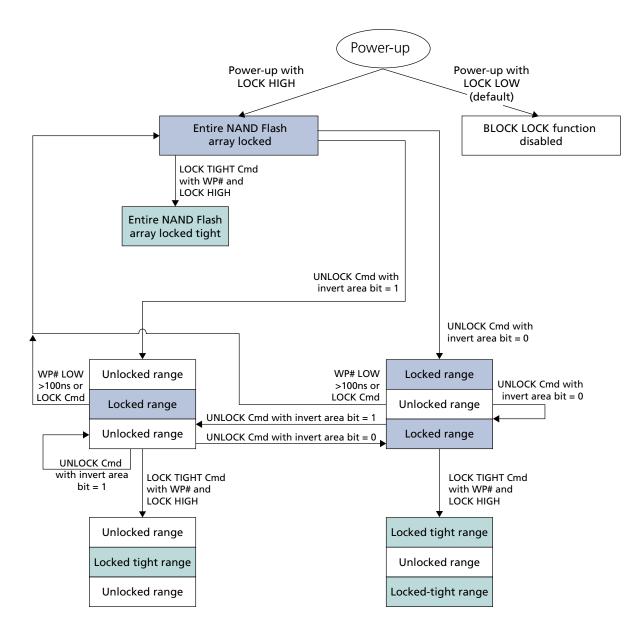

|             | BLOCK LOCK Flowchart                                                                                                                    |            |

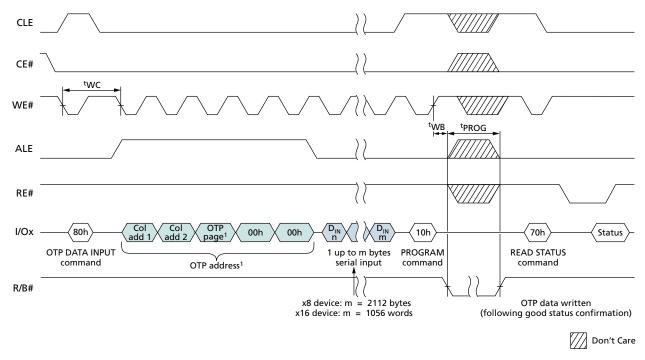

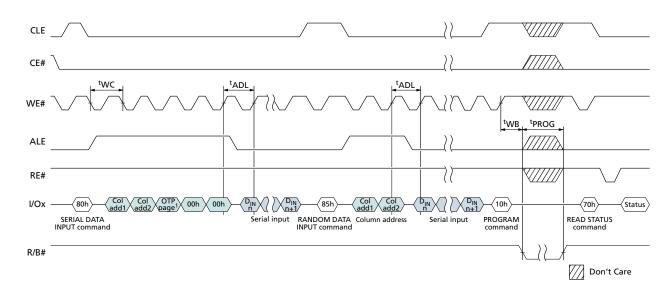

|             | OTP DATA PROGRAM (After Entering OTP Operation Mode)                                                                                    |            |

|             | OTP DATA PROGRAM Operation with RANDOM DATA INPUT (After Entering OTP Operation Mode)                                                   |            |

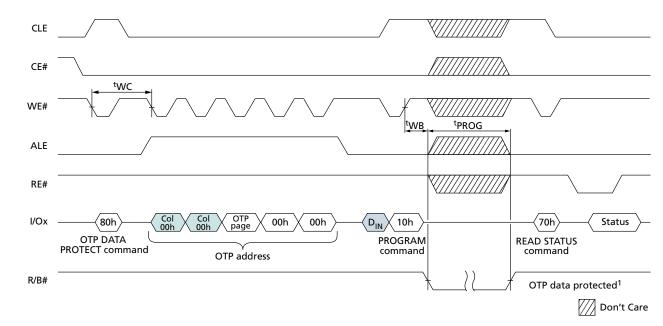

|             | OTP DATA PROTECT Operation (After Entering OTP Protect Mode)                                                                            |            |

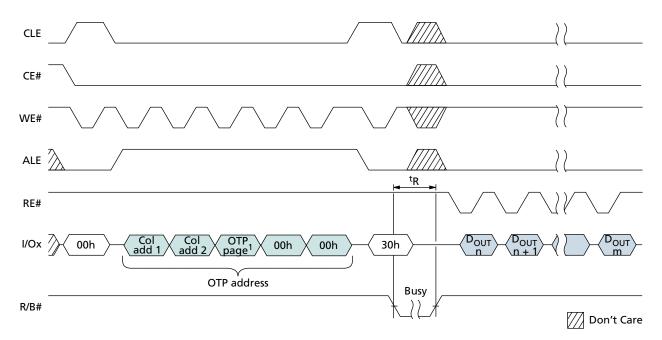

|             | OTP DATA READ                                                                                                                           |            |

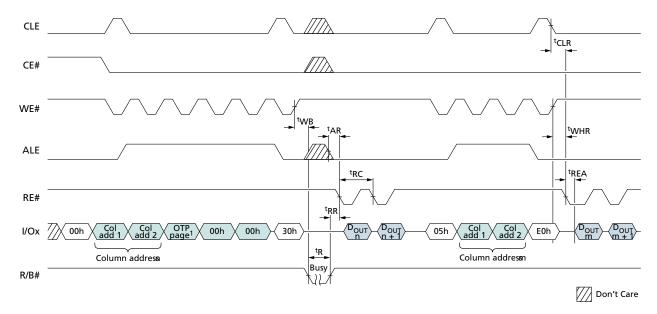

|             | OTP DATA READ with RANDOM DATA READ Operation                                                                                           |            |

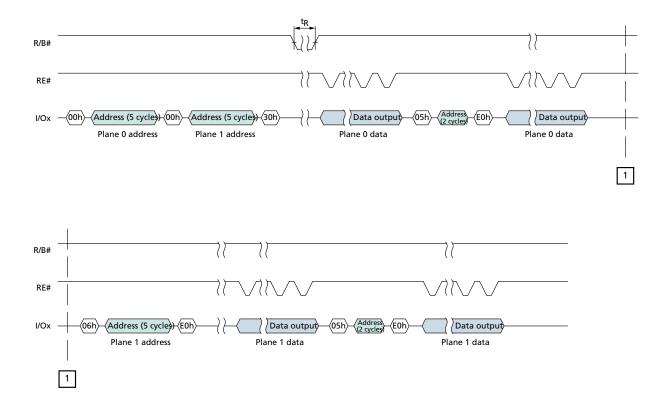

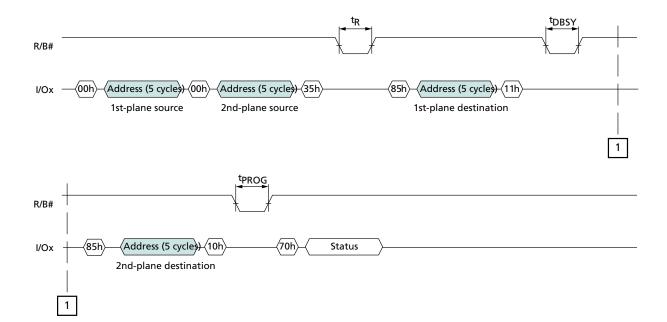

|             | TWO-PLANE PAGE READ                                                                                                                     |            |

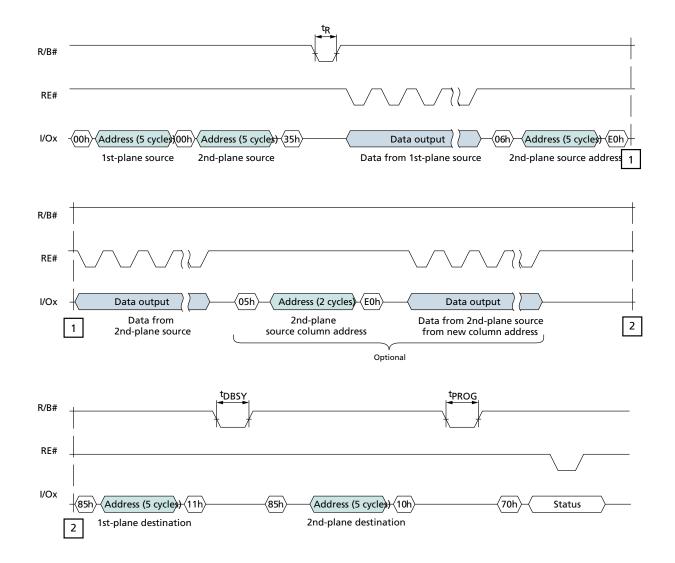

| Figure 69   | TWO-PLANE PAGE READ with RANDOM DATA READ                                                                                               | 92         |

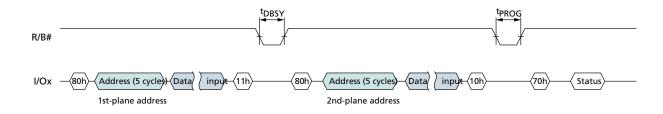

| Figure 70:  | TWO-PLANE PROGRAM PAGE                                                                                                                  | 92         |

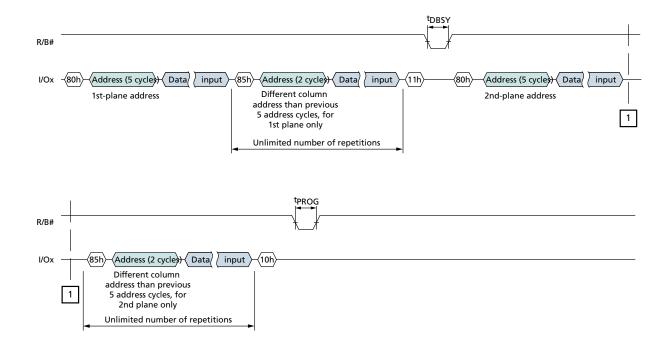

| Figure 71   | TWO-PLANE PROGRAM PAGE with RANDOM DATA INPUT                                                                                           | 93         |

| Figure 72   | TWO-PLANE PROGRAM PAGE CACHE MODE                                                                                                       | 94         |

| Figure 73:  | TWO-PLANE INTERNAL DATA MOVE                                                                                                            | 95         |

| Figure 74   | TWO-PLANE INTERNAL DATA MOVE with TWO-PLANE RANDOM DATA READ                                                                            | 96         |

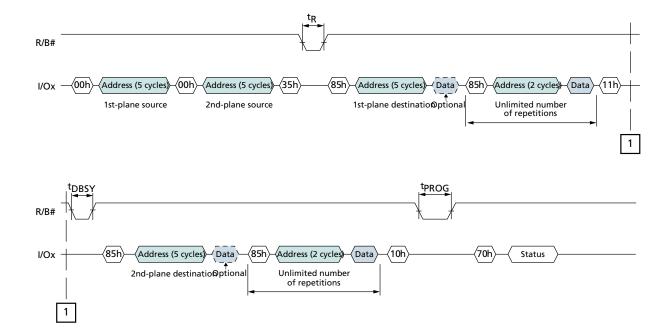

|             | TWO-PLANE INTERNAL DATA MOVE with RANDOM DATA INPUT                                                                                     |            |

|             | TWO-PLANE BLOCK ERASE                                                                                                                   |            |

|             | TWO-PLANE/MULTIPLE-DIE READ STATUS Cycle                                                                                                |            |

|             | Spare Area Mapping (x8)                                                                                                                 |            |

|             | Spare Area Mapping (xl6)                                                                                                                |            |

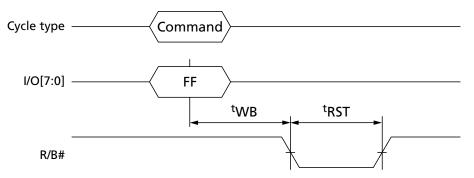

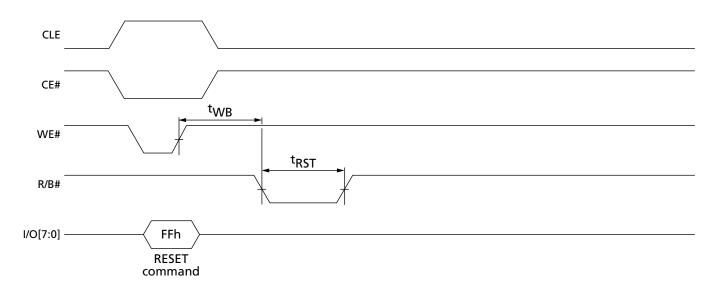

|             | RESET Operation                                                                                                                         |            |

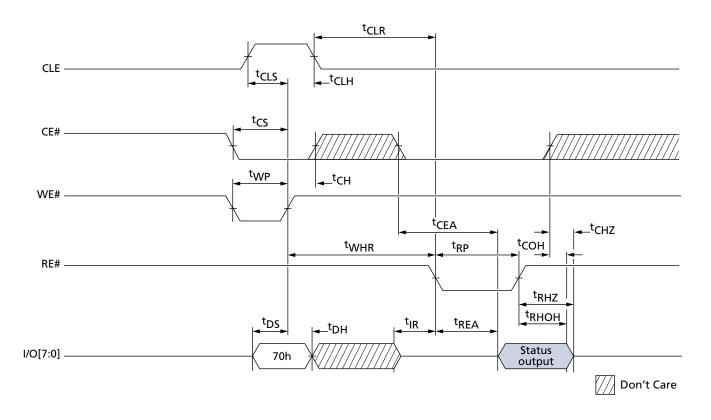

|             | READ STATUS Cycle                                                                                                                       |            |

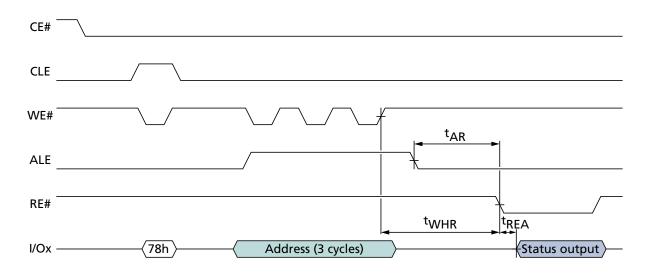

| Figure 82:  | READ STATUS ENHANCED Cycle                                                                                                              | 112        |

| Figure 83:  | READ PARAMETER PAGE                                                                                                                     | 113        |

|             | READ PAGE                                                                                                                               |            |

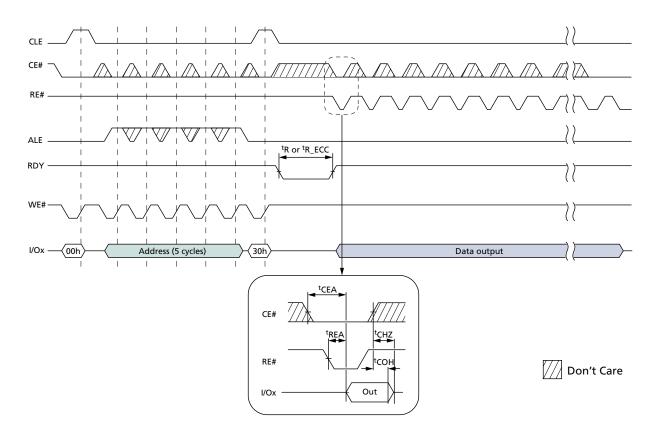

|             | READ PAGE Operation with CE# "Don't Care"                                                                                               |            |

|             | RANDOM DATA READ                                                                                                                        |            |

|             | READ PAGE CACHE SEQUENTIAL                                                                                                              |            |

| Figure 88:  | READ PAGE CACHE SLOUENTINE                                                                                                              | 117<br>110 |

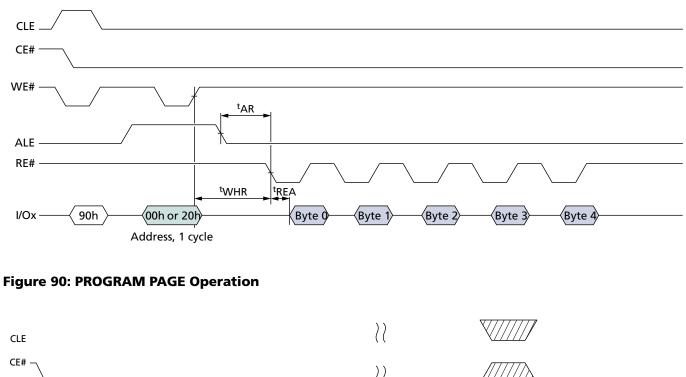

|             | READ ID Operation                                                                                                                       |            |

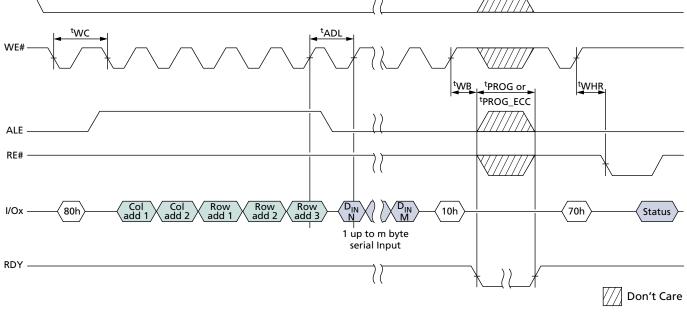

|             | PROGRAM PAGE Operation                                                                                                                  |            |

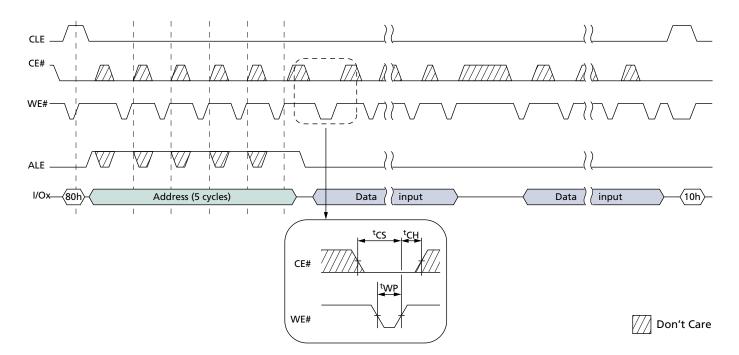

| Figure 91:  | PROGRAM PAGE Operation "                                                                                                                | 120        |

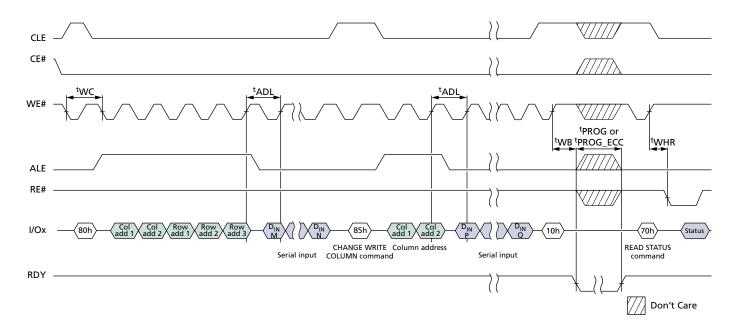

|             | PROGRAM PAGE Operation with RANDOM DATA INPUT                                                                                           |            |

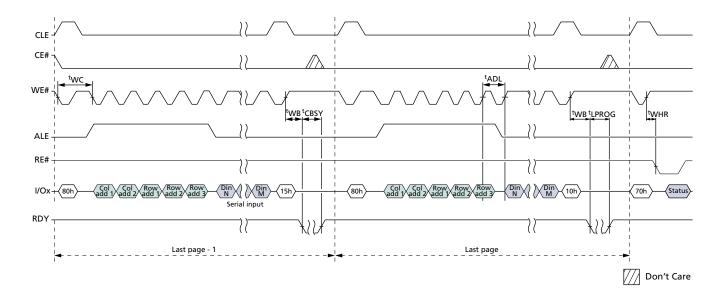

|             | PROGRAM PAGE CACHE                                                                                                                      |            |

| Figure 04   | PROGRAM PAGE CACHE<br>PROGRAM PAGE CACHE Ending on 15h                                                                                  | 121<br>191 |

|             |                                                                                                                                         |            |

|             | INTERNAL DATA MOVE<br>INTERNAL DATA MOVE (85h-10h) with Internal ECC Enabled                                                            |            |

|             | INTERNAL DATA MOVE (85h-10h) with Internal ECC Enabled<br>INTERNAL DATA MOVE (85h-10h) with Random Data Input with Internal ECC Enabled |            |

|             |                                                                                                                                         |            |

| 1.1gure 30; | ERASE BLOCK Operation                                                                                                                   | 123        |

## 2Gb: x8, x16 NAND Flash Memory General Description

## **General Description**

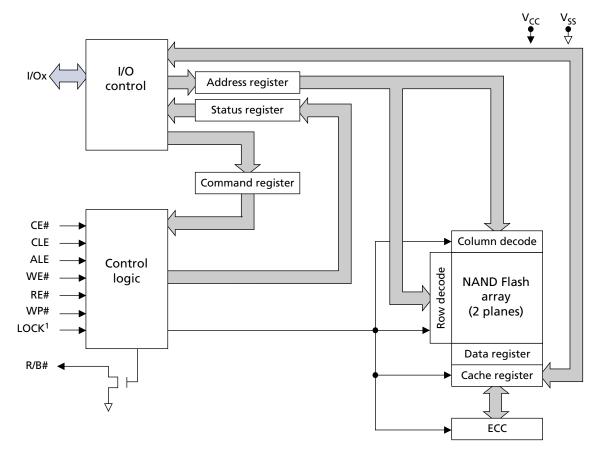

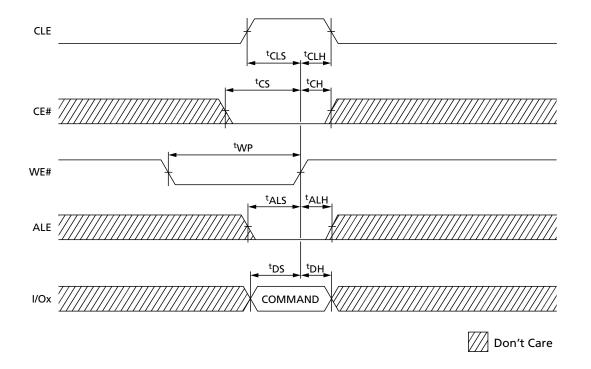

Micron NAND Flash devices include an asynchronous data interface for high-performance I/O operations. These devices use a highly multiplexed 8-bit bus (I/Ox) to transfer commands, address, and data. There are five control signals used to implement the asynchronous data interface: CE#, CLE, ALE, WE#, and RE#. Additional signals control hardware write protection and monitor device status (R/B#).

This hardware interface creates a low pin-count device with a standard pinout that remains the same from one density to another, enabling future upgrades to higher densities with no board redesign.

A target is the unit of memory accessed by a chip enable signal. A target contains one or more NAND Flash die. A NAND Flash die is the minimum unit that can independently execute commands and report status. A NAND Flash die, in the ONFI specification, is referred to as a logical unit (LUN). There is at least one NAND Flash die per chip enable signal. For further details, see Device and Array Organization.

This device has an internal 4-bit ECC that can be enabled using the GET/SET features. See Internal ECC and Spare Area Mapping for ECC for more information.

## **Signal Descriptions**

| Signal <sup>1</sup>              | Туре   | Description <sup>2</sup>                                                                                                                                                                   |

|----------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE                              | Input  | Address latch enable: Loads an address from I/O[7:0] into the address register.                                                                                                            |

| CE#                              | Input  | Chip enable: Enables or disables one or more die (LUNs) in a target.                                                                                                                       |

| CLE                              | Input  | <b>Command latch enable:</b> Loads a command from I/O[7:0] into the command register.                                                                                                      |

| LOCK                             | Input  | When LOCK is HIGH during power-up, the BLOCK LOCK function is enabled. To disable the BLOCK LOCK, connect LOCK to $V_{SS}$ during power-up, or leave it disconnected (internal pull-down). |

| RE#                              | Input  | <b>Read enable:</b> Transfers serial data from the NAND Flash to the host system.                                                                                                          |

| WE#                              | Input  | Write enable: Transfers commands, addresses, and serial data from the host system to the NAND Flash.                                                                                       |

| WP#                              | Input  | Write protect: Enables or disables array PROGRAM and ERASE operations.                                                                                                                     |

| l/O[7:0] (x8)<br>l/O[15:0] (x16) | I/O    | <b>Data inputs/outputs:</b> The bidirectional I/Os transfer address, data, and command information.                                                                                        |

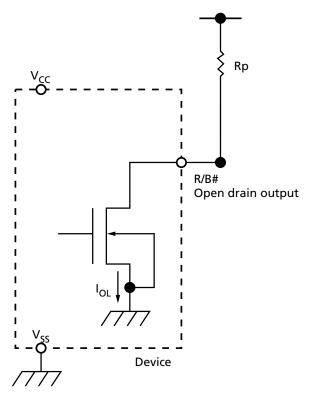

| R/B#                             | Output | <b>Ready/busy:</b> An open-drain, active-low output that requires an external pull-up resistor.<br>This signal indicates target array activity.                                            |

| V <sub>cc</sub>                  | Supply | V <sub>CC</sub> : Core power supply                                                                                                                                                        |

| V <sub>SS</sub>                  | Supply | V <sub>ss</sub> : Core ground connection                                                                                                                                                   |

| NC                               | _      | <b>No connect:</b> NCs are not internally connected. They can be driven or left unconnected.                                                                                               |

| DNU                              | -      | Do not use: DNUs must be left unconnected.                                                                                                                                                 |

#### **Table 1: Signal Definitions**

Notes:

s: 1. See Device and Array Organization for detailed signal connections.