## GDDR6 SGRAM

#### MT61K512M32

## 2 Channels x 512 Meg x 16 I/O, 2 Channels x 1 Gig x 8 I/O

#### **Features**

- $V_{DD} = V_{DDQ} = 1.35V \pm 3\%$  and  $1.25V \pm 3\%$

- $V_{PP} = 1.8V 3\% / +6\%$

- Data rate: 14 Gb/s, 16 Gb/s

- 2 separate independent channels (x16)

- x16/x8 and 2-channel/pseudo channel (PC) mode configurations set at reset

- Single ended interfaces per channel for command/ address (CA) and data

- Differential clock input CK\_t/CK\_c for CA per 2 channels

- Two differential clock inputs WCK\_t/WCK\_c per channel for data (DQ, DBI\_n, EDC)

- Double data rate (DDR) command/address (CK)

- Quad data rate (QDR) and double data rate (DDR) data (WCK), depending on operating frequency

- 16*n* prefetch architecture with 256 bits per array read or write access

- 16 internal banks

- 4 bank groups for <sup>t</sup>CCDL = 3<sup>t</sup>CK and 4<sup>t</sup>CK

- Programmable READ latency

- Programmable WRITE latency

- Write data mask function via CA bus with single and double byte mask granularity

- Data bus inversion (DBI) and CA bus inversion (CABI)

- Input/output PLL

- CA bus training: CA input monitoring via DQ/ DBI\_n/EDC signals

- WCK2CK clock training with phase information via EDC signals

- Data read and write training via read FIFO (depth = 6)

- Read/write data transmission integrity secured by cyclic redundancy check

- Programmable CRC READ latency

- Programmable CRC WRITE latency

- · Programmable EDC hold pattern for CDR

- RDQS mode on EDC pins

- Low power modes

- On-chip temperature sensor with read-out

- Auto precharge option for each burst access

- Auto refresh mode (32ms, 16k cycles) with per-bank and per-2-bank refresh options

- Temperature sensor controlled self refresh rate

- Digital <sup>t</sup>RAS lockout

- On-die termination (ODT) for all high-speed inputs

- Pseudo open drain (POD135 and POD125) compatible outputs

- ODT and output driver strength auto calibration with external resistor ZQ pin (120Ω)

- Internal V<sub>REF</sub> with DFE for data inputs, with input receiver characteristics programmable per pin

- Selectable external or internal  $V_{REF}$  for CA inputs; programmable  $V_{REF}$  offsets for internal  $V_{REF}$

- Vendor ID for device identification

- IEEE 1149.1 compliant boundary scan

- 180-ball BGA package

- Lead-free (RoHS-compliant) and halogen-free packaging

- $T_C = 0^{\circ}C \text{ to } +95^{\circ}C$

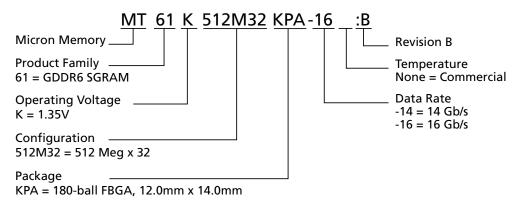

| Options <sup>1</sup>                                            | Marking |

|-----------------------------------------------------------------|---------|

| Organization                                                    |         |

| $-512 \text{ Meg} \times 32 \text{ (words} \times \text{bits)}$ | 512M32  |

| FBGA package                                                    |         |

| <ul><li>180-ball (12.0mm × 14.0mm)</li></ul>                    | KPA     |

| • Timing – maximum data rate                                    |         |

| - 14 Gb/s                                                       | -14     |

| - 16 Gb/s                                                       | -16     |

| Operating temperature                                           |         |

| - Commercial (0°C $\leq$ T <sub>C</sub> $\leq$ +95°C)           | None    |

| Revision                                                        | :В      |

Note: 1. Not all options listed can be combined to define an offered product. Use the part catalog search on http://www.micron.com for available offerings.

**Figure 1: Part Numbering**

#### **FBGA Part Marking Decoder**

Due to space limitations, FBGA-packaged components have an abbreviated part marking that is different from the part number. For a quick conversion of an FBGA code, see the FBGA Part Marking Decoder on Micron's web site: http://www.micron.com.

#### **Important Notes and Warnings**

Micron Technology, Inc. ("Micron") reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions. This document supersedes and replaces all information supplied prior to the publication hereof. You may not rely on any information set forth in this document if you obtain the product described herein from any unauthorized distributor or other source not authorized by Micron.

Automotive Applications. Products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets. Distributor and customer/distributor shall assume the sole risk and liability for and shall indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting directly or indirectly from any use of non-automotive-grade products in automotive applications. Customer/distributor shall ensure that the terms and conditions of sale between customer/distributor and any customer of distributor/customer (1) state that Micron products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting from any use of non-automotive-grade products in automotive applications.

Critical Applications. Products are not authorized for use in applications in which failure of the Micron component could result, directly or indirectly in death, personal injury, or severe property or environmental damage ("Critical Applications"). Customer must protect against death, personal injury, and severe property and environmental damage by incorporating safety design measures into customer's applications to ensure that failure of the Micron component will not result in such harms. Should customer or distributor purchase, use, or sell any Micron component for any critical application, customer and distributor shall indemnify and hold harmless Micron and its subsidiaries, subcontractors, and affiliates and the directors, officers, and employees of each against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, or death arising in any way out of such critical application, whether or not Micron or its subsidiaries, subcontractors, or affiliates were negligent in the design, manufacture, or warning of the Micron product.

Customer Responsibility. Customers are responsible for the design, manufacture, and operation of their systems, applications, and products using Micron products. ALL SEMICONDUCTOR PRODUCTS HAVE INHERENT FAIL-URE RATES AND LIMITED USEFUL LIVES. IT IS THE CUSTOMER'S SOLE RESPONSIBILITY TO DETERMINE WHETHER THE MICRON PRODUCT IS SUITABLE AND FIT FOR THE CUSTOMER'S SYSTEM, APPLICATION, OR PRODUCT. Customers must ensure that adequate design, manufacturing, and operating safeguards are included in customer's applications and products to eliminate the risk that personal injury, death, or severe property or environmental damages will result from failure of any semiconductor component.

Limited Warranty. In no event shall Micron be liable for any indirect, incidental, punitive, special or consequential damages (including without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort, warranty, breach of contract or other legal theory, unless explicitly stated in a written agreement executed by Micron's duly authorized representative.

## **Ball Assignments and Descriptions**

Figure 2: 180-Ball FBGA (Top View)

|   | 1                 | 2                | 3               | 4                | 5                | 6 | 7 | 8    | 9                  | 10               | 11               | 12              | 13               | 14               |   |

|---|-------------------|------------------|-----------------|------------------|------------------|---|---|------|--------------------|------------------|------------------|-----------------|------------------|------------------|---|

| Α | V <sub>DD</sub>   | V <sub>SS</sub>  | DQ1_A           | V <sub>SS</sub>  | V <sub>PP</sub>  |   |   |      |                    | V <sub>PP</sub>  | V <sub>ss</sub>  | DQ9_A           | V <sub>ss</sub>  | V <sub>DD</sub>  |   |

| В | V <sub>SS</sub>   | DQ3_A            | DQ2_A           | DQ0_A            | V <sub>DDQ</sub> |   |   |      |                    | V <sub>DDQ</sub> | DQ8_A            | DQ10_A          | DQ11_A           | V <sub>SS</sub>  |   |

| c | V <sub>DDQ</sub>  | EDC0_A           | V <sub>ss</sub> | V <sub>DDQ</sub> | V <sub>SS</sub>  |   |   |      |                    | V <sub>SS</sub>  | V <sub>DDQ</sub> | V <sub>ss</sub> | EDC1_A           | V <sub>DDQ</sub> |   |

| D | V <sub>SS</sub>   | DBI0_n_A         | V <sub>SS</sub> | WCK0_t<br>_A     | WCK0_c<br>_A     |   |   |      |                    | WCK1_c<br>_A     | WCK1_t<br>_A     | V <sub>SS</sub> | DBI1_n_A         | V <sub>SS</sub>  |   |

| E | V <sub>DD Q</sub> | DQ5_A            | DQ4_A           | V <sub>SS</sub>  | V <sub>DD</sub>  |   |   |      |                    | V <sub>DD</sub>  | V <sub>ss</sub>  | DQ12_A          | DQ13_A           | V <sub>DDQ</sub> |   |

| F | V <sub>SS</sub>   | DQ6_A            | V <sub>SS</sub> | V <sub>DDQ</sub> | TMS              |   |   |      |                    | TDI              | V <sub>DDQ</sub> | V <sub>SS</sub> | DQ14_A           | V <sub>SS</sub>  |   |

| G | V <sub>SS</sub>   | DQ7_A            | V <sub>SS</sub> | CA2_A            | DNU              |   |   |      |                    | CKE_n_A          | CA1_A            | V <sub>SS</sub> | DQ15_A           | V <sub>SS</sub>  |   |

| Н | V <sub>DDQ</sub>  | V <sub>DD</sub>  | CA0_A           | V <sub>SS</sub>  | CA4_A            |   |   |      |                    | CA5_A            | V <sub>SS</sub>  | CA3_A           | V <sub>DD</sub>  | V <sub>DDQ</sub> |   |

| J | RESET _n          | V <sub>DDQ</sub> | CA9_A           | CA8_A            | CABI_n_A         |   |   |      |                    | CK_t             | CA7_A            | CA6_A           | V <sub>DDQ</sub> | ZQ_A             |   |

| Κ | V <sub>REFC</sub> | V <sub>DDQ</sub> | CA9_B           | CA8_B            | CABI_n_B         |   |   |      |                    | CK_c             | CA7_B            | CA6_B           | V <sub>DDQ</sub> | ZQ_B             |   |

| L | V <sub>DDQ</sub>  | V <sub>DD</sub>  | CA0_B           | V <sub>SS</sub>  | CA4_B            |   |   |      |                    | CA5_B            | V <sub>SS</sub>  | CA3_B           | V <sub>DD</sub>  | V <sub>DDQ</sub> |   |

| М | V <sub>SS</sub>   | DQ7_B            | V <sub>SS</sub> | CA2_B            | DNU              |   |   |      |                    | CKE_n_B          | CA1_B            | V <sub>ss</sub> | DQ15_B           | V <sub>SS</sub>  | ı |

| N | V <sub>SS</sub>   | DQ6_B            | V <sub>SS</sub> | V <sub>DDQ</sub> | тск              |   |   |      |                    | TDO              | V <sub>DDQ</sub> | V <sub>SS</sub> | DQ14_B           | V <sub>SS</sub>  |   |

| Р | V <sub>DDQ</sub>  | DQ5_B            | DQ4_B           | V <sub>SS</sub>  | V <sub>DD</sub>  |   |   |      |                    | V <sub>DD</sub>  | V <sub>SS</sub>  | DQ12_B          | DQ13_B           | V <sub>DDQ</sub> |   |

| R | V <sub>SS</sub>   | DBI0_n_B         | V <sub>SS</sub> | WCK0_t<br>_B     | WCK0_c<br>_B     |   |   |      |                    | WCK1_c<br>_B     | WCK1_t<br>_B     | V <sub>SS</sub> | DBI1_n_B         | V <sub>SS</sub>  |   |

| Т | V <sub>DDQ</sub>  | EDC0_B           | V <sub>SS</sub> | V <sub>DDQ</sub> | V <sub>SS</sub>  |   |   |      |                    | V <sub>SS</sub>  | V <sub>DDQ</sub> | V <sub>SS</sub> | EDC1_B           | V <sub>DDQ</sub> |   |

| U | V <sub>SS</sub>   | DQ3_B            | DQ2_B           | DQ0_B            | V <sub>DDQ</sub> |   |   |      |                    | V <sub>DDQ</sub> | DQ8_B            | DQ10_B          | DQ11_B           | V <sub>SS</sub>  |   |

| V | V <sub>DD</sub>   | V <sub>ss</sub>  | DQ1_B           | V <sub>SS</sub>  | V <sub>PP</sub>  |   |   |      |                    | V <sub>PP</sub>  | V <sub>SS</sub>  | DQ9_B           | V <sub>ss</sub>  | V <sub>DD</sub>  |   |

|   |                   |                  |                 |                  |                  |   | D | Pata | Command<br>Address | d/               | Other signa      | al S            | Supply           | Ground           |   |

Note: 1. Channel A byte 1 and channel B byte 0 are disabled when the device is configured to x8 mode.

**Table 1: 180-Ball FBGA Ball Descriptions**

| Symbol                           | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK_t,<br>CK_c                    | Input     | <b>Clock:</b> CK_t and CK_c are differential clock inputs. CK_t and CK_c do not have channel indicators as one clock is shared between both channel A and channel B on a device. Command address (CA) inputs are latched on the rising and falling edge of CK. All latencies are referenced to CK.                                                                                 |

| WCK0_t, WCK0_c<br>WCK1_t, WCK1_c | Input     | <b>Write clock:</b> WCK_t and WCK_c are differential clocks used for write data capture and read data output. WCK0_t/WCK0_c are associated with DQ[7:0], DBI0_n, and EDC0. WCK1_t/WCK1_c are associated with DQ[15:8], DBI1_n, and EDC1.                                                                                                                                           |

| CKE_n                            | Input     | Clock enable: CKE_n LOW activates and CKE_n HIGH deactivates the internal clock, device input buffers, and output drivers excluding RESET_n, TDI, TDO, TMS, and TCK. Taking CKE_n HIGH provides PRECHARGE POWER-DOWN and SELF REFRESH operations (all banks idle), or ACTIVE POWER-DOWN (row ACTIVE in any bank). CKE_n must be maintained LOW throughout read and write accesses. |

| CA[9:0]                          | Input     | <b>Command address (CA):</b> The CA inputs receive packetized DDR command, address or other information, for example, the op-code for the MRS command. See Command Truth Table for details.                                                                                                                                                                                        |

| CABI_n                           | Input     | Command address bus inversion                                                                                                                                                                                                                                                                                                                                                      |

| DQ[15:0]                         | I/O       | Data input/output: Bidirectional 16-bit data bus.                                                                                                                                                                                                                                                                                                                                  |

| DBI[1:0]_n                       | I/O       | <b>Data bus inversion:</b> DBI0_n is associated with DQ[7:0], DBI1_n is associated with DQ[15:8].                                                                                                                                                                                                                                                                                  |

| EDC[1:0]                         | Output    | <b>Error detection code:</b> The calculated CRC data is transmitted on these signals. In addition these signals drive a "hold" pattern when idle. EDC0 is associated with DQ[7:0], EDC1 is associated with DQ[15:8].                                                                                                                                                               |

| $V_{DDQ}$                        | Supply    | I/O power supply: Isolated on the die for improved noise immunity.                                                                                                                                                                                                                                                                                                                 |

| $V_{DD}$                         | Supply    | Power supply                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>SS</sub>                  | Supply    | Ground                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>PP</sub>                  | Supply    | Pump voltage                                                                                                                                                                                                                                                                                                                                                                       |

| $V_{REFC}$                       | Supply    | Reference voltage for CA, CABI_n, and CKE_n signals                                                                                                                                                                                                                                                                                                                                |

| ZQ                               | Reference | External reference for auto calibration                                                                                                                                                                                                                                                                                                                                            |

| TDI                              | Input     | JTAG test data input                                                                                                                                                                                                                                                                                                                                                               |

| TDO                              | Output    | JTAG test data output                                                                                                                                                                                                                                                                                                                                                              |

| TMS                              | Input     | JTAG test mode select                                                                                                                                                                                                                                                                                                                                                              |

| TCK                              | Input     | JTAG test clock                                                                                                                                                                                                                                                                                                                                                                    |

| RESET_n                          | Input     | <b>Reset:</b> RESET_n low asynchronously initiates a full chip reset. With RESET_n LOW all ODTs are disabled. A full chip reset may be performed at any time by pulling RESET_n LOW.                                                                                                                                                                                               |

| DNU                              | _         | Do not use                                                                                                                                                                                                                                                                                                                                                                         |

Note: 1. Index "\_A" or "\_B" represents the channel indicator "A" and "B" of the device. Signal names including the channel indicator are used whenever more than one channel is referenced, for example, with the ball assignment. The channel indicator is omitted whenever features and functions common to both channels are described.

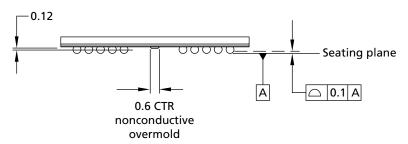

#### **Package Dimensions**

Figure 3: 180-Ball FBGA (KPA)

Notes: 1. Package dimension specification is compliant to JC11 MO328 variation P14.0x12.0-GJ-180A.

- 2. All dimensions are in millimeters.

- 3. Solder ball material: SAC-Q (92.5% Sn, 4% Ag, 3% Bi, 0.5% Cu).

### **Functional Description**

The GDDR6 SGRAM is a high-speed dynamic random-access memory designed for applications requiring high bandwidth. It is internally configured as 16-bank memory and contains 17,179,869,184 bits.

The GDDR6 SGRAM's high-speed interface is optimized for point-to-point connections to a host controller. On-die termination (ODT) is provided for all high-speed interface signals to eliminate the need for termination resistors in the system.

GDDR6 uses a 16*n*-prefetch architecture and a DDR or QDR interface to achieve high-speed operation. The device's architecture consists of two 16-bit-wide fully independent channels.

Read and write accesses to GDDR6 are burst oriented; accesses start at a selected location and consist of a total of 16 data words. Accesses begin with the registration of an ACTIVATE command, which is then followed by a READ, WRITE (WOM), or masked WRITE (WDM, WSM) command. The row and bank address to be accessed is registered coincident with the ACTIVATE command. The address bits registered coincident with the READ, WRITE, or masked WRITE command are used to select the bank and the starting column location for the burst access.

#### **Clocking**

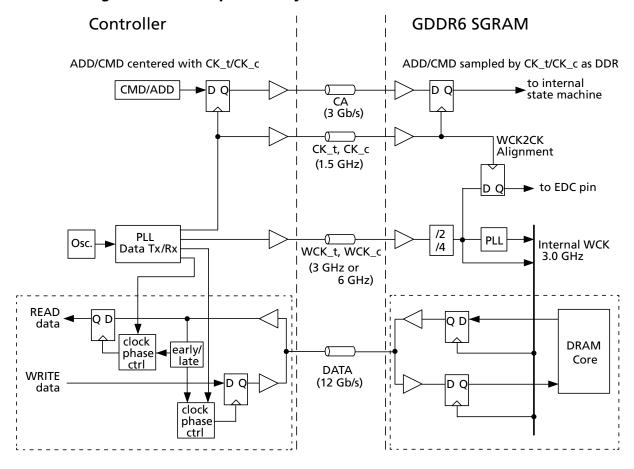

GDDR6 operates from a differential clock CK\_t and CK\_c. CK is common to both channels. Command and address (CA) are registered at every rising and falling CK edge. There are both single-cycle and multi-cycle commands. See Command Truth Table for details.

GDDR6 uses a free running differential forwarded clock (WCK\_t/WCK\_c) with both input and output data registered and driven respectively at both edges of the forwarded WCK.

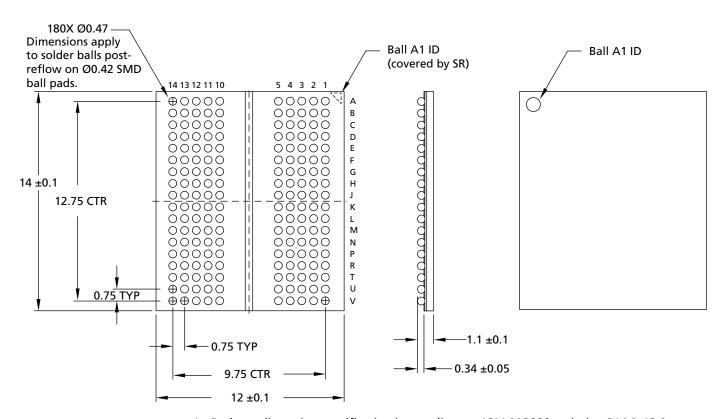

GDDR6 supports DDR and QDR operating modes for WCK frequency which differ in the DQ/DBI\_n pin to WCK clock frequency ratio. The figure below illustrates the difference between both modes.

This GDDR6 SGRAM device is designed with a WCK/byte granularity which is equivalent to one WCK per byte. The DRAM info bits for WCK granularity, WCK frequency, and internal WCK can be read by the host during the initialization process to determine the WCK architecture for the device.

Table 2: Example Clock and Interface Signal Frequency Relationship

| Pin          | DDR WCK     | QDR WCK     | Unit     |

|--------------|-------------|-------------|----------|

| CK_t, CK_c   | 1.5         | 1.5         | GHz      |

| CA           | 3.0         | 3.0         | Gb/s/pin |

| WCK_t, WCK_c | 6.0         | 3.0         | GHz      |

| DQ, DBI_n    | 12.0        | 12.0        | Gb/s/pin |

| EDC          | 6.0 or 12.0 | 6.0 or 12.0 | Gb/s/pin |

**Figure 4: Clocking and Interface Relationship**

Note: 1. The figure shows the relationship between the data rate of the buses and the clocks; it is not a timing diagram.

Figure 5: Block Diagram of an Example Clock System

#### 16Gb: 2 Channels x16/x8 GDDR6 SGRAM **Functional Description**

#### **Addressing**

GDDR6 addressing is defined for a single channel with devices having two channels per device.

**Table 3: Addressing**

|                               | 16Gb     | Density |  |  |  |

|-------------------------------|----------|---------|--|--|--|

| Parameter                     | x16 Mode | x8 Mode |  |  |  |

| Number of channels            |          | 2       |  |  |  |

| Memory density (per channel)  | 8        | 8Gb     |  |  |  |

| Memory prefetch (per channel) | 256b     | 128b    |  |  |  |

| Bank address (per channel)    | BA       | \[3:0]  |  |  |  |

| Row address (per channel)     | R[13:0]  | R[14:0] |  |  |  |

| Column address (per channel)  | C        | [6:0]   |  |  |  |

| Page size (per channel)       | 4KB      | 2KB     |  |  |  |

| Refresh                       | 16k      | R[14:0] |  |  |  |

- Notes: 1. The column address notation for GDDR6 does not include the lower four address bits as the burst order is always fixed for READ and WRITE.

- 2. Page size = 2^COLBITS × (Prefetch\_Size/8) where COLBITS is the number of column address bits.

## **Operations**

#### **Command Truth Table**

GDDR6 uses a packetized DDR command/address bus that encodes all commands and addresses on a 10-bit CA bus as outlined in the table below.

**Figure 6: Command Truth Table**

| Operation         | Symbol  | СК   | CK    | E_n | CA9 | CA8 | CA7             | CA6             | CA5            | CA4             | CA3            | CA2             | CA1            | CA0            | Notes    |

|-------------------|---------|------|-------|-----|-----|-----|-----------------|-----------------|----------------|-----------------|----------------|-----------------|----------------|----------------|----------|

| Operation         | Symbol  | Edge | n - 1 | n   | CAS | CAO | CA              | CAU             | CAS            | CA4             | CAS            | CAZ             | CAT            | CAU            | Notes    |

| NO OPERATION      | NOP (1) | R    | L     | L   | Н   | Н   | V               | V               | V              | V               | V              | V               | V              | V              | 1, 10    |

|                   |         | F    |       |     | Н   | Н   | V               | V               | V              | V               | V              | V               | V              | V              |          |

|                   | NOP (2) | R    | L     | L   | Н   | Н   | V               | V               | V              | V               | V              | V               | V              | V              |          |

|                   |         | F    |       |     | Н   | L   | V               | V               | V              | V               | V              | V               | V              | V              |          |

|                   | NOP (3) | R    | L     | L   | Н   | L   | V               | V               | V              | V               | V              | V               | V              | V              |          |

|                   |         | F    |       |     | Н   | Н   | V               | V               | V              | V               | V              | V               | V              | V              |          |

| MODE REGISTER SET | MRS     | R    | L     | L   | Н   | L   | M3              | M2              | M1             | M0              | OP3            | OP2             | OP1            | OP0            | 1, 2, 3  |

|                   |         | F    |       |     | Н   | L   | OP11            | OP10            | OP9            | OP8             | OP7            | OP6             | OP5            | OP4            |          |

| ACTIVATE          | ACT     | R    | L     | L   | L   | R14 | ВА3             | BA2             | BA1            | BA0             | R3             | R2              | R1             | R0             | 1, 2, 4  |

|                   |         | F    |       |     | R13 | R12 | R11             | R10             | R9             | R8              | R7             | R6              | R5             | R4             |          |

| READ              | RD      | R    | L     | L   | Н   | Н   | BA3             | BA2             | BA1            | BA0             | C3             | C2              | C1             | C0             | 1, 2, 5, |

|                   |         | F    |       |     | L   | Н   | L               | L               | V              | L               | CE             | C6              | C5             | C4             | 6        |

| READ with         | RDA     | R    | L     | L   | Н   | Н   | BA3             | BA2             | BA1            | BA0             | C3             | C2              | C1             | C0             | 1, 2, 5, |

| AUTO PRECHARGE    |         | F    |       |     | L   | Н   | L               | L               | V              | Н               | CE             | C6              | C5             | C4             | 6        |

| LOAD FIFO         | LDFF    | R    | L     | L   | Н   | Н   | В3              | B2              | B1             | В0              | D3             | D2              | D1             | D0             | 1, 2, 8  |

|                   |         | F    |       |     | L   | Н   | Н               | L               | D9             | D8              | D7             | D6              | D5             | D4             |          |

| READ TRAINING     | RDTR    | R    | L     | L   | Н   | Н   | V               | V               | V              | V               | V              | V               | V              | V              | 1, 2, 6  |

|                   |         | F    |       |     | L   | Н   | Н               | Н               | V              | L               | CE             | V               | V              | V              |          |

| WRITE             | WOM     | R    | L     | L   | Н   | Н   | BA3             | BA2             | BA1            | BA0             | C3             | C2              | C1             | C0             | 1, 2, 5, |

|                   |         | F    |       |     | L   | L   | L               | L               | V              | L               | CE             | C6              | C5             | C4             | 6        |

| WRITE with        | WOMA    | R    | L     | L   | Н   | Н   | BA3             | BA2             | BA1            | BA0             | C3             | C2              | C1             | C0             | 1, 2, 5, |

| AUTO PRECHARGE    |         | F    |       |     | L   | L   | L               | L               | V              | Н               | CE             | C6              | C5             | C4             | 6        |

| WRITE SINGLE      | WSM     | R    | L     | L   | Н   | Н   | BA3             | BA2             | BA1            | BA0             | C3             | C2              | C1             | C0             | 1, 2, 5, |

| BYTE MASK         |         | F    |       |     | L   | L   | L               | Н               | V              | L               | CE             | C6              | C5             | C4             | 6        |

|                   |         | R    |       |     | Н   | Н   | Byte 0<br>BST7  | Byte 0<br>BST6  | Byte 0<br>BST5 | Byte 0<br>BST4  | Byte 0<br>BST3 | Byte 0<br>BST2  | Byte 0<br>BST1 | Byte 0<br>BST0 |          |

|                   |         | F    |       |     | Н   | Н   | , ,             | Byte 0<br>BST14 |                | Byte 0<br>BST12 |                | Byte 0<br>BST10 | Byte 0<br>BST9 | Byte 0<br>BST8 |          |

|                   |         | R    |       |     | Н   | Н   | Byte 1<br>BST7  | Byte 1<br>BST6  | Byte 1<br>BST5 | Byte 1<br>BST4  | Byte 1<br>BST3 | Byte 1<br>BST2  | Byte 1<br>BST1 | Byte 1<br>BST0 |          |

|                   |         | F    |       |     | Н   | Н   | Byte 1<br>BST15 | Byte 1<br>BST14 |                | Byte 1<br>BST12 |                | Byte 1<br>BST10 | Byte 1<br>BST9 | Byte 1<br>BST8 |          |

**Figure 7: Command Truth Table (Continued)**

| Operation                        | Symbol | CK   | CKI   | _n | CA9 | CA8 | CA7             | CA6             | CA5             | CA4             | CA3             | CA2             | CA1            | CA0            | Notes    |

|----------------------------------|--------|------|-------|----|-----|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------|

| Operation                        | Symbol | Edge | n - 1 | n  |     | CAO | CA              |                 |                 | CAT             | CAS             | CAZ             | CAI            | САО            | Notes    |

| WRITE SINGLE                     | WSMA   | R    | L     | L  | Н   | Н   | ВАЗ             | BA2             | BA1             | BA0             | C3              | C2              | C1             | C0             | 1, 2, 5, |

| BYTE MASK with AUTO PRECHARGE    |        | F    |       |    | L   | L   | L               | Н               | V               | Н               | CE              | C6              | C5             | C4             | 6        |

|                                  |        | R    |       |    | Н   | Н   | Byte 0<br>BST7  | Byte 0<br>BST6  | Byte 0<br>BST5  | Byte 0<br>BST4  | Byte 0<br>BST3  | Byte 0<br>BST2  | Byte 0<br>BST1 | Byte 0<br>BST0 |          |

|                                  |        | F    |       |    | Н   | Н   | Byte 0<br>BST15 | Byte 0<br>BST14 | Byte 0<br>BST13 | Byte 0<br>BST12 | Byte 0<br>BST11 | Byte 0<br>BST10 | Byte 0<br>BST9 | Byte 0<br>BST8 |          |

|                                  |        | R    |       |    | Н   | Н   | Byte 1<br>BST7  | Byte 1<br>BST6  | Byte 1<br>BST5  | Byte 1<br>BST4  | Byte 1<br>BST3  | Byte 1<br>BST2  | Byte 1<br>BST1 | Byte 1<br>BST0 |          |

|                                  |        | F    |       |    | Н   | Н   | Byte 1<br>BST15 | Byte 1<br>BST14 | Byte 1<br>BST13 | Byte 1<br>BST12 | Byte 1<br>BST11 | Byte 1<br>BST10 | Byte 1<br>BST9 | Byte 1<br>BST8 |          |

| WRITE DOUBLE                     | WDM    | R    | L     | L  | Н   | Н   | BA3             | BA2             | BA1             | BA0             | C3              | C2              | C1             | C0             | 1, 2, 5, |

| BYTE MASK                        |        | F    |       |    | L   | L   | Н               | L               | V               | L               | CE              | C6              | C5             | C4             | 6        |

|                                  |        | R    |       |    | Н   | Н   | BST7            | BST6            | BST5            | BST4            | BST3            | BST2            | BST1           | BST0           |          |

|                                  |        | F    |       |    | Н   | Н   | BST15           | BST14           | BST13           | BST12           | BST11           | BST10           | BST9           | BST8           |          |

| WRITE DOUBLE                     | WDMA   | R    | L     | L  | Н   | Н   | BA3             | BA2             | BA1             | BA0             | C3              | C2              | C1             | C0             | 1, 2, 5, |

| BYTE MASK with<br>AUTO PRECHARGE |        | F    |       |    | L   | L   | Н               | L               | V               | Н               | CE              | C6              | C5             | C4             | 6        |

| AOTOTRECHARGE                    |        | R    |       |    | Н   | Н   | BST7            | BST6            | BST5            | BST4            | BST3            | BST2            | BST1           | BST0           |          |

|                                  |        | F    |       |    | Н   | Н   | BST15           | BST14           | BST13           | BST12           | BST11           | BST10           | BST9           | BST8           |          |

| WRITE TRAINING                   | WRTR   | R    | L     | L  | Н   | Н   | V               | V               | V               | V               | V               | V               | V              | V              | 1, 2, 6  |

|                                  |        | F    |       |    | L   | L   | Н               | Н               | V               | L               | CE              | V               | V              | V              |          |

| PRECHARGE                        | PREpb  | R    | L     | L  | Н   | L   | BA3             | BA2             | BA1             | BA0             | V               | V               | V              | V              | 1, 2, 9  |

|                                  |        | F    |       |    | L   | L   | V               | V               | V               | L               | V               | V               | V              | ٧              |          |

| PRECHARGE ALL                    | PREab  | R    | L     | L  | Н   | L   | V               | V               | V               | V               | V               | V               | V              | V              | 1, 2     |

|                                  |        | F    |       |    | L   | L   | V               | V               | V               | Н               | V               | V               | V              | V              |          |

| PER-BANK REFRESH                 | REFpb/ | R    | L     | L  | Н   | L   | BA3             | BA2             | BA1             | BA0             | V               | V               | V              | V              | 1, 2, 7, |

|                                  | REFp2b | F    |       |    | L   | Н   | V               | V               | V               | L               | V               | V               | V              | V              | 9        |

| REFRESH                          | REFab  | R    | L     | L  | Н   | L   | V               | V               | V               | V               | V               | V               | V              | V              | 1, 2, 7  |

|                                  |        | F    |       |    | L   | Н   | V               | V               | V               | Н               | V               | V               | V              | ٧              |          |

| POWER-DOWN ENTRY                 | PDE    | R    | L     | Н  | Н   | Н   | V               | V               | V               | V               | V               | V               | V              | V              | 1, 2     |

|                                  |        | F    |       |    | Н   | Н   | V               | V               | V               | V               | V               | V               | V              | V              |          |

| POWER-DOWN EXIT                  | PDX    | R    | Н     | L  | Н   | Н   | V               | V               | V               | V               | V               | V               | V              | V              | 1, 2     |

|                                  |        | F    |       |    | Н   | Н   | V               | V               | V               | V               | V               | V               | V              | V              | <u></u>  |

| SELF REFRESH ENTRY               | SRE    | R    | L     | Н  | Н   | L   | V               | V               | V               | V               | V               | V               | V              | V              | 1, 2, 7  |

|                                  |        | F    |       |    | L   | Н   | V               | V               | V               | V               | V               | V               | V              | V              |          |

| SELF REFRESH EXIT                | SRX    | R    | Н     | L  | Н   | Н   | V               | V               | V               | V               | V               | V               | V              | V              | 1, 2     |

|                                  |        | F    |       |    | Н   | Н   | V               | V               | V               | V               | V               | V               | V              | V              |          |

| COMMAND/ADDRESS                  | CAT    | R    | L     | Н  | V   | V   | V               | V               | V               | V               | V               | V               | V              | V              | 1, 2     |

| TRAINING CAPTURE                 |        | F    |       |    | V   | V   | V               | V               | V               | V               | V               | V               | V              | V              |          |

Notes: 1. H = Logic HIGH level; L = Logic LOW level; V = Valid signal (H or L, but not floating). R, F = Rising, Falling CK clock edge.

# 16Gb: 2 Channels x16/x8 GDDR6 SGRAM Functional Description

- 2. Values shown for CA[9:0] are logical values; the physical values are inverted when command/address bus inversion (CABI) is enabled and CABI\_n = L.

- 3. M[3:0] provide the mode register address (MRA), OP[11:0] the opcode to be loaded.

- 4. BA[3:0] provide the bank address, R[14:0] provide the row address.

- 5. BA[3:0] provide the bank address, C[6:0] provide the column address; no sub-word addressing within a burst of 16. BST[15:0] provide the write data mask for each burst position with WDM(A) and WSM(A) commands.

- 6. CE (channel enable) is intended for PC mode. The command is active when CE = H. When CE = L the data access is suppressed.

- 7. The command is REFRESH or PER-BANK REFRESH/PER-2-BANK REFRESH when CKE\_n(n) = L and SELF REFRESH ENTRY when CKE\_n(n) = H.

- 8. B[3:0] select the burst position, and D[9:0] provide the data.

- 9. BA[3:0] provide the bank address.

- 10. All three encodings perform the same NOP. NOP (2) and NOP (3) encodings are only allowed during CA Training.

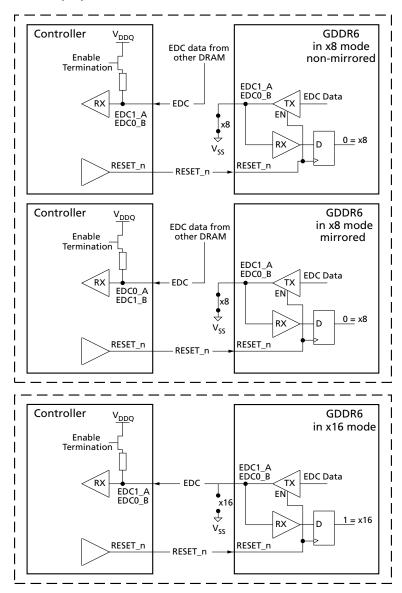

#### Clamshell (x8) Mode Enable

A GDDR6 SGRAM-based memory system is typically divided into several channels. GDDR6 has been optimized for a 16-bit-wide channel. A channel can be comprised of a single device operated in x16 mode, or two devices each operated in x8 mode. For x8 mode the devices are typically assembled on opposite sides of the PCB in what is referred as a clamshell layout.

Whether in x16 mode or x8 mode the device will operate with a point-to-point connection on the high-speed data signals. The disabled signals in x8 mode should all be in a High-Z state, non-terminating.

The x8 mode is detected at power-up on EDC1\_A and EDC0\_B. For x8 mode these signals are tied to  $V_{SS}$ ; they are part of the bytes that are disabled in this mode and therefore not needed for EDC functionality. For x16 mode these signals are active and always terminated to  $V_{DDO}$  in the system or by the controller.

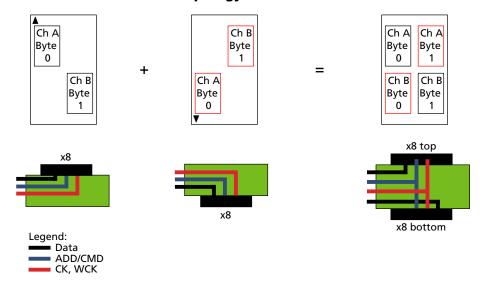

The configuration is set with RESET\_n going HIGH. Once the configuration has been set, it cannot be changed during normal operation. Typically, the configuration is fixed in the system. Details of the x8 mode detection are depicted in Figure 8. A comparison of x16 mode and x8 mode systems is shown in Figure 9.

**Table 4: Clamshell (x8) Mode Enable**

| Mode | EDC0_A    | EDC1_A                             | EDC0_B                     | EDC1_B    |

|------|-----------|------------------------------------|----------------------------|-----------|

| x8   | $V_{DDQ}$ | V <sub>SS</sub> (on board)         | V <sub>SS</sub> (on board) | $V_{DDQ}$ |

| x16  |           | V <sub>DDQ</sub> (terminated by th | ne system or controller)   |           |

Figure 8: Enabling Clamshell (x8) Mode

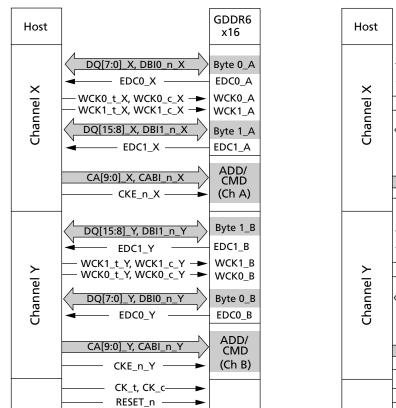

Figure 9: System View for x16 and x8 Modes

Figure 10 clarifies the use of x8 mode and how the bytes are enabled/disabled to give the controller the view of the same bytes that a controller sees with a single x16 device. For a 16-bit channel using two devices in a clamshell design, byte 0 comes from channel A from the top device and byte 1 comes from channel B from the bottom device and will look equivalent at the controller to a x16 mode.

**Figure 10: Byte Orientation in Clamshell Topology**

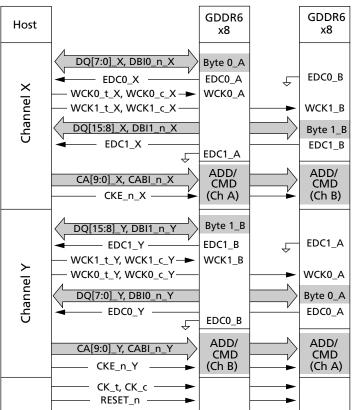

#### **Pseudo-Channel Mode**

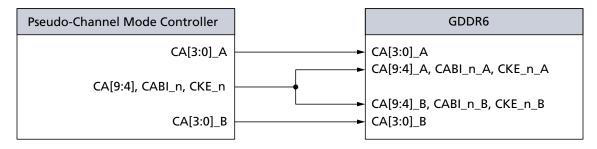

GDDR6 has been optimized for a 32B access across a 16-bit channel by providing a unique CA bus to each 16-bit-wide channel. For applications requiring fewer CA pins, GDDR6 includes support for a pseudo-channel (PC) mode where CA[9:4], CKE\_n, and CABI\_n on each channel are connected to a common bus, while CA[3:0] of each channel are connected to a separate bus. The command truth table is organized such that in PC mode the same command is decoded in both pseudo-channels, but READ and WRITE commands support a unique column address to each pseudo-channel. In PC mode, CKE n and CABI n are also shared across pseudo-channels.

In PC mode, the only difference in the DRAM is that termination on CA[9:4], CKE\_n, and CABI\_n can be configured differently from CA[3:0]. PC mode can be selected during initialization by driving CA6 = LOW on both channels when RESET\_n is driven HIGH.

**Figure 11: CA Pins in Pseudo-Channel Mode**

## **Operating Conditions**

#### **Absolute Maximum Ratings**

Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may adversely affect reliability.

**Table 5: Absolute Maximum Ratings**

| Symbol                            | Parameter                                                   | Min  | Max  | Unit | Notes |

|-----------------------------------|-------------------------------------------------------------|------|------|------|-------|

| $V_{DD}$                          | Voltage on V <sub>DD</sub> pin relative to V <sub>SS</sub>  | -0.3 | 2.0  | V    | 1     |

| V <sub>DDQ</sub>                  | Voltage on V <sub>DDQ</sub> pin relative to V <sub>SS</sub> | -0.3 | 2.0  | V    | 1     |

| V <sub>PP</sub>                   | Voltage on V <sub>PP</sub> pin relative to V <sub>SS</sub>  | -0.3 | 2.3  | V    | 2     |

| V <sub>IN</sub> /V <sub>OUT</sub> | Voltage on any pins relative to V <sub>SS</sub>             | -0.3 | 2.0  | V    |       |

| T <sub>STG</sub>                  | Storage temperature                                         | -55  | +125 | °C   | 3     |

Notes:

- 1.  $V_{DD}$  and  $V_{DDQ}$  must be within 300mV of each other at all times the device is powered-up.

- 2.  $V_{PP}$  must be equal or greater than  $V_{DD}$  and  $V_{DDQ}$  at all times the device is powered-up.

- 3. Storage temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, refer to the JESD51-2 standard.

#### **DC and AC Operating Conditions**

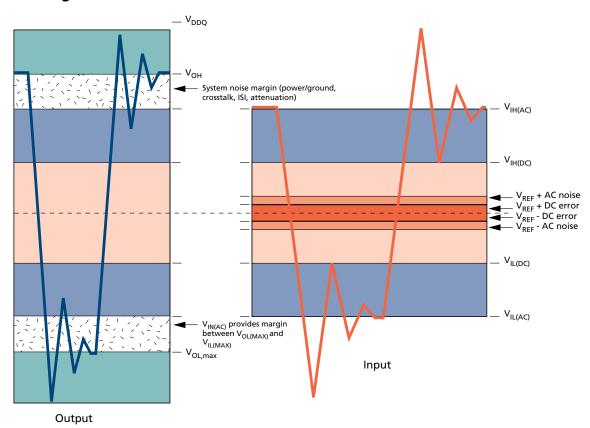

The interface of GDDR6 with  $1.35 VV_{DDQ}$  will follow the POD135 Standard (JESD8-21), Class D; The interface with  $1.25 VV_{DDQ}$  will follow the POD125 Standard (JESD8-30), Class A. All AC and DC values are referenced to the ball.

## **Table 6: DC Operating Conditions**

|                       |                                                                                                                                                                                |                           | POD135                                         |                           |                           | POD125                                         |                           |      |         |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------------|---------------------------|---------------------------|------------------------------------------------|---------------------------|------|---------|

| Symbol                | Parameter                                                                                                                                                                      | Min                       | Тур                                            | Max                       | Min                       | Тур                                            | Max                       | Unit | Notes   |

| V <sub>DD</sub>       | Device supply voltage                                                                                                                                                          | 1.3095                    | 1.35                                           | 1.3905                    | 1.2125                    | 1.25                                           | 1.2875                    | V    | 1, 2    |

| $V_{DDQ}$             | Output supply voltage                                                                                                                                                          | 1.3095                    | 1.35                                           | 1.3905                    | 1.2125                    | 1.25                                           | 1.2875                    | V    | 1, 2    |

| V <sub>PP</sub>       | Pump voltage                                                                                                                                                                   | 1.746                     | 1.8                                            | 1.908                     | 1.746                     | 1.8                                            | 1.908                     | V    | 2       |

| V <sub>REFD</sub>     | Reference voltage for DQ and DBI_n                                                                                                                                             | -                         | $0.7 \times V_{DDQ}$ or $0.725 \times V_{DDQ}$ | -                         | -                         | $0.7 \times V_{DDQ}$ or $0.725 \times V_{DDQ}$ | -                         | V    | 3, 4    |

| V <sub>REFD2</sub>    |                                                                                                                                                                                | _                         | 0.5 × V <sub>DDQ</sub>                         | -                         | -                         | $0.5 \times V_{DDQ}$                           | _                         | V    | 3, 4, 5 |

| V <sub>REFC</sub>     | Reference voltage for CA                                                                                                                                                       | 0.69 × V <sub>DDQ</sub>   | _                                              | 0.71 × V <sub>DDQ</sub>   | 0.69 × V <sub>DDQ</sub>   | _                                              | $0.71 \times V_{DDQ}$     | V    | 3, 6    |

| V <sub>REFC2</sub>    | 1                                                                                                                                                                              | 0.49 × V <sub>DDQ</sub>   | _                                              | 0.51 × V <sub>DDQ</sub>   | 0.49 × V <sub>DDQ</sub>   | _                                              | 0.51 × V <sub>DDQ</sub>   | V    | 3, 6, 7 |

| V <sub>IHA(DC)</sub>  | DC input logic HIGH voltage with V <sub>REFC</sub> for CA                                                                                                                      | V <sub>REFC</sub> + 0.135 | -                                              | -                         | V <sub>REFC</sub> + 0.125 | _                                              | -                         | V    |         |

| V <sub>ILA(DC)</sub>  | DC input logic LOW voltage with V <sub>REFC</sub> for CA                                                                                                                       | -                         | -                                              | V <sub>REFC</sub> - 0.135 | -                         | _                                              | V <sub>REFC</sub> - 0.125 | V    |         |

| V <sub>IHA2(DC)</sub> | DC input logic HIGH voltage with V <sub>REFC2</sub> for CA                                                                                                                     | V <sub>REFC2</sub> + 0.27 | -                                              | -                         | V <sub>REFC2</sub> + 0.25 | _                                              | -                         | V    |         |

| V <sub>ILA2(DC)</sub> | DC input logic LOW voltage with V <sub>REFC2</sub> for CA                                                                                                                      | -                         | _                                              | V <sub>REFC2</sub> - 0.27 | -                         | _                                              | V <sub>REFC2</sub> - 0.25 | V    |         |

| V <sub>IHD(DC)</sub>  | DC input logic HIGH voltage with V <sub>REFD</sub> for DQ and DBI_n                                                                                                            | V <sub>REFD</sub> + 0.09  | _                                              | -                         | V <sub>REFD</sub> + 0.085 | _                                              | -                         | V    |         |

| V <sub>ILD(DC)</sub>  | DC input logic LOW voltage with V <sub>REFD</sub> for DQ and DBI_n                                                                                                             | -                         | _                                              | V <sub>REFD</sub> - 0.09  | -                         | _                                              | V <sub>REFD</sub> - 0.085 | V    |         |

| V <sub>IHD2(DC)</sub> | DC input logic HIGH voltage with V <sub>REFD2</sub> for DQ and DBI_n                                                                                                           | V <sub>REFD2</sub> + 0.27 | _                                              | -                         | V <sub>REFD2</sub> + 0.25 | _                                              | -                         | V    |         |

| V <sub>ILD2(DC)</sub> | DC input logic LOW voltage with V <sub>REFD2</sub> for DQ and DBI_n                                                                                                            | -                         | _                                              | V <sub>REFD2</sub> - 0.27 | -                         | _                                              | V <sub>REFD2</sub> - 0.25 | V    |         |

| V <sub>IHR</sub>      | RESET_n and boundary scan input<br>logic HIGH voltage; EDC and CA<br>input logic HIGH voltage for<br>x16/x8 mode, PC vs. 2-channel<br>mode, CK and CA ODT select at re-<br>set | 0.8 × V <sub>DDQ</sub>    | -                                              | -                         | 0.8 × V <sub>DDQ</sub>    | -                                              | -                         | V    | 8       |

#### **Table 6: DC Operating Conditions (Continued)**

|                        |                                                                                                                                                                           |                          | POD135 |                          |                          | POD125       |                          |      |        |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------|--------------------------|--------------------------|--------------|--------------------------|------|--------|

| Symbol                 | Parameter                                                                                                                                                                 | Min                      | Тур    | Max                      | Min                      | Тур          | Max                      | Unit | Notes  |

| $V_{ILR}$              | RESET_n and boundary scan input<br>logic LOW voltage; EDC and CA in-<br>put logic LOW voltage for x16/x8<br>mode, PC vs. 2-channel mode, CK<br>and CA ODT select at reset | -                        | -      | 0.2 × V <sub>DDQ</sub>   | -                        | <del>-</del> | 0.2 × V <sub>DDQ</sub>   | V    | 8      |

| $V_{IN}$               | Single ended clock input voltage level: CK_t, CK_c, WCK_t, WCK_c                                                                                                          | -0.30                    | -      | $V_{DDQ} + 0.30$         | -0.30                    | _            | V <sub>DDQ</sub> + 0.30  | V    | 14     |

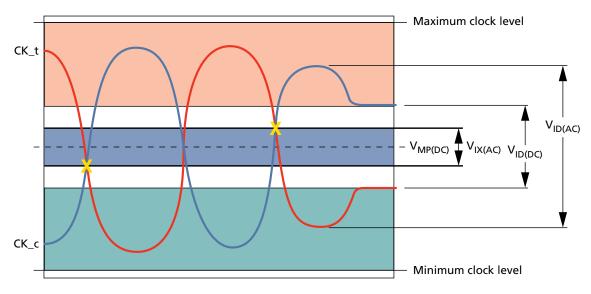

| V <sub>MP(DC)</sub>    | CK_t, CK_c clock input midpoint voltage                                                                                                                                   | V <sub>REFC</sub> - 0.10 | -      | V <sub>REFC</sub> + 0.10 | V <sub>REFC</sub> - 0.10 | -            | V <sub>REFC</sub> + 0.10 | V    | 9, 12  |

| V <sub>IDCK(DC)</sub>  | CK_t, CK_c clock input differential voltage                                                                                                                               | 0.198                    | -      | _                        | 0.18                     | -            | _                        | V    | 10, 12 |

| V <sub>IDWCK(DC)</sub> | WCK_t, WCK_c clock input differential voltage                                                                                                                             | 0.18                     | -      | _                        | 0.165                    | -            | _                        | V    | 11, 13 |

| Ι <sub>L</sub>         | Input leakage current (any input $0V \le V_{IN} \le V_{DDQ}$ ; all other signals not under test = $0V$ )                                                                  | -5                       | -      | 5                        | -5                       | -            | 5                        | μΑ   |        |

| I <sub>OZ</sub>        | Output leakage current (outputs are disabled; $0V \le V_{OUT} \le V_{DDQ}$ )                                                                                              | -5                       | -      | 5                        | <b>-</b> 5               | -            | 5                        | μΑ   |        |

| V <sub>OL(DC)</sub>    | Output logic low voltage                                                                                                                                                  | -                        | -      | 0.56                     | -                        | _            | 0.52                     | V    |        |

| ZQ                     | External resistor value                                                                                                                                                   | 115                      | 120    | 125                      | 115                      | 120          | 125                      | Ω    |        |

1. GDDR6 SGRAM devices are designed to tolerate PCB designs with separate  $V_{DD}$  and  $V_{DDO}$  power regulators. Notes:

- 2. DC bandwidth is limited to 20 MHz.

- 3. AC noise in the system is estimated at 50mV peak-to-peak for the purpose of DRAM design.

- 4. The reference voltage for DQ and DBI\_n pins is generated internally, and its values are determined by the half V<sub>RFFD</sub> and V<sub>RFFD</sub> level mode register bits. The typical V<sub>RFFD</sub> level depends on the selected data termination value (48 ohm or 60 ohm); See Mode Register 6 (MR6) for details.

- 5. Programmable  $V_{RFFD}$  levels are not supported with  $V_{RFFD2}$ .

- 6. The reference voltage source (external or internal) is determined at power-up; the reference voltage level is determined by half V<sub>REFC</sub> and the V<sub>REFC</sub> offset mode register bit.

- 7. Programmable  $V_{RFFC}$  offsets are not supported with  $V_{REFC2}$ .

- 8. VIHR and VILR apply to boundary scan input pins TDI, TMS, and TCK. VIHR and VILR apply to EDC and CA inputs at reset when latching default device configurations. VIHR and VILR also apply to CA, CABI\_n, CKE\_n, CK, DQ, DBI\_n, EDC, and WCK inputs when boundary scan mode is active and input data are latched in the capture-DR TAP controller state.

16Gb: 2 Channels x16/x8 GDDR6 SGRAM

Operating Conditions

Channels x16/x8

**Operating Conditions**

**GDDR6 SGRAM**

- 9. This provides a minimum of 0.845V to a maximum of 1.045V with POD135, and a minimum of 0.775V to a maximum of 0.975V with POD125, and is normally 70% of  $V_{DDO}$ . DRAM timings relative to CK cannot be guaranteed if these limits are exceeded.

- 10. V<sub>IDCK</sub> is the magnitude of the difference between the input level in CK\_t and the input level on CK\_c. The input reference level for signals other than CK\_t and CK\_c is V<sub>RFFC</sub>.

- 11. V<sub>IDWCK</sub> is the magnitude of the difference between the input level in WCK\_t and the input level on WCK\_c. The input reference level for signals other than WCK\_t and WCK\_c is either V<sub>REFC2</sub>, V<sub>REFC2</sub>, V<sub>REFD2</sub>.

- 12. The CK\_t and CK\_c input reference level (for timing referenced to CK\_t and CK\_c) is the point at which CK\_t and CK\_c cross. Refer to the applicable timings in the AC Timings table.

- 13. The WCK t and WCK c input reference level (for timing referenced to WCK t and WCK c) is the point at which WCK\_t and WCK\_c cross. Refer to the applicable timings in the AC Timings table.

- 14. Use V<sub>IHR</sub> and V<sub>IIR</sub> when boundary scan mode is active and input data are latched in the capture-DR TAP controller state.

Table 7: AC Operating Conditions (For Design Only<sup>9</sup>)

|                        |                                                                   | P                         | OD13 | 15                        | P                          | OD12 | 25                         |      |               |

|------------------------|-------------------------------------------------------------------|---------------------------|------|---------------------------|----------------------------|------|----------------------------|------|---------------|

| Symbol                 | Parameter                                                         | Min                       | Тур  | Max                       | Min                        | Тур  | Max                        | Unit | Notes         |

| V <sub>IHA(AC)</sub>   | AC input logic HIGH voltage with V <sub>REFC</sub> for CA         | V <sub>REFC</sub> + 0.18  | _    | -                         | V <sub>REFC</sub> + 0.165  | _    | -                          | V    |               |

| V <sub>ILA(AC)</sub>   | AC input logic LOW voltage with V <sub>REFC</sub> for CA          | -                         | _    | V <sub>REFC</sub> - 0.18  | _                          | _    | V <sub>REFC</sub> - 0.165  | V    |               |

| V <sub>IHA2(AC)</sub>  | AC input logic HIGH voltage with V <sub>REFC2</sub> for CA        | V <sub>REFC2</sub> + 0.36 | _    | -                         | V <sub>REFC</sub> + 0.333  | -    | -                          | V    |               |

| V <sub>ILA2(AC)</sub>  | AC input logic LOW voltage with V <sub>REFC2</sub> for CA         | -                         | _    | V <sub>REFC2</sub> - 0.36 | _                          | _    | V <sub>REFC</sub> - 0.333  | V    |               |

| V <sub>IHD(AC)</sub>   | AC input logic HIGH voltage with V <sub>REFD</sub> for DQ, DBI_n  | V <sub>REFD</sub> + 0.135 | -    | -                         | V <sub>REFD</sub> + 0.125  | -    | _                          | V    |               |

| V <sub>ILD(AC)</sub>   | AC input logic LOW voltage with V <sub>REFD</sub> for DQ, DBI_n   | -                         | _    | V <sub>REFD</sub> - 0.135 | _                          | _    | V <sub>REFD</sub> - 0.125  | V    |               |

| V <sub>IHD2(AC)</sub>  | AC input logic HIGH voltage with V <sub>REFD2</sub> for DQ, DBI_n | V <sub>REFD2</sub> + 0.36 | -    | -                         | V <sub>REFD2</sub> + 0.333 | -    | _                          | V    |               |

| V <sub>ILD2(AC)</sub>  | AC input logic LOW voltage with V <sub>REFD2</sub> for DQ, DBI_n  | -                         | _    | V <sub>REFD2</sub> - 0.36 | -                          | -    | V <sub>REFD2</sub> - 0.333 | V    |               |

| V <sub>IDCK(AC)</sub>  | CK_t, CK_c clock differential voltage                             | 0.36                      | -    | -                         | 0.333                      | _    | -                          | V    | 1, 3, 5       |

| V <sub>IDWCK(AC)</sub> | WCK_t, WCK_c clock input differential voltage                     | 0.27                      | -    | -                         | 0.25                       | _    | -                          | V    | 1, 4, 6       |

| V <sub>IXCK(AC)</sub>  | CK_t, CK_c clock input crossing point voltage                     | V <sub>REFC</sub> - 0.108 | -    | V <sub>REFC</sub> + 0.108 | V <sub>REFC</sub> - 0.10   | -    | V <sub>REFC</sub> + 0.10   | V    | 1, 2, 5       |

| V <sub>IXWCK(AC)</sub> | WCK_t, WCK_c clock input crossing point voltage                   | V <sub>REFD</sub> - 0.09  | _    | V <sub>REFD</sub> + 0.09  | V <sub>REFC</sub> - 0.09   | _    | V <sub>REFC</sub> + 0.09   | V    | 1, 2, 6,<br>7 |

Notes: 1. For AC operations, all DC clock requirements must be satisfied as well.

- 2. The value of  $V_{IXCK}$  and  $V_{IXWCK}$  is expected to equal 70%  $V_{DDO}$  for the transmitting device and must track variations in the DC level of the same.

- 3. V<sub>IDCK</sub> is the magnitude of the difference between the input level on CK\_t and the input level on CK\_c. The input reference level for signals other than CK\_t and CK\_c is V<sub>RFFC</sub>.

- 4. V<sub>IDWCK</sub> is the magnitude of the difference between the input level on WCK\_t and the input level on WCK\_c. The input reference level for signals other than WCK\_t and WCK\_c is either V<sub>REFC</sub>, V<sub>REFC</sub>, V<sub>REFD</sub>, or V<sub>REFD</sub>2.

- 5. The CK\_t and CK\_c input reference level (for timing referenced to CK\_t and CK\_c) is the point at which CK\_t and CK\_c cross. Refer to the applicable timings in the AC Timings table.

- 6. The WCK t and WCK c input reference level (for timing referenced to WCK t and WCK c) is the point at which WCK\_t and WCK\_c cross. Refer to the applicable timings in the AC Timings table.

- 7.  $V_{REFD}$  is either  $V_{REFD}$  or  $V_{REFD2}$ .

- 8. Figure 13 illustrates the exact relationship between (CK\_t CK\_c) or (WCK\_t WCK\_c) and V<sub>ID(AC)</sub>, V<sub>ID(DC)</sub>.

- 9. The AC operating conditions are for DRAM design only and are valid on the silicon at the input of the receiver. They are not intended to be measured.

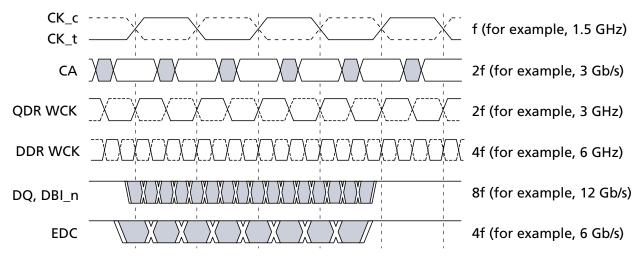

**Figure 12: Voltage Waveform**

Note: 1.  $V_{REF}$ ,  $V_{IH}$ , and  $V_{IL}$  refer to whichever  $V_{REFxx}$  ( $V_{REFD}$ ,  $V_{REFD2}$ ,  $V_{REFC2}$ , or  $V_{REFC2}$ ) is being used.

**Figure 13: Clock Waveform**

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-4000 www.micron.com/products/support Sales inquiries: 800-932-4992 Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

This data sheet contains minimum and maximum limits specified over the power supply and temperature range set forth herein. Although considered final, these specifications are subject to change, as further product development and data characterization sometimes occur.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Micron Technology: MT61K512M32KPA-14:B