# SPAFCBK-14G AC-DC Power Supply

The SPAFCBK-14G is a power-factor-corrected (PFC) power supply that converts standard AC mains power into a main output of 12 VDC for powering intermediate bus architectures (IBA) in high performance and reliability servers, routers, and network switches.

The SPAFCBK-14G meets international safety standards and displays the CE-Mark for the European Low Voltage Directive (LVD).

## **Key Features & Benefits**

- Open Compute (OCP) compliant

- Meeting 80 Plus "Platinum" Efficiency

- Wide input voltage range: 90 264 VAC

- AC input with power factor correction

- Always-On 10 W standby output (3.3 V/3 A)

- Hot-plug capable

- Active current share

- Small form factor: 321.5 x 54.5 x 40 mm (12.66 x 2.14 x 1.57 in)

- I2C communication interface for control, programming and monitoring with PSMI and Power Management Bus protocol

- Overtemperature, output overvoltage and overcurrent protection

# **Applications**

- High Performance Servers

- Routers

- Switches

# 1. ORDERING INFORMATION

| MODEL       | OUTPUT POWER | AC INPUT     | DC OUTPUT | AIRFLOW    |

|-------------|--------------|--------------|-----------|------------|

| SPAFCBK-14G | 750 W        | 90 - 264 VAC | 12 VDC    | N: Normal* |

<sup>\*</sup> Rear to front

# 2. ABSOLUTE MAXIMUM RATINGS

| PARAMETER                                  | CONDITIONS / DESCRIPTION | MIN  | NOM        | MAX | UNITS |

|--------------------------------------------|--------------------------|------|------------|-----|-------|

| Input Voltage                              |                          |      |            | 300 | VAC   |

| input voitage                              | Duration                 | 100  |            |     | ms    |

| Operating Temperature                      |                          | -5   |            | 55  | °C    |

| Storage Temperature                        | Non-operational          | -40  |            | 85  | °C    |

|                                            | Input to Case            |      | Basic      |     |       |

| Insulation Safety Rating                   | Input to Output          | F    | Reinforced |     |       |

|                                            | Output to Case           |      | Functional |     |       |

| Electric Strength Test Voltage<br>(Hi-Pot) | Input to Case            | 2121 |            |     | VDC   |

|                                            | Input to Output          | 2121 |            |     | VDC   |

|                                            | Output to Case           | 707  |            |     | VDC   |

# 3. INPUT SPECIFICATIONS

| PARAMETER                    | CONDITIONS / DESCRIPT                                      | TION                                 | MIN | NOM            | MAX | UNIT |

|------------------------------|------------------------------------------------------------|--------------------------------------|-----|----------------|-----|------|

| Input Operating Range        | Universal Input                                            |                                      | 90  | 115/230        | 264 | V    |

| Input Frequency              |                                                            |                                      | 47  | 50/60          | 63  | Hz   |

| Turn-On Voltage              |                                                            |                                      |     |                | 90  | V    |

| Turn-Off Voltage             |                                                            |                                      | 70  |                | 80  | V    |

| Input Current                | Maximum Current at V <sub>IN</sub> = 10                    | 0 V                                  |     |                | 11  | Α    |

| Input Current                | Maximum Current at V <sub>IN</sub> = 20                    | 0 V                                  |     |                | 6   | Α    |

| Turn-on Delay                | AC on                                                      |                                      | 1   |                | 3   | sec  |

| Enable / Inhibit             |                                                            |                                      |     | 150            | 200 | ms   |

| AC Line Inrush Peak Current  | @ cold turn-on                                             |                                      |     |                | 35  | Α    |

| AC Line infusit Peak Current | @ hot turn-on                                              |                                      |     |                | 50  | Α    |

| Power Factor                 | Typical, meets EN61000-3-2                                 |                                      |     | 0.99           |     |      |

| Efficiency                   | 230 V                                                      | lo (100 %)<br>lo (50 %)<br>lo (20 %) |     | 91<br>94<br>90 |     | %    |

| Hold Up Time                 | <ul><li>@ full load, low line</li><li>@ 60% load</li></ul> |                                      | 16  | 20             |     | ms   |

| Startup Time                 | @ 120 VAC, 60 Hz                                           |                                      |     |                | 3   | sec  |

| AC Leakage Current           | @ 264 VAC                                                  |                                      |     |                | 3.5 | mA   |

| Input Fusing                 | Non-user replaceable fuse in                               | the live line                        |     | 12.5           |     | Α    |

# 4. OUTPUT SPECIFICATIONS

| PARAMETER                             | CONDITIONS / DESCRIPTION                                                                                       | MIN   | NOM | MAX       | UNIT  |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------|-------|-----|-----------|-------|

| Output Voltage V1                     |                                                                                                                |       |     |           |       |

| Output Voltage                        |                                                                                                                |       | 12  |           | VDC   |

| Output Current                        |                                                                                                                |       | 62  |           | ADC   |

| Output Power                          |                                                                                                                |       | 750 |           | W     |

| Set Point Accuracy                    |                                                                                                                | -1    |     | +1        | %     |

| Line Regulation                       | Output voltage variation as input voltage changes from 85 V to 264 V with 50 % load                            |       |     | ±1        | %     |

| Load Regulation                       | Output voltage variation as load changes from 0 to 100 %                                                       |       |     | ±3        | %     |

| Total Output Voltage Range            |                                                                                                                | 11.64 |     | 12.36     | V     |

| Transient Response                    | I <sub>OUT</sub> changes 50 % of full load starting anywhere from 0 % to 50 % load, at slew rate of 1 A/μs     |       |     |           |       |

| Peak Deviation                        | Di/Dt=1A/us 50% full load change                                                                               |       | 3   | 4.2       | %     |

| Settling Time                         | Time until $V_{\text{OUT}}$ returns to regulation requirements                                                 |       | 0.5 |           | ms    |

| Ripple and Noise                      | Periodic and Random Deviation PARD ,DC to 200 MHz                                                              |       |     |           |       |

| Low Line and Full Load                | Differential Mode                                                                                              |       |     | 120       | mVp-p |

| Worst Case Condition                  | Differential and Common Mode                                                                                   |       |     | 120       | mVp-p |

| External Capacitance                  | Output Capacitance, 12V main output                                                                            | 500   |     | 11000     | uF    |

| Input Under Voltage                   |                                                                                                                | 85    |     | 90        | ٧     |

| Output Over Voltage                   | Over voltage Limit, latch off                                                                                  | 13.4  |     | 14.5      | V     |

| Output Current-limit Inception        |                                                                                                                | 120   |     | 150       | %     |

| Over-Temperature Warning and Shutdown |                                                                                                                |       |     | T(shut)-2 | °C    |

| Output Voltage V2                     |                                                                                                                |       |     |           |       |

| Output Voltage                        |                                                                                                                |       | 3.3 |           | VDC   |

| Output Current                        |                                                                                                                |       | 3   |           | ADC   |

| Set Point Accuracy                    |                                                                                                                |       | 1   |           | %     |

| Total Output Voltage Range            |                                                                                                                | 3.14  | 3.3 | 3.46      | V     |

| Ripple and Noise                      | Periodic and Random Deviation PARD DC to 200 MHz                                                               |       |     |           |       |

| Low Line and Full Load                | Differential Mode                                                                                              |       |     | 45        | mVp-p |

| Worst Case Condition                  | Differential and Common Mode                                                                                   |       |     | 45        | mVp-p |

| External Capacitance                  | 3V3 standby                                                                                                    | 20    |     | 1000      | uF    |

| Input Under Voltage                   |                                                                                                                | 80    |     | 90        | ٧     |

| Output Over Voltage                   | Over voltage Limit, latch off                                                                                  | 3.6   |     | 3.9       | ٧     |

| Output Current-limit Inception        |                                                                                                                | 120   |     | 150       | %     |

| Turn-On / Turn-Off                    |                                                                                                                |       |     |           |       |

| Turn-On Delay                         | Defined as time between after application of AC input (operating range) and Vout rising to 90% of final value. |       |     | 3         | sec   |

| Output Voltage Rise Time              | The output rise time is measured from 10% of Vnom to the lower limit of the regulation band.                   |       |     | 100       | ms    |

| Rate of output rise – dv/dt           | The output rise is Monotonic.                                                                                  |       | 100 |           | V/sec |

| Turn On Overshoot                     |                                                                                                                |       |     |           |       |

| Turn-On Overshoot                     |                                                                                                                |       |     | 5         | %     |

| Turn-Off Undershoot                   | Measured with $I_{OUT} = 4 A$ and no external load capacitor                                                   |       |     | 5         | %     |

#### 5. SIGNALING & CONTROL SPECIFICATIONS

The following section defines the input and output signals from the power supply. All digital signals should be compatible with +3.3 volt LVTTL logic levels. All control signal lines share the same return used for +3.3 volt standby (3.3 V<sub>SB</sub>).

## 5.1 POWER SUPPLY ENABLE (PS\_ON)

The PS\_ON signal is required to remotely turn on/off the power supply. PS\_ON is an active low, below 0.7 V signal that turns on the 12 VDC power rail. In the low state this input will not source more than 4 mA of current.

The 12 VDC output will be disabled when this input is driven higher than 2.1 V, or open circuited. See PS\_ON Signal Characteristics Table.

| Signal Type: Input signal to the power supply | Accepts an open collector/drain input from the system.<br>Pull-up to 3.3 V₅ located in power supply. |       |  |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------|-------|--|

| PS_ON = Low, PS_KILL = Low                    | ON                                                                                                   |       |  |

| PS_ON = Low, PS_KILL = Low                    | OFF                                                                                                  |       |  |

| PS_ON = Low, PS_KILL = Open                   | OFF                                                                                                  |       |  |

|                                               | MIN                                                                                                  | MAX   |  |

| Logic level low (power supply ON)             | 0 V                                                                                                  | 0.7 V |  |

| Logic level high (power supply OFF)           | 2.1 V                                                                                                | 3 V   |  |

| Output Source current, VPS_ON_L= low          | 4 mA                                                                                                 |       |  |

Table 1. PS\_ON Signal Characteristics

#### 5.2 POWER OK (PW\_OK)

PW\_OK is a power ok signal and will be pulled HIGH by the power supply to indicate that all the outputs are within the regulation limits of the power supply. When 12 VDC main output is < 10.9 V or > 13.2 V, or if any of the outputs fail due to over current protection, over voltage protection, over temperature, or fan failure then this output will be driven LOW. In the event AC mains power is lost, this signal must be driven LOW at least 20mS before the  $+3.3 \, V_{SB}$  output is lost. The output will be an open collector/drain. It will be capable of driving the output below 0.4V with a load of 4 mA. The start of the PW\_OK delay time is inhibited as long as any power supply's 12 VDC output is in current limit. See PW\_OK Signal Characteristics Table below.

| Signal Type: Output signal from the power supply | Open collector/drain output from the power supply. Pull-up to 3.3V located in power supply. |         |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------------|---------|--|

| PW_OK = High                                     | Power OK                                                                                    |         |  |

| PW_OK = Low                                      | Power Not OK                                                                                |         |  |

|                                                  | MIN                                                                                         | MAX     |  |

| Logic level low voltage, lsink = 4ma             | 0 V                                                                                         | 0.4 V   |  |

| Logic level high voltage, Isource = $200\mu A$   | 2.4 V                                                                                       | 3.3 V   |  |

| Input Sink current, PW_OK = Low                  |                                                                                             | 4 mA    |  |

| Output Source current, PW_OK = High              |                                                                                             | 2 mA    |  |

| PW_OK delay: (T9) TPW_OK_ON                      | 100 ms                                                                                      | 1000 ms |  |

| PW_OK rise and fall time (w/o decoupling cap)    |                                                                                             | 100 μs  |  |

| Power down delay: (T10) TPW_OK_OFF_12V           | 1 ms                                                                                        | 700 ms  |  |

Table 2. PW\_OK Signal Characteristics

## 5.3 INPUT VOLTAGE OK (AC\_OK)

This signal will be asserted, driven HIGH by the power supply to indicate that the input voltage meets the minimum requirements. After falling outside the input voltage requirements for more than 20 mSec, the signal must be driven Low. The output will be an open collector/drain. It will be capable of driving the output below 0.4 V with a load of 4 mA. See AC\_OK Signal Characteristics Table below.

| Signal Type: Output signal from the power supply | Open collector/drain output from the power supply. Pull-up to 3.3V located in power supply. |         |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------------|---------|--|

| AC_OK = High                                     | AC                                                                                          | OK      |  |

| AC_OK = Low                                      | AC Low (Not OK)                                                                             |         |  |

|                                                  | MIN                                                                                         | MAX     |  |

| Logic level low voltage, Isink = 4ma             | 0 V                                                                                         | 0.4 V   |  |

| Logic level high voltage, Isource = 200μA        | 2.4 V                                                                                       | 3.3 V   |  |

| Input Sink current, AC_OK = Low                  |                                                                                             | 4 mA    |  |

| Output Source current, AC_OK = High              |                                                                                             | 2 mA    |  |

| AC_OK delay: (T13) TAC_OK_ON                     |                                                                                             | 1500 ms |  |

| AC_OK rise and fall time (w/o decoupling cap)    |                                                                                             | 100 us  |  |

| AC_OK delay: (T8) TAC_OK_OFF                     |                                                                                             | 20 ms   |  |

Table 3. AC\_OK Signal Characteristics

# 5.4 PS\_KILL

This pin is used to force the 12 V main output off if the supply is removed from the system. At the system level this pin will be connected to the output return directly. When this input is low the power supply will operate. If the input is floating the 12 V main output will turn off while the  $3.3~V_{SB}$  will remain on. This signal overrides all other on-and-off signals. On the power supply connector, this pin is shorter than the others so it is a last-make and first-break contact. See PS\_KILL Signal Characteristics Table below.

| Signal Type: Input signal to the power supply | Accepts a ground input from the system. Pull-up to 3.3V located in the power supply. |       |  |

|-----------------------------------------------|--------------------------------------------------------------------------------------|-------|--|

| PS_KILL = Low, PS_ON = Low                    | ON                                                                                   |       |  |

| PS_KILL = Open, PS_ON = Low or Open           | OFF                                                                                  |       |  |

| PS_KILL = Low, PS_ON = Open                   | OFF                                                                                  |       |  |

|                                               | MIN                                                                                  | MAX   |  |

| Logic level low (power supply ON)             | 0 V                                                                                  | 1.0 V |  |

| Logic level high (power supply OFF)           | 2.0 V                                                                                | 3.3 V |  |

| Source current, VPSKILL = low                 |                                                                                      | 4 mA  |  |

Table 4. PS\_KILL Signal Characteristics

#### **5.5 PRESENT**

The PRESENT signal is used to sense the number of power supplies in the system (operational or not). This signal is connected to the power supply's output ground. See PRESENT Signal Characteristics Table below.

| Signal Type: Output signal from the power supply | Output from power supply that is connected to ground. Pull-up to 3.3V located in system. |       |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------|-------|--|

| PRESENT = Low                                    | Present                                                                                  |       |  |

| PRESENT = High                                   | Not Present                                                                              |       |  |

|                                                  | MIN                                                                                      | MAX   |  |

| Logic level low voltage, Isink=4mA               | 0 V                                                                                      | 0.4 V |  |

| Logic level high voltage, Isink = 50μA           |                                                                                          | 3.3 V |  |

| Sink current, PRESENT = low                      |                                                                                          | 4 mA  |  |

| Sink current, PRESENT = high                     |                                                                                          | 50 uA |  |

Table 5. PRESENT Signal Characteristics

## 5.6 SMBAlert

This signal indicates that the power supply is experiencing a problem that the user should investigate. This may be asserted due to Critical events or Warning events. See PSMI specification for further details.

| Signal Type: Output signal from the power supply | Open-drain output from power supply that is connected to ground. Pull-up to 3.3VSB located in system. |      |  |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|--|

| SMBAlert = Low                                   | Not Present                                                                                           |      |  |

| SMBAlert = High                                  | Present                                                                                               |      |  |

|                                                  | MIN                                                                                                   | MAX  |  |

| Logic level low voltage, Isink = 4mA             | 0V                                                                                                    | 0.4V |  |

| Logic level high voltage, Isink = 50μA           | -                                                                                                     | 3.3V |  |

| Sink current, SMBAlert = low                     | -                                                                                                     | 4mA  |  |

| Sink current, SMBAlert = high                    | -                                                                                                     | 50μΑ |  |

Table 6. SMBAlert Signal Characteristics

## 5.7 POWER SUPPLY INTERFACE (POWER MANAGEMENT BUS)

The Power Management Bus interface uses a serial SMBus interface for communication between the power supply(s) and the system. Power Management Bus allows the system to access status and power sensors in the power supply. The power sensors monitor both input and output power. The status monitors various critical and non-critical conditions in the power supply. One pin is the Serial Clock (SCL). The second pin is used for Serial Data (SDA). Both pins are bi-directional and are used to form a serial bus.

| Signal Type: Output signal from the power supply | Output from power supply that is connected to ground. Pull-up to 3.3VSB located in system. |      |  |

|--------------------------------------------------|--------------------------------------------------------------------------------------------|------|--|

|                                                  | MIN                                                                                        | MAX  |  |

| Logic level low voltage, Isink = 4mA             | OV                                                                                         | 0.4V |  |

| Logic level high voltage, lsink = 50μA           | -                                                                                          | 3.3V |  |

| Sink current, SCL and SDA = low                  | -                                                                                          | 4mA  |  |

| Sink current, SCL and SDA = high                 | -                                                                                          | 50uA |  |

Table 7. SCL and SDA Signal Characteristics

#### 5.8 POWER SUPPLY ADDRESSING

This signal indicates that the power supply address locations will be determined by external settings through the PS\_A0 and PS\_A1 address signals.

| Signal Type: Output signal from the power supply | Accepts a ground input from the system. Pull-up to 3.3V located in the power supply. |      |

|--------------------------------------------------|--------------------------------------------------------------------------------------|------|

|                                                  | MIN                                                                                  | MAX  |

| Logic level low voltage, Isink = 4mA             | 0V                                                                                   | 0.4V |

| Logic level high voltage, Isink = 50μA           | -                                                                                    | 3.3V |

| Sink current, PS_A0 and PS_A1 = low              | -                                                                                    | 4mA  |

| Sink current, PS_A0 and PS_A1 = high             | -                                                                                    | 50uA |

Table 8. PS\_A0 and PS\_A1 Signal Characteristics

| PS_A1 | PS_A0 | PSU_ID (MCU) Address | EEPROM Address |

|-------|-------|----------------------|----------------|

| 0     | 0     | В0                   | A0             |

| 0     | 1     | B2                   | A2             |

| 1     | 0     | B4                   | A4             |

| 1     | 1     | B6                   | A6             |

Table 9. Address Matrix

## **5.9 LOAD SHARING CONTROL**

The power supplies load share by using a single load share bus signal (ISHARE) connected between the power supplies for the 12V output. If the load sharing is disabled by shorting the load share bus to ground, the power system must continue to operate within regulation limits for loads less than or equal to the maximum specified. The failure of a power supply should not affect the load sharing or output voltages of the other supplies still operating.

# 5.10 LOAD SHARE SIGNAL CHARACTERISTICS

The load share signal provides both output current information and the load sharing function. The characteristics of the load share signal are defined below in the following table:

| ITEM                        | DESCRIPTION                                                                                                                               | MIN | NOM         | MAX | UNITS |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|-----|-------|

| Vshare; lout = max          | Voltage of load share bus at specified max output current.                                                                                | -   | 8           | -   | V     |

| dVshare/dlout; lout >1A     | Slope of load share bus voltage with changing load.                                                                                       | -   | 8 / Ioutmax | -   | V/A   |

| Ishare sink; Vshare = 8V    | Amount of current the load share bus outputs from each power supply sink.                                                                 | -   | -           | 0.5 | mA    |

| I share source; Vshare = 8V | Amount of current the load share bus outputs from each power supply source.                                                               | 4.0 | -           | -   | mA    |

| Tshare; lout = max          | Delay from output voltages in regulation to load sharing active with maximum load of one power supply and two power supplies in parallel. | -   | -           | 100 | mSec  |

Table 10. Load Share Bus Output Characteristics

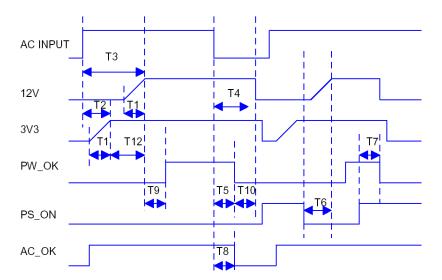

Figure 1. Timing Diagram

| PARAMETER            | MIN | TYP | MAX  | UNITS | CONDITION / COMMENTS                                                             |

|----------------------|-----|-----|------|-------|----------------------------------------------------------------------------------|

| T1 (Tout_rise)       | -   | -   | 100  | mSec  | Output voltage rise time from each main output                                   |

| T2 (Tsb_on_delay)    | -   | -   | 2500 | mSec  | Delay from AC being applied to 3V3 being within regulation                       |

| T3 (Tac_on_delay)    | -   | -   | 3000 | mSec  | Delay from AC being applied to all output voltages being within regulation       |

| T4 (Tvout_holdup)    | 16  | -   | -    | mSec  | Time all output voltages, including 3V3, stay within regulation after loss of AC |

| T5 (Tpw_ok_holdup)   | 5   | -   | -    | mSec  | Delay from loss of AC to de-assertion of PW_OK                                   |

| T6 (Tps_on_delay)    | -   | -   | 400  | mSec  | Delay from PS_ON active to output voltages within regulation limits              |

| T7 (Tps_on_pw_ok)    | -   | -   | 50   | mSec  | Delay from PS_ON de-active to PW_OK being de-<br>asserted                        |

| T8 (Tac_ok_off)      | -   | -   | 20   | mSec  | Delay from loss of AC input to de-assertion of AC_OK                             |

| T9 (Tpw_ok_on)       | 100 | -   | 1000 | mSec  | Delay from output voltages within regulation limits to PW_OK asserted at turn on |

| T10 (Tpw_ok_off_12V) | 1   | -   | 700  | mSec  | Delay from PW_OK de-asserted to 12VDC dropping out of regulation limits          |

| T11 (Tpw_ok_off_3V3) | 20  | -   | -    | mSec  | Delay from PW_OK de-asserted to 3V3 dropping out of regulation limits            |

| T12 (Tsb_vout)       | 50  | -   | 1000 | mSec  | Delay from 3V3 being in regulation to 12VDC being in regulation at AC turn on.   |

| T13 (Tac_ok_on)      | -   | -   | 1500 | mSec  | Delay from AC being applied to assertion of AC_OK                                |

Table 11.Timing Table

# 6. I<sup>2</sup>C INTERFACE

The  $l^2C$  interface should be isolated from primary circuits and be SELV rated. Provision is made to accommodate ground level shift between system  $l^2C$  ground and the supply's internal signal ground. The  $l^2C$  circuitry becomes active upon application of AC power at the input, or output to the supply. Inhibiting the output shall not affect the power to the  $l^2C$ . The signal transition region between 1 and 4 volts shall have no more than 50 mv peak-to-peak ringing. Rise and fall of these signals must be monotonic in the 1 to 4 volt region. Refer to software spec.

It is expected that the vendor supports most of the standard set of commands as per the Power Management Bus specification. However, the following set of "standard" commands MUST be supported at the minimum, either through Power Management Bus access or other methods to retrieve the information related to power efficiency.

Refer to SPAFCBK-14G Power Management Bus Communication manual for more details about the Power Management Bus Commands sets.

| COMMAND CODE | COMMAND NAME | TRANSACTION TYPE | COMMENT                                                       |

|--------------|--------------|------------------|---------------------------------------------------------------|

| 0x01         | OPERATION    | Write            | Turns on/off power supply. Command argument determines ON/OFF |

| 0x88         | READ_VIN     | Read             | Read input voltage                                            |

| 0x89         | READ_IIN     | Read             | Read input current                                            |

| 0x8B         | READ_VOUT    | Read             | Read output voltage                                           |

| 0x8C         | READ_IOUT    | Read             | Read output current                                           |

| 0x96         | READ_POUT    | Read             | Read Output Power                                             |

| 0x97         | READ_PIN     | Read             | Read Input Power                                              |

Table 12. Power Management Bus Commands

#### 7. EEPROM

A 32K bit EEPROM device (example: AT24C32CY6-YH-T) is used in the power supply for user information storage. The EEPROM address is determined by PS\_A0 & PS\_A1 settings. (Address Matrix Table). Write protection is enabled in default to prevent unintended write to the EEPROM. In order to write to the EEPROM, first the write protection needs to be disabled by sending the appropriate command to the PSU (Refer to SPAFCBK-14G Power Management Bus Communication Manual for more details).

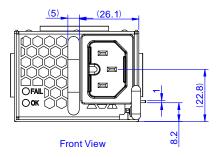

#### 8. LED INDICATORS

There will be 2 separate LED indicators, one green and one amber to indicate the power supply status. There will be a (slow) blinking green POWER LED (OK) to indicate that AC is applied to the PSU and the Standby Voltage is available. This same LED shall go steady to indicate that all the Power Outputs are available. This same LED or separate one will blink (slow) or be solid ON amber to indicate that the power supply has failed or reached a warning status and therefore a replacement of the unit is/maybe necessary.

The LED are visible on the power supply's exterior face. The LED location meets ESD Requirements.

| Power Supply Condition                                                                                              | Green (OK) LED Status | Amber (FAIL) LED Status |

|---------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|

| No AC power to all power supplies                                                                                   | OFF                   | OFF                     |

| Power Supply Failure (includes over voltage, over current, over temperature and fan failure)                        | OFF                   | ON                      |

| Power Supply Warning events where the power supply continues to operate (high temperature, high power and slow fan) | OFF                   | Blinking                |

| AC Present/ 12VSB on (PSU OFF)                                                                                      | Blinking              | OFF                     |

| Power Supply ON and OK                                                                                              | ON                    | OFF                     |

Table 13. LED Indicators

#### 9. SAFETY SPECIFICATIONS

Approved to the latest edition of the following standards: UL/CSA60950-1, IEC60950-1 and EN60950-1.

# **10. ENVIRONMENTAL SPECIFICATIONS**

| PARAMETER   | DESCRIPTION / CONDITION                                   |                          | MIN          | NOM | MAX        | UNIT |

|-------------|-----------------------------------------------------------|--------------------------|--------------|-----|------------|------|

| Temperature | Operating<br>Storage                                      |                          | -5<br>-40    |     | +55<br>+85 | °C   |

| Humidity    | Operating (non-condescending) Storage (non-condescending) |                          | +5           |     | 90<br>95   | %RH  |

| Altitude    | Operating without derating                                | up to 40°C<br>up to 55°C | 4000<br>1800 |     |            | m    |

| Reliability | MTFB (Telcordia)                                          |                          | 300          |     |            | kh   |

# 11. ELECTROMAGNETIC COMPATIBILITY

| PARAMETER                                                               | STANDARD / DESCRIPTION                                   |                          | CRITERIA   |

|-------------------------------------------------------------------------|----------------------------------------------------------|--------------------------|------------|

| Radiated Emissions                                                      | EN55022/CISPR 22 and FCC Part 15                         | Class B<br>> 0 dB margin |            |

| Conducted Emissions                                                     | EN55022/CISPR 22 and FCC Part 15                         | Class B > 0 dB margin    |            |

| Harmonics                                                               | EN61000-3-2 (AC Rated Input Current <=16 A per phase)    |                          |            |

| Harmonics                                                               | EN61000-3-12 (AC Rated Input Current >16 A and <=75 A pe | r phase)                 |            |

| Voltage Eluctuations and Elicker                                        | EN61000-3-3 (AC Rated Input Current <=16 A per phase)    |                          |            |

| Voltage Fluctuations and Flicker                                        |                                                          |                          |            |

| ESD                                                                     | EN/IEC61000-4-2 (8 kV Contact, 15 kV Air)                |                          | Criteria A |

| Radiated Immunity                                                       | IEC61000-4-3 (10 V/m)                                    |                          | Criteria A |

| EFT                                                                     |                                                          | 2 kV                     | Criteria B |

| CF1                                                                     | IEC61000-4-4 (5 kHz and 100 kHz repetition rates)        | 0.5 kV                   | Criteria A |

| Surge                                                                   | IEC61000-4-5 (4 kV CM, 2 kV DM)                          |                          | Criteria A |

| Conducted Immunity                                                      | IEC61000-4-6 (10 Vrms)                                   |                          | Criteria A |

| Power Frequency Magnetic Field                                          | IEC61000-4-8 (30 A/m)                                    |                          | Criteria A |

| Voltage dips, short interruptions and voltage variations immunity tests | IEC 61000-4-11                                           |                          |            |

| Ring Wave                                                               | IEC61000-4-12 (4 kV CM, 2 kV DM)                         |                          | Criteria A |

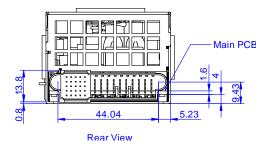

# 12. MECHANICAL SPECIFICATIONS

| PARAMETER  | DESCRIPTION / CONDITION | MIN | NOM   | MAX | UNIT |

|------------|-------------------------|-----|-------|-----|------|

|            | Width                   |     | 54.5  |     |      |

| Dimensions | Height                  |     | 40.0  |     | mm   |

|            | Depth                   |     | 333.5 |     |      |

| M Weight   |                         |     | 1.36  |     | kg   |

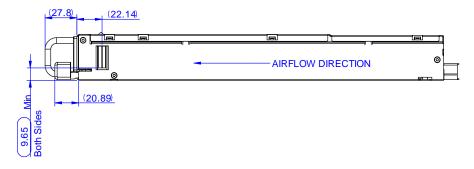

Figure 2. Side View 1

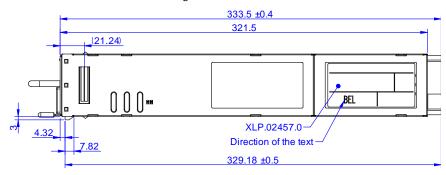

Figure 3. Top View

Figure 4. Front View

Figure 5. Rear View

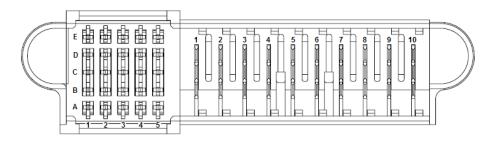

## 13, CONNECTIONS

## 13.1 OUTPUT CONNECTOR

The output connector is "Hot-pluggable" and interface with DC Power Distribution Board. The output connector shall ensure that the ground signal is connected first, then the power and interface Signals except for a final control signal, such as PSKILL and PRESENT/L which shall be connected last.

All connectors shall be capable of 100 insertions.

Manufacturer shall ensure that Safety Agency performs additional test, as applicable, to accept connector as suitable for "current interruption"

Applications as defined in UL1977. Minimum of 100 "hot" make and break Cycles.

**Asia-Pacific** +86 755 298 85888 Europe, Middle East +353 61 225 977 North America +1 408 785 5200

Unit: Tyco Electronics P/N 1926736-2 or FCI 10122460-002LF

Counter part: : Tyco Electronics P/N 2-1926739-5 or FCI 10108888-R10253SLF (Bel Power Solutions P/N: ZES.00672)

|         | PIN        | SIGNAL NAME  | LEVEL | COMMENTS                  |

|---------|------------|--------------|-------|---------------------------|

| P1- top | 6,7,8,9,10 | +12V         |       | Power contacts            |

| P2- top | 1,2,3,4,5  | Ground       |       | Power contacts            |

|         | A1         | VSB          |       |                           |

|         | B1         | VSB          |       |                           |

|         | C1         | VSB          |       |                           |

|         | D1         | VSB          |       |                           |

|         | E1         | VSB          |       |                           |

|         | A2         | SGND         |       | Signal ground             |

|         | B2         | SGND         |       | Signal ground             |

|         | C2         | reserved     |       |                           |

|         | D2         | Reserved     |       |                           |

|         | E2         | Reserved     |       |                           |

|         | A3         | PSKILL       |       | Short pin                 |

|         | B3         | Reserved     |       |                           |

|         | C3         | SDA          |       |                           |

|         | D3         | V1_SENSE_rtn |       |                           |

|         | E3         | V1_SENSE     |       |                           |

|         | A4         | SCL          |       |                           |

|         | B4         | PSON         |       |                           |

|         | C4         | ALERT        |       |                           |

|         | D4         | ISHARE       |       | 12 V current share signal |

|         | E4         | ACOK         |       |                           |

|         | A5         | A0           |       | Address 0                 |

|         | B5         | reserved     |       |                           |

|         | C5         | PWOK         |       |                           |

|         | D5         | A1           |       | Address 1                 |

|         | E5         | PRESENT_L    |       |                           |

|         |            |              |       |                           |

Table 14. Pin Description

# For more information on these products consult: tech.support@psbel.com

**NUCLEAR AND MEDICAL APPLICATIONS -** Products are not designed or intended for use as critical components in life support systems, equipment used in hazardous environments, or nuclear control systems.

**TECHNICAL REVISIONS** - The appearance of products, including safety agency certifications pictured on labels, may change depending on the date manufactured. Specifications are subject to change without notice.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Bel Power Solutions: SPAFCBK-14G