**User Manual**

**ARK-3400**

**Compact Embedded IPC**

Trusted ePlatform Services

### Copyright

The documentation and the software included with this product are copyrighted 2009 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice.

No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. Information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties, which may result from its use.

### **Acknowledgements**

Award is a trademark of Award Software International, Inc.

VIA is a trademark of VIA Technologies, Inc.

IBM, PC/AT, PS/2 and VGA are trademarks of International Business Machines Corporation.

Intel® and Pentium® are trademarks of Intel Corporation.

Microsoft Windows® is a registered trademark of Microsoft Corp.

RTL is a trademark of Realtek Semi-Conductor Co., Ltd.

ESS is a trademark of ESS Technology, Inc.

UMC is a trademark of United Microelectronics Corporation.

SMI is a trademark of Silicon Motion, Inc.

Creative is a trademark of Creative Technology LTD.

CHRONTEL is a trademark of Chrontel Inc.

All other product names or trademarks are properties of their respective owners.

For more information about this and other Advantech products, please visit our website at:

http://www.advantech.com/

http://www.advantech.com/ePlatform/

For technical support and service, please visit our support website at:

http://support.advantech.com.tw/support/

Part No. 2006K34000 Printed in China Edition 1 July 2009

### **Product Warranty (2 years)**

Advantech warrants to you, the original purchaser, that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products which have been repaired or altered by persons other than repair personnel authorized by Advantech, or which have been subject to misuse, abuse, accident or improper installation. Advantech assumes no liability under the terms of this warranty as a consequence of such events.

Because of Advantech's high quality-control standards and rigorous testing, most of our customers never need to use our repair service. If an Advantech product is defective, it will be repaired or replaced at no charge during the warranty period. For out-of-warranty repairs, you will be billed according to the cost of replacement materials, service time and freight. Please consult your dealer for more details.

If you think you have a defective product, follow these steps:

- 1. Collect all the information about the problem encountered. (For example, CPU speed, Advantech products used, other hardware and software used, etc.) Note anything abnormal and list any onscreen messages you get when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information readily available.

- If your product is diagnosed as defective, obtain an RMA (return merchandise authorization) number from your dealer. This allows us to process your return more quickly.

- 4. Carefully pack the defective product, a fully-completed Repair and Replacement Order Card and a photocopy proof of purchase date (such as your sales receipt) in a shippable container. A product returned without proof of the purchase date is not eligible for warranty service.

- 5. Write the RMA number visibly on the outside of the package and ship it prepaid to your dealer.

### **Declaration of Conformity**

#### **FCC Class A**

Note: This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

### **Technical Support and Assistance**

- Visit the Advantech web site at www.advantech.com/support where you can find the latest information about the product.

- Contact your distributor, sales representative, or Advantech's customer service center for technical support if you need additional assistance. Please have the following information ready before you call:

- Product name and serial number

- Description of your peripheral attachments

- Description of your software (operating system, version, application software,

- A complete description of the problem

- The exact wording of any error messages

### Warnings, Cautions and Notes

Warning! Warnings indicate conditions, which if not observed, can cause personal injury!

Caution! Cautions are included to help you avoid damaging hardware or losing data. e.g.

There is a danger of a new battery exploding if it is incorrectly installed. Do not attempt to recharge, force open, or heat the battery. Replace the battery only with the same or equivalent type recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.

Note!

Notes provide optional additional information.

### **Safety Instructions**

- 1. Read these safety instructions carefully.

- 2. Keep this User Manual for later reference.

- 3. Disconnect this equipment from any AC outlet before cleaning. Use a damp cloth. Do not use liquid or spray detergents for cleaning.

- 4. For plug-in equipment, the power outlet socket must be located near the equipment and must be easily accessible.

- 5. Keep this equipment away from humidity.

- 6. Put this equipment on a reliable surface during installation. Dropping it or letting it fall may cause damage.

- 7. The openings on the enclosure are for air convection. Protect the equipment from overheating. DO NOT COVER THE OPENINGS.

- 8. Make sure the voltage of the power source is correct before connecting the equipment to the power outlet.

- 9. Position the power cord so that people cannot step on it. Do not place anything over the power cord.

- 10. All cautions and warnings on the equipment should be noted.

- 11. If the equipment is not used for a long time, disconnect it from the power source to avoid damage by transient overvoltage.

- 12. Never pour any liquid into an opening. This may cause fire or electrical shock.

- 13. Never open the equipment. For safety reasons, the equipment should be opened only by qualified service personnel.

- If one of the following situations arises, get the equipment checked by service personnel:

- The power cord or plug is damaged.

- Liquid has penetrated into the equipment.

- The equipment has been exposed to moisture.

- The equipment does not work well, or you cannot get it to work according to the user's manual.

- The equipment has been dropped and damaged.

- The equipment has obvious signs of breakage.

- 14. Do not leave this equipment in an environment where the storage temperature may go below -20° C (-4° F) or above 60° C (140° F). This could damage the equipment. The equipment should be in a controlled environment.

- 15. CAUTION: Danger of explosion if battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the manufacturer, discard used batteries according to the manufacturer's instructions.

- 16. The sound pressure level at the operator's position according to IEC 704-1:1982 is no more than 70 dB (A).

- 17. RESTRICTED ACCESS AREA: The equipment should only be installed in a Restricted Access Area.

- 18. DISCLAIMER: This set of instructions is given according to IEC 704-1. Advantech disclaims all responsibility for the accuracy of any statements contained herein.

### Wichtige Sicherheishinweise

- 1. Bitte lesen sie Sich diese Hinweise sorgfältig durch.

- 2. Heben Sie diese Anleitung für den späteren Gebrauch auf.

- 3. Vor jedem Reinigen ist das Gerät vom Stromnetz zu trennen. Verwenden Sie Keine Flüssig-oder Aerosolreiniger. Am besten dient ein angefeuchtetes Tuch zur Reinigung.

- 4. Die NetzanschluBsteckdose soll nahe dem Gerät angebracht und leicht zugänglich sein.

- 5. Das Gerät ist vor Feuchtigkeit zu schützen.

- 6. Bei der Aufstellung des Gerätes ist auf sicheren Stand zu achten. Ein Kippen oder Fallen könnte Verletzungen hervorrufen.

- 7. Die Belüftungsöffnungen dienen zur Luftzirkulation die das Gerät vor überhitzung schützt. Sorgen Sie dafür, daB diese Öffnungen nicht abgedeckt werden.

- 8. Beachten Sie beim. AnschluB an das Stromnetz die AnschluBwerte.

- 9. Verlegen Sie die Netzanschlußleitung so, daß niemand darüber fallen kann. Es sollte auch nichts auf der Leitung abgestellt werden.

- 10. Alle Hinweise und Warnungen die sich am Geräten befinden sind zu beachten.

- 11. Wird das Gerät über einen längeren Zeitraum nicht benutzt, sollten Sie es vom Stromnetz trennen. Somit wird im Falle einer Überspannung eine Beschädigung vermieden.

- 12. Durch die Lüftungsöffnungen dürfen niemals Gegenstände oder Flüssigkeiten in das Gerät gelangen. Dies könnte einen Brand bzw. elektrischen Schlag auslösen.

- 13. Öffnen Sie niemals das Gerät. Das Gerät darf aus Gründen der elektrischen Sicherheit nur von authorisiertem Servicepersonal geöffnet werden. Wenn folgende Situationen auftreten ist das Gerät vom Stromnetz zu trennen und von einer qualifizierten Servicestelle zu überprüfen:

- Netzkabel oder Netzstecker sind beschädigt.

- Flüssigkeit ist in das Gerät eingedrungen.

- Das Gerät war Feuchtigkeit ausgesetzt.

- Wenn das Gerät nicht der Bedienungsanleitung entsprechend funktioniert oder Sie mit Hilfe dieser Anleitung keine Verbesserung erzielen.

- Das Gerät ist gefallen und/oder das Gehäuse ist beschädigt.

- Wenn das Gerät deutliche Anzeichen eines Defektes aufweist.

- 14. VOSICHT: Explisionsgefahr bei unsachgemaben Austausch der Batterie. Ersatz nur durch densellben order einem vom Hersteller empfohlene-mahnlichen Typ. Entsorgung gebrauchter Batterien navh Angaben des Herstellers.

- 15. ACHTUNG: Es besteht die Explosionsgefahr, falls die Batterie auf nicht fachmännische Weise gewechselt wird. Verfangen Sie die Batterie nur gleicher oder entsprechender Type, wie vom Hersteller empfohlen. Entsorgen Sie Batterien nach Anweisung des Herstellers.

- 16. Der arbeitsplatzbezogene Schalldruckpegel nach DIN 45 635 Teil 1000 beträgt 70dB(A) oder weiger.

- 17. Montageort: Das Gerät sollte nur in einem Bereich mit eingeschränktem Zugang montiert werden.

- 18. Haftungsausschluss: Die Bedienungsanleitungen wurden entsprechend der IEC-704-1 erstellt. Advantech lehnt jegliche Verantwortung für die Richtigkeit der in diesem Zusammenhang getätigten Aussagen ab.

### **Packing List**

Before installation, please ensure the following items have been shipped:

- 1 x ARK-3400 Unit

- 1 x DVI to CRT adapter connector

- 1 x Rubber foot kit

- 2 x Desk/Wall mount plate

- 1 x 4-pin Phoenix DC power connector

- 1 x Utility CD

- 1 x Registration and 2 years Warranty card

### **Ordering information**

Model Number Description

ARK-3400F-S5A1E Intel® Celeron® M 370 1.5GHz Box IPC ARK-3400F-S0A1E Intel® Celeron® M 373 1.0GHz Box IPC

### **Optional accessories**

| Part Number | Description                                                                                                 |

|-------------|-------------------------------------------------------------------------------------------------------------|

| 1757002161  | AC-to-DC Adapter, DC19 V/7.89A 150W, with Phoenix Power Plug, $0 \sim 40^{\circ}$ C for Home and Office Use |

| 1702002600  | Power cable 3-pin 180 cm, USA type                                                                          |

| 1702002605  | Power Cable 2-pin 180 cm, Europe Type                                                                       |

| 1702031801  | Power Cable 2-pin 180 cm, UK Type                                                                           |

| 1700004713  | Cable DVI-I to DVI and CRT                                                                                  |

| 1700009398  | LVDS cable for ARK-3400                                                                                     |

| 1700009396  | LVDS power cable for ARK-3400                                                                               |

| 1700009407  | Digital IO cable for ARK-3400 (Internal)                                                                    |

| 1700009405  | LPT cable for ARK-3400                                                                                      |

## **Contents**

| Chapter | 1   | General Introduction                                | 1  |

|---------|-----|-----------------------------------------------------|----|

|         | 1.1 | Introduction                                        | 2  |

|         | 1.2 | Product Feature                                     | 2  |

|         |     | 1.2.1 General                                       | 2  |

|         |     | 1.2.2 Display                                       |    |

|         |     | 1.2.3 Power Consumption                             | 2  |

|         | 1.3 | Hardware Specification                              |    |

|         | 1.4 | Mechanical Specification                            |    |

|         |     | 1.4.1 Dimensions                                    | 4  |

|         |     | Figure 1.1 ARK-3400 Mechanical Dimension Drawing    | 4  |

|         |     | 1.4.2 Weight                                        | 4  |

|         | 1.5 | Power requirement                                   | 4  |

|         |     | 1.5.1 System power                                  | 4  |

|         |     | 1.5.2 RTC battery                                   | 4  |

|         | 1.6 | Environmental Specifications                        | 5  |

|         |     | 1.6.1 Operation temperature                         | 5  |

|         |     | 1.6.2 Relative Humidity                             | 5  |

|         |     | 1.6.3 Storage temperature                           | 5  |

|         |     | 1.6.4 Vibration loading during operation            | 5  |

|         |     | 1.6.5 Shock during operation                        | 5  |

|         |     | 1.6.6 Safety                                        | 5  |

|         |     | 1.6.7 EMC                                           | 5  |

| Chapter | 2   | Hardware installation                               | 7  |

|         | 2.1 | ARK-3400 I/O Indication                             |    |

|         |     | Figure 2.1 ARK-3400 Front View                      | 8  |

|         |     | Figure 2.2 ARK-3400 Rear View                       | 8  |

|         | 2.2 | ARK-3400 Front Side External I/O Connectors         |    |

|         |     | 2.2.1 Power ON/OFF Button                           |    |

|         |     | Figure 2.3 Power ON/OFF Button                      |    |

|         |     | 2.2.2 Reset Button                                  |    |

|         |     | Figure 2.4 Reset Button                             |    |

|         |     | 2.2.3 LED Indicators                                |    |

|         |     | Figure 2.5 LED Indicators                           |    |

|         |     | 2.2.4 Audio Connector                               |    |

|         |     | Figure 2.6 Audio jack connectors                    |    |

|         |     | 2.2.5 COM Connector                                 |    |

|         |     | Figure 2.7 COM port connector                       |    |

|         |     | Table 2.1: COM standard serial port pin assignments |    |

|         |     | 2.2.6 eSATA Connector                               | _  |

|         |     | Figure 2.8 eSATA connector                          |    |

|         |     | 2.2.7 USB Connector                                 |    |

|         |     | Figure 2.9 USB connector                            |    |

|         |     | Table 2.2: USB Connector                            |    |

|         |     | 2.2.8 Compact Flash Card                            |    |

|         | 2.3 | ARK-3400 rear side external I/O connectors          |    |

|         |     | 2.3.1 Power Input Connector                         |    |

|         |     | Figure 2.10Power Input Connector                    | 11 |

|         |     | Table 2.3: Power connector pin assignments          |    |

|         |     | 2.3.2 Digital Visual Interface Connector (DVI-I)    |    |

|         |     | Figure 2.11DVI-I connector                          | 12 |

|         |     | Table 2.4: DVI-I Connector pin assignments          |    |

|         |     | 2.3.3 Ethernet Connector (LAN)                      | 13 |

|         |      |                                                                                                                                 | Figure 2.12Ethernet connector                     |                                                       |

|---------|------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------|

|         |      |                                                                                                                                 | Table 2.5: RJ-45 Connector pin assignments        |                                                       |

|         |      | 2.3.4                                                                                                                           | LVDS Connector                                    |                                                       |

|         |      |                                                                                                                                 | Figure 2.13LVDS Connector                         | 13                                                    |

|         |      |                                                                                                                                 | Table 2.6: LVDS Connector Pin Assignment          | 13                                                    |

|         |      | 2.3.5                                                                                                                           | LCD Backlight On/Off control Connector            |                                                       |

|         |      |                                                                                                                                 | Figure 2.14LCD Backlight connector                |                                                       |

|         |      |                                                                                                                                 | Table 2.7: LCD Backlight Connector Pin Assignment |                                                       |

|         |      | 2.3.6                                                                                                                           | LPT Connector                                     |                                                       |

|         |      | 2.3.0                                                                                                                           |                                                   |                                                       |

|         |      |                                                                                                                                 | Figure 2.15LPT Connector                          |                                                       |

|         |      |                                                                                                                                 | Table 2.8: LPT Connector Pin Assignment           |                                                       |

|         |      | 2.3.7                                                                                                                           | DIO Connector                                     |                                                       |

|         |      |                                                                                                                                 | Figure 2.16DIO Connector                          |                                                       |

|         |      |                                                                                                                                 | Table 2.9: DIO Connector Pin Assignment           | 15                                                    |

|         | 2.4  | Memo                                                                                                                            | ry Installation                                   | 16                                                    |

|         |      |                                                                                                                                 | Figure 2.17Memory Installation                    |                                                       |

|         | 2.5  | Compa                                                                                                                           | act Flash installation                            |                                                       |

|         |      | оор                                                                                                                             | Figure 2.18CF Card installation                   |                                                       |

|         | 2.6  | HDD ir                                                                                                                          | nstallation                                       |                                                       |

|         | 2.0  | וו טטוו                                                                                                                         | Figure 2.19HDD Installation                       |                                                       |

|         | 0.7  | DOI                                                                                                                             |                                                   |                                                       |

|         | 2.7  | PCI ca                                                                                                                          | rd installation                                   |                                                       |

|         |      |                                                                                                                                 | Figure 2.20PCI Card Installation                  |                                                       |

|         | 2.8  | Mini P                                                                                                                          | CI installation                                   |                                                       |

|         |      |                                                                                                                                 | Figure 2.21Mini PCI Card Installation             | 19                                                    |

|         | 2.9  | Antenr                                                                                                                          | na installation                                   | 20                                                    |

|         |      |                                                                                                                                 | Figure 2.22Remove the cover                       | 20                                                    |

|         |      |                                                                                                                                 | Figure 2.23Antenna installation                   |                                                       |

|         | 2.10 | Option                                                                                                                          | al Cable Installation                             |                                                       |

|         |      | G p 1.0                                                                                                                         | Figure 2.24Removable HDD Installation             |                                                       |

| Chantar | 7    |                                                                                                                                 | S cottings                                        | つつ                                                    |

| Chapter | 3    |                                                                                                                                 | S settings                                        |                                                       |

| Chapter | 3.1  | BIOS I                                                                                                                          | ntroduction                                       | 24                                                    |

| Chapter |      | BIOS S                                                                                                                          | ntroduction<br>Setup                              | 24<br>24                                              |

| Chapter | 3.1  | BIOS I                                                                                                                          | ntroductionSetup                                  | 24<br>24<br>25                                        |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1                                                                                                       | ntroductionSetupMain Menu                         | 24<br>24<br>25                                        |

| Chapter | 3.1  | BIOS S                                                                                                                          | ntroduction                                       | 24<br>24<br>25<br>25                                  |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1                                                                                                       | ntroduction                                       | 24<br>25<br>25<br>26                                  |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1                                                                                                       | ntroduction                                       | 24<br>25<br>25<br>26<br>26                            |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1                                                                                                       | ntroduction                                       | 24<br>25<br>25<br>26<br>26                            |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1                                                                                                       | ntroduction                                       | 24 25 25 26 26 28 30                                  |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3                                                                                     | ntroduction                                       | 24 25 25 26 26 28 30                                  |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                                                                            | ntroduction                                       | 24<br>25<br>25<br>26<br>26<br>28<br>30<br>30          |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3                                                                                     | ntroduction                                       | 24<br>25<br>25<br>26<br>26<br>28<br>30<br>30          |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5                                                                   | ntroduction                                       | 24<br>25<br>25<br>26<br>26<br>30<br>30<br>32<br>32    |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                                                                            | ntroduction                                       | 24 25 26 26 28 30 32 32                               |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6                                                          | ntroduction                                       | 24 25 26 26 28 30 30 32 32 34                         |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5                                                                   | ntroduction                                       | 24 24 25 26 28 30 30 32 32 34 36                      |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7                                                 | ntroduction                                       | 24 25 25 26 26 30 30 32 34 34 36 36                   |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6                                                          | ntroduction                                       | 24 24 25 26 26 30 30 32 34 34 36 36                   |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8                                        | ntroduction  Setup                                | 24 24 25 26 26 30 30 32 34 34 36 37 37                |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7                                                 | ntroduction Setup                                 | 24 24 25 26 26 30 30 32 34 34 36 37 37                |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8                                        | ntroduction  Setup                                | 24 24 25 26 26 30 30 32 34 34 36 37 37                |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9                               | ntroduction Setup                                 | 24 24 25 26 28 30 30 32 34 34 36 37 37 38             |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9                               | ntroduction                                       | 24 24 25 26 26 28 30 30 32 34 34 36 37 38 38          |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10                     | ntroduction Setup                                 | 24 24 25 26 26 30 30 32 34 34 36 37 38 38 39 39       |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10                     | ntroduction Setup                                 | 24 24 25 26 26 30 30 32 34 34 36 37 38 38 39 39       |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11           | ntroduction Setup                                 | 24 24 25 26 26 30 30 32 34 36 37 37 38 39 39 39       |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11           | ntroduction Setup                                 | 24 24 25 26 26 30 30 32 34 36 37 38 39 39 39          |

| Chapter | 3.1  | BIOS I<br>BIOS S<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11<br>3.2.12 | ntroduction Setup                                 | 24 24 25 26 26 30 30 32 34 34 36 37 38 39 39 39 39 39 |

|            | Figure 3.13Award BIOS Quit without Saving | 41             |

|------------|-------------------------------------------|----------------|

| Chapter 4  | Software Installation                     | 43             |

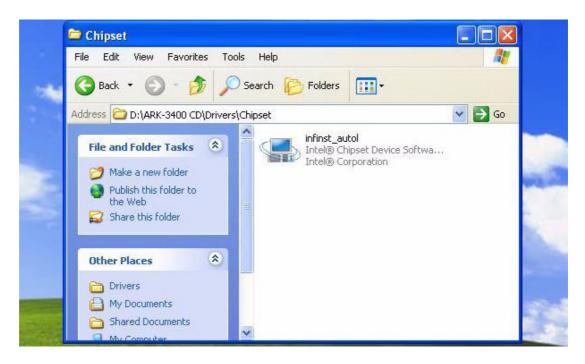

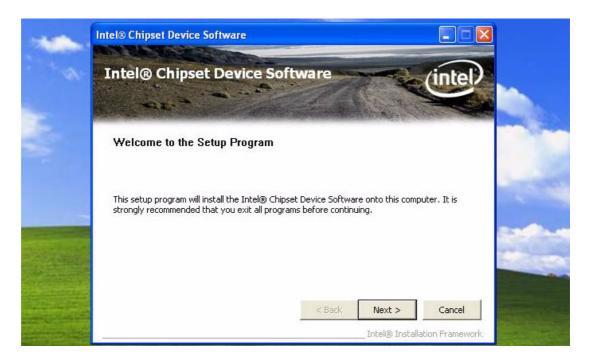

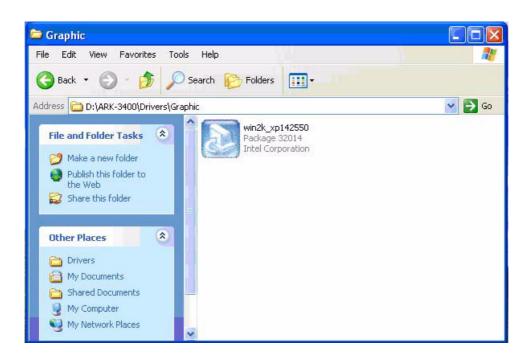

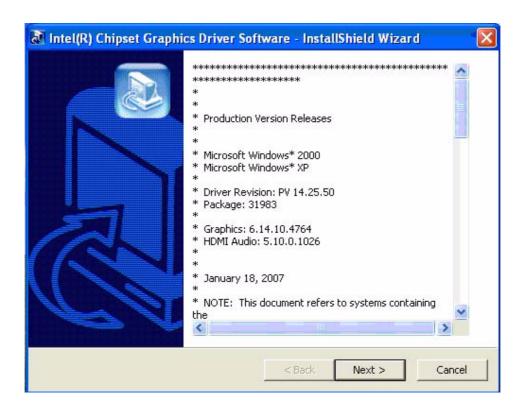

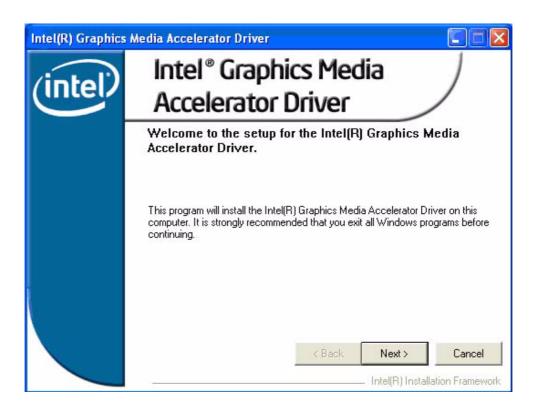

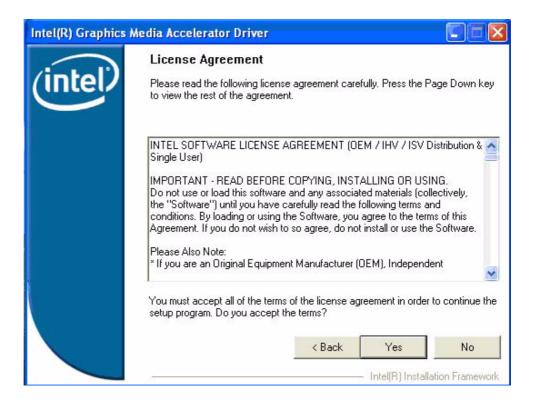

| 4.1        | Driver Installation                       | 44<br>47<br>50 |

| Appendix A | Function Settings                         | 55             |

| A.1        | Function Setting                          | 56<br>56       |

| Appendix B | Display Application                       | 59             |

| B.1        | IntroductionFigure B.1 BIOS VGA setting   |                |

| B.2<br>B.3 | LVDS  Dual Display  B.3.1 Display modes   | 60<br>60       |

| Appendix C | Application Notes                         |                |

| C.1<br>C.2 | RS-485 Auto Flow Control                  |                |

| Appendix D | Watchdog Timer                            | 69             |

| D.1        | Watchdog Timer                            | 70             |

| Appendix E | Programming GPIO                          | 71             |

| E.1<br>E.2 | Programming GPIOGPIO Programming          |                |

# Chapter

**General Introduction**

This chapter gives background information on ARK-3400 series.

### 1.1 Introduction

ARK-3400 Box IPC is an ideal application ready system platform solution. All electronics are protected in a compact sealed aluminum case for easy embedding in customers own housing, or as a stand-alone application, where space is limited and the environment harsh.

A solid sealed aluminum case provides vibration and dust resistance while also providing a passive cooling solution. The ARK-3400 provides system integrators with a turn-key solution and versatile application development path without breaking the bank or missing time to market deadlines.

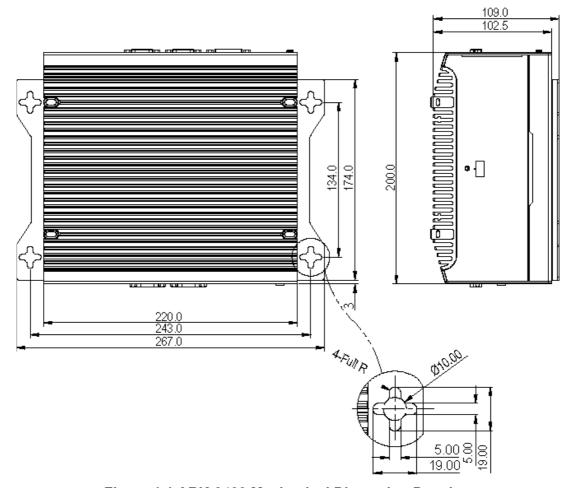

The ARK-3400 can be used as a standalone system, wall-mounted and desktop mounted. The system accepts a wide range of power supplies (DC power in) and comes in a footprint of only 220 mm x 102.5 mm x 200 mm (8.66" x 4.04" x 7.87"). The rugged cast aluminum case not only provides great protection from EMI, shock/vibration, cold and heat, but also passive cooling for quiet fanless operation.

The ARK-3400 answers this demand by offering 1 x DVI-I interface for dual display, 6 x USB 2.0 ports, 2 x Giga LAN port, audio function, 4 x COM ports, 1 x Mini PCI socket and 2 PCI expansion slots; packed into a small rugged unit and powered by an Celeron M processor. It also supports a wide range of input voltages from 12 VDC to 24 VDC. The ARK-3400 IPC supports 1 x 2.5" SATA HDD and 1 x Compact Flash card for storage options and it can provide the diversified application field.

#### 1.2 Product Feature

#### 1.2.1 General

- Intel® Mobile Celeron® at 1.5 GHz/1.0 GHz

- Dual display and support for wide screen with high resolution

- Support 2 GbE, eSATA, 6 USB 2.0 and 4 COMs

- Internal one 2.5-inch SATA HDD drive bay

- Various expansion interfaces for diverse applications

- Easy integration, easy maintenance, and wide input voltage range

#### 1.2.2 Display

- CRT display: Using a DVI to CRT adapter connector

- **Dual display:** CRT + DVI-D extended by DVI-I Y-cable (Optional)

- LVDS support: Support 48-bit LVDS interface (Optional)

#### 1.2.3 Power Consumption

- Typical: 21 W (CPU is Intel® Mobile Celeron® at 1.5 GHz and w/o expansion)

- Max.: 26 W (CPU is Intel® Mobile Celeron® at 1.5 GHz and w/o expansion)

### 1.3 Hardware Specification

- CPU: Intel® Celeron® M 370, 1.5 GHz/ Celeron® M 373, 1.0 GHz

- System Chipset: Intel® 910GMLE + ICH6M

- BIOS: AWARD<sup>TM</sup> 4 Mbit, FWH

- **System Memory:** 1 x 200-pin SODIMM socket, Support DDR2 333/400 MHz, up to 2 GB

- SSD: Supports 1 x CF Card TYPE I/II

- HDD: Supports 1 x industrial extend temperature grade 2.5" SATA HDD

- Watchdog Timer: Single chip Watchdog 255-level interval timer, setup by software

- I/O Interface: 2 x RS232, 2 x RS232/422/485 (w/ auto flow control)

- **USB:** 6 x USB 2.0 compliant Ports

- Audio: Supports Line-in, Line-out, Microphone-in

- Ethernet Chipset: 2 x Realtek 8111B (Gigabit LAN)

- Speed: 10/100/1000 MbpsInterface: 2 x RJ45 w/ LED

- Standard: IEEE 802.3z/ab (1000 Mbps) or IEEE 802.3u 100 Mbps compliant

- Expansion:

- PCI: 2 slots

- Mini PCI: 1 socket

- Chipset: Integrated graphics built in Intel® 910GMLE, Mobile Intel® Graphics Media Accelerator 900

- Memory Size: Dynamic Video Memory Technology (DVMT 3.0; Support up to 128 MB)

- Resolution:

- CRT: Up to 1920x1080 with 2 vertical taps

- DVI: Support up to UXGA (1600X1200 @ 75 Hz)

- **Dual Independent:** CRT + DVI-D (Extended by DVI-I Y-cable)

### 1.4 Mechanical Specification

#### 1.4.1 Dimensions

Figure 1.1 ARK-3400 Mechanical Dimension Drawing

### 1.4.2 Weight

3.8 kg (8.36 lb)

### 1.5 Power requirement

### 1.5.1 System power

Minimum power input: DC 14 V-24 V 4.8 A-2.8 A

### 1.5.2 RTC battery

3 V / 195 mAH BR2032

### 1.6 Environmental Specifications

### 1.6.1 Operation temperature

- With Industrial Grade CompactFlash disk: -20 ~ 55° C

- With 2.5-inch extended temperature hard disk -20 to 45° C, with air flow, speed=0.7 m/sec

#### 1.6.2 Relative Humidity

95% @ 40° C (non-condensing)

### 1.6.3 Storage temperature

-40 ~ 85° C (-40 ~ 185° F)

#### 1.6.4 Vibration loading during operation

- With CompactFlash disk: 5 Grms, IEC 60068-2-64, random, 5 ~ 500 Hz, 1 Oct./min, 1 hr/axis.

- With 2.5-inch hard disk: 1 Grms, IEC 60068-2-64, random, 5 ~ 500 Hz, 1 Oct./ min, 1 hr/axis.

#### 1.6.5 Shock during operation

- With CompactFlash disk: 50 G, IEC 60068-2-27, half sine, 11 ms duration

- With hard disk: 20 G, IEC 60068-2-27, half sine, 11 ms duration

#### **1.6.6 Safety**

UL, CCC, BSMI

#### 1.6.7 **EMC**

CE, FCC, CCC, BSMI

# Chapter

### **Hardware installation**

This chapter introduces external IO and the installation of ARK-3400 Hardware.

### 2.1 ARK-3400 I/O Indication

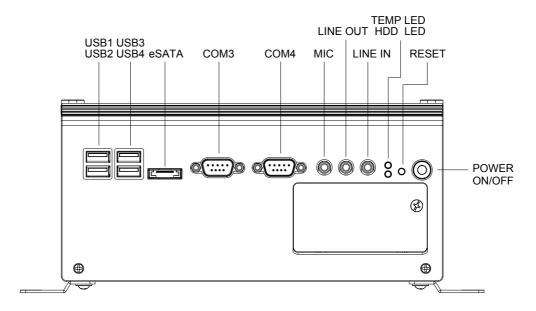

Figure 2.1 ARK-3400 Front View

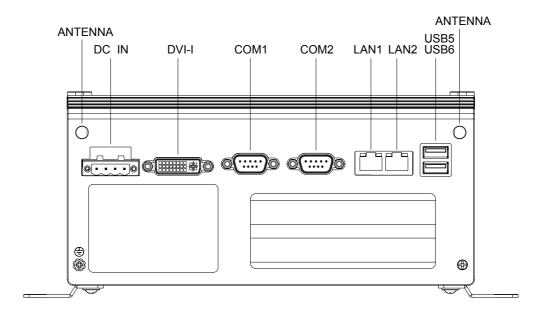

Figure 2.2 ARK-3400 Rear View

### 2.2 ARK-3400 Front Side External I/O Connectors

#### 2.2.1 Power ON/OFF Button

ARK-3400 comes with a Power On/Off button with LED indicators on the front side to show its On status (Green LED) and Off/Suspend status (Orange LED), that support dual function of Soft Power -On/Off (Instant off or Delay 4 Second), and Suspend.

Figure 2.3 Power ON/OFF Button

#### 2.2.2 Reset Button

ARK-3400 has a Reset button on front side. Press the button can to activates the reset function.

Figure 2.4 Reset Button

#### 2.2.3 LED Indicators

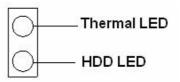

There are two LED on ARK-3400 front metal face plate for indicating system status: Thermal LED is for system thermal alarm status; and HDD LED is for HDD & compact flash disk status.

Figure 2.5 LED Indicators

#### 2.2.4 Audio Connector

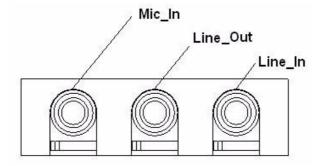

ARK-3400 offers stereo audio ports by three phone jack connectors of Line\_Out, Line\_In, Mic\_In. The audio chip controller is ALC203, Which is compliant with Azalea standard.

Figure 2.6 Audio jack connectors

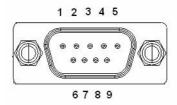

#### 2.2.5 COM Connector

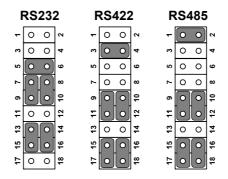

ARK-3400 provides four D-sub 9-pin connectors that are serial communication interface ports. The COM1/2 in the rear side support RS-232/422/485 by jumper setting, the COM3/4 in the front side support RS-232 only. Default setting of these four ports are RS-232.

Figure 2.7 COM port connector

|     | RS-232 RS-422 RS-485 |             |             |  |  |

|-----|----------------------|-------------|-------------|--|--|

| Pin | Signal Name          | Signal Name | Signal Name |  |  |

| 1   | DCD                  | Tx-         | DATA-       |  |  |

| 2   | RxD                  | Tx+         | DATA+       |  |  |

| 3   | TxD                  | Rx+         | NC          |  |  |

| 4   | DTR                  | Rx-         | NC          |  |  |

| 5   | GND                  | GND         | GND         |  |  |

| 6   | DSR                  | NC          | NC          |  |  |

| 7   | RTS                  | NC          | NC          |  |  |

| 8   | CTS                  | NC          | NC          |  |  |

| 9   | RI                   | NC          | NC          |  |  |

#### 2.2.6 eSATA Connector

ARK-3400 has a 7 pin external connector for eSATA device. That is fully compliant with SATA I/SATA II standards, its can be access with external SATA I/SATA II device then up to 300MB/sec.

Figure 2.8 eSATA connector

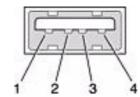

#### 2.2.7 USB Connector

ARK-3400 provides six connectors of USB interface, which give complete Plug & Play and hot swapping for up to 127 external devices. The USB interface complies with USB UHCI, Rev. 2.0 compliant. The USB interface can be disabled in the system BIOS setup. Please refer to Table. 2.2 for its pin assignments

The USB connectors are used for connecting any device that conforms to the USB interface. Many recent digital devices conform to this standard. The USB interface supports Plug and Play, which enables you to connect or disconnect a device whenever you want, without turning off the computer.

Figure 2.9 USB connector

| Table 2 | Table 2.2: USB Connector |     |             |  |  |

|---------|--------------------------|-----|-------------|--|--|

| Pin     | Signal name              | Pin | Signal name |  |  |

| 1       | VCC                      | 2   | USB_data-   |  |  |

| 3       | USB_data+                | 4   | GND         |  |  |

#### 2.2.8 Compact Flash Card

ARK-3400 is equipped with an external CF card. You can find the installation in Chapter 2.5.

### 2.3 ARK-3400 rear side external I/O connectors

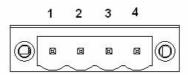

### 2.3.1 Power Input Connector

ARK-3400 comes with a four pins header that carries  $+14 \sim 24$  VDC external power input.

**Figure 2.10 Power Input Connector**

| Table 2.3: Power connector pin assignments |              |  |  |

|--------------------------------------------|--------------|--|--|

| Pin                                        | Signal Name  |  |  |

| 1                                          | GND          |  |  |

| 2                                          | +14 ~ 24 VDC |  |  |

| 3                                          | +14 ~ 24 VDC |  |  |

| 4                                          | GND          |  |  |

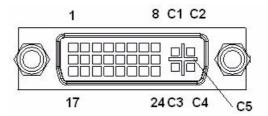

### 2.3.2 Digital Visual Interface Connector (DVI-I)

The ARK-3400 offers a integrate Digital Visual Interface connector by a D-sub 24-pin female DVI-I connector, it integrates analog and digital video signal. This supports high-speed, high-resolution digital display and traditional analog display.

Figure 2.11 DVI-I connector

| Table | Table 2.4: DVI-I Connector pin assignments |     |                        |  |  |

|-------|--------------------------------------------|-----|------------------------|--|--|

| Pin   | Signal Name                                | Pin | Signal Name            |  |  |

| 1     | TMDS Data 2-                               | 2   | TMDS Data 2+           |  |  |

| 3     | TMDS Data 2/4 shield                       | 4   | TMDS Data 4-           |  |  |

| 5     | TMDS Data 4+                               | 6   | DDC clock              |  |  |

| 7     | DDC data                                   | 8   | Analog vertical sync   |  |  |

| 9     | TMDS Data 1-                               | 10  | TMDS Data 1+           |  |  |

| 11    | TMDS Data 1/3 shield                       | 12  | TMDS Data 3-           |  |  |

| 13    | TMDS Data 3+                               | 14  | +5 V                   |  |  |

| 15    | Ground                                     | 16  | Hot plug detect        |  |  |

| 17    | TMDS data 0-                               | 18  | TMDS data 0+           |  |  |

| 19    | TMDS data 0/5 shield                       | 20  | TMDS data 5-           |  |  |

| 21    | TMDS data 5+                               | 22  | TMDS clock shield      |  |  |

| 23    | TMDS clock+                                | 24  | TMDS clock-            |  |  |

| C1    | Analog red                                 | C2  | Analog green           |  |  |

| C3    | Analog blue                                | C4  | Analog horizontal sync |  |  |

| C5    | Analog ground                              |     |                        |  |  |

#### 2.3.3 Ethernet Connector (LAN)

ARK-3400 provides two RJ45 connectors of Gb LAN interface, they are equipped with two Realtek 8111B Ethernet controllers that are fully compliant with IEEE 802.3u 10/100/1000 Mbps CSMA/CD standards. The Ethernet port provides a standard RJ-45 jack connector with LED indicators on the front side to show its Active/Link status (Green LED) and Speed status (Yellow LED).

Figure 2.12 Ethernet connector

| Table 2.5: RJ-45 Connector pin assignments |                              |  |

|--------------------------------------------|------------------------------|--|

| Pin                                        | 10/100/1000BaseT Signal Name |  |

| 1                                          | TX+                          |  |

| 2                                          | TX-                          |  |

| 3                                          | RX+                          |  |

| 4                                          | MDI2+                        |  |

| 5                                          | MDI2-                        |  |

| 6                                          | RX-                          |  |

| 7                                          | MDI3+                        |  |

| 8                                          | MDI3-                        |  |

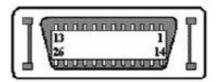

#### 2.3.4 LVDS Connector

The ARK-3400 comes with a D-Sub 26-pin connector that carries LVDS signal output, and can direct connect to LVDS LCD Display via external cable.

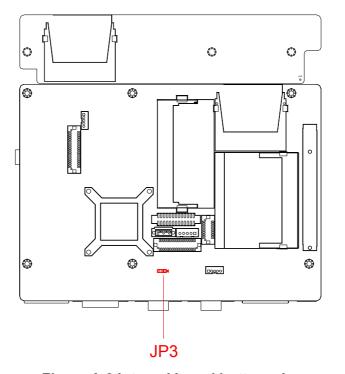

The system also provide a jumper of JP3 on internal motherboard for selecting the LCD signal power of 5V or 3.3V, please refer to the jumper table of JP3, and °×Full Disassembly Procedure°± to adjust it. Up. The default setting of JP3 is 3.3V.

Figure 2.13 LVDS Connector

| Table | 2.6: LVDS Connecto | or Pin Assignmen | t            |  |

|-------|--------------------|------------------|--------------|--|

| Pin   | Signal Name        | Pin              | Signal name  |  |

| 1     | LVDS_CLKBP         | 14               | LVDS_CLKBM   |  |

| 2     | GND                | 15               | LVDS_YAM0    |  |

| 3     | LVDS_YAP0          | 16               | LVDS_YAM1    |  |

| 4     | LVDS_YAP1          | 17               | LVDS_YAM2    |  |

| 5     | LVDS_YAP2          | 18               | LVDS_CLKAM   |  |

| 6     | LVDS_CLKAP         | 19               | GND          |  |

| 7     | +3.3 or +5 V       | 20               | +3.3 or +5 V |  |

|       |                    |                  |              |  |

| Table | 2.6: LVDS Conne | ector Pin Assignment |           |  |

|-------|-----------------|----------------------|-----------|--|

| 8     | GND             | 21                   | LVDS_YAM3 |  |

| 9     | LVDS_YAP3       | 22                   | LVDS_YBM0 |  |

| 10    | LVDS_YBP0       | 23                   | LVDS_YBM1 |  |

| 11    | LVDS_YBP1       | 24                   | LVDS_YBM2 |  |

| 12    | LVDS_YBP2       | 25                   | LVDS_YBM3 |  |

| 13    | LVDS_YBP3       | 26                   | GND       |  |

#### 2.3.5 LCD Backlight On/Off control Connector

The ARK-3400 comes with a D-Sub 9-pin connector which provides BKLTEN signal as well as +12 V, +5 V and Ground Pin signals that allow the user to connect these signals to LCD Inverter to implement the LCD On/Off control.

- Provides BKLTEN signal that inverter Module requires for inverter on/off control.

- Provides +12 V, + 5 V as the Inverter Power Source. The additional VBR signal pin could be connected to the LCD Inverter that allows the user to achieve brightness adjustment through customer's software utility.

Figure 2.14 LCD Backlight connector

| Table 2.7: LCD Backlight Connector Pin Assignment |             |  |

|---------------------------------------------------|-------------|--|

| Pin                                               | Signal name |  |

| 1                                                 | +12 V       |  |

| 2                                                 | GND         |  |

| 3                                                 | BKLTEN      |  |

| 4                                                 | VBR         |  |

| 5                                                 | +5 V        |  |

| 6                                                 | Reserved    |  |

| 7                                                 | Reserved    |  |

| 8                                                 | Reserved    |  |

| 9                                                 | Reserved    |  |

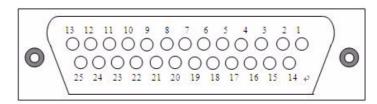

#### 2.3.6 LPT Connector

The ARK-3400 provides one D-sub 25-pin female connector, which offers printers or other communication interface port. If you want to use LPT port, you can find the Pin assignment as following.

Figure 2.15 LPT Connector

| Table 2.8 | 3: LPT Connector Pin Assi | gnment |             |

|-----------|---------------------------|--------|-------------|

| Pin       | Signal Name               | Pin    | Signal name |

| 1         | STROBE                    | 14     | ALF         |

| 2         | PD0                       | 15     | ERROR       |

| 3         | PD1                       | 16     | INIT        |

| 4         | PD2                       | 17     | SLCTIN      |

| 5         | PD3                       | 18     | GND         |

| 6         | PD4                       | 19     | GND         |

| 7         | PD5                       | 20     | GND         |

| 8         | PD6                       | 21     | GND         |

| 9         | PD7                       | 22     | GND         |

| 10        | ACK                       | 23     | GND         |

| 11        | BUSY                      | 24     | GND         |

| 12        | PE                        | 25     | GND         |

| 13        | SLCT                      |        |             |

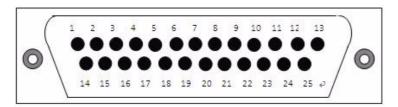

#### 2.3.7 DIO Connector

The ARK-3400 provides one D-sub 25-pin male connector, which offers Digital I/O communication interface port. If you want to use DIO port, you can find the Pin assignment as following.

Figure 2.16 DIO Connector

| Table 2.9: DIO Connector Pin Assignment |             |     |             |  |  |

|-----------------------------------------|-------------|-----|-------------|--|--|

| Pin                                     | Signal Name | Pin | Signal name |  |  |

| 1                                       | DIO0-0      | 14  | DIO1-0      |  |  |

| 2                                       | DIO0-1      | 15  | DIO1-1      |  |  |

| 3                                       | DIO0-2      | 16  | DIO1-2      |  |  |

| 4                                       | DIO0-3      | 17  | DIO1-3      |  |  |

| 5                                       | DIO0-4      | 18  | DIO1-4      |  |  |

| 6                                       | DIO0-5      | 19  | DIO1-5      |  |  |

| 7                                       | DIO0-6      | 20  | DIO1-6      |  |  |

| 8                                       | DIO0-7      | 21  | DIO1-7      |  |  |

| 9                                       | GND         | 22  | GND         |  |  |

| 10                                      | GND         | 23  | GND         |  |  |

| 11                                      | GND         | 24  | GND         |  |  |

| 12                                      | +5 V        | 25  | +5 V        |  |  |

| 13                                      | +5 V        |     |             |  |  |

### 2.4 Memory Installation

- 1. Flip the system upside down, and open the bottom cover by unscrewing the 4 screws.

- 2. Insert the memory module into the SODIMM socket.

- 3. Replace cover with screws.

Figure 2.17 Memory Installation

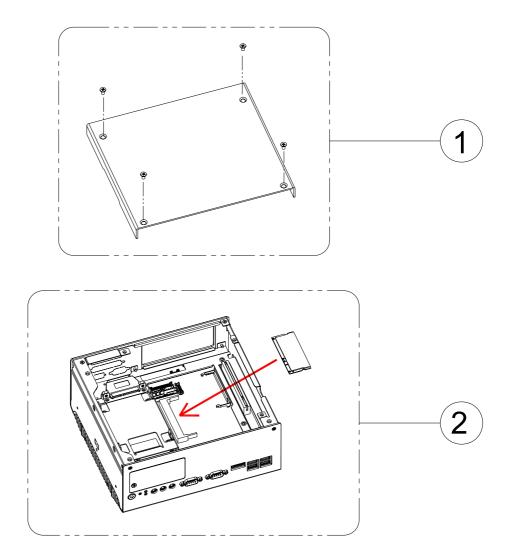

#### **Compact Flash installation** 2.5

- Open the front CF/HDD door by loosening the door screw.

- 2. Insert the CF card into the CF socket.

- 3. Reassemble.

Figure 2.18 CF Card installation

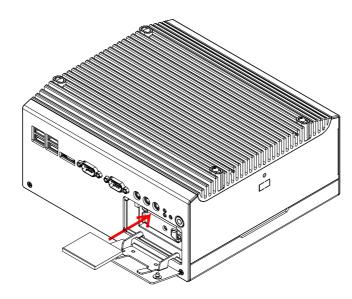

#### 2.6 **HDD** installation

- Remove the bottom cover by unscrewing the 4 screws. (Refer to Chapter 2.4)

- 2. Install the 2.5-inch SATA HDD with 4 HDD screws.

- 3. Connect the SATA signal cable and power cable to the connectors.

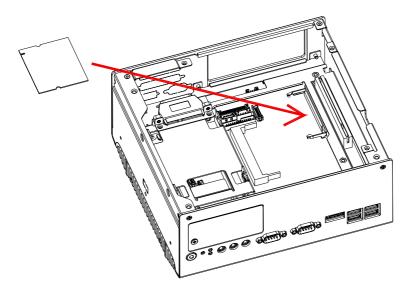

Figure 2.19 HDD Installation

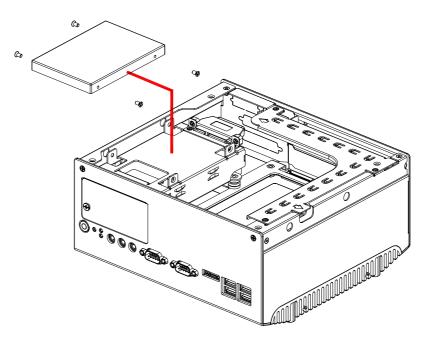

### 2.7 PCI card installation

- 1. Remove the bottom cover by unscrewing the 4 screws. (Refer to Chapter 2.4)

- 2. Remove the Riser card module.

- 3. Insert the PCI extension card into the PCI slot of the riser card module.

- 4. Reassemble the Riser card module.

- 5. Reattach the bottom cover.

Figure 2.20 PCI Card Installation

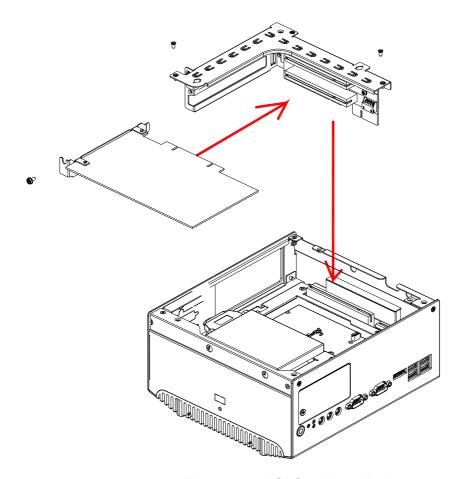

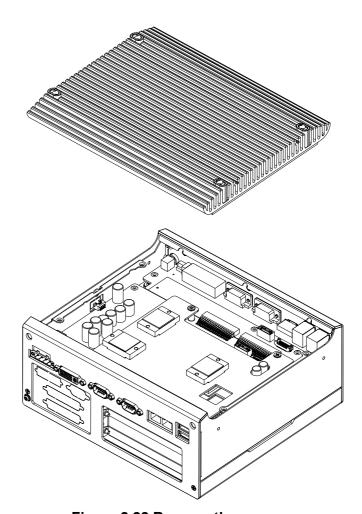

### 2.8 Mini PCI installation

- 1. Open the bottom cover and remove the Riser card module. (Refer Chapter 2.4)

- 2. Insert the Mini PCI card into the Mini PCI socket and latch it into place.

Figure 2.21 Mini PCI Card Installation

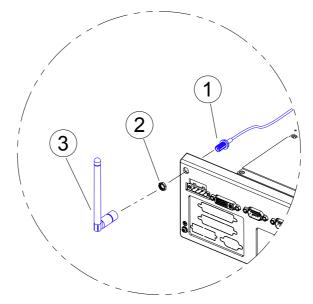

### 2.9 Antenna installation

- 1. Remove the heatsink by loosening the fixing screws.

- 2. Pass the internal antenna cable jack through the antenna hole on the rear panel and fix it by tightening the matched nut.

- 3. Put on the external antenna cable.

Figure 2.22 Remove the cover

Figure 2.23 Antenna installation

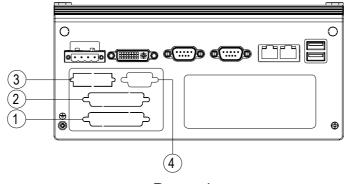

### 2.10 Optional Cable Installation

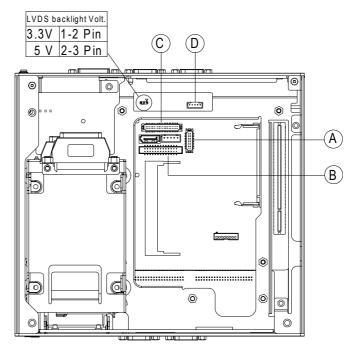

Open the bottom cover and follow the illustration and table below for optional cable installation and connection.

Rear view

Bottom view (Opened)

Figure 2.24 Removable HDD Installation

|                                     | Outer connector fixing(connection) | Inner connector fixing(connection) |

|-------------------------------------|------------------------------------|------------------------------------|

| DIO cable (P/N: 1700009407)         | 1                                  | A                                  |

| LPT cable (P/N: 1700009405)         | 2                                  | В                                  |

| LVDS cable (P/N: 1700009398)        | 3                                  | С                                  |

| LVDS power cable (P/N: 1700009396)* | 4                                  | D                                  |

Note!

When the LVDS panel power source is provided from the system, the LVDS voltage jumper needs to be selected.

# Chapter

**BIOS** settings

This chapter introduces how to set BIOS configuration data.

#### 3.1 BIOS Introduction

Advantech provides full-featured Award BIOS that delivers the superior performance, compatibility and functionality that system integrators demand.

The modular, adaptable AwardBIOS supports the broadest range of third-party peripherals and all popular chipsets, plus Intel, AMD, nVidia, VIA, and compatible CPUs from 386 through Pentium and AMD Geode, K7 and K8 (including multiple processor platforms), and VIA Eden C3 and C7 CPU.

You can use Advantech's utilities to select and install features as needed.

### 3.2 BIOS Setup

The ARK-3400 series system has build-in AwardBIOS with a CMOS SETUP utility which allows the user to configure required settings or to activate certain system features.

The CMOS SETUP saves the configuration in the CMOS RAM of the motherboard. When the power is turned off, the battery on the board supplies the necessary power to the CMOS RAM.

When the power is turned on, press the <Del> button during the BIOS POST (Power-On Self Test) will take you to the CMOS SETUP screen.

| CONTROL KEYS               |                                                      |  |

|----------------------------|------------------------------------------------------|--|

| < ↑ >< ↓ >< ← >< → >       | Move to highlight item                               |  |

| <enter></enter>            | Select Item                                          |  |

| <esc></esc>                | Main Menu - Quit and not save changes into CMOS      |  |

| \ESC>                      | Sub Menu - Exit current page and return to Main Menu |  |

| <page +="" up=""></page>   | Increase the numeric value or make changes           |  |

| <page -="" down=""></page> | Decrease the numeric value or make changes           |  |

| <f1></f1>                  | General help, for Setup Sub Menu                     |  |

| <f2></f2>                  | Item Help                                            |  |

| <f5></f5>                  | Load Previous Values                                 |  |

| <f7></f7>                  | Load Optimized Default                               |  |

| <f10></f10>                | Save all CMOS changes                                |  |

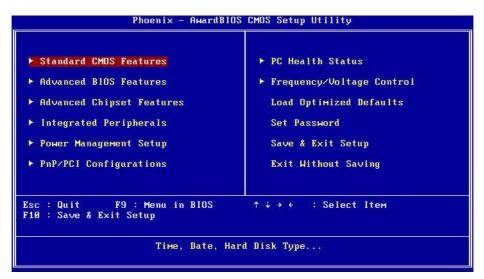

# 3.2.1 Main Menu

Press <Del> to enter AwardBIOS CMOS Setup Utility, the Main Menu will appear on the screen. Use arrow keys to select among the items and press <Enter> to accept or enter the sub-menu.

Figure 3.1 Award BIOS CMOS Setup Utility

#### Standard CMOS Features

This setup page includes all the items in standard compatible BIOS.

#### Advanced BIOS Features

This setup page includes all the items of Award BIOS enhanced features.

# Advanced Chipset Features

This setup page includes all the items of Chipset configuration features.

#### Integrated Peripherals

This setup page includes all onboard peripheral devices.

# Power Management Setup

This setup page includes all the items of Power Management features.

#### PnP/PCI Configurations

This setup page includes PnP OS and PCI device configuration.

#### PC Health Status

This setup page includes the system auto detect CPU and system temperature, voltage, fan speed.

## ■ Frequency/Voltage Control

This setup page includes CPU host clock control, frequency ratio and voltage.

#### Load Optimized Defaults

This setup page includes Load system optimized value, and the system would be in best performance configuration.

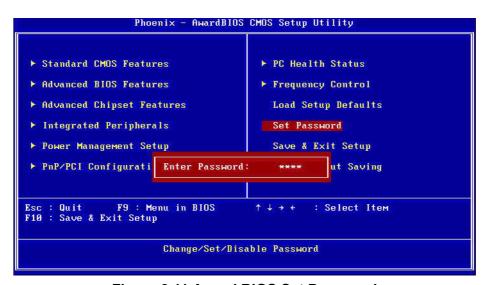

#### ■ Set Password

Establish, change or disable password.

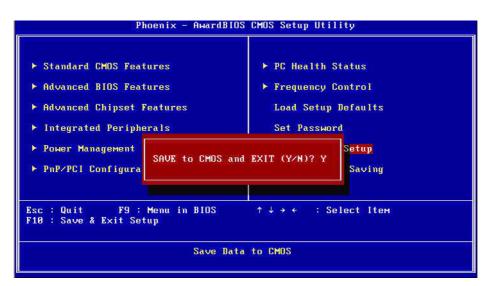

#### Save & Exit Setup

Save CMOS value settings to CMOS and exit BIOS setup.

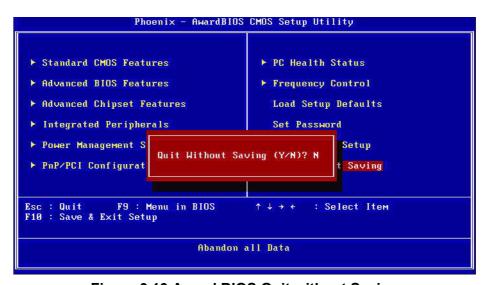

# Exit Without Saving

Abandon all CMOS value changes and exit BIOS setup.

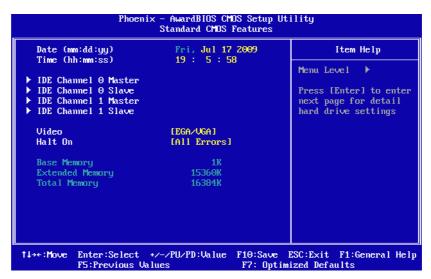

# 3.2.2 Standard CMOS Features

Figure 3.2 Award BIOS Standard CMOS Features

#### Date

The date format is <weekday>, <month>, <day>, <year>.

Weekday From Sun to Sat, determined and display by BIOS only

Month From Jan to Dec.

Day From 1 to 31

Year From 1999 through 2098

#### Time

The time format in <nour> <minute> <second>, is based on 24-hour time.

#### ■ IDE Channel 0 Master

CF Card Auto-Detection Press "Enter" for automatic device detection.

# ■ IDE Channel 2 Master

eSATA HDD Auto-Detection Press "Enter" for automatic device detection.

#### IDE Channel 2 Slave

SATA HDD Auto-Detection Press "Enter" for automatic device detection.

#### Video

The item determines that VGA display support type.

EGA/VGA Support VGA color mode.

CGA 40 Support VGA color mode.CGA 80 Support VGA color mode.MONO Support VGA mono mode.

# Halt on

The item determines whether the computer will stop if an error is detected during power up.

No Errors The system boot but will not stop for any error

All Errors Whenever the BIOS detects a non-fatal error the system

will be stopped.

All, But Keyboard The system boot will not stop for a keyboard error,

but it will stop for all other errors.

**Base Memory**

The POST of the BIOS will determine the amount of base (or conventional) memory installed in the system.

# Extended Memory

The POST of the BIOS will detect the amount of extended memory (above 1 MB in CPU's memory address map) installed in the system.

# ■ Total Memory

This item displays the total system memory size.

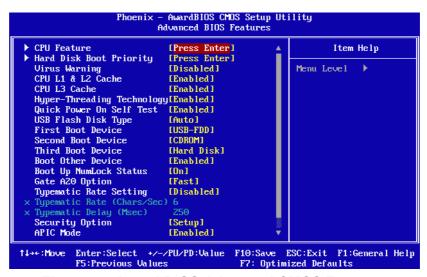

# 3.2.3 Advanced BIOS Features

Figure 3.3 Award BIOS Advanced CMOS Features

#### CPU Feature

This item allows user to adjust CPU features, CPU ratio, VID and Thermal and special features like XD flag.

### Hard Disk Boot Priority

This item allows user to select boot sequence for system device HDD, SCSI, RAID.

### Virus Warning [Disabled]

This item allows user to choose the VIRUS Warning feature for IDE Hard Disk boot sector protection.

#### ■ CPU L1 & L2 Cache [Enabled]

This item allows user to enable CPU L2 cache and ECC checking function.

### Quick Power On Self Test [Enabled]

This field speeds up the Power-On Self Test (POST) routine by skipping retesting a second, third and forth time. Setup setting default is enabled.

# USB Flash Disk Type [Auto]

This item allows user to changed flash disk format. Setup setting default is auto.

### ■ First / Second / Third / Other Boot Drive

Hard Disk Assign this boot device priority to Hard Disk. CDROM Assign this boot device priority to CDROM. USB-FDD Assign this boot device priority to USB-FDD. **USB-ZIP** Assign this boot device priority to USB-ZIP. **USB-CDROM** Assign this boot device priority to USB-CDROM. LAN1 Assign this boot device priority to LAN. LAN2 Assign this boot device priority to LAN. Disable this boot function. Disabled

#### Boot Up NumLock Status [On]

This item enables users to activate the Number Lock function at system boot.

# ■ Gate A20 Option [Fast]

This item enables users to switch A20 control by port 92 or not.

#### ■ Typematic Rate Setting [Disabled]

This item enables users to set the two typematic control items.

Typematic Rate (Chars/Sec)

The speed at which the system registers repeated keystrokes.

Eight settings are 6, 8, 10, 12, 15, 20, 24 and 30.

Typematic Delay (Msec)

This item sets the keypress delay before typematic repetition kicks in.

Four delay options are 250, 500, 750 and 1000.

# Security Option [Setup]

System Correct password must be supplied for both System boot, and

for Setup page access.

Setup Correct password must be supplied for access to Setup page.

(Default value)

# APIC Mode [Enabled]

This item allows user to enable or disable "Advanced Programmable Interrupt Controller". APIC is implemented in the motherboard and must be supported by the operating system, and it extends the number of IRQs available.

# ■ MPS Version Control for OS [1.4]

This item sets the operating system multiprocessor support version.

# OS Select For DRAM > 64 MB [Non-OS2]

Select OS2 only if the system is running the OS/2 operating system with greater than 64 MB of RAM on the system.

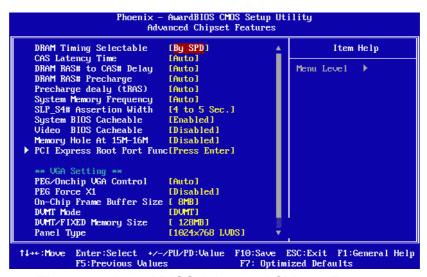

# 3.2.4 Advanced Chipset Features

Figure 3.4 Award BIOS Advanced Chipset Features

## Note!

This "Advanced Chipset Features" screen controls the configuration of the board's chipset for fine-tuning system performance. Screen options depend on the specific chipset. It is strongly recommended that only technical users make changes to the default settings.

### DRAM Timing Selectable [By SPD]

This item allows the user to set optimal timings for items 2 through 5. The system default setting of "By SPD" follows the SPD information on the ROM chip and ensures the system runs stably, with optimal performance.

#### CAS Latency Time [Auto]

This item allows the user to set the timing delay in clock cycles before SDRAM starts a read command after receiving it.

#### ■ DRAM RAS# to CAS# Delay [Auto]

This item allows the user to set the timing of the transition from RAS (row address strobe) to CAS (column address strobe) as both rows and columns are separately addressed shortly after the DRAM is refreshed.

#### DRAM RAS# Precharge [Auto]

This item allows the user to set the DRAM RAS# precharge timing. The system default is set to "Auto" to reference the data from the SPD ROM.

#### Precharge delay (tRAS) [Auto]

This item allows the user to adjust memory precharge time.

## ■ System Memory Frequency [Auto]

This item allows the user to adjust memory frequency to improve performance.

# ■ SLP\_S4# Assertion Width [4 to 5 sec.]

This item allows user to adjust SLP\_S4# signal. This field indicates the minimum assertion width of the SLP\_S4# signal to ensure that the DRAMs have been safely power-cycled.

#### System BIOS Cacheable [Enabled]

This item allows the system BIOS to be cached to allow faster execution and better performance.

# Video BIOS Cacheable [Disabled]

This item allows the video BIOS to be cached to allow faster execution and better performance.

# Memory Hole At 15 M-16 M [Disabled]

This item reserves 15MB-16MB memory address space to ISA expansion cards that specifically require the setting. Memory from 15MB-16MB will be unavailable to the system because only the expansion cards can access memory in this area.

### PCI Express Root port Func [Press Enter]

This item allows the user to adjust PCIE port on, off, or auto.

## ■ PEG/Onboard VGA Control [Auto]

This item allows the user to select whether onboard graphics processor or the PCI card.

# On-Chip Frame Buffer Size [8 MB]

This item allows the user to adjust on-chip graphics of memory buffer.

# ■ DVMT Mode [DVMT]

Intel's Dynamic Video Memory Technology (DVMT) takes that concept further by allowing the system to dynamically allocate memory resources according to the demands of the system at any point in time. The key idea in DVMT is to improve the efficiency of the memory allocated to either system or graphics processor.

The BIOS feature that controls all this is the DVMT Mode BIOS feature. It allows you to select the DVMT operating mode.

Fixed

The graphics driver will reserve a fixed portion of the system memory as graphics memory. This ensures that the graphics processor has a guaranteed amount of graphics memory but the downside is once allocated, this memory cannot be used by the operating system even when it is not in use.

**DVMT**

The graphics chip will dynamically allocate system memory as graphics memory, according to system and graphics require ments. The system memory is allocated as graphics memory when graphics-intensive applications are running but when the need for graphics memory drops, the allocated graphics memory can be released to the operating system for other uses.

вотн

The graphics driver will allocate a fixed amount of memory as dedicated graphics memory, as well as allow more system memory to be dynamically allocated between the graphics processor and the operating system.

# ■ DVMT/FIXED Memory Size [128 MB]

This item allows the user to adjust DVMT/FIXED graphics memory size.

#### Panel Type [1024 x 768 LVDS]

These fields allow you to select the LCD Panel type. The default values for these ports are:

| _ | 640 x 480   | LVDS          |

|---|-------------|---------------|

| _ | 800 x 600   | LVDS          |

| _ | 1024 x 768  | LVDS          |

| _ | 1280 x 1024 | LVDS          |

| _ | 1400 x 1050 | RB LVDS(LFP1) |

| _ | 1400 x 1050 | Non-RB (LFP1) |

# - 1600 x 1200 LVDS (LFP1)

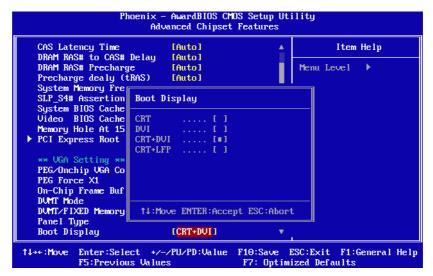

# ■ Boot Display [CRT+EFP]

This item allows the user to adjust panel resolution.

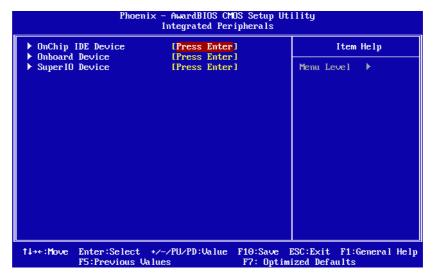

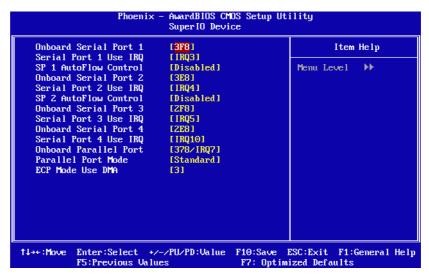

# 3.2.5 Integrated Peripherals

Figure 3.5 Award BIOS Integrated Peripherals

#### Note!

This "Integrated Peripherals" option controls the configuration of the board's chipset, includes IDE, ATA, SATA, USB, AC97, MC97 and Super IO and Sensor devices; this page depends on the particular chipset installed.

#### OnChip IDE Device

This item enables users to set the OnChip IDE device status, includes enable IDE devices and setting PIO and DMA access mode, and some of new chipset also support for SATA device (Serial-ATA).

## Onboard Device

This item enables users to set the USB, Azalia/AC97, LAN status enable or disable.

#### Super IO Device

This item enables users to set the Super IO device status, includes enable Floppy, COM, LPT, IR and control GPIO and Power fail status.

# Onboard Serial port 1 [3F8]

This item allows user to adjust serial port 1 address.

#### Serial port 1 Use IRQ [IRQ3]

This item allows user to adjust serial port 1 IRQ.

#### SP 1 AutoFlow Control [Disabled]

Auto flow control is used in RS-485, is used to tri-state the transmitter when no other data is available, so that other nodes can use the shared lines.

When auto flow control is enable, the device monitors the local output buffer for not empty and empty conditions. If enable, the flow control will force signal to the desired polarity under the empty or not empty condition.

#### Onboard Serial port 2 [3E8]

This item allows user to adjust serial port 2 address.

# Serial port 2 Use IRQ [IRQ4]

This item allows user to adjust serial port 2 IRQ.

# SP 2 AutoFlow Control [Disabled]

Auto flow control is used in RS-485, is used to tri-state the transmitter when no other data is available, so that other nodes can use the shared lines.

When auto flow control is enable, the device monitors the local output buffer for not empty and empty conditions. If enable, the flow control will force signal to the desired polarity under the empty or not empty condition.

# Onboard Serial port 3 [2F8]

This item allows user to adjust serial port 3 address.

# Serial port 3 Use IRQ [IRQ5]

This item allows user to adjust serial port 3 IRQ.

# ■ Onboard Serial port 4 [2E8]

This item allows user to adjust serial port 4 address.

# ■ Serial port 4 Use IRQ [IRQ10]

This item allows user to adjust serial port 4 IRQ.

# ■ Onboard Parallel Port [378/IRQ7]

This item allows user to adjust Parallel port address and IRQ.

# ■ Parallel Port Mode [Standard]

This item allows user to adjust parallel port mode of standard/SPP/EPP and ECP.

# ■ ECP Mode Use DMA [3]

This item allows user to adjust ECP DMA resource.

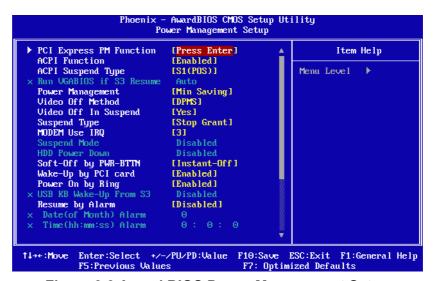

# 3.2.6 Power Management Setup

Figure 3.6 Award BIOS Power Management Setup

#### Note!

This "Power Management Setup" screen configures the system to most effectively save energy while operating in a manner consistent with your computer use.

- PCI Express PM Function [Press Enter]

- PCI Express PME [Enabled]

This item allows user to select boot sequence for Enabled(default)/Disable.

# ■ ACPI Function [Enabled]

This item defines the ACPI (Advanced Configuration and Power Management) feature that makes hardware status information available to the operating system, and communicate PC and system devices for improving the power management.

#### ACPI Suspend Type [S1 (POS)]

This item allows user to select sleep state when suspend.

S1(POS) The suspend mode is equivalent to a software power down;

S3(STR) The system shuts down with the exception of a refresh current to the system memory.

#### ■ Run VGA BIOS if S3 Resume [Auto]

This item allows system to reinitialize VGA BIOS after system resume from ACPI S3 mode.

#### ■ Power Management [User Define]

This item allows user to select system power saving mode.

Min Saving Minimum power management. Suspend Mode=1 hr.

Max Saving Maximum power management. Suspend Mode=1 min.

User Define Allows user to set each mode individually. Suspend Mode= Disabled or 1 min ~1 hr.

#### ■ Video Off Method [DPMS]

This item allows user to determine the manner is which the monitor is blanked.

V/H SYNC+Blank This option will cause system to turn off vertical and horizontal synchronization ports and write blanks to the

video buffer.

Blank Screen This option only writes blanks to the video buffer.

DPMS Initial display power management signaling.

# Video Off In Suspend [Yes]

This item allows user to turn off Video during system enter suspend mode.

# Suspend Type [Stop Grant]

This item allows user to determine the suspend type.

# ■ Modem use IRQ [3]

This item allows user to determine the IRQ which the MODEM can use.

# Suspend Mode [Disabled]

This item allows user to determine the time of system inactivity, all devices except the CPU will be shut off.

# ■ HDD Power Down Mode [Disabled]

This item allows user to determine the time of system inactivity, the hard disk drive will be powered down.

# Soft-Off by PWR-BTTN [Instant-Off]

This item allows user to define function of power button.

Instant-Off Press power button then Power off instantly.

Delay 4 Sec Press power button 4 sec. to Power off.

# ■ Wake-Up by PCI card [Enabled]

This item allows user to defines PCI cards to wake up the system from the suspend mode.

# Power On by Ring [Enabled]

This item allows the user to enable and define how the system will resume by activation of the modem ring.

#### ■ Resume by Alarm [Disabled]

This item allows user to enable and key in Date/time to power on system

Disabled Disable this function.

Enabled Enable alarm function to power on system

Data (of month) Alarm1-31

Time (HH:MM:SS) Alarm(0-23): (0-59): 0-59)

# Reload Global Timer Events

Primary IDE 0 [Disabled]

Primary IDE 1 [Disabled]

Secondary IDE 0 [Disabled]

Secondary IDE 1 [Disabled]

FDD,COM,FPT Port [Disabled]

PCI PIRQ[A-D]# [Disabled]

Power Fail Function [Always Off]

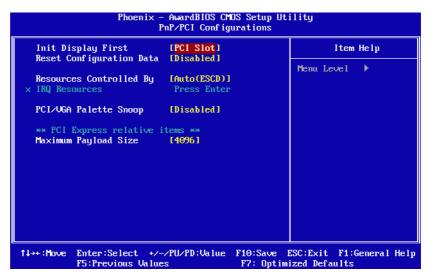

# 3.2.7 PnP/PCI Configurations

Figure 3.7 Award BIOS PnP/PCI Configurations

# Note!

Use this "PnP/PCI Configurations" option for setting up the IRQ and DMA (both PnP and PCI) bus assignments.

# ■ Init Display First [PCI Slot]

This item is setting for start up Video output from PCI or Onboard device.

#### Reset Configuration Data [Disabled]

This item allow user to clear any PnP configuration data stored in the BIOS.

# ■ Resources Controlled By [Auto (ESCD)]

IRQ Resources

This item allows you respectively assign an interruptive type for IRQ-3, 4, 5, 7, 9, 10, 11, 12, 14, and 15.

# ■ PCI VGA Palette Snoop [Disabled]

The item is designed to solve problems caused by some non-standard VGA cards. A built-in VGA system does not need this function.

# ■ Maximum payload Size [4096]

The item allows user to adjust maximum TLP (Transaction Layer Packet) payload size.

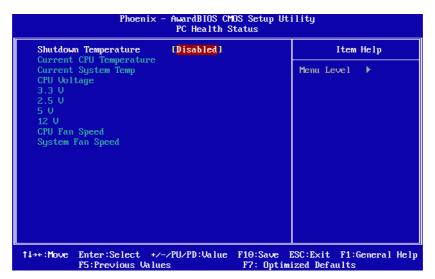

# 3.2.8 PC Health Status

Figure 3.8 Award BIOS PC Health Status

#### Note!

This "PC Health Status" screen reports the thermal, fan and voltage status of the board. This page depends on the particular chipset installed.

- Shutdown Temperature [Disabled]

This item control when to notify ACPI OS to shut down the system.

- Current CPU Temperature [Show Only]

This item displays current CPU temperature.

- Current System Temperature [Show Only]

This item displays current System temperature.

- VCC Core /+3.3V /+2.5V /+5V/ +12V [Show Only]

This item displays current CPU and system voltage.

- CPU/System Fan Speed [Show Only]

This item displays CPU/System fan speed.

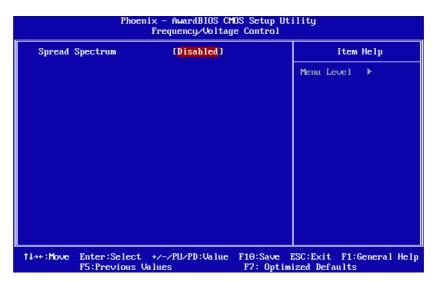

# 3.2.9 Frequency/voltage Control

Figure 3.9 Award BIOS Frequency/Voltage Control

# Note!

This "Frequency/Voltage Control" screen controls the CPU Host and PCI frequency, this page this page depends on the particular CPU and chipset installed; some items will only show up when you install a processor which supports those functions.

# ■ Spread Spectrum [Disabled]

This item enables users to set the spread spectrum modulation.

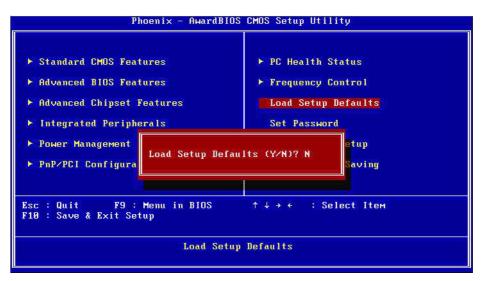

Figure 3.10 Award BIOS Load Setup Defaults

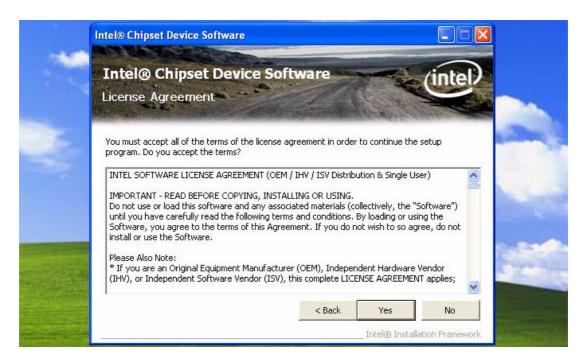

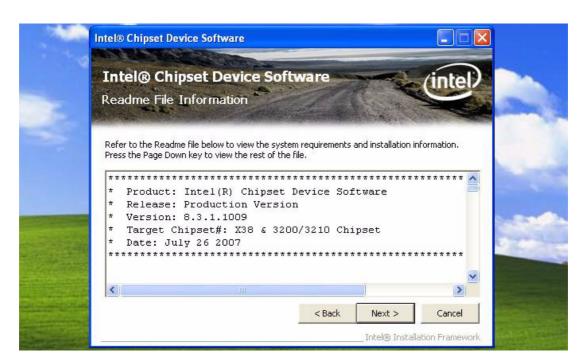

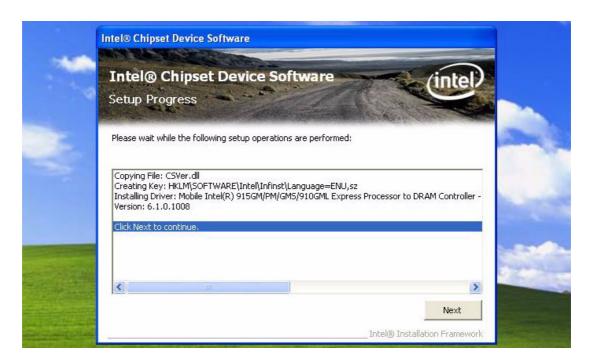

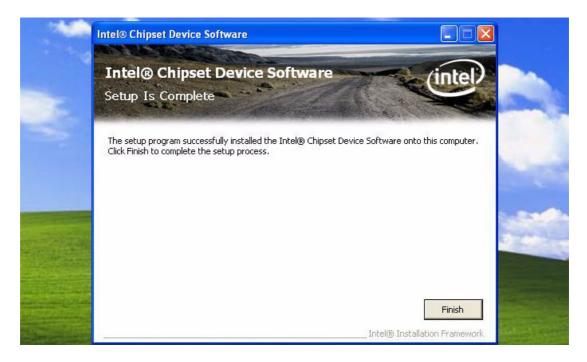

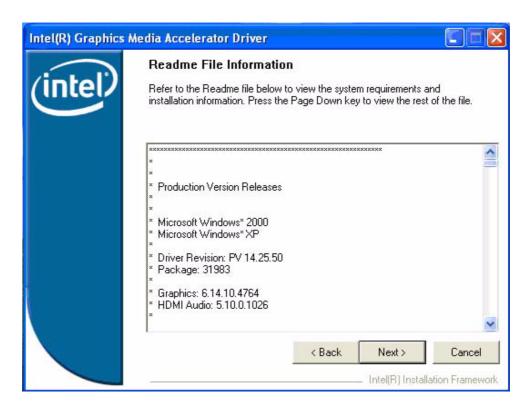

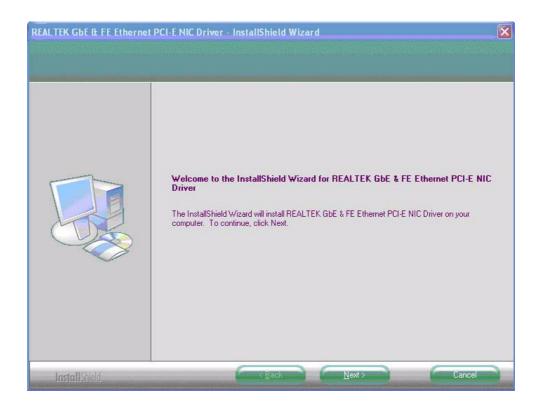

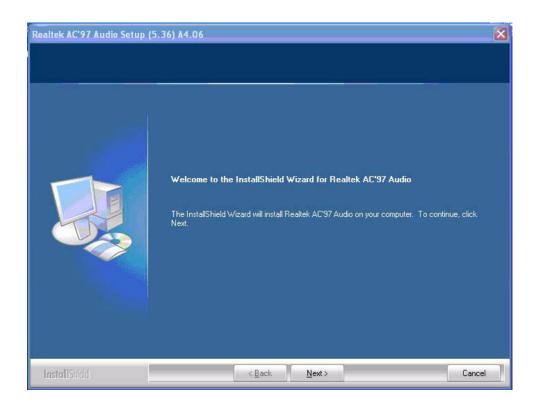

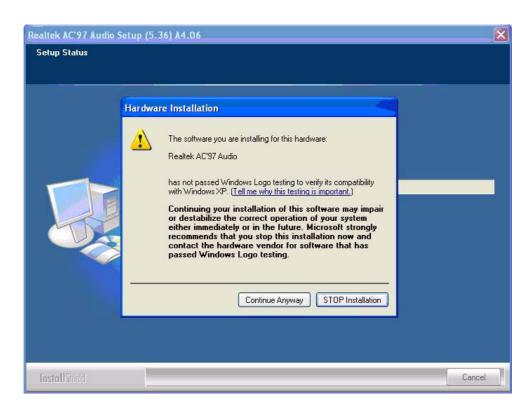

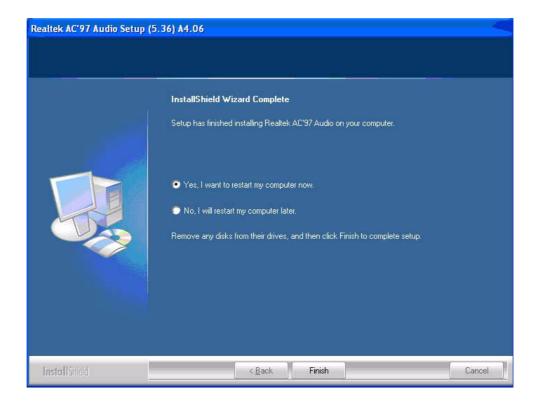

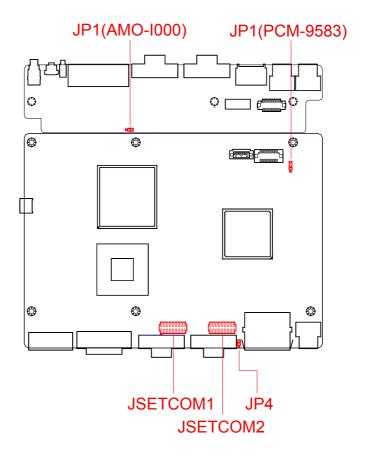

#### Note!