| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

# **ENGINEERING SPECIFICATIONS**

**Product Name:**

CA3-8D256 CA3-8D512 CA3-GD1024

M.2 PCle Gen3 x 4 Lane SSD

Author: Caleto Yang

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

| Version | History                     | Date       |

|---------|-----------------------------|------------|

| 1.0     | First Release               | 2017/04/21 |

| 1.1     | 區分 CA3-8DXXX 跟 CA3-GDXXX 機種 | 2017/12/22 |

|         | Considential                |            |

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

# Copyright 2016 LITE-ON IT CORPORATION Disclaimer

The information in this document is subject to change without prior notice in order to improve reliability, design, and function and does not represent a commitment on the part of the manufacturer. In no event will the manufacturer be liable for direct, indirect, special, incidental, or consequential damages arising out of the use or inability to use the product or documentation, even if advised of the possibility of such damages.

This document contains proprietary information protected by copyright.

All rights are reserved. No part of this datasheet may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of LITEON IT Corporation.

DOC NO

: 9C10000127

Rev.

Issued Date

: 2017/04/21

V1.1

Revised Date

: 2017/12/22

| Table of C | Contents                              |           |

|------------|---------------------------------------|-----------|

| 1          | Introduction                          | 5         |

| 1.1        | Overview:                             | 5         |

| 1.2        | Product Specification                 | 6         |

| 1.3        | Functional Block Diagram              | . 17      |

| 1.4        | Mechanical Drawing:                   | . 18      |

| 1.5        | Architecture                          | . 19      |

| 1.6        | Bootable Device:                      | . 19      |

| 1.7        | Power Mode Support                    | . 20      |

| 2          | Pin Locations and Signal Descriptions | 21        |

| 2.1        | Pin Locations                         | . 21      |

| 2.2        | M.2 Socket Definition                 | . 22      |

| 2.3        | Socket 3 PCle-based SSD Module Pinout | . 23      |

| 3          | PCI Express                           | 24        |

| 3.1        | Interface                             | . 24      |

| 3.2        | Auxiliary Signals                     | . 24      |

| 3.3        | Reference Clock                       | . 24      |

| 3.4        | UART Interface                        |           |

| 4          | Admin Command Sets                    | <b>30</b> |

| 4.1        | Admin Command                         | . 30      |

| 4.2        | Namespace Feature Set                 | . 30      |

| 4.3        | Security Feature Set                  | . 31      |

| 5          | NVMe Command Sets                     | <b>32</b> |

| 5.1        | NVMe Command                          | . 32      |

| 5.2        | Power Management Feature Set          | . 32      |

| 6          | References                            | 33        |

| 7          | Terms and Acronyms                    |           |

| 8          | Endurance                             |           |

| DOC NO       | : 9C10000127 | Rev.   |

|--------------|--------------|--------|

| Issued Date  | : 2017/04/21 | V1 1   |

| Revised Date | : 2017/12/22 | V 1. I |

# 1 Introduction

#### 1.1 Overview:

The CA3-8DXXX/CA3-GDXXXX PCIe Gen3 x 4 Lane series Solid State Drive (SSD) delivers leading performance in an industry standard M.2 type 2280-S3-M/2280-D3-M form factor while simultaneously improving system responsiveness for applications over standard rotating drive media or hard disk drives. By combining leading NAND flash memory technology with our innovative high performance firmware, LITEON IT delivers a SSD for PCIe hard disk drive drop-in replacement with enhanced performance, reliability, ruggedness and power savings. Since there are no rotating platters, moving heads, fragile actuators, or unnecessary delays due to spin-up time or positional seek time that can slow down the storage subsystem, significant I/O and throughput performance improvement is achieved as compared to rotating media or hard disk drives. This document describes the specifications of the CA3-8DXXX/CA3-GDXXXX PCIe Gen3 x 4 Lane series M.2 SSD in M.2 type 2280-S3-M/2280-D3-M form factors.

The CA3-8DXXX/CA3-GDXXXX PCle Gen3 x 4 Lane series M.2 SSD primarily targets M.2 based laptop PCs, highly rugged client devices, as well as thin and light mini/sub-notebooks. Key attributes include high performance, low power, increased system responsiveness, high reliability, and enhanced ruggedness as compared to standard hard drives. The CA3-8DXXX/CA3-GDXXXX PCle Gen3 x 4 Lane series M.2 SSD is available in M.2 type 2280-S3-M/2280-D3-M form factor that are electrically, mechanically, and software compatible with existing M.2 slots. Our flexible design allows interchangeability with existing hard drives based on the M.2 interface standard.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

# 1.2 Product Specification

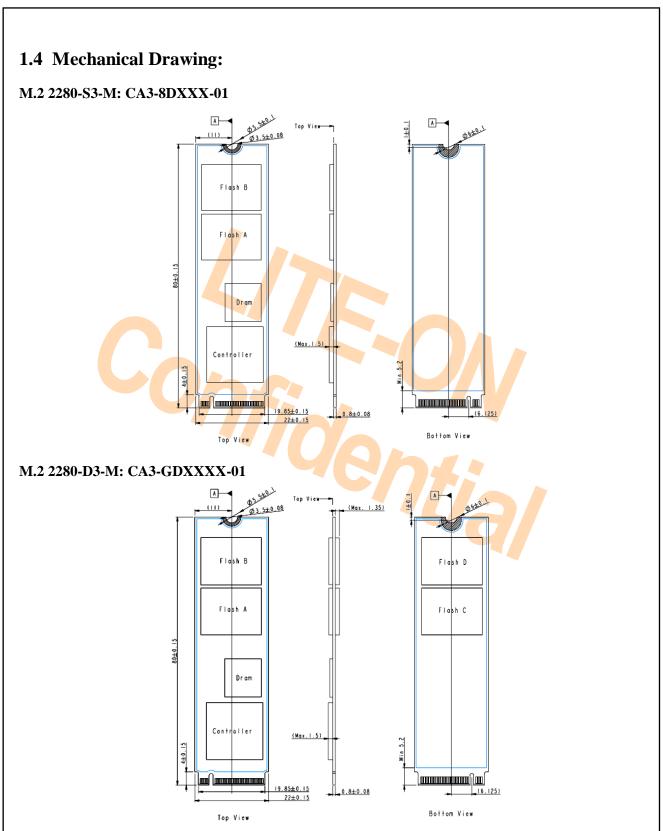

**1.2.1.** Form Factor: M.2 type 2280-S3-M/2280-D3-M SSD form factor

1.2.2. Capacity: available now

M.2 2280-S3-M 256/512GB (CA3-8D256/512)

M.2 2280-D3-M 1024GB (CA3-GD1024)

Table 1 User Addressable Sectors

| Unformatted capacity | Total user addressable sectors in LBA mode |

|----------------------|--------------------------------------------|

| 256GB                | 500,118,192                                |

| 512GB                | 1,000,215,216                              |

| 1024GB               | 2,000,409,264                              |

#### Notes:

- 1). 1GB=1,000,000,000 bytes and not all of the memory can be used for storage.

- 2). 1 Sector = 512 bytes

#### 1.2.3. Flash:

Triple-Level Cell (TLC) component with Toggle-Mode

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

#### 1.2.4. Band Performance

Table 2 Maximum Sustained Read and Write Bandwidth on Windows 10 platform

| Capacity | Access Type                 | MB/s |

|----------|-----------------------------|------|

|          | Sequential Read             | 2800 |

| 256 GB   | Sequential Write            | 800  |

|          | Sequential Write (TLC mode) | 280  |

|          | Sequential Read             | 3000 |

| 512 GB   | Sequential Write            | 1600 |

|          | Sequential Write (TLC mode) | 500  |

|          | Sequential Read             | 3000 |

| 1024 GB  | Sequential Write            | 2000 |

|          | Sequential Write (TLC mode) | 900  |

- 1). Performance measured using Crystal Disk Mark 5.0.2, QD32 T1, 1GiB test size, 5 cycles.

- 2). PCle link speed is gen3x4.

- 3). Write cache enabled & 4K boundary data.

- 4). Test by secondary drive (data drive & clean state).

- 5). Performance based on internal testing on Z87 platform/ Intel i5-4570K 3.2Ghz/ ASUS Z87-A Windows 10; Performance may vary on different platforms, NVMe driver and OS.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

#### 1.2.5. Read and Write IOPS

#### Table 3 Random Read/Write Input/Output Operations per Second on Windows 10 platform

| Capacity | Access Type     | IOPS |

|----------|-----------------|------|

| 256 GB   | 4K Read (IOPS)  | 150K |

| 230 GB   | 4K Write (IOPS) | 150K |

| 512 GB   | 4K Read (IOPS)  | 300K |

| 312 GB   | 4K Write (IOPS) | 260K |

| 1024 GB  | 4K Read (IOPS)  | 380K |

| 1024 GB  | 4K Write (IOPS) | 260K |

- 1). Performance measured using Crystal Disk Mark 5.0.2, QD32 T4, 1GiB test size, 5 cycles.

- 2). Test by secondary drive (data drive & clean state).

- 3). PCle link speed is gen3x4.

- 4). Performance based on internal testing on Z87 platform/ Intel i5-4570K 3.2Ghz/ ASUS Z87-A Windows 10; Performance may vary on different platforms, NVMe driver and OS.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

#### 1.2.6. Ready Time

#### **Table 4 Latency Specifications**

| Туре              | Average Latency |

|-------------------|-----------------|

| Power on to Ready | 1 sec           |

#### Notes:

- 1). Write cache enabled

- 2). Device measured using Drive Master

- 3). PCIe link speed is gen3x4.

- 4). Test results may be different on different platform.

- 5). Power on to ready time assumes proper shutdown (Power removal preceded by host Shutdown Notification)

#### 1.2.7. Compatibility

- -- NVM Express Specification

- -- PCI Express Base Specification

- -- PCI Express M.2 Electromechanical Specification

- -- Microsoft latest WHCK Certification

- -- Support Legacy and UEFI BIOS

- -- TCG Storage Security Subsystem Class: OPAL

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

#### **1.2.8.** Supported Operating System and Chipset

--Operating System

Windows 7 x86, x64 / Windows 8 x86, x64 / Windows 10

Linux series, Red Hat 6.5, Fedora, SUSE, Ubuntu

Windows Server 2008, 2012

--Chipset:

\*\*Please make sure the BIOS of the used mother board be updated to the latest version.

#### Table 5 Tested platform w/o issues

| Manufacturer | Platform            | Chipset                      | Manufacturer | Platform    | Chipset                  |

|--------------|---------------------|------------------------------|--------------|-------------|--------------------------|

| Echo 13      | Alienware<br>AW13R2 | Intel Sunrise Point-LP       | Precision    | 7440 AIO    | Intel Sunrise Point Q170 |

| Echo 15      | Alienware<br>AW15R2 | Intel Sunrise Point<br>HM170 | Precision    | 3420 SFF    | Intel Sunrise Point C236 |

| Echo 17      | Alienware<br>AW17R3 | Intel Sunrise Point<br>HM170 | Precision    | 3620MT      | Intel Sunrise Point C236 |

| XPS 13       | 9350                | Intel Sunrise Point-LP       | Optiplex     | 3040 MT     | Intel Sunrise Point H110 |

| Precision    | 5510                | Intel Sunrise Point CM236    | Optiplex     | 3240 AIO    | Intel Sunrise Point H110 |

| XPS 15       | 9550                | Intel Sunrise Point<br>HM170 | ASUS         | Z170 DELUXE | Intel Sunrise Point Z170 |

| Inspiron 15  | 7568                | Intel Sunrise Point-LP       |              |             |                          |

| Optiplex     | 3040 MT             | Intel Sunrise Point H110     |              |             |                          |

| OptiPlex     | 3240 AIO            | Intel Sunrise Point M110     |              |             |                          |

| ProDesk      | 490 G3 MT           | Intel Sunrise Point H170     |              |             |                          |

| ProDesk      | 600 G2 DM           | Intel Sunrise Point Q150     |              |             |                          |

| Inspiron     | 5559                | Intel Sunrise Point-LP       |              |             |                          |

| Inspiron 11  | 3153                | Intel Sunrise Point-LP       |              |             |                          |

| Inspiron 13  | 7353                | Intel Sunrise Point-LP       |              |             |                          |

| Predator 15  | G9-591              | Intel Sunrise Point<br>HM170 |              |             |                          |

| MS           | Surface Pro 4       | Intel Sunrise Point-LP       |              |             |                          |

| XPS Desktop  | 8900                | Intel Sunrise Point Z170     |              |             |                          |

| Alienware    | X51 R3              | Intel Sunrise Point Z170     |              |             |                          |

| OptiPlex     | 7040 SFF            | Intel Sunrise Point Q170     |              |             |                          |

| OptiPlex     | 5040 SFF            |                              |              |             |                          |

DOC NO

: 9C10000127

Rev.

Issued Date

: 2017/04/21

V1.1

Revised Date

: 2017/12/22

# Table 6 Tested platform w/ issue

|              | Highlighted Platforms / Motherboards with known issue |             |  |

|--------------|-------------------------------------------------------|-------------|--|

| Manufacturer | Chipset                                               | Description |  |

|              |                                                       |             |  |

|              |                                                       |             |  |

|              |                                                       |             |  |

|              |                                                       |             |  |

|              |                                                       |             |  |

|              |                                                       |             |  |

|              |                                                       |             |  |

|              |                                                       |             |  |

|              |                                                       |             |  |

|              | 50h                                                   |             |  |

|              |                                                       | 100001      |  |

|              |                                                       | 1/4/2/      |  |

|              | <u> </u>                                              |             |  |

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

#### 1.2.9. Certifications

#### **Table 7 Device Certifications**

| Certification  | Description                                               |  |

|----------------|-----------------------------------------------------------|--|

|                | Indicates conformity with the essential health and safety |  |

| CE compliant   | requirements set out in European Directives Low voltage   |  |

|                | Directive and EMC Directive                               |  |

| III poutified  | Underwriters Laboratories, Inc. Component Recognition     |  |

| UL certified   | UL60 <mark>95</mark> 0-1                                  |  |

|                | Compliance to the Taiwan EMC standard "Limits and         |  |

| BSMI           | methods of Radio Disturbance Characteristics of           |  |

|                | Information Technology Equipment, CNS 13438 Class B"      |  |

| Microsoft WHQL | Microsoft Windows Hardware Quality Labs                   |  |

| RoHS compliant | Restriction of Hazardous Substance Directive              |  |

#### 1.2.10. PCle M.2 interface Power Management

3.3V Input/ Max current (RMS): 3A

### 1.2.11. Power Consumption

**Table 8 Operating Voltage & Current**

| Description                         | Min   | Max   | Unit |

|-------------------------------------|-------|-------|------|

| Operating voltage for 3.3V (+/- 5%) | 3.135 | 3.465 | V    |

#### **Table 9 Power Consumption**

| Capacity | Operation  | Max | Unit |

|----------|------------|-----|------|

|          | Start-up   | 6   | W    |

| 1024 GB  | Read-Write | 8   | W    |

| DOC NO       | : 9C10000127 | Rev.   |

|--------------|--------------|--------|

| Issued Date  | : 2017/04/21 | V1 1   |

| Revised Date | : 2017/12/22 | V 1. I |

#### 1.2.12. Temperature

**Table 10 Temperature Relative Specifications**

| Environment | Mode          | Min | Max | Unit |

|-------------|---------------|-----|-----|------|

| Ambient     | Operating     | 0   | 70  | °C   |

| Temperature | Non-operating | -40 | 85  | °C   |

|             | Operation     | 5   | 95  | %    |

| Humidity    | Non-operation | 5   | 95  | %    |

#### Note:

Measured without condensation

#### 1.2.13. Reliability

Table 11 Reliability specifications

| Parameter                        | Value             |

|----------------------------------|-------------------|

| Mean Time between Failure (MTBF) | > 1,500,000 hours |

| Power on/off cycle <sup>2</sup>  | 50,000 cycles     |

- 1).MTBF is calculated based on a Part Stress Analysis. It assumes nominal voltage with all other parameters within specified range.

- 2). Power on/off cycles is defined as power being removed from the drive, and the restored. Most host systems remove power from the drive when entering suspend and hibernate as well as on a system shutdown.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

#### 1.2.14. Shock and Vibration

#### **Table 12 Shock and Vibration**

| Item                   | Mode          | Timing/Frequency      | Max      |

|------------------------|---------------|-----------------------|----------|

| Shock <sup>1</sup>     | Non-operating | At 0.5 msec half-sine | 1500G    |

| Vibration <sup>2</sup> | Non-operation | 2-500 Hz              | 3.1 Grms |

- 1). Shock specifications assume that the SSD is mounted securely with the input vibration applied to the drive mounting screws. Stimulus may be applied in the X, Y or Z axis.

- 2). Vibration specifications assume that the SSD is mounted securely with the input vibration applied to the drive mounting screws. Stimulus may be applied in the X, Y or Z axis. The measured specification is in root mean squared form.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

#### 1.2.15. Electrostatic discharge (ESD)

Electromagnetic Immunity tests assume the SSD is properly installed in the representative host system. The drive operates properly without errors degradation in performance when subjected to radio frequency (RF) environments defined in the following table.

**Table 13 Radio Frequency Specifications**

| Test                           | Description                                                                               | Performance criteria | Reference standard           |

|--------------------------------|-------------------------------------------------------------------------------------------|----------------------|------------------------------|

| Electrostatic discharge        | Con <mark>tact ±4</mark> KV Air: ±8KV                                                     | Α                    | IEC 61000-4-2:2008           |

| Electrostatic discharge        | Contact ±6KV Air: ±12KV                                                                   | В                    | IEC 61000-4-2:2008           |

| Electrostatic discharge        | Contact ±8KV Air: ±15KV                                                                   | С                    | IEC 61000-4-2:2008           |

| Radiated RF immunity           | 80~1000MHz, 3V/m, 80% AM with 1 KHz sine<br>900 MHz, 3 V/m, 50% pulse modulation at 200Hz | A                    | IEC 61000-4-3:2008           |

| Electrical fast transient      | ±1KV on AC mains ±0.5KV on external I/O                                                   | В                    | +Corr.1:2006<br>+Corr.2:2007 |

| Surge immunity                 | ±1KV differential ±2KV common, AC mains                                                   | В                    | IEC 61000-4-5:2005           |

| Conducted RF immunity          | 150KHz~80 MHz, 3 Vrms, 80% AM with 1KHz sine                                              | A                    | IEC 61000-4-6:2008           |

| Power frequency magnetic field | 50Hz, 1A/m (r.m.s.)                                                                       | А                    | JEC 61000-4-6:2008           |

- 1.Performance criterion A = The device shall continue to operate as intended, i.e., normal unit operation with no degradation of performance.

- 2.Performance criterion B = The device shall continue to operate as intended after completion of test, however, during the test, some degradation of performance is allowed as long as there is no data loss operator intervention to restore device function.

- 3.Performance criterion C = Temporary loss of function is allowed. Operator intervention is acceptable to restore device function.

- 4. Contact electrostatic discharge is applied to drive enclosure.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

#### **1.2.16.** Weight:

Weight spec. = 10 g Max. (CA3-8DXXX/CA3-GDXXXX)

**1.2.17.** Dimension:

Form factor:

M.2 2280: 80.0 mm x 22.0 mm x 2.30 mm (L x W x H) (CA3-8DXXX) 80.0 mm x 22.0 mm x 3.65 mm (L x W x H) (CA3-GDXXXX)

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1_1  |

| Revised Date | : 2017/12/22 | V 1.1 |

#### 1.5 Architecture

The CA3-8DXXX/CA3-GDXXXX PCIe Gen3 x 4 Lane Solid State Drive (SSD) utilizes a cost effective system-on-chip (SoC) design to provide a full 4GB/s bandwidth with the host while managing multiple flash memory devices on multiple channels internally.

#### 1.6 Bootable Device:

The CA3-8DXXX/CA3-GDXXXX PCle Gen3 x 4 Lane Solid State Drive (SSD) is configured as a bootable device. This supported function allows users to manage it as a main system drive and to boot from PCle SSD.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

# 1.7 Power Mode Support

PCI Express feature enables the hardware to engage actively in automatic Link power management. CA3-8DXXX/CA3-GDXXXX PCIe Gen3 x 4 Lane SSD Supports L0, L0s and L1 mode.

- -L0: Full On (Active power / Active mode)

- -LOs: Idle (Lower power / Idle mode)

- -L1: Idle (Lower power / sleep mode)

The Link state transits automatically from LO (full on) to an LOs/L1 (idle) state to save power when there is no data transferring. The device reduces power by gating internal clocks, and the CLKREQ# signal transited by host will enable lower power mode of some internal components such as PCIe PHY. Once the data can be transferred across the Link, the state will be brought back to LO by the hardware.

Table 14 Radio Frequency Specifications

| Input Voltage | State       |              | 10 <mark>24 G</mark> B<br>( W ) |      |

|---------------|-------------|--------------|---------------------------------|------|

|               |             | After pow    | er-on                           | 2.4  |

|               | Active Mode | Max.         |                                 |      |

|               | (LO state)  | Read/Write   | rms                             | 8    |

| 3.3V ± 5%     |             | Performance  |                                 |      |

| 3.5V ± 570    |             | Idle Mode    |                                 |      |

|               |             | (LOs state)  |                                 | 2.8  |

|               |             | Sleep Mode   |                                 |      |

|               |             | (L1.2 state) |                                 | 0.01 |

<sup>%</sup>LO stands for power states after power-on and before entering LOs/L1,

<sup>\*</sup>To enable L1 lower mode, the CLKREQ# signal must be sent by host.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

# 2 PIN LOCATIONS AND SIGNAL DESCRIPTIONS

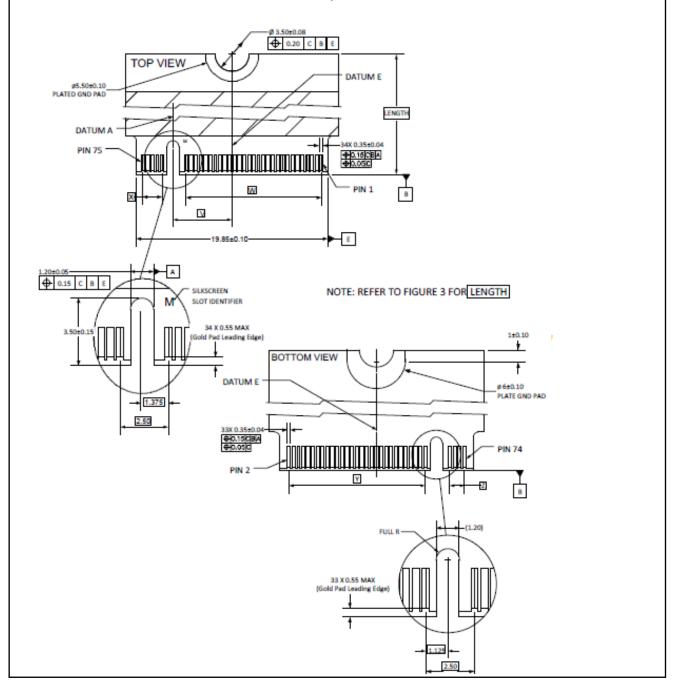

### 2.1 Pin Locations

The data and power connector pin locations of the CA3-8DXXX/CA3-GDXXXX PCIe SSD Gen3 x 4 Lane are shown below. This M.2 device contains Socket 3 + M key.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

### 2.2 M.2 Socket Definition

The PCI Express interface supported in Socket 3 is a 4 Lane PCI Express interface intended for premium SSD devices that need this sort of host interface.

|                        | Туре | Soldered-down<br>Module Height<br>Options |     | Connector<br>Key |       | onnectorized<br>Module Height<br>Options | Module<br>Key |

|------------------------|------|-------------------------------------------|-----|------------------|-------|------------------------------------------|---------------|

| Socket 1               | 1216 | S1, S3                                    | E   | N/A              | N/A   | N/A                                      | N/A           |

| Connectivity           | N/A  | N/A                                       | N/A | A, E             | 1630  | S1, D1, S3, D3, D4                       | A, E, A+E     |

|                        | 2226 | S1, S3                                    | E   | A, E             | 2230  | S1, D1, S3, D3, D4                       | A, E, A+E     |

|                        | 3026 | S1, S3                                    | A+E | A, E             | 3030  | S1, D1, S3, D3, D4                       | A, E, A+E     |

| Socket 2<br>WWAN/Other | N/A  | N/A                                       | N/A | В                | 3042  | S1, D1, S3, D3, D4                       | В             |

| Socket 2               | N/A  | N/A                                       | N/A | В                | 2230  | S2, D2, S3, D3, D5                       | B+M           |

| SSD/Other              | N/A  | N/A                                       | N/A | В                | 2242  | S2, D2, S3, D3, D5                       | B+M           |

|                        | N/A  | N/A                                       | N/A | В                | 2260  | S2, D2, S3, D3, D5                       | B+M           |

|                        | N/A  | N/A                                       | N/A | В                | 2280  | S2, D2, S3, D3, D5                       | B+M           |

|                        | N/A  | N/A                                       | N/A | В                | 22110 | S2, D2, S3, D3, D5                       | B+M           |

| Socket 3               | N/A  | N/A                                       | N/A | M                | 2242  | S2, D2, S3, D3, D5                       | M, B+M        |

| SSD Drive              | N/A  | N/A                                       | N/A | M                | 2260  | S2, D2, S3, D3, D5                       | M, B+M        |

|                        | N/A  | N/A                                       | N/A | М                | 2280  | S2, D2, S3, D3, D5                       | M, B+M        |

|                        | N/A  | N/A                                       | N/A | М                | 22110 | S2, D2, S3, D3, D5                       | M, B+M        |

|                        |      |                                           |     |                  |       | 46                                       |               |

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

# 2.3 Socket 3 PCIe-based SSD Module Pinout

|    |          | GND            | 75 |

|----|----------|----------------|----|

| 74 | 3.3V     | GND            | 73 |

| 72 | 3.3V     | GND            | 71 |

| 70 | 3.3V     | PEDET          | 69 |

| 68 | SUSCLK   | N/C            | 67 |

|    | Vav      | Key            | 6/ |

|    | Key      | ,              |    |

|    | Key      | Key            |    |

|    | Key      | Key            |    |

| 50 | Key      | Key            |    |

| 58 | Reserved | GND            | 57 |

| 56 | Reserved | REFCLKp        | 55 |

| 54 | PEWAKE#  | REFCLKn        | 53 |

| 52 | CLKREQ#  | GND            | 51 |

| 50 | PERST#   | PERp0          | 49 |

| 48 | N/C      | PERn0          | 47 |

| 46 | N/C      | GND            | 45 |

| 44 | ALERT#   | PETp0          | 43 |

| 42 | SMB_DATA | PETn0          | 41 |

| 40 | SMB_CLK  | GND            | 39 |

| 38 | N/C      | PERp1          | 37 |

| 36 | N/C      | PERn1          | 35 |

| 34 | N/C      | GND            | 33 |

| 32 | N/C      | PETp1          | 31 |

| 30 | N/C      | PETn1          | 29 |

| 28 | N/C      | GND            | 27 |

| 26 | N/C      | PERp2          | 25 |

| 24 | N/C      | PERn2          | 23 |

| 22 | N/C      | GND            | 21 |

| 20 | N/C      | PETp2          | 19 |

| 18 | 3.3V     | PETn2          | 17 |

| 16 | 3.3V     | GND            | 15 |

| 14 | 3.3V     | PERp3          | 13 |

| 12 | 3.3V     | PERn3          | 11 |

| 10 | LED#     | GND            | 9  |

| 8  | N/C      | PETp3          | 7  |

| 6  | N/C      | PEID3<br>PETn3 | 5  |

| 4  | 3.3V     |                | 3  |

| 2  | 3.3V     | GND            |    |

|    |          | GND            | 1  |

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

# 3 PCI EXPRESS

#### 3.1 Interface

The PCI Express interface supports the x1 PCI Express interface (one Lane). A Lane consists of an input and an output high-speed differential pair. Also supported is a PCI Express reference clock. Refer to the PCI Express Base Specification for more details on the functional requirements for the PCI Express interface signals.

Socket 1 pin out has provisions for an additional PCI Express lane indicated by the suffix 1 to the signal names. These additional PETx1 and PERx1 signal sets can serve as the second Lane to the original PCI Express interface, or alternatively, they can be complimented with a second set of REFCLKx1 and a set of Auxiliary Signals on the adjacent reserved pins to form a complete second PCI Express x1 interface.

### 3.2 Auxiliary Signals

The auxiliary signals are provided on the system connector to assist with certain system level functionality or implementation. These signals are not required by the PCI Express architecture, but may be required by specific implementations such as PCI Express M.2 Card. The high-speed signal voltage levels are compatible with advanced silicon processes. The optional low speed signals are defined to use the +3.3V supply, as it is the lowest common voltage available. Most ASIC processes have high voltage (thick gate oxide) I/O transistors compatible with +3.3V. The use of the +3.3V supply allows PCI Express signaling to be used with existing control bus structures, avoiding a buffered set of signals and bridges between the buses.

The PCI Express M.2 Card add-in card and system connectors support the auxiliary signals that are described in the following sections.

#### 3.3 Reference Clock

The REFCLK+/REFCLK- signals are used to assist the synchronization of the card's PCI Express interface timing circuits. Availability of the reference clock at the card interface may be gated by the CLKREQ# signal as described in section 3.1.5.1, CLKREQ# Signal. When the reference clock is not available, it will be in the parked state. A parked state is when the clock is not being driven by a clock driver and both REFCLK+ and REFCLK- are pulled to ground by the ground termination resistors. Refer to the PCI Express Card Electromechanical Specification for more details on the functional and tolerance requirements for the reference clock signals.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

#### 3.3.1 CLKREQ# Signal

The CLKREQ# signal is an open drain, active low signal that is driven low by the PCI Express M.2 add-I Card function to request that the PCI Express reference clock be available (active clock state) in order to allow the PCI Express interface to send/receive data. Operation of the CLKREQ# signal is determined by the state of the Enable Clock Power Management bit in the Link Control Register (offset 010h). When disabled, the CLKREQ# signal shall be asserted at all times whenever power is applied to the card, with the exception that it may be de-asserted during L1 PM Sub states. When enabled, the CLKREQ# signal may be de-asserted during the L1 Link state.

The CLKREQ# signal is also used by the L1 PM Sub states mechanism. In this case, CLKREQ# can be asserted by either the system or add-in card to initiate an L1 exit. See the PCI Express Base Specification for details on the functional requirements for the CLKREQ# signal when implementing L1 PM Sub states.

Whenever dynamic clock management is enabled and when a card stops driving CLKREQ# low, it indicates that the device is ready for the reference clock to transition from the active clock state to a parked (not available) clock state. Reference clocks are not guaranteed to be parked by the host system when CLKREQ# gets de-asserted and module designs shall be tolerant of an active reference clock even when CLKREQ# is de-asserted by the module.

The card must drive the CLKREQ# signal low during power up, whenever it is reset, and whenever it requires the reference clock to be in the active clock state. Whenever PERST# is asserted, including when the device is not in D0, CLKREQ# shall be asserted.

It is important to note that the PCI Express device must delay de-assertion of its CLKREQ# signal until it is ready for its reference clock to be parked. The device must be able to assert its clock request signal, whether or not the reference clock is active or parked, when it needs to put its Link back into the LO Link state. Finally, the device must be able to sense an electrical idle break on its up-stream-directed receive port and assert its clock request, whether or not the reference clock is active or parked.

The assertion and de-assertion of CLKREQ# are asynchronous with respect to the reference clock. Add-in cards that do not implement a PCI Express interface shall leave this output unconnected on the card. CLKREQ# has additional electrical requirements over and above standard open drain signals that allow it to be shared between devices that are powered off and other devices that may be powered on. The additional requirements include careful circuit design to ensure that a voltage applied to the CLKREQ# signal network never causes damage to a component even if that particular component's power is not applied.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

Additionally, the device must ensure that it does not pull CLKREQ# low unless CLKREQ# is being intentionally asserted in all cases; including when the related function is in D3cold. This means that any component implementing CLKREQ# must be designed such that:

- -Unpowered CLKREQ# output circuits are not damaged if a voltage is applied to them from other powered "wire-Red" sources of CLKREQ#.

- -When power is removed from its CLKREQ# generation logic, the unpowered output does not present a low impedance path to ground or any other voltage.

These additional requirements ensure that the CLKREQ# signal network continues to function properly when a mixture of powered and unpowered components have their CLKREQ# outputs wire-ORed together. It is important to note that most commonly available open drain and tri-state buffer circuit designs used "as is" do not satisfy the additional circuit design requirements for CLKREQ#.

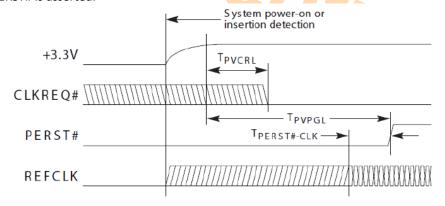

#### 3.3.2 Power-up Requirements

CLKREQ# is asserted in response to PERST# assertion. On power up, CLKREQ# must be asserted by a PCI Express device within a delay (TPVCRL) from the power rails achieving specified operating limits and PERST# assertion (see Figure 78). This delay is to allow adequate time for the power to stabilize on the card and certain system functions to start prior to the card starting up. CLKREQ# may not be de-asserted while PERST# is asserted.

Note:  $T_{PVCRL}$  is measured from the later rising edge of +3.3V.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

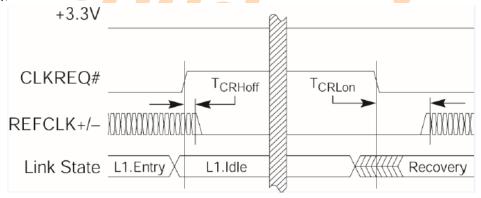

#### 3.3.3 Dynamic Clock Control

After a PCI Express device has powered up and whenever its upstream link enters the L1 link state, it shall allow its reference clock to be turned off (put into the parked clock state). To accomplish this, the device de-asserts CLKREQ# (high) and must allow that the reference clock will transition to the parked clock state within a delay (TCRHoff). Figure 79 shows the CLKREQ# clock control timing diagram.

To exit L1, the device must assert CLKREQ# (low) to re-enable the reference clock. After the device asserts CLKREQ# (low) it must allow that the reference clock will continue to be in the parked clock state for a delay (TCRLon) before transitioning to the active clock state. The time that it takes for the device to assert CLKREQ# and for the system to return the reference clock to the active clock state are serialized with respect to the remainder of L1 recovery. This time must be taken into account when the device is reporting its L1 exit latency.

When the PCI Express device supports, and is enabled for, Latency Tolerance Reporting (LTR), the device must allow that the reference clock transition to the active clock state may be additionally delayed by the system up to a maximum value consistent with requirements for the LTR mechanism. During this delay, the reference clock must remain parked. When exiting the parked state following the delay, the clock must be stable and valid within 400 ns.

#### 3.3.4 Clock Request Support Reporting and Enabling

Support for the CLKREQ# dynamic clock protocol should be reported using bit 18 in the PCI Express link capabilities register (offset 0C4h). To enable dynamic clock management, bit 8 of the Link Control register (offset 010h) is provided. By default, the card shall enable CLKREQ# dynamic clock protocol upon initial power up and in response to any warm reset by the host system. System software may subsequently disable this feature as needed. Refer to the PCI Express Base Specification, Revision 1.1 (or later) for more information regarding these bits.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

#### 3.3.5 PERST# Signal

- -The PERST# signal is de-asserted to indicate when the system power sources are within their specified voltage tolerance and are stable.

- -PERST# should be used to initialize the card functions once power sources stabilize.

- -PERST# is asserted when power is switched off and also can be used by the system to force a hardware reset on the card.

- -System may use PERST# to cause a warm reset of the add-in card.

Refer to the PCI Express Card Electromechanical Specification for more details on the functional requirements for the PERST# signal.

#### 3.3.6 WAKE# Signal

PCI Express M.2 Cards must implement WAKE# if the card supports either the wakeup function or the OBFF mechanism. Refer to the PCI Express Card Electromechanical Specification for more details on the functional requirements for the WAKE# signal.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

#### 3.4 UART Interface

The on-chip asynchronous interface (UART, Universal Asynchronous Receiver and Transmitter) can be used for communication with other host controllers or systems. The UART can handle 8-bit data frames and inserts one start and one stop bit (with/without parity).

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

# 4 ADMIN COMMAND SETS

#### 4.1 Admin Command

The CA3-8DXXX/CA3-GDXXXX PCIe Gen3 x4 Lane SSD supports all the mandatory Admin commands defined in the NVMe 1.2 specification which consists of

- · Delete I/O Submission Queue

- · Create I/O Submission Queue

- · Get Log Page

- · Delete I/O Completion Queue

- · Create I/O Completion Queue

- Identify

- · Abort

- · Set Features

- Get Features

- · Asynchronous Event Request

The CA3-8DXXX/CA3-GDXXXX PCIe Gen3 x 4 Lane SSD supports all the following optional commands

- · Namespace Management

- · Firmware Commit

- · Firmware Image Download

- · Namespace Attachment

- · Security Send

- · Security Receive

# 4.2 Namespace Feature Set

The Namespace Management command is used to create a namespace or delete a namespace. The Namespace Attachment command is used to attach and detach controllers from a namespace.

Namespace management is intended for use during manufacturing or by a system administrator.

When a namespace is detached from a controller or deleted it becomes an inactive namespace on that controller. Previously submitted but uncompleted or subsequently submitted commands to the affected namespace are handled by the controller as if they were issued to an inactive namespace.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

# 4.3 Security Feature Set

The Security Receive command transfers the status and data result of one or more Security Send commands that were previously submitted to the controller.

The association between a Security Receive command and previous Security Send commands is dependent on the Security Protocol. The format of the data to be transferred is dependent on the Security Protocol. Refer to SPC-4 for Security Protocol details.

Each Security Receive command returns the appropriate data corresponding to a Security Send command as defined by the rules of the Security Protocol. The Security Receive command data may not be retained if there is a loss of communication between the controller and host, or if a controller reset occurs.

The Security Send command is used to transfer security protocol data to the controller. The data structure transferred to the controller as part of this command contains security protocol specific commands to be performed by the controller. The data structure transferred may also contain data or parameters associated with the security protocol commands. Status and data that is to be returned to the host for the security protocol commands submitted by a Security Send command are retrieved with the Security Receive command.

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

# 5 NVME COMMAND SETS

#### 5.1 NVMe Command

The CA3-8DXXX/CA3-GDXXXX PCIe Gen3 x4 Lane SSD supports all the mandatory NVMe commands defined in the NVMe 1.2 specification, which consists of

- Flush

- · Write

- · Read

The CA3-8DXXX/CA3-GDXXXX PCIe Gen3 x 4 Lane SSD supports all the following optional commands

- · Write Uncorrectable

- · Dataset Management

### 5.2 Power Management Feature Set

The power management capability allows the host to manage NVM subsystem power statically or dynamically. Static power management consists of the host determining the maximum power that may be allocated to an NVM subsystem and setting the NVM Express power state to one that consumes this amount of power or less. Dynamic power management consists of the host modifying the NVM Express power state to best satisfy changing power and performance objectives. This power management mechanism is meant to complement and not replace autonomous power management performed by a controller.

Associated with each power state is a Power State Descriptor in the Identify Controller data structure. The descriptors for all implemented power states may be viewed as forming a table as shown for a controller with three implemented power states. The Maximum Power (MP) field indicates the instantaneous maximum power that may be consumed in that state. The controller may employ autonomous power management techniques to reduce power consumption below this level, but under no circumstances is power allowed to exceed this level.

| Power<br>State | Maximum<br>Power | Operational<br>State | Entry<br>Latency | Exit<br>Latency |

|----------------|------------------|----------------------|------------------|-----------------|

| 0              | 8W               | Yes                  | <5us             | <5us            |

| 3              | 50mW             | No                   | <1ms             | <10ms           |

| 4              | 10mW             | No                   | <5ms             | <50ms           |

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

# 6 REFERENCES

This document references standards defined by a variety of organizations as listed below.

#### **Table 55 Standards References**

| Title                                                                           | Location                                                               |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------|

| VCCI                                                                            | http://www.vcci.or.jp/vcci_e/general/join/index.htm                    |

| ROHS                                                                            | Search for material description datasheet at http://intel.pcnalert.com |

| SFF-8144, 1.8" drive form factor                                                | http://www.sffcommittee.org                                            |

| PCI Express Specification                                                       | http://www.pcisig.com                                                  |

| SFF-8223, 2.5" Drive w/Serial Attachment Connector                              | http://www.sffcommittee.org                                            |

| SFF-8201, 2.5" drive form factor                                                | http://www.sffcommittee.org                                            |

| NVM Express Specification                                                       | http://www.nvmexpress.org                                              |

| International Electro Technical Commission                                      |                                                                        |

| EB61000 4-2 Personnel Electrostatic Discharge Immunity                          | 14/6/                                                                  |

| 4-3 Electromagnetic compatibility (EMC)                                         | http://www.iec.ch                                                      |

| 4-4 Electromagnetic compatibility (EMC) 4-5 Electromagnetic compatibility (EMC) |                                                                        |

| 4-6Electromagnetic compatibility (EMC)                                          |                                                                        |

| 4-11 (Voltage variations)                                                       |                                                                        |

| ENV 50204 (Radiated electromagnetic field from digital radio telephones)        | http://www.iec.ch                                                      |

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1.1  |

| Revised Date | : 2017/12/22 | V 1.1 |

# 7 TERMS AND ACRONYMS

This document incorporates many industry- and device-specific words use the following list to define a variety of terms and acronyms.

**Table 66 Glossary of Terms and Acronyms**

| Table 66 Glossary of Terms and Acronyms |                                                                          |  |

|-----------------------------------------|--------------------------------------------------------------------------|--|

| Term                                    | Definition                                                               |  |

| BER                                     | Bit Error Rate, or percentage of bits that have errors relative to the   |  |

| DEN                                     | total number of bits received                                            |  |

| BIOS                                    | Basic Input/Output System                                                |  |

| Chipset                                 | A term used to define a collection of integrated components required     |  |

| Спрасс                                  | to ma <mark>ke</mark> a PC fu <mark>nction</mark>                        |  |

| DMA                                     | Dire <mark>ct Memory Access</mark>                                       |  |

| DRAM                                    | Dyn <mark>amic Rando</mark> m Ac <mark>ce</mark> ss M <mark>emory</mark> |  |

| EXT                                     | Extended                                                                 |  |

| FP                                      | First Party                                                              |  |

| GB                                      | Giga-byte defined as 1X109 bytes                                         |  |

| HCI                                     | Host Controller Interface                                                |  |

| HCT                                     | Hardware Compatibility Test                                              |  |

| HDD                                     | Hard Disk Drive                                                          |  |

| IOPS                                    | Input output operations per second                                       |  |

| LBA                                     | Logical Block Address                                                    |  |

| MB                                      | Mega-bytes defined as 1x10 <sup>6</sup> bytes                            |  |

| mSATA                                   | Mini-SATA                                                                |  |

| MTBF                                    | Mean time between failure                                                |  |

|                                         | Native Command Queuing                                                   |  |

| NCQ                                     | The ability of the SATA hard drive to re-order commands in order to      |  |

|                                         | maximize the efficiency of gathering data from the platters              |  |

| NOP                                     | No operation                                                             |  |

| NTFS                                    | NT file system                                                           |  |

| OEM                                     | Original Equipment Manufacturer                                          |  |

| OS                                      | Operation System                                                         |  |

| Port                                    | The point at which a SATA drive physically connected to the SATA         |  |

| POIL                                    | controller                                                               |  |

| RAID                                    | Redundant Array of Independent Disks                                     |  |

| RMS                                     | Root Mean Squared                                                        |  |

| RPM                                     | Revolutions per Minute                                                   |  |

| RTM                                     | Release to Manufacture                                                   |  |

| SATA                                    | Serial ATA                                                               |  |

| SFF                                     | Small Form Factor                                                        |  |

|                                         | Self-Monitoring, Analysis and reporting Technology                       |  |

| SMART                                   | An open standard for developing hard drive and software systems that     |  |

|                                         | automatically monitors a hard drive's health and reports potential       |  |

|                                         | problems                                                                 |  |

| DOC NO       | : 9C10000127 | Rev. |  |

|--------------|--------------|------|--|

| Issued Date  | : 2017/04/21 | V1.1 |  |

| Revised Date | : 2017/12/22 | V1.1 |  |

|             | Revised Date . 2017/12/22                                                                                                                              |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSD         | Solid State Drive                                                                                                                                      |

| ГВD         | To Be Determined                                                                                                                                       |

| VHQL        | Microsoft* Windows Hardware Quality Labs                                                                                                               |

| Write Cache | A memory device within a hard drive, which is allocated for the temporary storage of data before that data is copied to its permanent storage location |

| /CCI        | Voluntary Control Council for Interface                                                                                                                |

| 4           | Amperage or Amp                                                                                                                                        |

| OC .        | Direct Current                                                                                                                                         |

| GND         | Ground                                                                                                                                                 |

| GNSS        | Global Navigation Satellite System (GPS+GLONASS)                                                                                                       |

| HDR         | Hybrid Digital Radio                                                                                                                                   |

| HSIC        | High Speed Inter-Chip                                                                                                                                  |

| /F          | Interfa <mark>ce</mark>                                                                                                                                |

| 1/0         | Input/Output                                                                                                                                           |

| IR          | Current x Resistance = Voltage                                                                                                                         |

| 2C          | Inter-Integrated Circuit                                                                                                                               |

| 25          | Integrated Interchip Sound                                                                                                                             |

| .ED         | Light Emitting Diode                                                                                                                                   |

| .GA         | Laned Grid Array                                                                                                                                       |

| nΩ          | milli Ohm                                                                                                                                              |

| nA          | milli Amp                                                                                                                                              |

| nV          | milli Volt                                                                                                                                             |

| NFC         | Near Field Communications                                                                                                                              |

| VI.2        | Formally called Next Generation Form Factor (NGFF)                                                                                                     |

| NB          | Notebook                                                                                                                                               |

| VIC         | Network Interface Card                                                                                                                                 |

| IC          | Not Connected                                                                                                                                          |

| SATA        | Serial Advanced Technology Attachment or Serial ATA                                                                                                    |

| PCle        | Peripheral Component Interconnect Express                                                                                                              |

| PCM         | Pulse Code Modulation                                                                                                                                  |

| SDIO        | Secure Digital Input Output                                                                                                                            |

| SIM         | Subscriber Identity Module                                                                                                                             |

| SSD         | Sold-State Storage Device                                                                                                                              |

| F           | Radio Frequency                                                                                                                                        |

| RM          | Root Mean Square                                                                                                                                       |

| oHS         | Restriction of Hazardous Substances Directive                                                                                                          |

| RTC         | Real Time Clock                                                                                                                                        |

| RFU         | Reserved for Future Use                                                                                                                                |

| MIL         | User Identity Module                                                                                                                                   |

| JART        | Universal Asynchronous Receive Transmit                                                                                                                |

| V           | Wattage or Watts                                                                                                                                       |

| NiGig       | Wireless Giga communication                                                                                                                            |

| WLANE       | Wireless Local Area Network                                                                                                                            |

| WPAN        | Wireless Personal Area Network                                                                                                                         |

| WWAN        | Wireless Wide Area Network                                                                                                                             |

| /           | Voltage                                                                                                                                                |

| DOC NO       | : 9C10000127 | Rev.  |

|--------------|--------------|-------|

| Issued Date  | : 2017/04/21 | V1 1  |

| Revised Date | : 2017/12/22 | V 1.1 |

# 8. ENDURANCE

| Capacity | TBW (Total Bytes Written) |

|----------|---------------------------|

| 256GB    | Up to 290 TB              |

| 512GB    | Up to 493 TB              |

| 1024GB   | Up to 850 TB              |

Note: TBW value is derived from JEDEC based on population of SSDs statistics.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Advantech: 96FD80-P256-LIS