# **Viterbi IP Core User Guide**

Updated for  $Intel^{\ensuremath{\mathbb{R}}}$  Quartus  $\ensuremath{\mathbb{R}}$  Prime Design Suite: **17.1**

ID: 683280 Version: 2017.11.06

**UG-VITERBI**

# Contents

| 1. About the Viterbi IP Core                                          | . 3 |

|-----------------------------------------------------------------------|-----|

| 1.1. Intel <sup>®</sup> DSP IP Core Features                          | .3  |

| 1.2. Viterbi IP Core Features                                         | .4  |

| 1.3. DSP IP Core Device Family Support                                | .4  |

| 1.4. DSP IP Core Verification.                                        |     |

| 1.5. Viterbi IP Core Release Information                              | .5  |

| 1.6. Viterbi IP Core Performance and Resource Utilization             | . 5 |

| 2. Viterbi IP Core Getting Started                                    | 9   |

| 2.1. Installing and Licensing Intel FPGA IP Cores                     | . 9 |

| 2.1.1. Intel FPGA IP Evaluation Mode                                  |     |

| 2.1.2. Viterbi IP Core Intel FPGA IP Evaluation Mode Timeout Behavior |     |

| 2.2. IP Catalog and Parameter Editor                                  |     |

| 2.3. Generating IP Cores (Intel Quartus Prime Pro Edition)            |     |

| 2.3.1. IP Core Generation Output (Intel Quartus Prime Pro Edition)    |     |

| 2.4. Simulating Intel FPGA IP Cores                                   |     |

| 2.5. DSP Builder for Intel FPGAs Design Flow                          | 18  |

| 3. Viterbi IP Core Functional Description 1                           |     |

| 3.1. Decoder                                                          |     |

| 3.2. Convolutional Encoder                                            |     |

| 3.3. Trellis Coded Modulation                                         |     |

| 3.3.1. Half-Rate Convolutional Codes                                  |     |

| 3.3.2. Trellis Decoder                                                |     |

| 3.3.3. About Converting Received Signals                              |     |

| 3.3.4. Trellis Termination                                            |     |

| 3.3.5. Trellis Initialization                                         |     |

| 3.4. Viterbi IP Core Parameters                                       |     |

| 3.4.1. Architecture                                                   | -   |

| 3.4.2. Code Sets                                                      |     |

| 3.4.3. Viterbi Parameters                                             |     |

| 3.4.4. Test Data                                                      |     |

| 3.5. Viterbi IP Core Interfaces and Signals                           |     |

| 3.5.1. Avalon-ST Interfaces in DSP IP Cores                           |     |

| 3.5.2. Global Signals                                                 |     |

| 3.5.3. Avalon-ST Sink Signals                                         |     |

| 3.5.4. Avalon Source-ST Signals                                       |     |

| 3.5.5. Configuration Signals<br>3.5.6. Status Signals                 |     |

| 3.5.6. Status Signals                                                 |     |

|                                                                       |     |

| A. Viterbi IP Core User Guide Document Archives                       |     |

| 5. Document Revision History                                          | 38  |

Send Feedback

# **1. About the Viterbi IP Core**

#### **Related Information**

- Introduction to Intel FPGA IP Cores Provides general information about all Intel FPGA IP cores, including parameterizing, generating, upgrading, and simulating IP cores.

- Creating Version-Independent IP and Qsys Simulation Scripts Create simulation scripts that do not require manual updates for software or IP version upgrades.

- Project Management Best Practices

Guidelines for efficient management and portability of your project and IP files.

- Viterbi IP Core User Guide Document Archives on page 37 Provides a list of user guides for previous versions of the Viterbi IP core.

# **1.1. Intel<sup>®</sup> DSP IP Core Features**

- Avalon<sup>®</sup> Streaming (Avalon-ST) interfaces

- DSP Builder for Intel<sup>®</sup> FPGAs ready

- Testbenches to verify the IP core

- IP functional simulation models for use in Intel-supported VHDL and Verilog HDL simulators

# **1.2. Viterbi IP Core Features**

- High-speed parallel architecture:

- Performance of over 250 megabits per second (Mbps)

- Fully parallel operation

- Optimized block decoding and continuous decoding

- Low to medium-speed, hybrid architecture:

- Configurable number of add compare and select (ACS) units

- Memory-based architecture

- Wide range of performance; wide range of logic area

- Fully parameterized Viterbi decoder, including:

- Number of coded bits

- Constraint length

- Number of soft bits

- Traceback length

- Polynomial for each coded bit

- Variable constraint length

- Trellis coded modulation (TCM) option

# **1.3. DSP IP Core Device Family Support**

Intel offers the following device support levels for Intel FPGA IP cores:

- Advance support—the IP core is available for simulation and compilation for this device family. FPGA programming file (.pof) support is not available for Quartus Prime Pro Stratix 10 Edition Beta software and as such IP timing closure cannot be guaranteed. Timing models include initial engineering estimates of delays based on early post-layout information. The timing models are subject to change as silicon testing improves the correlation between the actual silicon and the timing models. You can use this IP core for system architecture and resource utilization studies, simulation, pinout, system latency assessments, basic timing assessments (pipeline budgeting), and I/O transfer strategy (data-path width, burst depth, I/O standards tradeoffs).

- Preliminary support—Intel verifies the IP core with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. You can use it in production designs with caution.

- Final support—Intel verifies the IP core with final timing models for this device family. The IP core meets all functional and timing requirements for the device family. You can use it in production designs.

#### Table 1. DSP IP Core Device Family Support

| Device Family            | Support   |

|--------------------------|-----------|

| Arria <sup>®</sup> II GX | Final     |

| Arria II GZ              | Final     |

|                          | continued |

| Device Family                  | Support    |

|--------------------------------|------------|

| Arria V                        | Final      |

| Intel Arria 10                 | Final      |

| Cyclone <sup>®</sup> IV        | Final      |

| Cyclone V                      | Final      |

| Intel Cyclone 10               | Final      |

| Intel MAX <sup>®</sup> 10 FPGA | Final      |

| Stratix <sup>®</sup> IV GT     | Final      |

| Stratix IV GX/E                | Final      |

| Stratix V                      | Final      |

| Intel Stratix 10               | Advance    |

| Other device families          | No support |

# **1.4. DSP IP Core Verification**

Before releasing a version of an IP core, Intel runs comprehensive regression tests to verify its quality and correctness. Intel generates custom variations of the IP core to exercise the various parameter options and thoroughly simulates the resulting simulation models with the results verified against master simulation models.

# **1.5. Viterbi IP Core Release Information**

Use the release information when licensing the IP core.

#### Table 2.Release Information

| Item          | Description                                                               |

|---------------|---------------------------------------------------------------------------|

| Version       | 17.1                                                                      |

| Release Date  | November 2017                                                             |

| Ordering Code | IP-VITERBI/HS (parallel architecture) IP-VITERBI/SS (hybrid architecture) |

Intel verifies that the current version of the Quartus Prime software compiles the previous version of each IP core. Intel does not verify that the Quartus Prime software compiles IP core versions older than the previous version. The *Intel FPGA IP Release Notes* lists any exceptions.

#### **Related Information**

- Intel FPGA IP Release Notes

- Errata for Viterbi IP core in the Knowledge Base

# **1.6. Viterbi IP Core Performance and Resource Utilization**

This typical expected performance uses different architectures and constraint length, L, combinations, and ACS units, A, and the Quartus Prime software. Performance largely depends on constraint length, L.

#### **Hybrid Architecture**

The typical expected performance for a hybrid Viterbi IP core uses the Quartus Prime software with the Arria V (5AGXFB3H4F40C4), Cyclone V (5CGXFC7D6F31C6), and Stratix V (5SGSMD4H2F35C2) devices and the following parameters:

- *v* = 6 × L

- softbits = 3

- *N* = 2

where:

intel

- v is the traceback length

- *L* is the constraint length

- *N* is the number of coded bits

- *A* is the number of ACS units

#### Table 3.Typical Performance

| Par | ameters | Device    | ALM   | f <sub>MAX</sub> (MHz) | Memory |      | Re      | gisters    |

|-----|---------|-----------|-------|------------------------|--------|------|---------|------------|

| L   | Α       |           |       |                        | M10K   | M20K | Primary | Secondary  |

| 5   | 1       | Arria 10  | 401   | 383                    |        | 3    | 422     | 40         |

| 5   | 1       | Arria V   | 323   | 201                    | 5      |      | 390     | 60         |

| 5   | 1       | Cyclone V | 324   | 172                    | 5      |      | 390     | 53         |

| 5   | 1       | Stratix V | 316   | 432                    |        | 5    | 388     | 44         |

| 7   | 1       | Arria 10  | 521   | 370                    |        | 4    | 559     | 50         |

| 7   | 1       | Arria V   | 427   | 207                    | 6      |      | 507     | 58         |

| 7   | 1       | Cyclone V | 427   | 185                    | 6      |      | 507     | 74         |

| 7   | 1       | Stratix V | 417   | 438                    |        | 6    | 506     | 51         |

| 7   | 2       | Arria 10  | 622   | 363                    |        | 4    | 670     | 51         |

| 7   | 2       | Arria V   | 529   | 215                    | 6      |      | 625     | 71         |

| 7   | 2       | Cyclone V | 532   | 180                    | 6      |      | 625     | 74         |

| 7   | 2       | Stratix V | 502   | 408                    |        | 6    | 625     | 56         |

| 7   | 4       | Arria 10  | 835   | 366                    |        | 4    | 885     | 101        |

| 7   | 4       | Arria V   | 744   | 204                    | 6      |      | 856     | 99         |

| 7   | 4       | Cyclone V | 746   | 173                    | 6      |      | 856     | 100        |

| 7   | 4       | Stratix V | 652   | 382                    |        | 6    | 856     | 82         |

| 9   | 1       | Arria 10  | 932   | 343                    |        | 9    | 970     | 88         |

|     | 1       | Arria V   | 792   | 190                    | 11     |      | 927     | 90         |

| 9   | 1       | Cyclone V | 794   | 176                    | 11     |      | 926     | 96         |

| 9   | 1       | Stratix V | 777   | 393                    |        | 11   | 924     | 94         |

| 9   | 16      | Arria V   | 2,118 | 188                    | 17     |      | 2,743   | 309        |

|     |         |           |       |                        |        |      |         | continued. |

| Para | meters | Device    | ALM   | f <sub>MAX</sub> (MHz) | Mer  | Memory |         | gisters   |

|------|--------|-----------|-------|------------------------|------|--------|---------|-----------|

| L    | Α      |           |       |                        | M10K | M20K   | Primary | Secondary |

| 9    | 16     | Cyclone V | 2,119 | 163                    | 17   |        | 2,744   | 275       |

| 9    | 16     | Stratix V | 1,887 | 348                    |      | 17     | 2,738   | 198       |

| 9    | 2      | Arria 10  | 1,029 | 363                    |      | 9      | 1,091   | 74        |

| 9    | 2      | Arria V   | 889   | 205                    | 11   |        | 1,053   | 98        |

| 9    | 2      | Cyclone V | 889   | 180                    | 11   |        | 1,053   | 96        |

| 9    | 2      | Stratix V | 883   | 377                    |      | 11     | 1,053   | 115       |

| 9    | 4      | Arria 10  | 1,240 | 298                    |      | 9      | 1,321   | 87        |

| 9    | 4      | Arria V   | 1,097 | 201                    | 11   |        | 1,302   | 137       |

| 9    | 4      | Cyclone V | 1,096 | 159                    | 11   |        | 1,302   | 126       |

| 9    | 4      | Stratix V | 1,021 | 390                    |      | 11     | 1,302   | 119       |

| 9    | 8      | Arria V   | 1,465 | 197                    | 13   |        | 1,788   | 193       |

| 9    | 8      | Cyclone V | 1,465 | 163                    | 13   |        | 1,789   | 191       |

| 9    | 8      | Stratix V | 1,398 | 351                    |      | 13     | 1,790   | 154       |

#### **Parallel Architecture**

The typical expected performance for a parallel Viterbi IP core uses the Quartus Prime software with the Arria V (5AGXFB3H4F40C4), Cyclone V (5CGXFC7D6F31C6), and Stratix V (5SGSMD4H2F35C2) devices. The following parameters apply:

- $v = 6 \times L$

- *N* = 2

where:

- v is the traceback length

- *L* is the constraint length

- *N* is the number of coded bits

#### Table 4.Typical Performance

| Parameters |           | Parameters   |                   | Parameters |       |       |      |      |         |           | Memory |  | Registers |  |

|------------|-----------|--------------|-------------------|------------|-------|-------|------|------|---------|-----------|--------|--|-----------|--|

| softbits   | L         | Optimization | Best State Finder |            | (     | (MHz) | М10К | М20К | Primary | Secondary |        |  |           |  |

| 5          | 3         | -            | On                | Arria 10   | 420   | 400   |      | 5    | 500     | 63        |        |  |           |  |

| 7          | 3         | -            | On                | Arria 10   | 453   | 351   |      | 5    | 534     | 75        |        |  |           |  |

| 3          | 3         | -            | Off               | Arria 10   | 396   | 423   |      | 5    | 473     | 39        |        |  |           |  |

| 5          | 3         | -            | Off               | Arria 10   | 420   | 400   |      | 5    | 500     | 63        |        |  |           |  |

| 7          | 3         | _            | Off               | Arria 10   | 453   | 351   |      | 5    | 534     | 75        |        |  |           |  |

| 3          | 7         | Block        | Off               | Arria 10   | 1,454 | 354   |      | 3    | 817     | 154       |        |  |           |  |

| 3          | 7         | Block        | Off               | Arria V    | 1,537 | 201   | 5    |      | 1,166   | 168       |        |  |           |  |

| 3          | 7         | Block        | Off               | Cyclone V  | 1,544 | 149   | 5    |      | 1,167   | 88        |        |  |           |  |

|            | continued |              |                   |            |       |       |      |      |         |           |        |  |           |  |

| Parameters |   | Device       | ALMs              | fMAX      | Memory |       | Registers |      |         |           |

|------------|---|--------------|-------------------|-----------|--------|-------|-----------|------|---------|-----------|

| softbits   | L | Optimization | Best State Finder |           |        | (MHz) | M10K      | M20K | Primary | Secondary |

| 3          | 7 | Block        | Off               | Stratix V | 1,521  | 352   |           | 3    | 1,167   | 154       |

| 3          | 3 | _            | Off               | Arria V   | 378    | 237   | 5         |      | 456     | 67        |

| 3          | 3 | -            | Off               | Cyclone V | 378    | 200   | 5         |      | 456     | 84        |

| 3          | 3 | -            | Off               | Stratix V | 378    | 405   |           | 5    | 455     | 45        |

| 5          | 3 | _            | Off               | Arria V   | 397    | 210   | 5         |      | 483     | 68        |

| 5          | 3 | -            | Off               | Cyclone V | 397    | 188   | 5         |      | 484     | 81        |

| 5          | 3 | _            | Off               | Stratix V | 396    | 406   |           | 5    | 482     | 92        |

| 3          | 3 | -            | On                | Arria V   | 378    | 237   | 5         |      | 456     | 67        |

| 3          | 3 | -            | On                | Cyclone V | 378    | 200   | 5         |      | 456     | 84        |

| 3          | 3 | _            | On                | Stratix V | 378    | 405   |           | 5    | 455     | 45        |

| 5          | 3 | -            | On                | Arria V   | 397    | 210   | 5         |      | 483     | 68        |

| 5          | 3 | _            | On                | Cyclone V | 397    | 188   | 5         |      | 484     | 81        |

| 5          | 3 | _            | On                | Stratix V | 396    | 406   |           | 5    | 482     | 92        |

| 7          | 3 | -            | On                | Arria V   | 424    | 219   | 5         |      | 518     | 82        |

| 7          | 3 | _            | On                | Cyclone V | 424    | 185   | 5         |      | 519     | 76        |

| 7          | 3 | -            | On                | Stratix V | 424    | 408   |           | 5    | 517     | 69        |

| 7          | 3 | _            | Off               | Arria V   | 424    | 219   | 5         |      | 518     | 82        |

| 7          | 3 | -            | Off               | Cyclone V | 424    | 185   | 5         |      | 519     | 76        |

| 7          | 3 | _            | Off               | Stratix V | 424    | 408   |           | 5    | 517     | 69        |

| 7          | 4 | _            | Off               | Arria V   | 424    | 219   | 5         |      | 518     | 82        |

| 7          | 4 | _            | Off               | Cyclone V | 424    | 185   | 5         |      | 519     | 76        |

| 7          | 4 | _            | Off               | Stratix V | 424    | 408   |           | 5    | 517     | 69        |

| 3          | 7 | Continuous   | Off               | Arria 10  | 1,180  | 365   |           | 5    | 829     | 178       |

| 3          | 7 | Continuous   | Off               | Arria V   | 1,222  | 187   | 9         |      | 1,137   | 250       |

| 3          | 7 | Continuous   | Off               | Cyclone V | 1,223  | 157   | 9         |      | 1,137   | 187       |

| 3          | 7 | Continuous   | Off               | Stratix V | 1,220  | 325   |           | 5    | 1,137   | 168       |

# 2. Viterbi IP Core Getting Started

#### 1.

# 2.1. Installing and Licensing Intel FPGA IP Cores

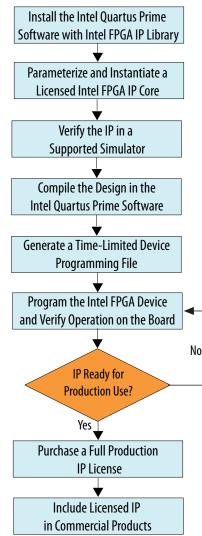

The Intel Quartus<sup>®</sup> Prime software installation includes the Intel FPGA IP library. This library provides many useful IP cores for your production use without the need for an additional license. Some Intel FPGA IP cores require purchase of a separate license for production use. The Intel FPGA IP Evaluation Mode allows you to evaluate these licensed Intel FPGA IP cores in simulation and hardware, before deciding to purchase a full production IP core license. You only need to purchase a full production license for licensed Intel IP cores after you complete hardware testing and are ready to use the IP in production.

The Intel Quartus Prime software installs IP cores in the following locations by default:

#### Figure 1. IP Core Installation Path

#### 📄 intelFPGA(\_pro)

- quartus - Contains the Intel Quartus Prime software

**ip** - Contains the Intel FPGA IP library and third-party IP cores

**altera** - Contains the Intel FPGA IP library source code

*<IP name>* - Contains the Intel FPGA IP source files

#### Table 5. IP Core Installation Locations

| Location                                                               | Software                                | Platform |

|------------------------------------------------------------------------|-----------------------------------------|----------|

| <pre><drive>:\intelFPGA_pro\quartus\ip\altera</drive></pre>            | Intel Quartus Prime Pro Edition         | Windows* |

| <pre><drive>:\intelFPGA\quartus\ip\altera</drive></pre>                | Intel Quartus Prime Standard<br>Edition | Windows  |

| <pre><home directory="">:/intelFPGA_pro/quartus/ip/altera</home></pre> | Intel Quartus Prime Pro Edition         | Linux*   |

| <home directory="">:/intelFPGA/quartus/ip/altera</home>                | Intel Quartus Prime Standard<br>Edition | Linux    |

# 2.1.1. Intel FPGA IP Evaluation Mode

The free Intel FPGA IP Evaluation Mode allows you to evaluate licensed Intel FPGA IP cores in simulation and hardware before purchase. Intel FPGA IP Evaluation Mode supports the following evaluations without additional license:

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

Send Feedback

- Simulate the behavior of a licensed Intel FPGA IP core in your system.

- Verify the functionality, size, and speed of the IP core quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device with your IP core and verify your design in hardware.

Intel FPGA IP Evaluation Mode supports the following operation modes:

- Tethered—Allows running the design containing the licensed Intel FPGA IP indefinitely with a connection between your board and the host computer. Tethered mode requires a serial joint test action group (JTAG) cable connected between the JTAG port on your board and the host computer, which is running the Intel Quartus Prime Programmer for the duration of the hardware evaluation period. The Programmer only requires a minimum installation of the Intel Quartus Prime software, and requires no Intel Quartus Prime license. The host computer controls the evaluation time by sending a periodic signal to the device via the JTAG port. If all licensed IP cores in the design support tethered mode, the evaluation time runs until any IP core evaluation expires. If all of the IP cores support unlimited evaluation time, the device does not time-out.

- Untethered—Allows running the design containing the licensed IP for a limited time. The IP core reverts to untethered mode if the device disconnects from the host computer running the Intel Quartus Prime software. The IP core also reverts to untethered mode if any other licensed IP core in the design does not support tethered mode.

When the evaluation time expires for any licensed Intel FPGA IP in the design, the design stops functioning. All IP cores that use the Intel FPGA IP Evaluation Mode time out simultaneously when any IP core in the design times out. When the evaluation time expires, you must reprogram the FPGA device before continuing hardware verification. To extend use of the IP core for production, purchase a full production license for the IP core.

You must purchase the license and generate a full production license key before you can generate an unrestricted device programming file. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (*<project name>\_\_\_\_\_\_\_inted.sof*) that expires at the time limit.

#### Figure 2. Intel FPGA IP Evaluation Mode Flow

*Note:* Refer to each IP core's user guide for parameterization steps and implementation details.

Intel licenses IP cores on a per-seat, perpetual basis. The license fee includes firstyear maintenance and support. You must renew the maintenance contract to receive updates, bug fixes, and technical support beyond the first year. You must purchase a full production license for Intel FPGA IP cores that require a production license, before generating programming files that you may use for an unlimited time. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (*<project name>\_time\_limited.sof*) that expires at the time limit. To obtain your production license keys, visit the *Self-Service Licensing Center*.

The Intel FPGA Software License Agreements govern the installation and use of licensed IP cores, the Intel Quartus Prime design software, and all unlicensed IP cores.

Send Feedback

#### **Related Information**

- Self-Service Licensing Center

- Intel Quartus Prime Licensing

- Intel FPGA Software Installation and Licensing

### 2.1.2. Viterbi IP Core Intel FPGA IP Evaluation Mode Timeout Behavior

All IP cores in a device time out simultaneously when the most restrictive evaluation time is reached. If there is more than one IP core in a design, the time-out behavior of the other IP cores may mask the time-out behavior of a specific IP core .

For IP cores, the untethered time-out is 1 hour; the tethered time-out value is indefinite. Your design stops working after the hardware evaluation time expires. The Quartus Prime software uses Intel FPGA IP Evaluation Mode Files (.ocp) in your project directory to identify your use of the Intel FPGA IP Evaluation Mode evaluation program. After you activate the feature, do not delete these files..

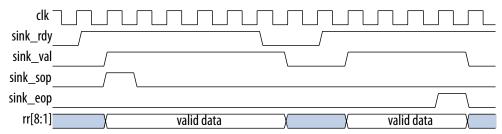

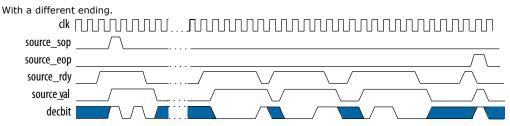

When the evaluation time expires the  $\operatorname{decbit}$  signal goes low .

#### **Related Information**

AN 320: OpenCore Plus Evaluation of Megafunctions

## 2.2. IP Catalog and Parameter Editor

The IP Catalog displays the IP cores available for your project. Use the following features of the IP Catalog to locate and customize an IP core:

- Filter IP Catalog to Show IP for active device family or Show IP for all device families. If you have no project open, select the Device Family in IP Catalog.

- Type in the Search field to locate any full or partial IP core name in IP Catalog.

- Right-click an IP core name in IP Catalog to display details about supported devices, to open the IP core's installation folder, and for links to IP documentation.

- Click Search for Partner IP to access partner IP information on the web.

The parameter editor prompts you to specify an IP variation name, optional ports, and output file generation options. The parameter editor generates a top-level Intel Quartus Prime IP file (.ip) for an IP variation in Intel Quartus Prime Pro Edition projects.

The parameter editor generates a top-level Quartus IP file (.qip) for an IP variation in Intel Quartus Prime Standard Edition projects. These files represent the IP variation in the project, and store parameterization information.

#### Figure 3. IP Parameter Editor (Intel Quartus Prime Pro Edition)

| 🦉 Parameters 🛛                                                                                                         |                                 | - d 🗆      | Details 🛱 💾 Block Symbol 🕸 🗕 🛛                   |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------|--------------------------------------------------|

| System: test Path: iopII_C                                                                                             |                                 |            | Show signals                                     |

| Intel FPGA IOPLL<br>altera_iopII<br>PLL Settings Casca                                                                 | ding Dynamic Reconfiguration Ar | Details    | iopII_0<br>reset                                 |

| T Device                                                                                                               |                                 |            | rst reset export locked                          |

| Device Family:                                                                                                         | Arria 10                        |            | refcik, outciko                                  |

| Component:                                                                                                             | 10AS016C3U19E2LG                |            | refcik cik outcik                                |

| Speed Grade:                                                                                                           |                                 |            | altera_iopil                                     |

| 🔻 General                                                                                                              |                                 |            | ***************************************          |

| Reference Clock Freque                                                                                                 | ncv: 100.0 MHz                  |            | IP Parameters     IP Block Symb                  |

| 🗹 Enable locked outpu                                                                                                  | it port                         |            |                                                  |

| 🔲 Enable physical outp                                                                                                 | out clock parameters            |            |                                                  |

| Compensation                                                                                                           | out clock parameters            |            |                                                  |

|                                                                                                                        | direct                          |            | and Records - 12                                 |

| Compensation                                                                                                           |                                 | best jitte | of Presets 🛛                                     |

| <ul> <li>Compensation</li> <li>Compensation Mode:</li> <li>Direct mode is suitable</li> <li>Output Clocks</li> </ul>   | direct 🗸                        | best jitte | -                                                |

| <ul> <li>Compensation</li> <li>Compensation Mode:</li> <li>Direct mode is suitable</li> </ul>                          | direct 🗸                        | best jitte | Presets for iopII_0                              |

| <ul> <li>Compensation</li> <li>Compensation Mode:</li> <li>Direct mode is suitable</li> <li>Output Clocks</li> </ul>   | direct                          | best jitte | Presets for lopil_0  Clear preset filters        |

| Compensation<br>Compensation Mode:<br>Direct mode is suitable<br>Output Clocks<br>Number Of Clocks:                    | direct                          | best jitte | Presets for iopII_0                              |

| Compensation<br>Compensation Mode:<br>Direct mode is suitable<br>Output Clocks<br>Number Of Clocks:                    | direct                          | best jitte | Presets for lopil_0  Clear preset filters        |

| Compensation<br>Compensation Mode:<br>Direct mode is suitable<br>Output Clocks<br>Number Of Clocks:<br>System Messages | direct                          | best jitte | Presets for iopII_0 Clear preset filters Project |

### Figure 4. IP Parameter Editor (Intel Quartus Prime Standard Edition)

| 🕴 Parameters 🛛                                       | - d 着                                                                                     | 🖸 Details 🔅 Block Symbol 🔅 🗕 🛃 🖬                   | •••• IP Port and |

|------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|

| stem: unsaved Path: xcvr_native_al                   | 10_0                                                                                      |                                                    | D                |

| Arria 10 Transceiver Native<br>Itera_xcvr_native_a10 | e PHY                                                                                     | Arria 10 Transceiver                               | Parameter        |

| " General                                            |                                                                                           | Hative IIII                                        | Details          |

| Message level for rule violations:                   | error 👻                                                                                   | Name altera_xcvr_native_a10                        |                  |

| " Common PMA Options                                 |                                                                                           | Version 17.0                                       |                  |

| VCCR_GXB and VCCT_GXB supply vol                     | tage for the Transcelver, a wy                                                            | Author Altera Corporation                          |                  |

| Tranceiver Link Type:                                |                                                                                           | Description Arria 10 Transceiver Nati              |                  |

|                                                      | SR 💌                                                                                      | Group Interface Protocols/Trans                    |                  |

| Note - The above options are only us                 | ed for GUI rule validation. Use Quartus II Setting File (.qsf) assignments to set these p | Data Sheet http://www.altera.com/li                |                  |

|                                                      |                                                                                           | User Guide https://documentation.at                |                  |

| Datapath Options                                     |                                                                                           |                                                    |                  |

| Transceiver configuration rules:                     | Basic/Custom (Standard PCS)                                                               | 🔍 🛛 🕹                                              |                  |

| PMA configuration rules:                             | A O New IP Variation <@sj-slscf011>                                                       | $\otimes$                                          |                  |

| Transceiver mode:                                    | Your IP settings will be saved in a .qsys file.                                           | esets 🕴 🗕 🗗 🗖                                      |                  |

| Number of data channels:                             |                                                                                           | s for xcvr_native_a10_0                            |                  |

| Data rate:                                           | Create IP Variation                                                                       | ×                                                  |                  |

| Enable datapath and interface re                     | Entity name: unnamed                                                                      | 1                                                  |                  |

| Enable simplified data interface                     | Save in folder: /users/ibrossar                                                           | ck New to create a preset.                         |                  |

| Disconnect analog resets                             | save in router. Pasers jon ossa                                                           | 10GBASE-R                                          |                  |

|                                                      | Target Device                                                                             | 10GBASE-R Low Latency                              |                  |

| Messages 🕺                                           | Family, Arria 10                                                                          | 10GBASE-R Register Mode                            |                  |

|                                                      |                                                                                           | 10GBASE-R w/ KR-FEC                                |                  |

| Type Path<br>S Info Messages                         | Device: 10AS016C3019E2LG                                                                  | CPRI 9.8Gbps Auto Mode<br>CPRI 9.8Gbps Manual Mode |                  |

| Unsaved.xcvr_native_a10                              | Info: Your IP will be saved in /users/jbrossar/unnamed.gsys.                              | DisplayPort Duplex 4 SYMBOLS PER CLOCK             |                  |

| unsaved.xcvr_native_all                              |                                                                                           | DisplayPort Rx 4 SYMBOLS PER CLOCK                 |                  |

| 0 unsaved.xcvr_native_al0                            |                                                                                           |                                                    |                  |

| 0 unsaved.xcvr native a10                            | :                                                                                         | DK Update Delete New                               |                  |

| 1                                                    |                                                                                           |                                                    |                  |

|                                                      | · · · · · · · · · · · · · · · · · · ·                                                     |                                                    |                  |

Specify IP Variation Name .....

# 2.3. Generating IP Cores (Intel Quartus Prime Pro Edition)

Quickly configure Intel FPGA IP cores in the Intel Quartus Prime parameter editor. Double-click any component in the IP Catalog to launch the parameter editor. The parameter editor allows you to define a custom variation of the IP core. The parameter editor generates the IP variation synthesis and optional simulation files, and adds the .ip file representing the variation to your project automatically.

#### Figure 5. IP Parameter Editor (Intel Quartus Prime Pro Edition)

| 🔒 📀 IP Parameter Editor Pro - test* (/data/jbrossar/designs/stp_i         | in_hdl_example/test.ip) <@sj-slscf011 📀 🔗 🛛 🛞 |

|---------------------------------------------------------------------------|-----------------------------------------------|

| <u>File Edit System Generate Yiew Tools H</u> elp                         |                                               |

| n Parameters 🕴 🗕 🖬 🗖                                                      | Details 🛛 🚆 Block Symbol 🔅 🛛 🗕 🗗 🗖            |

| System: test Path: iopII_0                                                | Show signals                                  |

| Intel FPGA IOPLL<br>altera_iopII                                          | iopll_0                                       |

| PLL Settings Cascading Dynamic Reconfiguration Advanced                   | reset, locked                                 |

| * Device                                                                  |                                               |

| Device Family: Arria 10                                                   | refcik, outcikO<br>refcik, outcikO            |

| Component: 10AS016C3U19E2LG                                               |                                               |

| Speed Grade:                                                              | altera_iopil                                  |

| 🔻 General                                                                 |                                               |

| Reference Clock Frequency: 100.0 MHz                                      | IP Parameters IP Block Symbol                 |

| Enable locked output port                                                 |                                               |

| Enable physical output clock parameters                                   |                                               |

| Compensation                                                              |                                               |

| Compensation Mode:                                                        | 🍯 Presets 🛛 🗕 🗗 🗖                             |

| Direct mode is suitable for most applications. It provides the best jitte | Presets for iopII_0                           |

| Output Clocks                                                             | Clear preset filters                          |

| Number Of Clocks:                                                         |                                               |

|                                                                           | Region                                        |

| 1000 XXX                                                                  | Project                                       |

| 👌 System Messages 🙁 🗕 🗗 🗖                                                 |                                               |

| Type Path 📉                                                               | Apply Update Delete New                       |

| 0 Errors, 0 Warnings                                                      | Generate HDL Finish                           |

Follow these steps to locate, instantiate, and customize an IP core in the parameter editor:

- 1. Create or open an Intel Quartus Prime project (.qpf) to contain the instantiated IP variation.

- In the IP Catalog (Tools ➤ IP Catalog), locate and double-click the name of the IP core to customize. To locate a specific component, type some or all of the component's name in the IP Catalog search box. The New IP Variation window appears.

- 3. Specify a top-level name for your custom IP variation. Do not include spaces in IP variation names or paths. The parameter editor saves the IP variation settings in a file named <your\_ip>.ip. Click **OK**. The parameter editor appears.

- 4. Set the parameter values in the parameter editor and view the block diagram for the component. The **Parameterization Messages** tab at the bottom displays any errors in IP parameters:

- Optionally, select preset parameter values if provided for your IP core. Presets specify initial parameter values for specific applications.

- Specify parameters defining the IP core functionality, port configurations, and device-specific features.

- Specify options for processing the IP core files in other EDA tools.

*Note:* Refer to your IP core user guide for information about specific IP core parameters.

- 5. Click Generate HDL. The Generation dialog box appears.

- 6. Specify output file generation options, and then click **Generate**. The synthesis and simulation files generate according to your specifications.

- 7. To generate a simulation testbench, click **Generate ➤ Generate Testbench System**. Specify testbench generation options, and then click **Generate**.

- 8. To generate an HDL instantiation template that you can copy and paste into your text editor, click **Generate ➤ Show Instantiation Template**.

- 9. Click **Finish**. Click **Yes** if prompted to add files representing the IP variation to your project.

- 10. After generating and instantiating your IP variation, make appropriate pin assignments to connect ports.

- *Note:* Some IP cores generate different HDL implementations according to the IP core parameters. The underlying RTL of these IP cores contains a unique hash code that prevents module name collisions between different variations of the IP core. This unique code remains consistent, given the same IP settings and software version during IP generation. This unique code can change if you edit the IP core's parameters or upgrade the IP core version. To avoid dependency on these unique codes in your simulation environment, refer to *Generating a Combined Simulator Setup Script*.

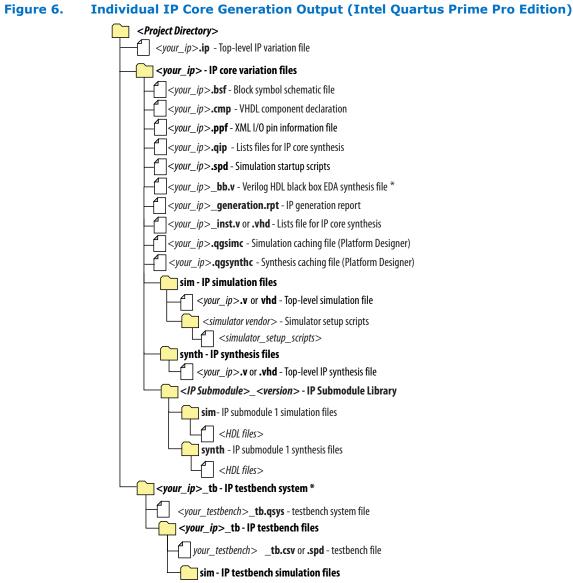

### 2.3.1. IP Core Generation Output (Intel Quartus Prime Pro Edition)

The Intel Quartus Prime software generates the following output file structure for individual IP cores that are not part of a Platform Designer system.

Send Feedback

\* If supported and enabled for your IP core variation.

#### Table 6. Output Files of Intel FPGA IP Generation

| File Name                                     | Description                                                                                                                                                                                                |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <your_ip>.ip</your_ip>                        | Top-level IP variation file that contains the parameterization of an IP core in your project. If the IP variation is part of a Platform Designer system, the parameter editor also generates a .qsys file. |

| <your_ip>.cmp</your_ip>                       | The VHDL Component Declaration ( . ${\rm cmp}$ ) file is a text file that contains local generic and port definitions that you use in VHDL design files.                                                   |

| <pre><your_ip>_generation.rpt</your_ip></pre> | IP or Platform Designer generation log file. Displays a summary of the messages during IP generation.                                                                                                      |

|                                               | continued                                                                                                                                                                                                  |

Viterbi IP Core User Guide

#### 2. Viterbi IP Core Getting Started 683280 | 2017.11.06

# intel

| File Name                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <pre><your_ip>.ggsimc (Platform Designer systems only)</your_ip></pre> | Simulation caching file that compares the .qsys and .ip files with the current parameterization of the Platform Designer system and IP core. This comparison determines if Platform Designer can skip regeneration of the HDL.                                                                                                                                                                                                                                                   |  |  |

| <your_ip>.qgsynth (Platform<br/>Designer systems only)</your_ip>       | Synthesis caching file that compares the .qsys and .ip files with the current parameterization of the Platform Designer system and IP core. This comparison determines if Platform Designer can skip regeneration of the HDL.                                                                                                                                                                                                                                                    |  |  |

| <your_ip>.qip</your_ip>                                                | Contains all information to integrate and compile the IP component.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| <your_ip>.csv</your_ip>                                                | Contains information about the upgrade status of the IP component.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| <your_ip>.bsf</your_ip>                                                | A symbol representation of the IP variation for use in Block Diagram Files (.bdf).                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| <your_ip>.spd</your_ip>                                                | Input file that ip-make-simscript requires to generate simulation scripts.<br>The .spd file contains a list of files you generate for simulation, along with<br>information about memories that you initialize.                                                                                                                                                                                                                                                                  |  |  |

| <your_ip>.ppf</your_ip>                                                | The Pin Planner File $(.ppf)$ stores the port and node assignments for IP components you create for use with the Pin Planner.                                                                                                                                                                                                                                                                                                                                                    |  |  |

| <your_ip>_bb.v</your_ip>                                               | Use the Verilog blackbox $(\_bb.v)$ file as an empty module declaration for use as a blackbox.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| <your_ip>_inst.v or _inst.vhd</your_ip>                                | HDL example instantiation template. Copy and paste the contents of this file into your HDL file to instantiate the IP variation.                                                                                                                                                                                                                                                                                                                                                 |  |  |

| < <i>your_ip</i> >.regmap                                              | If the IP contains register information, the Intel Quartus Prime software<br>generates the .regmap file. The .regmap file describes the register map<br>information of master and slave interfaces. This file complements<br>the .sopcinfo file by providing more detailed register information about the<br>system. This file enables register display views and user customizable statistics<br>in System Console.                                                             |  |  |

| <your_ip>.svd</your_ip>                                                | Allows HPS System Debug tools to view the register maps of peripherals that connect to HPS within a Platform Designer system.<br>During synthesis, the Intel Quartus Prime software stores the .svd files for slave interface visible to the System Console masters in the .sof file in the debug session. System Console reads this section, which Platform Designer queries for register map information. For system slaves, Platform Designer accesses the registers by name. |  |  |

| <your_ip>.v <your_ip>.vhd</your_ip></your_ip>                          | HDL files that instantiate each submodule or child IP core for synthesis or simulation.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| mentor/                                                                | Contains a msim_setup.tcl script to set up and run a ModelSim simulation.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| aldec/                                                                 | Contains a Riviera*-PRO script rivierapro_setup.tcl to setup and run a simulation.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| /synopsys/vcs                                                          | Contains a shell script $vcs\_setup.sh$ to set up and run a VCS* simulation.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| /synopsys/vcsmx                                                        | Contains a shell script vcsmx_setup.sh and synopsys_sim.setup file to set up and run a VCS MX* simulation.                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| /cadence                                                               | Contains a shell script ncsim_setup.sh and other setup files to set up and run an NCSIM simulation.                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| /submodules                                                            | Contains HDL files for the IP core submodule.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| <ip submodule="">/</ip>                                                | Platform Designer generates /synth and /sim sub-directories for each IP submodule directory that Platform Designer generates.                                                                                                                                                                                                                                                                                                                                                    |  |  |

Send Feedback

# 2.4. Simulating Intel FPGA IP Cores

The Intel Quartus Prime software supports IP core RTL simulation in specific EDA simulators. IP generation creates simulation files, including the functional simulation model, any testbench (or example design), and vendor-specific simulator setup scripts for each IP core. Use the functional simulation model and any testbench or example design for simulation. IP generation output may also include scripts to compile and run any testbench. The scripts list all models or libraries you require to simulate your IP core.

The Intel Quartus Prime software provides integration with many simulators and supports multiple simulation flows, including your own scripted and custom simulation flows. Whichever flow you choose, IP core simulation involves the following steps:

- 1. Generate simulation model, testbench (or example design), and simulator setup script files.

- 2. Set up your simulator environment and any simulation scripts.

- 3. Compile simulation model libraries.

- 4. Run your simulator.

# 2.5. DSP Builder for Intel FPGAs Design Flow

DSP Builder for Intel FPGAs shortens digital signal processing (DSP) design cycles by helping you create the hardware representation of a DSP design in an algorithm-friendly development environment.

This IP core supports DSP Builder for Intel FPGAs. Use the DSP Builder for Intel FPGAs flow if you want to create a DSP Builder for Intel FPGAs model that includes an IP core variation; use IP Catalog if you want to create an IP core variation that you can instantiate manually in your design.

#### **Related Information**

Using MegaCore Functions chapter in the DSP Builder for Intel FPGAs Handbook.

Viterbi IP Core User Guide

intel

# **3. Viterbi IP Core Functional Description**

# 3.1. Decoder

The Viterbi decoder can be a continuous or block decoder.

The continuous decoder processes a number of symbols greater than the traceback length. When the decoder traces back the number of bits (traceback length), it delivers output bits. This behavior changes when you assert the end of packet (EOP) signal. The decoder then switches to block decoding, starting traceback from the last symbol or state. The tr\_init\_state signal indicates the end state that starts the traceback operation. For block decoding Intel recommends you indicate the end state of the tail bits (usually zero) and set the tb\_type signal to 1.

# **3.2. Convolutional Encoder**

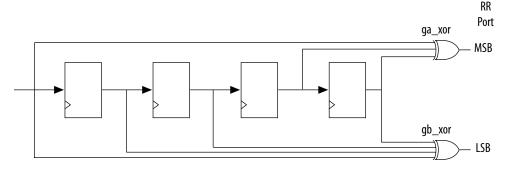

The viterbi IP core convolutional encoder.

#### Figure 7. Convolutional Encoder

L = 5, N = 2 and polynomials GA = 19 and GB = 29. GA in decimal is 19, which is equal to 10011 in binary. The most significant bit of the binary representation is the connection at the input data bit; the least significant bit (LSB) represents the connection at the end of the shift register chain. The XOR function implements the modulo-2 adding operation

# **3.3. Trellis Coded Modulation**

Trellis coded modulation (TCM) combines modulation and encoding processes to achieve better efficiency without increasing the bandwidth.

Bandwidth-constrained channels operate in the region R/W > 1, where R = data rate and W = bandwidth available. For such channels, digital communication systems use bandwidth efficient multilevel phase modulation. For example, phase shift keying (PSK), phase amplitude modulation (PAM), or quadrature amplitude modulation (QAM).

ISO 9001:2015 Registered

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

When you apply TCM to a bandwidth-constrained channel, you see a performance gain without expanding the signal bandwidth. An increase in the number of signal phases from four to eight requires approximately 4dB in additional signal power to maintain the same error rate. Hence, if TCM is to provide a benefit, the performance gain of the rate 2/3 code must overcome this 4dB penalty. If the modulation is an integral part of the encoding process and is designed in conjunction with the code to increase the minimum Euclidian distance between the pairs of coded signals, the loss from the expansion of the signal set is easily overcome and significant coding gain is achieved with relatively simple codes.

Any bandwidth-constrained system benefits from this technique, for example, satellite modem systems. The TCM Viterbi decoder only supports N = 2 (only mother code rates of 1/2).

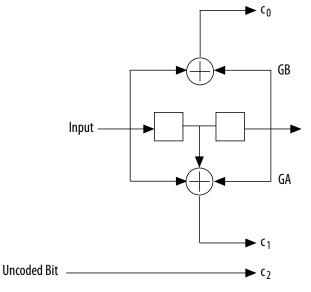

### 3.3.1. Half-Rate Convolutional Codes

A 1/2 rate convolutional code encodes one information bit and leaves the second information bit uncoded.

#### Figure 8. Half-Rate Convolutional Code

With an eight-point signal constellation (e.g. eight-PSK), the two bits select one of the four subsets in the signal constellation. The remaining information bit selects one of the two points within each subset.

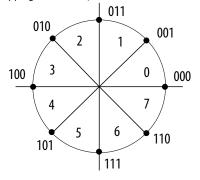

#### Figure 9. Mapping of Coded Bits and Sector Numbers

The specific mapping is not important. You can derive other mappings by permutating subsets in a way that preserves the main property of increased minimum distance among the subsets. However, you can create any other mapping, including symbol mappings for 8-PSK, 16-PSK and others.

If you create another mapping, you must correctly connect the branch metrics created outside the IP core to the input ports and correctly configure the polynomials GA and GB for the trellis generation.

Send Feedback

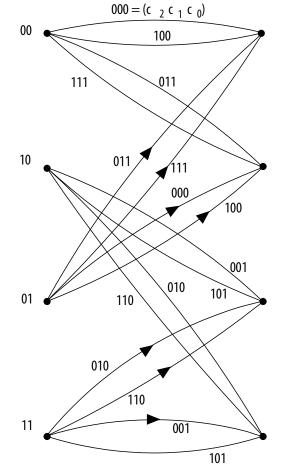

#### Figure 10. Four-State Trellis

The four-state trellis is the trellis for the 1/2 rate convolution encoder with the addition of parallel paths in each transition to accommodate the uncoded bit c2. The decoder uses the coded bits (c1, c0) to select one of the four subsets that contain two signal points each It uses the uncoded bit to select one of the two signal points within each subset.

### **3.3.2. Trellis Decoder**

The decoder processes an arriving symbol to obtain four branch metric values and a sector number. The branch metrics enter the Viterbi decoder in trellis mode and it obtains the encoded bit.

The encoder re-encodes this bit stream and the decoder uses the output of this encoder with the sector number information to retrieve the uncoded bit. The testbench implements all the logic. The wizard generates the branch metric values and sector number values, so you need no logic to create these values. The testbench reads the sector number when it needs it. It has no delay functionality nor rotation. The wizard-created data introduces has no phase error so the phase is aligned. In a real system, you must calculate the phase. For a TCM code the BER block does not produce a meaningful output (numerr), because the BER block does not compute errors at the input for TCM codes.

decdat0

#### Rotate Delay Trellis ► decdat1 Sector Output Sector Number Number Demapper ROM (I, Q) T to Branch Rate 1/2 Q Metric Convolutional and Encoder Sector Number Branch Viterbi

Metric

Rotate

#### Figure 11. Implementation of the Viterbi Decoder as a Trellis Decoder

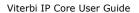

## 3.3.3. About Converting Received Signals

The Viterbi decoder calculates the distances to the nearest four symbol points as an unsigned number in the range 0...00 to 1...11 (number of softbits).

Decoder

Trellis Mode

Where the range is equal to the radius of the symbol map. The decoder works with accumulative metrics (not Euclidean metrics), so the decoder inverts these distances (000 becomes 111; 001 becomes110).

# Figure 12. Conversion of Received Symbol into Four Branch Metrics and a Sector Number

For example, consider a received symbol that lands in sector number 2 with the following distances to the four nearest symbol map points:

- 1111

- 1101

- 1011

- 0001

Where the distance of the radius for 4 softbits is 1111. The distances are inverted to obtain the following branch metrics:

- Branch metric 0 = 0000

- Branch metric 1 = 0010

- Branch metric 2 = 0100

- Branch metric 3 = 1110

The decoder uses the coded bits (c1, c0) to select the branch metric number, which it uses to decide where to connect the branch metrics to the rr input of the Viterbi decoder. Branch metric 3 goes to the most significant bits (MSB) of rr; branch metric 0 goes to the least significant bits (LSB) of rr.

Send Feedback

3. Viterbi IP Core Functional Description 683280 | 2017.11.06

## 3.3.4. Trellis Termination

Block decoders must properly decode the last bits of the block and adapt to the convolutional encoder.

Tail-biting feeds the convolutional encoder with a block and terminates it with (L - 1) unknown bits taken from the end of the block. Tail-biting sets the initial state of the convolutional encoder with the last (L - 1) information bits. Tail-biting is decoded by replicating the block at the decoder or double feeding the block into the decoder. By decoding in the middle point, the trellis is forced into the state that is both the initial state and the end state. From the first decoding block, you can take the last half of the block; from the second decoded block (or second pass through the decoder), you can obtain the first half of the block.

*Note:* In tail-biting, the block size must be large enough to train the decoder, otherwise you may see BER loss.

Alternatively, if you initialize the convolutional encoder to zero, the initial state of the trellis is zero. The decoder knows the last (L - 1) bits to the convolutional encoder. They bring the convolutional encoder to a known end state. The decoder then uses this information to set the end state of the trellis with tr\_init\_state, which is derived from the last (L - 1) bits of the block in reverse order. For example, for a block that ends in: ...000101 If L = 5 and the decoder knows the last (L - 1) = 4 bits, it sets tr\_init\_state as 0101, which reversed and in binary is 1010, or 10 in decimal. The wizard generates tr\_init\_state as if it knows the last (L - 1) bits of each block.

### 3.3.5. Trellis Initialization

The parallel decoder always starts its trellis from state zero for a new block.

However, the hybrid decoder allows you to set the initial state (usually zero) with  $bm_init\_state$ . This signal ranges from 0 to 2 (L - 1) - 1, which are the trellis states. The  $bm_init\_value$  signal initializes the state metric of the state indicated by  $bm_init\_state$ . The decoder initializes all other states with zero. The appropriate value for this port is approximately  $2^{(bmgwide - 2)}$  or any value between  $2^{(N + softbits)}$  to  $2^{(bmgwide - 1)}$ . Continuous decoders never reset the state metrics, which creates a possible difference if the same block of data is sent several times. Initially, the decoder sets the state metrics so that the state metric for state 0 is 0, and all others infinity. For any subsequent blocks, the state metrics contain whatever they have when the previous block ends.

# **3.4. Viterbi IP Core Parameters**

### **3.4.1. Architecture**

#### Table 7. **Architecture Parameters**

| Parameter           | Value                      | Description                                                                                                                                                                               |  |  |

|---------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Viterbi architecure | Hybrid or Parallel         | Selects the hybrid or parallel architecture.                                                                                                                                              |  |  |

| BER                 | On or Off                  | Specifies the BER estimator option, refer to "BER Estimator" on page 3–<br>7.                                                                                                             |  |  |

| Node Sync           | On or Off                  | Specifies the node synchronization option (only available when BER option is on).                                                                                                         |  |  |

| Optimizations       | None, Continuous, or Block | Specifies the optimization for the parallel decoder. if you select <b>None</b> you can turn on <b>Best State Finder</b> . However, to use less logic, turn off <b>Best State Finder</b> . |  |  |

#### 3.4.1.1. BER Estimator

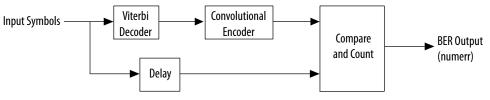

The BER estimator option uses a re-encode and compare approach for estimating the number of errors in the input data.

#### Figure 13. **BER Block Diagram**

In cases where the signal-to-noise ratio is sufficiently high to allow the decoder to decode an error-free output, the BER estimation is very close to the actual channel BER. When the decoder is not decoding an error-free output, the estimated BER is higher and more random than the actual channel BER, which introduces a degree of uncertainty directly proportional to the output errors.

Note: For a TCM code, the BER block does not produce a meaningful output (numerr) because the BER block does not compute errors at the input for TCM codes.

# 1.00e-01 BER 1.00e-02 --- Actual BER --- Estimated BER 1.00e-03 3.00 3.50 4.00 4.50 5.00 5.50 6.00 Signal-to-Noise Ratio

#### Figure 14. Graph Comparing Actual BER with Estimated BER

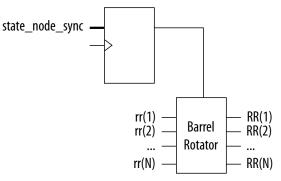

#### 3.4.1.2. Node Synchronization

If you are not using external synchronization, you may not know the order of your N bits. The node synchronization option allows you to rotate the rr inputs until the decoder is in synchronization. To use node synchronization, you observe the BER and keep changing state\_node\_sync to rotate the rr inputs until you get the correct value for the BER.

#### Figure 15. Node Synchronization Block Diagram

The following equation represents node synchronization:

RR[i] = rr[((state\_node\_sync + i - 1) mod N) + 1]

where i is 1 to N.

RR and rr are treated as an array of width N of busses softbits wide. The range of valid values for state\_node\_sync is 0 to (N - 1).

Send Feedback

# 3.4.2. Code Sets

| Parameter                     | Value                                | Description                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of Code<br>Sets        | 1 to 8                               | The Viterbi IP core supports multiple code definitions. The multiple code set option allows up to eight code sets, where a code set comprises a code rate and associated generating polynomials.                                                                                                                                                               |

| Number of coded bits. (N)     | 2 to 7 (hybrid)<br>2 to 4 (parallel) | For every bit to be encoded, N bits are output. With the multiple code set option there are up to 5 different N parameters, which can be in any order. Valid only for Viterbi mode. For TCM mode only N = 2 is supported                                                                                                                                       |

| Constraint length<br>(L)      | 3 to 9                               | The constraint length. Defines the number of states in the convolutional encoder, where number of states = $2(L - 1)$ . You can choose different values of L for each code set.                                                                                                                                                                                |

| Decimal or Octal              | -                                    | Decimal or octal base representation for the generator polynomials. The design file representation is decimal, but you have the option of entering in either decimal or octal base.                                                                                                                                                                            |