# **PCI Express Compiler**

# **User Guide**

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 www.altera.com

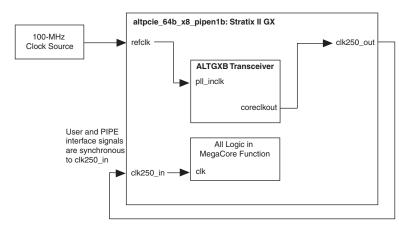

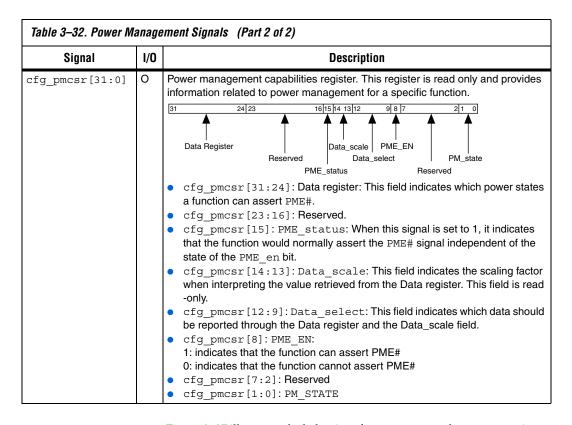

MegaCore Version: **Document Version:** 6.1 rev. 2 Document Date: December 2006

6.1

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published in-

formation and before placing orders for products or services.

## **Contents**

| About This User Guide                                    |      |

|----------------------------------------------------------|------|

| Revision History                                         | i    |

| How to Contact Altera                                    |      |

| Typographic Conventions                                  |      |

| Chapter 1. About This Compiler                           |      |

| Release Information                                      | 1–1  |

| Device Family Support                                    |      |

| New in PCI Express Compiler Version 6.1                  |      |

| Features                                                 |      |

| General Description                                      | 1–3  |

| Testbench & Example Designs: Simple DMA and Chaining DMA |      |

| OpenCore Plus Evaluation                                 |      |

| Performance                                              |      |

|                                                          |      |

| Chapter 2. Getting Started                               |      |

| Design Flow                                              | 2–1  |

| PCI Express Walkthrough                                  |      |

| Launch the MegaWizard Plug-In Manager                    |      |

| Parameterize                                             |      |

| Set Up Simulation                                        | 2-9  |

| Generate Files                                           |      |

| Simulate the Design                                      | 2–14 |

| IP Functional Simulation Model                           | 2–14 |

| Compile the Design                                       |      |

| Program a Device                                         |      |

| Set Up Licensing                                         | 2–16 |

#### Chapter 3. Specifications Clocking 3–72 Chapter 4. External PHYs External PHY Support 4–1 External PHY Constraint Support 4–16

| Chapter 5. Testbench & Example Designs                       |      |

|--------------------------------------------------------------|------|

| Testbench                                                    |      |

| Simple DMA Example Design                                    |      |

| Example Design BAR/Address Map                               |      |

| Chaining DMA Example Design                                  |      |

| Example Design BAR/Address Map                               |      |

| Chaining DMA Descriptor Tables                               |      |

| Test Driver Modules                                          |      |

| BFM Test Driver Module For Simple DMA Example Design         |      |

| BFM Test Driver Module for Chaining DMA Example Design       |      |

| Root Port BFM                                                |      |

| BFM Memory Map                                               |      |

| Configuration Space Bus and Device Numbering                 |      |

| Configuration of Root Port and Endpoint                      |      |

| Issuing Read & Write Transactions to the Application Layer   |      |

| BFM Procedures and Functions                                 |      |

| BFM Read and Write Procedures                                |      |

| BFM Performance Counting                                     |      |

| BFM Read/Write Request Procedures                            |      |

| BFM Configuration Procedures                                 |      |

| BFM Shared Memory Access Procedures                          |      |

| BFM Log & Message Procedures                                 |      |

| Verilog HDL Formatting Functions                             |      |

| Procedures and Functions Specific to the chaining DMA Design | 5–61 |

| Appendix A.                                                  |      |

| Configuration Signals                                        |      |

| Configuration Signals for x1 and x4 MegaCore Functions       | A-1  |

| Configuration Signals for x8 MegaCore Functions              | A-6  |

| Appendix B.                                                  |      |

| Fransaction Layer Packet Header Formats                      |      |

| Content Without Data Payload                                 | B-1  |

| Content with Data Payload                                    |      |

| •                                                            |      |

| Appendix C.                                                  |      |

| Test Port Interface Signals                                  |      |

| Test-Out Interface Signals for                               |      |

| x1 and x4 MegaCore Functions                                 |      |

| Test-Out Interface Signals for x8 MegaCore Functions         | C-19 |

| Test-In Interface                                            | C-22 |

## **About This User Guide**

### **Revision History**

The table below displays the revision history for the chapters in this User Guide.

| Chapter | Date          | Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | December 2006 | 6.1     | Added support for the Stratix® III device family     Updated version and performance information                                                                                                                                                                                                                                                                                                                                         |

|         | April 2006    | 2.1.0   | Rearranged content     Updated performance information                                                                                                                                                                                                                                                                                                                                                                                   |

|         | October 2005  | 2.0.0   | <ul> <li>Added x8 support</li> <li>Added device support for Stratix II GX and Cyclone<sup>®</sup> II</li> <li>Updated performance information</li> </ul>                                                                                                                                                                                                                                                                                 |

|         | June 2005     | 1.0.0   | First release                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2       | December      | 6.1     | <ul> <li>Updated screen shots and version numbers</li> <li>Modified text to accommodate new MegaWizard<sup>®</sup> interface</li> <li>Updated installation diagram</li> <li>Updated walkthrough to accommodate new MegaWizard interface</li> </ul>                                                                                                                                                                                       |

|         | April 2006    | 2.1.0   | <ul> <li>Updated screen shots and version numbers</li> <li>Added steps for sourcing Tcl constraint file during compilation to the walkthrough in the section "Compile the Design" on page 2–15</li> <li>Moved installation information to release notes</li> </ul>                                                                                                                                                                       |

|         | October 2005  | 2.0.0   | Updated screen shots and version numbers                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | June 2005     | 1.0.0   | First release                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3       | December 2006 | 6.1     | <ul> <li>Updated screen shots and parameters for new MegaWizard interface</li> <li>Corrected timing diagrams</li> </ul>                                                                                                                                                                                                                                                                                                                  |

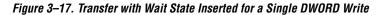

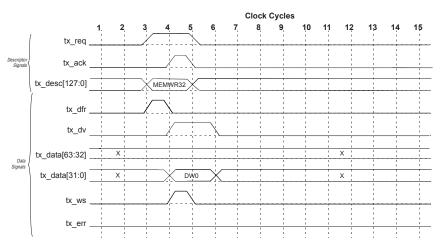

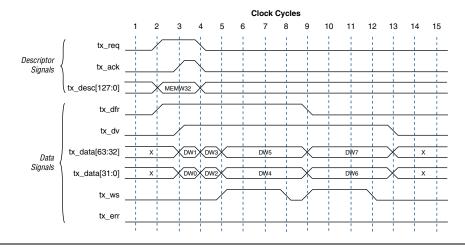

|         | April 2006    | 2.1.0   | <ul> <li>Added section "Analyzing Throughput" on page 3–11</li> <li>Updated screen shots and version numbers</li> <li>Updated System Settings, Capabilities, Buffer Setup, and Power Management Pages and their parameters</li> <li>Added three waveform diagrams:         Transfer for a single write         Transaction layer not ready to accept packet         Transfer with wait state inserted for a single DWORD     </li> </ul> |

|         | October 2005  | 2.0.0   | Updated screen shots and version numbers                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | June 2005     | 1.0.0   | First release                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Chapter    | Date          | Version        | Changes Made                                                                                                                                                                                                                        |

|------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4          | December 2006 | 6.1            | <ul> <li>Modified file names to accommodate new project directory<br/>structure</li> <li>Added references for high performance, Chaining DMA Example</li> </ul>                                                                     |

|            | April 2006    | 2.1.0          | New chapter, "External PHYs", added for external PHY support                                                                                                                                                                        |

| 5          | December 2006 | 6.1            | Added high performance, Chaining DMA Example                                                                                                                                                                                        |

|            | April 2006    | 2.1.0          | <ul> <li>Updated chapter number to chapter 5</li> <li>Added section</li> <li>Added two BFM Read/Write Procedures:         <ul> <li>ebfm_start_perf_sample Procedure</li> <li>ebfm_disp_perf_sample Procedure</li> </ul> </li> </ul> |

|            | October 2005  | 2.0.0          | Updated screen shots and version numbers                                                                                                                                                                                            |

|            | June 2005     | 1.0.0          | First release                                                                                                                                                                                                                       |

| Appendix A | April 2006    | 2.1.0          | Removed restrictions for x8 ECRC                                                                                                                                                                                                    |

|            | June 2005     | 1.0.0          | First release                                                                                                                                                                                                                       |

| Appendix B | October 2005  | 2.1.0          | Minor corrections                                                                                                                                                                                                                   |

|            | June 2005     | 1.0.0          | First release                                                                                                                                                                                                                       |

| Appendix C | April         | 2.1.0          | Updated ECRC to include ECRC support for x8                                                                                                                                                                                         |

|            | October 2005  | 1.0.0          | Updated ECRC noting no support for x8                                                                                                                                                                                               |

|            | June 2005     |                | First release                                                                                                                                                                                                                       |

| all        | April 2006    | 2.1.0<br>rev 2 | Minor format changes throughout user guide                                                                                                                                                                                          |

### How to Contact Altera

For the most up-to-date information about Altera® products, go to the Altera website at www.altera.com. For technical support on this product, go to www.altera.com/mysupport. For additional information about Altera products, consult the sources shown below.

| Information Type              | USA & Canada                                                   | All Other Locations                                                    |  |  |

|-------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|--|--|

| Technical support             | www.altera.com/mysupport/                                      | www.altera.com/mysupport/                                              |  |  |

|                               | (800) 800-EPLD (3753)<br>(7:00 a.m. to 5:00 p.m. Pacific Time) | +1 408-544-8767<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time  |  |  |

| Product literature            | www.altera.com                                                 | www.altera.com                                                         |  |  |

| Altera literature services    | literature@altera.com                                          | literature@altera.com                                                  |  |  |

| Nontechnical customer service | (800) 767-3753                                                 | + 1 408-544-7000<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time |  |  |

| FTP site                      | ftp.altera.com                                                 | ftp.altera.com                                                         |  |  |

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                                                                        |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file.                                                                                   |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Design.                                                                                                                                                                                                                   |

| Italic type                                 | Internal timing parameters and variables are shown in italic type. Examples: $t_{PlA}$ , $n+1$ .                                                                                                                                                                                                                                  |

|                                             | Variable names are enclosed in angle brackets (< >) and shown in italic type. Example: <file name="">, <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre></file>                                                                                                                            |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                                      |

| "Subheading Title"                          | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                                      |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: $\mathtt{data1}$ , $\mathtt{tdi}$ , $\mathtt{input}$ . Active-low signals are denoted by suffix $\mathtt{n}$ , $\mathtt{e.g.}$ , $\mathtt{resetn}$ .                                                                                                         |

|                                             | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (for example, the VHDL keyword BEGIN), as well as logic function names (for example, TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc.         | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                                  |

| •••                                         | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                              |

| ✓                                           | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                               |

|                                             | The hand points to information that requires special attention.                                                                                                                                                                                                                                                                   |

| CAUTION                                     | A caution calls attention to a condition or possible situation that can damage or destroy the product or the user's work.                                                                                                                                                                                                         |

| WARNING                                     | A warning calls attention to a condition or possible situation that can cause injury to the user.                                                                                                                                                                                                                                 |

| 4                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                                        |

| •••                                         | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                                    |

## 1. About This Compiler

### Release Information

Table 1–1 provides information about this release of the Altera® PCI Express Compiler.

| Table 1–1. PCI Express Compiler Release Information |                                     |  |  |  |  |

|-----------------------------------------------------|-------------------------------------|--|--|--|--|

| Item Description                                    |                                     |  |  |  |  |

| Version                                             | 6.1                                 |  |  |  |  |

| Release Date                                        | December 2006                       |  |  |  |  |

| Ordering Code                                       | IP-PCIE/1<br>IP-PCIE/4<br>IP-PCIE/8 |  |  |  |  |

| Product IDs                                         | 00A9<br>00AA<br>00AB                |  |  |  |  |

| Vendor ID                                           | 6A66                                |  |  |  |  |

# Device Family Support

MegaCore® functions provide either full or preliminary support for target Altera device families:

- Full support means the MegaCore function meets all functional and timing requirements for the device family and may be used in production designs

- Preliminary support means the MegaCore function meets all functional requirements, but may still be undergoing timing analysis for the device family; it may be used in production designs with caution.

Table 1–2 shows the level of support offered by the PCI Express Compiler to each Altera device family.

| Table 1–2. Device Family Support |             |  |  |  |

|----------------------------------|-------------|--|--|--|

| Device Family                    | Support     |  |  |  |

| Cyclone® II                      | Full        |  |  |  |

| HardCopy® II                     | Preliminary |  |  |  |

| Stratix® II                      | Full        |  |  |  |

| Stratix II GX                    | Preliminary |  |  |  |

| Stratix III                      | Preliminary |  |  |  |

| Stratix GX                       | Full        |  |  |  |

| Other device families            | No support  |  |  |  |

## New in PCI Express Compiler Version 6.1

The following features have been added to this version:

- Stratix III device support

- New MegaWizard<sup>®</sup> interface

- High performance example design with chaining DMA

- Reduced latency for common clock applications

#### **Features**

- Support for x1, x4, and x8 endpoint applications including nontransparent bridging applications

- Cyclone II, , HardCopy II, Stratix II, Stratix II GX, Stratix III, and Stratix GX support

- Embedded transceiver support for x1, x4, and x8 applications

- x8 support in Stratix II GX devices

- Extensive external PHY support for the x1 and x4 MegaCore functions

- Compliance for PCI Express Base Specification 1.1

- Easy integration into customer design

- Functional simulation models for use in Altera-supported VHDL and Verilog HDL simulators

- Simple DMA example design

- High performance chaining DMA example design

- Highly flexible and configurable MegaCore functions

- Up to 4 virtual channels

- Maximum payload up to 2Kbyte (128, 256, 512, 1,024, or 2,048 bytes)

- Retry buffer size up to 16Kbytes (from 256 bytes to 16 KBytes)

- Access to high reliability features

- Optional end-to-end cyclic redundancy code (ECRC)/advanced error reporting (AER) support for x1, x4, and x8 lanes

- Free evaluation using OpenCore Plus

# General Description

The PCI Express Compiler generates customized PCI Express MegaCore functions you use to design PCI Express endpoints, including non-transparent bridges, or truly unique designs combining multiple PCI Express components in a single Altera device. The PCI Express MegaCore functions are PCI Express Base Specification Revision 1.1 or PCI Express MegaCore functions are PCI Express Base Specification Revision 1.0a compliant, and implement all required and most optional features of the specification for the transaction, data link, and physical layers.

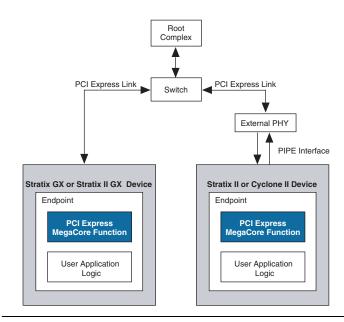

The PCI Express Compiler allows you to select from 3 MegaCore functions that support x1, x4, or x8 operation and that are suitable for endpoint applications. Figure 1–1 shows how the PCI Express MegaCore functions can be used in an example system. If you target the MegaCore function for Stratix GX or Stratix II GX devices, the MegaCore function includes a complete PHY layer, including the MAC, PCS, and PMA layers. If you target other device architectures, the PCI Express Compiler generates the MegaCore function with the Intel-designed PIPE interface, making the MegaCore function usable with other PIPE-compliant external PHY devices.

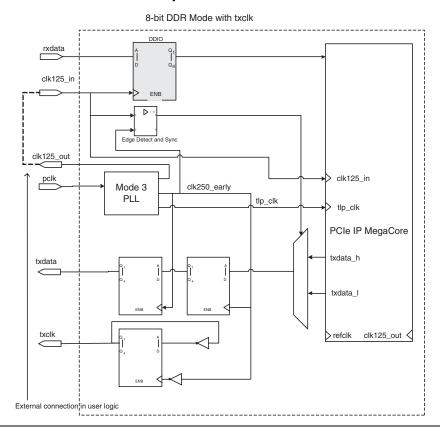

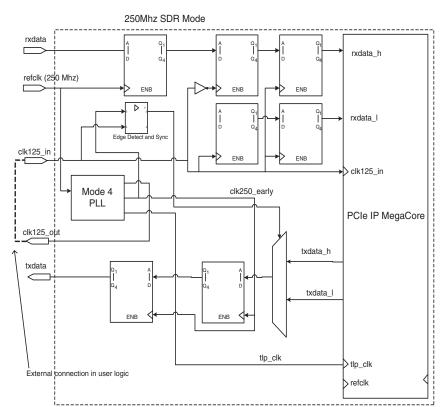

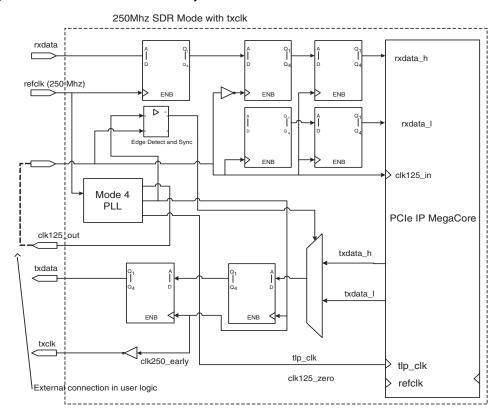

When selecting your external PHY, the PCI Express MegaCore functions support a wide range of PHYs including the TI XIO1100 PHY in 8-bit DDR mode or 16-bit SDR mode; Philips PX1011A for 8-bit SDR mode, a serial PHY for Stratix II GX and Stratix GX devices, and a range of custom PHYs using 8-bit/16-bit SDR with or without source synchronous transmit cock modes and 8-bit DDR with or without source synchronous transmit clock modes.

Figure 1–1. Example PCI Express System

Optimized for Altera devices, the PCI Express Compiler supports all memory, I/O, configuration, and message transactions. The MegaCore functions have a highly optimized application interface to achieve maximum effective throughput. Because the Compiler is parameterizable, you can customize them to meet design requirements by using the MegaWizard interface in the Quartus® II software. For example, the MegaCore functions can support up to 4 virtual channels for x1 or x4 configurations, or up to 2 channels for x8 configurations. You also can customize the payload size, buffer sizes, and configuration space (base address registers support and other registers). Additionally, the PCI Express Compiler supports end-to-end cyclic redundancy code (ECRC) and advanced error reporting for x1, x4, and x8 configurations.

The PCI Express MegaCore functions also include debug features that allow observation and control of the MegaCore functions. These additional inputs and outputs help with faster debugging of system-level problems.

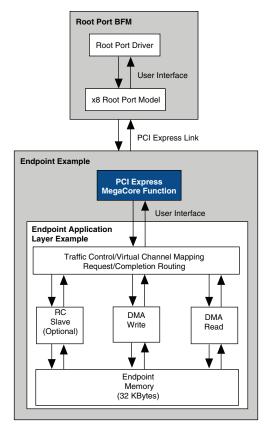

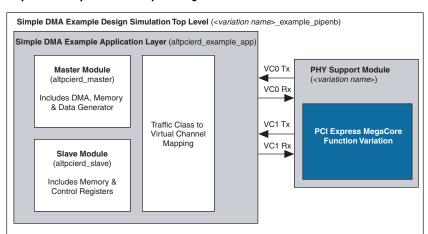

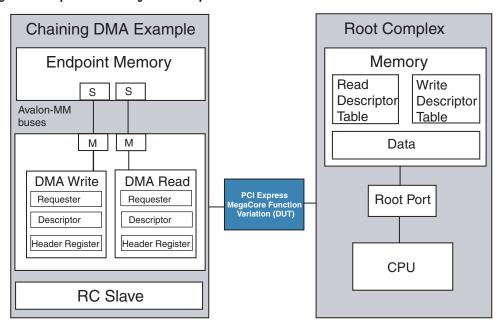

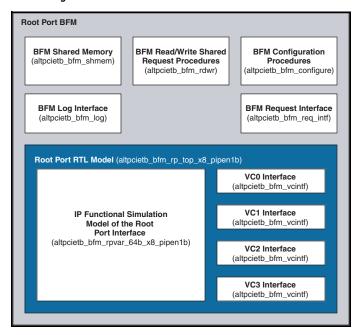

#### Testbench & Example Designs: Simple DMA and Chaining DMA

The PCI Express Compiler includes an endpoint testbench that incorporates a basic root port bus functional model (BFM) and two endpoint design examples: simple DMA and chaining DMA. Both endpoint design examples illustrate the application interface to the PCI Express MegaCore function and are delivered as clear-text source-code (VHDL and Verilog HDL) suitable for both simulation and synthesis, as well as OpenCore Plus evaluation of the MegaCore function in hardware. The basic root port BFM incorporates a driver and an IP functional simulation model of a root port. Figure 1–2 illustrates the endpoint testbench setup for the simple DMA example. Figure 1–3 illustrates the testbench for the chaining DMA example.

Root Port BFM Root Port Driver User Interface x8 Root Port Model PCI Express Link **Endpoint Simple DMA Example PCI Express** MegaCore Function User Interface **Endpoint Application** Layer Example Traffic Control/Virtual Channel Mapping Request/Completion Routing DMA DMA Target Control Control Control Registers Target DMA Memory Memory (32 KBytes) (32 KBytes)

Figure 1-2. Testbench for the Simple DMA Example

You can replace the endpoint application layer example shown in Figure 1-2 or Figure 1-3 with your own application layer design and then modify the BFM driver to generate the transactions needed to test your application layer.

Figure 1-3. Testbench for the Chaining DMA Example

#### **OpenCore Plus Evaluation**

With Altera's free OpenCore Plus evaluation feature, you can perform the following actions:

- Simulate the behavior of a MegaCore function within your system

- Verify the functionality of your design, as well as quickly and easily evaluate its size and speed

- Generate time-limited device programming files for designs that include MegaCore functions

- Program a device and verify your design in hardware

You only need to purchase a license for the MegaCore function when you are completely satisfied with its functionality and performance, and want to take your design to production.

For more information on OpenCore Plus hardware evaluation using the PCI Express compiler, see "OpenCore Plus Time-Out Behavior" on page 3–30 and *AN 320: OpenCore Plus Evaluation of Megafunctions*.

#### **Performance**

Tables in this section show typical expected performance for various parameters using the Quartus II software, version 6.1 for the device families listed.

For the performance data in Table 1–3 through Table 1–7, the parameters below were set.

- On the Buffer Setup page, for x1, x4, and x8 configurations, the following values were set:

- Maximum payload size was set to 256 Bytes unless specified otherwise.

- Desired performance for received requests and Desired performance for completions were both set to Medium. unless otherwise specified.

For a description of the Buffer Setup page settings, see Table 3–20 on page 3–38.

On the Capabilities page, the number of Tags supported was set as to 16 for all configurations unless specified otherwise.

For a description of Capabilities page settings, see Table 3–19 on page 3–35.

Table 1–3 shows the typical expected performance for different parameters, using the Quartus II software, version 6.1 for Cyclone II (EP2C35F484C6) devices.

| Table 1–3. Performance - Cyclone II Devices |                       |                   |       |                  |  |  |  |

|---------------------------------------------|-----------------------|-------------------|-------|------------------|--|--|--|

|                                             | Parameters            |                   |       | Memory<br>Blocks |  |  |  |

| x1/x4                                       | Internal<br>Clock MHz | Logic<br>Elements | M4K   |                  |  |  |  |

| x1                                          | 125                   | 1                 | 9500  | 10               |  |  |  |

| x1                                          | 125                   | 2                 | 12400 | 15               |  |  |  |

| x1(1)                                       | 62.5                  | 1                 | 7800  | 11               |  |  |  |

| x1                                          | 62.5                  | 2                 | 10500 | 18               |  |  |  |

| x4                                          | 125                   | 1                 | 12100 | 18               |  |  |  |

| x4                                          | 125                   | 2                 | 15200 | 27               |  |  |  |

Notes for Table 1-3

<sup>(1)</sup> Max payload was set to 128B, the number of Tags supported was set to 4, and Desired performance for received requests and Desired performance for completions were both set to Low.

$6.1\ Table\ 1–4$  shows the typical expected performance for different parameters, using the Quartus II software, version 6.1 for Stratix II (EP2S130GF1508C3) devices.

| Table 1–4. Performance - Stratix II Devices |                          |                                  |                        |                        |      |     |  |  |

|---------------------------------------------|--------------------------|----------------------------------|------------------------|------------------------|------|-----|--|--|

| Parameters                                  |                          |                                  |                        | Memory Blocks          |      |     |  |  |

| x1/x4                                       | Internal<br>Clock<br>MHz | Number of<br>Virtual<br>Channels | Combinational<br>ALUTs | Dedicated<br>Registers | M512 | M4K |  |  |

| x1                                          | 125                      | 1                                | 6600                   | 3400                   | 2    | 8   |  |  |

| x1                                          | 125                      | 2                                | 8900                   | 4500                   | 3    | 12  |  |  |

| x4                                          | 125                      | 1                                | 8700                   | 4400                   | 6    | 12  |  |  |

| x4                                          | 125                      | 2                                | 11000                  | 5600                   | 7    | 20  |  |  |

Table 1–5 shows the typical expected performance for different parameters, using the Quartus II software version 6.1 for Stratix II GX (EP2SGX130GF1508C3) devices.

| Table 1–5. Per                                         | Table 1–5. Performance - Stratix II GX Devices |                        |                        |      |               |    |  |  |

|--------------------------------------------------------|------------------------------------------------|------------------------|------------------------|------|---------------|----|--|--|

|                                                        | Parameters                                     |                        |                        |      | Memory Blocks |    |  |  |

| x1/x4/x8 Internal Number of Clock Virtual MHz Channels |                                                | Combinational<br>ALUTs | Dedicated<br>Registers | M512 | M4K           |    |  |  |

| x1                                                     | 125                                            | 1                      | 6600                   | 3400 | 2             | 8  |  |  |

| x1                                                     | 125                                            | 2                      | 8900                   | 4500 | 3             | 12 |  |  |

| x4                                                     | 125                                            | 1                      | 8700                   | 4400 | 6             | 12 |  |  |

| x4                                                     | 125                                            | 2                      | 11000                  | 5600 | 7             | 20 |  |  |

| x8                                                     | 250                                            | 1                      | 8300                   | 5800 | 10            | 12 |  |  |

| x8                                                     | 250                                            | 2                      | 10200                  | 6900 | 11            | 20 |  |  |

Table 1–6 shows the typical expected performance for different parameters, using the Quartus II software version 6.1 for Stratix III (EP3SL200F1152C3) devices.

| Table 1–6. Performance - Stratix III Devices |                          |                         |                                  |                        |                        |                  |  |  |

|----------------------------------------------|--------------------------|-------------------------|----------------------------------|------------------------|------------------------|------------------|--|--|

|                                              | Parai                    | neters                  |                                  |                        |                        | Memory<br>Blocks |  |  |

| x1/x4                                        | Internal<br>Clock<br>MHz | Max<br>Payload<br>Bytes | Number<br>of Virtual<br>Channels | Combinational<br>ALUTs | Dedicated<br>Registers | М9К              |  |  |

| x1                                           | 125                      | 256                     | 1                                | 6500                   | 3400                   | 5                |  |  |

| x1                                           | 125                      | 256                     | 2                                | 8700                   | 4500                   | 9                |  |  |

| x4                                           | 125                      | 256                     | 1                                | 8500                   | 4500                   | 7                |  |  |

| x4                                           | 125                      | 256                     | 2                                | 10900                  | 5600                   | 12               |  |  |

Table 1–7 shows the typical expected performance for different parameters, using the Quartus II software version 6.1 for Stratix GX (EP1SGX25CF672C5) devices.

| Table 1–7. Performance - Stratix GX |                       |                                  |                   |               |     |  |  |

|-------------------------------------|-----------------------|----------------------------------|-------------------|---------------|-----|--|--|

| Parameters                          |                       |                                  |                   | Memory Blocks |     |  |  |

| x1/x4                               | Internal<br>Clock MHz | Number of<br>Virtual<br>Channels | Logic<br>Elements | M512          | M4K |  |  |

| x1                                  | 125                   | 1                                | 9500              | 2             | 9   |  |  |

| x1                                  | 125                   | 2                                | 12300             | 2             | 14  |  |  |

| х4                                  | 125                   | 1                                | 14500             | 6             | 16  |  |  |

| x4                                  | 125                   | 2                                | 17100             | 7             | 24  |  |  |

The following table shows the recommended device family speed grades for the supported link widths and internal clock frequencies. When the internal clock frequency is 125 MHz or 250 MHz, the recommended setting is that the Quartus II Analysis & Synthesis Optimization Technique be set to **Speed**.

See the *Quartus II Development Software Handbook* for more information on how to set this.

Table 1–8. Recommended Device Family and Speed Grades **Internal Clock** Recommended Speed Link Width **Device Family** Grades Frequency 125MHz -6 Cyclone II x1, x4 х1 62.5MHz -6, -7, -8*(4)* Stratix II GX 125MHz x1, x4 -3, -4, -5 *(1)* x8 250MHz -3(1), -4(2), (3)Stratix II x1, x4 125MHz -3, -4, -5 *(1)* х1 62.5Mhz -3, -4, -5 Stratix III x1, x4 125MHz -2, -3, -4х1 62.5MHz -2.-3.-4 Stratix GX x1, x4 125MHz -5(1)62.5MHz х1 -5,-6

#### Notes:

- (1) To achieve timing closure for these speed grades and variations enabling Physical Synthesis in the Quartus II Fitter Settings is required with these options enabled: Perform physical synthesis for combinational logic, perform register duplication, and perform register retiming. See the *Quartus II Development Software Handbook* for more information on how to set these options.

- (2) Achieving timing closure for x8 in Stratix II GX -4 will require use of the Quartus Design Space Explorer with multiple seeds.

- (3) Multiple VCs, ECRC support, and greater than 16 tags are not recommended for x8 variations in Stratix II GX -4.

- (4) In the -8 speed grade, the External PHY 16-bit SDR or 8-bit SDR modes are recommended

## 2. Getting Started

### **Design Flow**

To evaluate the PCI Express Compiler using the OpenCore Plus feature include these steps in your design flow:

Obtain and install the PCI Express Compiler.

The PCI Express Compiler is part of the MegaCore® IP Library, which is distributed with the Quartus II software and downloadable from the Altera website, www.altera.com.

For system requirements and installation instructions, refer to *Quartus II* Installation & Licensing for Windows or *Quartus II Installation & Licensing for UNIX & Linux* on the Altera website at

#### www.altera.com/literature/lit-qts.jsp

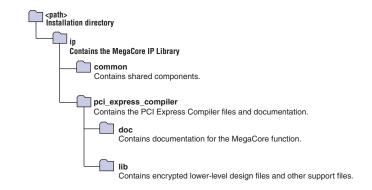

Figure 2–1 shows the directory structure after you install the PCI Express Compiler, where *<path>* is the installation directory. The default installation directory on Windows is **c:\altera\61**; on UNIX and Linux it is **/opt/altera/61**.

Figure 2-1. Directory Structure

- 2. Create a custom variation using the PCI Express Compiler.

- 3. Implement the rest of your design using the design entry method of your choice.

- Use the IP functional simulation model to verify the operation of your design.

For more information on IP functional simulation models, refer to the *Simulating Altera IP in Third-Party Simulation Tools* chapter in volume 3 of the *Quartus II Development Software Handbook*.

5. Use the Quartus II software to compile your design.

You can also generate an OpenCore Plus time-limited programming file, which you can use to verify the operation of your design in hardware.

6. Purchase a license for the PCI Express Compiler.

After you have purchased a license for the PCI Express Compiler Compiler, follow these additional steps:

- 1. Set up licensing.

- Generate a programming file for the Altera® device(s) on your board.

- 3. Program the Altera device(s) with the completed design.

# PCI Express Walkthrough

The PCI Express Compiler comes with 2 example designs. This walkthrough guides you through the process of launching the MegaWizard interface using the MegaWizard Plug-in Manager, parameterizing the MegaCore, and simulating the MegaCore with your choice of the 2 supplied example designs. After generating a custom variation of the PCI Express MegaCore function, you can incorporate it into your overall project.

This walkthrough consists of the following steps:

- Launch the MegaWizard Plug-In Manager

- Parameterize

- Set Up Simulation

- Generate Files

The PCI Express Compiler MegaWizard interface creates two example top-level designs to connect with the PCI Express MegaCore function variation that you create. The example top-level designs can be compiled for an Altera device by the Quartus II software. The example simple DMA top-level design is named <*variation name*>\_example\_top. This walkthrough uses pex as the variation name and pex\_example\_top as the simple DMA top-level example design.

The example chaining DMA top-level design is named **pex\_example\_chaining\_top**.

#### Launch the MegaWizard Plug-In Manager

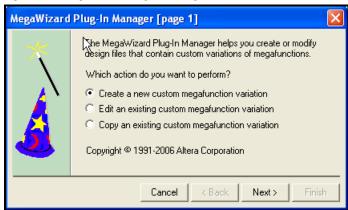

To launch the MegaWizard® Plug-In Manager in the Quartus II software, follow these steps:

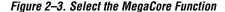

1. Start the MegaWizard Plug-In Manager by choosing **MegaWizard Plug-In Manager** (Tools menu). The **MegaWizard Plug-In Manager** dialog box displays (see Figure 2–2).

Refer to the Quartus II Help for more information on how to use the MegaWizard Plug-In Manager.

Figure 2-2. MegaWizard Plug-In Manager

2. Specify that you want to create a new custom megafunction variation and click **Next**.

- 3. Expand the **Interfaces** directory under **Installed Plug-Ins** by clicking the + icon left of the directory name, then click **PCI Express Compiler v6.1**.

- 4. Choose the device family you want to use for this MegaCore function variation. For example, **Stratix II GX**.

- Select the output file type for your design; the MegaWizard Plug-In Manager supports VHDL and Verilog HDL. In this example, choose Verilog HDL.

- 6. The MegaWizard Plug-In Manager shows the project path that you specified. Append a variation name for the MegaCore function output files roject path\<variation name</p>>. For this walkthrough, specify pex for the name of the MegaCore function files:

#### c:\altera\pcie\_project\pex.vhd

Figure 2–3 shows the MegaWizard Plug-In Manager after you have made these settings.

Click Next to display the Parameter Settings page for the PCI Express Compiler (see Figure 2–4).

You can change the page that the MegaWizard Plug-In Manager displays by clicking **Next** or **Back** at the bottom of the dialog box. You can move directly to a named page by clicking **Parameter Settings**, **Simulation Model**, or **Summary** tab.

Also, you can directly display individual parameter settings by clicking on options on specific parameter pages.

#### **Parameterize**

To parameterize your MegaCore function, follow these steps:

For this section, you can use the parameter settings shown in the figures or your own settings. The example design is generated to adapt to most settings, although some tests may not run for specific settings. The parameter settings required to use the testbench fully are noted for each MegaWizard page.

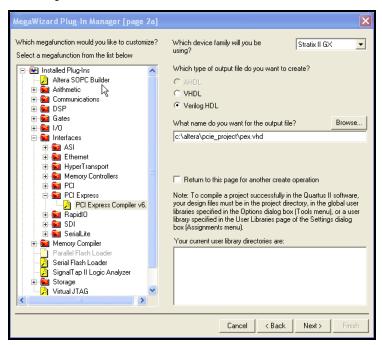

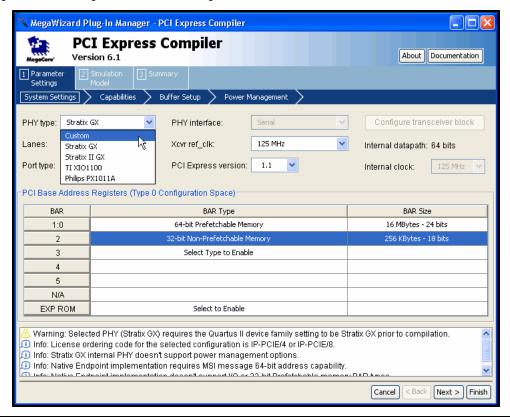

Click the Parameter Settings tab in the MegaWizard interface (see Figure 2–4).

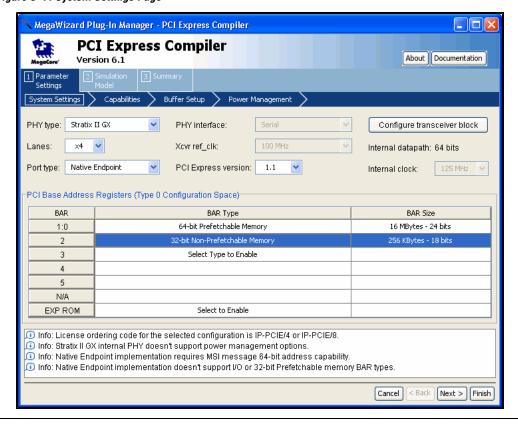

The **System Settings** page is the first page displayed. Set parameters on this page that are appropriate for the MegaCore function instance you will implement. See Figure 2–4.

Figure 2-4. System Settings Page

To enable all of the tests in the provided testbench and Simple DMA example design, make the BAR assignments shown in Table 2–1 below.

| Table 2–1. BAR Assignments |                                |                     |  |  |

|----------------------------|--------------------------------|---------------------|--|--|

| BAR                        | BAR TYPE                       | BAR Size            |  |  |

| 1:0                        | 64-Bit Prefetchable Memory     | 16 MBytes - 24 bits |  |  |

| 2                          | 32-bit Non-Prefetchable Memory | 256 Kbytes -18 bits |  |  |

Many other BAR settings allow full testing of the Simple DMA example design. See the "BFM Test Driver Module For Simple DMA Example Design" on page 5–20 for a description of what settings the test module uses.

See "Parameter Settings" on page 3–31 for a detailed description of the available parameters.

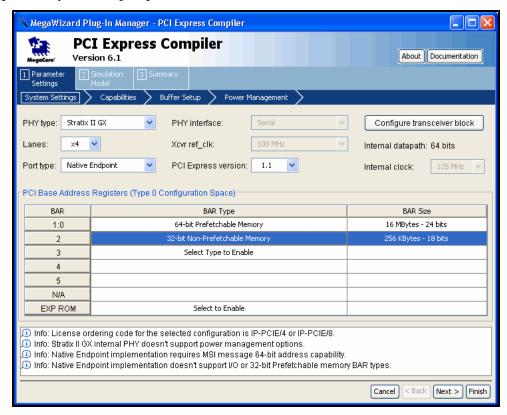

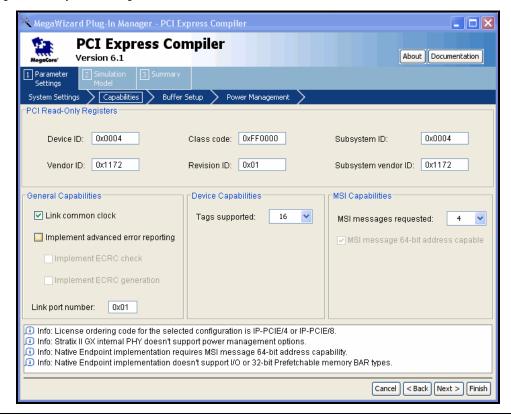

- 2. Click **Next** to display the **Capabilities** page.

- 3. With the **Capabilities** page open, make the appropriate settings and click **Next** to display the **Buffer Setup** page. See Figure 2–5.

Figure 2-5. Capabilities Page

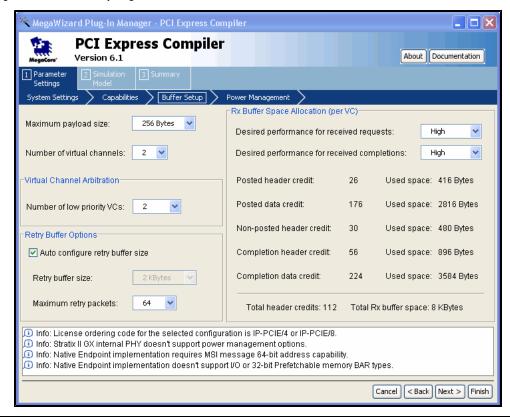

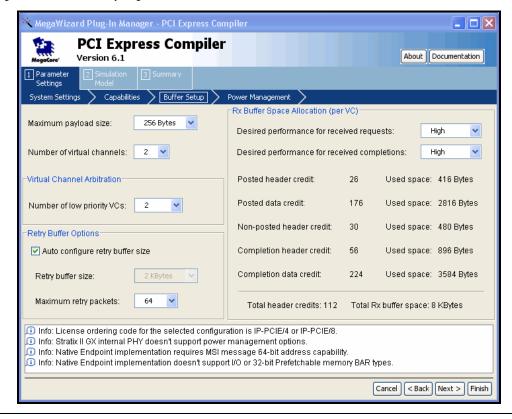

4. The **Buffer Setup** page opens. Make the appropriate settings and click **Next**. See Figure 2–6.

Figure 2-6. Buffer Setup Page

To determine the appropriate settings for the **Desired performance for received requests** and **Desired performance for received completions** parameters, refer to Table 3–20 on page 3–38. For additional information regarding data credits, refer to Table 3–2 on page 3–15.

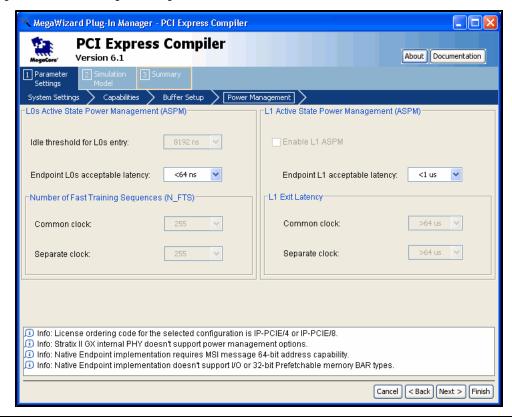

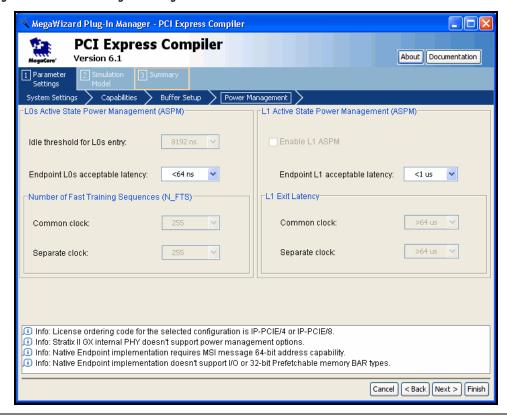

5. The **Power Management** page opens. Make the appropriate settings. See Figure 2–7.

Figure 2-7. Power Management Page

- 6. To apply the settings, click **Finish**.

- 7. Click **Next** (or the **Simulation Model** page) to display the simulation setup page (see Figure 2–8).

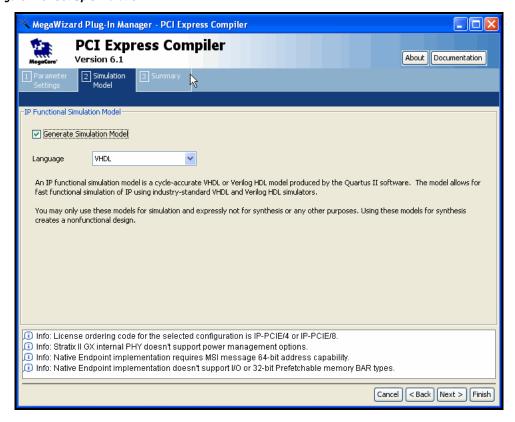

### **Set Up Simulation**

An IP functional simulation model is a cycle-accurate VHDL or Verilog HDL model produced by the Quartus II software. The model allows for fast functional simulation of IP using industry-standard VHDL and Verilog HDL simulators.

You may only use these simulation model output files for simulation purposes and expressly not for synthesis or any other purposes. Using these models for synthesis will create a nonfunctional design.

To generate an IP functional simulation model for your MegaCore function, follow these steps:

1. Click the **Simulation Model** tab (see Figure 2–8).

Figure 2-8. Set Up Simulation

- 2. Click the checkbox to enable the **Generate Simulation Model** (see Figure 2–8).

- 3. Choose the language in the **Language** list pulldown.

Click Next (or the Summary tab) to display the summary page (see Figure 2–9).

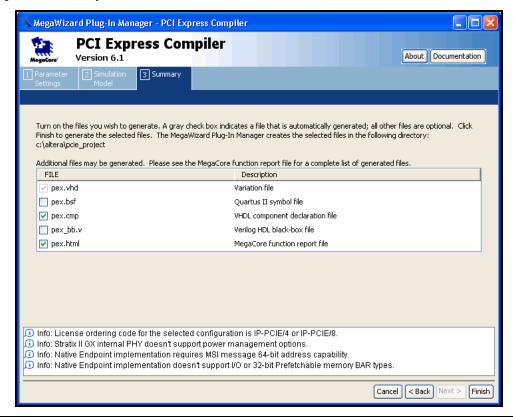

Figure 2-9. Summary

#### **Generate Files**

To generate the files, follow these steps:

Turn on the files you wish to generate. Use the check boxes on the Summary page to enable or disable the generation of specified files. A gray checkmark indicates a file that is automatically generated; any other checkmark indicates an optional file.

At this stage you can still click **Back** or any of the tabs, **Parameters Setting**, **Simulation Model**, or **Summary**, tabs to display any of the other pages in the MegaWizard Plug-In Manager, if you want to change any of the parameters.

To generate the specified files and close the MegaWizard Plug-In Manager, click Finish.

The Generation Panel displays file generation status. When all files have been generated, the Generation panel returns a Generation Successful status message. Click **Exit** to close the panel. The generation phase can take several minutes to complete. A generation report, written to the project directory and named *<variation name>*.html, lists the files and ports generated.

Figure 2-10. Generation Panel

Table 2–2 describes the generated files and other files that may be in your project directory. The names and types of files specified in the summary vary based on whether you created your design using VHDL or Verilog HDL.

| Table 2–2. Generated Files Notes (1)& (2) (Part 1 of 2) |                                                                                                                                                                                                                                                                                                                       |  |  |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Filename                                                | Description                                                                                                                                                                                                                                                                                                           |  |  |

| <variation name="">.ppf</variation>                     | This XML file describes the MegaCore pin attributes to the Quartus II Pin Planner. MegaCore pin attributes include pin direction, location, I/O standard assignments, and drive strength. If you launch the MegaWizard outside of the Pin Planner application, you must explicitly load this file to use Pin Planner. |  |  |

| <variation name="">.ppx</variation>                     | This XML file is a Pin Planner support file that Pin Planner automatically uses. This file must remain in the same directory as the pex.ppf file.                                                                                                                                                                     |  |  |

| <variation name="">.html</variation>                    | MegaCore function report file.                                                                                                                                                                                                                                                                                        |  |  |

| Table 2–2. Generated Files Notes (1)& (2) (Part 2 of 2)                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Filename                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| < <i>variation name&gt;.vhd</i> or<br>< <i>variation name&gt;.v</i>                               | This file instantiates the <variation name="">_core module (or entity) that is described elsewhere in this table and includes additional logic required to suppor the specific external or internal PHY you have choser for your variation. You must instantiate this file inside o your design. You should include this file when you compile your design in the Quartus II software and in your simulation project.</variation> |  |  |

| <pre><variation name="">_core.vhd or <variation name="">_core.v</variation></variation></pre>     | This file instantiates the PCI Express Transaction, Data Link, and Physical layers. It is instantiated inside the < <i>variation name&gt;</i> module (or entity). Include this file when you compile your design in the Quartus II software.                                                                                                                                                                                      |  |  |

| <pre><variation name="">_core.vho or or <variation name="">_core.vo</variation></variation></pre> | This file includes the VHDL or Verilog HDL IP functional simulation model of the < <i>variation name</i> >_ <b>core</b> entity (or module). Include this file when simulating your design.                                                                                                                                                                                                                                        |  |  |

- (1) These files are variation dependent, some may be absent or their names may change.

- (2) <variation name> is a prefix variation name supplied automatically by the MegaWizard Plug-In Manager.

You can now integrate your custom MegaCore function variation into your design, simulate, and compile.

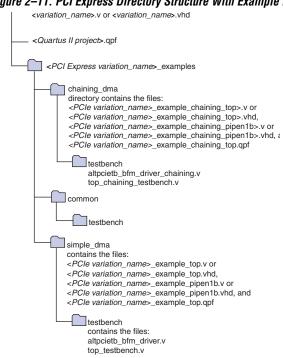

Quartus II software also creates a three-level subdirectory in your project directory named <*variation name>*\_examples. Figure 2–11 illustrates this directory structure. This subdirectory contains a PCI Express BFM and testbench for testing both the Simple DMA example design and the chaining DMA example design. The directory also includes scripts for running the testbench in the ModelSim simulator. See Chapter 5, Testbench & Example Designs for a list and brief description of the files created for the testbench.

Figure 2–11. PCI Express Directory Structure With Example Directory

# Simulate the Design

You can simulate your design using the MegaWizard-generated VHDL and Verilog HDL IP functional simulation models.

For more information on IP functional simulation models, refer to the *Simulating Altera IP in Third-Party Simulation Tools* chapter in volume 3 of the *Quartus II Development Software Handbook*.

#### **IP Functional Simulation Model**

To run the testbench in the ModelSim simulator, follow these steps:

- 1. Start the ModelSim simulator.

- From the ModelSim File menu, use Change Directory to change the working directory to the appropriate example design directory.

For the simple DMA example design, change to the directory: <*your project directory*>/*<variation name*>\_examples/simple\_dma

or

for the chaining DMA example design, change to the directory: <variation name>\_examples/chaining\_dma

Click OK.

3. In the ModelSim Transcript window, execute the command do runtb.do, which sets up the required libraries, compiles the netlist files, and runs the testbench. The ModelSim Transcript window displays messages from the BFM reflecting various values read from the variation file's configuration space. These messages reflect the values entered during the parameterize step of the walkthrough.

Altera also provides the DOS command window batch file **runtb.bat** and the shell script **runtb.sh** to run the testbench in ModelSim command-line mode.

For more information on the testbench, BFM, and included example application, see Chapter 5, Testbench & Example Designs.

# Compile the Design

You can use the Quartus II software to compile the example designs. Refer to Quartus II Help for instructions on compiling your design. In the Quartus II software, open the Simple DMA example design project that you created in "PCI Express Walkthrough" on page 2–2:

c:\altera\pcie\_project\pex\_examples\simple\_dma\pex\_example\_top

This example Quartus II project has the recommended synthesis, fitter, and timing analysis settings for the parameters chosen in the variation used in this example design.

To verify the PCI Express assignments in your project, follow these steps:

- Choose Start Compilation (Processing menu) in the Quartus II software.

- After compilation, expand the Timing Analyzer or TimeQuest

Timing Analyzer folder in the Compilation Report panel by clicking the

+ icon next to the folder name. Note whether the timing constraints were

successfully met from this section of the Compilation Report.

If your design does not initially meet the timing constraints, try using the **Design Space Explorer** in the Quartus II software to find the optimal Fitter settings for your design to meet the timing constraints. To use the **Design Space Explorer**, choose **Launch Design Space Explorer** (Tools Menu).

# Program a Device

After you have compiled your design, program your targeted Altera device, and verify your design in hardware.

With Altera's free OpenCore Plus evaluation feature, you can evaluate the PCI Express MegaCore function before you purchase a license. OpenCore Plus evaluation allows you to generate an IP functional simulation model and produce a time-limited programming file.

For more information on IP functional simulation models, see the *Simulating Altera IP in Third-Party Simulation Tools* chapter in volume 3 of the *Quartus II Development Software Handbook*.

You can simulate the PCI Express MegaCore function in your design and perform a time-limited evaluation of your design in hardware.

For more information on OpenCore Plus hardware evaluation using the PCI Express MegaCore function, see "OpenCore Plus Time-Out Behavior" on page 3–30 and *AN 320: OpenCore Plus Evaluation of Megafunctions*.

# Set Up Licensing

You need to purchase a license for the MegaCore function only when you are completely satisfied with its functionality and performance, and want to take your design to production.

After you purchase a license for the PCI Express MegaCore function, you can request a license file from the Altera website at **www.altera.com/licensing** and install it on your computer. When you request a license file, Altera emails you a **license.dat** file. If you do not have Internet access, contact your local Altera representative.

# 3. Specifications

# Functional Description

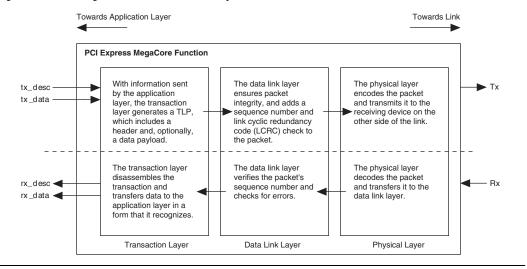

Figure 3–1 broadly describes the roles of each layer of the PCI Express MegaCore function.

Figure 3–1. The MegaCore Function's Three Layers

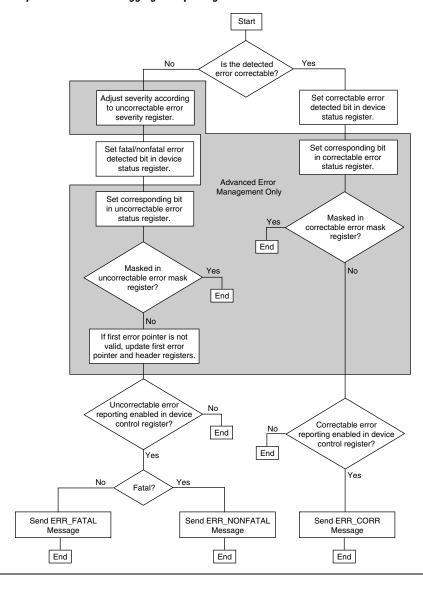

The PCI Express MegaCore functions comply with the PCI Express Base Specification 1.1 or the PCI Express Base Specification Revision 1.0a, and implements all three layers of the specification:

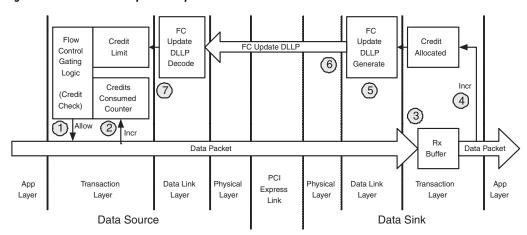

- Transaction Layer—The transaction layer contains the configuration space, which manages communication with the your application layer: the receive and transmit channels, the receive buffer, and flow control credits.

- Data Link Layer—The data link layer, located between the physical layer and the transaction layer, manages packet transmission and maintains data integrity at the link level. Specifically, the data link layer:

- Manages transmission and reception of data link layer packets

- Generates all transmission cyclical redundancy code (CRC) checks and checks all CRCs during reception

- Manages the retry buffer and retry mechanism according to received ACK/NAK data link layer packets

- Initializes the flow control mechanism for data link layer packets and routes flow control credits to and from the transaction layer

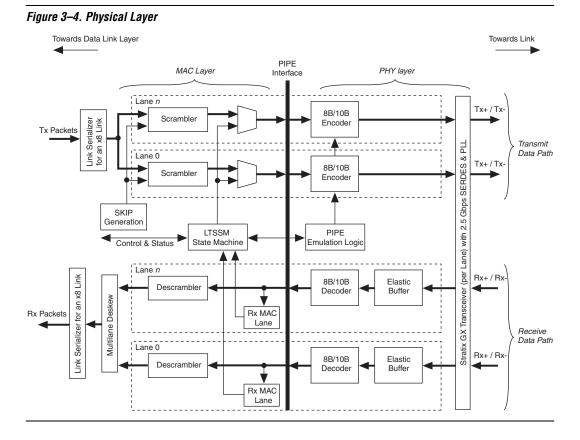

- Physical Layer—The physical layer initializes the speed, lane numbering, and lane width of the PCI Express link according to packets received from the link and directives received from higher layers.

## **Endpoint Types**

The MegaCore function can implement either a native PCI Express endpoint or a legacy endpoint. Altera recommends using native PCI Express endpoints for new applications; they support memory space read and write transactions only. Legacy endpoints provide compatibility with existing applications and can support I/O space read and write transactions.

See the PCI Express specification endpoint description for further information on the differences between native PCI Express and legacy endpoints.

## **Transaction Layer**

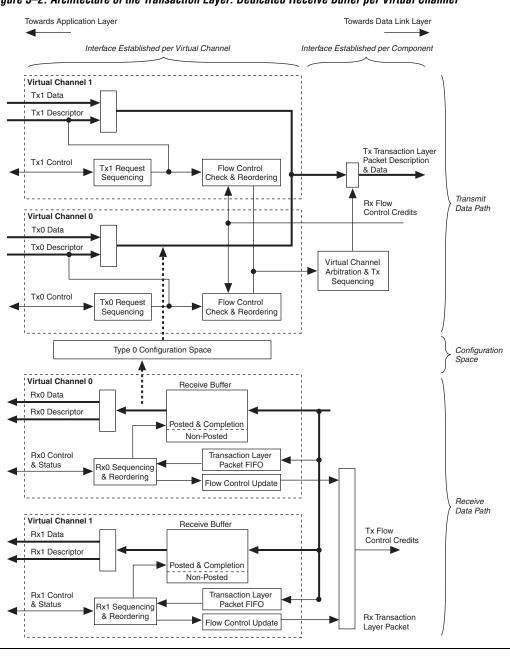

The transaction layer lies between the application layer and the data link layer. It generates and receives transaction layer packets. Figure 3–2 illustrates the transaction layer of a component with two initialized virtual channels. The transaction layer contains three general subblocks: the transmit data path, the configuration space, and the receive data path, which are shown with vertical braces in Figure 3–2.

Figure 3-2. Architecture of the Transaction Layer: Dedicated Receive Buffer per Virtual Channel

Tracing a transaction through the receive data path involves the following steps:

- The transaction layer receives a transaction layer packet from the data link layer.

- The configuration space determines whether the transaction layer packet is well formed and directs the packet to the appropriate virtual channel based on TC/virtual channel mapping.

- Within each virtual channel, transaction layer packets are stored in a specific part of the receive buffer depending on the type of transaction (posted, non-posted, and completion).

- The transaction layer packet FIFO block stores the address of the buffered transaction layer packet.

- 5. The receive sequencing and reordering block shuffles the order of waiting transaction layer packets as needed, fetches the address of the priority transaction layer packet from the transaction layer packet FIFO block, and initiates the transfer of the transaction layer packet to the application layer. Receive logic separates the descriptor from the data of the transaction layer packet and transfers them across the receive descriptor bus rx\_desc[135:0], and receive data bus rx\_data[63:0] to the application layers.

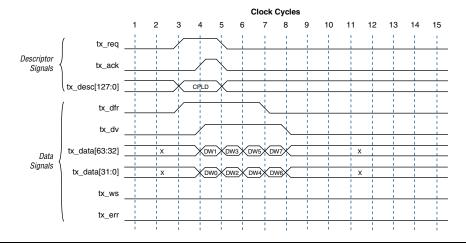

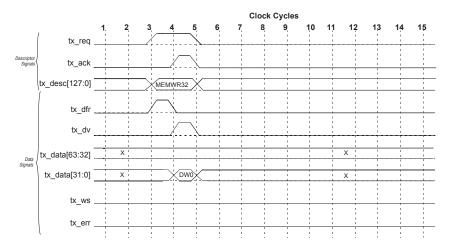

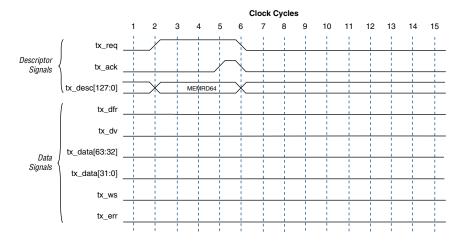

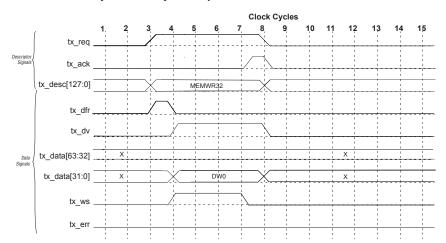

Tracing a transaction through the transmit data path involves the following steps:

- The MegaCore function informs the application layer with transmit credit tx\_cred[21:0] that sufficient flow control credits exist for a particular type of transaction. The application layer may choose to ignore this information.

- 2. The application layer requests a transaction layer packet transmission. The application layer must provide the PCI Express transaction header on the tx\_desc[127:0] bus and be prepared to provide the entire data payload on the tx\_data[63:0] bus in consecutive cycles.

- 3. The MegaCore function verifies that sufficient flow control credits exist, and acknowledges or postpones the request.

- 4. The transaction layer packet is forwarded by the application layer, the transaction layer arbitrates among virtual channels, and then forwards the priority transaction layer packet to the data link layer.

#### Transmit Virtual Channel Arbitration

The PCI Express MegaCore function allows you to divide the virtual channels into high and low priority groups as specified in Chapter 6 of the PCI Express Base Specification 1.1 or the PCI Express Base Specification Revision 1.0a.

Arbitration of high-priority virtual channels uses a strict priority arbitration scheme in which higher numbered virtual channels always have higher priority than lower numbered virtual channels. Low-priority virtual channels use a fixed round robin arbitration scheme.

You can use the settings on the **Buffer Setup** page accessible from the **Parameter Settings** tab in the MegaWizard interface to specify the number of virtual channels and the number of virtual channels in the low priority group. See "Buffer Setup Page" on page 3–37.

#### Configuration Space

The configuration space implements all configuration registers and associated functions below.

- Type 0 Configuration Space

- PCI Power Management Capability Structure

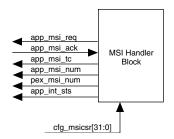

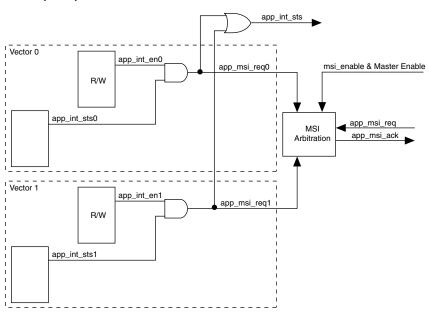

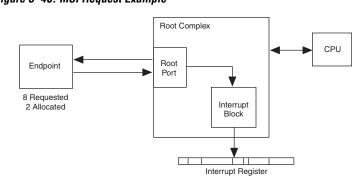

- Message Signaled Interrupt (MSI) Capability Structure

- PCI Express Capability Structure

- Virtual Channel Capabilities

The configuration space also generates all messages (PME#, INT, error, power slot limit, etc.), MSI requests, and completion packets from configuration requests that flow in the direction of the root complex, except power slot limit messages, which are generated by a downstream port in the direction of the PCI Express link. All such transactions are dependent upon the content of the PCI Express configuration space as described in the PCI Express<sup>TM</sup> Base Specification Revision 1.0a.

See "Configuration Space Register Content" on page 3–18 or Chapter 7 in the *PCI Express Base Specification 1.1* or the *PCI Express Base Specification Revision 1.0a* for the complete content of these registers.

#### Transaction Layer Routing Rules

Transactions follow these routing rules.

- In the receive direction (i.e., from the PCI Express link), memory and I/O requests that match to the defined BARs route to the receive interface. The application layer logic processes the requests and generates the read completions, if needed.

- Received type 0 configuration requests route to the internal configuration space and the MegaCore function generates and transmits the completion.

- The MegaCore function internally handles supported received message transactions (power management and slot power limit).

- The transaction layer treats all other received transactions (including memory or I/O requests that do not match a defined BAR) as unsupported requests. The transaction layer sets the appropriate error bits and transmits a completion, if needed. These unsupported requests are not made visible to the application layer, the header and data is dropped.

- The transaction layer sends all memory and I/O requests, as well as completions generated by the application layer and passed to the transmit interface, to the PCI Express link.

- The MegaCore function can generate and transmit power management, interrupt, and error signaling messages automatically under the control of dedicated signals. Additionally, the MegaCore function can generate MSI requests under the control of the dedicated signals.

#### Receive Buffer Bypass Mode

If the receive buffer is empty and the rx\_descriptor register of a given virtual channel does not contain valid data, the MegaCore function bypasses the receive buffer, which decreases latency.

In reality, the receive buffer is not truly bypassed, because the descriptor is written simultaneously to the receive buffer and the rx\_descriptor register. However, barring the need to resend the transaction layer packet, the data in the receive buffer is never accessed.

#### Receive Buffer Reordering

The receive data path implements a receive buffer reordering function that allows posted and completion transactions to pass non-posted transactions (as allowed by PCI Express ordering rules) when the application layer is unable to accept additional non-posted transactions.

The application layer dynamically enables the Rx Buffer reordering by asserting the rx\_mask signal. rx\_mask masks non-posted request transactions made to the application interface so that only posted and completion transactions are presented to the application.

The MegaCore function operates in receive buffer bypass mode when rx\_mask is asserted. However, if masked requests exist, the MegaCore function exits receive buffer bypass mode upon deassertion of rx mask.

#### **Data Link Layer**

The data link layer is located between the transaction layer and the physical layer. It is responsible for maintaining packet integrity and for communication (by data link layer packet transmission) at the PCI Express link level (as opposed to component communication by transaction layer packet transmission within the fabric). Specifically, the data link layer is responsible for the following:

- Link management through the reception and transmission of data link layer packets, which are used:

- To initialize and update flow control credits for each virtual channel

- For power management of data link layer packet reception and transmission

- To transmit and receive ACK/NACK packets

- Data integrity through generation and checking of CRCs for transaction layer packets and data link layer packets

- Transaction layer packet retransmission in case of NAK data link layer packet reception using the retry buffer

- Management of the retry buffer

- Link retraining requests in case of error (through the LTSSM of the physical layer)

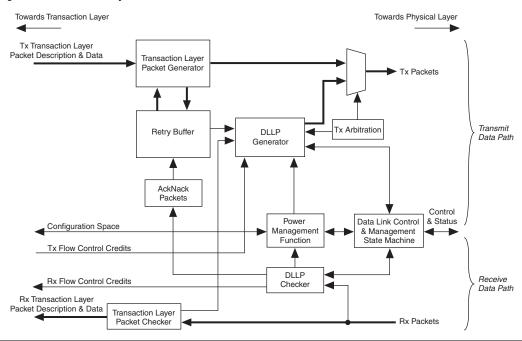

Figure 3–3 illustrates the architecture of the data link layer.

Figure 3-3. Data Link Layer

The data link layer has the following subblocks:

- Data Link Control and Management State Machine—This state machine is synchronized with the physical layer's LTSSM state machine and is also connected to the configuration space registers. It initializes the link and virtual channel flow control credits and reports status to the configuration space. (Virtual channel 0 is initialized by default, as are additional virtual channels if they have been physically enabled and the software permits them.)

- Power Management—This function handles the handshake to enter low power mode. Such a transition is based on register values in the configuration space and received PM DLLPs.

- Data Link Layer Packet Generator and Checker—This block is associated with the data link layer packet's 16-bit CRC and maintains the integrity of transmitted packets.

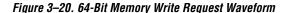

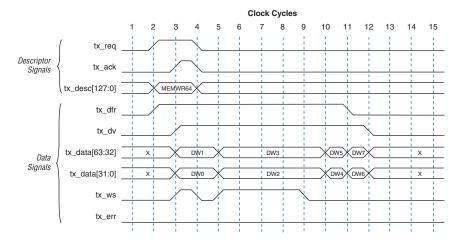

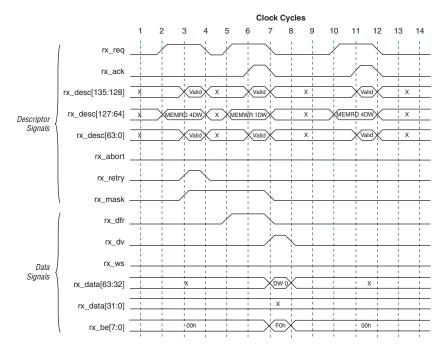

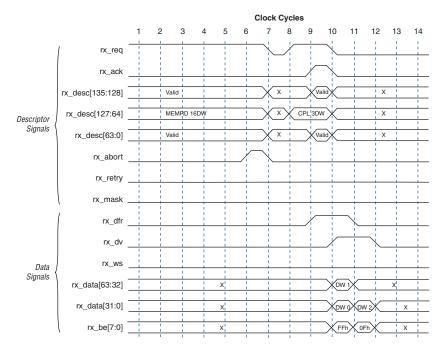

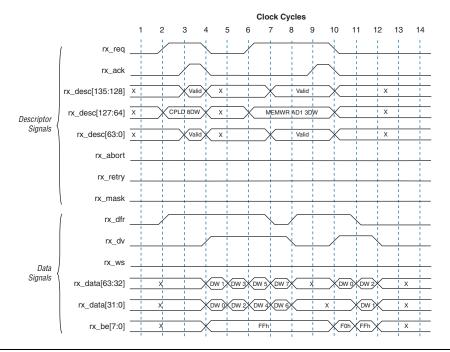

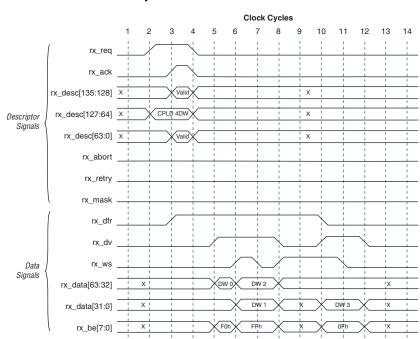

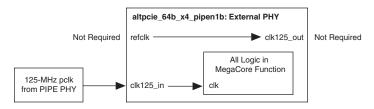

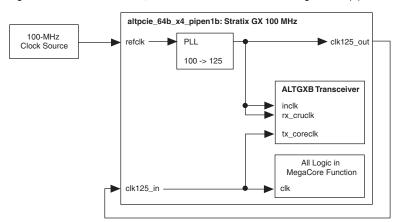

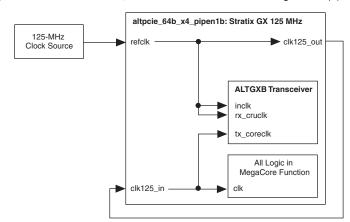

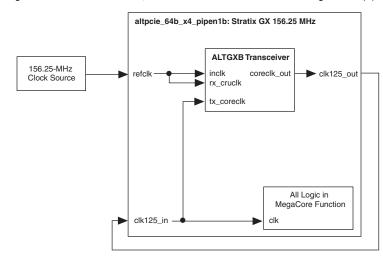

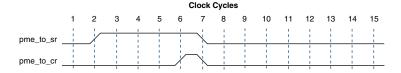

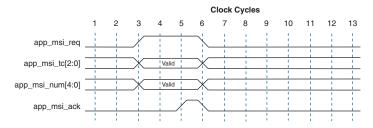

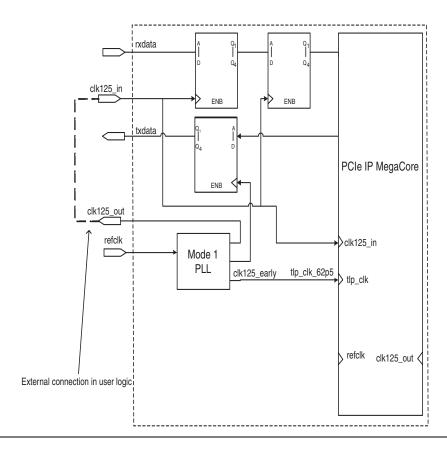

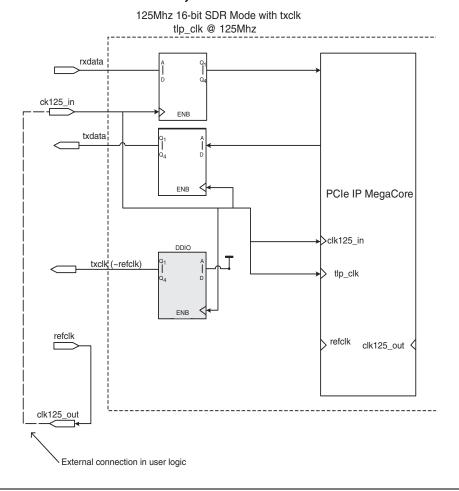

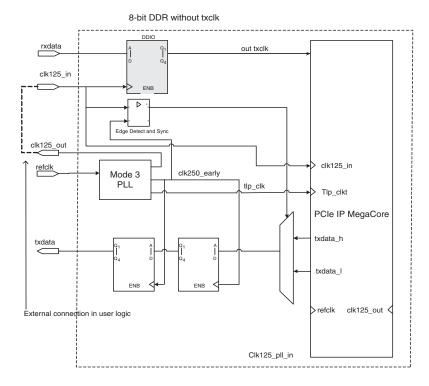

- Transaction Layer Packet Generator—This block generates transmit packets according to the descriptor and data received from the transaction layer, generating a sequence number and a 32-bit CRC. The packets are also sent to the retry buffer for internal storage. In retry mode, the transaction layer packet generator receives the packets from the retry buffer and generates the CRC for the transmit packet.