# PCI Compiler User Guide

The PCI Compiler is scheduled for product obsolescence and discontinued support as described in PDN1410. Therefore, Altera does not recommend use of this IP in new designs. For more information about Altera's current IP offering, refer to Altera's Intellectual Property website.

101 Innovation Drive San Jose, CA 95134 www.altera.com

Compiler Version: Document Date: 11.1 October 2011

Copyright © 2011 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera ascumes no responsibility or liability arising out of the application or use of any information, product, or service describe herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

UG-PCICOMPILER-4.12

# Contents

### **About PCI Compiler**

| Introduction                                      | 1    |

|---------------------------------------------------|------|

| Release Information                               | 2    |

| Device Family Support                             | 2    |

| Features                                          |      |

| Common Features                                   |      |

| PCI Compiler with MegaWizard Plug-in Manager Flow | 4    |

| PCI Compiler with SOPC Builder Flow               |      |

| General Description                               | 5    |

| PCI MegaCore Functions                            | 5    |

| PCI Testbench                                     | 6    |

| PCI Compiler with MegaWizard Plug-in Manager Flow | 6    |

| PCI Compiler With SOPC Builder Flow               |      |

| Selecting the Appropriate Flow for Your Design    | 9    |

| PCI Compiler With SOPC Builder Flow               | 9    |

| PCI Compiler With MegaWizard Plug-in Manager Flow |      |

| Compliance Summary                                |      |

| Performance and Resource Utilization              | . 11 |

| PCI Compiler with MegaWizard Plug-in Manager Flow | 11   |

| PCI Compiler with SOPC Builder Flow               |      |

| Installation and Licensing                        | . 17 |

| OpenCore Plus Evaluation                          |      |

| OpenCore Plus Time-Out Behavior                   | 19   |

# Section I. PCI Compiler With MegaWizard Plug-In Manager Flow

### **Chapter 1. Getting Started**

| Design Flow                              | 1–1  |

|------------------------------------------|------|

| PCI MegaCore Function Design Walkthrough | 1–2  |

| Create a New Quartus II Project          | 1–2  |

| Launch IP Toolbench                      | 1–4  |

| Step 1: Parameterize                     | 1–5  |

| Step 2: Set Up Simulation                | 1–7  |

| Step 3: Generate                         | 1–7  |

| Simulate the Design                      | 1–9  |

| Simulation in the Quartus II Software    | 1–11 |

| The Quartus II Simulation Files          | 1–12 |

| Master Simulation Files                  | 1–13 |

| Target Simulation Files                  | 1–15 |

|                                          |      |

| Compile the Design 1                          | 1–16 |

|-----------------------------------------------|------|

| Program a Device 1                            |      |

| PCI Timing Support 1                          |      |

| Using the Reference Designs 1                 |      |

| pci_mt32 MegaCore Function Reference Design1  |      |

| Synthesis & Compilation Instructions 1        | 1–20 |

| pci_mt64 MegaCore Function Reference Design 1 |      |

| synthesis & Compilation Instructions 1        |      |

### **Chapter 2. Parameter Settings**

| Parameterize PCI Compiler               | . 2–1 |

|-----------------------------------------|-------|

| PCI MegaCore Function Settings          |       |

| Read-Only PCI Configuration Registers   |       |

| PCI Base Address Registers (BARs)       |       |

| Advanced PCI MegaCore Function Features |       |

| Optional Registers                      |       |

| Optional Interrupt Capabilities         |       |

| Master Features                         |       |

| Variation File Parameters               | . 2–7 |

### **Chapter 3. Functional Description**

| Functional Overview                                 |      |

|-----------------------------------------------------|------|

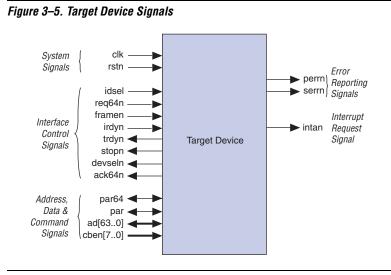

| Target Device Signals & Signal Assertion            |      |

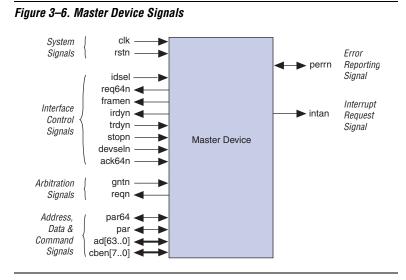

| Master Device Signals & Signal Assertion            |      |

| PCI Bus Signals                                     |      |

| Parameterized Configuration Register Signals        | 3–15 |

| Local Address, Data, Command, & Byte Enable Signals |      |

| Target Local-Side Signals                           |      |

| Master Local-Side Signals                           | 3–24 |

| PCI Bus Commands                                    | 3–27 |

| Configuration Registers                             |      |

| Vendor ID Register                                  | 3–31 |

| Device ID Register                                  | 3–31 |

| Command Register                                    | 3–32 |

| Status Register                                     | 3–33 |

| Revision ID Register                                | 3–34 |

| Class Code Register                                 |      |

| Cache Line Size Register                            | 3–35 |

| Latency Timer Register                              | 3–36 |

| Header Type Register                                |      |

| Base Address Registers                              |      |

| CardBus CIS Pointer Register                        | 3–40 |

| Subsystem Vendor ID Register                        | 3–40 |

| Subsystem ID Register                               | 3–41 |

| Expansion ROM Base Address Register                 |      |

| Capabilities Pointer                                | 3–42 |

| Interrupt Line Register                             | 3–43 |

|                                                     |      |

| Interrupt Pin Register                                                       | 3–43         |

|------------------------------------------------------------------------------|--------------|

| Minimum Grant Register                                                       |              |

| Maximum Latency Register                                                     |              |

| Target Mode Operation                                                        | 3–44         |

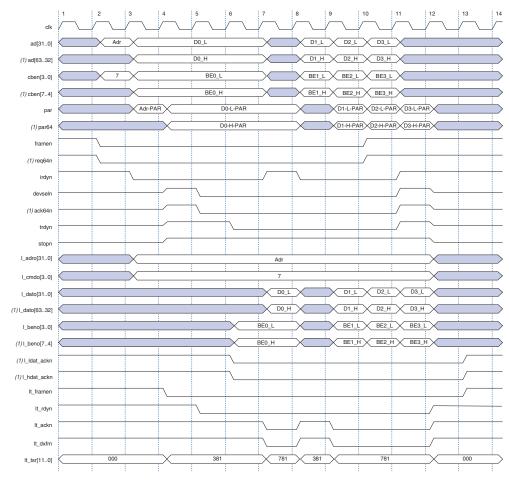

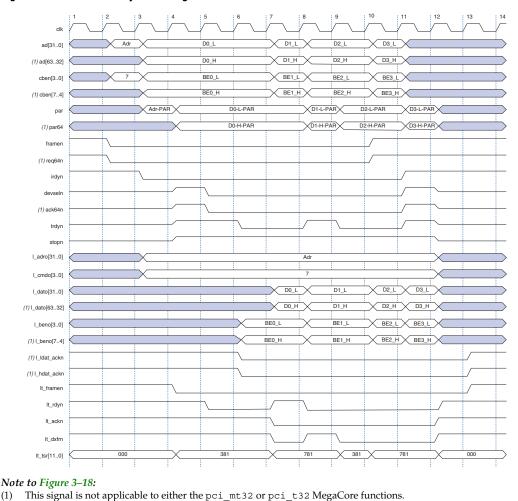

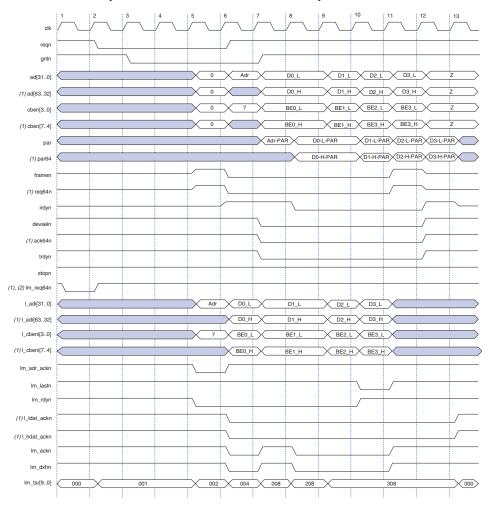

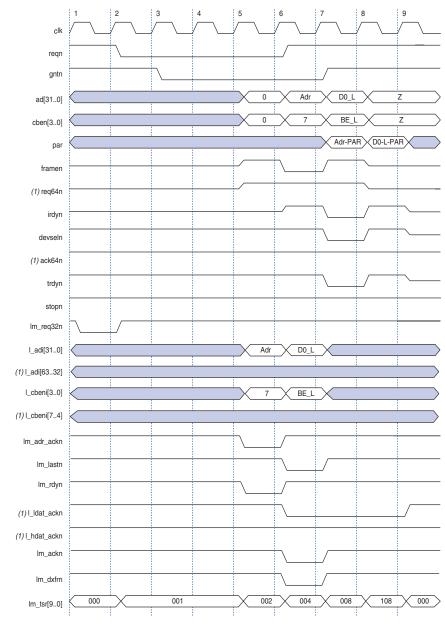

| Target Read Transactions                                                     | 3–48         |

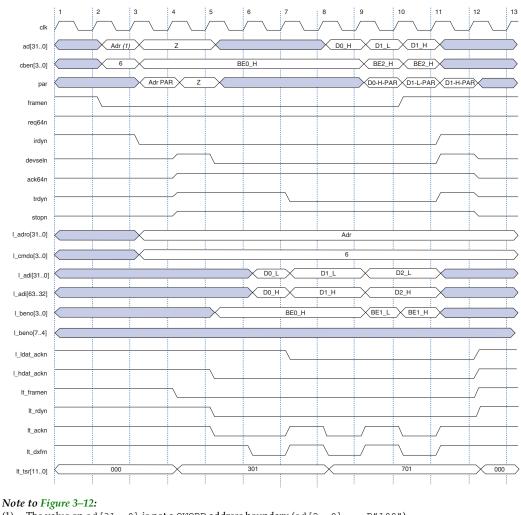

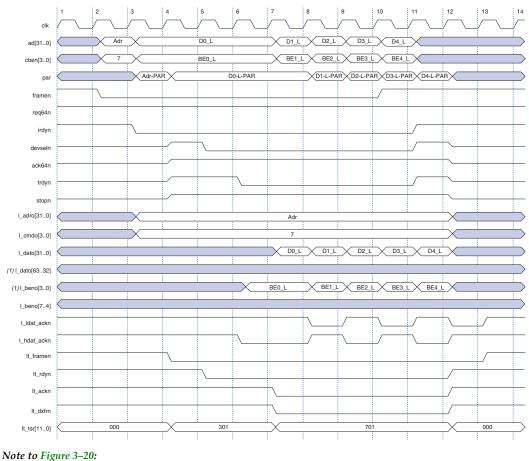

| Memory Read Transactions                                                     | 3–48         |

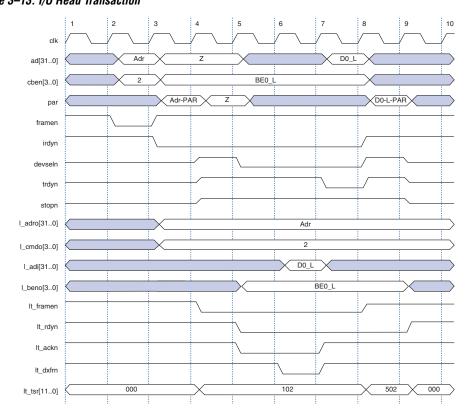

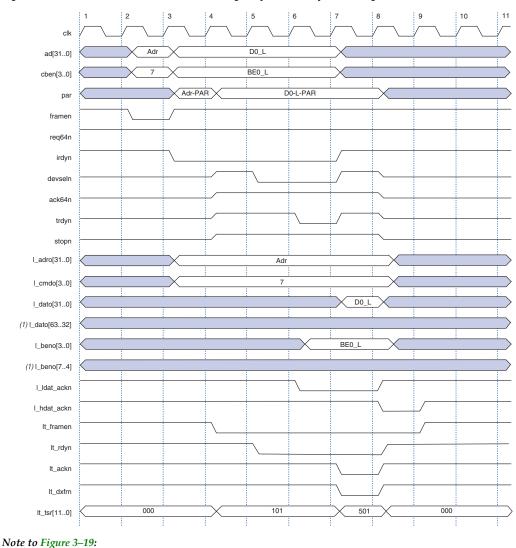

| I/O Read Transactions                                                        | 3–61         |

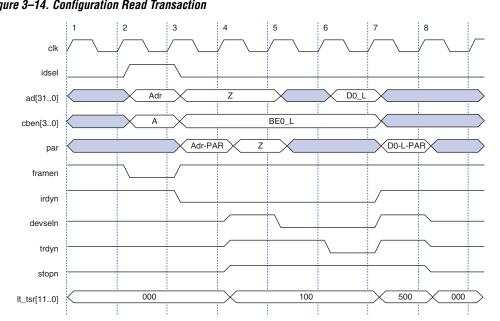

| Configuration Read Transactions                                              |              |

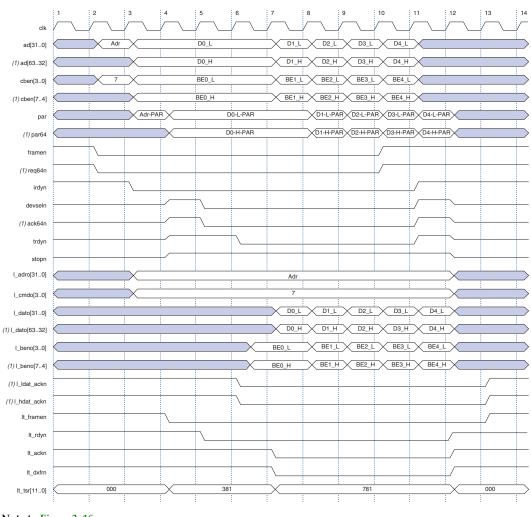

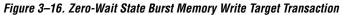

| Target Write Transactions                                                    | 3–63         |

| Memory Write Transactions                                                    | 3–63         |

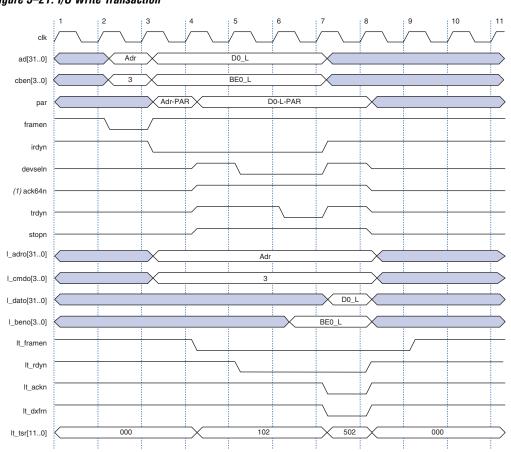

| I/O Write Transactions                                                       |              |

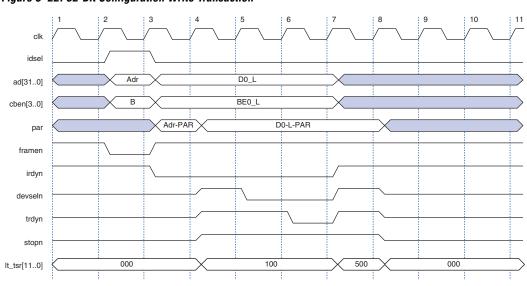

| Configuration Write Transactions                                             |              |

| Target Transaction Terminations                                              | 3–77         |

| Řetry                                                                        | 3–77         |

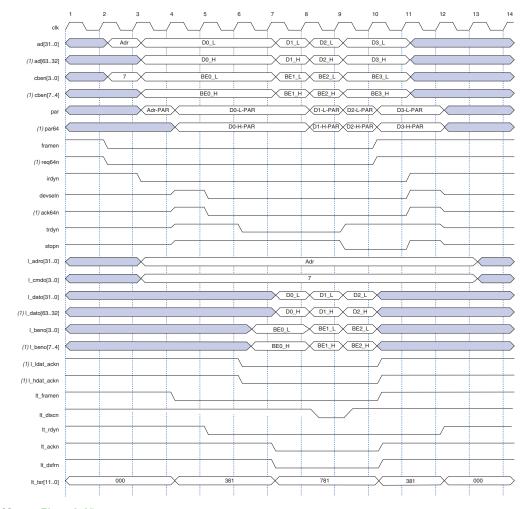

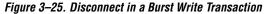

| Disconnect                                                                   | 3–79         |

| Target Abort                                                                 | 3–86         |

| Additional Design Guidelines for Target Transactions                         |              |

| Master Mode Operation                                                        |              |

| PCI Bus Parking                                                              |              |

| Design Consideration                                                         |              |

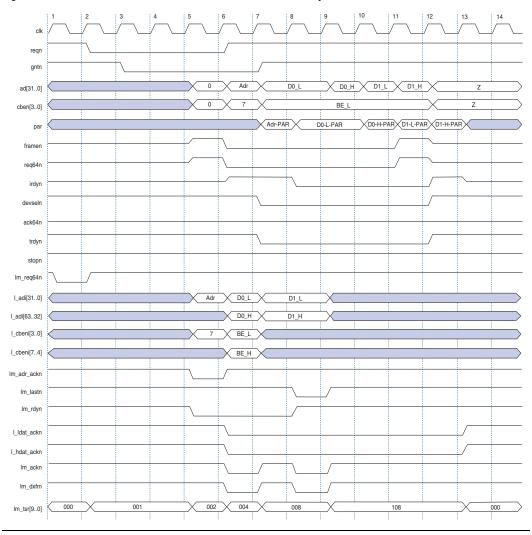

| Master Read Transactions                                                     | 3–93         |

| Memory Read Transactions                                                     |              |

| I/O & Configuration Read Transactions                                        |              |

| Master Write Transactions                                                    |              |

| Memory Write Transactions                                                    |              |

| I/O & Configuration Write Master Transactions                                |              |

| Abnormal Master Transaction Termination                                      |              |

| Latency Timer Expires                                                        |              |

| Retry                                                                        |              |

| Disconnect Without Data                                                      |              |

| Disconnect with Data                                                         |              |

| Target Abort                                                                 |              |

| Master Abort                                                                 |              |

| Host Bridge Operation                                                        |              |

| Using the PCI MegaCore Function as a Host Bridge                             |              |

| PCI Configuration Read Transaction from the pci_mt64 Local Master Device to  | the Internal |

| Configuration Space                                                          |              |

| PCI Configuration Write Transaction from the pci_mt64 Local Master Device to | the Internal |

| Configuration Space                                                          |              |

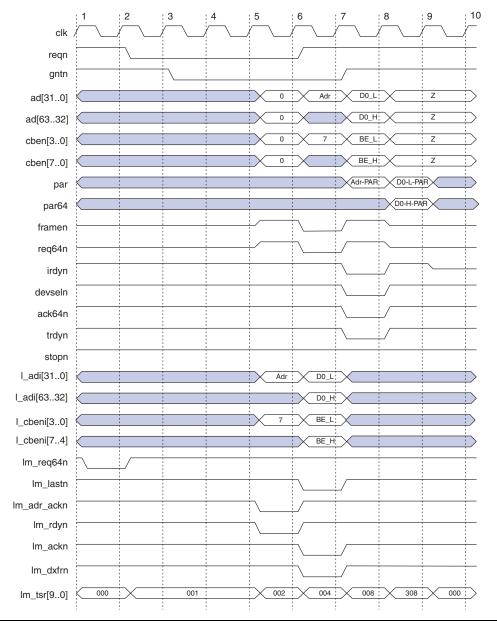

| 64-Bit Addressing, Dual Address Cycle (DAC)                                  |              |

| Target Mode Operation                                                        |              |

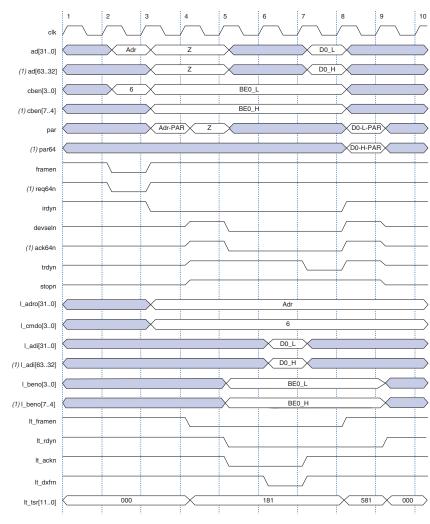

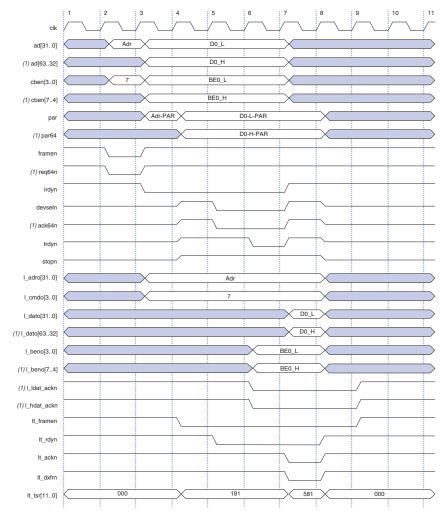

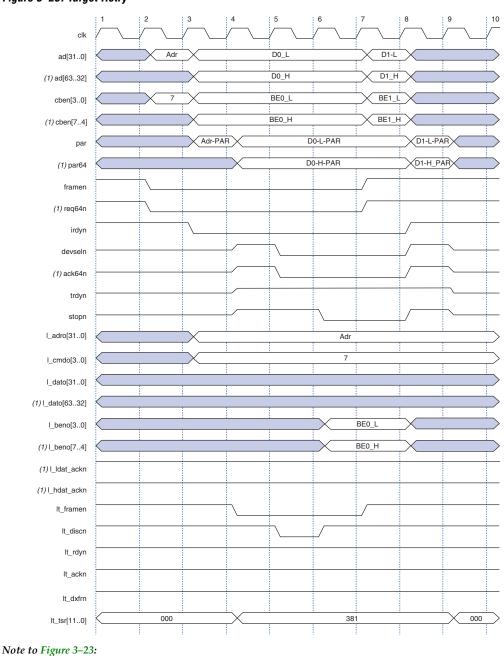

| 64-Bit Address, 64-Bit Data Single-Cycle Target Read Transaction             |              |

| Master Mode Operation                                                        |              |

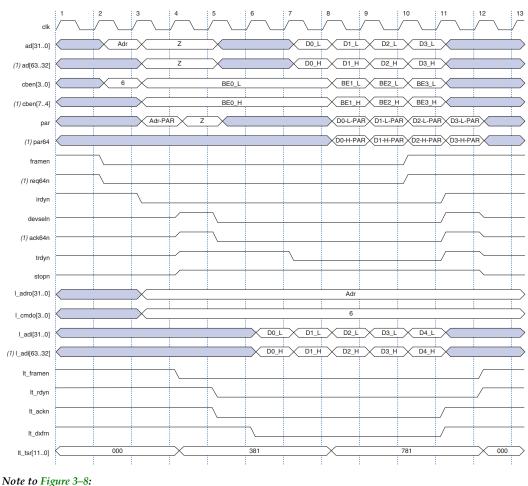

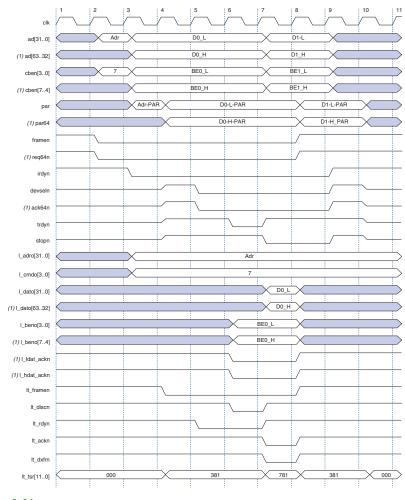

| 64-Bit Address, 64-Bit Data Master Burst Memory Read Transaction             |              |

|                                                                              |              |

### Chapter 4. Testbench

| General Description 4-1 |

|-------------------------|

|-------------------------|

| Features                            |

|-------------------------------------|

| PCI Testbench Files                 |

| Testbench Specifications 4–6        |

| Master Transactor (mstr_tranx) 4–7  |

| PROCEDURES and TASKS Sections 4-7   |

| INITIALIZATION Section 4-8          |

| USER COMMANDS Section 4-8           |

| Target Transactor (trgt_tranx) 4–12 |

| FILE IO section 4-13                |

| PROCEDURES and TASKS sections 4-13  |

| Bus Monitor (monitor) 4-14          |

| Clock Generator (clk_gen) 4-14      |

| Arbiter (arbiter)                   |

| Pull Up (pull_up)                   |

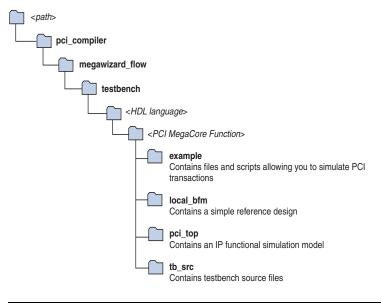

| Local Reference Design 4–15         |

| Local Target                        |

| DMA Engine                          |

| Local Master 4-19                   |

| lm_lastn Generator 4–19             |

| Prefetch                            |

| LPM RAM                             |

| Simulation Flow                     |

# Section II. PCI Compiler With SOPC Builder Flow

### **Chapter 5. Getting Started**

| Design Flow                                             | 5–1  |

|---------------------------------------------------------|------|

| PCI Compiler with SOPC Builder Flow Design Walkthrough  |      |

| Create a New Quartus II Project                         | 5–3  |

| Set Up the PCI-Avalon Bridge                            | 5–5  |

| Add the Remaining Components to the SOPC Builder System | 5–7  |

| Complete the Connections in SOPC Builder                | 5–8  |

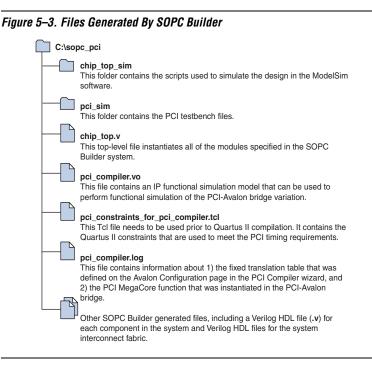

| Generate the SOPC Builder System                        | 5–9  |

| Files Generated by SOPC Builder                         | 5–10 |

| Simulate the Design                                     | 5–11 |

| Compile the Design                                      | 5–13 |

| Program a Device                                        | 5–14 |

| Upgrading Systems from a Previous Version               | 5–15 |

### **Chapter 6. Parameter Settings**

| System Options-2                                     |      |

|------------------------------------------------------|------|

| PCI Bus Speed                                        |      |

| PCI Data Bus Width                                   |      |

| PCI Clock/Reset Settings                             | 6–9  |

| PCI Bus Arbiter                                      |      |

| PCI Configuration                                    |      |

| PCI Base Address Registers                           |      |

| PCI Read-Only Registers                              |      |

| Setting the PCI Base Address Register Values         | 6–11 |

| Manual Setting of the BAR Size & Avalon Base Address |      |

| Avalon Configuration                                 |      |

### **Chapter 7. Functional Description**

| Functional Overview                           | . 7–1  |

|-----------------------------------------------|--------|

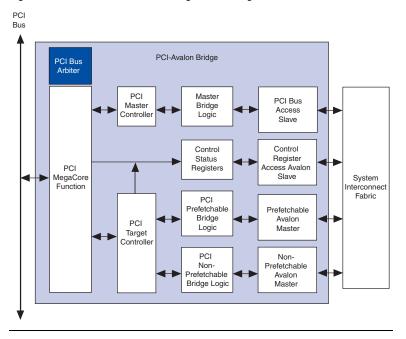

| PCI-Avalon Bridge Blocks                      | . 7–2  |

| Avalon-MM Ports                               |        |

| Control/Status Register Module                | . 7–5  |

| PCI MegaCore Function                         | . 7–5  |

| PCI Bus Arbiter                               | . 7–6  |

| Other PCI-Avalon Bridge Modules               | . 7–6  |

| PCI Operational Modes                         | . 7–6  |

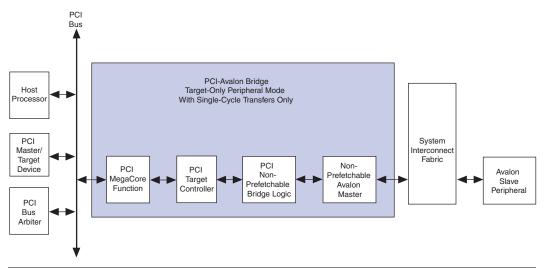

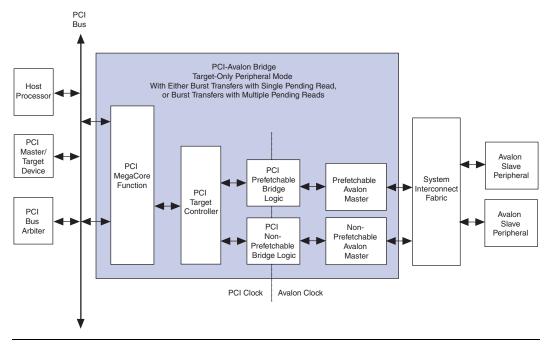

| PCI Target-Only Peripheral Mode Operation     | . 7–6  |

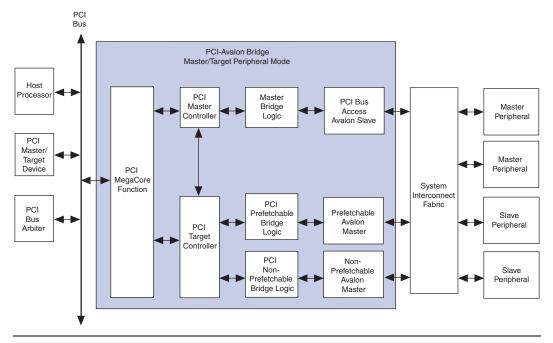

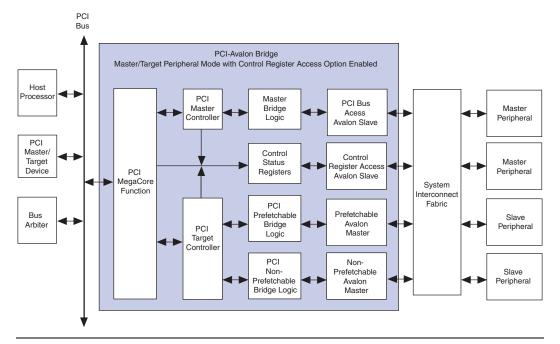

| PCI Master/Target Peripheral Mode Operation   | . 7–8  |

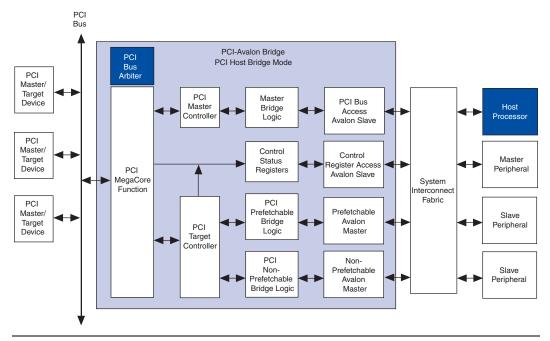

| PCI Host-Bridge Device Mode Operation         |        |

| Performance Profiles                          | 7–11   |

| Target Performance                            | 7–12   |

| Master Performance                            | 7–12   |

| Interface Signals                             | 7–13   |

| PCI Bus Arbiter Signals                       | 7 - 14 |

| PCI Bus Commands                              | 7–15   |

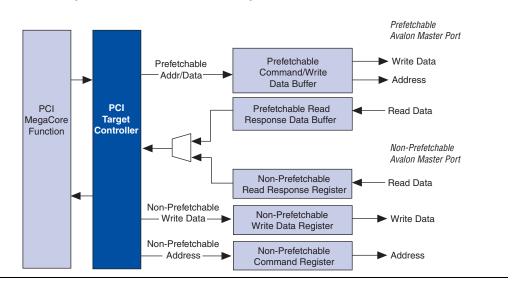

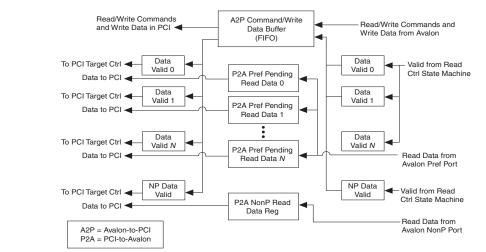

| PCI Target Operation                          | 7 - 15 |

| Non-Prefetchable Operations                   | 7 - 17 |

| Non-Prefetchable Write Operations             | 7 - 18 |

| I/O Write Operations                          | 7–19   |

| Non-Prefetchable Read Operations              | 7–19   |

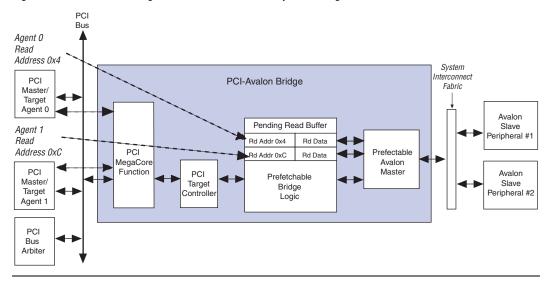

| Prefetchable Operations                       | 7–21   |

| Prefetchable Write Operations                 | 7–22   |

| Prefetchable Read Operations                  |        |

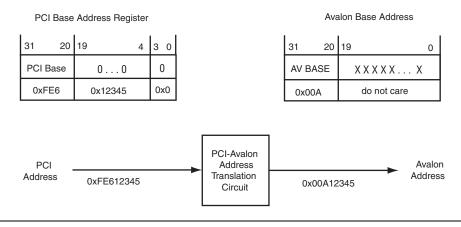

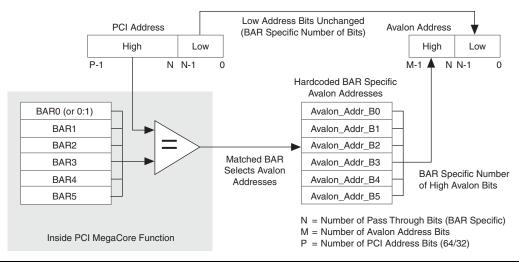

| PCI-to-Avalon Address Translation             | 7–26   |

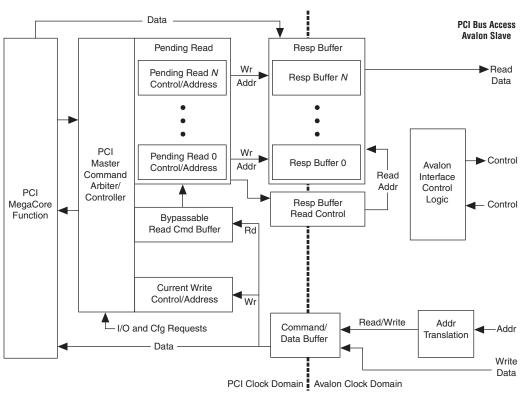

| PCI Master Operation                          |        |

| Avalon-To-PCI Read & Write Operation          | 7–28   |

| Avalon-to-PCI Write Requests                  | 7–31   |

| Avalon-to-PCI Read Requests                   | 7–32   |

| Arbitration Among Pending PCI Master Requests | 7–34   |

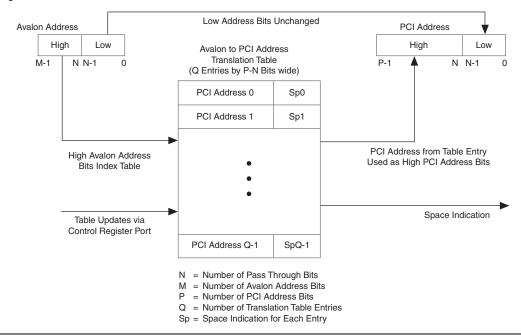

| Avalon-to-PCI Address Translation             | 7–35   |

| Ordering of Requests                          |        |

| Ordering of Avalon-to-PCI Operations          | 7–39   |

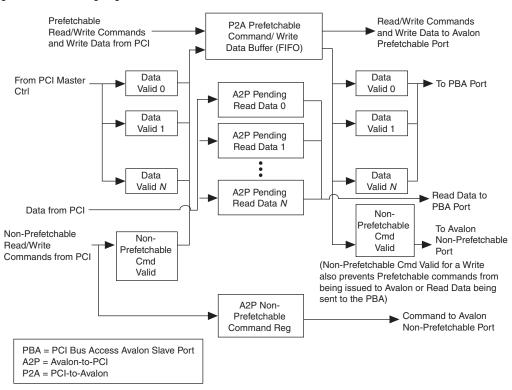

| Ordering PCI-to-Avalon Operations       | 7–42 |

|-----------------------------------------|------|

| PCI Host-Bridge Operation               |      |

| Altera-Provided PCI Bus Arbiter         | 7–45 |

| Interrupts                              | 7–46 |

| Ĝeneration of PCI Interrupts            |      |

| Reception of PCI Interrupts             |      |

| Generation of Avalon-MM Interrupts      | 7–47 |

| Control & Status Registers              |      |

| PCI Interrupt Status Register           | 7–49 |

| PCI Interrupt Enable Register           | 7–51 |

| PCI Mailbox Register Access             | 7–52 |

| Avalon-to-PCI Address Translation Table |      |

| Read-Only Configuration Registers       | 7–54 |

| Avalon-MM Interrupt Status Register     | 7–56 |

| Avalon-MM Interrupt Enable Register     | 7–60 |

| Avalon Mailbox Register Access          | 7–60 |

### **Chapter 8. Testbench**

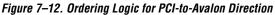

| General Description            | 8–1   |

|--------------------------------|-------|

| Features                       | 8–2   |

| PCI Testbench Files            | 8–3   |

| Testbench Specifications       | . 8–4 |

| Master Transactor (mstr_tranx) | 8–5   |

| PROCEDURES and TASKS Sections  | 8–5   |

| INITIALIZATION Section         | 8–6   |

| USER COMMANDS Section          | 8–7   |

| cfg_rd                         | 8–7   |

| cfg_wr                         | 8-8   |

| mem_wr_32                      |       |

| mem_rd_32                      | . 8–9 |

| mem_wr_64                      | 8–10  |

| mem_rd_64                      |       |

| io_wr                          | 8–11  |

| io_rd                          | 8–11  |

| Target Transactor (trgt_tranx) | 8–12  |

| FILE IO section                | 8–13  |

| PROCEDURES and TASKS sections  | 8–13  |

| Bus Monitor (monitor)          | 8–13  |

| Arbiter (arbiter)              | 8–14  |

| Pull Up (pull_up)              | 8–14  |

| Simulation Flow                | 8–15  |

### Appendix A. Using PCI Constraint File Tcl Scripts

| Introduction                                      | A–1 |

|---------------------------------------------------|-----|

| PCI Constraint Files                              | A–1 |

| Simultaneous Switching Noise (SSN) Considerations | A–2 |

| Additional Options                                |     |

| -speed                                                        | A–3 |

|---------------------------------------------------------------|-----|

| -no_compile                                                   |     |

| -no_pinouts                                                   |     |

| -pin_prefix                                                   |     |

| -pin_suffix                                                   |     |

| -help                                                         |     |

| Upgrading Assignments from a Previous Version of PCI Compiler |     |

| Upgrading PCI Assignments Containing Nondefault PCI Pin Names | A–8 |

### **Additional Information**

| Revision History        | Info-i   |

|-------------------------|----------|

| How to Contact Altera   | Info-ii  |

| Typographic Conventions | Info–iii |

# **About PCI Compiler**

### Introduction

The Altera<sup>®</sup> PCI Compiler provides many options for creating custom, high-performance PCI bus interface designs. Whether your system's top priority is high bandwidth, high speed, or a combination of features, you can use the PCI Compiler to meet your system requirements.

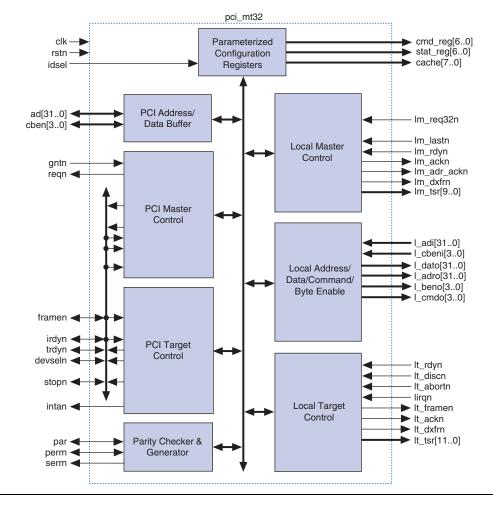

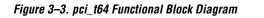

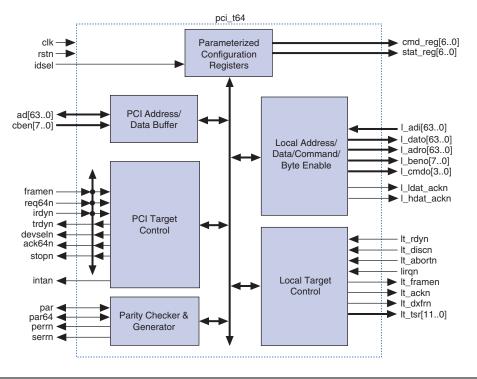

The PCI Compiler contains the pci\_mt64, pci\_mt32, pci\_t64, and pci\_t32 MegaCore<sup>®</sup> functions, a Verilog HDL and VHDL testbench, and reference designs. Altera also offers the following development kits as PCI hardware prototyping platforms:

- PCI High-Speed Development Kit, Stratix Professional Edition

- PCI Development Kit, Cyclone II Edition

These kits include a PCI development board, a reference design, software drivers, and a graphical user interface to help you evaluate the PCI solution in a system.

You can create PCI systems using one of the following design flows in the Quartus® II software.

■ MegaWizard<sup>™</sup> Plug-in Manager flow

This option allows you to choose a specific PCI MegaCore function, specify parameters, generate design files, and manually integrate the parameterized PCI MegaCore function into your overall system.

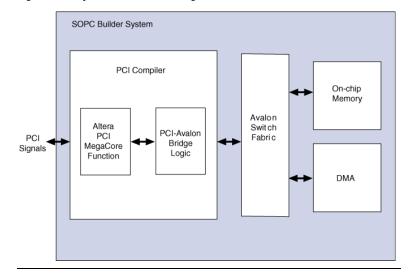

SOPC Builder flow

This option allows you to build a complete PCI system—componentby-component—using an automatically-generated sytem interconnect fabric. The SOPC Builder uses the PCI-Avalon®-Memory-Mapped (Avalon-MM) bridge to connect the PCI bus to the interconnect, allowing you to easily create any system that includes one or more of the Avalon-MM peripherals.

# Release Information

Table 1 provides information about this release of the PCI Compiler.

| Table 1. PCI Compiler User Guide Release Information |                                                                                                                                                             |  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ltem                                                 | Description                                                                                                                                                 |  |

| Version                                              | 11.1                                                                                                                                                        |  |

| Release Date                                         | October 2011                                                                                                                                                |  |

| Ordering Codes                                       | IP-PCI/MT64, IP-PCI/T64,<br>IP-PCI/MT32, IP-PCI/T32                                                                                                         |  |

| Product IDs                                          | <pre>pci_mt64 MegaCore function: 0011,<br/>pci_t64 MegaCore function: 0025,<br/>pci_mt32 MegaCore function: 0022,<br/>pci_t32 MegaCore function: 0024</pre> |  |

| Vendor ID                                            | 6AF7                                                                                                                                                        |  |

# Device Family Support

The MegaCore functions provide either final or preliminary support for target Altera device families:

- Final support means the core is verified with final timing models for this device family. The core meets all functional and timing requirements for the device family and can be used in production designs.

- Preliminary support means the core is verified with preliminary timing models for this device family. The core meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution.

- HardCopy Compilation means the core is verified with final timing models for the HardCopy® device family. The core meets all functional and timing requirements for the device family and can be used in production designs.

- HardCopy Companion means the core is verified with preliminary timing models for the HardCopy companion device. The core meets all functional requirements, but might still be undergoing timing analysis for HardCopy device family. It can be used in production designs with caution.

Table 2 shows the level of support offered by the User Guide MegaCore functions for each Altera device family.

| Table 2. Device Family Support |                                      |  |

|--------------------------------|--------------------------------------|--|

| Device Family                  | Support                              |  |

| Arria®GX                       | Final                                |  |

| Arria II GX                    | Final                                |  |

| Cyclone®                       | Final                                |  |

| Cyclone II                     | Final                                |  |

| Cyclone III                    | Final                                |  |

| Cyclone III LS                 | Final                                |  |

| Cyclone IV (E, GX)             | Final                                |  |

| HardCopy II                    | HardCopy Compilation                 |  |

| HardCopy III                   | Refer to the What's New in Altera IP |  |

| HardCopy IV (E, GX)            | page of the Altera website.          |  |

| MAX®II (1)                     | Final                                |  |

| Stratix®                       | Final                                |  |

| Stratix GX                     | Final                                |  |

| Stratix II                     | Final                                |  |

| Stratix II GX                  | Final                                |  |

| Stratix III                    | Final                                |  |

| Stratix IV (E, GX)             | Final                                |  |

| Other device families          | No support                           |  |

#### Note to Table 2:

(1) MAX II devices are supported by the pci\_mt32 and pci\_t32 MegaCore functions only.

### **Features**

This section summarizes the features of the PCI Compiler.

#### **Common Features**

The following list outlines the common features of the PCI Compiler.

- Fully compliant with the PCI Special Interest Group (PCI SIG) PCI Local Bus Specification, Revision 3.0

- Supports both 32-bit and 64-bit interfaces

- Supports Master/Target and Target-Only modes

- IP functional simulation models enable simulation of a register transfer level (RTL) model of a PCI MegaCore function in VHDL and Verilog HDL simulators

- OpenCore Plus hardware evaluation feature enables testing of a PCI MegaCore function in hardware prior to purchasing a license

- Configuration registers:

- Parameterized registers: device ID, vendor ID, class code, revision ID, BAR0 through BAR5, subsystem ID, subsystemvendor ID, maximum latency, minimum grant, capabilities list pointer, expansion ROM BAR

- Parameterized default or preset base address (available for all six BARs) and expansion ROM base address

- Non-parameterized registers: command, status, header type 0, latency timer, cache line size, interrupt pin, interrupt line

- Host bridge application support

### PCI Compiler with MegaWizard Plug-in Manager Flow

The following list outlines the features of the PCI Compiler with MegaWizard Plug-in Manager flow.

- IP Toolbench wizard-driven interface makes it easy to generate a custom variation of a PCI MegaCore function

- PCI target features:

- Capabilities list pointer support

- Expansion ROM BAR support

- Local-side requests for target abort, retry, or disconnect

- Local-side interrupt requests

- PCI master features (pci\_mt64 and pci\_mt32 only):

- Allows on-chip arbitration logic

- Allows disabling latency timer

- 64-bit PCI features (pci\_mt64 and pci\_t64 only):

- 64-bit addressing support as both master and target

- Initiates 64-bit addressing, using dual-address cycle (DAC)

- Initiates 64-bit memory transactions

- Dynamically negotiates 64-bit transactions and automatically multiplexes data on the local 64-bit data bus

### PCI Compiler with SOPC Builder Flow

The following list outlines the features of the PCI Compiler with SOPC Builder flow.

- SOPC Builder ready

- PCI complexities, such as retry and disconnect are handled by the PCI/Avalon Bridge logic and transparent to the user

- Hard-coded (fixed) or run-time configurable (dynamic) Avalon-to-PCI address translation

- Hard-coded or automatic PCI-to-Avalon address translation

- Separate Avalon Memory-mapped (Avalon-MM) slave ports for PCI bus access (PBA) and control register access (CRA)

- Support for Avalon-MM burst mode

- Option for independent or common PCI and Avalon clock domains

- Option to increase PCI read performance by increasing the number of pending reads and maximum read burst size.

- Internal Arbiter in Host Bridge and Target/Master mode

General Description This section provides a general description of the following:

- PCI MegaCore Functions

- PCI Testbench

- PCI Compiler with MegaWizard Plug-in Manager Flow

- PCI Compiler with SOPC Builder Flow

### **PCI MegaCore Functions**

The PCI MegaCore functions are hardware-tested, high-performance, flexible implementations of PCI interfaces. These functions handle the PCI protocol and timing requirements internally. The back-end interface is designed for easy integration, allowing you to focus your engineering efforts on value-added custom development to significantly reduce timeto-market.

Optimized for Altera devices, the PCI MegaCore functions support configuration, I/O, and memory transactions. The small size of the functions, combined with the high density of Altera's devices, provides ample resources for custom local logic to accompany the PCI interface. The high performance of Altera's devices also enables these functions to support unlimited cycles of zero wait state memory-burst transactions. These functions can operate at either 33- or 66-MHz PCI bus clock speeds, allowing them to achieve up to 132 Megabytes per second (MBytes/s) throughput in a 32-bit 33-MHz PCI bus system and up to 528 MBytes/s throughput in a 64-bit 66-MHz PCI bus system.

In the pci\_mt64 and pci\_mt32 functions, the master and target interfaces can operate independently, allowing maximum throughput and efficient usage of the PCI bus. For instance, while the target interface is accepting zero wait state burst write data, the local logic may simultaneously request PCI bus mastership, thus minimizing latency. To ensure timing and protocol compliance, the PCI MegaCore functions have been rigorously hardware tested. Refer to "Compliance Summary" on page 10 for more information on the hardware tests performed.

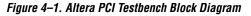

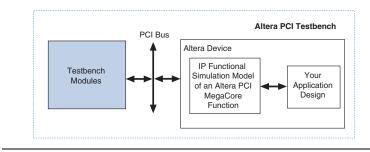

### **PCI** Testbench

The PCI testbench, provided in Verilog HDL and VHDL, facilitates the design and verification of systems that implement any of the PCI MegaCore functions. You can build a PCI behavioral simulation environment by using components of the PCI testbench, the IP functional simulation model of your PCI MegaCore function variation, and the rest of your Verilog HDL or VHDL design.

### PCI Compiler with MegaWizard Plug-in Manager Flow

With this flow, you design to a low-level interface that allows custom PCI transaction design. Because you are designing the logic to interface to the PCI MegaCore function, you have more control of individual module functionality.

This flow is recommended for users who have previously designed with the PCI Compiler or whose highest priority is to minimize design latency.

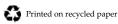

For example, if you are designing a PCI-to-DDR2 SDRAM controller interface you need to do the following:

- Specify the PCI MegaCore function parameters.

- Design the 'back end' user design, including master control logic, target control logic, data path first-in first-out (FIFO) buffers, and direct memory access (DMA) engine.

- Design the DDR2 SDRAM controller interface.

- Specify the DDR2 SDRAM MegaCore function parameters.

- Design internal PCI and DDR2 SDRAM logic blocks.

- Write RTL code that connects the PCI and DDR2 SDRAM blocks.

Figure 1 shows a PCI-to-DDR2 SDRAM controller interface design using the PCI Compiler with MegaWizard Plug-in Manager flow; shaded areas represent user-customized blocks.

For more information about the PCI Compiler with MegaWizard flow, refer to Chapter 1, Getting Started.

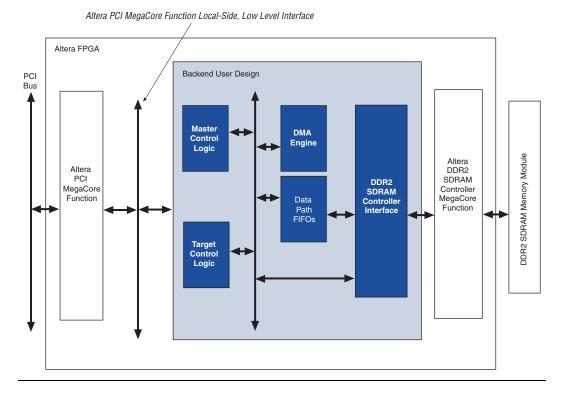

### **PCI Compiler With SOPC Builder Flow**

With this flow, you specify system components and choose system options from a rich set of features, and the SOPC Builder then automatically generates the interconnect logic and simulation environment. Thus, you define and generate a complete system in dramatically less time than manually integrating separate IP blocks.

#### This flow is recommended for users who are new to the PCI Compiler or whose highest priority is to minimize design time.

For example, Figure 2 shows the PCI-to-DDR2 SDRAM design using the PCI Compiler with SOPC Builder flow; the dashed-lines indicate pre-existing components that are added to the design via the SOPC Builder graphical user interface (GUI). When comparing Figure 1 with Figure 2, you can see that the PCI Compiler with SOPC Builder flow option requires far less user customization.

Figure 2. PCI-to-DDR2 SDRAM Design Using the PCI Compiler With SOPC Builder Flow

•••

For more information about the PCI Compiler with SOPC Builder flow, refer to Chapter 5, Getting Started.

For more information about SOPC Builder, refer to volume 4 of the *Quartus II Handbook*.

# Selecting the Appropriate Flow for Your Design

Table 3 summarizes the guidelines for selecting a particular flow over another. In most cases, the PCI Compiler with SOPC Builder flow is the appropriate choice.

| Table 3. PCI Compiler Parameterization Flow Selection Guidelines                |

|---------------------------------------------------------------------------------|

| <i>Table J. F GI GUIIIPITEI F al'allietetization i tow Selection Guidellies</i> |

| SOPC Builder Flow                                                                                                                                                                          | MegaWizard Plug-in Manager Flow                                                                                                                                                               |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <ul> <li>You would like to quickly integrate<br/>multiple system blocks.</li> <li>You are creating a new PCI design.</li> <li>You have limited PCI bus protocol<br/>experience.</li> </ul> | <ul> <li>You are migrating a design that<br/>uses a previous version of PCI<br/>Compiler.</li> <li>You require features that are not<br/>supported with the SOPC Builder<br/>flow.</li> </ul> |  |

### PCI Compiler With SOPC Builder Flow

This section lists the advantages and disadvantages of the PCI Compiler with the SOPC Builder flow.

#### Advantages

- Dramatically faster time-to-market

- Requires minimal PCI bus protocol design expertise

- Very short learning curve

- Access to rich feature set

- Uses simple and flexible GUI to create complete PCI system within hours

- Predesigned 'back end' and 'local side' interconnect

- Uses an automatically-generated simulation environment

- Create custom components and integrate them by using the component wizard

- All components are automatically interconnected

#### Disadvantages

- Does not allow you to customize PCI transaction behavior

- Some applications may have excessive overhead in size and performance

### PCI Compiler With MegaWizard Plug-in Manager Flow

This section lists the advantages and disadvantages of the PCI Compiler with MegaWizard Plug-in Manager flow.

#### Advantages

- More control of the system feature set

- Can design directly from the PCI interface to peripheral devices

- Can access local-side interface to reduce clock cycles and achieve higher bandwidth

#### Disadvantages

- Requires manual integration of system modules

- Cannot easily use existing SOPC Builder peripherals

- Requires a register transfer level (RTL) file for each instantiation

- Requires significant knowledge of the PCI bus protocol

# Compliance Summary

The MegaCore functions are compliant with the requirements specified in the *PCI SIG PCI Local Bus Specification, Revision 3.0* and *Compliance Checklist, Revision 3.0*.

To ensure PCI compliance, Altera has performed extensive validation of the PCI MegaCore functions. Validation includes both simulation and hardware testing. The following simulations are covered by the validation suite for the PCI MegaCore functions:

- PCI-SIG checklist simulations

- Applicable operating rules in Appendix C of the *PCI Local Bus Specification, Revision 3.0,* including:

- Basic protocol

- Signal stability

- Master and target signals

- Data phases

- Arbitration

- Latency

- Device selection

- Parity

- Local-side interface functionality

- Corner cases of the PCI and local-side interface, such as random wait state insertion

In addition to simulation, Altera performed extensive hardware testing on the functions to ensure robustness and PCI compliance. The test platforms include the Agilent E2928A PCI Bus Exerciser and Analyzer, an Altera PCI development board with a device configured with a PCI MegaCore function and a reference design, and PCI bus agents such as a host bridge, Ethernet network adapter, and video card. The Altera PCI MegaCore functions were tested on the Stratix EP1S25F1020C5 and EP1S60F1020C6 devices. Hardware testing ensures that the PCI MegaCore functions operate flawlessly under the most stringent conditions.

During hardware testing with the Agilent E2928A PCI Bus Exerciser and Analyzer, various tests were performed to guarantee robustness and strict compliance. These tests included the following:

- Memory read/write

- I/O read/write

- Configuration read/write

The tests generate random transaction types and parameters at the PCI and local sides. The Agilent E2928A PCI Bus Exerciser and Analyzer simulated random behavior on the PCI bus by randomizing transactions with variable parameters such as the following:

- Bus commands

- Burst length

- Data types

- Wait states

- Terminations

- Error conditions

The local side also emulated a variety of test conditions in which the PCI MegaCore functions experienced random wait states and terminations. During the tests, the Agilent E2928A PCI Bus Exerciser and Analyzer also acted as a PCI protocol and data integrity checker as well as a logic analyzer to aid in debugging. This testing ensures that the functions operate under the most stringent conditions in your system.

For more information on the Agilent E2928A PCI Bus Exerciser and Analyzer, refer to the Agilent website at www.agilent.com.

# Performance and Resource Utilization

This section lists the speed and approximate resource utilization of the PCI MegaCore functions in supported Altera device families.

### PCI Compiler with MegaWizard Plug-in Manager Flow

The speed and resource utilization estimates are based on a PCI MegaCore function using one BAR that reserves 1 MByte of memory. Implementing additional BARs generates additional logic in the PCI MegaCore function. Using different parameter options may result in additional logic generated within the function. Results were generated using the Quartus II software version 11.1.

Table 4 shows PCI MegaCore function resource utilization and performance data for Stratix II devices.

| Table 4. PCI MegaCore Function Performance in Stratix II Devices (1) |                            |          |                        |

|----------------------------------------------------------------------|----------------------------|----------|------------------------|

| PCI Function                                                         | Utilization<br>(ALUTs) (2) | I/O Pins | f <sub>MAX</sub> (MHz) |

| pci_mt64                                                             | 1,083                      | 89       | > 67                   |

| pci_t64                                                              | 714                        | 87       | > 67                   |

| pci_mt32                                                             | 754                        | 50       | > 67                   |

| pci_t32                                                              | 448                        | 48       | > 67                   |

#### Notes to Table 4:

- This data was obtained by compiling each of the PCI MegaCore functions (parameterized to use one BAR that reserves 1 MByte of memory) in the Stratix II EP2S60F1020C5 device.

- (2) The Utilization for Stratix II devices is based on the number of adaptive look-up tables (ALUTs) used for the design as reported by the Quartus II software.

Table 5 shows PCI MegaCore function resource utilization and performance for Stratix, Stratix GX, and Cyclone devices.

| Table 5. PCI MegaCore Function Performance in Stratix, Stratix GX &Cyclone Devices(1) |                         |          |                        |

|---------------------------------------------------------------------------------------|-------------------------|----------|------------------------|

| PCI Function                                                                          | Logic Elements<br>(LEs) | I/O Pins | f <sub>MAX</sub> (MHz) |

| pci_mt64                                                                              | 1,378                   | 89       | > 67                   |

| pci_t64                                                                               | 966                     | 87       | > 67                   |

| pci_mt32                                                                              | 1007                    | 50       | > 67                   |

| pci_t32                                                                               | 661                     | 48       | > 67                   |

#### Note to Table 5:

(1) The PCI MegaCore functions use approximately the same number of LEs for the Stratix, Stratix GX, and Cyclone device families. This data was obtained by compiling each of the PCI MegaCore functions (parameterized to use one BAR that reserves 1 MByte of memory) in the Stratix EP1S60F1020C6 device. Table 6 shows PCI MegaCore function resource utilization and performance data for Cyclone II devices.

| Table 6. PCI MegaCore Function Performance in Cyclone II Devices $(1)$ |                         |          |                        |

|------------------------------------------------------------------------|-------------------------|----------|------------------------|

| PCI Function                                                           | Logic Elements<br>(LEs) | I/O Pins | f <sub>MAX</sub> (MHz) |

| pci_mt64                                                               | 1,219                   | 89       | > 67                   |

| pci_t64                                                                | 778                     | 87       | > 67                   |

| pci_mt32                                                               | 847                     | 50       | > 67                   |

| pci_t32                                                                | 504                     | 48       | > 67                   |

#### Note to Table 6:

This data was obtained by compiling each of the PCI MegaCore functions (parameterized to use one BAR that reserves 1 MByte of memory) in the Cyclone II EP2C35F672C7 device.

Table 7 shows PCI MegaCore function resource utilization and performance for MAX II devices.

| Table 7. PCI MegaCore Function Performance in MAX II Devices (1), (2) |                         |          |                        |  |  |  |  |

|-----------------------------------------------------------------------|-------------------------|----------|------------------------|--|--|--|--|

| PCI Function                                                          | Logic Elements<br>(LEs) | I/O Pins | f <sub>MAX</sub> (MHz) |  |  |  |  |

| pci_mt32                                                              | 789                     | 50       | > 67                   |  |  |  |  |

| pci_t32                                                               | 455                     | 48       | > 67                   |  |  |  |  |

#### Notes to Table 7:

- This data was obtained by compiling each of the PCI MegaCore functions (parameterized to use one BAR that reserves 1 MByte of memory) in the MAX II EPM2210F324C3 device.

- (2) pci\_mt64 and pci\_t64 MegaCore functions are not supported in MAX II devices.

### PCI Compiler with SOPC Builder Flow

The speed and resource utilization estimates are for the supported devices when operating in the PCI Target-Only, PCI Master/Target, and PCI Host-Bridge device modes for each of the application-specific performance settings.

Performance results will vary depending on the user-specified parameters that are built into the system module.

Table 8 lists memory utilization and performance data for Stratix II devices.

| Table 8. Memory Utilization & Performance Data for Stratix II Devices (4) |                                |               |                         |                                |             |                         |                                |             |                           |

|---------------------------------------------------------------------------|--------------------------------|---------------|-------------------------|--------------------------------|-------------|-------------------------|--------------------------------|-------------|---------------------------|

| PCI<br>Device<br>Mode                                                     | Performance Setting<br>as: (1) |               | 32-Bit PCI Interface    |                                |             | 64-Bit I                | PCI                            |             |                           |

|                                                                           | PCI Target                     | PCI<br>Master | Utilization<br>ALUTs(2) | M4K<br>Memory<br>Blocks<br>(3) | l/O<br>Pins | Utilization<br>ALUTs(2) | M4K<br>Memory<br>Blocks<br>(3) | I/O<br>Pins | f <sub>MAX</sub><br>(MHz) |

| PCI                                                                       | Min                            | N/A           | 543                     | 0                              | 48          | 767                     | 0                              | 87          | >67                       |

| Target-<br>Only                                                           | Typical                        | N/A           | 886                     | 4                              | 48          | 1,165                   | 6                              | 87          | >67                       |

| Only                                                                      | Max                            | N/A           | 1,240                   | 4                              | 48          | 1,556                   | 68                             | 87          | >67                       |

| PCI                                                                       | Min                            | Typical       | 1,726                   | 6                              | 50          | 2,393                   | 9                              | 89          | >67                       |

| Master/<br>Target                                                         | Typical                        | Typical       | 1,953                   | 8                              | 50          | 2,729                   | 123                            | 89          | >67                       |

| larger                                                                    | Max                            | Typical       | 2,321                   | 8                              | 50          | 3,114                   | 12                             | 89          | >67                       |

|                                                                           | Min                            | Max           | 2,532                   | 9                              | 50          | 3,665                   | 15                             | 89          | >67                       |

|                                                                           | Typical                        | Max           | 2,753                   | 11                             | 50          | 3,989                   | 18                             | 89          | >67                       |

|                                                                           | Max                            | Max           | 3,149                   | 11                             | 50          | 4,350                   | 18                             | 89          | >67                       |

Notes to Table 8:

- Min = Single-cycle transactions

Typical = Burst transactions with a single pending read

Max = Burst transactions with multiple pending reads

- (2) The LE count for Stratix II devices is based on the number of adaptive look-up tables (ALUTs) used for the design as reported by the Quartus II software.

- (3) In some compilations one M512 block was used, but it is not counted.

- (4) The data was obtained by performing compilations on a Stratix II EP2S60F1020C5 device. Each of the device types was parameterized to use one BAR that reserved 1 MByte of memory on the Avalon-MM side. For the PCI Master/Target Peripheral mode, one MByte of memory was reserved on the PCI side.

Table 9 lists memory utilization and performance data for Cyclone II devices.

| Table 9. N             | lemory Utilizati            | on & Performa | nce Data fo                | r Cyclone               | II Devi     | ces (2)                    |                         |             |                           |

|------------------------|-----------------------------|---------------|----------------------------|-------------------------|-------------|----------------------------|-------------------------|-------------|---------------------------|

| PCI                    | Performance Setting as: (1) |               | 32-Bit PCI Interface       |                         |             | 64-Bit PCI Interface       |                         |             | PCI                       |

| Device<br>Mode         | PCI Target                  | PCI Master    | Logic<br>Elements<br>(LEs) | M4K<br>Memory<br>Blocks | I/O<br>Pins | Logic<br>Elements<br>(LEs) | M4K<br>Memory<br>Blocks | I/O<br>Pins | f <sub>MAX</sub><br>(MHz) |

| PCI<br>Target-<br>Only | Min                         | N/A           | 547                        | 0                       | 48          | 1,114                      | 0                       | 87          | >67                       |

|                        | Typical                     | N/A           | 1,113                      | 4                       | 48          | 1,565                      | 6                       | 87          | >67                       |

| Olliy                  | Max                         | N/A           | 1,605                      | 4                       | 48          | 2,051                      | 6                       | 87          | >67                       |

| PCI                    | Min                         | Typical       | 2,117                      | 7                       | 50          | 3,075                      | 9                       | 89          | >67                       |

| Master/<br>Target      | Typical                     | Typical       | 2,319                      | 9                       | 50          | 3,391                      | 13                      | 89          | >67                       |

| larger                 | Max                         | Typical       | 2,806                      | 9                       | 50          | 3,915                      | 13                      | 89          | >67                       |

|                        | Min                         | Max           | 3,096                      | 7                       | 50          | 4,655                      | 9                       | 89          | >67                       |

|                        | Typical                     | Max           | 3,328                      | 9                       | 50          | 4,939                      | 13                      | 89          | >67                       |

|                        | Max                         | Max           | 3,806                      | 9                       | 50          | 5,454                      | 13                      | 89          | >67                       |

Notes to Table 9:

(1) **Min** = Single-cycle transactions

**Typical** = Burst transactions with a single pending read

Max = Burst transactions with multiple pending reads

(2) The data was obtained by performing compilations on a Cyclone II EP2C35F672C7 device. Each of the device types was parameterized to use one BAR that reserved 1 MByte of memory on the Avalon-MM side. For the PCI Master/Target Peripheral mode, one MByte of memory was reserved on the PCI side.

Table 10 lists memory utilization and performance data for Stratix, Stratix GX, and Cyclone devices.

|                       | Performance | Setting as: (1) | 32-Bit                     | PCI Interfa                     | ice         | 64-Bit                     | PCI Interfa                     | PCI Interface |                                  |

|-----------------------|-------------|-----------------|----------------------------|---------------------------------|-------------|----------------------------|---------------------------------|---------------|----------------------------------|

| PCI<br>Device<br>Mode | PCI Target  | PCI Master      | Logic<br>Elements<br>(LEs) | M512<br>Memory<br>Blocks<br>(2) | I/O<br>Pins | Logic<br>Elements<br>(LEs) | M512<br>Memory<br>Blocks<br>(2) | I/O<br>Pins   | PCI<br>f <sub>MAX</sub><br>(MHz) |

| PCI                   | Min         | N/A             | 852                        | 0                               | 48          | 1,186                      | 0                               | 87            | >67                              |

| Target-<br>Only       | Typical     | N/A             | 1,460                      | 4                               | 48          | 1,949                      | 6                               | 87            | >67                              |

|                       | Мах         | N/A             | 1,940                      | 4                               | 48          | 2,442                      | 6                               | 87            | >67                              |

le 10. Memory Utilization & Performance Data for Stratix, Stratix GX & Cyclone Devices (3) (Pa

Table 10. Memory Utilization & Performance Data for Stratix, Stratix GX & Cyclone Devices (3) (Part 2 of 2)

|                          | Performance Setting as: (1) |            | 32-Bit PCI Interface       |                                 |             | 64-Bit PCI Interface       |                                 |             |                                  |

|--------------------------|-----------------------------|------------|----------------------------|---------------------------------|-------------|----------------------------|---------------------------------|-------------|----------------------------------|

| PCI<br>Device<br>Mode    | PCI Target                  | PCI Master | Logic<br>Elements<br>(LEs) | M512<br>Memory<br>Blocks<br>(2) | I/O<br>Pins | Logic<br>Elements<br>(LEs) | M512<br>Memory<br>Blocks<br>(2) | I/O<br>Pins | PCI<br>f <sub>max</sub><br>(MHz) |

| PCI<br>Master/<br>Target | Min                         | Typical    | 2,715                      | 7                               | 50          | 3,668                      | 10                              | 89          | >67                              |

|                          | Typical                     | Typical    | 3,053                      | 9                               | 50          | 4,187                      | 14                              | 89          | >67                              |

|                          | Max                         | Typical    | 3,540                      | 9                               | 50          | 4,682                      | 14                              | 89          | >67                              |

|                          | Min                         | Max        | 3,728                      | 10                              | 50          | 5,138                      | 16                              | 89          | >67                              |

|                          | Typical                     | Max        | 4,059                      | 12                              | 50          | 5,634                      | 20                              | 89          | >67                              |

|                          | Max                         | Max        | 4,788                      | 14                              | 50          | 6,696                      | 22                              | 89          | >67                              |

#### Notes to Table 10:

- Min = Single-cycle transactions

Typical = Burst transactions with a single pending read

Max = Burst transactions with multiple pending reads

- (2) In Cyclone devices, memory is implemented in M4K blocks, not M512 blocks.

- (3) The data was obtained by performing compilations on a Cyclone EP1C20F400C7 device. Each of the device types was parameterized to use one BAR that reserved 1 MByte of memory on the Avalon-MM side. For the PCI Master/Target Peripheral mode, one MByte of memory was reserved on the PCI side.

Table 11 lists memory utilization and performance data for MAX II devices.

MAX II devices only support the PCI Target-Only peripheral and the single-cycle performance setting.

| Table 11. M        | emory Utilization | n & Performance L | Data for MAX II            | Devices (2)      |          |                               |  |

|--------------------|-------------------|-------------------|----------------------------|------------------|----------|-------------------------------|--|

| PCI                | Performance       | Setting as: (1)   | 32                         | ce               |          |                               |  |

| Device<br>Mode     | PCI Target        | PCI Master        | Logic<br>Elements<br>(LEs) | Memory<br>Blocks | I/O Pins | PCI f <sub>MAX</sub><br>(MHz) |  |

| PCI<br>Target-Only | Min               | N/A               | 770                        | 0                | 48       | >67                           |  |

Notes to Table 11:

(1) **Min** = Single-cycle transactions

(2) The data was obtained by performing compilations on a MAX II EPM2210F324C3 device. The device type was parameterized to use one BAR that reserved 1 MByte of memory on the Avalon-MM side.

## Installation and Licensing

••••

The User Guide is part of the MegaCore IP Library, which is distributed with the Quartus II software and downloadable from the Altera website, www.altera.com.

For system requirements and installation instructions, refer to *Altera Software Installation and Licensing*.

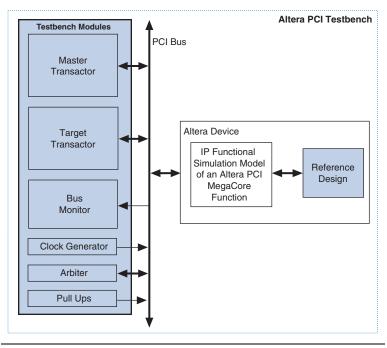

Figure 3 shows the directory structure after you install the PCI Compiler User Guide, where *<path>* is the installation directory. The default installation directory on Windows is **c:\altera**\*<version>*; on Linux it is **/opt/altera***<version>*.

### Figure 3. Directory Structure

| <pre> <path>     Installation directory.</path></pre>                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ip                                                                                                                                                                                                     |

| Contains the Altera MegaCore IP Library and third-party IP cores.                                                                                                                                      |

| Contains the Altera MegaCore IP Library.                                                                                                                                                               |

| Contains shared components.                                                                                                                                                                            |

| ip_toolbench<br>Contains common IP Toolbench files.                                                                                                                                                    |

| Contains the PCI Compiler files.                                                                                                                                                                       |

| const_files<br>Contains constraint files that include all necessary assignments to meet your PCI timing requirements for<br>all supported Altera device families and development kits.                 |

| lib         Contains encrypted lower-level design files and other support files.           On Linux systems, you must add this directory as a user library in the Quartus II software.                 |

| ip_toolbench<br>Contains the necessary files for the parameterization wizard.                                                                                                                          |

| Sopc_builder<br>Contains the necessary files for the SOPC Builder GUI. For Linux, this directory must be<br>added to the Component/Kit Library search path by choosing SOPC Builder Setup (File menu). |

| inc<br>Contains a header file that can be used in PCI Compiler with SOPC Builder flow. The header<br>file contains macros to access control and status registers inside the PCI-Avalon bridge.         |

| megawizard_flow<br>Contains the files that are specific for PCI Compiler with MegaWizard flow.                                                                                                         |

| examples<br>Contains example Quartus II projects and simulation waveforms for each of the PCI MegaCore functions.                                                                                      |

| ref_designs<br>Contains reference designs for common functions implemented with the PCI MegaCore functions.                                                                                            |

| testbench<br>Contains Verilog HDL and VHDL testbenches for simulating designs.                                                                                                                         |

| sopc_flow<br>Contains the files that are specific for PCI Compiler with SOPC Builder.                                                                                                                  |

| example<br>Contains example Quartus II projects using SOPC Builder.                                                                                                                                    |

| testbench<br>Contains the Verilog HDL and VHDL testbenches for simulating designs that include the PCI-Avalon bridge.                                                                                  |

### **OpenCore Plus Evaluation**

With Altera's free OpenCore Plus evaluation feature, you can perform the following actions:

- Simulate the behavior of a megafunction (Altera MegaCore function or AMPP<sup>SM</sup> megafunction) within your system.

- Verify the functionality of your design, as well as evaluate its size and speed quickly and easily.

- Generate time-limited device programming files for designs that include megafunctions.

- Program a device and verify your design in hardware.

You only need to purchase a license for the megafunction when you are completely satisfied with its functionality and performance, and want to take your design to production.

After you purchase a license for PCI Compiler MegaCore function, you can request a license file from the Altera website at www.altera.com/licensing and install it on your computer. When you request a license file, Altera emails you a **license.dat** file. If you do not have Internet access, contact your local Altera representative.

For more information on OpenCore Plus hardware evaluation, refer to *AN 320: OpenCore Plus Evaluation of Megafunctions*.

### **OpenCore Plus Time-Out Behavior**

OpenCore Plus hardware evaluation supports the following two operation modes:

- *Untethered*—the design runs for a limited time.

- Tethered—requires a connection between your board and the host computer. If tethered mode is supported by all megafunctions in a design, the device can operate for a longer time or indefinitely.

All megafunctions in a device time out simultaneously when the most restrictive evaluation time is reached. If there is more than one megafunction in a design, a specific megafunction's time-out behavior may be masked by the time-out behavior of the other megafunctions.

For MegaCore functions, the untethered time-out is 1 hour; the tethered time-out value is indefinite.

Your design stops working after the hardware evaluation time expires.

# Section I. PCI Compiler With MegaWizard Plug-In Manager Flow

The Altera PCI Compiler provides a complete solution for implementing a conventional PCI interface using Altera devices. It contains the Altera pci\_mt64, pci\_mt32, pci\_t64, and pci\_t32 MegaCore functions, a Verilog HDL and VHDL testbench, and reference designs.

This section includes the following chapters:

- Chapter 1, Getting Started

- Chapter 2, Parameter Settings

- Chapter 3, Functional Description

- Chapter 4, Testbench

# 1. Getting Started

## **Design Flow**

To evaluate a PCI Compiler MegaCore function using the OpenCore Plus feature include these steps in your design flow:

- 1. Obtain and install the PCI Compiler.

- 2. Create a custom variation of a PCI MegaCore function using IP Toolbench.

- IP Toolbench is a toolbar from which you can quickly and easily view documentation, choose a PCI MegaCore function, specify parameters, and generate all of the files necessary for integrating the parameterized PCI MegaCore function into your design.

- 3. Implement the rest of your system using the design entry method of your choice.

- 4. Use the IP Toolbench-generated IP functional simulation model to verify the operation of your design.

- For more information on IP functional simulation models, refer to the *Simulating Altera in Third-Party Simulation Tools* chapter in volume 3 of the *Quartus II Handbook*.

- 5. Use an Altera-provided PCI constraint file to meet the timing requirements of the PCI specification.

- For more information on obtaining and using Altera-provided PCI constraint files in your design, refer to Appendix A, Using PCI Constraint File Tcl Scripts.

- 6. Use the Quartus II software to compile your design and perform static timing analysis.

- You can generate an OpenCore Plus time-limited programming file, which you can use to verify the operation of your design in hardware.

- 7. Purchase a license for the PCI Compiler.

After you have purchased a license for the PCI Compiler, the design flow involves the following additional steps:

- 1. Set up licensing.

- 2. Generate a programming file for the Altera device(s) on your board.

- 3. Program the Altera device(s) with the completed design.

- 4. Perform design verification.

## PCI MegaCore Function Design Walkthrough

This walkthrough explains how to create a custom variation of a PCI MegaCore function using the Altera PCI IP Toolbench and the Quartus II software. When you finish generating a custom variation of the PCI MegaCore function, you can incorporate it into your overall project.

This walkthrough explains how to create a custom variation of the pci\_mt64 MegaCore function in Verilog HDL. You can also use these procedures for the pci\_mt32, pci\_t32 and pci\_t64 MegaCore functions, and substitute VHDL for Verilog HDL.

Altera recommends that you use the pci\_mt32 MegaCore function for 32-bit applications. The pci\_mt64 MegaCore function has additional logic and I/O pins which are wasted if used in a 32-bit mode applications.

You can interface the pci\_mt64 MegaCore function with 32-bit agents on the bus. To operate in 32-bit mode only, connect an input pin to the l\_dis\_64\_extn signal. This signal disables the 64-bit extension signals if driven low.

This walkthrough consists of these steps:

- Create a New Quartus II Project

- Launch IP Toolbench

- Step 1: Parameterize

- Step 2: Set Up Simulation

- Step 3: Generate

### **Create a New Quartus II Project**

You need to create a new Quartus II project with the **New Project Wizard**, which specifies the working directory for the project, assigns the project name, and designates the name of the top-level design entity.

To create a new project, follow these steps:

- Choose Programs > Altera > Quartus II < version> (Windows Start menu) to run the Quartus II software. You can also use the Quartus II Web Edition software.

- 2. Choose New Project Wizard (File menu).

- 3. Click **Next** in the **New Project Wizard: Introduction** (the introduction does not display if you turned it off previously).

- 4. In the **New Project Wizard: Directory, Name, Top-Level Entity** page, enter the following information:

- a. Specify the working directory for your project. This walkthrough uses the directory:

#### c:\altera\projects

- b. Specify the name of the project. This walkthrough uses **pci\_project** for the project name.

- The Quartus II software automatically specifies a top-level design entity that has the same name as the project. Do not change it.

- 5. Click **Next** to close this page and display the **New Project Wizard: Add Files** page.

- When you specify a directory that does not already exist, a message asks if the specified directory should be created. Click **Yes** to create the directory.

- 6. If you installed the MegaCore IP library in a different directory from where you installed the Quartus II software, add user libraries by following these steps on the **New Project Wizard: Add Files** page:

- a. Click **User Libraries**.

- b. Type <path>\pci\_compiler\lib\ into the Library name box, where <path> is the directory in which you installed the PCI Compiler.

- c. Click Add to add the path to the Quartus II project.

- d. Click **OK** to save the library path in the project.

- 7. Click **Next** to close this page and display the **New Project Wizard: Family & Device Settings** page.

- 8. On the New Project Wizard: Family & Device Settings page, choose the following:

- In the **Family** list, choose **Stratix** as the target device family.

- Under Target device, select a Specific device selected in the 'Available devices' list.

- Under Show in 'Available device' list, in the Speed Grade list, choose Any.

- In the **Available Devices** list, select **EP1S60F1020C5**.

- These procedures create a design targeting the Stratix device family. You can also use these procedures for other supported device families. MAX II devices are supported by the pci\_mt32 and pci\_t32 MegaCore functions only.

- 9. The remaining pages in the **New Project Wizard** are optional. Click **Finish** to complete the Quartus II project.

You have finished creating your new Quartus II project.

### Launch IP Toolbench

To launch IP Toolbench in the Quartus II software, follow these steps:

- 1. Start the MegaWizard Plug-In Manager by choosing **MegaWizard Plug-In Manager** (Tools menu). The **MegaWizard Plug-In Manager** dialog box is displayed.

- For more information on MegaWizard Plug-in Manager, refer to Quartus II Help.

- 2. Specify that you want to create a new custom megafunction variation and click **Next**.

- 3. Under **Installed Plug-Ins**, expand the **Interfaces**>**PCI** folder, and click on **PCI** to select the **PCI Compiler v10.1**.

- 4. Select the output file type for your design; the wizard supports VHDL and Verilog HDL. For this walkthrough, choose **Verilog HDL**.

- 5. The MegaWizard Plug-In Manager shows the project path that you specified in the New Project Wizard. Append a variation name for the MegaCore function output files using the format *<project path>*\*<variation name>*. For this walkthrough, specify c:\altera\projects for the directory name, and pci\_project.v for the output file variation name.

- 6. Click **Next** to launch IP Toolbench for the PCI Compiler.

### Step 1: Parameterize

To parameterize your MegaCore function, follow these steps:

- 1. Click **Step 1: Parameterize** in IP Toolbench to open the **Parameterize PCI Compiler** dialog box.

- For more information on the parameters you set during this walkthrough, refer to Chapter 2, Parameter Settings.

- 2. On the **PCI MegaCore Function Settings** page, select the following options:

- a. Under **Technology**, select **PCI**.

- b. Under Application Speed, turn on PCI 66-MHz Capable.

- c. Select the desired PCI MegaCore function in the PCI MegaCore section. For this walkthrough select 64-Bit Master/Target (pci\_mt64).

- 3. Click **Next** to open the **Read-Only PCI Configuration Registers** page. You can modify the values of the read-only PCI configuration registers on this page. For this walkthrough, use the default settings.

4. Click **Next** to open the **Base Address Registers (BARs)** page. This page allows you to configure the PCI base address registers (BARs) that define the address ranges of Memory and I/O write and read requests that your application will claim for the PCI interface.

For this walkthrough, specify these settings:

- a. Ensure that **Implement Only 32 Bit BARs** is selected under **32/64 Bit BARs**.

- b. Click **BAR0 = 1 MBytes (Memory)**.

- c. A window showing default settings for BAR0 displays. For this walkthrough, use the default sliding pointer setting so that **BAR0** reserves 1 MByte (0xFFF00000) of memory.

- d. Click OK.

- e. Click BAR1.

- f. A window showing the default settings for BAR1 displays. Turn on **Enable**.

- g. Select I/O for the type of memory reserved.

- h. Move the sliding pointer so that BAR1 reserves 64 Bytes (0xFFFFFC1) of I/O memory.

- i. Click OK.

- j. Select BAR2 Unused: Click to Configure.

- k. A window showing default settings of BAR2 displays. Turn on **Enable**.

- 1. Move the sliding pointer so that BAR2 reserves 1 MByte (0xFFF00000) of memory.

- m. Click OK.

- 5. Click **Next** to open the **Advanced PCI MegaCore Features** page. For this walkthrough, use the default settings for all options on this page.

- 6. Click **Finish** to complete the parameterization of your pci\_mt64 MegaCore function variation.

### Step 2: Set Up Simulation

An IP functional simulation model is a cycle-accurate VHDL or Verilog HDL model file produced by the Quartus II software. The model allows for fast functional simulation of IP using industry-standard VHDL and Verilog HDL simulators.

Only use these simulation model output files for simulation purposes and expressly not for synthesis or any other purposes. Using these models for synthesis creates a nonfunctional design.