## JESD204C Intel<sup>®</sup> FPGA IP User Guide

Updated for  $Intel^{\ensuremath{\mathbb{R}}}$  Quartus  $\ensuremath{\mathbb{R}}$  Prime Design Suite: **20.1**

IP Version: 1.1.0

# intel

## Contents

| 1. About the JESD204C Intel FPGA IP User Guide                                                                                                                                                                                                                                                                                      | 4                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2. Overview of the JESD204C Intel FPGA IP                                                                                                                                                                                                                                                                                           | .7                                     |

| 2.1. Release Information                                                                                                                                                                                                                                                                                                            | 10<br>10<br>11                         |

| 3. Functional Description                                                                                                                                                                                                                                                                                                           | 4                                      |

| 3.1. Clocks.       1         3.1.1. Device Clock.       1         3.1.2. Frame Clock and Link Clock.       1         3.2. Local Extended Multiblock Clock.       1         3.2.1. LEMC Counter.       1         3.3. CRC Encoding/Decoding.       1         3.4. Scrambler/Descrambler.       1                                     | 14<br>15<br>15<br>16<br>17             |

| 4. Getting Started 1                                                                                                                                                                                                                                                                                                                |                                        |

| 4.1. Installing and Licensing Intel FPGA IP Cores.14.2. Intel FPGA IP Evaluation Mode.14.3. IP Catalog and Parameter Editor.24.4. JESD204C IP Component Files.24.5. Creating a New Intel Quartus Prime Project.24.6. Parameterizing and Generating the IP.24.7. Compiling the JESD204C IP Design.24.8. Programming an FPGA Device.2 | 19<br>22<br>22<br>23<br>23<br>23<br>24 |

| 5. Designing with the JESD204C Intel FPGA IP 2                                                                                                                                                                                                                                                                                      |                                        |

| <ul> <li>5.1. JESD204C TX and RX Reset Sequence</li></ul>                                                                                                                                                                                                                                                                           | 26<br>27<br>28<br>28<br>29<br>29<br>29 |

| 6. JESD204C Intel FPGA IP Parameters 3                                                                                                                                                                                                                                                                                              | \$5                                    |

| 7. Interface Signals                                                                                                                                                                                                                                                                                                                | 39                                     |

| 7.1. Transmitter Signals                                                                                                                                                                                                                                                                                                            |                                        |

| 8. Control and Status Registers5                                                                                                                                                                                                                                                                                                    | 57                                     |

| 8.1. Transmitter Registers                                                                                                                                                                                                                                                                                                          | 59                                     |

| 7. JEJDZUTC TILLEI FFGA IF USEI GUIUE AICHIVES                                                                                                                                                                                                                                                                                      | 5                                      |

Contents

#### 10. Document Revision History for the JESD204C Intel FPGA IP User Guide......94

## **1. About the JESD204C Intel FPGA IP User Guide**

This user guide provides the features, architecture description, steps to instantiate, and guidelines to design the JESD204C Intel<sup>®</sup> FPGA IP using Intel Stratix<sup>®</sup> 10 and Intel Agilex<sup>m</sup> devices.

#### **Intended Audience**

This document is intended for:

- Design architect to make IP selection during system level design planning phase

- Hardware designers when integrating the IP into their system level design

- Validation engineers during system level simulation and hardware validation phase

#### **Related Documents**

The following table lists other reference documents which are related to the JESD protocol.

#### Table 1.Related Documents

| Reference                                           | Description                                                                                                                                                       |  |  |  |  |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| JESD204C Intel Agilex Design Example User Guide     | Provides information about how to instantiate JESD204C design examples using Intel Agilex devices.                                                                |  |  |  |  |  |

| JESD204C Intel Stratix 10 Design Example User Guide | Provides information about how to instantiate JESD204C design examples using Intel Stratix 10 devices.                                                            |  |  |  |  |  |

| JESD204B Intel FPGA IP User Guide                   | Provides information about the JESD204B Intel FPGA IP.                                                                                                            |  |  |  |  |  |

| Intel Agilex Device Data Sheet                      | This document describes the electrical characteristics,<br>switching characteristics, configuration specifications, and<br>timing for Intel Agilex devices.       |  |  |  |  |  |

| Intel Stratix 10 Device Data Sheet                  | Provides information about the electrical characteristics,<br>switching characteristics, configuration specifications, and<br>timing for Intel Stratix 10 devices |  |  |  |  |  |

| E-Tile Transceiver PHY User Guide                   | Provides information about the E-tile Transceiver PHY.                                                                                                            |  |  |  |  |  |

#### **Acronyms and Glossary**

#### Table 2.Acronym List

| Acronym | Expansion                       |  |  |  |

|---------|---------------------------------|--|--|--|

| LEMC    | Local Extended Multiblock Clock |  |  |  |

| FC      | Frame clock rate                |  |  |  |

| ADC     | Analog to Digital Converter     |  |  |  |

| DAC     | Digital to Analog Converter     |  |  |  |

|         | continued                       |  |  |  |

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

#### 1. About the JESD204C Intel FPGA IP User Guide UG-20226 | 2021.06.16

| Acronym    | Expansion                                                                                      |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DSP        | Digital Signal Processor                                                                       |  |  |  |  |  |

| ТХ         | Transmitter                                                                                    |  |  |  |  |  |

| RX         | Receiver                                                                                       |  |  |  |  |  |

| DLL        | Data link layer                                                                                |  |  |  |  |  |

| CSR        | Control and status register                                                                    |  |  |  |  |  |

| CRU        | Clock and Reset Unit                                                                           |  |  |  |  |  |

| ISR        | Interrupt Service Routine                                                                      |  |  |  |  |  |

| FIFO       | First-In-First-Out                                                                             |  |  |  |  |  |

| SERDES     | Serializer Deserializer                                                                        |  |  |  |  |  |

| ECC        | Error Correcting Code                                                                          |  |  |  |  |  |

| FEC        | Forward Error Correction                                                                       |  |  |  |  |  |

| SERR       | Single Error Detection (in ECC, correctable)                                                   |  |  |  |  |  |

| DERR       | Double Error Detection (in ECC, fatal)                                                         |  |  |  |  |  |

| PRBS       | Pseudorandom binary sequence                                                                   |  |  |  |  |  |

| МАС        | Media Access Controller. MAC includes protocol sublayer, transport layer, and data link layer. |  |  |  |  |  |

| РНҮ        | Physical Layer. PHY typically includes the physical layer, SERDES, drivers, receivers and CDR. |  |  |  |  |  |

| PCS        | Physical Coding Sub-layer                                                                      |  |  |  |  |  |

| РМА        | Physical Medium Attachment                                                                     |  |  |  |  |  |

| RBD        | RX Buffer Delay                                                                                |  |  |  |  |  |

| UI         | Unit Interval = duration of serial bit                                                         |  |  |  |  |  |

| RBD count  | RX Buffer Delay latest lane arrival                                                            |  |  |  |  |  |

| RBD offset | RX Buffer Delay release opportunity                                                            |  |  |  |  |  |

| SH         | Sync header                                                                                    |  |  |  |  |  |

| TL         | Transport layer                                                                                |  |  |  |  |  |

#### Table 3.Glossary List

| Term             | Description                                                                                                        |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Converter Device | ADC or DAC converter                                                                                               |  |  |  |  |  |

| Logic Device     | FPGA or ASIC                                                                                                       |  |  |  |  |  |

| Octet            | A group of 8 bits, serving as input to 64/66 encoder and output from the decoder                                   |  |  |  |  |  |

| Nibble           | A set of 4 bits which is the base working unit of JESD204C specifications                                          |  |  |  |  |  |

| Block            | A 66-bit symbol generated by the 64/66 encoding scheme                                                             |  |  |  |  |  |

| Line Rate        | Effective data rate of serial link<br>Lane Line Rate = (Mx Sx N'x 66/64 x FC) / L                                  |  |  |  |  |  |

| Link Clock       | The associated parallel data will be 128 bit/132 bit instead of 64 bit/66 bit.<br>Link Clock = Lane Line Rate/132. |  |  |  |  |  |

|                  | continued                                                                                                          |  |  |  |  |  |

# intel.

#### 1. About the JESD204C Intel FPGA IP User Guide UG-20226 | 2021.06.16

| Term                    | Description                                                                                                                                  |  |  |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Frame                   | A set of consecutive octets in which the position of each octet can be identified by reference to a frame alignment signal.                  |  |  |  |  |  |  |

| Frame Clock             | A system clock which runs at the frame's rate, that must be $1x$ , $2x$ , or $4x$ link clock.                                                |  |  |  |  |  |  |

| Samples per frame clock | Samples per clock, the total samples in frame clock for the converter device.                                                                |  |  |  |  |  |  |

| LEMC                    | Internal clock used to align the boundary of the extended multiblocks between lanes and into the external references (SYSREF or Subclass 1). |  |  |  |  |  |  |

| Subclass 0              | No support for deterministic latency. Data should be immediately released upon lane to lane deskew on receiver.                              |  |  |  |  |  |  |

| Subclass 1              | Deterministic latency using SYSREF.                                                                                                          |  |  |  |  |  |  |

| Multipoint Link         | Inter-device links with 2 or more converter devices.                                                                                         |  |  |  |  |  |  |

| 64B/66B Encoding        | Line code that maps 64-bit data to 66 bits to form a block. The base level data structure is a block that starts with 2-bit sync header.     |  |  |  |  |  |  |

#### Table 4.Symbols

| Term | Description                                                        |  |  |  |  |  |

|------|--------------------------------------------------------------------|--|--|--|--|--|

| L    | Number of lanes per converter device                               |  |  |  |  |  |

| М    | Number of converters per device                                    |  |  |  |  |  |

| F    | Number of octets per frame on a single lane                        |  |  |  |  |  |

| S    | Number of samples transmitted per single converter per frame cycle |  |  |  |  |  |

| Ν    | Converter resolution                                               |  |  |  |  |  |

| N'   | Total number of bits per sample in the user data format            |  |  |  |  |  |

| CS   | Number of control bits per conversion sample                       |  |  |  |  |  |

| CF   | Number of control words per frame clock period per link            |  |  |  |  |  |

| HD   | High Density user data format                                      |  |  |  |  |  |

| E    | Number of multiblocks in an extended multiblock                    |  |  |  |  |  |

## 2. Overview of the JESD204C Intel FPGA IP

The JESD204C Intel FPGA IP is a high-speed point-to-point serial interface for digitalto-analog (DAC) or analog-to-digital (ADC) converters to transfer data to FPGA devices. This unidirectional serial interface runs at a maximum data rate of 28.9 Gbps. This protocol offers higher bandwidth, low I/O count and supports scalability in both number of lanes and data rates.

The JESD204C Intel FPGA IP addresses multidevice synchronization using Subclass 1 to achieve deterministic latency.

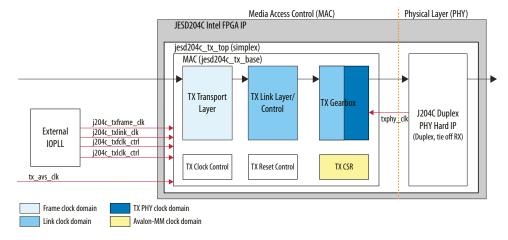

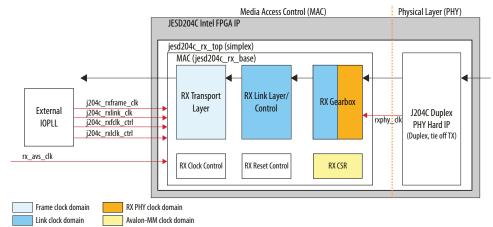

The JESD204C Intel FPGA IP supports TX-only, RX-only, and Duplex (TX and RX) mode. The Intel FPGA IP is a unidirectional protocol where interfacing to ADC utilizes the transceiver RX path and interfacing to DAC utilizes the transceiver TX path.

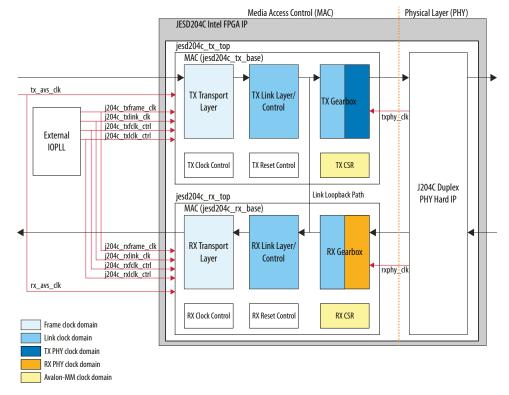

The Intel FPGA IP incorporates:

- Media access control (MAC)—data link layer (DLL) and transport layer (TL) blocks that control the link states.

- Physical layer (PHY)—physical coding sublayer (PCS) and physical media attachment (PMA) block.

The transport layer (TL) in the MAC controls the assembling and disassembling of the frames.

## intel

#### Figure 1. JESD204C Duplex Functional Block Diagram

#### Figure 2. JESD204C TX-only Functional Block Diagram

#### Figure 3. JESD204C RX-only Functional Block Diagram

## 2.1. Release Information

Intel FPGA IP versions match the Intel Quartus<sup>®</sup> Prime Design Suite software versions until v19.1. Starting in Intel Quartus Prime Design Suite software version 19.2, Intel FPGA IP has a new versioning scheme.

The Intel FPGA IP version (X.Y.Z) number can change with each Intel Quartus Prime software version. A change in:

- X indicates a major revision of the IP. If you update the Intel Quartus Prime software, you must regenerate the IP.

- Y indicates the IP includes new features. Regenerate your IP to include these new features.

- Z indicates the IP includes minor changes. Regenerate your IP to include these changes.

#### Table 5. JESD204C Intel FPGA IP Release Information

| Item                                    | Description |  |  |  |  |

|-----------------------------------------|-------------|--|--|--|--|

| IP Version                              | 1.1.0       |  |  |  |  |

| Intel Quartus Prime Pro Edition Version | 20.1        |  |  |  |  |

| Release Date                            | 2020.04.13  |  |  |  |  |

| Ordering Code                           | IP-JESD204C |  |  |  |  |

#### **Related Information**

#### JESD204C Intel FPGA IP Release Notes

Provides information about the new features and updates for each IP release.

Send Feedback

## 2.2. Device Family Support

#### Table 6.Intel Device Family Support

| Device Family             | Support Level |  |  |  |

|---------------------------|---------------|--|--|--|

| Intel Agilex (E-tile)     | Final         |  |  |  |

| Intel Stratix 10 (E-tile) | Final         |  |  |  |

The following terms define device support levels for Intel FPGA IP cores:

- Advance support—the IP core is available for simulation and compilation for this device family. Timing models include initial engineering estimates of delays based on early post-layout information. The timing models are subject to change as silicon testing improves the correlation between the actual silicon and the timing models. You can use this IP core for system architecture and resource utilization studies, simulation, pinout, system latency assessments, basic timing assessments (pipeline budgeting), and I/O transfer strategy (data-path width, burst depth, I/O standards tradeoffs).

- Preliminary support—the IP core is verified with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution.

- Final support—the IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.

## 2.3. JESD204C Intel FPGA IP Features

The JESD204C Intel FPGA IP is a high-speed point-to-point serial interface intellectual property (IP). The JESD204C Intel FPGA IP is the latest IP from Intel that supports the JESD204C protocol. This IP is not backwards compatible and does not support JESD204B protocol. You can use the existing the JESD204B Intel FPGA IP to support JESD204B protocol.

#### Table 7. Brief Information about the JESD204C Intel FPGA IP

| Features          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Protocol Features | <ul> <li>Joint Electron Device Engineering Council (JEDEC) JESD204C standard 2017</li> <li>Device subclass:         <ul> <li>Subclass 0—No deterministic latency.</li> <li>Subclass 1—Uses SYSREF signal to support deterministic latency</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                 |

| Core Features     | <ul> <li>Data rate of up to 28.9 Gbps for Intel Agilex and Intel Stratix 10 (E-tile) devices.</li> <li>Single or multiple lanes (up to 16 lanes per link)</li> <li>Local extended multiblock clock (LEMC) counter based on E=1 to 256</li> <li>Serial lane alignment and monitoring</li> <li>Lane synchronization</li> <li>Modular design that supports multidevice synchronization</li> <li>MAC and PHY partitioning</li> <li>Deterministic latency support</li> <li>64/66 encoding</li> <li>Scrambling/descrambling</li> </ul> |

|                   | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Features              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | <ul> <li>Avalon<sup>®</sup> streaming interface for transmit and receive datapaths</li> <li>Avalon memory-mapped interface for control and status registers (CSR)</li> <li>Dynamic generation of simulation testbench</li> <li>Bonded and non-bonded TX PMA mode</li> <li>Optional support for ECC M20K DCFIFO</li> <li>Options for sync header configurations         <ul> <li>CRC-12</li> <li>Standalone command channels</li> </ul> </li> </ul> |

| Limitations           | No FEC support                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Typical Application   | <ul> <li>Wireless communication equipment</li> <li>Broadcast equipment</li> <li>Military equipment</li> <li>Medical equipment</li> <li>Test and measurement equipment</li> </ul>                                                                                                                                                                                                                                                                   |

| Device Family Support | Intel Agilex and Intel Stratix 10 (E-tile) FPGA devices                                                                                                                                                                                                                                                                                                                                                                                            |

| Design Tools          | <ul> <li>Platform Designer parameter editor in the Intel Quartus Prime Pro Edition software for design creation and compilation</li> <li>Timing Analyzer in the Intel Quartus Prime software for timing analysis</li> <li>ModelSim* - Intel FPGA Starter Edition, VCS*/VCS MX, and Xcelium* Parallel simulator software for design simulation or synthesis</li> </ul>                                                                              |

## 2.4. Presets

Intel offers presets to assist you in creating your designs.

#### Table 8.Available Presets

| Presets | Resolutio<br>n | Lane Rate<br>(Mbps) | L | М | F  | S | HD | E | CS | CF | Transceiver<br>Reference Clock<br>(refclk) Frequency<br>(MHz) |

|---------|----------------|---------------------|---|---|----|---|----|---|----|----|---------------------------------------------------------------|

| Duplex  | 24             | 24333.3             | 2 | 8 | 12 | 1 | 0  | 3 | 0  | 0  | 368.681818                                                    |

|         | 16             | 16222.2             | 4 | 8 | 4  | 1 | 0  | 4 | 0  | 0  | 245.787878                                                    |

## 2.5. Performance and Resource Utilization

#### Table 9. JESD204C Intel FPGA IP Performance

| Device Family             | PMA Speed Grade | FPGA Fabric Speed Grade | Enable Soft PCS (Gbps) |  |  |  |

|---------------------------|-----------------|-------------------------|------------------------|--|--|--|

| Intel Agilex (E-tile)     | 1               | -1                      | 5.0 to 28.9            |  |  |  |

|                           | 2               | -2                      | 5.0 to 28.3            |  |  |  |

|                           |                 | -3                      | 5.0 to 25.6            |  |  |  |

|                           | 3               | -2                      | 5.0 to 17.4            |  |  |  |

|                           |                 | -3                      | 5.0 to 17.4            |  |  |  |

| Intel Stratix 10 (E-tile) | 1               | -1                      | 5.0 to 28.9            |  |  |  |

|                           |                 | -2                      | 5.0 to 25.6            |  |  |  |

|                           | 2               | -1                      | 5.0 to 28.3            |  |  |  |

|                           | continued       |                         |                        |  |  |  |

| Device Family | PMA Speed Grade | FPGA Fabric Speed Grade | Enable Soft PCS (Gbps) |

|---------------|-----------------|-------------------------|------------------------|

|               |                 | -2                      | 5.0 to 25.6            |

|               | 3               | -1                      | 5.0 to 17.4            |

|               |                 | -2                      | 5.0 to 17.4            |

|               |                 | -3                      | 5.0 to 17.4            |

The following table lists the estimated resource utilization data of the JESD204C IP. These results are obtained using the Intel Quartus Prime software targeting the Intel Agilex, AGFB014R24A3E3VR0 device and Intel Stratix 10, 1ST280EY3F55E3VGS1 device.

The variations for resource utilization are configured with the following parameter settings:

#### Table 10. Parameter Settings to Obtain the Resource Utilization Data

| Parameter                             | Setting        |

|---------------------------------------|----------------|

| JESD204C Wrapper                      | Base and PHY   |

| JESD204C Subclass                     | 1              |

| Data Rate                             | 17.4 Gbps      |

| Bonding Mode                          | Non-bonded     |

| Reference Clock Frequency             | 263.636363 MHz |

| Enable Scrambler (SCR)                | On             |

| Enable Error Code Correction (ECC_EN) | Off            |

#### Table 11. JESD204C IP Resource Utilization for Intel Agilex Devices

| Variants | L | м | F  | FCLK_<br>MULP | WIDTH<br>_MULP | ALM   | ALUT  | Logic<br>Register | M20K  |

|----------|---|---|----|---------------|----------------|-------|-------|-------------------|-------|

| ТХ       | 4 | 8 | 6  | 1             | 8              | 6885  | 6488  | 9113              | 2     |

|          | 4 | 8 | 6  | 2             | 4              | 7012  | 7080  | 9780              | 2     |

|          | 4 | 8 | 4  | 1             | 4              | 5382  | 5810  | 7509              | 2     |

|          | 4 | 8 | 4  | 2             | 2              | 6311  | 6876  | 9458              | 2     |

|          | 2 | 8 | 6  | 1             | 8              | 3901  | 3883  | 5306              | 2     |

|          | 2 | 8 | 6  | 2             | 4              | 4066  | 4247  | 5916              | 2     |

|          | 8 | 8 | 3  | 1             | 16             | 12492 | 11374 | 15988             | 2     |

|          | 8 | 8 | 3  | 2             | 8              | 12983 | 12577 | 18074             | 2     |

|          | 3 | 8 | 4  | 1             | 2              | 4410  | 4801  | 6290              | 2     |

|          | 3 | 8 | 4  | 2             | 1              | 5030  | 5617  | 7604              | 2     |

| RX       | 2 | 8 | 12 | 1             | 4              | 5236  | 5780  | 6434              | 10    |

|          | 2 | 8 | 12 | 2             | 2              | 4755  | 5347  | 5846              | 10    |

|          | 1 | 2 | 8  | 1             | 4              | 2650  | 3189  | 3428              | 4     |

|          | 1 | 2 | 8  | 2             | 2              | 2637  | 3224  | 3436              | 4     |

|          |   |   |    |               |                |       |       | cont              | inued |

2. Overview of the JESD204C Intel FPGA IP UG-20226 | 2021.06.16

## intel

| Variants | L | м | F  | FCLK_<br>MULP | WIDTH<br>_MULP | ALM   | ALUT  | Logic<br>Register | M20K |

|----------|---|---|----|---------------|----------------|-------|-------|-------------------|------|

|          | 1 | 4 | 24 | 1             | 4              | 3281  | 3881  | 4311              | 6    |

|          | 1 | 4 | 24 | 2             | 2              | 2963  | 3567  | 3919              | 6    |

|          | 8 | 1 | 1  | 1             | 16             | 13582 | 15237 | 14634             | 34   |

|          | 8 | 1 | 1  | 2             | 8              | 13743 | 16028 | 15894             | 34   |

|          | 3 | 2 | 4  | 1             | 4              | 5560  | 6244  | 6209              | 9    |

|          | 3 | 2 | 4  | 2             | 2              | 5717  | 6658  | 6741              | 12   |

| Table 12. | JESD204C IP Resource Utilization for Intel Stratix 10 Devices |

|-----------|---------------------------------------------------------------|

|           |                                                               |

| Variants | L | м | F  | FCLK_<br>MULP | WIDTH<br>_MULP | ALM   | ALUT  | Logic<br>Register | M20K |

|----------|---|---|----|---------------|----------------|-------|-------|-------------------|------|

| ТХ       | 4 | 8 | 6  | 1             | 8              | 6865  | 6474  | 9253              | 2    |

|          | 4 | 8 | 6  | 2             | 4              | 7002  | 7084  | 10092             | 2    |

|          | 4 | 8 | 4  | 1             | 4              | 5398  | 5829  | 7708              | 2    |

|          | 4 | 8 | 4  | 2             | 2              | 6712  | 7445  | 10171             | 2    |

|          | 2 | 8 | 6  | 1             | 8              | 3944  | 3881  | 5369              | 2    |

|          | 2 | 8 | 6  | 2             | 4              | 4190  | 4310  | 6015              | 2    |

|          | 8 | 8 | 3  | 1             | 16             | 12601 | 11494 | 16877             | 2    |

|          | 8 | 8 | 3  | 2             | 8              | 13157 | 12746 | 18645             | 2    |

|          | 3 | 8 | 4  | 1             | 2              | 4405  | 4827  | 6344              | 2    |

|          | 3 | 8 | 4  | 2             | 1              | 5052  | 5638  | 7678              | 2    |

| RX       | 2 | 8 | 12 | 1             | 4              | 5266  | 5827  | 6349              | 10   |

|          | 2 | 8 | 12 | 2             | 2              | 4819  | 5420  | 5944              | 10   |

|          | 1 | 2 | 8  | 1             | 4              | 2642  | 3204  | 3385              | 4    |

|          | 1 | 2 | 8  | 2             | 2              | 2672  | 3214  | 3484              | 4    |

|          | 1 | 4 | 24 | 1             | 4              | 3243  | 3837  | 4166              | 6    |

|          | 1 | 4 | 24 | 2             | 2              | 3027  | 3585  | 3914              | 6    |

|          | 8 | 1 | 1  | 1             | 16             | 13511 | 15225 | 14903             | 34   |

|          | 8 | 1 | 1  | 2             | 8              | 13344 | 15812 | 14891             | 34   |

|          | 3 | 2 | 4  | 1             | 4              | 5524  | 6228  | 6332              | 9    |

|          | 3 | 2 | 4  | 2             | 2              | 5751  | 6673  | 6966              | 12   |

intel

## 3. Functional Description

The JESD204C IP consists of scrambler and descrambler, transport layer, data link layer and physical layer.

The transport layer maps and packetizes the data samples into JESD204C frame data format. The transport layer operates in the parameters of M, N, S, CS and CF and maps into the parameters of F octets and L lanes. The transport layer is part of the JESD204C IP.

This IP supports line rate up to 28.9 Gbps per lane, and uses device clock which in turns generates the desired internal clocks for the transceivers and core logic. The frame clock does not need to be a physical input to the FPGA based on the *JESD204C Specification*.

To support multidevice synchronization, JESD204C IP uses Local Extended Multiblock Clock (LEMC) as a common timing reference. The IP generates the LEMC counter and uses *SYSREF* to align and reset the LEMC counter.

The IP supports Subclass 0 and Subclass 1. With Subclass 1, the IP can use the SYSREF signal and Device clock routed to achieve deterministic latency between the logic and converter devices.

## 3.1. Clocks

The JESD204C IP runs on link clock (link layer) and frame clock (transport layer). The transceiver runs in the link clock domain and the serial clock domain.

| Clock Signal                                                | Formula                                 | Description                                                                                                                                                                                                    |

|-------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX/RX device clock<br>j204c_pll_refclk                      | PLL selection                           | The device clock is the PLL reference clock to the transceiver PLL.                                                                                                                                            |

| TX/RX link clock<br>j204c_txlink_clk<br>j204c_rxlink_clk    | Line rate/132                           | The timing reference for the JESD204C IP. The link clock is line rate divided by 132 because the link clock operates in a 132-bit data bus domain architecture after 64B/66B encoding.                         |

| TX/RX frame clock<br>j204c_txframe_clk<br>j204c_rxframe_clk | (Link clock<br>frequency*FCLK_MULP) MHz | The frame clock as per the JESD204C specification. The frame clock is always 1x, 2x, or 4x of the link clock.                                                                                                  |

| TX/RX Avalon-MM (AVMM)<br>clock<br>j204c_tx_avs_clk         | -                                       | The configuration clock for the JESD204C IP control and status registers through the Avalon-MM interface. This clock is asynchronous to all the other clocks. The frequency range of this clock is 75–125 MHz. |

|                                                             | 1                                       | continued                                                                                                                                                                                                      |

#### Table 13.JESD204C IP Clocks

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

| Clock Signal                                          | Formula      | Description                                                                                                                                           |

|-------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| j204c_rx_avs_clk                                      |              |                                                                                                                                                       |

| TX/RX PHY clock<br>j204c_txphy_clk<br>j204c_rxphy_clk | Line rate/64 | The PHY clock internally generated from the transceiver parallel clock for the TX path or the recovered clock generated from the CDR for the RX path. |

| Transceiver reconfig clock<br>j204c_reconfig_clk      | _            | The transceiver reconfiguration clock. The frequency range of this clock is 100–162 MHz.                                                              |

### **3.1.1. Device Clock**

In a converter device, the sampling clock is typically the device clock. The JESD204C IP uses the device clock to generate the desired internal clocks for the transceivers and core logic.

For the JESD204C IP link in an FPGA logic device, you can select one of the options provided in the **PLL/CDR reference clock frequency** parameter in the JESD204C IP parameter editor.

In the single reference clock design, both sets of pins are driven by the same clock source. The device clock is used as the transceiver PLL reference clock and also the core PLL reference clock. In the dual reference clock design, each set of pins are driven by a different clock source. The device clock is used as the core PLL reference clock and the other reference clock (phase-locked to device clock) is used as the transceiver PLL reference clock. If you want to use the same reference clock for the transceiver and core PLLs, you must use two separate input pins for these PLL reference clocks in your design. Use a common clock source on the board to generate two separate clocks of the same frequency to drive the inputs.

The device clock frequency depends on the data rate and total number of lanes. When you generate the IP, the Intel Quartus Prime Pro Edition software provides the available reference frequency for the transceiver PLL and core PLL based on your selection.

For Subclass 1 application, ensure that the routing of the SYSREF signal and the device clock to the FPGA has matching trace lengths.

### 3.1.2. Frame Clock and Link Clock

The frame clock frequency always equals the link clock frequency times the frame clock frequency multiplier (FCLK\_MULP):

Frame clock frequency = FCLK\_MULP x Link clock frequency

You can set the frame clock frequency multiplier through the JESD204C IP parameter editor. The valid values for the multiplier are limited to 1, 2, and 4. Because of the fixed relationship between the link clock and the frame clock, the Avalon-ST data will not always be streaming.

To provide consistency across the design regardless of frame clock and sampling clock, the link clock is used as a timing reference.

The IOPLL core should provide both the frame clock and link clock from the same PLL as these two clocks are treated as synchronous in the design.

For JESD204 TX and RX IPs, j204c\_txlclk\_ctrl or j204c\_rxlclk\_ctrl provides the phase information of a link clock rising edge that aligned to a frame clock rising edge.

Similarly, j204c\_txfclk\_ctrl or j204c\_rxfclk\_ctrl provides the phase information of a frame clock rising edge that aligned to a link clock rising edge. This additional clock phase information handles the transfer between frame clock and link clock in a synchronous manner.

## **3.2. Local Extended Multiblock Clock**

The JESD204C IP uses the Extended Multiblock Clock (LEMC) as a common timing reference to support multidevice configuration.

LEMC is an internal clock that aligns the boundaries of the extended multiblocks between lanes. In deterministic latency devices, LEMC aligns the boundaries to an external reference, for example, SYSREF. The use of LEMC is mandatory in Subclass 1 modes but optional in Subclass 0 modes.

The JESD204C IP implements LEMC as a counter that increments in link clock counts, and depends on the **Multiblocks in an extended multiblock (E)** parameter. The extended multiblock is a container of a number of multiblocks.

The E parameter depends on these two factors:

- The parameter must allow an integer of F within an extended multiblock. For example, if F=3, 32 multiblocks contain 256 octets (32x64/8). 256 octets is not divisible by F=3. So, for F=3, the minimum E is 3.

- E must be larger than the maximum possible delay variation across any two lanes of a link.

In Subclass 1 deterministic latency system, SYSREF is distributed to the devices to be aligned in the system. The SYSREF signal resets the internal LEMC clock edge when the sampled SYSREF rising edge transitions from 0 to 1.

The JESD204C IP does not use the device clock directly to sample SYSREF because of the source synchronous signaling of SYSREF with respect to the device clock sampling from the clock chip. The IP uses the link clock to sample SYSREF. The PLL that provides the link clock or frame clock must be in normal mode to phase-compensate the link clock to the device clock.

You can program a single or multiple sampling of SYSREF through the JESD204C control and status registers.

- A single sampling SYSREF does not detect SYSREF period errors.

- A continuous sampling mode detects SYSREF period errors.

In most converter device systems, disable SYSREF sampling if there are no errors, and begin link operation with a link reinitialization request.

#### 3.2.1. LEMC Counter

JESD204C IP maintains an LEMC counter that counts from 0 to  $(E^*32)-1$  and wraps around again.

In Subclass 0 system, the LEMC counter starts at the deassertion of the link reset signal, without waiting for SYSREF detection.

In Subclass 1 deterministic latency system, all transmitters and receivers receive a common SYSREF, and the LEMC counter resets within two link clock cycles. SYSREF must be the same for the converter devices, which are grouped and required to be synchronized together.

Maximum SYSREF frequency = data rate/(66x32xE).

#### Table 14. Example of SYSREF Frequency Calculation

In this example, you can choose to perform one of the following options:

- Provide two SYSREF and a device clock; in which the ADC groups share the device clock and the two SYSREF clock (1.42 MHz and 2.84 MHz).

- Provide 1 SYSREF running at 1.4 MHz and a device clock for the two ADC groups and one DAC group because the SYSREF period in the DAC is in the multiplication of *n* integer.

| Group                | Configuration                                                                | SYSREF Frequency                |

|----------------------|------------------------------------------------------------------------------|---------------------------------|

| ADC Group 1 (2 ADCs) | <ul> <li>LMF = 222</li> <li>E = 2</li> <li>Data rate = 6,000 Mbps</li> </ul> | (6,000 MHz/(66x32x2) = 1.42 MHz |

| ADC Group 2 (2 ADCs) | <ul> <li>LMF = 811</li> <li>E = 1</li> <li>Data rate = 6,000 Mbps</li> </ul> | (6,000 MHz/(66x32x1) = 2.84 MHz |

| DAC Group 3 (2 DACs) | <ul> <li>LMF = 222</li> <li>E = 1</li> <li>Data rate = 3,000 Mbps</li> </ul> | (3,000 MHz/(66x32x1) = 1.42 MHz |

*Note:* 1.42 MHz is the common maximum SYSREF frequency. You can lower the frequency to 0.71 MHz and the design still works.

### **3.3. CRC Encoding/Decoding**

The JESD204C IP supports only CRC-12 encoding/decoding.

The CRC-12 encoder computes 12 parity bits using this polynomial:

$0 \times 987 = x^{12} + x^9 + x^8 + x^3 + x^2 + x^1 + 1$

### 3.4. Scrambler/Descrambler

Both the scrambler and descrambler are designed in a 128-bit parallel implementation and the scrambling/descrambling order starts from the first octet with MSB first.

# intel

#### Figure 4. Scrambling/Descrambling Order

| MSB  | LSB  | MSB  | LSB  |         | •       |

|------|------|------|------|---------|---------|

| Octe | et 1 | Octe | et 2 | Octet 3 | Octet 4 |

The JESD204C TX and RX IP core support scrambling by implementing a 128-bit parallel scrambler in each lane. The scrambler and descrambler are located in the JESD204C IP MAC interfacing to the Avalon-ST interface. You can enable or disable scrambling through CSR configuration for all lanes. Mixed mode operation, where scrambling is enabled for some lanes, is not permitted.

The scrambling polynomial is:

$x^{58} + x^{39} + 1$

The descrambler can self-synchronize in 58 bits. In a typical application where the reset value of the scrambler seed is different from the converter device to FPGA logic device, the correct user data is recovered in the receiver in 1 link clock (due to the 128-bit architecture). The PRBS pattern checker on the transport layer should always disable checking of the first eight octets from the JESD204C RX IP.

Send Feedback

## 4. Getting Started

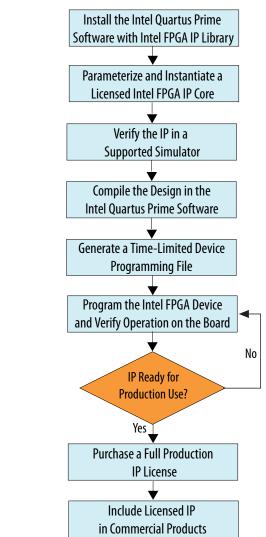

## 4.1. Installing and Licensing Intel FPGA IP Cores

The Intel Quartus Prime software installation includes the Intel FPGA IP library. This library provides many useful IP cores for your production use without the need for an additional license. Some Intel FPGA IP cores require purchase of a separate license for production use. The Intel FPGA IP Evaluation Mode allows you to evaluate these licensed Intel FPGA IP cores in simulation and hardware, before deciding to purchase a full production IP core license. You only need to purchase a full production license for licensed Intel IP cores after you complete hardware testing and are ready to use the IP in production.

The Intel Quartus Prime software installs IP cores in the following locations by default:

#### Figure 5. IP Core Installation Path

#### 🔁 intelFPGA(\_pro)

**quartus** - Contains the Intel Quartus Prime software

**ip** - Contains the Intel FPGA IP library and third-party IP cores

altera - Contains the Intel FPGA IP library source code

- -

- Contains the Intel FPGA IP source files

#### Table 15. IP Core Installation Locations

| Location                                                       | Software                                | Platform |

|----------------------------------------------------------------|-----------------------------------------|----------|

| <drive>:\intelFPGA_pro\ip\altera</drive>                       | Intel Quartus Prime Pro Edition         | Windows* |

| <drive>:\intelFPGA\ip\altera</drive>                           | Intel Quartus Prime Standard Edition    | Windows  |

| <pre><home directory="">:/intelFPGA_pro/ip/altera</home></pre> | Intel Quartus Prime Pro Edition         | Linux*   |

| <home directory="">:/intelFPGA/ip/altera</home>                | Intel Quartus Prime Standard<br>Edition | Linux    |

*Note:* The Intel Quartus Prime software does not support spaces in the installation path.

## **4.2. Intel FPGA IP Evaluation Mode**

The free Intel FPGA IP Evaluation Mode allows you to evaluate licensed Intel FPGA IP cores in simulation and hardware before purchase. Intel FPGA IP Evaluation Mode supports the following evaluations without additional license:

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

- Simulate the behavior of a licensed Intel FPGA IP core in your system.

- Verify the functionality, size, and speed of the IP core quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device with your IP core and verify your design in hardware.

Intel FPGA IP Evaluation Mode supports the following operation modes:

- **Tethered**—Allows running the design containing the licensed Intel FPGA IP indefinitely with a connection between your board and the host computer. Tethered mode requires a serial joint test action group (JTAG) cable connected between the JTAG port on your board and the host computer, which is running the Intel Quartus Prime Programmer for the duration of the hardware evaluation period. The Programmer only requires a minimum installation of the Intel Quartus Prime software, and requires no Intel Quartus Prime license. The host computer controls the evaluation time by sending a periodic signal to the device via the JTAG port. If all licensed IP cores in the design support tethered mode, the evaluation time runs until any IP core evaluation expires. If all of the IP cores support unlimited evaluation time, the device does not time-out.

- Untethered—Allows running the design containing the licensed IP for a limited time. The IP core reverts to untethered mode if the device disconnects from the host computer running the Intel Quartus Prime software. The IP core also reverts to untethered mode if any other licensed IP core in the design does not support tethered mode.

When the evaluation time expires for any licensed Intel FPGA IP in the design, the design stops functioning. All IP cores that use the Intel FPGA IP Evaluation Mode time out simultaneously when any IP core in the design times out. When the evaluation time expires, you must reprogram the FPGA device before continuing hardware verification. To extend use of the IP core for production, purchase a full production license for the IP core.

## intel

#### Figure 6. Intel FPGA IP Evaluation Mode Flow

*Note:* Refer to each IP core's user guide for parameterization steps and implementation details.

Intel licenses IP cores on a per-seat, perpetual basis. The license fee includes firstyear maintenance and support. You must renew the maintenance contract to receive updates, bug fixes, and technical support beyond the first year. You must purchase a full production license for Intel FPGA IP cores that require a production license, before generating programming files that you may use for an unlimited time. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (*<project name>\_time\_limited.sof*) that expires at the time limit. To obtain your production license keys, visit the Self-Service Licensing Center.

The Intel FPGA Software License Agreements govern the installation and use of licensed IP cores, the Intel Quartus Prime design software, and all unlicensed IP cores.

#### **Related Information**

- Intel FPGA Licensing Support Center

- Introduction to Intel FPGA Software Installation and Licensing

## 4.3. IP Catalog and Parameter Editor

The IP Catalog displays the IP cores available for your project, including Intel FPGA IP and other IP that you add to the IP Catalog search path.. Use the following features of the IP Catalog to locate and customize an IP core:

- Filter IP Catalog to Show IP for active device family or Show IP for all device families. If you have no project open, select the Device Family in IP Catalog.

- Type in the Search field to locate any full or partial IP core name in IP Catalog.

- Right-click an IP core name in IP Catalog to display details about supported devices, to open the IP core's installation folder, and for links to IP documentation.

- Click **Search for Partner IP** to access partner IP information on the web.

The parameter editor prompts you to specify an IP variation name, optional ports, and output file generation options. The parameter editor generates a top-level Intel Quartus Prime IP file (.ip) for an IP variation in Intel Quartus Prime Pro Edition projects or Quartus IP file (.qip) for an IP variation in Intel Quartus Prime Standard Edition projects.

### 4.4. JESD204C IP Component Files

The following table describes the generated files and other files that may be in your project directory. The names and types of generated files specified may vary depending on whether you create your design with VHDL or Verilog HDL.

| Extension                                               | Description                                                                                                                                                                                                                                                                                                                                  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <variation name="">.<b>v</b> or <b>.vhd</b></variation> | IP core variation file, which defines a VHDL or Verilog HDL description of the custom<br>Instantiate the entity defined by this file inside of your design. Include this file when<br>compiling your design in the Intel Quartus Prime software.                                                                                             |  |  |

| <variation name="">.cmp</variation>                     | A VHDL component declaration file for the IP variation. Add the contents of this file to any VHDL architecture that instantiates the IP.                                                                                                                                                                                                     |  |  |

| <variation name="">.sdc</variation>                     | Contains timing constraints for your IP variation.                                                                                                                                                                                                                                                                                           |  |  |

| <variation name="">.qip or .ip</variation>              | Contains Intel Quartus Prime project information for your IP variation.                                                                                                                                                                                                                                                                      |  |  |

| <variation name="">.tcl</variation>                     | Tcl script file to run in Intel Quartus Prime software.                                                                                                                                                                                                                                                                                      |  |  |

| <variation name="">.sip</variation>                     | Contains IP library mapping information required by the Intel Quartus Prime software<br>The Intel Quartus Prime software generates a . <b>sip</b> file during generation of some Int<br>FPGA IP cores. You must add any generated <b>.sip</b> file to your project for use by<br>NativeLink simulation and the Intel Quartus Prime Archiver. |  |  |

| <variation name="">.spd</variation>                     | Contains a list of required simulation files for your IP.                                                                                                                                                                                                                                                                                    |  |  |

#### Table 16. Generated Files

#### 4.5. Creating a New Intel Quartus Prime Project

You can create a new Intel Quartus Prime project with the **New Project Wizard**. Creating a new project allows you to do the following:

- Specify the working directory for the project.

- Assign the project name.

- Designate the name of the top-level design entity.

- 1. Launch the Intel Quartus Prime software.

- 2. On the File menu, click New Project Wizard.

- 3. In the **New Project Wizard: Directory, Name, Top-Level Entity** page, specify the working directory, project name, and top-level design entity name. Click **Next**.

- 4. In the **New Project Wizard: Add Files** page, select the existing design files (if any) you want to include in the project. Click **Next**.

- 5. In the **New Project Wizard: Family & Device Settings** page, select the device family and specific device you want to target for compilation. Click **Next**.

- 6. In the **EDA Tool Settings** page, select the EDA tools you want to use with the Intel Quartus Prime software to develop your project.

- 7. Review the summary of your chosen settings in the **New Project Wizard** window, then click **Finish** to complete the Intel Quartus Prime project creation.

#### 4.6. Parameterizing and Generating the IP

Refer to JESD204C Intel FPGA IP Parameters on page 35 for the IP parameter values and description.

- 1. In the IP Catalog (**Tools** ➤ **IP Catalog**), locate and double-click the JESD204C Intel FPGA IP.

- 2. Specify a top-level name for your custom IP variation. This name identifies the IP variation files in your project. If prompted, also specify the target Intel FPGA device family and output file HDL preference. Click **OK**.

- 3. After parameterizing the core, go to the Example Design tab and click **Generate Example Design** to create the simulation testbench. Skip to 5 if you do not want to generate the design example.

- 4. Set a name for your <example\_design\_directory> and click OK to generate supporting files and scripts. The testbench and scripts are located in the <example\_design\_directory>/ simulation folder.

The **Generate Example Design** option generates supporting files for the following entities:

- IP core design example for simulation—refer to *Generating and Simulating the Design Example* section in the respective design example user guides.

- IP core design example for synthesis—refer to Compiling the *JESD204C Design Example* section in the respective design example user guides.

- 5. Click **Finish** or **Generate HDL** to generate synthesis and other optional files matching your IP variation specifications. The parameter editor generates the top-level .ip, .qip or .qsys IP variation file and HDL files for synthesis and simulation.

The top-level IP variation is added to the current Intel Quartus Prime project. Click **Project > Add/Remove Files in Project** to manually add a .qip or .qsys file to a project. Make appropriate pin assignments to connect ports.

*Note:* Some parameter options are grayed out if they are not supported in a selected configuration or it is a derived parameter.

## 4.7. Compiling the JESD204C IP Design

Refer to the Designing with the JESD204C Intel FPGA IP on page 25 before compiling the JESD204C IP core design.

To compile your design, click **Start Compilation** on the Processing menu in the Intel Quartus Prime software. You can use the generated .ip or .qip file to include relevant files into your project.

#### **Related Information**

#### Intel Quartus Prime Help More information about compilation in Intel Quartus Prime software.

### 4.8. Programming an FPGA Device

After successfully compiling your design, program the targeted Intel device with the Intel Quartus Prime Programmer and verify the design in hardware. For instructions on programming the FPGA device, refer to the *Intel Quartus Prime Pro Edition User Guide: Programmer*.

intel

## 5. Designing with the JESD204C Intel FPGA IP

When designing with the JESD204C Intel FPGA IP, you need to take into account certain considerations to ensure a fully-functioning design. Follow the design guidelines provided.

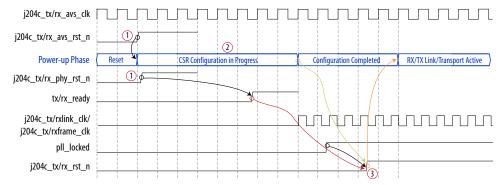

## 5.1. JESD204C TX and RX Reset Sequence

The JESD204C base core and transport layer require various resets for the IP and transceiver. All the resets in the core assert asynchronously and deassert synchronously.

#### Table 17.JESD204C IP Resets

| Reset Signal                                                | Clock Domain                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX/RX Link and Frame Reset                                  | TX/RX link clock                                                            | You can deassert the link and frame reset after the     configuration phase completes                                                                                                                                                                                                                                                                                                                                                                                                   |

| j204c_tx_rst_n<br>j204c_rx_rst_n                            | TX/RX frame clock                                                           | <ul> <li>configuration phase completes.</li> <li>After this reset deasserts, the JESD204C IP is in operation mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                           |

| TX/RX PHY Reset<br>j204c_tx_phy_rst_n<br>j204c_rx_phy_rst_n | Transceiver Native PHY clock                                                | <ul> <li>The transceiver requires this reset to reset the PMA and PCS blocks.</li> <li>Intel recommends that you assert the link and frame reset when this reset asserts.</li> </ul>                                                                                                                                                                                                                                                                                                    |

| TX/RX AVS Reset<br>j204c_tx_avs_rst_n<br>j204c_rx_avs_rst_n | TX/RX Avalon-MM reset for<br>CSR<br>(j204c_tx_avs_clk/<br>j204c_rx_avs_clk) | <ul> <li>This reset is for the Avalon-MM slave interface, which consists of the Configuration and Status Register (CSR) blocks.</li> <li>This reset must deassert first before the JESD204C IP link reset and frame reset deassert.</li> <li>After this reset deasserts, configuration phase starts. You can program the CSR register values if a non-default value is required.</li> <li>Intel recommends that you assert the link and frame reset when this reset asserts.</li> </ul> |

#### Figure 7. JESD204C TX/RX Reset Sequence

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

ISO 9001:2015 Registered

The descriptions below correspond to the Figure 7 on page 25:

- 1. The sequence begins when the TX/RX AVS reset and TX/RX PHY reset deassert.

- 2. During the configuration phase, you can configure the run-time CSR parameters. The number of clock cycles does not matter provided that j204c\_tx\_rst\_n/ j204c\_rx\_rst\_n remains asserted.

- 3. j204c\_tx\_rst\_n/j204c\_rx\_rst\_n only deasserts after configuration phase, and when the PLL is locked and the transceiver is ready. Internally, in the JESD204C IP, j204c\_tx\_rst\_n/j204c\_rx\_rst\_n synchronizes to the respective clock domains. You can assert j204c\_tx\_rst\_n/j204c\_rx\_rst\_n at any time after its initial deassertion, but when you deassert, make sure the configuration phase is over, the PLL is locked, and the transceiver is ready.

### **5.2. Configuration Phase**

Before the hardware reset deasserts, if you want to make any changes to your JESD204C IP configuration, you have to make the changes during the configuration phase.

The configuration phase is the only right phase to change the configuration because all configuration registers are quasi-static in nature and stable before the IP comes out of reset. The known exception to this rule is the SYSREF control registers.

If you want to make a change in the link configuration, such as disable interrupts, during mid-operation, you must always do a link re-initialization.

### 5.3. Link Reinitialization

The JESD204C IP implements a simple synchronous clear to all data and control logics during link reinitialization.

Link reinitialization occurs in two ways:

- You manually trigger link reinitialization by setting the link\_reinit bit. The hardware clears the link\_reinit and reinit\_in\_prog bits when link reinitialization completes.

- The hardware automatically triggers link reinitialization because of errors. You have full control, through the tx\_err and rx\_err registers, to set the specific type of errors to trigger link reinitialization automatically. The hardware clears the reinit\_in\_prog bit when link reinitialization completes.

- *Note:* Link reinitialization does not initiate SYSREF re-detection. Use the sysref\_singledet bit to re-detect SYSREF edge. Link reinitialization affects only the transport layer and link layer; the CSR, transceiver, and the PHY-related logics are not affected.

## **5.4.** SYSREF Sampling

You can choose to enable continuous SYSREF sampling or a single SYSREF detection.

The software logic programs the clock cleaner to the SPI to enable SYSREF generation. To resample SYSREF, the software logic writes to the SYSREF\_CTRL registers to enable either a continuous sampling or a single detection. If both bits are enabled, continuous sampling takes precedence.

You may want to disable SYSREF sampling after some time. Disabling SYSREF sampling also disables the continuous sampling mode, and subsequently programs the clock cleaner to disable SYSREF output.

Consider one of the following recommendations to configure the SYSREF resampling flow:

- Set the sysref\_singledet, sysref\_alwayson, and sysref\_lemc\_err\_en\_reinit register bits to 1.

- If a new SYSREF edge is detected, the JESD204C IP clears the sysref\_singledet bit and automatically starts a link reinitialization.

- All the Avalon-ST interface signals return to default state.

- The LEMC block resets to reflect the newly detected SYSREF edge.

- All the Avalon-ST interface signals are active again based on a new LEMC data.

- If LEMC error interrupt is enabled, the JESD204C needs to service and clear the error.

- 2. Set the sysref\_singledet bit to 1 and sysref\_alwayson bit to 0.

- If a new SYSREF edge is detected, the JESD204C IP clears the sysref\_singledet bit, but no automatic start of link reinitialization.

- All the Avalon-ST interface signals remain active.

- The LEMC block resets to reflect the newly detected SYSREF edge.

- In the TX IP, the egress sync header (SH) adjusts as LEMC undergoes realignment to the new SYSREF edge. The corresponding RX (that receives the adjusted SH) may subject to SH-related errors.

- In the RX IP, the ingress Avalon-ST data does not get affected because the change of LEMC does not impact the already streaming data. However, the link loses its deterministic latency characteristic. To restore the deterministic latency behavior, a link reinitialization is required.

- You must set the link\_reinit bit to 1 after sysref\_singledet clears to start a link reinitialization.

- All the Avalon-ST interface signals return to default state, and get reactivated based on a new LEMC data.

To better handle the racing between the assertion of the link\_reinit bit (through user-specified or auto reinitialization) and the assertion of the sysref\_singledet bit, the IP imposes the following behavior:

- For TX core: If the the link\_reinit bit asserts), the Avalon-ST interface deactivates. After the link reinitialization is complete, the Avalon-ST gets activated only when the sysref\_singledet deasserts.

- For RX core: If the the link\_reinit bit asserts, the Avalon-ST interface deactivates. After the link reinitialization is complete, the Avalon-ST gets activated only when the sysref\_singledet deasserts, and SH (j204c\_rx\_sh\_lock) and EMB (j204c\_rx\_emb\_lock) have achieved lock.

## 5.5. Interrupt and Error Handling

The JESD204C IP interrupts the processor when there are errors or reinitialization requests in the design. The interrupts are peripheral and level sensitive.

The IP holds a level-sensitive interrupt signal asserted until the peripheral deasserts the interrupt signal. When the level-sensitive interrupt is high, the state of the interrupt in the Interrupt Controller is pending or active pending. If the peripheral deasserts the interrupt signal for any reason, the Interrupt Controller removes the pending state from the interrupt.

Every error condition in the JESD204C IP latches on the error status and keeps the interrupt signal asserted until the error is serviced and the ISR writes a 1 to clear the error status.

When interrupt is asserted and fulfills the Interrupt Controller configuration (e.g. priority, interrupt IDs), the processor jumps to the Interrupt Service Routine (ISR) to execute the routine.