# **CPRI v6.0 IP Core User Guide**

Last updated for Quartus Prime Design Suite: 17.0 IR3, 17.0, 17.0 Update 1,

Send Feedback

17.0 Update 2 UG-20008 2019.01.02

101 Innovation Drive San Jose, CA 95134 www.altera.com

## Contents

| About the CPRI v6.0 IP Core                                               | 1-1  |

|---------------------------------------------------------------------------|------|

| CPRI v6.0 IP Core Supported Features                                      |      |

| CPRI v6.0 IP Core Device Family and Speed Grade Support                   |      |

| Device Family Support                                                     |      |

| CPRI v6.0 IP Core Performance: Device and Transceiver Speed Grade Support |      |

| IP Core Verification                                                      |      |

| Resource Utilization for CPRI v6.0 IP Cores                               | 1-6  |

| Release Information                                                       | 1-8  |

| Getting Started with the CPRI v6.0 IP Core                                | 2-1  |

| Installation and Licensing                                                |      |

| Generating CPRI v6.0 IP Cores                                             |      |

| CPRI v6.0 IP Core File Structure                                          |      |

| CPRI v6.0 IP Core Parameters                                              |      |

| Integrating Your IP Core in Your Design: Required External Blocks         |      |

| Adding the Transceiver TX PLL IP Core                                     |      |

| Adding the Reset Controller                                               |      |

| Adding the Transceiver Reconfiguration Controller                         |      |

| Adding the Off-Chip Clean-Up PLL                                          |      |

| Adding and Connecting the Single-Trip Delay Calibration Blocks            |      |

| Simulating Intel FPGA IP Cores                                            |      |

| Understanding the Testbench                                               | 2-26 |

| Running the Testbench                                                     | 2-26 |

| Compiling the Full Design and Programming the FPGA                        | 2-28 |

| Functional Description                                                    | 3-1  |

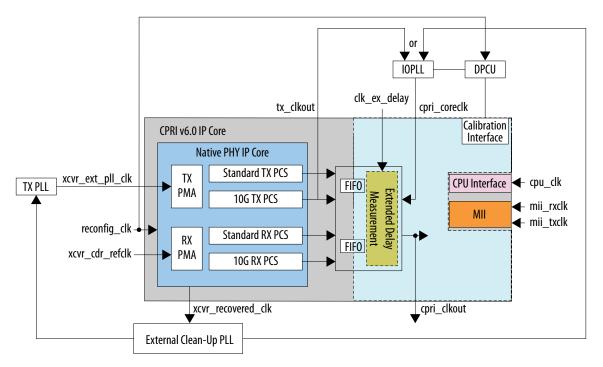

| Interfaces Overview                                                       |      |

| CPRI v6.0 IP Core Clocking Structure                                      |      |

| Example CPRI v6.0 Clock Connections in Different Clocking Modes           |      |

| CPRI v6.0 IP Core Reset Requirements                                      |      |

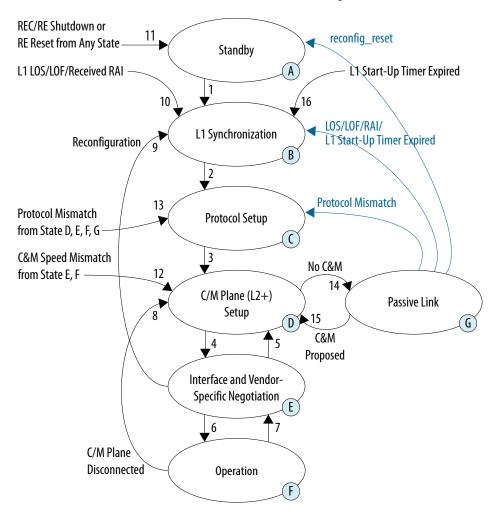

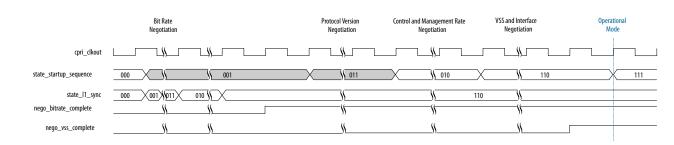

| Start-Up Sequence Following Reset                                         |      |

| Start-Up Sequence Interface Signals                                       |      |

| AUX Interface                                                             |      |

| AUX Interface Signals                                                     | 3-18 |

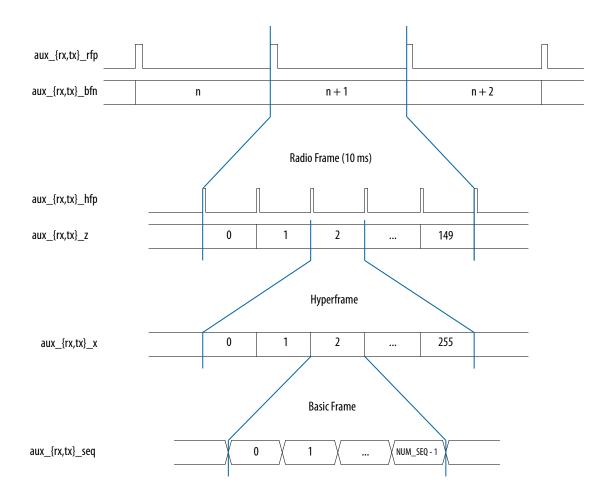

| AUX Interface Synchronization                                             |      |

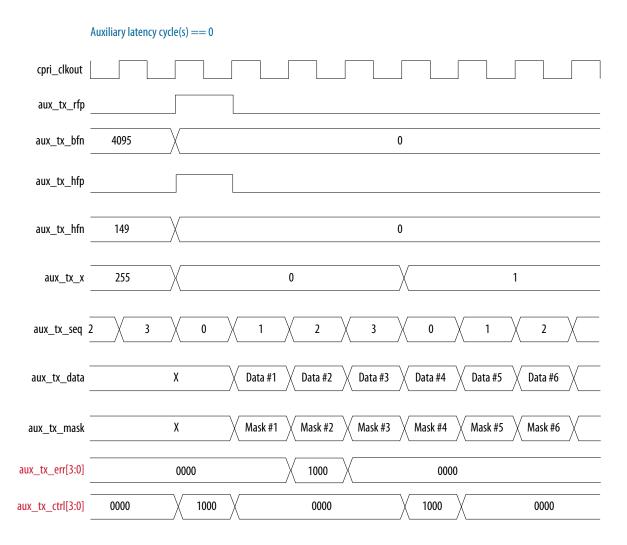

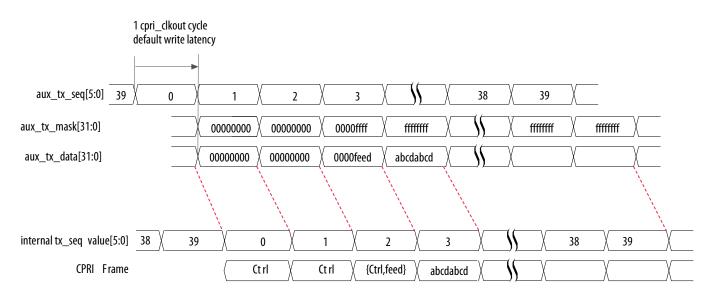

| Auxiliary Latency Cycles                                                  |      |

| Direct Interface CPRI Frame Data Format                                   | 3-28 |

| Direct IQ Interface                                                       |      |

| Ctrl_AxC Interface                                                        |      |

| Direct Vendor Specific Access Interface                                   |      |

| Real-Time Vendor Specific Interface                                       | 3-36 |

| то | C-3 |

|----|-----|

|----|-----|

| Direct HDLC Serial Interface                                                    |                                        |

|---------------------------------------------------------------------------------|----------------------------------------|

| Direct L1 Control and Status Interface                                          |                                        |

| L1 Debug Interface                                                              |                                        |

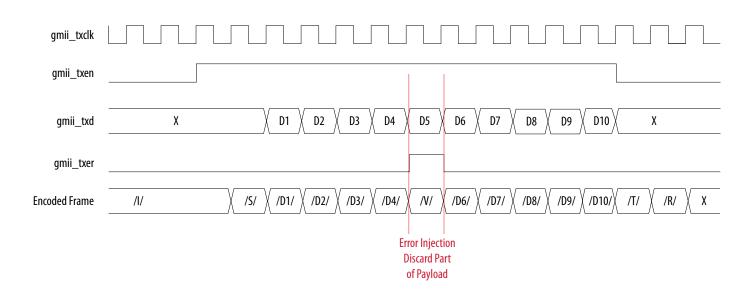

| Media Independent Interface (MII) to External Ethernet Block                    |                                        |

| Gigabit Media Independent Interface (GMII) to External Ethernet Block           |                                        |

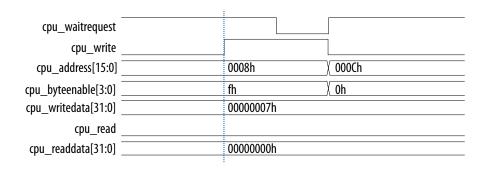

| CPU Interface to CPRI v6.0 IP Core Registers                                    |                                        |

| CPU Interface Signals                                                           |                                        |

| Accessing the Hyperframe Control Words                                          |                                        |

| Auto-Rate Negotiation                                                           |                                        |

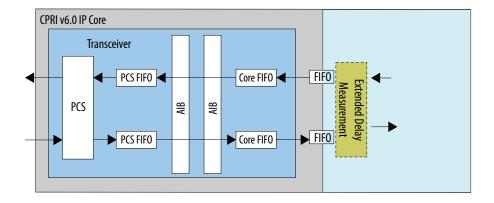

| Extended Delay Measurement                                                      |                                        |

| Extended Delay Measurement for Soft Internal Buffers                            |                                        |

| Extended Delay Measurement for Intel Stratix 10 Hard FIFOs                      |                                        |

| Extended Delay Measurement Interface                                            |                                        |

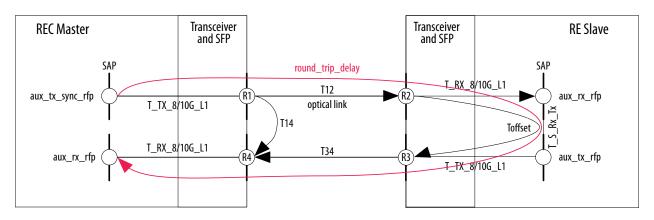

| Deterministic Latency and Delay Measurement and Calibration                     |                                        |

| Delay Measurement and Calibration Features                                      |                                        |

| Delay Requirements                                                              |                                        |

| Single-Hop Delay Measurement                                                    |                                        |

| Multi-Hop Delay Measurement                                                     |                                        |

| Delay Calibration Features                                                      |                                        |

| CPRI v6.0 IP Core Transceiver and Transceiver Management Interfaces             |                                        |

| CPRI Link                                                                       |                                        |

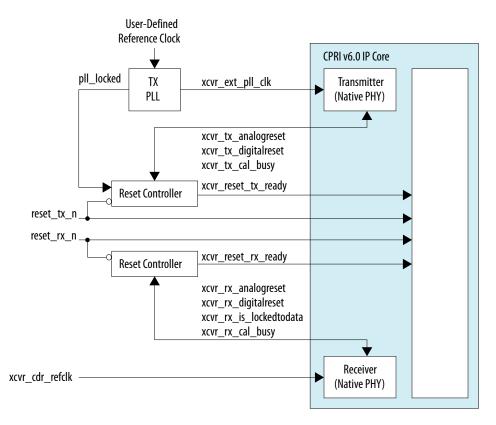

| Main Transceiver Clock and Reset Signals                                        |                                        |

| Arria V, Arria V GZ, Cyclone V, and Stratix V Transceiver Reconfiguration Inter |                                        |

| Intel Arria 10 and Intel Stratix 10 Transceiver Reconfiguration Interface       |                                        |

| Interface to the External Reset Controller                                      |                                        |

| Interface to the External PLL.                                                  |                                        |

| Transceiver Debug Interface                                                     |                                        |

| Testing Features                                                                |                                        |

| CPRI v6.0 IP Core Loopback Modes                                                |                                        |

| CPRI v6.0 IP Core Self-Synchronization Feature                                  |                                        |

|                                                                                 |                                        |

| CPRI v6.0 IP Core Signals                                                       |                                        |

| CPRI v6.0 IP Core L2 Interface                                                  |                                        |

| CPRI v6.0 IP Core L1 Direct Access Interfaces                                   |                                        |

| CPRI v6.0 IP Core Management Interfaces                                         |                                        |

| CPRI v6.0 IP Core Transceiver and Transceiver Management Signals                |                                        |

| of Revenues of the sole franscerver and franscerver management orginals         | ······································ |

| CPRI v6.0 IP Core Registers                                                     | 5-1                                    |

| INTR Register                                                                   |                                        |

| L1_STATUS Register                                                              |                                        |

| L1_CONFIG Register                                                              |                                        |

| BIT_RATE_CONFIG Register                                                        |                                        |

| PROT_VER Register                                                               |                                        |

| TX_SCR Register                                                                 |                                        |

| RX_SCR Register                                                                 |                                        |

| CM_CONFIG Register                                                              |                                        |

| CM_STATUS Register                                                              |                                        |

|                                                                                 |                                        |

| START_UP_SEQ Register                            | 5-9  |

|--------------------------------------------------|------|

| START_UP_SEQ Register<br>START_UP_TIMER Register | 5-11 |

| FLSAR Register                                   |      |

| CTRL_INDEX Register                              |      |

| TX_CTRL Register                                 | 5-13 |

| RX_CTRL Register                                 |      |

| RX_ERR Register                                  |      |

| RX_BFN Register                                  | 5-14 |

| LOOPBACK Register                                | 5-15 |

| TX_DELAY Register                                | 5-16 |

| RX_DELAY Register                                | 5-17 |

| TX_EX_DELAY Register                             |      |

| RX_EX_DELAY Register                             |      |

| ROUND_TRIP_DELAY Register                        | 5-19 |

| XCVR_BITSLIP Register                            |      |

| DELAY_CAL_STD_CTRL1 Register                     |      |

| DELAY_CAL_STD_CTRL2 Register                     |      |

| DELAY_CAL_STD_CTRL3 Register                     |      |

| DELAY_CAL_STD_CTRL4 Register                     |      |

| DELAY_CAL_STD_CTRL5 Register                     |      |

| DELAY_CAL_STD_STATUS Register                    | 5-24 |

| DELAY_CAL_RTD Register                           |      |

| XCVR_TX_FIFO_DELAY Register                      | 5-25 |

| XCVR_RX_FIFO_DELAY Register                      |      |

| Additional Information                        | A-1 |

|-----------------------------------------------|-----|

| CPRI v6.0 IP Core User Guide Archives         |     |

| CPRI v6.0 IP Core User Guide Revision History |     |

## About the CPRI v6.0 IP Core

| 2019.01.02 |                         |  |

|------------|-------------------------|--|

| UG-20008   | Subscribe Send Feedback |  |

The Common Public Radio Interface (CPRI) v6.0 Intel<sup>®</sup> FPGA IP core implements the *CPRI Specification V6.0 (2013-08-30)*. CPRI is a high-speed serial interface for network radio equipment controllers (REC) to receive data from and provide data to remote radio equipment (RE).

The CPRI v6.0 IP core targets high-performance, remote, radio network applications. You can configure the CPRI v6.0 IP core as an RE or an REC.

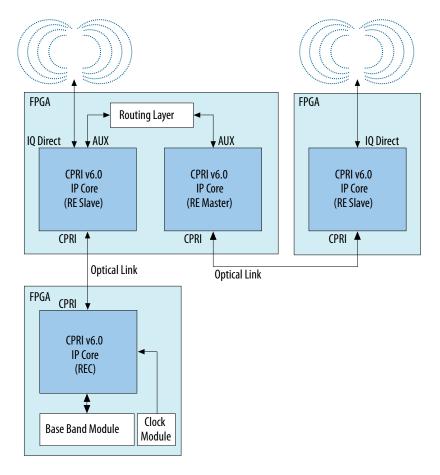

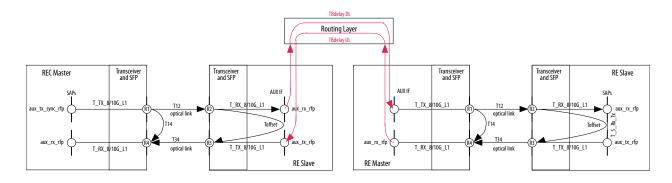

#### Figure 1-1: Typical CPRI Application on Intel FPGA Devices

Example system implementation with a two-hop daisy chain. Optical links between devices support high performance.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

e. 9001:2015 ly Registered

ISO

\*Other names and brands may be claimed as the property of others.

## **CPRI v6.0 IP Core Supported Features**

The CPRI v6.0 IP core offers the following features:

- Compliant with the *Common Public Radio Interface (CPRI) Specification V6.0 (2013-08-30) Interface Specification* available on the CPRI Industry Initiative website (www.cpri.info).

- Supports radio equipment controller (REC) and radio equipment (RE) module configurations.

- Supports the following CPRI link features:

- Configurable CPRI communication line bit rate (to 0.6144, 1.2288, 2.4576, 3.0720, 4.9152, 6.144, 8.11008, 9.8304, or 10.1376 Gbps) using Intel FPGA on-chip high-speed transceivers.

- CPRI line bit rate auto-rate negotiation support.

- Configurable and run-time programmable synchronization mode: master port or slave port on a CPRI link.

- Scrambling and descrambling at 8.11008 and 10.1376 Gbps.

- Optional scrambling and descrambling at 4.9152, 6.1440, and 9.8304 Gbps.

- Transmitter (Tx) and receiver (Rx) delay measurement and calibration.

- Optional support for single-trip delay calibration.

- Optional round-trip delay calibration.

- L1 link status and alarm (Z.130.0) control and status monitoring.

- Access to all Vendor Specific data.

- Diagnostic parallel reverse loopback paths.

- Diagnostic serial and parallel forward loopback paths.

- Diagnostic stand-alone slave testing mode.

- Includes the following interfaces:

- Register access interface to external or on-chip processor, using the Intel Avalon<sup>®</sup> Memory-Mapped (Avalon-MM) interconnect specification.

- Optional auxiliary (AUX) interface for full access to raw CPRI frame. Provides direct access to full radioframe, synchronizes the frame position with timing references, and enables routing application support from slave to master ports to implement daisy-chain topologies.

- Optional choice of IEEE 802.3 100BASE-X compliant 10/100 Mbps MII or 1000BASE-X compliant 1Gbps GMII for Ethernet frame access.

- Optional direct I/Q access interface enables integration of all user-defined air standard I/Q mapping schemes.

- Optional external I/Q mapper and demapper modules with reference design support.

- Optional external I/Q compression and decompression modules with reference design support.

- Optional vendor specific data access interfaces provide direct access to Vendor Specific (VS), Control AxC (Ctrl\_AxC), and Real-time Vendor Specific (RTVS) subchannels.

- Optional HDLC serial interface provides direct access to slow control and management subchannels.

- Optional L1 inband interface provides direct access to Z.130.0 link status and alarm control word.

#### **Related Information**

#### • CPRI Industry Initiative website

For a detailed specification of the CPRI protocol refer to the *CPRI Specification V6.0 (2013-08-30) Interface Specification* available on the CPRI Industry Initiative website.

- Altera wiki CPRI v6.0 IP core information Includes links to the I/Q mapper and other CPRI v6.0 IP core reference designs.

- Intel FPGA Design Store Includes CPRI v6.0 reference designs.

## CPRI v6.0 IP Core Device Family and Speed Grade Support

The following sections list the device family and device speed grade support offered by the CPRI v6.0 IP core:

#### **Device Family Support**

| lable | I-I: Intel FF | GA IP COR | e Device | Support Levels |  |

|-------|---------------|-----------|----------|----------------|--|

|       |               |           |          |                |  |

| Device Support Level | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance              | The IP core is available for simulation and compila-<br>tion for this device family. Timing models include<br>initial engineering estimates of delays based on early<br>post-layout information. The timing models are<br>subject to change as silicon testing improves the<br>correlation between the actual silicon and the<br>timing models. You can use this IP core for system<br>architecture and resource utilization studies,<br>simulation, pinout, system latency assessments,<br>basic timing assessments (pipeline budgeting), and<br>I/O transfer strategy (datapath width, burst depth, I/<br>O standards tradeoffs). |

| Preliminary          | Intel has verified the IP core with preliminary<br>timing models for this device family. The IP core<br>meets all functional requirements, but might still be<br>undergoing timing analysis for the device family. It<br>can be used in production designs with caution.                                                                                                                                                                                                                                                                                                                                                            |

| Final                | Intel has verified the IP core with final timing<br>models for this device family. The IP core meets all<br>functional and timing requirements for the device<br>family and can be used in production designs.                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### Table 1-2: CPRI v6.0 IP Core Device Family Support

Shows the level of support offered by the CPRI v6.0 IP core for each Intel FPGA device family.

About the CPRI v6.0 IP Core

| Device Family                 | Support                                                                                                                                                                                                                                                                                                                    |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel Stratix <sup>®</sup> 10 | Advance                                                                                                                                                                                                                                                                                                                    |

|                               | Intel Stratix 10 device support is available only in<br>the Intel Quartus <sup>®</sup> Prime Pro Edition software v17.0<br>IR3. It is not available in software releases 17.0, 17.0<br>Update 1, and 17.0 Update 2. The software release<br>v17.0 IR3 supports only L-tile devices.                                        |

| Intel Arria <sup>®</sup> 10   | Default support level provided in the Intel Quartus<br>Prime software. Refer to the <i>Quartus Prime</i><br><i>Standard Edition Software and Device Support</i><br><i>Release Notes</i> and the <i>Quartus Prime Pro Edition</i><br><i>Software and Device Support Release Notes</i> for the<br>relevant software release. |

| Arria V (GX and GT)           | Default support level provided in Intel Quartus<br>Prime Standard Edition software. Refer to the<br><i>Quartus Prime Standard Edition Software and</i><br><i>Device Support Release Notes</i> for the relevant<br>software release.                                                                                        |

| Arria V GZ                    | Default support level provided in Intel Quartus<br>Prime Standard Edition software. Refer to the<br><i>Quartus Prime Standard Edition Software and</i><br><i>Device Support Release Notes</i> for the relevant<br>software release.                                                                                        |

| Cyclone V (GX and GT)         | Default support level provided in Intel Quartus<br>Prime Standard Edition software. Refer to the<br><i>Quartus Prime Standard Edition Software and</i><br><i>Device Support Release Notes</i> for the relevant<br>software release.                                                                                        |

| Stratix V (GX and GT)         | Default support level provided in Intel Quartus<br>Prime Standard Edition software. Refer to the<br><i>Quartus Prime Standard Edition Software and</i><br><i>Device Support Release Notes</i> for the relevant<br>software release.                                                                                        |

| Other device families         | No support                                                                                                                                                                                                                                                                                                                 |

#### **Related Information**

• CPRI v6.0 IP Core Performance: Device and Transceiver Speed Grade Support on page 1-5

About the CPRI v6.0 IP Core

Reports the default device support levels in the current version of the Intel Quartus Prime Standard Edition software.

**Timing and Power Models** ٠ Reports the default device support levels in the current version of the Intel Quartus Prime Pro Edition software.

### CPRI v6.0 IP Core Performance: Device and Transceiver Speed Grade Support

#### Table 1-3: Slowest Supported Device Speed Grade and Supported Transceiver Speed Grade

Lower device speed grade numbers correspond to faster devices. The entry -x indicates that both the industrial speed grade Ix and the commercial speed grade Cx are supported for this device family and CPRI line bit rate. Table entries show slowest supported device speed grade / supported transceiver speed grade.

| Dovice Family       |                        | CPRI Line Bit Rate (Gbps)      |         |         |         |        |         |        |         |

|---------------------|------------------------|--------------------------------|---------|---------|---------|--------|---------|--------|---------|

| Device Family       | 0.6144                 | 1.2288                         | 2.4576  | 3.072   | 4.9152  | 6.1440 | 8.11008 | 9.8304 | 10.1376 |

| Intel<br>Stratix 10 | (1)                    | -2 / -3                        |         |         |         |        |         |        |         |

| Intel Arria<br>10   | (1)                    |                                | -3 / -4 |         |         |        |         |        |         |

| Stratix V<br>GT     |                        | -3 / H3 -2 / H2                |         |         |         |        |         |        |         |

| Stratix V<br>GX     |                        | -4 / H3 -2 / H2                |         |         |         |        |         |        |         |

| Arria V<br>GZ       |                        | -4 / H3 -3 / H2 <sup>(1)</sup> |         |         |         | (1)    |         |        |         |

| Arria V<br>GX       | -6 / H6                |                                |         | -5 / H4 | -5 / H4 |        | (1)     |        |         |

| Arria V<br>GT       | -5/H3                  |                                |         | •       | -       |        | (1)     |        |         |

| Cyclone V<br>GT     | -7 / H5 <sup>(1)</sup> |                                |         |         |         |        |         |        |         |

| Cyclone V<br>GX     | -8 / H7 -7 / H6        |                                |         |         |         | (1)    |         |        |         |

About the CPRI v6.0 IP Core

1-5

<sup>&</sup>lt;sup>(1)</sup> The CPRI v6.0 IP core does not support this CPRI line bit rate for this device family.

## **IP Core Verification**

To ensure functional correctness of the CPRI v6.0 IP core, Intel performs extensive validation through both simulation and hardware testing. Before releasing a version of the CPRI v6.0 IP core, Intel runs comprehensive regression tests in the associated version of the Intel Quartus Prime software.

#### **Related Information**

- Knowledge Base Errata for CPRI v6.0 IP core Some exceptions to functional correctness are documented in the CPRI v6.0 IP core errata.

- Altera wiki CPRI v6.0 Errata page Other exceptions to functional correctness are documented on the Altera wiki CPRI v6.0 Errata page.

## **Resource Utilization for CPRI v6.0 IP Cores**

Resource utilization changes depending on the parameter settings you specify in the CPRI v6.0 parameter editor. For example, with every additional interface you enable, the IP core requires additional resources to implement the module that supports that interface.

The resource utilization numbers are approximate as the Intel Quartus Prime Fitter assigns resources based on the entirety of your design. The numbers below result from a single run on a simple design. Your results may vary.

#### Table 1-4: Minimum and Maximum IP Core Variations for Resource Utilization Reporting

The IP core FPGA resource utilization table reports resource utilization for a minimum IP core variation and a maximum IP core variation. Parameters not specified remain at their default values, or their values do not affect resource utilization.

| Parameter                                                                         | Minimum Variation                                                                                                                                                         | Maximum Variation                          |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Line bit rate                                                                     | <ul><li>1.2288 Gbps for target device<br/>in the Intel Arria 10 and Intel<br/>Stratix 10 device families,</li><li>0.6144 Gbps for all other<br/>device families</li></ul> | Maximum bit rate (device family dependent) |

| Synchronization mode                                                              | Master                                                                                                                                                                    | Master                                     |

| Operation mode                                                                    | TX/RX Duplex                                                                                                                                                              | TX/RX Duplex                               |

| Core clock source input                                                           | Internal                                                                                                                                                                  | Internal                                   |

| Receiver soft buffer depth                                                        | 4                                                                                                                                                                         | 8                                          |

| Auxiliary and direct<br>interfaces write latency<br>cycle(s)                      |                                                                                                                                                                           | 9                                          |

| Enable interface, for all<br>optional direct interfaces in<br>the L1 Features tab | Off                                                                                                                                                                       | On                                         |

About the CPRI v6.0 IP Core

| Parameter                                    | Minimum Variation | Maximum Variation |

|----------------------------------------------|-------------------|-------------------|

| Ethernet PCS interface                       | NONE              | GMII              |

| L2 Ethernet PCS Tx/Rx<br>FIFO depth          | _                 | 11                |

| Enable single-trip delay calibration         | Off               | Off               |

| Enable round-trip delay calibration          | Off               | On                |

| Round-trip delay calibra-<br>tion FIFO depth | _                 | 4                 |

#### Table 1-5: IP Core FPGA Resource Utilization

Lists the resources and expected performance for minimum and maximum variations of the CPRI v6.0 IP core in each supported device family.

These results were obtained using the Intel Quartus Prime v17.0 IR3 software on an Intel Stratix 10 device, and using the Intel Quartus Prime v17.0 software for all other target device families.

- The numbers of ALMs and logic registers are rounded up to the nearest 100.

- The numbers of ALMs, before rounding, are the **ALMs needed** numbers from the Intel Quartus Prime Fitter Report.

| Intel Stratix 10 Device (with L-Tile Transceivers) | ALMs | Logic Registers | M20K Blocks |

|----------------------------------------------------|------|-----------------|-------------|

| Minimum (1.2288 Gbps CPRI line bit rate)           | 1100 | 1600            | 2           |

| Maximum (10.1376 Gbps CPRI line bit rate)          | 4000 | 5100            | 23          |

| Intel Arria 10 Device                              | ALMs | Logic Registers | M20K Blocks |

| Minimum (1.2288 Gbps CPRI line bit rate)           | 700  | 1400            | 2           |

| Maximum (10.1376 Gbps CPRI line bit rate)          | 4000 | 5000            | 24          |

| Arria V GX or GT Device                            | ALMs | Logic Registers | M10K Blocks |

| Minimum (0.6144 Gbps CPRI line bit rate)           | 700  | 1300            | 3           |

| Maximum (6.144 Gbps CPRI line bit rate)            | 3300 | 4800            | 39          |

| Arria V GZ Device                                  | ALMs | Logic Registers | M20K Blocks |

| Minimum (0.6144 Gbps CPRI line bit rate)           | 700  | 1400            | 2           |

| Maximum (9.8304 Gbps CPRI line bit rate)           | 3700 | 5000            | 21          |

About the CPRI v6.0 IP Core

**Altera Corporation**

1-8

| Cyclone V GX or GT Device                 | ALMs | Logic Registers | M10K Blocks |

|-------------------------------------------|------|-----------------|-------------|

| Minimum (0.6144 Gbps CPRI line bit rate)  | 700  | 1400            | 2           |

| Maximum (4.9512 Gbps CPRI line bit rate)  | 4100 | 5800            | 27          |

| Stratix V GX or GT Device                 | ALMs | Logic Registers | M20K Blocks |

| Minimum (0.6144 Gbps CPRI line bit rate)  | 700  | 1400            | 2           |

| Maximum (10.1376 Gbps CPRI line bit rate) | 3700 | 5500            | 20          |

#### **Related Information**

#### Fitter Resources Reports in the Intel Quartus Prime Help

Information about Intel Quartus Prime resource utilization reporting, including ALMs needed.

## **Release Information**

#### Table 1-6: CPRI v6.0 IP Core Current Release Information

| Item                                               | Description                                      |

|----------------------------------------------------|--------------------------------------------------|

| Compatible Intel Quartus Prime<br>Software Version | 17.0 IR3, 17.0, 17.0 Update 1, and 17.0 Update 2 |

| Release Date                                       | 2017.08.07                                       |

| Ordering Codes                                     | IP-CPRI-V6                                       |

About the CPRI v6.0 IP Core

## Getting Started with the CPRI v6.0 IP Core

Explains how to install, parameterize, and simulate the CPRI v6.0 IP core.

#### Installation and Licensing on page 2-2

The CPRI v6.0 IP core is an extended FPGA IP core which is not included with the Intel Quartus Prime release. This section provides a general overview of the Intel extended FPGA IP core installation process to help you quickly get started with any Intel extended FPGA IP core.

#### Generating CPRI v6.0 IP Cores on page 2-3

After you install and integrate the extended IP core in the ACDS release, the CPRI v6.0 IP core supports the standard customization and generation process. This IP core does not generate a testbench or example design simultaneously with generation of the IP core. Instead, you must use the Example Design button in the CPRI v6.0 parameter editor to generate the testbench. This IP core is not supported in Qsys.

#### CPRI v6.0 IP Core File Structure on page 2-3

The Intel Quartus Prime software generates the following IP core output file structure.

#### CPRI v6.0 IP Core Parameters on page 2-7

The CPRI v6.0 parameter editor provides the parameters you can set to configure the CPRI v6.0 IP core and simulation testbench.

#### Integrating Your IP Core in Your Design: Required External Blocks on page 2-17

You must connect your CPRI v6.0 IP core to some additional required design components. Your design can simulate and compile without some of these connections and logical blocks, but it will not function correctly in hardware unless all of them are present and connected in your design.

#### Simulating Intel FPGA IP Cores on page 2-25

The Intel Quartus Prime software supports RTL- and gate-level design simulation of Intel FPGA IP cores in supported EDA simulators. Simulation involves setting up your simulator working environment, compiling simulation model libraries, and running your simulation.

**Understanding the Testbench** on page 2-26 Intel provides a demonstration testbench with the CPRI v6.0 IP core.

Running the Testbench on page 2-26

To run the CPRI v6.0 IP core demonstration testbench, follow these steps.

Compiling the Full Design and Programming the FPGA on page 2-28

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

#### 2-2 Installation and Licensing

#### **Related Information**

#### Introduction to Intel FPGA IP IP Cores

Additional information about generating an Intel FPGA IP core and integrating it in your Intel Quartus Prime project.

## Installation and Licensing

The CPRI v6.0 IP core is an extended FPGA IP core which is not included with the Intel Quartus Prime release. This section provides a general overview of the Intel extended FPGA IP core installation process to help you quickly get started with any Intel extended FPGA IP core.

The Intel extended FPGA IP cores are available from the Altera Self-Service Licensing Center (SSLC). Refer to Related Information below for the correct link for this IP core.

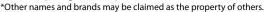

#### Figure 2-1: IP Core Installation Directory Structure

Directory structure after you install the CPRI v6.0 IP core.

#### Table 2-1: IP Core Installation Locations

| Location                                                                                   | Software                                | Platform |

|--------------------------------------------------------------------------------------------|-----------------------------------------|----------|

| <pre><drive>:\intelFPGA_pro\<version>\ quartus\ip\altera_cloud</version></drive></pre>     | Intel Quartus Prime Pro<br>Edition      | Windows* |

| <pre><drive>:\intelFPGA\<version>\quartus\ ip\altera_cloud</version></drive></pre>         | Intel Quartus Prime<br>Standard Edition | Windows  |

| <home directory="">:/intelFPGA_pro/<br/><version>/quartus/ip/altera_cloud</version></home> | Intel Quartus Prime Pro<br>Edition      | Linux*   |

| <home directory="">:/intelFPGA/<version><br/>/quartus/ip/altera_cloud</version></home>     | Intel Quartus Prime<br>Standard Edition | Linux    |

#### **Related Information**

• Intel FPGA website

2-3

#### • Self-Service Licensing Center (SSLC)

After you purchase the CPRI v6.0 IP core, the IP core is available for download from the SSLC page in your myAltera account. You must create a myAltera account if you do not have one already, and log in to access the SSLC. On the SSLC page, click Run for this IP core. The SSLC provides an installation dialog box to guide your installation of the IP core.

## **Generating CPRI v6.0 IP Cores**

You can quickly configure a custom IP variation in the parameter editor. Use the following steps to specify CPRI v6.0 IP core options and parameters in the parameter editor.

- 1. In the IP Catalog (Tools > IP Catalog), locate and double-click the name CPRI v6.0. The parameter editor appears.

- 2. Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation settings in a file named *<your\_ip*.gsys (in Intel Quartus Prime Standard Edition) or *<your\_ip*.ip (in Intel Quartus Prime Pro Edition). Click **OK**.

- **3.** Specify the parameters and options for your IP variation in the parameter editor, including one or more of the following. Refer to "IP Core Parameters" for information about specific IP core parameters.

- Specify parameters defining the IP core functionality, port configurations, and device-specific features.

- Specify options for processing the IP core files in other EDA tools.

- 4. Click Generate HDL. The Generation dialog box appears.

- **5.** Specify output file generation options, and then click **Generate**. The IP variation files generate according to your specifications.

- **6.** To generate a simulation testbench, click **Generate Example Design**. Please refer to the instructions in the *Running the Testbench* section.

- 7. To generate an HDL instantiation template that you can copy and paste into your text editor, click Generate > Show Instantiation Template.

- 8. Click Finish. The parameter editor adds the top-level .qsys or .ip file to the current project automatically. If you are prompted to manually add the .qsys file to the project, click **Project** > **Add/Remove Files in Project** to add the file.

- **9.** After generating and instantiating your IP variation, make appropriate pin assignments to connect ports.

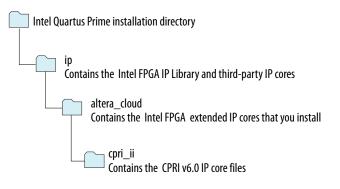

## **CPRI v6.0 IP Core File Structure**

The Intel Quartus Prime software generates the following IP core output file structure.

Altera Corporation

#### Table 2-2: IP Core Generated Files

| File Name                                                                | Description                                                                    |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| <your_ip>.gsys (Intel Quartus<br/>Prime Standard Edition only)</your_ip> | The Qsys system or top-level IP variation file. < <i>your_ip</i> > is the name |

| <pre><your_ip>.ip (Intel Quartus Prime Pro Edition only)</your_ip></pre> | that you give your IP variation.                                               |

Getting Started with the CPRI v6.0 IP Core

UG-20008 2019.01.02

2-5

| File Name                                     | Description                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <system>.sopcinfo</system>                    | Describes the connections and IP component parameterizations in<br>your Qsys system. You can parse its contents to get requirements<br>when you develop software drivers for IP components. (Intel Quartus<br>Prime Standard Edition only)                                                                                                                             |

|                                               | Downstream tools such as the Intel Nios <sup>®</sup> II tool chain use this file.<br>The .sopcinfo file and the system.h file generated for the Nios II<br>tool chain include address map information for each slave relative to<br>each master that accesses the slave. Different masters may have a<br>different address map to access a particular slave component. |

| <your_ip>.cmp</your_ip>                       | The VHDL Component Declaration ( <b>.cmp</b> ) file is a text file that contains local generic and port definitions that you can use in VHDL design files.                                                                                                                                                                                                             |

| <your_ip>.html</your_ip>                      | A report that contains connection information, a memory map<br>showing the address of each slave with respect to each master to<br>which it is connected, and parameter assignments.                                                                                                                                                                                   |

| <pre><your_ip>_generation.rpt</your_ip></pre> | IP or Qsys generation log file. A summary of the messages during IP generation.                                                                                                                                                                                                                                                                                        |

| <pre><your_ip>.debuginfo</your_ip></pre>      | Contains post-generation information. Used to pass System Console<br>and Bus Analyzer Toolkit information about the Qsys interconnect.<br>The Bus Analysis Toolkit uses this file to identify debug components<br>in the Qsys interconnect. (Intel Quartus Prime Standard Edition only)                                                                                |

| <your_ip>.qgsimc</your_ip>                    | Lists simulation parameters to support incremental regeneration.<br>(Intel Quartus Prime Pro Edition only)                                                                                                                                                                                                                                                             |

| <pre><your_ip>.qgsynthc</your_ip></pre>       | Lists synthesis parameters to support incremental regeneration. (Intel<br>Quartus Prime Pro Edition only)                                                                                                                                                                                                                                                              |

| <your_ip>.qip</your_ip>                       | Contains all the required information about the IP component to integrate and compile the IP component in the Quartus Prime software.                                                                                                                                                                                                                                  |

| <your_ip>.csv</your_ip>                       | Contains information about the upgrade status of the IP component.                                                                                                                                                                                                                                                                                                     |

| <your_ip>.bsf</your_ip>                       | A Block Symbol File (. <b>bsf</b> ) representation of the IP variation for use in Quartus Prime Block Diagram Files ( <b>.bdf</b> ).                                                                                                                                                                                                                                   |

| <your_ip>.spd</your_ip>                       | Required input file for ip-make-simscript to generate simulation scripts for supported simulators. The <b>.spd</b> file contains a list of files generated for simulation, along with information about memories that you can initialize.                                                                                                                              |

| <your_ip>.ppf</your_ip>                       | The Pin Planner File ( <b>.ppf</b> ) stores the port and node assignments for IP components created for use with the Pin Planner.                                                                                                                                                                                                                                      |

| <your_ip>_bb.v</your_ip>                      | You can use the Verilog black-box ( <b>_bb.v</b> ) file as an empty module declaration for use as a black box.                                                                                                                                                                                                                                                         |

Altera Corporation

2-6

UG-20008 2019.01.02

| File Name                                 | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <your_ip>.sip</your_ip>                   | Contains information required for NativeLink simulation of IP components. You must add the <b>.sip</b> file to your Intel Quartus Prime project.                                                                                                                                                                                                                                                |

| <your_ip>_inst.v and _ inst.vhd</your_ip> | HDL example instantiation template. You can copy and paste the contents of this file into your HDL file to instantiate the IP variation.                                                                                                                                                                                                                                                        |

| <your_ip>.regmap</your_ip>                | If IP contains register information, <b>.regmap</b> file generates.<br>The <b>.regmap</b> file describes the register map information of master<br>and slave interfaces. This file complements the <b>.sopcinfo</b> file by<br>providing more detailed register information about the system. This<br>enables register display views and user customizable statistics in the<br>System Console. |

| <your_ip>.svd</your_ip>                   | Allows hard processor system (HPS) System Debug tools to view the register maps of peripherals connected to HPS within a Qsys system.                                                                                                                                                                                                                                                           |

|                                           | During synthesis, the <b>.svd</b> files for slave interfaces visible to System<br>Console masters are stored in the <b>.sof</b> file in the debug section.<br>System Console reads this section, which Qsys can query for register<br>map information. For system slaves, Qsys can access the registers by<br>name.                                                                             |

| <your_ip>.v<br/>and</your_ip>             | HDL files that instantiate each submodule or child IP core for synthesis or simulation.                                                                                                                                                                                                                                                                                                         |

| <your_ip>.vhd</your_ip>                   |                                                                                                                                                                                                                                                                                                                                                                                                 |

| mentor/                                   | Contains a ModelSim script msim_setup.tcl to set up and run a simulation.                                                                                                                                                                                                                                                                                                                       |

| aldec/                                    | Contains a Riviera-PRO script rivierapro_setup.tcl to setup and run a simulation.                                                                                                                                                                                                                                                                                                               |

| synopsys/vcs/                             | Contains a shell script vcs_setup.sh to set up and run a VCS <sup>®</sup> simulation.                                                                                                                                                                                                                                                                                                           |

| synopsys/vcsmx/                           | Contains a shell script vcsmx_setup.sh and synopsys_<br>sim.setup file to set up and run a VCS MX <sup>®</sup> simulation.                                                                                                                                                                                                                                                                      |

| cadence/                                  | Contains a shell script ncsim_setup.sh and other setup files to set<br>up and run an NCSIM simulation.                                                                                                                                                                                                                                                                                          |

| submodules/                               | Contains HDL files for the IP core submodule.                                                                                                                                                                                                                                                                                                                                                   |

| <child cores="" ip="">/</child>           | For each generated child IP core directory, Qsys generates synth/<br>andsim/ sub-directories.                                                                                                                                                                                                                                                                                                   |

Getting Started with the CPRI v6.0 IP Core

## **CPRI v6.0 IP Core Parameters**

The CPRI v6.0 parameter editor provides the parameters you can set to configure the CPRI v6.0 IP core and simulation testbench.

The CPRI v6.0 parameter editor has three tabs.

#### Table 2-3: General CPRI v6.0 IP Core Parameters

Describes the general parameters for customizing the CPRI v6.0 IP core. These parameters appear on the **General** tab in the CPRI v6.0 parameter editor.

| Parameter                   | Options                                                                                                                                                     | Default<br>Setting                                              | Parameter Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line bit rate (Mbits/<br>s) | <ul> <li>614.4</li> <li>1228.8</li> <li>2457.6</li> <li>3072.0</li> <li>4915.2</li> <li>6144.0</li> <li>8110.08</li> <li>9830.4</li> <li>10137.6</li> </ul> | Lowest<br>bit rate<br>supporte<br>d for the<br>device<br>family | Selects the CPRI line bit rate. Refer to <b>CPRI v6.0 IP</b><br><b>Core Performance: Device and Transceiver Speed</b><br><b>Grade Support</b> on page 1-5 for supported CPRI line<br>bit rates in the supported device families.<br>The parameter editor does not allow you to specify a<br>CPRI line bit rate that the target device does not<br>support.                                                                                                                                                                                                                                                                                                                                              |

| Synchronization<br>mode     | <ul><li>Master</li><li>Slave</li></ul>                                                                                                                      | Master                                                          | Specifies whether the CPRI v6.0 IP core is<br>configured as a CPRI link master or a CPRI link<br>slave.<br>The value of this parameter determines the initial<br>and reset clocking mode of the CPRI v6.0 IP core.<br>You can modify the IP core clocking mode<br>dynamically by modifying the value of the synchro-<br>nization_mode field of the L1_CONFIG register.                                                                                                                                                                                                                                                                                                                                  |

| Operation mode              | <ul> <li>TX/RX<br/>Duplex</li> <li>TX Simplex</li> <li>RX Simplex</li> </ul>                                                                                | TX/RX<br>Duplex                                                 | Specifies whether the CPRI v6.0 IP core is<br>configured with RX functionality only (RX Simplex)<br>, with TX functionality only (TX Simplex), or with<br>both RX and TX functionality (TX/TX Duplex).<br>If you specify a simplex mode, the Quartus Prime<br>Fitter synthesizes logic for only one direction of<br>traffic. If the CPRI v6.0 IP core is in TX simplex<br>operation mode, it can transmit on the CPRI link<br>but cannot receive. If the CPRI v6.0 IP core is in RX<br>simplex operation mode, it can receive traffic on the<br>CPRI link but cannot transmit.<br>Currently, IP core variations that target an Intel<br>Stratix 10 device support only the <b>TX/RX Duplex</b><br>mode. |

| Parameter                                  | Options                                                | Default<br>Setting | Parameter Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------|--------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core clock source<br>input                 | External     Internal                                  | Internal           | Specifies the clock source of the cpri_coreclk.<br>In the internal clocking scheme, you should drive<br>the cpri_coreclk with the cleaned-up xcvr_<br>recovered_clk in CPRI slave IP cores, and with the<br>external master clock in CPRI master IP cores. In<br>this clocking scheme, the IP core uses the cpri_<br>coreclk input clock only when the IP core is<br>running at the CPRI line bit rate of 8.11008 or<br>10.1376 Gbps,<br>The external clocking scheme supports the single-                                                                                                                                                                                  |

|                                            |                                                        |                    | trip delay calibration feature. In this clocking<br>scheme, the IP core uses this clock at all CPRI line<br>bit rates. You can drive the cpri_coreclk input<br>clock with the tx_clkout output clock from the TX<br>PCS.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Transmitter local<br>clock division factor | <ul> <li>1</li> <li>2</li> <li>3</li> <li>4</li> </ul> | 1                  | Specifies the division factor for the local clock<br>divider. The IP core divides the high speed clock<br>from the transceiver TX PLL (xcvr_ext_pll_clk)<br>to generate the serial TX clock.<br>This feature supports the configuration of multiple<br>instances of the CPRI v6.0 IP core that run at<br>different CPRI line bit rates but share use of the<br>same TX PLL.<br>This parameter is not available if you set the value of<br><b>Operation mode</b> to <b>RX Simplex</b> .<br>IP core variations that target an Intel Arria 10 device<br>or an Intel Stratix 10 device, with <b>Line bit rate</b> set to<br>4915.2 Mbps or slower, support only the value of 1. |

Getting Started with the CPRI v6.0 IP Core

2-9

| Parameter                                       | Options               | Default<br>Setting | Parameter Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------|-----------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of receiver<br>CDR reference<br>clock(s) | • 1<br>• 2            | 1                  | Specifies the width of the receiver reference clock<br>that controls the receiver. The CPRI v6.0 IP core<br>supports the selection of one or two clocks. This<br>option supports auto-negotiation to and from the<br>CPRI line bit rate of 10.1376 Gbps in CPRI v6.0 IP<br>core variations that target a Stratix V device. Refer<br>to "IP Core Clocking Structure."                                                                                                                             |

|                                                 |                       |                    | If you set this parameter to the value of 1, the xcvr_<br>cdr_refclk is a single clock. If you set this<br>parameter to the value of 2, the xcvr_cdr_refclk<br>input signal is two bits wide, to support two distinct<br>reference clocks.                                                                                                                                                                                                                                                       |

|                                                 |                       |                    | Intel recommends that you specify a two-bit clock<br>for Stratix V variations that are expected to<br>implement auto-negotiation up to a 10.1376 Gbps<br>CPRI line bit rate. In this case the typical design<br>drives one bit of the xcvr_cdr_refclk clock with a<br>common 307.2 MHz clock for the lower CPRI line<br>bit rates and drives the other bit with a 253.44 MHz<br>clock for the 10.1376 Gbps CPRI line bit rate.<br>However, these specific clock frequencies are not<br>required. |

|                                                 |                       |                    | If the value of this parameter is 2, the receiver clocks<br>the CDR with the xcvr_cdr_refclk[0] input signal<br>by default. You can switch the receiver to use xcvr_<br>cdr_refclk[1], or back to xcvr_cdr_refclk[0],<br>by dynamically reconfiguring the RX transceiver.                                                                                                                                                                                                                        |

|                                                 |                       |                    | IP core variations that target a device family other<br>than the Stratix V device family, support only a<br>single-bit receiver reference clock.                                                                                                                                                                                                                                                                                                                                                 |

|                                                 |                       |                    | This parameter is not available if you set the value of <b>Operation mode</b> to <b>TX Simplex</b> .                                                                                                                                                                                                                                                                                                                                                                                             |

| Receiver CDR<br>reference clock                 | Per drop-down<br>menu | 307.2              | Specifies the incoming reference clock frequency for the receiver CDR PLL, in MHz.                                                                                                                                                                                                                                                                                                                                                                                                               |

| frequency (MHz)                                 |                       |                    | You must drive the input clock xcvr_cdr_refclk or xcvr_cdr_refclk[0] at the frequency you specify for this parameter.                                                                                                                                                                                                                                                                                                                                                                            |

|                                                 |                       |                    | This parameter is not available if you set the value of <b>Operation mode</b> to <b>TX Simplex</b> .                                                                                                                                                                                                                                                                                                                                                                                             |

| Parameter                                                         | Options          | Default<br>Setting | Parameter Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------|------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCCR_GXB and<br>VCCT_GXB supply<br>voltage for the<br>transceiver |                  | 1_0V               | Specifies whether the transceiver supply voltage is 1.1 V or 1.0 V. The supply voltage must match the voltage you specify for this parameter, in IP core variations that target an Intel Stratix 10 device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                   |                  |                    | This parameter affects only IP core variations that<br>target an Intel Stratix 10 device. You can ignore it for<br>other device families.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Recovered clock<br>source                                         | • PCS<br>• PMA   | PCS                | <ul> <li>Specifies the clock source of the xcvr_recovered_clk.</li> <li>Intel recommends that you set this parameter to the value of <b>PMA</b> in IP core variations that target a Stratix V device, if you expect your IP core to autonegotiate to or from the CPRI line bit rate of 10.1376 Gbps. In this case, sourcing the recovered clock from the PMA improves jitter on that clock. If you specify the PCS source, the IP core switches between two PCS-internal clocks at auto-negotiation to or from the CPRI line bit rate of 10.1376 Gbps.</li> <li>This parameter is not available for</li> <li>CPRI master IP cores</li> <li>IP cores that target an Intel Stratix 10 device</li> </ul>                                                                                                                                                                                       |

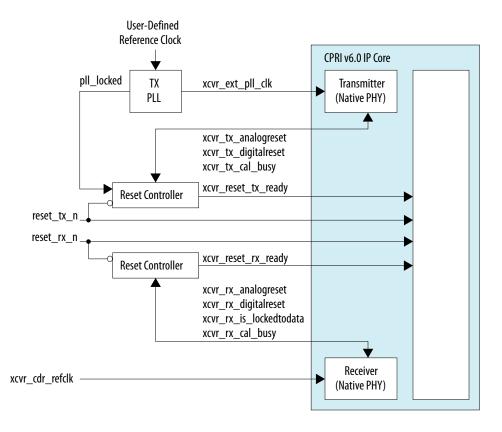

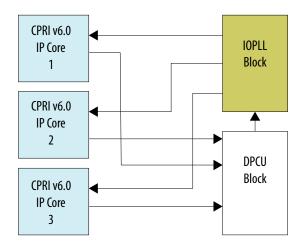

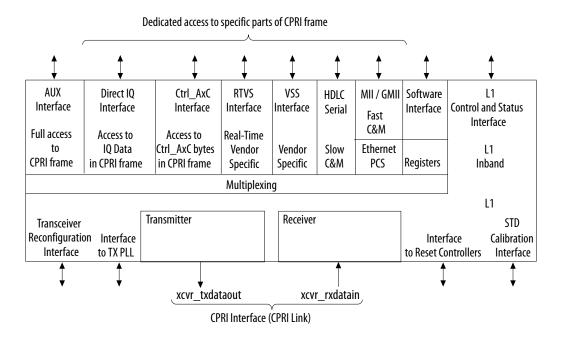

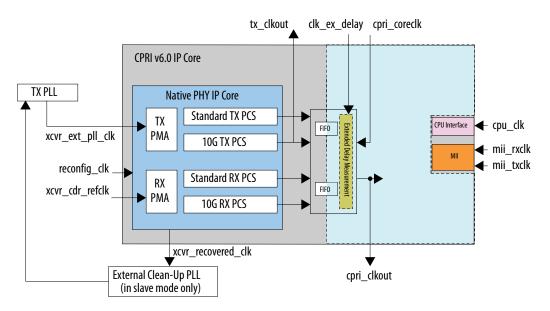

| Receiver soft buffer                                              | 4, 5, 6, 7, or 8 | 6                  | <ul> <li>IP cores for which you set the value of <b>Operation</b><br/>mode to <b>TX Simplex</b></li> <li>The value you specify for this parameter is log<sub>2</sub> of</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |