## Intel<sup>®</sup> Arria<sup>®</sup> 10 Avalon<sup>®</sup> Streaming with SR-IOV IP for PCIe\* User Guide

Updated for Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Suite: **20.4**

683686 2022.01.11

UG-01161

## Contents

| 1. | Datasheet                                                                                                              | 6    |

|----|------------------------------------------------------------------------------------------------------------------------|------|

|    | 1.1. Intel <sup>®</sup> Arria <sup>®</sup> 10 Avalon <sup>®</sup> -ST Interface with SR-IOV for PCI Express* Datasheet | 6    |

|    | 1.1.1. SR-IOV Features                                                                                                 | 7    |

|    | 1.2. Release Information                                                                                               | 8    |

|    | 1.3. Device Family Support                                                                                             | 9    |

|    | 1.4. Debug Features                                                                                                    |      |

|    | 1.5. IP Core Verification                                                                                              |      |

|    | 1.5.1. Compatibility Testing Environment                                                                               |      |

|    | 1.6. Performance and Resource Utilization                                                                              |      |

|    | 1.7. Recommended Speed Grades for SR-IOV Interface                                                                     | . 10 |

| 2. | Getting Started with the SR-IOV Design Example                                                                         | 12   |

|    | 2.1. Directory Structure for Intel Arria 10 SR-IOV Design Example                                                      |      |

|    | 2.2. Design Components for the SR-IOV Design Example                                                                   |      |

|    | 2.3. Generating the SR-IOV Design Example                                                                              |      |

|    | 2.4. Compiling and Simulating the Design for SR-IOV                                                                    |      |

| -  |                                                                                                                        |      |

| 3. | Parameter Settings                                                                                                     |      |

|    | 3.1. Parameters                                                                                                        |      |

|    | 3.2. Intel Arria 10 Avalon-ST Settings                                                                                 |      |

|    | 3.3. Intel Arria 10 SR-IOV System Settings                                                                             |      |

|    | 3.4. Base Address Register (BAR) Settings                                                                              |      |

|    | 3.5. SR-IOV Device Identification Registers                                                                            |      |

|    | 3.6. Intel Arria 10 Interrupt Capabilities<br>3.7. Physical Function TLP Processing Hints (TPH)                        | . 22 |

|    |                                                                                                                        |      |

|    | 3.8. Address Translation Services (ATS)<br>3.9. PCI Express and PCI Capabilities Parameters                            |      |

|    | 3.9.1. PCI Express and PCI Capabilities Parameters                                                                     |      |

|    | 3.9.2. Error Reporting                                                                                                 |      |

|    | 3.9.3. Link Capabilities                                                                                               |      |

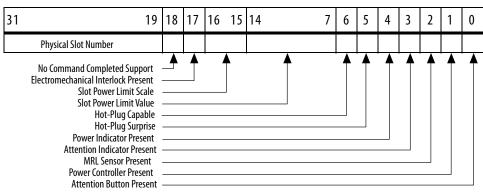

|    | 3.9.4. Slot Capabilities                                                                                               |      |

|    | 3.9.5. Power Management                                                                                                |      |

|    | 3.10. PHY Characteristics                                                                                              |      |

|    | 3.11. Example Designs                                                                                                  |      |

| -  |                                                                                                                        |      |

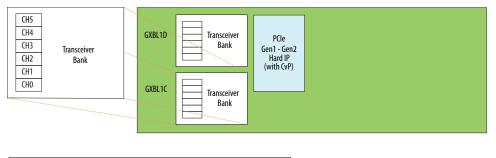

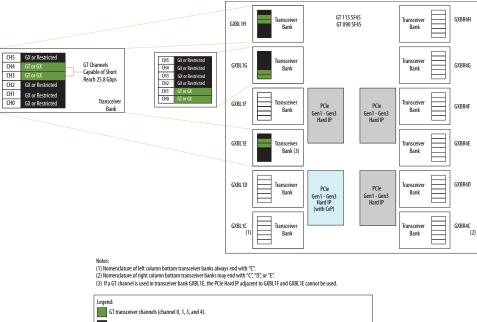

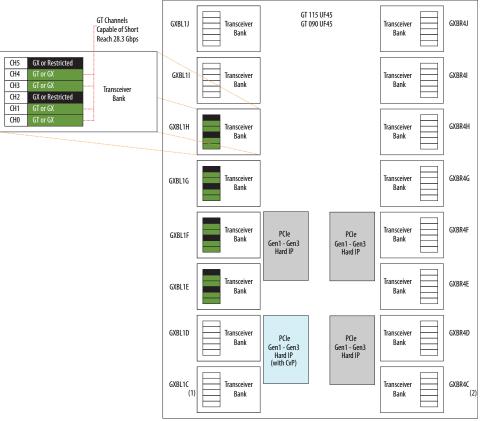

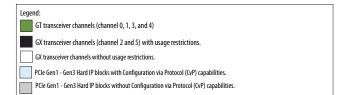

| 4. | Physical Layout                                                                                                        |      |

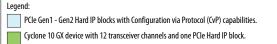

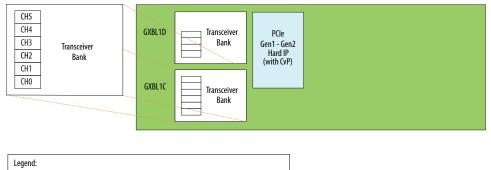

|    | 4.1. Hard IP Block Placement In Intel Cyclone 10 GX Devices                                                            |      |

|    | 4.2. Hard IP Block Placement In Intel Arria 10 Devices                                                                 |      |

|    | 4.3. Channel and Pin Placement for the Gen1, Gen2, and Gen3 Data Rates                                                 |      |

|    | 4.4. Channel Placement and fPLL and ATX PLL Usage for the Gen3 Data Rate                                               |      |

|    | 4.5. PCI Express Gen3 Bank Usage Restrictions                                                                          | .37  |

| 5. | Interfaces and Signal Descriptions                                                                                     | .38  |

|    | 5.1. Avalon-ST TX Interface                                                                                            | . 39 |

|    | 5.2. Component-Specific Avalon-ST Interface Signals                                                                    | . 40 |

|    | 5.3. Avalon-ST RX Interface                                                                                            | .44  |

|    | 5.4. BAR Hit Signals                                                                                                   |      |

|    | 5.5. Configuration Status Interface                                                                                    | . 46 |

#### Contents

# intel.

|       | 5.6. Clock Signals                                                                   |     |

|-------|--------------------------------------------------------------------------------------|-----|

|       | 5.7. Function-Level Reset (FLR) Interface                                            | 47  |

|       | 5.8. SR-IOV Interrupt Interface                                                      |     |

|       | 5.9. Configuration Extension Bus (CEB) Interface                                     | .53 |

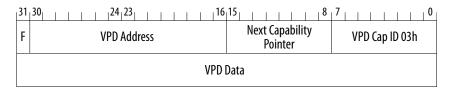

|       | 5.9.1. Vital Product Data (VPD) Capability                                           | 55  |

|       | 5.10. Implementing MSI-X Interrupts                                                  | .58 |

|       | 5.11. Control Shadow Interface                                                       | 59  |

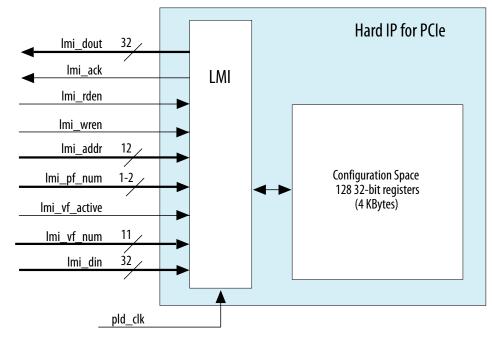

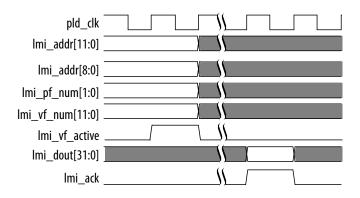

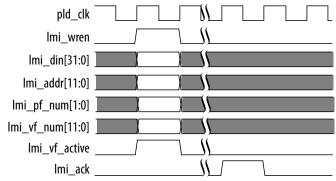

|       | 5.12. Local Management Interface (LMI) Signals                                       | .60 |

|       | 5.13. Reset, Status, and Link Training Signals                                       | 62  |

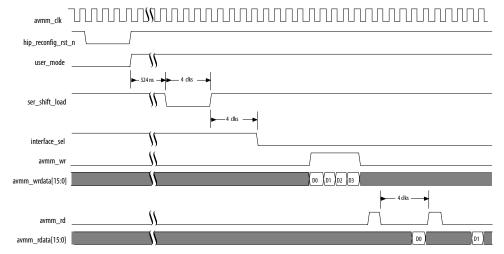

|       | 5.14. Hard IP Reconfiguration Interface                                              | 66  |

|       | 5.15. Serial Data Signals                                                            | 67  |

|       | 5.16. Test Signals                                                                   | .68 |

|       | 5.17. PIPE Interface Signals                                                         |     |

|       | 5.18. Intel Arria 10 Development Kit Conduit Interface                               | 71  |

|       | gisters                                                                              | 70  |

| 6. Re | -                                                                                    |     |

|       | 6.1. Addresses for Physical and Virtual Functions                                    |     |

|       | 6.2. Correspondence between Configuration Space Registers and the PCIe Specification |     |

|       | 6.3. PCI and PCI Express Configuration Space Registers                               |     |

|       | 6.3.1. Type 0 Configuration Space Registers                                          |     |

|       | 6.3.2. PCI and PCI Express Configuration Space Register Content                      |     |

|       | 6.3.3. Interrupt Line and Interrupt Pin Register                                     |     |

|       | 6.4. MSI Registers                                                                   |     |

|       | 6.5. MSI-X Capability Structure                                                      |     |

|       | 6.6. Power Management Capability Structure                                           |     |

|       | 6.7. PCI Express Capability Structure                                                |     |

|       | 6.8. Advanced Error Reporting (AER) Enhanced Capability Header Register              |     |

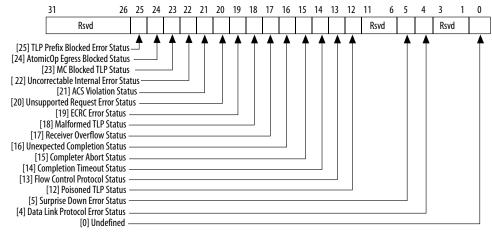

|       | 6.9. Uncorrectable Error Status Register                                             |     |

|       | 6.10. Uncorrectable Error Mask Register                                              |     |

|       | 6.11. Uncorrectable Error Severity Register                                          |     |

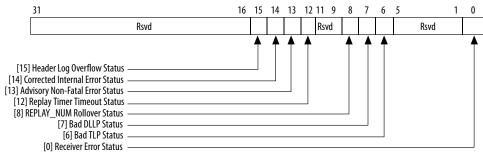

|       | 6.12. Correctable Error Status Register                                              |     |

|       | 6.13. Correctable Error Mask Register                                                |     |

|       | 6.14. Advanced Error Capabilities and Control Register                               |     |

|       | 6.15. Header Log Registers 0-3                                                       |     |

|       | 6.16. SR-IOV Virtualization Extended Capabilities Registers                          |     |

|       | 6.16.1. SR-IOV Virtualization Extended Capabilities Registers Address Map            |     |

|       | 6.16.2. ARI Enhanced Capability Header                                               |     |

|       | 6.16.3. SR-IOV Enhanced Capability Registers                                         |     |

|       | 6.16.4. Initial VFs and Total VFs Registers                                          |     |

|       | 6.16.5. VF Device ID Register                                                        |     |

|       | 6.16.6. Page Size Registers                                                          |     |

|       | 6.16.7. VF Base Address Registers (BARs) 0-5                                         |     |

|       | 6.16.8. Secondary PCI Express Extended Capability Header                             | 97  |

|       | 6.16.9. Lane Status Registers                                                        |     |

|       | 6.16.10. Transaction Processing Hints (TPH) Requester Enhanced Capability Header     | .98 |

|       | 6.17. Virtual Function Registers                                                     | 98  |

| 7 Do  | set and Clocks1                                                                      | ია  |

| /. Re |                                                                                      |     |

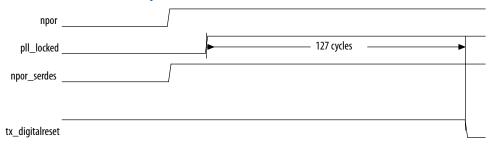

|       | 7.1. Reset Sequence for Hard IP for PCI Express IP Core and Application Layer        |     |

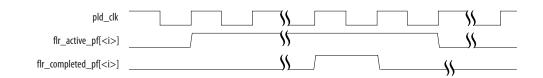

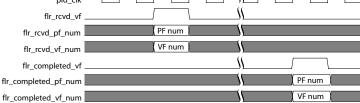

|       | 7.2. Function Level Reset (FLR)                                                      |     |

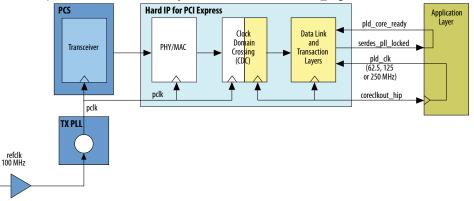

|       | 7.3. Clocks                                                                          | .03 |

| 7.3.1. Clock Domains         104           7.3.2. Clock Summary         105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

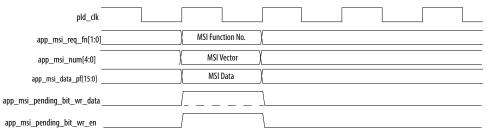

| 8. Programming and Testing SR-IOV Bridge MSI Interrupts.       106         8.1. Setting Up and Verifying MSI Interrupts.       106         8.2. Masking MSI Interrupts.       106         8.3. Dropping a Pending MSI Interrupt       107                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9. Error Handling1099.1. Physical Layer Errors1099.2. Data Link Layer Errors1109.3. Transaction Layer Errors1109.4. Error Reporting and Data Poisoning1119.5. Uncorrectable and Correctable Error Status Bits112                                                                                                                                                                                                                                                                                                                                                                                                                                       |

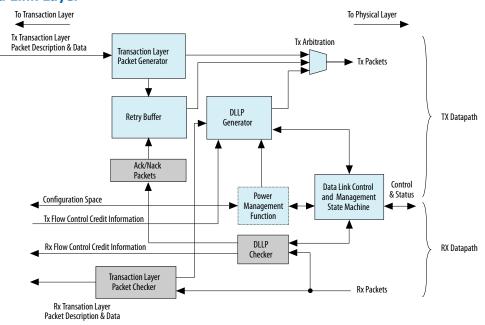

| 10. IP Core Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>11. Design Implementation124</b> 11.1. Making Pin Assignments to Assign I/O Standard to Serial Data Pins12411.2. Recommended Reset Sequence to Avoid Link Training Issues12511.3. SDC Timing Constraints125                                                                                                                                                                                                                                                                                                                                                                                                                                         |

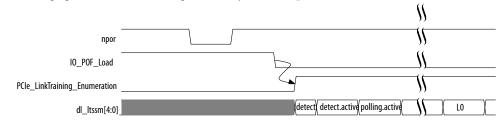

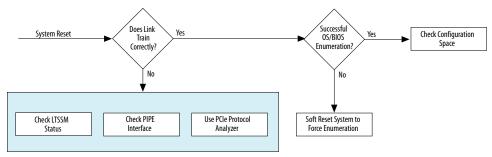

| <b>12. Debugging</b> 12612.1. Setting Up Simulation12612.1.1. Changing Between Serial and PIPE Simulation12612.1.2. Using the PIPE Interface for Gen1 and Gen2 Variants12612.1.3. Viewing the Important PIPE Interface Signals12712.1.4. Disabling the Scrambler for Gen1 and Gen2 Simulations12712.1.5. Disabling 8B/10B Encoding and Decoding for Gen1 and Gen2 Simulations12712.2. Simulation Fails To Progress Beyond Polling.Active State12712.3. Hardware Bring-Up Issues12812.4. Link Training12812.5. Creating a Signal Tap Debug File to Match Your Design Hierarchy12912.6. Use Third-Party PCIe Analyzer12912.7. BIOS Enumeration Issues130 |

| <b>13. Document Revision History</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A.1. TLP Packet Formats without Data Payload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Β. | Intel Arria 10 Avalon-ST with SR-IOV Interface for PCIe Solutions User Guide |     |

|----|------------------------------------------------------------------------------|-----|

|    | Archive                                                                      | 138 |

## **1. Datasheet**

## **1.1.** Intel<sup>®</sup> Arria<sup>®</sup> **10** Avalon<sup>®</sup>-ST Interface with SR-IOV for PCI Express\* Datasheet

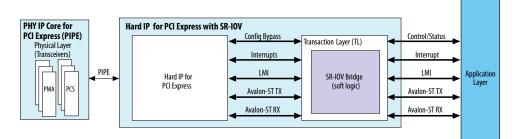

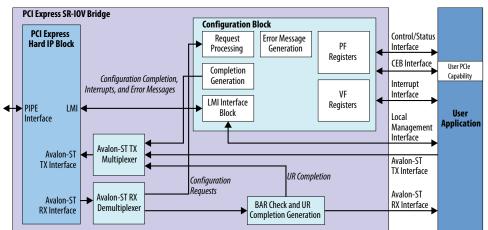

Intel<sup>®</sup> Arria<sup>®</sup> 10 FPGAs include a configurable, hardened protocol stack for PCI Express\* that is compliant with *PCI Express Base Specification 2.1 or 3.0*. The Intel Arria 10 Hard IP for PCI Express with Single Root I/O Virtualization (SR-IOV) IP core consists of this hardened protocol stack and the SR-IOV soft logic. The SR-IOV soft logic uses the Configuration Space Bypass mode of the Hard IP to bypass the internal configuration block and BAR matching logic. These functions are implemented in external soft logic. Soft logic in the SR-IOV Bridge also implements interrupts and error reporting.

The SR-IOV Bridge was redesigned to support up to 8 Physical Functions (PFs) and 2048 Virtual Functions (VFs). The SR-IOV bridge also supports the Address Translation Services (ATS) and TLP Processing Hints (TPH) capabilities.

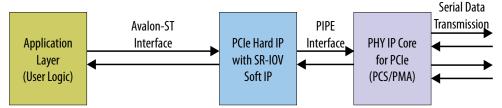

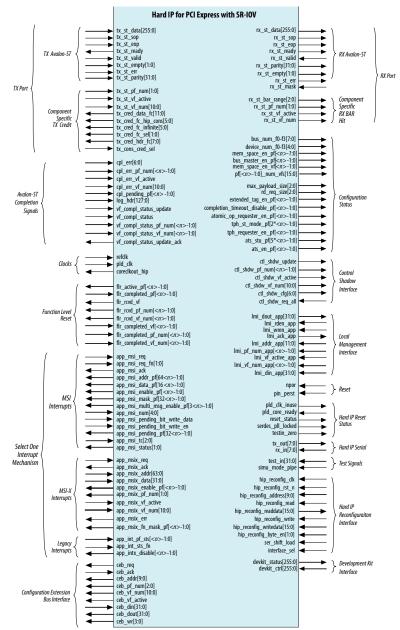

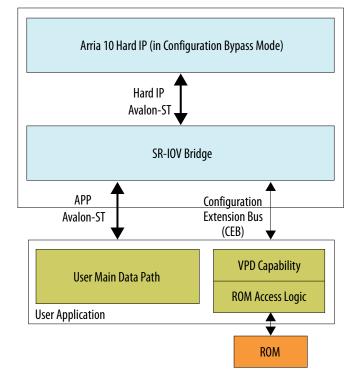

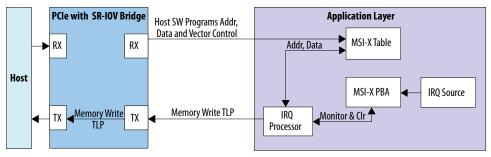

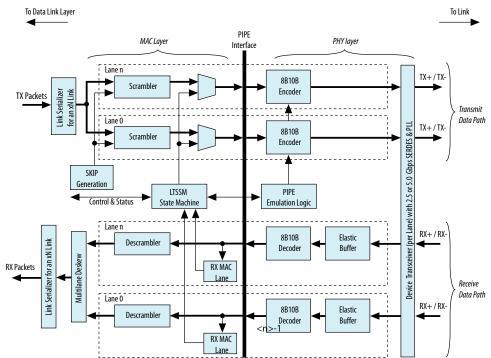

### Figure 1. Intel Arria 10 PCIe Variant with SR-IOV

The following figure shows the high-level modules and connecting interfaces for this variant.

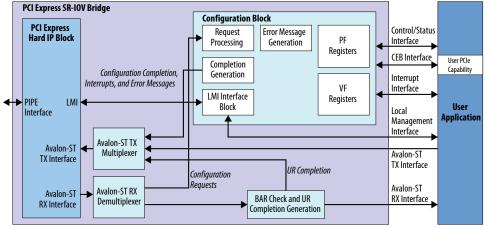

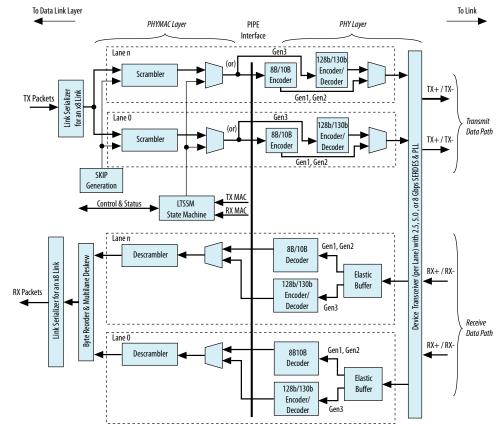

### Figure 2. Intel Arria 10 PCIe Variant with SR-IOV

The following figure provides the next level of detail for the modules that comprise the SR-IOV Bridge.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

ISO 9001:2015 Registered

### Table 2. PCI Express Data Throughput

The following table shows the aggregate bandwidth of a PCI Express link for Gen2 and Gen3 for supported link widths. The protocol specifies 2.5 giga-transfers per second for Gen1, 5.0 giga-transfers per second for Gen2, and 8.0 giga-transfers per second for Gen3. This table provides bandwidths for a single transmit (TX) or receive (RX) channel. The numbers double for duplex operation. Gen1 and Gen2 use 8B/10B encoding which introduces a 20% overhead. In contrast, Gen3 uses 128b/130b encoding which reduces the data throughput lost to encoding to about 1.5%.

|                                                 | Link Width |    |

|-------------------------------------------------|------------|----|

|                                                 | ×4         | ×8 |

| PCI Express Gen2 (5.0 Gbps) - 256-bit interface | N/A        | 32 |

| PCI Express Gen3 (8.0 Gbps) - 256-bit interface | 31.51      | 63 |

#### **Related Information**

- Introduction to Intel FPGA IP Cores Provides general information about all Intel FPGA IP cores, including parameterizing, generating, upgrading, and simulating IP cores.

- Creating Version-Independent IP and Platform Designer Simulation Scripts Create simulation scripts that do not require manual updates for software or IP version upgrades.

- Intel Arria 10 Avalon-ST with SR-IOV Interface for PCIe Solutions User Guide Archive on page 138

- Avalon Interface Specifications For information about the Avalon-ST interface protocol.

- Arria 10 Avalon-ST Interface for PCIe Solutions User Guide For the Avalon-ST interface to the application without SR-IOV.

- PCI Express Base Specification 3.0

## **1.1.1. SR-IOV Features**

New features in the Intel Quartus Prime 17.1 release:

• Added parameter to invert TX polarity.

The Intel Arria 10 Hard IP for PCI Express with SR-IOV supports the following features:

- Support for ×4, and ×8 configurations with Gen2 or Gen3 lane rates for Endpoints

- Configuration Spaces for up to eight PCIe Physical Functions (PFs) and a maximum of 2048 Virtual Functions (VFs) for the PFs

- Base address register (BAR) checking logic

- Dedicated 16 kilobyte (KB) receive buffer

- Platform Designer example designs demonstrating parameterization, design modules, and connectivity

- Extended credit allocation settings to better optimize the RX buffer space based on application type

- Support for Advanced Error Reporting (AER) for PFs

- Support for Address Translation Services (ATS) and TLP Processing Hints (TPH) capabilities

- Support for a Control Shadow Interface to read the current settings for some of the VF Control Register fields in the PCI and PCI Express Configuration Spaces

- Support for Configuration Space Bypass Mode, allowing you to design a custom Configuration Space and support multiple functions

- Support for Function Level Reset (FLR) for PFs and VFs

- Support for Gen3 PIPE simulation

- Support for the following interrupt types:

- Message signaled interrupts (MSI) for PFs

- MSI-X for PFs and VFs

- Legacy interrupts for PFs

- Easy to use:

- Flexible configuration.

- Example designs to get started.

The Intel Arria 10 Avalon-ST Interface with SR-IOV PCIe Solutions User Guide explains how to use this IP core and not the PCI Express protocol. Although there is inevitable overlap between these two purposes, use this document only in conjunction with an understanding of the PCI Express Base Specification.

*Note:* This release provides separate user guides for the different variants.

### **Related Information**

- Arria 10 Avalon-MM DMA Interface for PCIe Solutions User Guide For the Avalon-MM interface and DMA functionality.

- Arria 10 Avalon-MM Interface for PCIe Solutions User Guide For the Avalon-MM interface with no DMA.

- Arria 10 Avalon-ST Interface for PCIe Solutions User Guide For the Avalon-ST interface.

## **1.2. Release Information**

### Table 3. Hard IP for PCI Express Release Information

| Item           | Description                                       |

|----------------|---------------------------------------------------|

| Version        | 17.1                                              |

| Release Date   | November 2017                                     |

| Ordering Codes | Primary: IP-PCIE/SRIOV<br>Renewal: IPR-PCIE/SRIOV |

| Product IDs    | 00FB                                              |

| Vendor ID      | 6AF7                                              |

Intel verifies that the current version of the Quartus Prime software compiles the previous version of each IP core, if this IP core was included in the previous release. Intel reports any exceptions to this verification in the *Intel IP Release Notes* or clarifies them in the Quartus Prime IP Update tool. Intel does not verify compilation with IP core versions older than the previous release.

### **Related Information**

Errata for the Intel Arria 10 Hard IP for PCI Express IP Core in the Knowledge Base

## **1.3. Device Family Support**

The following terms define device support levels for Intel FPGA IP cores:

- Advance support—the IP core is available for simulation and compilation for this device family. Timing models include initial engineering estimates of delays based on early post-layout information. The timing models are subject to change as silicon testing improves the correlation between the actual silicon and the timing models. You can use this IP core for system architecture and resource utilization studies, simulation, pinout, system latency assessments, basic timing assessments (pipeline budgeting), and I/O transfer strategy (data-path width, burst depth, I/O standards tradeoffs).

- **Preliminary support**—the IP core is verified with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution.

- **Final support**—the IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.

### Table 4.Device Family Support

| Device Family         | Support Level                                                                                            |

|-----------------------|----------------------------------------------------------------------------------------------------------|

| Intel Arria 10        | Final.                                                                                                   |

| Other device families | Refer to the Intel's PCI Express IP Solutions web page for support information on other device families. |

## **1.4. Debug Features**

Debug features allow observation and control of the Hard IP for faster debugging of system-level problems.

### **Related Information**

Debugging on page 126

## **1.5. IP Core Verification**

To ensure compliance with the PCI Express specification, Intel performs extensive verification. The simulation environment uses multiple testbenches that consist of industry-standard bus functional models (BFMs) driving the PCI Express link interface. Intel performs the following tests in the simulation environment:

- Directed and pseudorandom stimuli test the Application Layer interface, Configuration Space, and all types and sizes of TLPs

- Error injection tests inject errors in the link, TLPs, and Data Link Layer Packets (DLLPs), and check for the proper responses

- PCI-SIG<sup>®</sup> Compliance Checklist tests that specifically test the items in the checklist

- Random tests that test a wide range of traffic patterns

Intel provides example designs that you can leverage to test your PCBs and complete compliance base board testing (CBB testing) at PCI-SIG, upon request.

## **1.5.1.** Compatibility Testing Environment

Intel has performed significant hardware testing to ensure a reliable solution. In addition, Intel internally tests every release with motherboards and PCI Express switches from a variety of manufacturers. All PCI-SIG compliance tests are run with each IP core release.

## **1.6. Performance and Resource Utilization**

Because the PCIe protocol stack is implemented in hardened logic, it uses no core device resources (no ALMs and no embedded memory).

The SR-IOV Bridge is implemented is soft logic, requiring FPGA fabric resources. The following table shows the typical device resource utilization for selected configurations using the current version of the Quartus Prime software. With the exception of M20K memory blocks, the numbers of ALMs and logic registers are rounded up to the nearest 50.

0

0

| Number of PFs and VFs | ALMs  | M20K Memory Blocks | Logic Registers |

|-----------------------|-------|--------------------|-----------------|

| 1 PF, 4 VFs           | 2350  | 0                  | 5200            |

| 2 PFs, 4 VFs          | 3600  | 0                  | 6500            |

| 4 PFs, 4 VFs          | 4650  | 0                  | 7700            |

| 1 PF, 2048 VFs        | 10350 | 0                  | 5700            |

| 2 PFs, 2048 VFs       | 11750 | 0                  | 7500            |

| 4 PFs 2048 VFs        | 14150 | 0                  | 10650           |

### Table 5. Performance and Resource Utilization Intel Arria 10 Avalon-ST with SR-IOV

### **Related Information**

Running the Fitter

For information on Fitter constraints.

## **1.7. Recommended Speed Grades for SR-IOV Interface**

2300

3450

5100

6300

2 PFs

4 PFs

### Table 6. Intel Arria 10 Recommended Speed Grades for All SR-IOV Configurations

Intel recommends setting the Quartus Prime Analysis & Synthesis Settings **Optimization Technique** to **Speed** when the Application Layer clock frequency is 250 MHz. For information about optimizing synthesis, refer to "Setting Up and Running Analysis and Synthesis in Quartus Prime Help. For more information about how to effect the **Optimization Technique** settings, refer to Area and Timing Optimization in volume 2 of the *Quartus Prime Handbook*. Refer to the *Related Links* below.

| Link Rate | Link Width | Interface<br>Width | Application Clock Frequency<br>(MHz) | Recommended Speed Grades |

|-----------|------------|--------------------|--------------------------------------|--------------------------|

| Gen2      | ×8         | 256 bits           | 125                                  | -1, -2, -3               |

| Gen3      | ×4         | 256 bits           | 125                                  | -1, -2, -3               |

| Gens      | ×8         | 256 bits           | 250                                  | -1, -2                   |

### **Related Information**

- Running Synthesis For settings that affect timing closure.

- Intel FPGA Software Installation and Licensing Manual For comprehensive information for installing and licensing Intel FPGA software.

## 2. Getting Started with the SR-IOV Design Example

The SR-IOV example design consists of a PCIe Endpoint that includes an SR-IOV bridge configured for one PF and four VFs. The example design also includes a basic application to facilitate host accesses to a target memory. This design example supports simulation. In simulation, the testbench issues downstream memory accesses to the virtual function BAR. The testbench then reads the data written and compares it to the expected result. The test passes if all the comparisons pass.

When you install the Intel Quartus Prime software you also install the IP Library. This installation includes design examples for Hard IP for PCI Express under the <install\_dir>/ip/altera/altera\_pcie/ directory. You can copy the design examples from the <install\_dir>/ip/altera/ altera\_pcie/ altera\_pcie/ altera\_pcie\_al0\_ed/example\_design/al0 directory. This walkthrough uses the sriov2\_target\_g3x8\_lpf\_4vf.qsys design example.

*Note:* Starting in the Quartus Prime 16.0 software release, you cannot simulate or compile SR-IOV designs without a license. Contact your local sales representative or email pcie@altera.com to obtain a license.

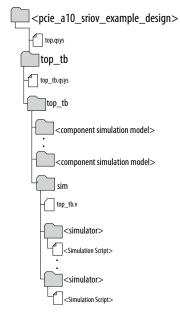

## **2.1. Directory Structure for Intel Arria 10 SR-IOV Design Example**

### Figure 3. Directory Structure for the Generated Example Design

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

ISO 9001:2015 Registered

## **2.2. Design Components for the SR-IOV Design Example**

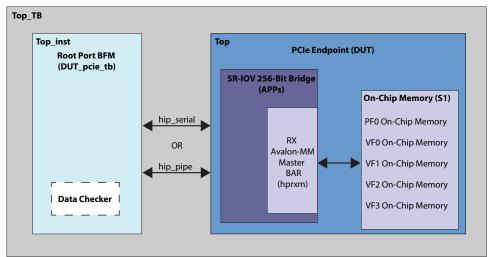

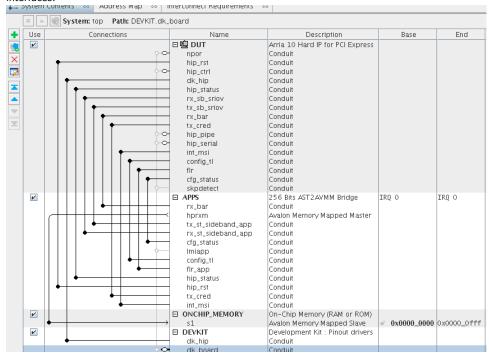

## Figure 4.Platform Designer Testbench for Intel Arria 10 Gen1 x8 128-bit SR-IOV<br/>Design Example

### Figure 5. Platform Designer Schematic for Top

This image of the Intel Arria 10 PCI Express DMA Design Example shows only the Avalon-ST, clock, and reset interfaces.

Send Feedback

The testbench includes a PCIe Root Port BFM and a PCIe Gen3 x8 Endpoint implemented in hard logic. The SR-IOV bridge, implemented in soft logic, drives memory writes and reads to the four VFs. The simulation includes the following stages:

- Link Training

- Configuration

- Memory writes to each VF

- Memory reads and compares to the expected data

## 2.3. Generating the SR-IOV Design Example

After installing the Quartus Prime software, copy the design examples from the <install\_dir>/ip/altera/ altera\_pcie/altera\_pcie\_al0\_ed/ example\_design/al0 directory. This walkthrough uses the sriov2\_top\_target\_gen3x8\_lpf\_4vf.qsys design example. To run the simulation, you must rename the design example top.qsys

- 1. Launch Platform Designer and open top.qsys.

- 2. On the Generate menu, select Generate Testbench System.

- 3. For Create testbench Platform Designer system, select Standard, BFMs for stand Platform Designer interfaces.

- 4. For Create testbench simulation model, select either Verilog or VHDL.

- For Output Directory ➤ Testbench, you can accept the default directory or modify it.

- 6. Click Generate.

- Note: Intel Arria 10 devices do not support the Create timing and resource estimates for third-party EDA synthesis tools option on the Generate

Generate HDL menu. You can select this menu item, but generation fails.

## 2.4. Compiling and Simulating the Design for SR-IOV

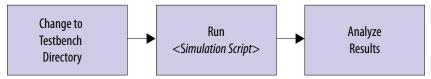

### Figure 6. Procedure

Follow these steps to compile and simulate the design:

- 1. Change the simulation directory.

- 2. Run the simulation script for the simulator of your choice. Refer to the table below.

- 3. Analyze the results.

| in | tol |   |

|----|-----|---|

|    |     | ® |

| Simulator           | Working Directory                                                     | Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mentor<br>ModelSim* | <example_design>/top_tb/<br/>top_tb/sim/mentor/</example_design>      | <ul> <li>a. Invoke vsim</li> <li>b. do msim_setup.tcl</li> <li>c. ld_debug</li> <li>d. run -all</li> <li>e. A successful simulation ends with the following message,<br/>"Simulation stopped due to successful completion! Simulation passed."</li> </ul>                                                                                                                                                                                                                  |

| Mentor VCS*         | <example_design>/top_tb/<br/>top_tb/sim/synopsys/vcs</example_design> | <ul> <li>a. sh vcs_setup.sh USER_DEFINED_SIM_OPTIONS=""</li> <li>b. A successful simulation ends with the following message,<br/>"Simulation stopped due to successful completion! Simulation<br/>passed."</li> </ul>                                                                                                                                                                                                                                                      |

| Cadence<br>NCSim*   | <example_design>top_tb/<br/>top_tb/sim/cadence</example_design>       | <ul> <li>a. Create a shell script, my_setup.sh. This script allows you to add additional commands and override the defaults included in ncsim_setup.sh.</li> <li>b. Include the following command in my_setup.sh: source ncsim_setup.sh USER_DEFINED_SIM_OPTIONS=""</li> <li>c. chmod +x *.sh</li> <li>d/my_setup.sh</li> <li>e. A successful simulation ends with the following message, "Simulation stopped due to successful completion! Simulation passed."</li> </ul> |

## Table 7.Steps to Run Simulation

Send Feedback

## **3. Parameter Settings**

## 3.1. Parameters

This chapter provides a reference for all the parameters of the IP core.

### Table 8. Design Environment Parameter

Starting in Intel Quartus Prime 18.0, there is a new parameter **Design Environment** in the parameters editor window.

| Parameter             | Value                | Description                                                                                                                                                                                                                                                                                  |

|-----------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design<br>Environment | Standalone<br>System | <ul> <li>Identifies the environment that the IP is in.</li> <li>The Standalone environment refers to the IP being in a standalone state where all its interfaces are exported.</li> <li>The System environment refers to the IP being instantiated in a Platform Designer system.</li> </ul> |

### Table 9.System Settings

| Interface TypeAvalon-MMNote: WAvalon-MM with DMA<br>Avalon-ST with SR-IOVNote: WHard IP modeGen3x8, Interface: 256-bit, 250 MHz<br>Gen3x4, Interface: 128-bit, 250 MHz<br>Gen3x2, Interface: 128-bit, 250 MHz<br>Gen3x2, Interface: 64-bit, 125 MHz<br>Gen3x1, Interface: 64-bit, 125 MHz<br>Gen2x8, Interface: 128-bit, 125 MHz<br>Gen2x4, Interface: 64-bit, 125 MHz<br>Gen1x4, Interface: 64-bit, 125 MHz<br>Gen1x8, Interface: 64-bit, 125 MHz<br>Gen1x8, Interface: 64-bit, 125 MHz<br>Gen1x4, Interface: 64-bit, 125 MHz<br>Gen1x4, Interface: 64-bit, 125 MHz<br>Gen1x1, Interface: 64-bit, 62.5 MHzNote: W | Description                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gen3x4, Interface: 256-bit, 125 MHz<br>Gen3x4, Interface: 128-bit, 250 MHz<br>Gen3x2, Interface: 128-bit, 125 MHz<br>Gen3x2, Interface: 64-bit, 250 MHz<br>Gen3x1, Interface: 64-bit, 125 MHz<br>Gen2x8, Interface: 128-bit, 125 MHz<br>Gen2x4, Interface: 64-bit, 125 MHz<br>Gen2x4, Interface: 64-bit, 125 MHz<br>Gen1x8, Interface: 64-bit, 125 MHz<br>Gen1x8, Interface: 64-bit, 125 MHz<br>Gen1x4, Interface: 64-bit, 125 MHz<br>Gen1x4, Interface: 64-bit, 125 MHz<br>Gen1x2, Interface: 64-bit, 125 MHz<br>Gen1x1, Interface: 64-bit, 125 MHz<br>Gen1x1, Interface: 64-bit, 125 MHz<br>Gen1x1, Interface: 64-bit, 125 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | the interface to the Application Layer.<br>When the <b>Design Environment</b> parameter is<br>et to <b>System</b> , all four <b>Application Interface</b><br><b>'ypes</b> are available. However, when <b>Design</b><br><b>invironment</b> is set to <b>Standalone</b> , only<br><b>Avalon-ST</b> and <b>Avalon-ST</b> with <b>SR-IOV</b> are<br>available. |

| Deut true Deutine Enduciet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | the following elements:<br>lane data rate. Gen1, Gen2, and Gen3 are<br>ported<br>width of the data interface between the hard<br>ransaction Layer and the Application Layer<br>lemented in the FPGA fabric<br>Application Layer interface frequency<br>yclone <sup>®</sup> 10 GX devices support up to Gen2 x4<br>rations.                                  |

| Port type         Native Endpoint         Specifie           Root Port         Specifie         Specifie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | es the port type.                                                                                                                                                                                                                                                                                                                                           |

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

ISO 9001:2015 Registered

### 3. Parameter Settings 683686 | 2022.01.11

# intel

| Parameter                                                                | Value                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                          |                                | The Endpoint stores parameters in the Type 0<br>Configuration Space. The Root Port stores parameters<br>in the Type 1 Configuration Space.<br>The <b>Avalon-ST with SR-IOV</b> interface supports only<br><b>Native Endpoint</b> operation.<br>You can enable the Root Port in the current release.<br>Root Port mode only supports the Avalon <sup>®</sup> -MM<br>interface type, and it only supports basic simulation<br>and compilation. However, the Root Port mode is not<br>fully verified.                                                                                                                                                             |

| RX Buffer credit<br>allocation -<br>performance for<br>received requests | Minimum<br>Low<br>Balanced     | Determines the allocation of posted header credits,<br>posted data credits, non-posted header credits,<br>completion header credits, and completion data<br>credits in the 16 KB RX buffer. The settings allow you<br>to adjust the credit allocation to optimize your system.<br>The credit allocation for the selected setting displays<br>in the <b>Message</b> pane. The <b>Message</b> pane<br>dynamically updates the number of credits for Posted,<br>Non-Posted Headers and Data, and Completion<br>Headers and Data as you change this selection.                                                                                                     |

|                                                                          |                                | <ul> <li>Refer to the <i>Throughput Optimization</i> chapter for more information about optimizing your design.</li> <li>Refer to the <i>RX Buffer Allocation Selections Available by Interface Type</i> below for the availability of these settings by interface type.</li> <li>Minimum—configures the minimum PCIe specification allowed for non-posted and posted request credits, leaving most of the RX Buffer space for received completion header and data. Select this option for variations where application logic generates many</li> </ul>                                                                                                        |

|                                                                          |                                | read requests and only infrequently receives single<br>requests from the PCIe link.<br><b>Low</b> —configures a slightly larger amount of RX Buffer<br>space for non-posted and posted request credits, but<br>still dedicates most of the space for received<br>completion header and data. Select this option for<br>variations where application logic generates many<br>read requests and infrequently receives small bursts<br>of requests from the PCIe link. This option is<br>recommended for typical endpoint applications where<br>most of the PCIe traffic is generated by a DMA engine<br>that is located in the endpoint application layer logic. |

|                                                                          |                                | Balanced—configures approximately half the RX<br>Buffer space to received requests and the other half of<br>the RX Buffer space to received completions. Select<br>this option for variations where the received requests<br>and received completions are roughly equal.                                                                                                                                                                                                                                                                                                                                                                                       |

| RX Buffer<br>completion<br>credits                                       | Header credits<br>Data credits | Displays the number of completion credits in the 16<br>KB RX buffer resulting from the credit allocation<br>parameter. Each header credit is 16 bytes. Each data<br>credit is 20 bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## 3.2. Intel Arria 10 Avalon-ST Settings

## Table 10. System Settings for PCI Express

| Parameter                                                            | Value  | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable Avalon-ST<br>reset output port                                | On/Off | When <b>On</b> , the generated reset output port has the same functionality that the reset_status port included in the Reset and Link Status interface.                                                                                                                                                                                                                                                        |

| Enable byte parity<br>ports on Avalon-<br>ST interface               | On/Off | <ul> <li>When <b>On</b>, the RX and TX datapaths are parity protected. Parity is odd. The Application Layer must provide valid byte parity in the Avalon-ST TX direction.</li> <li>This parameter is only available for the Avalon-ST Intel Arria 10 Hard IP for PCI Express.</li> </ul>                                                                                                                       |

| Enable multiple<br>packets per cycle<br>for the 256-bit<br>interface | On/Off | When <b>On</b> , the 256-bit Avalon-ST interface supports the transmission of TLPs starting at any 128-bit address boundary, allowing support for multiple packets in a single cycle. To support multiple packets per cycle, the Avalon-ST interface includes 2 start of packet and end of packet signals for the 256-bit Avalon-ST interfaces. This is not supported for the Avalon-ST with SR-IOV interface. |

| Enable credit<br>consumed<br>selection port                          | On/Off | When you turn on this option, the core includes the tx_cons_cred_sel port. This parameter does not apply to the Avalon-MM interface.                                                                                                                                                                                                                                                                           |

| Enable<br>Configuration<br>bypass (CfgBP)                            | On/Off | When <b>On</b> , the Intel Arria 10 Hard IP for PCI Express bypasses the<br>Transaction Layer Configuration Space registers included as part of the Hard<br>IP, allowing you to substitute a custom Configuration Space implemented in<br>soft logic.<br>This parameter is not available for the Avalon-MM IP Cores.                                                                                           |

| Enable local<br>management<br>interface (LMI)                        | On/Off | When <b>On</b> , your variant includes the optional LMI interface. This interface is used to log error descriptor information in the TLP header log registers. The LMI interface provides the same access to Configuration Space registers as Configuration TLP requests.                                                                                                                                      |

## **Related Information**

PCI Express Base Specification 3.0

## 3.3. Intel Arria 10 SR-IOV System Settings

| Parameter                                                                                                                   | Value     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Total Physical Functions (PFs) :                                                                                            | 1 - 8     | This core supports 1 - 8 Physical Functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Total Virtual Functions of<br>Physical Function0 (PF0 VFs) -<br>Total Virtual Functions of<br>Physical Function7 (PF7 VFs): | 0 - 2048  | <ul> <li>Total number of VFs assigned to a PF. You can assign VFs in the following granularities:</li> <li>Granularity of 1 for 1-8 VFs</li> <li>Granularity of 4 for 8-256 VFs</li> <li>Granularity of 64 for 256-1024 VFs</li> <li>Granularity of 512 for 1024-2048 VFs</li> <li>The sum of VFs assigned to all PFs cannot exceed the 2048 VF total.</li> <li><i>Note:</i> The granularity restriction for assigning VFs applies to both the total VFs of each individual PF as well as the sum of all VFs across all enabled PFs. See the example and snapshot following this table for more details.</li> </ul> |

| System Supported Page Size:                                                                                                 | 4KB - 4MB | Specifies the pages sizes supported. Sets the Supported Page Sizes register of the SR-IOV Capability structure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Enable SR-IOV Support                                                                                                       | On/Off    | When <b>On</b> , the variant supports multiple PFs and VFs. When <b>Off</b> , .supports PFs only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                             |           | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

### 3. Parameter Settings 683686 | 2022.01.11

# intel

| Parameter                                                                                                                                                              | Value  | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable Alternative Routing-ID<br>(ARI) support                                                                                                                         | On/Off | When <b>On</b> , ARI supports up to 256 functions. Refer to <i>Section</i> 6.1.3 Alternative Routing-ID Interpretation (ARI) of the PCI Express Base Specification for more information about ARI.                                                                                                                                                                                                                                    |

| Enable Functional Level Reset<br>(FLR)                                                                                                                                 | On/Off | When <b>On</b> , each function has its own, individual reset.                                                                                                                                                                                                                                                                                                                                                                         |

| Enable TLP Processing Hints<br>(TPH) support for PFs                                                                                                                   | On/Off | When <b>On</b> , the variant includes the TPH registers to help you                                                                                                                                                                                                                                                                                                                                                                   |

| Enable TLP Processing Hints<br>(TPH) support for VFs                                                                                                                   |        | improve latency and traffic congestion.                                                                                                                                                                                                                                                                                                                                                                                               |

| Enable Address Translation<br>Services (ATS) support for PFs                                                                                                           | On/Off | When <b>O</b> n the unright includes the ATC registers                                                                                                                                                                                                                                                                                                                                                                                |

| Enable Address Translation<br>Services (ATS) support for VFs                                                                                                           |        | When <b>On</b> , the variant includes the ATS registers.                                                                                                                                                                                                                                                                                                                                                                              |

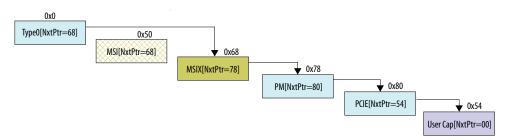

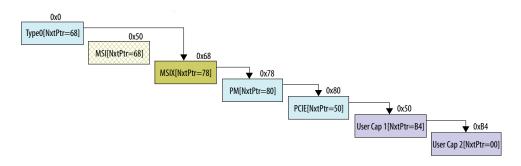

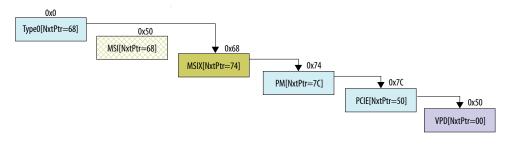

| Enable PCI Express Extended<br>Space (CEB)                                                                                                                             | On/Off | When On, the IP core variant includes the optional Configuration Extension Bus (CEB) interface. This interface provides a way to add extra capabilities on top of those available in the internal configuration space of the SR-IOV Bridge. <sup>(1)</sup>                                                                                                                                                                            |

| CEB PF External Standard<br>Capability Pointer Address (DW<br>Address in Hex)                                                                                          | 0x0    | Specifies the address for the next pointer field of the last<br>capability structure within the SR-IOV bridge for the physical<br>function. It allows the internal PCI Compatible region<br>capability to point to the capability implemented in user logic<br>and establish the link list for the first 256 bytes in the register<br>address space.                                                                                  |

| Capability Pointer Address (DW       capability s         Address in Hex)       function. It         capability to       and establis         space.       Supports th |        | Specifies the address for the next pointer field of the last<br>capability structure within the SR-IOV bridge for the physical<br>function. It allows the internal PCI Compatible region<br>capability to point to the capability implemented in user logic<br>and establish the link list for the PCIe extended configuration<br>space.<br>Supports the address range from 0x100 (DW address) or<br>0x400 (byte address) and beyond. |

| CEB VF External Standard<br>Capability Pointer Address (DW<br>Address in Hex)                                                                                          | 0x0    | Specifies the address for the next pointer field of the last<br>capability structure within the SR-IOV bridge for the virtual<br>function. It allows the internal PCI Compatible region<br>capability to point to the capability implemented in user logic<br>and establish the link list for the first 256 bytes in the register<br>address space.                                                                                   |

| CEB VF External Extended<br>Capability Pointer Address (DW<br>Address in Hex)                                                                                          | 0x0    | Specifies the address for the next pointer field of the last<br>capability structure within the SR-IOV bridge for the virtual<br>function. It allows the internal PCI Compatible region<br>capability to point to the capability implemented in user logic<br>and establish the link list for the PCIe extended configuration<br>space.<br>Supports the address range from 0x100 (DW address) or<br>0x400 (byte address) and beyond.  |

| CEB REQ to ACK Latency (in Clock<br>Cycles)                                                                                                                            | 1 - 7  | Specifies the timeout value for the request issued on the CEB interface. The SR-IOV bridge will send a completion with all zeros in the data and completion status field back to the host after the timeout.<br>Note: A large ACK latency time may result in a bandwidth degradation.                                                                                                                                                 |

(1) To implement user capabilities registers, Intel recommends that you use an open address space in the configuration space across all available Physical Functions (PFs) and Virtual Functions (VFs). Developing user capabilities registers for individual PFs or VFs is not possible.

The granularity restriction for assigning VFs applies to both the total VFs of each individual PF as well as the sum of all VFs across all enabled PFs. For example, the setting in the snapshot below is invalid since the sum of all VFs assigned to all PFs (i.e, 268 VFs) is not a multiple of 64 and therefore does not meed the granularity restriction even though the VF counts of individual PFs are valid (i.e, they are multiples of 4).

| ( |             |                                                                         | ug and Extension Options | PHY Charac |                    |

|---|-------------|-------------------------------------------------------------------------|--------------------------|------------|--------------------|

| ľ | System      | Settings Avalon-ST Settings SR-IOV System Settings                      | SR-IOV Base Address Reg  | listers    | Device Identificat |

|   | Total Phys  | sical Functions (PFs):                                                  | 4                        |            |                    |

|   | Total Virtu | al Functions of Physical Function0 (PF0 VFs):                           | 64                       |            | =                  |

|   | Total Virtu | al Functions of Physical Function1 (PF1 VFs):                           | 68                       |            | =                  |

|   | Total Virtu | al Functions of Physical Function2 (PF2 VFs):                           | 68                       |            | =                  |

|   | Total Virtu | al Functions of Physical Function3 (PF3 VFs):                           | 68                       |            | =                  |

|   | Supported   | i page sizes:                                                           | 4KB, 8KB, 64KB, 256KB, 1 | MB, 4MB    | -                  |

|   | 🖌 Enabl     | e SR-IOV support                                                        |                          |            |                    |

|   | 🖌 Enabl     | e Alternative Routing-ID Interpretation (ARI) support                   |                          |            |                    |

|   | 📃 Enabl     | e TLP Processing Hints (TPH) for PFs (0 to 3)                           |                          |            |                    |

|   | Enabl       | e TLP Processing Hints (TPH) for VFs                                    |                          |            |                    |

|   | Enabl       | e Address Translation Services (ATS) for PFs (0 to 3)                   |                          |            |                    |

|   | 🔄 Enabl     | e Address Translation Services (ATS) for VFs                            |                          |            |                    |

|   | 🖌 Enabl     | e PCI Express Extended Space (CEB)                                      |                          |            |                    |

|   | CEB P       | PF External Standard Capability Pointer Address (DW address in Hex):    | 0x0000001b               |            |                    |

|   | CEB P       | PF External Extended Capability Pointer Address (DW address in Hex):    | 0x00000000               |            |                    |

|   | CEBV        | /F External Standard Capability Pointer Address (DW address in Hex):    | 0x00000000               |            |                    |

|   | CEB V       | /F External Extended Capability Pointer Address (DW address in Hex):    | 0x00000000               |            |                    |

|   | CEB F       | REQ to ACK latency (in Clock Cycles) :                                  | 1                        |            |                    |

|   |             |                                                                         |                          |            |                    |

| • |             |                                                                         |                          |            |                    |

| - | ramotoriz   | ation Messages                                                          |                          |            |                    |

| a |             |                                                                         |                          |            |                    |

| Ŷ | Туре        | Messag                                                                  | le                       |            |                    |

|   |             | The empty signal width should be 1 bits.                                |                          |            |                    |

|   | <u> </u>    | The empty signal width should be 1 bits.                                |                          |            |                    |

| የ | 8           |                                                                         |                          |            |                    |

|   | 8           | TOTAL_VF count must be set in multiple of 64. It is short by 52 to beco | ome multiple of 64       |            |                    |

| Ŷ | 0           |                                                                         |                          |            |                    |

## **Related Information**

PCI Express Base Specification 2.1 or 3.0

## 3.4. Base Address Register (BAR) Settings

Each function can implement up to six BARs. You can configure up to six 32-bit BARs or three 64-bit BARs for both PFs and VFs. The BAR settings are the same for all VFs associated with a PF.

### Table 11. BAR Registers

| Parameter              | Value            | Description                                               |  |

|------------------------|------------------|-----------------------------------------------------------|--|

| Present<br>(BAR0-BAR5) | Enabled/Disabled | Indicates whether or not this BAR is instantiated.        |  |

| Туре                   | 32-bit address   | <b>32-bit address</b> Specifies 32- or 64-bit addressing. |  |

|                        |                  | continued                                                 |  |